基于TS101和FPGA的视频综合模块的设计与实现

基于FPGA的视频处理系统设计与实现

基于FPGA的视频处理系统设计与实现随着数字化技术与高清视频的普及,基于FPGA的视频处理系统的应用也越来越广泛。

它们可以满足人们对于视频质量、速度和响应性能的要求。

FPGA作为一种高度可编程的器件,可根据应用需求任意重构电路结构,使得视频处理系统具有高度的扩展性、灵活性和定制性。

本文将从设计目标、系统结构、视频数据流传输、数字信号处理、硬件开发与软件开发等多个方面来介绍基于FPGA的视频处理系统的设计与实现。

一、设计目标在设计基于FPGA的视频处理系统时,我们需要考虑以下几个方面:1.视频质量:在视频的采集、传输和显示过程中需要确保视频的清晰、流畅和无噪音。

2.速度:视频处理系统需要具备高速的处理能力,可以迅速对视频进行处理,以达到实时性和响应性能。

3.低功耗:由于FPGA系统是基于硬件实现的,所以需要考虑低功耗来满足电源限制和延长电池寿命。

4.设计可重用:这就需要设计出可重用的平台,方便进行软件开发和硬件设计。

二、系统结构基于FPGA的视频处理系统的系统结构如图1所示。

它主要由三个部分组成:视频输入模块、视频处理模块和视频输出模块。

1.视频输入模块视频输入模块主要负责从相机或视频文件中采集视频数据,并将其转换成数字信号传输给FPGA。

该模块包括视频采集和视频解码两个部分。

2.视频处理模块视频处理模块主要是对采集到的视频数据进行处理,包括降噪、滤波、缩放、边缘检测、图像增强等操作。

它往往是FPGA设计的重点。

3.视频输出模块视频输出模块主要把处理好的视频数据输出到显示器、硬盘或网络等外设上,并在此过程中再次进行编码技术,使传输数据量减小,加快传输速度。

该模块还需要实现垂直同步、交错、逆交错等技术来保证视频输出的正确性和质量。

图1:基于FPGA的视频处理系统结构图三、视频数据流传输视频数据流传输是视频处理系统中非常重要的一环,它利用高带宽的总线来传输大量数据。

视频数据流传输主要有以下三种方式:1.像素传输像素传输是最常用的一种方式,它将每个像素的RGB值保存在一个字节中,并采用三根数据线分别传输每个像素的R、G、B值。

基于FPGA的视频处理系统设计

基于FPGA的视频处理系统设计随着科技的快速发展,视频技术在人们的日常生活中也得到了广泛的应用。

为了满足不同场景下的需求,高精度、高速度的视频处理系统成为了迫切需要解决的问题。

而基于FPGA的视频处理系统则成为了当下较为常用的一种实现方式。

一、FPGA的优势FPGA(Field Programmable Gate Array)是一种可编程数字电路的芯片。

和传统的ASIC(专用集成电路)相比,FPGA具有以下优势:1. 灵活性高,可以通过重新编程实现改变电路功能。

2. 可以实现高性能计算,处理效率高。

3. 集成度高,可以集成大量外设。

基于FPGA的视频处理系统正是利用了FPGA的优势来实现高效、高精度的视频处理。

二、视频处理系统的核心模块基于FPGA的视频处理系统通常包含以下核心模块:视频输入模块、视频输出模块、视频处理模块和控制模块。

现在我们分别来了解一下每个模块的功能:1. 视频输入模块视频输入模块用于将输入的视频信号转换成数字信号,并对数字信号进行预处理,以满足后续处理的需求。

通常会进行去噪、增强和格式转换等处理。

其中格式转换是非常重要的一步,因为不同的视频源可能采用不同的格式,统一格式可以方便后续处理。

2. 视频输出模块视频输出模块用于将处理好的数字信号转换成模拟信号,并输出到显示器或其他设备上。

在转换前,需要对数字信号进行一定的处理,常见的处理方式包括降噪和增强等。

3. 视频处理模块视频处理模块是整个系统的核心部分,它可以对数字信号进行各种形式的处理,如降噪、增强、滤波、压缩等。

其中压缩是视频处理中最重要的部分之一,因为视频信号通常会占用大量的存储空间和带宽资源。

视频压缩技术可以将视频信号压缩到较小的存储空间或带宽上,从而实现高效的存储和传输。

4. 控制模块控制模块用于控制整个视频处理系统的运行和参数配置等。

通常会使用外部开发板或者软件进行控制。

在控制模块的指导下,整个视频处理系统可以进行各种不同的操作,方便用户进行定制化的需求处理。

基于FPGA的视频缩放设计与实现

基于FPGA的视频缩放设计与实现

FPGA视频缩放是一种基于现场可编程门阵列(FPGA)实现的视频处理技术。

它通过对视频帧进行采样和重构,实现对视频尺寸的调整,从而满足不同的视觉需求。

本文将介绍FPGA视频缩放的设计与实现。

FPGA视频缩放的设计从以下几个方面展开:图像采集、图像处理和图像显示。

需要通过摄像头或者视频源采集视频图像,并将其传输到FPGA芯片内部。

然后,对采集到的视频图像进行处理,包括图像缩放、噪声滤波等操作。

将处理后的图像传输到显示设备,如显示器或者电视机。

在FPGA视频缩放的实现过程中,需要使用一些常用的图像处理算法和技术。

最常见的是双线性插值算法。

该算法利用附近的像素值来估计目标像素的值,以实现图像的缩放。

在此基础上,还可以使用其他的图像处理技术,如直方图均衡化、边缘检测等,以提高图像质量。

在设计FPGA视频缩放系统时,还需要考虑硬件资源和性能的问题。

FPGA芯片的资源有限,需要合理利用和分配。

视频处理过程中会涉及到大量的数据计算和存储,对FPGA芯片的性能要求较高。

需要对系统进行优化,采用并行计算和高速缓存等技术,以提高系统的性能和效率。

还需要考虑FPGA视频缩放系统的可靠性和可扩展性。

在设计过程中,需要进行模块化设计,将不同的功能模块进行划分和组合,以方便系统的测试和维护。

还应具备一定的可扩展性,以便于后期对系统进行升级和扩展。

基于FPGA的视频转换模块设计与实现

引 言

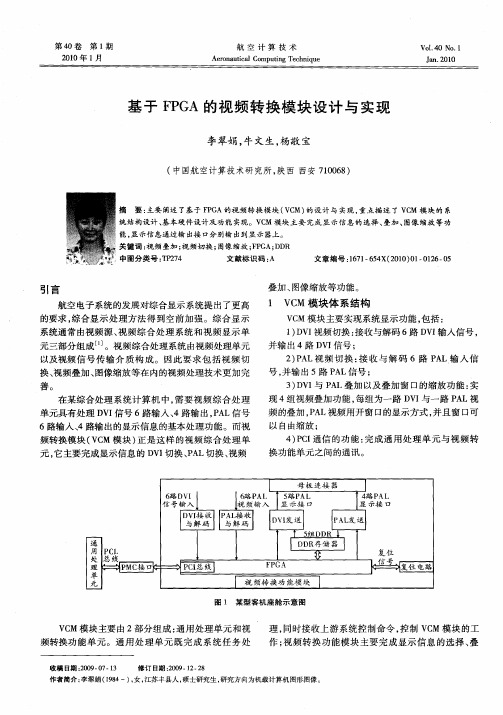

航 空 电子 系 统 的发 展对综 合显 示 系统提 出 了更 高 的要求 , 综合 显 示 处 理方 法 得 到 空前 加 强 。综 合显 示 系统通 常 由视频 源 、 频 综 合处 理 系 统 和视 频 显示 单 视 元三部 分组 成 。视频综 合处 理 系统 由视 频处 理单 元

样 , 以存 储 器设 备 的 内部 的数 据 存储 量 是 接 口数 据 所 存储 量 的两倍 ( 时钟 的上 升 沿 指 C 的上 升 沿 和 C K K#

V M 模块 采用 以现场 可 编程 逻 辑 阵 ( P A) 中 C FG 为 心 的组成 模 式 , 件 主 要 由 F G D I 解 码 芯 片 、 硬 P A、 V 编 P L编解 码芯 片 、 D A D R存 储 器 、 位 电路 、 MC接 口、 复 P

以及视 频 信 号 传 输 介 质 构 成 。 因此 要 求 包 括 视 频 切 换 、 频叠加 、 视 图像缩放 等 在 内的视频 处理 技术更 加 完 善。

叠加 、 图像 缩放等 功 能 。

1 VC 模 块 体 系结 构 M

V M模 块 主要实 现系 统显示 功 能 , C 包括 : 1D I ) V 视频 切换 : 接收 与解 码 6路 D I 入信 号 , V输 并输 出 4路 D I 号 ; V信

21 0 0年 1 月

李翠娟 等 : 于 F G 基 P A的视频转换模块设计与实现

加 、 口缩放 等 功 能 。通 用处 理 单 元 和 视 频转 换 功 能 窗

量 的数据 进行 高速 存储 , 因此需 要存 取 速度快 、 取 时 读 间 缩短 、 时性 匹配强 的存储 器 , D R( o beD t 实 而 D D u l aa

基于FPGA的多路视频合成系统的设计

产 品 的 调试 、修 改 及 升 级 比较 困难 ,成 本 较 高 。 F GA ( i dPo rmma l Ga ra ,现场 可编 P Fe rga l be t A ry e 程 门阵列 )器件具 有并行 处理 速度高 、集成 度高 、 功耗 低 、设 计灵活 等特 点 ,且 有快速 高效 的开 发平

帧 后 读 出 ,格 式 再 生 后送 入 视 频编 码 器 S 7 2 AA 1 1

1 多路视频合成系统 的组成结构

系统 以F GA为 核心 , 与视频 解 码模 块 、视 频 P 编码 芯片 和S AM等外 围器 件一起 构成 整个 多路视 R

还 原成模 拟信 号送 显示器 输 出 。

、 匐 l 造

基于F G P A的多路视频合成 系统的设计

Synt hesi y em s s st desi ul i de bas gn of m t- vi o ed on FPGA

陈文辉 ,覃永新 ,黄庆南

CHEN W en h iQ I o g xn HUANG n — a . u. N Y n — i, Qig n n

字视 频 信号 ,F G P A对其 进行 抽取 和 帧合 成等 数据

格 式 转换 ,再 通 过 视 频 编码 芯 片 的数 模 转 换 送入

VG A显示 器 ,可 显示 1 、9 6 分 割画面 ,并 、4 、1 路

通过 按键轮 流切 换视 频 画面 。

存 储 地 址 与屏 幕 中 的像 素 地 址 一 一对 应 ,写满 一

2 基 于F G P A的多路视频合成 系统 的

设计

图2 出了多路视 频合 成 系统 的内部结 构 图。 给

基于FPGA的视频缩放设计与实现

基于FPGA的视频缩放设计与实现FPGA(现场可编程门阵列)是一种可编程的集成电路芯片,因其灵活性和可重构性而广泛应用于嵌入式系统中。

视频缩放是一种常见的图像处理技术,可以将输入视频的分辨率调整为不同的大小。

本文将介绍基于FPGA的视频缩放设计与实现。

视频缩放的基本原理是通过插值算法来改变视频的分辨率。

常见的插值算法有最近邻插值、双线性插值和双三次插值等。

在FPGA中实现视频缩放,可以利用FPGA的并行计算能力和高性能特点来提高图像处理的效率和质量。

设计一个基于FPGA的视频缩放系统,主要包括以下几个步骤:需要定义输入和输出视频的分辨率。

输入视频的分辨率决定了系统的输入数据量,而输出视频的分辨率则是设计目标。

需要选择合适的插值算法。

最近邻插值是一种简单的插值算法,它会直接复制原始图像的像素点。

双线性插值通过对周围像素的加权平均来计算新像素的值,可以提供更平滑的图像。

双三次插值在双线性插值的基础上添加了更多的像素,可以提供更高的图像质量。

然后,需要设计并实现插值算法的硬件模块。

FPGA中的硬件模块可以利用并行计算来加快图像处理的速度。

根据选择的插值算法,可以设计相应的模块来进行像素的计算和写入。

需要进行系统的综合和验证。

综合是将设计代码转化为FPGA可使用的实际硬件资源的过程。

验证是通过对输入视频进行处理并与期望输出进行比较来确认系统的正确性。

基于FPGA的视频缩放系统有很多应用场景,如监控系统、视频通信系统和多媒体播放系统等。

通过利用FPGA的高性能和灵活性,可以实现高效的视频处理和优质的视觉效果。

基于FPGA的视频缩放设计与实现可以通过选择合适的插值算法、设计相应的硬件模块和进行系统的综合和验证来实现。

这种系统可以在各种应用场景中提供高效的视频处理和优质的视觉效果。

基于FPGA的视频缩放设计与实现

基于FPGA的视频缩放设计与实现随着数字视频技术的不断发展,视频缩放技术在媒体处理和通信领域中扮演着越来越重要的角色。

视频缩放技术能够对视频图像进行放大或缩小操作,以适应不同的显示设备或带宽要求。

在实际应用中,往往需要高效、实时地对视频进行缩放处理,利用FPGA实现视频缩放成为了一种重要的方法。

本文将介绍基于FPGA的视频缩放设计与实现。

首先将对视频缩放技术进行简要介绍,然后分析FPGA在视频缩放中的优势,接着将介绍基于FPGA 的视频缩放设计与实现流程,并最后进行总结。

一、视频缩放技术简介视频缩放技术是数字视频处理中的一种重要技术,其主要功能是根据目标设备的分辨率或显示需求,对原始视频图像进行放大或缩小操作。

视频缩放技术在电视、监控、视频会议、数字电视、数字信号处理等领域有着广泛的应用。

视频缩放技术的实现一般分为硬件和软件两种方式,其中硬件方式通常采用专用芯片或FPGA实现,能够提供更高的处理速度和更低的时延。

二、FPGA在视频缩放中的优势FPGA(Field-Programmable Gate Array)是一种可编程的数字集成电路,具有灵活性强、时序可控、并行性好等优势。

在视频处理中,FPGA能够利用其并行处理能力和高速IO 接口,实现高效、实时的视频缩放处理。

相比于软件方法,利用FPGA实现视频缩放能够获得更高的性能和更低的功耗。

三、基于FPGA的视频缩放设计与实现1. 系统架构设计基于FPGA的视频缩放系统通常由视频输入接口、视频缓存、视频缩放核以及视频输出接口等部分组成。

视频输入接口负责接收原始视频信号,视频缓存用于暂存视频数据,视频缩放核实现视频图像的缩放操作,视频输出接口将处理后的视频信号输出到显示设备中。

2. 视频缩放算法视频缩放算法是视频缩放系统的关键,常用的视频缩放算法有双线性插值法、最近邻插值法、双三次插值法等。

在FPGA实现视频缩放时,通常会选择适合硬件实现的算法,以提高处理速度和降低资源消耗。

基于FPGA的视频处理系统设计与实现

基于FPGA的视频处理系统设计与实现一、引言随着科技的不断发展,视频处理技术在各个领域中扮演着越来越重要的角色。

而基于现场可编程门阵列(Field-Programmable Gate Array,FPGA)的视频处理系统由于其灵活性和高性能而备受关注。

本文将探讨基于FPGA的视频处理系统的设计与实现,包括系统架构、关键技术和应用场景等方面的内容。

二、系统架构设计基于FPGA的视频处理系统通常包括视频输入模块、图像处理模块和视频输出模块三个主要部分。

其中,视频输入模块负责接收外部视频信号并将其转换为数字信号;图像处理模块则对接收到的视频数据进行各种算法处理,如滤波、边缘检测、目标识别等;最后,视频输出模块将处理后的视频信号输出到显示设备上。

三、关键技术1. FPGA编程FPGA作为一种可编程逻辑器件,其编程是基于硬件描述语言(HDL)进行的。

常用的HDL包括Verilog和VHDL,开发人员需要熟练掌握这些语言以实现对FPGA的编程。

2. 视频信号处理算法在视频处理系统中,各种算法对系统性能起着至关重要的作用。

常见的视频处理算法包括运动估计、帧间压缩、图像增强等,开发人员需要根据实际需求选择合适的算法并进行优化。

3. 性能优化由于视频处理对计算资源要求较高,因此在设计系统时需要考虑如何优化性能。

这包括合理分配硬件资源、设计高效的算法以及减少功耗等方面。

四、应用场景基于FPGA的视频处理系统在各个领域都有广泛的应用,例如智能监控、医疗影像分析、工业检测等。

这些应用场景对系统性能和稳定性提出了更高的要求,同时也为FPGA技术的发展提供了更多可能性。

五、实现案例以智能监控系统为例,我们可以设计一个基于FPGA的视频处理系统,实现对监控画面的实时分析和识别。

通过结合图像处理算法和硬件加速技术,可以提高监控系统的响应速度和准确性,从而更好地满足用户需求。

六、总结基于FPGA的视频处理系统具有灵活性高、性能优越等优点,在各个领域都有着广阔的应用前景。

基于FPGA的视频缩放设计与实现

基于FPGA的视频缩放设计与实现FPGA(Field Programmable Gate Array)是一种可编程的硬件,可以用来实现各种数字电路。

FPGA在视频处理方面具有很大的潜力,可以用来实现视频的缩放、转换等功能。

本文将介绍基于FPGA的视频缩放设计与实现。

1. FPGA基础知识FPGA是一种可编程的逻辑器件,内部由大量的可编程逻辑单元(CLB)、存储单元、IO 资源等组成。

利用FPGA的可编程特性,可以将数字电路实现在FPGA的逻辑单元上,从而实现各种功能。

FPGA具有并行处理能力和灵活的可编程特性,非常适合用来实现视频处理相关的功能。

2. 视频信号基础视频信号是由一系列的图像帧组成的,每一帧都是由像素构成的。

视频的分辨率表示了每一帧的像素数量,分辨率越高,画面越清晰。

视频的缩放就是改变视频的分辨率,可以将视频的分辨率调整为更高或更低的值。

3. 视频缩放原理视频缩放可以通过插值算法实现,常用的插值算法有最近邻插值、双线性插值、双三次插值等。

在FPGA中实现视频缩放,通常采用像素重复和插值相结合的方法,先将原始视频的像素点复制到更大的画面中,然后通过插值算法填充空白像素点,从而实现视频的缩放。

(1)视频输入模块:将视频信号输入到FPGA中,通常需要将视频信号转换为数字信号,再输入到FPGA的输入模块中。

(2)视频存储模块:将视频信号存储到FPGA的存储模块中,以便后续的处理。

(3)视频处理模块:在FPGA的可编程逻辑单元中实现视频的缩放算法,包括像素重复和插值处理。

(4)视频输出模块:将处理后的视频信号输出到显示设备或存储设备中。

基于FPGA的视频缩放实现可以采用Verilog或VHDL等硬件描述语言来实现视频处理模块。

首先需要设计视频信号处理模块,包括视频输入模块、视频处理模块和视频输出模块。

然后根据视频处理算法编写Verilog或VHDL代码,将视频处理模块实现在FPGA的可编程逻辑单元中。

基于FPGA的高性能视频采集与处理系统设计

基于FPGA的高性能视频采集与处理系统设计随着现代科技的发展,视频数据应用越来越广泛。

为了满足高性能视频采集与处理的需求,我们设计了一套基于FPGA(现场可编程门阵列)的系统。

本文将详细介绍该系统的设计原理、技术细节和应用场景。

一、设计原理基于FPGA的高性能视频采集与处理系统的设计原理是利用FPGA的并行处理能力和灵活性,通过硬件描述语言来实现视频信号的采集、处理和输出。

二、系统架构该系统的架构包括视频输入模块、视频处理模块和视频输出模块。

1. 视频输入模块视频输入模块通过视频采集卡或接口板来接收外部视频信号,并将信号转化为数字信号,以供后续处理。

2. 视频处理模块视频处理模块是整个系统的核心部分。

它包括图像采样、预处理、压缩编码和图像增强等功能。

在FPGA中,可以使用图像采样芯片通过并行采样技术实现高速、高精度的视频采集。

针对图像预处理,可以利用FPGA内部的逻辑电路来实现图像滤波、边缘检测、运动检测等。

压缩编码部分可以采用现有的视频编码算法,如H.264或HEVC,并利用FPGA的并行计算能力来加速编码过程。

图像增强功能可以通过FPGA内部的图像处理单元来实现,例如对比度增强、色彩调整和图像修复等。

3. 视频输出模块视频输出模块将处理后的视频信号输出到显示设备或其他存储设备。

可以通过HDMI接口或其他视频输出接口将信号传输到显示屏,也可以通过网络接口将信号传输到服务器或存储设备。

三、技术细节1. FPGA的选择在设计高性能视频采集与处理系统时,选择适合的FPGA芯片非常重要。

需要考虑FPGA的逻辑单元数量、存储资源和计算能力。

较新的FPGA芯片,如Xilinx Virtex UltraScale+系列或Intel Stratix 10系列,拥有更强的计算和存储能力,适合处理高分辨率的视频信号。

2. 硬件描述语言硬件描述语言(HDL)是实现FPGA设计的关键工具。

常用的HDL语言包括Verilog和VHDL。

基于FPGA的视频叠加融合系统设计与实现

基于 F P G A的视频叠加融合系统设计与实现

万 鹏, 杨 大 伟

( 哈 尔滨 工程 大 学 信 息 与通 信 工 程 学 院 , 黑 龙 江 哈 尔滨 1 5 0 0 0 1 )

F P G A i s d e s i g n e d a n d i m p l e m e n t e d . T h e s y s t e m c a n a d j u s t p r o p o r t i o n o f s i z e a n d l o c a t i o n o f t h e v i d e o i m a g e s u p e r i m p o s e d f u s i o n

Wa n Pe ng, Ya n g Da we i

( C o l l e g e o f I n f o r ma t i o n a n d C o m mu n i c a t i o n E n g i n e e r i n g , Ha r b i n E n g i n e e i r n g U n i v e r s i t y, Ha e r b i n 1 5 0 0 0 1 , C h i n a )

摘 要 :针 对 两 通 道 视 频 图 像 叠 加 融 合 ,设 计 并 实 现 了 一 种 实 时 性 好 、 灵 活 性 强 的 F P G A硬 件 系

统 。该 系 统 可 以根 据 实 际 需 求 进 行 任 意 比 例 和 任 意 位 置 的 视 频 图像 叠 加 融 合 。方 案 经 仿 真 验 证 后 , 运

用 双 线性 插值 缩放 算 法 、 D D R 2存 储 以及 叠 加 融合 等技 术在 F P G A硬 件 平 台上 实现 。 结 果表 明 , 该 系统

基于FPGA的视频缩放设计与实现

基于FPGA的视频缩放设计与实现引言随着现代科技的发展,视频技术已经成为人们生活中不可或缺的一部分。

视频数据量大,对硬件性能要求较高,因此需要进行视频数据的处理和优化。

视频缩放是视频处理中的一个重要环节,其在视频传输、显示和存储等方面具有广泛的应用。

本文将介绍基于FPGA(Field Programmable Gate Array)的视频缩放设计与实现。

一、视频缩放原理视频缩放是指改变视频图像的尺寸大小,包括放大和缩小两种操作。

在数字视频处理中,视频数据以像素矩阵的形式表示,因此视频缩放实质上是对像素数据进行重新采样和插值。

视频缩放的实现一般包括以下几个步骤:输入视频数据读取、图像缩放计算、数据插值和输出处理。

1. 输入视频数据读取:视频数据一般以数字信号的形式输入到FPGA中,需要将视频数据转换为FPGA可处理的格式。

常见的视频接口有HDMI、VGA等,需要通过适配器或者解码器将视频数据转换为FPGA可直接处理的数字信号。

2. 图像缩放计算:图像缩放是通过插值算法来实现的,常见的插值算法有最近邻插值、双线性插值、三次样条插值等。

这些算法都需要对每个输出像素的位置进行计算和插值,以从输入图像中获取相应的像素值。

3. 数据插值:数据插值是指根据输入像素的位置和值来计算输出像素的值。

不同的插值算法会对图像质量和处理性能产生不同的影响,需要根据具体的应用场景选择合适的插值算法。

4. 输出处理:经过插值计算得到的新的像素数据需要进行输出处理,将其转换为适合输出设备显示的格式,并发送到输出接口进行显示或者存储。

FPGA是一种可编程的数字电路,具有灵活的硬件设计能力和高性能的并行处理能力,非常适合用于视频处理和图像处理。

基于FPGA的视频缩放设计需要结合硬件逻辑的设计和数字信号处理的算法实现,具体步骤如下:1. 硬件逻辑设计:视频缩放需要涉及大量的并行计算和数据流处理,因此需要设计合理的硬件逻辑结构来实现。

基于FPGA的视频采集显示系统设计

基于FPGA的视频采集显示系统设计

随着数字技术的迅猛发展和市场需求的急剧增长,视频采集和显示系统成为了一种必不可少的应用。

基于FPGA技术,可以开发出高效、可靠、灵活的视频采集和显示系统,满足不同领域的需求。

本文将介绍一个基于FPGA的视频采集显示系统设计方案,主要包括硬件设计和软件设计两个部分。

硬件设计:

1、采集模块:使用高清摄像头作为采集设备,通过FPGA芯片的MIPI接口采集视频信号,实现高清输出。

2、处理模块:将采集到的视频信号传输到FPGA芯片中,对视频信号进行处理和编码,包括颜色空间转换、降噪、滤波等处理方法,同时进行图像压缩,减小数据量的同时提高传输速率。

3、显示模块:将处理后的视频信号经过FPGA芯片的HDMI 接口输出到显示器上,实现高清视频的显示。

软件设计:

1、FPGA芯片的FPGA逻辑设计:采用VHDL语言进行数字电路设计,实现采集模块、处理模块和显示模块的逻辑功能。

2、CPU端软件设计:控制FPGA芯片的视频处理流程,包括采集、处理和显示过程控制,以及图像参数设置等功能。

总结:

基于FPGA技术的视频采集和显示系统,具有高效、可靠、灵活的特点。

本方案将摄像头作为采集设备,通过FPGA芯片的处理和编码模块进行处理,实现了高清视频的输出,并且简化了视频数据的传输。

通过FPGA芯片的逻辑设计和CPU 端软件设计,实现了简单的控制和参数设置功能,提高了效率和便捷性。

未来,基于FPGA的视频采集和显示系统将成为数字视频技术的重要组成部分,助力推动数字技术的发展。

基于fpga的视频显示系统设计与实现

摘要随着多媒体时代的到来,视频已经成为人们获取信息的重要方式,因此视频显示技术成为目前的研究热点。

目前视频显示方式大致分为ASIC显示方式和FPGA显示方式两类。

通常ASIC显示方式具有高成本、通用性低和不易更改等缺点,与此相比FPGA显示方式则具有明显优势,且适用性更广。

本文选取Altera公司的Cyclone V系列FPGA芯片作为处理平台,以红外探测器作为视频数据来源,采用FPGA显示方式实现视频显示系统。

本文的主要工作内容分为系统总体设计、视频采集处理和视频显示三部分。

系统总体设计部分:介绍系统的总体硬件架构和系统的FPGA实现框图。

视频采集处理部分:通过SPI协议配置A/D芯片,将驱动红外探测器后输出的模拟视频信号转换为数字视频信号,并对数字视频信号进行一系列相关算法处理。

视频显示部分:分为两路显示,一路将RGB 格式的数字视频信号转换为YCbCr格式,然后进行CVBS视频编码并利用ADV7127进行数模转换得到CVBS模拟视频信号,输出到电视机上显示;另一路对数字视频信号进行图像缩放处理,然后进行HDMI视频编码和并串转换得到三路单比特数据信号和一路时钟信号,输出到HDMI显示器上显示。

本文利用EDA设计工具Modelsim对系统中各个模块进行仿真并上板调试,验证各个模块功能的正确性,最后将各个模块融合设计成视频显示系统。

实验表明,该系统稳定可靠,显示效果良好,工作温度范围广。

关键词:视频显示CVBS HDMI FPGA ModelsimABSTRACTWith the arrival of the multimedia era, video has become an important way to get information, so the video display technology has become the current hot research. There are generally two kinds of display patterns now: ASIC display pattern and FPGA display pattern. In general, ASIC display pattern has disadvantages of high cost, low generality and not easy to change, however, FPGA display pattern avoids these and has wider usage.The article selects the Cyclone V FPGA produced by Altera as processing platform and the infrared detector as video data sources, which enable us to realize video display system by FPGA display pattern. The main work in this article is divided into three parts: the overall design of system, video capturing and processing and video display. The first part, the overall design of system, introduces the hardware architecture and the realization of the system based on FPGA. The second part, video capturing and processing, includes converting analog video signal which is gotten by driving infrared detector into digital video signal by configuring analog-to-digital chip with SPI, and then processing digital video signal with a series of algorithms. The third part, video display, includes two ways of display. The one includes encoding digital video signal of YCbCr format with CVBS, which is converted from digital video signal of RGB format, and then converting digital video signal after encoding into analog video signal through ADV7127 which outputs to TV. The other includes encoding video signal after image scaling with HDMI, and then converting digital video signal after encoding into three single bits of data signal and a clock signal which outputs to HDMI display.This article simulates each module in the system with EDA tools Modelsim and debugs it on the board to prove the validity of the function of each module, which finally is integrated into video display system. The results of experiments show that the system is stable and reliable, and displays and works well in wide temperature range.Keywords:Video display CVBS HDMI FPGA Modelsim目录摘要 (I)ABSTRACT (II)目录................................................................................................................. I II 1 绪论1.1 研究背景和目的意义 (1)1.2 视频显示技术概述 (2)1.3 视频显示方式发展现状 (4)1.4 本文研究内容和结构安排 (6)2系统设计平台及接口规范2.1 系统设计平台 (8)2.2 CVBS显示接口标准 (10)2.3 HDMI显示接口标准 (14)2.4 本章小结 (20)3 视频显示系统设计与FPGA实现3.1 系统总体设计 (21)3.2 视频采集处理部分 (26)3.3 CVBS显示模块 (31)3.4 HDMI显示模块 (38)3.5 本章小结 (45)4 系统仿真与实验结果4.1 系统仿真 (46)4.2 实验结果 (50)4.3 本章小结 (55)5总结和展望5.1 总结 (56)5.2 展望 (57)致谢 (58)参考文献 (59)1绪论1.1研究背景和目的意义红外线进入人们的视野始于1800年英国物理学家威廉·赫歇尔使用三棱镜分解太阳光的实验,自此红外线进入高速发展期。

基于FPGA的视频缩放设计与实现

基于FPGA的视频缩放设计与实现视频缩放主要是指将一个视频信号按照一定的比例进行放大或缩小,以适应不同尺寸的显示设备。

在实现视频缩放功能时,需要考虑到图像质量的保持和计算的复杂性。

设计一个高效的视频缩放系统是至关重要的。

1. 视频输入与输出模块设计:通过视频输入模块将视频信号输入到FPGA芯片中,然后通过视频输出模块将处理后的视频信号输出到显示设备。

这两个模块需要对视频信号进行采样、处理和传输,确保视频信号的稳定和可靠性。

2. 图像缩放算法选择:常用的视频缩放算法包括双线性插值算法、双三次插值算法等。

选择适合 FPGA 实现的算法是非常重要的,需要考虑算法的计算复杂度和资源占用情况。

3. FPGA架构设计:根据所选的视频缩放算法,设计FPGA的逻辑架构。

可以利用FPGA 的并行计算能力,将视频帧分块处理,降低计算复杂度。

对于图像数据在 FPGA 内部的存储和传输方式也需要进行合理的设计。

4. 高效的图像处理流水线设计:为了提高图像处理的效率,可以将处理过程划分为多个阶段,并通过流水线的方式来进行并行处理。

这样可以避免不必要的数据依赖,提高处理速度。

5. 内存和带宽管理:视频缩放需要对数据进行存储和传输,因此需要合理管理FPGA 内部的存储器资源。

由于视频数据量大,需要考虑存储器和带宽的管理方式,以充分利用FPGA的资源。

6. 开发工具的选择:选择合适的FPGA开发工具,如Vivado、Quartus等,进行视频缩放系统的设计和实现。

这些开发工具提供了完善的设计工具和调试功能,能够提高开发效率和方便调试。

基于FPGA的视频缩放设计与实现可以满足不同场景下的视频需求,如将高分辨率的视频信号缩小适应低分辨率的显示设备,或将低分辨率的视频信号放大适应高分辨率的显示设备。

通过合理的设计和优化,可以实现高效、稳定的视频缩放系统。

基于FPGA的视频格式转换电路设计

基于FPGA的视频格式转换电路设计近年来,随着多媒体技术的快速发展,高清视频已经成为了现代社会中不可或缺的一部分。

但是由于硬件与软件的兼容性问题,不同的视频设备之间无法兼容最新的高清视频格式,给用户的使用带来了很大的不便。

为了解决这个问题,我们设计了一种基于FPGA的视频格式转换电路,能够将各种高清视频格式进行转换,从而实现兼容性。

FPGA(Field Programmable Gate Array,现场可编程门阵列)是一种高度灵活、可编程的硬件平台。

它能够快速重构电路,适应各种应用场景。

基于FPGA的视频格式转换电路,不仅可以进行高效的对数码视频信号的处理,还能够适应不同的视频格式,以及支持多种信号的输入和输出。

该电路主要由三个部分组成:输入信号口、输出信号口和控制器。

其中,输入信号口用于接收各种视频输入信号,例如HDMI、VGA等,输出信号口用于输出高清视频信号,而控制器则能够控制视频输入、输出以及信号格式的转换。

在设计中,我们采用了一种数字信号处理器(DSP)的方式实现视频格式的转换。

该处理器可实现多种转换模式,包括分辨率、色彩空间以及帧速率等转换。

同时,还可以实现多路视频输入的混合处理,从而满足不同用户的需求。

此外,我们还加入了一些特别的功能,例如实时物体检测技术、人脸识别技术等。

这些技术能够对视频进行特殊的处理,以响应用户对不同视频应用领域中的不同需求,提高整个系统的性能和用户体验。

总之,基于FPGA的视频格式转换电路,具有灵活性高、功能齐全、性能稳定的特点。

它能够有效地解决多种视频格式之间的兼容问题,适应各种全色、分辨率、帧速率等多种转换模式,实现多路视频信号的同时混合处理,为现代社会提供更为优质的视频享受。

基于FPGA的视频缩放设计与实现

基于FPGA的视频缩放设计与实现FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,可以在硬件中实现各种复杂的数字电路。

由于其具有高度灵活性和可重构性的特点,FPGA被广泛应用于图像和视频处理领域。

视频缩放是一种常见的图像处理操作,可以将视频的分辨率调整为需要的大小,以适应不同的显示设备。

本文将详细介绍基于FPGA的视频缩放的设计与实现。

视频缩放的基本原理是通过插值方法来改变图像的尺寸。

最常用的插值方法是双线性插值,即通过对相邻像素的加权平均来计算新像素的值。

在FPGA中实现视频缩放,首先需要将视频信号通过视频输入接口读取到FPGA中进行处理。

然后,使用视频缓存模块将图像数据存储在FPGA的片内存储器中。

接下来,将图像数据传递给视频缩放模块进行处理,并通过视频输出接口将缩放后的图像信号输出。

在视频缩放模块中,可以使用插值算法来实现双线性插值。

双线性插值需要对原始图像的四个相邻像素进行加权平均来计算新像素的值。

具体来说,对于目标像素的位置(x,y),需要找到其在原始图像中的最近的四个像素点(x1,y1)、(x1,y2)、(x2,y1)和(x2,y2)。

然后,根据其位置与最近四个像素点之间的距离,计算插值系数,并通过加权求和得到新像素的值。

在FPGA中实现视频缩放,可以使用硬件描述语言(HDL)来描述设计。

常用的HDL语言包括VHDL和Verilog。

使用HDL语言,可以将整个视频缩放系统分为多个模块,每个模块负责完成特定的功能。

可以将视频输入接口、视频缓存模块、视频缩放模块和视频输出接口设计为独立的模块,并通过数据线和控制信号线进行连接。

在进行FPGA设计时,需要考虑到硬件资源的限制。

视频缩放操作需要进行大量的计算和存储操作,因此需要合理地分配硬件资源。

可以使用FPGA中的片内存储器来存储图像数据,以减少对外部存储器的访问次数。

还可以使用并行计算和流水线技术来提高计算效率。

基于FPGA的多视频信号叠加系统的设计与实现

信息科学科技创新导报 Science and Technology Innovation Herald162随着平安城市建设的不断推进,视频监控系统成为社会立体化防控的重要组成部分。

随着城市的发展,监控点位剧增,视频信号随之剧增,对于终端显示能力的需求也不断剧增。

不仅要求实时显示,还要求能够同时显示更多的信息,此时就需要视频叠加技术。

1 系统整体设计该文介绍了基于F PGA的多视频叠加系统,该系统支持多路视频源的输入。

系统支持PA L、VGA、HDM I、SDI四种格式视频源输入,经过F PGA系统处理,视频数据最终完成视频叠加并通过LV D S 输出到终端显示。

系统由五大模块组成,包括视频采集预处理模块、I 2C总线接口模块、DDR 3 S D R A M 存储模块、放大叠加融合模块、LV D S 输出显示模块。

本设计的创新点在于系统可同时支持PA L 、VG A、H DM I、SDI四种格式的视频图像的采集,并完成后续的视频叠加动作。

作为一种新型的视频叠加技术,它具有灵活性强,功能强大,实时性高,体积小,功耗低等特点,具有广泛的应用前景。

本设计在以F PGA为主控芯片的硬件平台上实现视频图像的缩放与叠加融合功能,可实现多路任意分辨率输入视频信号在屏幕任意位置叠加显示,通过缩放算法对每一路视频信号进行放大或缩小,进而调整各路视频信号在终端显示中的比例;还可通过更改各路视频的相应参数,调节各路视频在终端显示的位置。

该方案实时性好,处理速度快,灵活性较高。

2 I ²C总线接口模块I ²C总线是一种双线串行总线,分别是串行数据S DA 和串行时钟SCL 线。

它采用多主多从的结构,所有连接在总线上的设备都有唯一的地址识别。

为实现图像位置、大小的可配置性,系统设置了I ²C总线接口模块,用于接收配置数据。

F PGA仅接收配置数据值,所以只需要把F PGA作为从机设备且只有写操作。

基于TS101和FPGA的视频综合模块的设计与实现

基于TS101和FPGA的视频综合模块的设计与实现

李建峰;苏金涛

【期刊名称】《电脑知识与技术》

【年(卷),期】2013(000)010

【摘要】提出了一种基于TS101和FPGA的多媒体视频综合显示的方法,介绍了TS101的原理与应用,给出了以FPGA为核心的多路视频源的视频综合显示设计,并给出了相应的系统硬件设计实现,对于视频综合显示提供了一种可以借鉴的方法。

【总页数】3页(P2461-2463)

【作者】李建峰;苏金涛

【作者单位】江苏自动化研究所,江苏连云港,222061;江苏自动化研究所,江苏连云港,222061

【正文语种】中文

【中图分类】TP37

【相关文献】

1.基于FPGA的立体视频画面分割模块的设计与实现 [J], 陈鼎如;苏萍;马建设

2.基于SIP的视频会议系统视频模块的设计与实现 [J], 万晓榆;张溢华;樊自甫

3.基于FPGA的视频转换模块设计与实现 [J], 李翠娟;牛文生;杨敬宝

4.基于TS101和FPGA的视频综合模块的设计与实现 [J], 李建峰;苏金涛;

5.一种基于FPGA的机载视频压缩模块的设计 [J], 朱鹏程; 赵君; 文光兵

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

目 前 多媒 体视频信号 的合成 方法u , 大 多采用 如下方式 : 待合成 的模拟视频 信号通过视频采集模块将转换 成数字信号 , 数字视 频信 号再进入 视频合 成模块进 行多路 视频信号 合成 。视频采 集模块 和视 频合成模 块 间视频 信号 的传 输大多采 用 C P U总线方 式

( 地址线 、 数据线 、 控制线 ) 或I S A总线 、 或M U L T I — B U S 总线 、 或P C I 总线 。采用 以上的总线方式一方面各模块 间走线复杂 , 复杂的走 线降低 了系统 的抗 干扰性 , 导致可 靠性降低 , 另一 方面数据 的传 输速度会受 到限制 , 并且缺乏应 有的灵活性 。基于此 目的设计 了 基于 T S 1 0 1 和F P G A的视频综合模 块 , 由于T S 1 0 1 带有多个 L I N K接 口, 每个 L I N K口的结构 由8 位双向数据线 、 2 个 时钟线 、 1 个方 向

Vo 1 . 9 , No . 1 0 , Ap r i l 2 01 3.

T e l : + 8 6 — 5 5 1 — 6 5 6 9 0 9 6 3 6 5 6 9 0 9 6 4

基于 T S 1 0 1 和F P GA的视频综合模块 的设计 与实现

李 建 峰 , 苏 金 涛

线组成 , L I N K口结构简单可靠 , 外部多路视频信号均可通过 L I N K 接 口进入视频综合模块合成 一 1 。

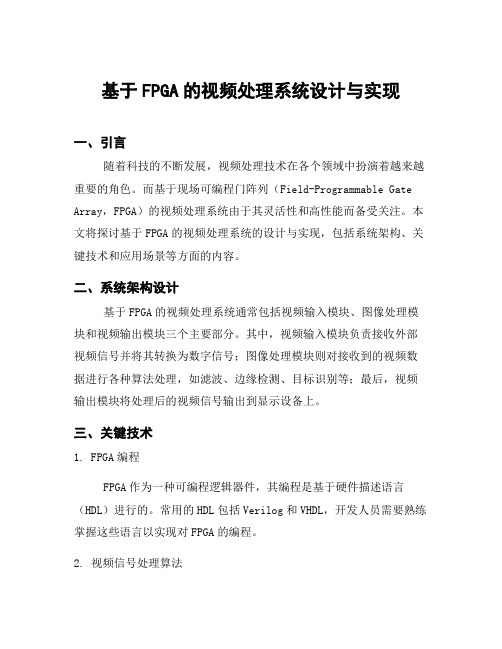

1模块 设计 方 案

视频综合模 块原理构 成如 图 l 示, 在模块 中 , 可有4 路外部视频信 号 、 2 路计算 机的 D V I 视频信 号进入视频综合模 块 , 4 路外 部 视频信号 通过 D S P ( T S 1 0 1 ) 的L I NK口进入 视频综合模块 。模块 主要 有 D S P ( 采用 AD公 司D S P芯 片T S 1 0 1 ) 、 F P G A、 存 储器 、 D / A转 换、 视频数模 转换 等几个部分组成构成 。 视频综合模块具体: [ 作原理 如下 : 外部视频数据 ( 电视视频或雷 达视频 ) 进入 D S P ( T S I O 1 ) 的L I N K口, 通过 D S P 的D MA通道将进入 L I NK E l 的数据传人 D S P内, 视 频 数据加工处 理后将数据存 储于双端 口存储 器 ( V R A M) 相应 位置上 ; 计算机 D V I 视频信号解码转成 数字信号后进入 F P G A, 在F P . G A控制下将 V R A M内的 L I N K数据 和 D V I 视频 信号综合叠加 , 叠加 后的数据在视频 时序控制下刷新输 出, 通过D / A转换模块 以差 分R B G和 R B G + H V两种格 式输 出。在 视频综合 模块上共 有两个 D S P , 可 接收 4 个L I N K口的视频数据 和 2 路D V I 视 频信号 。由于 两D S P间又有 L I N K互联 , 因此外部 L I N K输入数据 可共 享 , 提高 了模块 的灵 活性 。

( 江苏 自动化研究所 , 江苏 连云港 2 2 2 0 6 1 )

摘要 : 提 出 了一 种 基 于 T S 1 0 1 和F P G A的 多媒 体 视 频 综 合 显 示 的 方 法 , 介绍 了T S 1 0 1 的原理与应 用, 给 出了以F P G A为 核 心

的 多路视 频源的视频综合显示设计 , 并给 出了相应的 系统硬件设计 实现 , 对 于视频综合显示提供 了一种 可以借鉴 的方 法。

Ab s t r a c t : T h e p a p e r s h o ws a me t h o d o f v i d e o —s y n t h e s i s d e s i g n b a s e d o n T S1 01 a n d F P GA a n d i n t r o d u c e s t h e p in r c i p l e o f T S 1 0 1 . Mo r e o v e r We p r o p o s e t h e u s e mu l t i p l e v i d e o s o u r c e F P GA a s t h e c o r e v i d e o d i s p l a y me t h o d , a n d g i v e s a d e t a i l e d s y s t e m h a r d w a r e d e s i g n a n d i mp l e me n t a t i o n . F o r v i d e o i n t e g r a t e d d i s p l a y we p r o v i d a r e f e r e n c e me t h o d . Ke y wo r ds : v i d e o s y n t h e s i s ; mu l t i v i d e o s o u r c e; d i s p l a y ; t s l 0 1 ; F P G A

I S SN 1 00 9 - 3 0 4 4

E— ma i h e d u f @d n z s . n e t . c n

ht t p: / / www. d nz s . n e t . a n

、

C o m p u t e r K n o w l e d g e a n d T e c h n o l o g y电脑 知 识 与技术

L I J i a n — f e n g , S U J i n — t a o

O i a n g s u A u t o ma t i o n R e s e a r c h I n s t i t u t e , L i a n y u n g a n g 2 2 2 0 6 1 , C h i n a )

关键词 : 视频综合 ; 多路 视 频 源 ; 显 示; T S 1 0 1 ; F P G A 中图 分 类 号 : T P 3 7 文献标识码 : A 文 章编 号 : 1 0 0 9 — 3 0 4 4 ( 2 0 1 3 ) 1 0 — 2 4 6 1 — 0 3

Th e De s i g n o f a TS1 0 1 a n d F PGA— b a s e d o n Vi d e o a n d I mp l e me n t a t i o n