ADP5065ACBZ-1-R7;中文规格书,Datasheet资料

ADP-101-G1 通用多功能保护测控装置技术和使用说明书

装置初始操作密码是 001。

序号 1

版本号 V1.00

文档修改摘要 第一版

修改日期 2012-11-05

目录

1 概述 .........................................................................................................................................1 1.1 应用范围 ..........................................................................................................................1 1.2 保护配置和功能 ..............................................................................................................1 1.2.1 保护配置 ...................................................................................................................1 1.2.2 测控功能 ...................................................................................................................1 1.2.3 保护信息功能 ...........................................................................................................1 1.3 性能特征 ..........................................................................................................................2

ATSTK520;中文规格书,Datasheet资料

STK520 .............................................................................................. User GuideSTK520 User Guide 3Table of ContentsSection 1Introduction............................................................................................1-2Section 2Using the STK520 Top Module.............................................................2-42.1Connecting the STK520 to the STK500 Starter Kit..................................2-42.1.1Placing an AT90PWM3 on the STK520.............................................2-42.1.2Placing an AT90PWM2 on the STK520.............................................2-52.2Programming the AVR..............................................................................2-72.2.1In-System Programming....................................................................2-72.2.2High-voltage Programming................................................................2-82.3JTAGICE mkII Connector.........................................................................2-92.4STK520 Jumpers, Leds & Test Points....................................................2-112.5DALI Interface.........................................................................................2-122.6Potentiometer.........................................................................................2-13Section 3Troubleshooting Guide........................................................................3-14Section 4Technical Specifications......................................................................4-16Section 5Technical Support ...............................................................................5-17Section 6Complete Schematics .........................................................................6-20IntroductionSection 1IntroductionThe STK520 board is a top module designed to add AT90PWM family support to theSTK500 development board from Atmel Corporation.The STK520 includes connectors and hardware allowing full utilization of the new fea-tures of the AT90PWM, while the Zero Insertion Force (ZIF) socket allows easy to use ofSO24 & SO32 packages for prototyping.This user guide acts as a general getting started guide as well as a complete technicalreference for advanced users.Notice that in this guide, the word AVR is used to refer to the target component(AT90PWM2, AT90PWM3...)Figure 1-1. STK520 Top Module for STK500Introduction1.1Features STK520 is a New Member of the Successful STK500 Starter Kit Family.Supports the AT90PWM2 & AT90PWM3.DALI Hardware Interface.Supported by AVR Studio® 4.Zero Insertion Force Socket for SO24 & SO32 Packages.High Voltage Parallell Programming.Serial Programming.DALI Peripherals can be Disconnected from the Device.6 Pin Connector for On-chip Debugging using JTAG MKII Emulator.Potentiometer for the Demo Application.Quick Reference to all Switches and Jumpers in the Silk-Screen of the PCB.Using the STK520 Top Module Section 2Using the STK520 Top Module2.1Connecting the STK520 to theSTK500 Starter Kit Connect the STK520 to the STK500 expansion header 0 and 1. It is important that the top module is connected in the correct orientation as shown in Figure 2-1. The EXPAND0 written on the STK520 top module should match the EXPAND0 written beside the expansion header on the STK500 board.Figure 2-1. Connecting STK520 to the STK500 BoardNote:Connecting the STK520 with wrong orientation may damage the board.2.1.1Placing anAT90PWM3 on theSTK520The STK520 contains both a ZIF socket for a SO32 package. Care should be taken so that the device is mounted with the correct orientation. Figure 2-2 shows the location of pin1 for the ZIF socket.Using the STK520 Top ModuleFigure 2-2. Pin1 on ZIF SocketCaution: Do not mount an AT90PWM3 on the STK520 at the same time as an AVR ismounted on the STK500 board or at the same time as an AT90PWM2 is mounted on theSTK520 board. None of the devices might work as intended.2.1.2Placing anAT90PWM2 on theSTK520The STK520 contains both a ZIF socket for a SO24 package. Care should be taken so that the device is mounted with the correct orientation. Figure 2-2 shows the location of pin1 for the ZIF socket.Figure 2-3. Pin1 on ZIF SocketPIN1PIN1Using the STK520 Top Module Caution: Do not mount an AT90PWM2 on the STK520 at the same time as an AVR is mounted on the STK500 board or at the same time as an AT90PWM3 is mounted on the STK520 board. None of the devices might work as intended.Using the STK520 Top Module2.2Programming theAVR The AVR (AT90PWM2, AT90PWM3...) can be programmed using both SPI and High-voltage Parallel Programming. This section will explain how to connect the programming cables to successfully use one of these two modes. The AVR Studio STK500 software is used in the same way as for other AVR partsNote:The AT90PWM3 also support Self Programming, See AVR109 application note for more information on this topic.2.2.1In-SystemProgramming Figure 2-4. In-System ProgrammingTo program the AT90PWM3 using ISP Programming mode, connect the 6-wire cable between the ISP6PIN connector on the STK500 board and the ISP connector on the STK520 board as shown in Figure 2-4. The device can be programmed using the Serial Programming mode in the AVR Studio4 STK500 software.Note:See STK500 User Guide for information on how to use the STK500 front-end software for ISP Programming.Using the STK520 Top Module2.2.2High-voltageProgramming Figure 2-5. High-voltage (Parallel) ProgrammingTo program the AVR using High-voltage (Parallel) Programming, connect the PROGC-TRL to PORTD and PROGDATA to PORTB on the STK500 as shown in Figure 2-5. Make sure that the TOSC-switch is placed in the XTAL position.As described in the STK500 User Guide (jumper settings), mount the BSEL2 jumper in order to High-voltage Program the ATmega devices. This setting also applies to High-voltage Programming of the AVR.The device can now be programmed using the High-voltage Programming mode in AVR Studio STK500 software.Note:See the STK500 User Guide for information on how to use the STK500 front-end software in High-voltage Programming mode.Note:For the High-voltage Programming mode to function correctly, the target voltage must be higher than 4.5V.Using the STK520 Top Module2.3JTAGICE mkIIConnector See the following document :“JTAGICE mkII Quick Start Guide” which purpose is “Connecting to a target board with the AVR JTAGICE mkII”.This note explains which signals are required for ISP and which signals are required for debugWIRE.Figure 2-6 shows how to connect the JTAGICE mkII probe on the STK520 board. Figure 2-6. Connecting JTAG ICE to the STK520The ISP connector is used for the AT90PWM3 built-in debugWire interface. The pin out of the connector is shown in Table 2-1 and is compliant with the pin out of the JTAG ICE available from Atmel. Connecting a JTAG ICE to this connector allows On-chip Debug-ging of the AT90PWM3.More information about the JTAG ICE and On-chip Debugging can be found in the AVR JTAG ICE User Guide, which is available at the Atmel web site, .分销商库存信息: ATMELATSTK520。

ADL5606ACPZ-R7;中文规格书,Datasheet资料

ADL5606

TABLE OF CONTENTS

Features .............................................................................................. 1 Applications....................................................................................... 1 General Description ......................................................................... 1 Functional Block Diagram .............................................................. 1 Revision History ............................................................................... 2 Specifications..................................................................................... 3

The ADL5606 is fabricated on a GaAs HBT process and is packaged in a compact 4 mm × 4 mm, 16-lead LFCSP that uses an exposed paddle for excellent thermal impedance. The ADL5606 operates from −40°C to +85°C. A fully populated evaluation board tuned to 2140 MHz is also available.

SN6505B隔离式电源说明书

10 µF1ZHCA801A–February 2018–Revised March 2019隔离式电源,低噪声电路:5V 、100mA Analog Engineer's Circuit:DataConvertersZHCA801A–February 2018–Revised March 2019隔离式电源,低噪声电路:5V 、100mAReed Kaczmarek电源AVDD Vee Vdd 5.0V6.5V5.0V设计说明此设计展示了采用变压器驱动器和低压降稳压器(LDO)的隔离式电源。

此设计旨在与数字隔离式SAR ADC 结合使用(如数字隔离式ADS8689设计中所示)。

工业应用需要隔离接口的情况下,便是此设计与SAR ADC 结合后的主要应用场合。

根据输出电流要求和输出电压噪声要求不同,可以选择不同的变压器驱动器和LDO 。

该电源的设计和测试均基于采用ADS8689的PCB ,本文档稍后会显示ADS8689的性能以证明该电源的有效性。

该电路实现方案适用于如下一些应用:模拟输入模块、心电图(ECG)、脉动式血氧计和临床患者监护仪。

2ZHCA801A–February 2018–Revised March 2019隔离式电源,低噪声电路:5V 、100mA 规格规格目标值测得值LDO 输出电流<100mA 每通道16mA LDO 输出电压噪声<1mV RMS不适用ADS8689信噪比(SNR)92dB 92.4dB ADS8689总谐波失真(THD)–112dB111.3dB设计注意事项1.确定变压器次级侧所需的电源电流。

此信息将用于组件选择。

2.选择变压器和变压器驱动器对于设计正确的隔离式电源非常重要。

3.SN6505B 上的CLK 引脚可连接到外部时钟或悬空以便使用内部420kHz 时钟。

组件选择1.根据所需的输出电流选择变压器驱动器。

•SN6505将提供高达1A 的输出电流。

FGA25N120FTD;中文规格书,Datasheet资料

@ TC = 25oC @ TC = 100oC

Diode continuous Forward current Maximum Power Dissipation Maximum Power Dissipation Operating Junction Temperature

@ TC = 100oC @ TC = 25oC @ TC = 100oC

Symbol

Parameter

Test Conditions

VFM

Diode Forward Voltage

IF = 25A

TC = 25oC TC = 125oC

trr

Diode Reverse Recovery Time

TC = 25oC TC = 125oC

Irr

Diode Reverse Recovery Time

©2009 Fairchild Semiconductor Corporation

1

FGA25N120FTD Rev. A1

G

E

Ratings

1200 ± 25 50 25 75 25 313 125 -55 to +150 -55 to +150 300

Units

V V A A A A W W oC oC

Applications

• Induction heating and Microvewave oven • Soft switching applications

February 2009

tm

General Description

Using advanced field stop trench technology, Fairchild’s 1200V trench IGBTs offer superior conduction and switching performances, and easy parallel operation with exceptional avalanche ruggedness. This device is designed for soft switching applications.

AD8253ARMZ-R7,AD8253ARMZ-R7,AD8253ARMZ-R7,AD8253ARMZ-RL,AD8253ARMZ, 规格书,Datasheet 资料

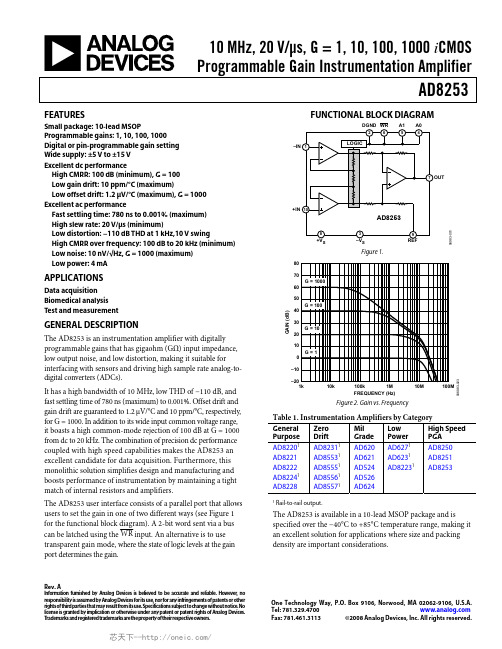

10 MHz, 20 V/μs, G = 1, 10, 100, 1000 i CMOSProgrammable Gain Instrumentation AmplifierAD8253 Rev. AInformation furnished by Analog Devices is believed to be accurate and reliable. However, noresponsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, Norwood, M A 02062-9106, U.S.A. Tel: 781.329.4700 Fax: 781.461.3113 ©2008 Analog Devices, Inc. All rights reserved.FEATURESSmall package: 10-lead MSOPProgrammable gains: 1, 10, 100, 1000Digital or pin-programmable gain settingWide supply: ±5 V to ±15 VExcellent dc performanceHigh CMRR: 100 dB (minimum), G = 100Low gain drift: 10 ppm/°C (maximum)Low offset drift: 1.2 μV/°C (maximum), G = 1000 Excellent ac performanceFast settling time: 780 ns to 0.001% (maximum)High slew rate: 20 V/μs (minimum)Low distortion: −110 dB THD at 1 kHz,10 V swingHigh CMRR over frequency: 100 dB to 20 kHz (minimum) Low noise: 10 nV/√Hz, G = 1000 (maximum)Low power: 4 mAAPPLICATIONSData acquisitionBiomedical analysisTest and measurementGENERAL DESCRIPTIONThe AD8253 is an instrumentation amplifier with digitally programmable gains that has gigaohm (GΩ) input impedance, low output noise, and low distortion, making it suitable for interfacing with sensors and driving high sample rate analog-to-digital converters (ADCs).It has a high bandwidth of 10 MHz, low THD of −110 dB, and fast settling time of 780 ns (maximum) to 0.001%. Offset drift and gain drift are guaranteed to 1.2 μV/°C and 10 ppm/°C, respectively, for G = 1000. In addition to its wide input common voltage range, it boasts a high common-mode rejection of 100 dB at G = 1000 from dc to 20 kHz. The combination of precision dc performance coupled with high speed capabilities makes the AD8253 an excellent candidate for data acquisition. Furthermore, this monolithic solution simplifies design and manufacturing and boosts performance of instrumentation by maintaining a tight match of internal resistors and amplifiers.The AD8253 user interface consists of a parallel port that allows users to set the gain in one of two different ways (see Figure 1 for the functional block diagram). A 2-bit word sent via a bus can be latched using the WR input. An alternative is to use transparent gain mode, where the state of logic levels at the gain port determines the gain.FUNCTIONAL BLOCK DIAGRAMS S+IN6983-1Figure 1.8070605040302010–10–201k10k100k1M10M100MFREQUENCY (Hz)GAIN(dB)6983-23Figure 2. Gain vs. FrequencyTable 1. Instrumentation Amplifiers by CategoryGeneralPurposeZeroDriftMilGradeLowPowerHigh SpeedPGAAD82201AD82311AD620AD6271AD8250AD8221AD85531AD621AD6231AD8251AD8222AD85551AD524AD82231AD8253AD82241AD85561AD526AD8228AD85571AD6241 Rail-to-rail output.The AD8253 is available in a 10-lead MSOP package and is specified over the −40°C to +85°C temperature range, making it an excellent solution for applications where size and packing density are important considerations.AD8253Rev. A | Page 2 of 24TABLE OF CONTENTSFeatures .............................................................................................. 1 Applications ....................................................................................... 1 General Description ......................................................................... 1 Functional Block Diagram .............................................................. 1 Revision History ............................................................................... 2 Specifications ..................................................................................... 3 Timing Diagram ........................................................................... 5 Absolute Maximum Ratings ............................................................ 6 Maximum Power Dissipation ..................................................... 6 ESD Caution .................................................................................. 6 Pin Configuration and Function Descriptions ............................. 7 Typical Performance Characteristics ............................................. 8 Theory of Operation ...................................................................... 16 Gain Selection ............................................................................. 16 Power Supply Regulation and Bypassing ................................ 18 Input Bias Current Return Path ............................................... 18 Input Protection ......................................................................... 18 Reference Terminal .................................................................... 19 Common-Mode Input Voltage Range ..................................... 19 Layout .......................................................................................... 19 RF Interference ........................................................................... 19 Driving an Analog-to-Digital Converter ................................ 20 Applications Information .............................................................. 21 Differential Output .................................................................... 21 Setting Gains with a Microcontroller ...................................... 21 Data Acquisition ......................................................................... 22 Outline Dimensions ....................................................................... 23 Ordering Guide .. (23)REVISION HISTORY8/08—Rev. 0 to Rev. AChanges to Ordering Guide (23)7/08—Revision 0: Initial VersionAD8253SPECIFICATIONS+V S = +15 V, −V S = −15 V, V REF = 0 V @ T A = 25°C, G = 1, R L = 2 kΩ, unless otherwise noted.Table 2.Parameter Conditions Min Typ Max Unit COMMON-MODE REJECTION RATIO (CMRR)CMRR to 60 Hz with 1 kΩ Source Imbalance +IN = −IN = −10 V to +10 VG = 1 80 100 dBG = 10 96 120 dBG = 100 100 120 dBG = 1000 100 120 dB CMRR to 20 kHz1+IN = −IN = −10 V to +10 VG = 1 80 dBG = 10 96 dBG = 100 100 dBG = 1000 100 dB NOISEVoltage Noise, 1 kHz, RTIG = 1 45 nV/√HzG = 10 12 nV/√HzG = 100 11 nV/√HzG = 1000 10 nV/√Hz0.1 Hz to 10 Hz, RTIG = 1 2.5 μV p-pG = 10 1 μV p-pG = 100 0.5 μV p-pG = 1000 0.5 μV p-p Current Noise, 1 kHz 5 pA/√Hz Current Noise, 0.1 Hz to 10 Hz 60 pA p-p VOLTAGE OFFSETOffset RTI V OS G = 1, 10, 100, 1000 ±150 + 900/G μV Over Temperature T = −40°C to +85°C ±210 + 900/G μV Average TC T = −40°C to +85°C ±1.2 + 5/G μV/°C Offset Referred to the Input vs. Supply (PSR) V S = ±5 V to ±15 V ±5 + 25/G μV/V INPUT CURRENTInput Bias Current 5 50 nA Over Temperature2T = −40°C to +85°C 40 60 nA Average TC T = −40°C to +85°C 400 pA/°C Input Offset Current 5 40 nA Over Temperature T = −40°C to +85°C 40 nA Average TC T = −40°C to +85°C 160 pA/°C DYNAMIC RESPONSESmall-Signal −3 dB BandwidthG = 1 10 MHzG = 10 4 MHzG = 100 550 kHzG = 1000 60 kHz Settling Time 0.01% ΔOUT = 10 V stepG = 1 700 nsG = 10 680 nsG = 100 1.5 μsG = 1000 14 μsRev. A | Page 3 of 24AD8253Rev. A | Page 4 of 24AD8253Rev. A | Page 5 of 24Parameter Conditions Min Typ Max UnitPOWER SUPPLY Operating Range±5 ±15 V Quiescent Current, +I S 4.6 5.3 mA Quiescent Current, −I S 4.5 5.3mA Over Temperature T = −40°C to +85°C 6 mA TEMPERATURE RANGE Specified Performance−40 +85 °C1 See Figure 20 for CMRR vs. frequency for more information on typical performance over frequency.2Input bias current over temperature: minimum at hot and maximum at cold. 3See Figure 30 for input voltage limit vs. supply voltage and temperature. 4See Figure 32, Figure 33, and Figure 34 for output voltage swing vs. supply voltage and temperature for various loads. 5Add time for the output to slew and settle to calculate the total time for a gain change.TIMING DIAGRAMA0, A1WR06983-003Figure 3. Timing Diagram for Latched Gain Mode (See the Timing for Latched Gain Mode Section)AD8253Rev. A | Page 6 of 24ABSOLUTE MAXIMUM RATINGSTable 3.Parameter RatingSupply Voltage ±17 VPower Dissipation See Figure 4Output Short-Circuit CurrentIndefinite 1 Common-Mode Input Voltage ±V S Differential Input Voltage ±V S Digital Logic Inputs±V SStorage Temperature Range –65°C to +125°C Operating Temperature Range 2–40°C to +85°C Lead Temperature (Soldering 10 sec) 300°C Junction Temperature140°C θJA (4-Layer JEDEC Standard Board) 112°C/W Package Glass Transition Temperature140°C1 Assumes the load is referenced to midsupply.2Temperature for specified performance is −40°C to +85°C. For performance to +125°C, see the Typical Performance Characteristics section.Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operationalsection of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.MAXIMUM POWER DISSIPATIONThe maximum safe power dissipation in the AD8253 package is limited by the associated rise in junction temperature (T J ) on the die. The plastic encapsulating the die locally reaches the junction temperature. At approximately 140°C, which is the glass transition temperature, the plastic changes its properties. Even temporarily exceeding this temperature limit can change the stresses that the package exerts on the die, permanently shifting the parametric performance of the AD8253. Exceeding a junction temperature of 140°C for an extended period can result in changes in silicon devices, potentially causing failure. The still-air thermal properties of the package and PCB (θJA ), the ambient temperature (T A ), and the total power dissipated in the package (P D ) determine the junction temperature of the die. The junction temperature is calculated as()JA D A J θP T T ×+=The power dissipated in the package (P D ) is the sum of the quiescent power dissipation and the power dissipated in the package due to the load drive for all outputs. The quiescent power is the voltage between the supply pins (V S ) times the quiescent current (I S ). Assuming the load (R L ) is referenced tomidsupply, the total drive power is V S /2 × I OUT , some of which isdissipated in the package and some of which is dissipated in theload (V OUT × I OUT ). The difference between the total drive power and the load power is the drive power dissipated in the package.P D = Quiescent Power + (Total Drive Power − Load Power )()L 2OUT L OUTS S S D R V –R V2V I V P ⎟⎟⎠⎞⎜⎜⎝⎛×+×= In single-supply operation with R L referenced to −V S , the worstcase is V OUT = V S /2.Airflow increases heat dissipation, effectively reducing θJA . In addition, more metal directly in contact with the package leads from metal traces through holes, ground, and power planes reduces the θJA .Figure 4 shows the maximum safe power dissipation in the package vs. the ambient temperature on a 4-layer JEDEC standard board.2.001.751.501.251.000.750.500.250–40–20120100806040200M A X I M U M P O W E R D I S S I P A T I O N (W )AMBIENT TEMPERATURE (°C)06983-004Figure 4. Maximum Power Dissipation vs. Ambient TemperatureESD CAUTIONAD8253Rev. A | Page 7 of 24PIN CONFIGURATION AND FUNCTION DESCRIPTIONS–IN DGND –V S A0A1+INREF+V S OUT WRAD8253TOP VIEW(Not to Scale)1234510987606983-005Figure 5. 10-Lead MSOP (RM-10) Pin ConfigurationAD8253Rev. A | Page 8 of 24TYPICAL PERFORMANCE CHARACTERISTICST A @ 25°C, +V S = +15 V , −V S = −15 V , R L = 10 kΩ, unless otherwise noted.CMRR (µV/V)21006983-006N U M B E R O F U N I T S180150120906030–60–40–20020INPUT OFFSET CURRENT (nA)240120180601502109030604020006983-009N U M B E R O F U N I T S–60–20–40Figure 6. Typical Distribution of CMRR, G = 1 Figure 9. Typical Distribution of Input Offset CurrentINPUT OFFSET VOLTAGE, V OSI , RTI (µV)180120150200100006983-007N U M B E R O F U N I T S–200–10006983-0101100kFREQUENCY (Hz)N O I S E (n V /√H z )101001k10k8070605040302010Figure 10. Voltage Spectral Density Noise vs. FrequencyFigure 7. Typical Distribution of Offset Voltage, V OSI 06983-011INPUT BIAS CURRENT (nA)30020025015010050906030006983-008N U M B E R O F U N I T S–90–30–60Figure 11. 0.1 Hz to 10 Hz RTI Voltage Noise, G = 1Figure 8. Typical Distribution of Input Bias CurrentAD8253Rev. A | Page 9 of 2406983-012Figure 12. 0.1 Hz to 10 Hz RTI Voltage Noise, G = 1000 06983-01318011FREQUENCY (Hz)N O I S E (p A /√H z )00k 101001k 10k 161412108642Figure 13. Current Noise Spectral Density vs. Frequency 06983-014Figure 14. 0.1 Hz to 10 Hz Current Noise 201816141210864200.010.1110WARM-UP TIME (Minutes)C H A N G E I N I N P U T O F F S E T V O L T A G E (µV )06983-015Figure 15. Change in Input Offset Voltage vs. Warm-Up Time, G = 10001401201008040600101M06983-016FREQUENCY (Hz)P S R R (d B )1001k 10k 100k 20Figure 16. Positive PSRR vs. Frequency, RTI1401201008040600101M06983-017FREQUENCY (Hz)P S R R (d B )1001k 10k 100k 20Figure 17. Negative PSRR vs. Frequency, RTIAD8253Rev. A | Page 10 of 2420100–10–20–30–40–50–6012.0I B +10.59.07.56.04.53.01.50–15–10–5051015COMMON-MODE VOLTAGE (V)I N P U T B I A S C U R R E N T (n A )I N P U T O F F S E T C U R R E N T (n A )06983-018I B –I OSFigure 18. Input Bias Current and Offset Current vs. Common-Mode Voltage 302520151050–10–5–60–40–20020406080100120140TEMPERATURE (°C)I N P U T B I A S C U R R E N T A N D O F F S E T C U R R E N T (n A )06983-019I B +I B –I OS Figure 19. Input Bias Current and Offset Current vs. Temperature 012010080604020106983-020FREQUENCY (Hz)C M R R (d B )1001k 10k 100k 1MFigure 20. CMRR vs. Frequency120100806040201006983-021FREQUENCY (Hz)C M R R (d B)1001k 10k 100k 1MFigure 21. CMRR vs. Frequency, 1 kΩ Source Imbalance–15–5013006983-022TEMPERATURE (°C)C M R R (µV /V )10155–5–10–30–101030507090110Figure 22. CMRR vs. Temperature, G = 180706050403020100–10–201k10k100k 1M 10M 100MFREQUENCY (Hz)G A I N (d B )006983-023Figure 23. Gain vs. Frequency40302010–10–300–20–40–10–8–6–4–2024681006983-024N O N L I N E A R I T Y (10p p m /D I V )OUTPUT VOLTAGE (V)Figure 24. Gain Nonlinearity, G = 1, R L = 10 kΩ, 2 kΩ, 600 Ω 40302010–10–300–20–40–10–8–6–4–2024681006983-025N O N L I N E A R I T Y (10p p m /D I V )OUTPUT VOLTAGE (V)Figure 25. Gain Nonlinearity, G = 10, R L = 10 kΩ, 2 kΩ, 600 Ω 80604020–20–600–40–80–10–8–6–4–2024681006983-026N O N L I N E A R I T Y (10p p m /D I V )OUTPUT VOLTAGE (V)Figure 26. Gain Nonlinearity, G = 100, R L = 10 kΩ, 2 kΩ, 600 Ω400300200100–100–3000–200–400–10–8–6–4–2024681006983-027N O N L I N E A R I T Y (10 p p m /D I V )OUTPUT VOLTAGE (V)Figure 27. Gain Nonlinearity, G = 1000, R L = 10 kΩ, 2 kΩ, 600 Ω16–1606983-028OUTPUT VOLTAGE (V)I N P U T C O M M O N -M O D E V O L T A G E (V )1284–4–8–12–12–8–44812Figure 28. Input Common-Mode Voltage Range vs. Output Voltage, G = 116–16–161606983-029OUTPUT VOLTAGE (V)I N P U T C O M M O N -M O D E V O L T A G E (V )1284–4–8–12–12–8–44812Figure 29. Input Common-Mode Voltage Range vs. Output Voltage, G = 1000+V S –V S4106983-030SUPPLY VOLTAGE (±V S )I N P U T V O L T A G E (V )R E F E R R E D T O S U P P L Y V O L T A G E S6–1–2+2+168101214Figure 30. Input Voltage Limit vs. Supply Voltage, G = 1, V REF = 0 V, R L = 10 kΩ–1––100m–10–1–100µ–10µ10DIFFERENTIAL INPUT VOLTAGE (V)C U R R E N T (m A )06983-0311001101001Figure 31. Fault Current Draw vs. Input Voltage, G = 1000, R L = 10 kΩ +V S –V S4106983-032SUPPLY VOLTAGE (±V S )OU T P U T V O L T A G E S W I N G (V )R E F E R R E D T O S U P P L Y V O L T A G E S668101214–0.2–0.4–0.6–0.8–1.0–1.2+1.0+1.2+0.8+0.6+0.4+0.2Figure 32. Output Voltage Swing vs. Supply Voltage, G = 1000, R L = 2 kΩ +V S –V S4106983-033SUPPLY VOLTAGE (±V S )O U T P U T V O L T A G E S W I N G (V )R E F E R R E D T O S U P P L Y V O L T A G E S668101214–0.2–0.4–0.6–0.8–1.0+1.0+0.8+0.6+0.4+0.2Figure 33. Output Voltage Swing vs. Supply Voltage, G =1000, R L = 10 kΩ15–1510010k06983-034LOAD RESISTANCE (Ω)1k105–5–10O U T P U T V O L T A G E S W I N G (V )Figure 34. Output Voltage Swing vs. Load Resistance+V S –V S4106983-035OUTPUT CURRENT (mA)668101214–0.4–0.8–1.2–1.6–2.0+2.0+1.6+1.2+0.8+0.4O U T P U T V O L T A G E S W I N G (V )R E F E R R E D T O S U P P L Y V O L T A G E SFigure 35. Output Voltage Swing vs. Output Current06983-036Figure 36. Small-Signal Pulse Response for Various Capacitive Loads, G = 1069TIME (µs)Figure 37. Large-Signal Pulse Response and Settling Time, G = 1, R L= 10 kΩ06983-038TIME (µs)Figure 38. Large-Signal Pulse Response and Settling Time,G = 10, R L= 10 kΩ06983-039TIME (µs)Figure 39. Large-Signal Pulse Response and Settling Time,G = 100, R L= 10 kΩ06983-040TIME (µs)Figure 40. Large-Signal Pulse Response and Settling Time,G = 1000, R L= 10 kΩ06983-041Figure 41. Small-Signal Response,G = 1, R L = 2 kΩ, C L = 10006983-042Figure 42. Small-Signal Response, G = 10, R L = 2 kΩ, C L = 100 pF06983-043Figure 43. Small-Signal Response, G = 100, R L = 2 kΩ, C L = 100 pF06983-044Figure 44. Small-Signal Response, G = 1000, R L = 2 kΩ, C L = 100 pF 06983-045120014000STEP SIZE (V)T I M E (n s )10008006004002004681012141618Figure 45. Settling Time vs. Step Size, G = 1, R L = 10 kΩ06983-04612001400STEP SIZE (V)T I M E (n s )10008006004002004681012141618Figure 46. Settling Time vs. Step Size, G = 10, R L = 10 kΩ06983-04722STEP SIZE (V)T I M E (n s )10008006001800160014004002004681012141618Figure 47. Settling Time vs. Step Size, G = 100, R L = 10 kΩ06983-048STEP SIZE (V)T I M E (µs )1086181614424681012141618Figure 48. Settling Time vs. Step Size, G = 1000, R L = 10 kΩ0–10–20–30–40–50–60–70–80–90–120–110–100101M06983-049FREQUENCY (Hz)T H D + N (d B )1001k 10k 100k Figure 49. Total Harmonic Distortion vs. Frequency,10 Hz to 22 kHz Band-Pass Filter, 2 kΩ Load0–10–20–30–40–50–60–70–80–90–120–110–100101M06983-050FREQUENCY (Hz)T H D + N (d B )1001k 10k 100k Figure 50. Total Harmonic Distortion vs. Frequency, 10 Hz to 500 kHz Band-Pass Filter, 2 kΩ LoadTHEORY OF OPERATIONREFOUTSS 06983-061Figure 51. Simplified SchematicTransparent Gain ModeThe AD8253 is a monolithic instrumentation amplifier based on the classic 3-op-amp topology, as shown in Figure 51. It is fabricated on the Analog Devices, Inc., proprietary i CMOS® process that provides precision linear performance and a robust digital interface. A parallel interface allows users to digitally program gains of 1, 10, 100, and 1000. Gain control is achieved by switching resistors in an internal precision resistor array (as shown in Figure 51).The easiest way to set the gain is to program it directly via a logic high or logic low voltage applied to A0 and A1. Figure 52 shows an example of this gain setting method, referred to through-out the data sheet as transparent gain mode. Tie WR to the negative supply to engage transparent gain mode. In this mode, any change in voltage applied to A0 and A1 from logic low to logic high, or vice versa, immediately results in a gain change. is the truth table for transparent gain mode, and shows the AD8253 configured in transparent gain mode.Table 5Figure 52All internal amplifiers employ distortion cancellation circuitry and achieve high linearity and ultralow THD. Laser-trimmed resistors allow for a maximum gain error of less than 0.03% for G = 1 and a minimum CMRR of 100 dB for G = 1000. A pinout optimized for high CMRR over frequency enables the AD8253 to offer a guaranteed minimum CMRR over frequency of 80 dB at 20 kHz (G = 1). The balanced input reduces the parasitics that in the past had adversely affected CMRR performance.NOTE:1. IN TRANSPARENT GAIN MODE, WR IS TIED TO −V S .THE VOLTAGE LEVELS ON A0 AND A1 DETERMINE THE GAIN. IN THIS EXAMPLE, BOTH A0 AND A1 ARE SET TO LOGIC HIGH, RESULTING IN A GAIN OF 1000.06983-051GAIN SELECTIONThis section describes how to configure the AD8253 for basic operation. Logic low and logic high voltage limits are listed in the Specifications section. Typically, logic low is 0 V and logic high is 5 V; both voltages are measured with respect to DGND. Refer to the specifications table (Table 2) for the permissible voltage range of DGND. The gain of the AD8253 can be set using two methods: transparent gain mode and latched gain mode. Regardless of the mode, pull-up or pull-down resistors should be used to provide a well-defined voltage at the A0 and A1 pins.Figure 52. Transparent Gain Mode, A0 and A1 = High, G = 1000Latched Gain ModeSome applications have multiple programmable devices such as multiplexers or other programmable gain instrumentation amplifiers on the same PCB. In such cases, devices can share a data bus. The gain of the AD8253 can be set using WR as a latch, allowing other devices to share A0 and A1. shows a schematic using this method, known as latched gain mode. The AD8253 is in this mode when Figure 53WR is held at logic high or logic low, typically 5 V and 0 V , respectively. The voltages on A0 and A1 are read on the downward edge of the WR signal as it transitions from logic high to logic low. This latches in the logic levels on A0 and A1, resulting in a gain change. See the truth table listing in for more on these gain changes.Table 6NOTE:FROM LOGIC HIGH TO LOGIC LOW, THE VOLTAGES ON A0AND A1 ARE READ AND LATCHED IN, RESULTING IN AGAIN CHANGE. IN THIS EXAMPLE, THE GAIN SWITCHES TO G = 1000.06983-052Figure 53. Latched Gain Mode, G = 10001X = don’t care.On power-up, the AD8253 defaults to a gain of 1 when inlatched gain mode. In contrast, if the AD8253 is configured in transparent gain mode, it starts at the gain indicated by the voltage levels on A0 and A1 on power-up.Timing for Latched Gain ModeIn latched gain mode, logic levels at A0 and A1 must be held for a minimum setup time, t SU , before the downward edge of WR latches in the gain. Similarly, they must be held for a minimum hold time, t HD , after the downward edge of WR to ensure that the gain is latched in correctly. After t HD , A0 and A1 may change logic levels, but the gain does not change until the next downward edge of WR . The minimum duration that WR can be held high is t -HIGH , and t -LOW is the minimum duration that WR can be held low. Digital timing specifications are listed in The time required for a gain change is dominated by the settling time of the amplifier. A timing diagram is shown in . Table 2.Figure 54When sharing a data bus with other devices, logic levels applied to those devices can potentially feed through to the output of the AD8253. Feedthrough can be minimized by decreasing the edge rate of the logic signals. Furthermore, careful layout of the PCB also reduces coupling between the digital and analog portions of the board.A0, A106983-053Figure 54. Timing Diagram for Latched Gain ModePOWER SUPPLY REGULATION AND BYPASSINGThe AD8253 has high PSRR. However, for optimal performance, a stable dc voltage should be used to power the instrumentation amplifier. Noise on the supply pins can adversely affect per-formance. As in all linear circuits, bypass capacitors must be used to decouple the amplifier.Place a 0.1 μF capacitor close to each supply pin. A 10 μF tantalum capacitor can be used farther away from the part (see Figure 55) and, in most cases, it can be shared by other precision integrated circuits.06983-054Figure 55. Supply Decoupling, REF, and Output Referred to GroundINPUT BIAS CURRENT RETURN PATHThe AD8253 input bias current must have a return path to its local analog ground. When the source, such as a thermocouple, cannot provide a return current path, one should be created (see Figure 56).THERMOCOUPLE+V –V SCAPACITIVELY COUPLED +V SREFCC–V SAD8253TRANSFORMER+V SREF–V SAD8253INCORRECTCAPACITIVELY COUPLEDf HIGH-PASS THERMOCOUPLE+V TRANSFORMER–V SCORRECT06983-055Figure 56. Creating an I BIAS PathINPUT PROTECTIONAll terminals of the AD8253 are protected against ESD. An external resistor should be used in series with each of the inputs to limit current for voltages greater than 0.5 V beyond either supply rail. In such a case, the AD8253 safely handles a continuous 6 mA current at room temperature. For applications where the AD8253 encounters extreme overload voltages, external series resistors and low leakage diode clamps such as BAV199Ls, FJH1100s, or SP720s should be used.REFERENCE TERMINALThe reference terminal, REF, is at one end of a 10 kΩ resistor (see Figure 51). The instrumentation amplifier output is referenced to the voltage on the REF terminal; this is useful when the output signal needs to be offset to voltages other than its local analog ground. For example, a voltage source can be tied to the REF pin to level shift the output so that the AD8253 can interface with a single-supply ADC. The allowable reference voltage range is a function of the gain, common-mode input, and supply voltages. The REF pin should not exceed either +V S or −V S by more than 0.5 V .For best performance, especially in cases where the output is not measured with respect to the REF terminal, source imped-ance to the REF terminal should be kept low because parasiticresistance can adversely affect CMRR and gain accuracy.INCORRECTCORRECT06983-056Figure 57. Driving the Reference PinCOMMON-MODE INPUT VOLTAGE RANGEThe 3-op-amp architecture of the AD8253 applies gain and then removes the common-mode voltage. Therefore, internal nodes in the AD8253 experience a combination of both the gained signal and the common-mode signal. This combined signal can be limited by the voltage supplies even when the individual input and output signals are not. Figure 28 and Figure 29 show the allowable common-mode input voltage ranges for various output voltages, supply voltages, and gains.LAYOUTGroundingIn mixed-signal circuits, low level analog signals need to be isolated from the noisy digital environment. Designing with the AD8253 is no exception. Its supply voltages are referenced to an analog ground. Its digital circuit is referenced to a digital ground. Although it is convenient to tie both grounds to a single ground plane, the current traveling through the ground wires and PC board can cause an error. Therefore, use separate analog and digital ground planes. Only at one point, star ground, should analog and digital ground meet.The output voltage of the AD8253 develops with respect to the potential on the reference terminal. Take care to tie REF to the appropriate local analog ground or to connect it to a voltage that is referenced to the local analog ground.Coupling NoiseTo prevent coupling noise onto the AD8253, follow these guidelines: • Do not run digital lines under the device.• Run the analog ground plane under the AD8253.•Shield fast-switching signals with digital ground to avoid radiating noise to other sections of the board, and never run them near analog signal paths.• Avoid crossover of digital and analog signals.• Connect digital and analog ground at one point only (typically under the ADC).•Power supply lines should use large traces to ensure a low impedance path. Decoupling is necessary; follow the guidelines listed in the Power Supply Regulation and Bypassing section.Common-Mode RejectionThe AD8253 has high CMRR over frequency, giving it greater immunity to disturbances, such as line noise and its associated harmonics, in contrast to typical in amps whose CMRR falls off around 200 Hz. They often need common-mode filters at the inputs to compensate for this shortcoming. The AD8253 is able to reject CMRR over a greater frequency range, reducing the need for input common-mode filtering.Careful board layout maximizes system performance. T o maintain high CMRR over frequency, lay out the input traces symmetrically. Ensure that the traces maintain resistive and capacitive balance; this holds for additional PCB metal layers under the input pins and traces. Source resistance and capacitance should be placed as close to the inputs as possible. Should a trace cross the inputs (from another layer), it should be routed perpendicular to the input traces.RF INTERFERENCERF rectification is often a problem when amplifiers are used in applications where there are strong RF signals. The disturbance can appear as a small dc offset voltage. High frequency signals can be filtered with a low-pass RC network placed at the input of the instrumentation amplifier, as shown in Figure 58. The filter limits the input signal bandwidth according to the following relationship:)C C (R 1FilterFreq C D DIFF +=2π2CCM RC 1FilterFreq π2=where C D ≥ 10 C C .。

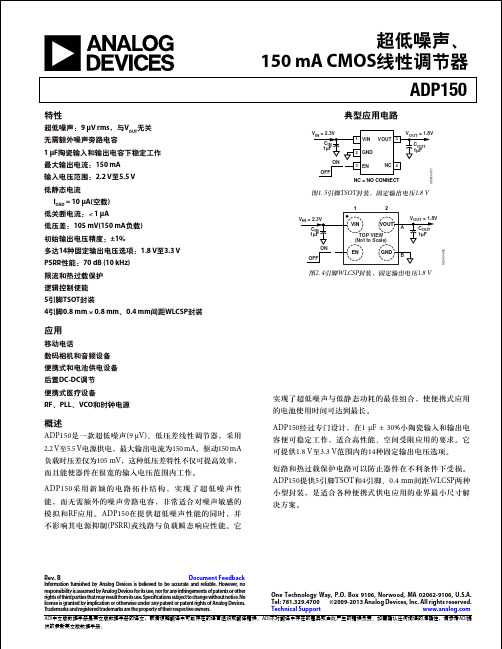

ADP150_cn中文PDF

移动电话 数码相机和音频设备 便携式和电池供电设备 后置DC-DC调节 便携式医疗设备 RF、PLL、VCO和时钟电源

概述

ADP150是一款超低噪声(9 μV)、低压差线性调节器,采用 2.2 V至5.5 V电源供电,最大输出电流为150 mA。驱动150 mA 负载时压差仅为105 mV,这种低压差特性不仅可提高效率, 而且能使器件在很宽的输入电压范围内工作。

特性

超低噪声:9 μV rms,与VOUT无关 无需额外噪声旁路电容 1 μF陶瓷输入和输出电容下稳定工作 最大输出电流:150 mA 输入电压范围:2.2 V至5.5 V 低静态电流

IGND = 10 μA(空载) 低关断电流:< 1 μA 低压差:105 mV(150 mA负载) 初始输出电压精度:±1% 多达14种固定输出电压选项:1.8 V至3.3 V PSRR性能:70 dB (10 kHz) 限流和热过载保护 逻辑控制使能 5引脚TSOT封装 4引脚0.8 mm × 0.8 mm、0.4 mm间距WLCSP封装

VOUT = 1.8V

A

COUT

1µF

EN

GND B

图2. 4引脚WLCSP封装,固定输出电压1.8 V

08343-002

实现了超低噪声与低静态功耗的最佳组合,使便式应用 的电池使用时间可达到最长。

ADP150经过专门设计,在1 μF ± 30%小陶瓷输入和输出电 容便可稳定工作,适合高性能、空间受限应用的要求。它 可提供1.8 V至3.3 V范围内的14种固定输出电压选项。

ON

OFF

1 VIN VOUT 5 2 GND

VOUT = 1.8V

COUT 1µF

3 EN

NC 4

uPD71055GB-10中文资料

Document No. A18501EJ3V0DS00 (3rd edition)Date Published March 2008 NS Printed in Japan © NEC Electronics Corporation 2007Disclaimer• This product is not functionally equivalent to any similar non-NEC Electronics product. NEC Electronics shall assume no responsibility for any loss or damage incurred by customers or third parties resulting from the replacement of products similarto, but other than, the μPD71055GB-10-3B4.• NEC Electronics shall assume no responsibility for any loss or damage incurred by customers or third parties resulting from the use of this product outside the conditions described in the absolute maximum ratings, recommended operation range, andquality grades.COMPARISON OF μPD65881GB-P03 AND μPD71055Feature ThisProduct μPD71055 ReferencePart number (mark) μPD65881GB-P03-3BS-A(658N55) μPD71055GB-10-3B4(standard NEC Electronics mark)−Package type Only 44-pin QFP QFP, DIP, QFJ −Package shape (comparison of 44-pin QFP) The body size and package width are the same, but the pin lengthsand pin bending method are different.4. PACKAGEDRAWINGFunction of pin 1 IC (connection with external pinprohibited)NC 1. PIN LAYOUTLead-free support Yes No ORDERINGINFORMATIONRecommended soldering conditions IR60-207-3, partial heating IR35-00-3, VP15-00-3,WS60-00-1, partial heating5. RECOMMENDEDSOLDERING CONDITIONSAbsolute maximum ratingsPower supply voltage −0.5 to +6.0 (V) −0.5 to +7.0 (V) Input voltage −0.5 to +6.0 (V) −0.5 to V DD+0.3 (V) Output voltage −0.5 to +6.0 (V) −0.5 to V DD+0.3 (V)Recommended operating range T A=−40 to +85°C, V DD = 5 V±10%This product does not guarantee operation at less than 4.5 V.DC characteristics Partially differentAC characteristics This product has the following restrictions on load capacitance.D7 to D0: 150 pF or lessP07 to P00, P17 to P10, P27 to P20: 40 pF or less 2. ELECTRICAL SPECIFICATIONSORDERING INFORMATIONPartNumber PackageμPD65881GB-P03-3BS-A 44-pin plastic QFP (10 x 10 mm)Remark Products with -A at the end of the part number are lead-free products.QUALITY GRADES"Standard"This product is intended to be used for applications such as computers, office equipment, communications equipment, test and measurement equipment, and home electronic appliances. It therefore cannot be used for the following applications.Applications requiring special or specific grades, such as transportation equipment (automobiles, trains, ships, etc.), traffic control systems, medical equipment, aircraft equipment, and aerospace equipment.Remark For details of quality grades, refer to Quality Grades on NEC Semiconductor Devices (document number: C11531E).Data Sheet A18501EJ3V0DS2Data Sheet A18501EJ3V0DS3BLOCK DIAGRAM (μPD71055)D 7 -D 07 -D 017 -P 1027 -P 24 (P 23)23 (P 22) -P 20CSRESETA1A0RD WR1. PIN LAYOUTFor a description of pin functions, refer to the μPD71055 Data Sheet (document number: IC-1921).Note This pin is connected to GND or V DD in the chip. To enhance the power supply to handle noise, this pin can be connected to the power supply pin of the board to improve the noise resistance performance.4Data Sheet A18501EJ3V0DS2. ELECTRICAL SPECIFICATIONSThis section describes only the differences with the μPD71055.For electrical specifications other than those below, refer to the μPD71055 Data Sheet (document number: IC-1921).Absolute Maximum RatingsParameter Symbol Conditions Ratings Unit Power supply voltage V DD−0.5 to +6.0 V Input voltage V I−0.5 to +6.0 V Output voltage V O−0.5 to +6.0 V Caution Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. In other words, the absolute maximum ratings are values at which the product maybegin to suffer degradation. Therefore the product must be used under conditions that ensure thatthe absolute maximum ratings are not exceeded.Recommended Operating RangeThis is the same as the μPD71055. This product does not guarantee operation at less than 4.5 V.DC Characteristics (V DD = 5 V±10%, T A = −40 to +85°C)This Product μPD71055Parameter SymbolCondition Min. Typ. Max. Condition Min. Typ. Max.UnitInput voltage, high V IH 2.29 V DD 2.2 V DD+0.3 VInput voltage, low V IL 0.00 0.77 −0.5 0.8 VI OH =0 mA V DD−0.1Output voltage, high V OHI OH =3.0 mA V DD−0.4I OH =−400 μA0.7×V DD VOutput voltage, low V OL I OL =3 mA 0.4I OL =2.5 mA0.4VOutput current, low I OL 3.0 2.5 mAAC CharacteristicsThese are similar to the μPD71055 characteristics, except for the following restrictions on load capacitance. Operation outside the range of these restrictions is not guaranteed.D7 to D0: 150 pF or lessP07 to P00, P17 to P10, P27 to P20: 40 pF or lessData Sheet A18501EJ3V0DS 53. CAUTIONS WHEN CONSIDERING ADOPTION OF THIS PRODUCTWhen considering the adoption of this product, note the following points.(1) Functional check using product samplesBefore adopting this product, make sure to request product samples from NEC Electronics to check the functions. Product samples are available free of charge.When mounting this product onto different multiple printed circuit boards, extensively check the functions by changing the supply voltage to be supplied to the printed circuit boards as well as the temperature conditions for all printed circuit boards.The standard number of product samples is five. When requesting product samples, provide the following information to your NEC Electronics sales representative.Your company name, your name, product application, the period of starting adoption, the number of products to be adopted(2) Submitting the Approval SheetWhen normal operation has been confirmed and the adoption has been decided, complete a copy of the Approval Sheet (Appendix of this document) and submit it to NEC Electronics.(3) Shipment inspectionShipment inspection is performed for this product using the μPD71055GB-10-3B4 shipment test pattern. The DC characteristics satisfy the gate array shipment inspection.(4) Order amountOrders from a minimum of 100 units, and in units of 100 are accepted.(5) Package, packing formThe dimensions are partially different from the μPD71055GB-10-3B4. Refer to the package drawing and confirm that the product can actually be mounted. Dry pack tray packing is used for packing.(6) PriceContact your local NEC Electronics sales representative for pricing information.(7) Obtaining the μPD71055 Data Sheet NoteThe μPD71055 (original product) Data Sheet is available from the NEC Electronics Web site(/) at/nesdis/image/IC-1921B.pdfNote Please make this data sheet a standalone document. Do not refer customers to the data sheet for an obsolete device.6Data Sheet A18501EJ3V0DSData Sheet A18501EJ3V0DS74. PACKAGE DRAWING44-PIN PLASTIC QFP (10x10)ITEM MILLIMETERS A B D G 13.2±0.210.0±0.20.8 (T.P.)1.0J 13.2±0.2K S44GB-80-3BS-2C 10.0±0.2I 0.161.6±0.2L 0.8±0.2F 1.0N P Q S0.102.7±0.10.125±0.0753.0 MAX.M 0.17+0.06−0.05H 0.37+0.08−0.07R 3°+7°−3°NOTEEach lead centerline is located within 0.16 mm ofits true position (T.P.) at maximum material condition.detail of lead end5. RECOMMENDED SOLDERING CONDITIONSThese products should be soldered and mounted under the following recommended conditions.For soldering methods and conditions other than those recommended below, please contact an NEC Electronicssales representative.For technical information, see the following website.Semiconductor Device Mount Manual (/pkg/en/mount/index.html)Soldering MethodSoldering ConditonsRecommended Condition SymbolInfrared reflowPackage peak temperature: 260°CTime: 60 seconds max. (at 220°C or higher)Count: 3 times or lessExposure limit: 7 days Note(after that, prebake at 125°C for 20 to 72 hours)IR60-207-3Partial heatingPin temperature: 350°C max. Time: 3 seconds max. (per pin row)−Note After opening the dry pack, store it at 25°C or less and 65% RH or less for the allowable storage period.Caution Do not use different soldering methods together (except for partial heating).APPENDIX APPROVAL SHEETCopy this page and complete and confirm the required items.If you accept the conditions, sign and submit this sheet to NEC Electronics.8Data Sheet A18501EJ3V0DSData Sheet A18501EJ3V0DS 9The information in this document is current as of March, 2008. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document.NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of a customer's equipment shall be done under the full responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".The "Specific" quality grade applies only to NEC Electronics products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.(Note)••••••M8E 02. 11-1(1)(2)"NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes itsmajority-owned subsidiaries."NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (asdefined above).Computers, office equipment, communications equipment, test and measurement equipment, audioand visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disastersystems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, lifesupport systems and medical equipment for life support, etc."Standard":"Special":"Specific":。

at89c1051中文资料

ØÙÚVk)Il rÛÁÜÃ ±´Î !ÛÁÜÃ ±´Î ÝÞßJàáV»ÒÓ

Ô Ð XÁÂâ ã äå £æ±

ç{»¼½ ¾¿À è Ð XÈÉÜ \zÁÜà èÈÉ Ð¤£ Ф¥ (zÁÜ{éáVÓ

\ ØêëVÒÓ

RS¨©

w yô|}áV$% õö 8ô|}áV di ëz:ôJ

2(. /45 ^5 {³ |2à}ÒO45IJìÜ45\~3454i{³ PJ; à2( N Z=*!IJ¨© èÏ2(45.¨©PJ

ÆÇ

www.tai-yan.co ÈÉ?ÊË m §ÌÌ

·

/b ÍÎÀ Ï bs Ð X Ð X^Ñ ¯ f_ ´µ¶ X Ф£ Ф¥ DEVÒÓ

wK&Vj452(ÒOk^^l rl eÂZ=*f8cÈmôghÂi tú:b2(

6n&cd:op23:bqrsÏ.

w ÛO45 $%

t RSV$% :l uvw*xfúV

电子器件采购平台: IC资料查询网站: 电子工程技术论坛:/bbs

# ( ÈÉU^ 2VÏ.]$ ® X#Q^WðñRS # »¼ |êeV>$%# ®)ô»îï ®)îï93 îï!Ü v\ï½

X

ê

t mn àgz\ }ZW ¡¢PÒ

W ¡¢B & Wmn\p¡¢

v è

ai

AQZ105D;AQZ107D;AQZ207D;AQZ204D;AQZ202D;中文规格书,Datasheet资料

TYPES1. DC type* Load voltage and current of DC type: DC2. AC/DC type* Load voltage and current of AC/DC type: Peak AC/DCOutput rating*PackagePart No.Packing quantityLoad voltage Load currentInner cartonOuter cartonDC only 60 V 3.6 A SIL4-pin AQZ102D25 pcs.500 pcs.100 V2.3 A AQZ105D 200 V 1.1 A AQZ107D 400 V 0.6 AAQZ104DOutput rating*PackagePart No.Packing quantityLoad voltage Load currentInner cartonOuter cartonAC/DCdual use60 V 2.7 A SIL4-pin AQZ202D 25 pcs.500 pcs.100 V 1.8 A AQZ205D 200 V 0.9 A AQZ207D 400 V0.45 AAQZ204Dmm inchRoHS compliantFEATURES1. A voltage-sensitive power PhotoMOSConventional power PhotoMOS are connected externally to an input limiting resistor in order to obtain the appropriate LED current. Adding an internal constant-current element renders the input limiting resistor unnecessary, making it possible for the PhotoMOS to be voltage-driven.2. Wide range of input voltagesAllows a wide range of input voltages from 4 to 30 V DC. The PhotoMOS can be used in 5 V , 12 V or 24 V DC systems.3. Both AC/DC dual types and DC-only types availableThe AC/DC dual type is capable of bi-directional control, and unlikeconventional SSRs, does not have to be used differently depending on the load. The DC-only type is well suited for control of DC solenoids and DC motors.4. High capacitySupports the various types of loadcontrol, from very small loads to a max. 2.7 A for the AC/DC dual type, max. 3.6 A for the DC-only type.5. High sensitivity and low on-resistanceMax. 3.6 A load can be controlled with the min. input voltage of 4 V DC. The on-resistance is also low at typ. 0.033 Ω (AQZ102D).6. Slim SIL4-pin package(W) 3.5 × (D) 21.0 × (H) 12.5 mm (W) .138 × (D) .827 × (H) .492 inch The compact size of the 4-pin SIL package allows high density mounting.Height includes standoff1 Form A Voltage-sensitive (AQZ10❍D, 20❍D)RATING1. DC type1) Absolute maximum ratings (Ambient temperature: 25°C 77°F )2) Electrical characteristics (Ambient temperature: 25°C 77°F )2. AC/DC type1) Absolute maximum ratings (Ambient temperature: 25°C 77°F )ItemSymbol AQZ102DAQZ105DAQZ107DAQZ104DRemarksInput Input voltageV IN 30 V Input reverse voltageV RIN 5 V Power dissipation P in 300 mWOutputLoad voltage (DC)V L 60 V 100 V 200 V 400 V Continuous load current (DC)I L 3.6 A 2.3 A 1.1 A 0.6 A Peak load current I peak 9.0 A6.0 A3.0 A1.5 A100 ms (1 shot), V L = DCPower dissipationP out 1.35 W T otal power dissipation P T 1.35 W I/O isolation voltage V iso2,500 V ACT emperature limitsOperating T opr –40°C to +85°C –40°F to +185°F (4 V q V IN q 6 V)–40°C to +75°C –40°F to +167°F (6 V < V IN q 15 V)–40°C to +60°C –40°F to +140°F (15 V < V IN q 30 V)Non-condensing at low temperaturesStorageT stg–40°C to +100°C –40°F to +212°FItemSymbol AQZ102DAQZ105DAQZ107DAQZ104DRemarksInputOperate voltageT ypical V Fon 1.4 V I L = 100 mA V L = 10 V Maximum 4 V T urn off voltage Minimum V Foff 0.8 V I L = 100 mA V L = 10 V T ypical 1.3 V Input current T ypical I IN 6.5 mAV IN = 5 V OutputOn resistanceT ypical R on 0.033 Ω0.090 Ω0.33 Ω 1.23 ΩV IN = 5 V I L = Max.Within 1 s on time Maximum 0.09 Ω0.17 Ω0.55 Ω1.6 ΩOff state leakage current Maximum I Leak 10 µAV IN = 0 V V L = Max.T ransfercharacteristicsT urn on time*T ypical T on3.3 ms2.2 ms1.5 ms1.2 msV IN = 5 V I L = 100 mA V L = 10 V Maximum 10.0 msT urn off time*T ypical T off 0.2 ms0.1 msV IN = 5 V I L = 100 mA V L = 10 V Maximum 3.0 ms I/O capacitanceT ypical C iso 0.8 pF f = 1 MHz V B = 0 VMaximum 1.5 pF Initial I/O isolation resistance Minimum R iso 1,000 M Ω500 V DC Maximum operating speedMaximum —0.5 cpsV IN = 5 VDuty factor = 50%I L ×V L = 200 (VA)Vibration resistance Minimum —10 to 55 Hz at double amplitude of 3 mm2 hours for3 axes Shock resistanceMinimum—4,900 m/s 2 {500 G}1 ms3 times for 3 axesItemSymbol AQZ202DAQZ205DAQZ207DAQZ204DRemarksInputInput voltageV IN 30 V Input reverse voltage V RIN 5 V Power dissipationP in 300 mWOutputLoad voltage (peak AC)V L 60 V 100 V 200 V 400 V Continuous load currentI L 2.7 A 1.8 A 0.9 A 0.45 A Peak AC, DCPeak load current I peak 9.0 A6.0 A3.0 A1.5 A100 ms (1 shot), V L = DCPower dissipationP out 1.6 W T otal power dissipation P T 1.6 W I/O isolation voltage V iso 2,500 V ACT emperature limitsOperating T opr –40°C to +85°C –40°F to +185°F (4 V q V IN q 6 V)–40°C to +75°C –40°F to +167°F (6 V < V IN q 15 V)–40°C to +60°C –40°F to +140°F (15 V < V IN q 30 V)Non-condensing at low temperaturesStorageT stg–40°C to +100°C –40°F to +212°F1 Form A Voltage-sensitive (AQZ10❍D, 20❍D)■ For Dimensions.■ For Schematic and Wiring Diagrams.■ For Cautions for Use.■ These products are not designed for automotive use.If you are considering to use these products for automotive applications, please contact your local Panasonic Corporation technical representative.For more information.REFERENCE DATA1. Load current vs. ambient temperature characteristicsAllowable ambient temperature:–40°C to +85°C–40°F to +185°F;V IN : Input voltage; I L (derate):Load current (derate); I L : Absolute maximum ratings of continuous load current2.-(1) Load current vs. ambient temperaturecharacteristics in adjacent mountingInput voltage: 4V q V IN q 6V;I L (derate): Load current (derate); I L : Absolute maximum ratings of continuous load current; : Adjacent mounting pitch2.-(2) Load current vs. ambient temperature characteristics in adjacent mountingInput voltage: 6V < V IN q 15V;I L (derate): Load current (derate); I L : Absolute maximum ratings of continuous load current; : Adjacent mounting pitchAmbient temperature, °CAmbient temperature, °CI L (d e r a t e ) × 100, %I LAmbient temperature, °CI L (d e r a t e ) × 100, %I L1 Form A Voltage-sensitive (AQZ10❍D, 20❍D)2.-(3) Load current vs. ambient temperature characteristics in adjacent mountingInput voltage: 15V<V IN q 30V;I L (derate): Load current (derate); I L : Absolute maximum ratings of continuous load current; : Adjacent mounting pitch3.-(1) On resistance vs. ambient temperature characteristics (DC type)Input voltage: 5 V;Continuous load current:3.6 A (DC) (AQZ102D)2.3 A (DC) (AQZ105D)3.-(2) On resistance vs. ambient temperature characteristics (DC type)Input voltage: 5 V;Continuous load current:1.1 A (DC) (AQZ107D)0.6 A (DC) (AQZ104D)Ambient temperature, °CI L (d e r a t e ) × 100, %I LAmbient temperature, °CO n r e s i s t a n c e , ΩAmbient temperature, °CO n r e s i s t a n c e ,Ω3.-(3) On resistance vs. ambient temperature characteristics (AC/DC type)Input voltage: 5 V;Continuous load current:2.7 A (DC) (AQZ202D)1.8 A (DC) (AQZ205D)3.-(4) On resistance vs. ambient temperature characteristics (AC/DC type)Input voltage: 5 V;Continuous load current:0.9 A (DC) (AQZ207D)0.45 A (DC) (AQZ204D)4.-(1) T urn on time vs. ambient temperature characteristics (DC type)Input voltage: 5 V; Load voltage: 10 V (DC);Continuous load current: 100 mA (DC)Ambient temperature, °CO n r e s i s t a n c e , ΩO n r e s is t a n c e , ΩAmbient temperature, °C461028Ambient temperature, °CT u r n o n t i m e , m s4.-(2) T urn on time vs. ambient temperature characteristics (AC/DC type)Input voltage: 5 V;Load voltage: 10 V (DC);Continuous load current: 100 mA (DC)5.-(1) T urn off time vs. ambient temperature characteristics (DC type)Input voltage: 5 V; Load voltage: 10 V (DC);Continuous load current: 100 mA (DC)5.-(2) T urn off time vs. ambient temperature characteristics (AC/DC type)Input voltage: 5 V; Load voltage: 10 V (DC);Continuous load current: 100 mA (DC)Ambient temperature, °CTu r n o n t i m e , m sAmbient temperature, °CT u rn o f f t i m e , m sAmbient temperature, °CT u r n o f f t i m e , m s6. Operate voltage vs. ambient temperature characteristicsLoad voltage: 10 V (DC);Continuous load current: 100 mA (DC)7. T urn off voltage vs. ambient temperature characteristicsLoad voltage: 10 V (DC);Continuous load current: 100 mA (DC)8. Input current vs. ambient temperature characteristicsInput voltage: 5 V2.03.0–405.00–20204060801.04.085Ambient temperature, °CO p e r a t e v o l t a g e , V02.03.0–405.00–20204060801.04.085Ambient temperature, °CT u r n o f f v o l t a g e , m s46–40100–20204060802885Ambient temperature, °CI n p u t c u r r e n t , m A1 Form A Voltage-sensitive (AQZ10❍D, 20❍D)ACCESSORY (mm inch )9.-(1) Current vs. voltage characteristics of output at MOS portion (DC type)Ambient temperature: 25°C 77°F9.-(2) Current vs. voltage characteristics of output at MOS portion (AC/DC type)Ambient temperature: 25°C 77°F10. Input current vs. input voltage characteristicsAmbient temperature: 25°C 77°F461005101520282530Input voltage, VI n p u t c u r r e n t , m A11.-(1) Off state leakage current vs. load voltage characteristicsAmbient temperature: 25°C 77°F11.-(2) Off state leakage current vs. load voltage characteristicsAmbient temperature: 25°C 77°F12. Maximum operating speed vs. load voltage × load current characteristicsInput voltage: 5V; Ambient temperature: 25°C 77°F10–310–610–910Load voltage, VO f f s t a t e l e a k a g e c u r r e n t , A10–310–610–910Load voltage, VO f f s t a t e l e a k ag e c u r r e n t , AMaximum voltage, V ×Load current, AM a x i m u m o p e r a t i n g s p e e d , c p s13.-(1) Output capacitance vs. applied voltage characteristics (DC type)Frequency: 1 MHz; Ambient temperature: 25°C 77°F13.-(2) Output capacitance vs. applied voltage characteristics (AC/DC type)Frequency: 1 MHz; Ambient temperature: 25°C 77°FApplied voltage, VO u t p u t c a p a c i t a n ce , p FApplied voltage, VO u t p u t c a p a c i t a n c e , p F SocketPA1a-PSPA1a-PS-HPC board pattern (BOTTOM VIEW)Standard typeSelf clinching typeT olerance: ±0.1 ±.004分销商库存信息:PANASONICAQZ105D AQZ107D AQZ207D AQZ204D AQZ202D AQZ205D。

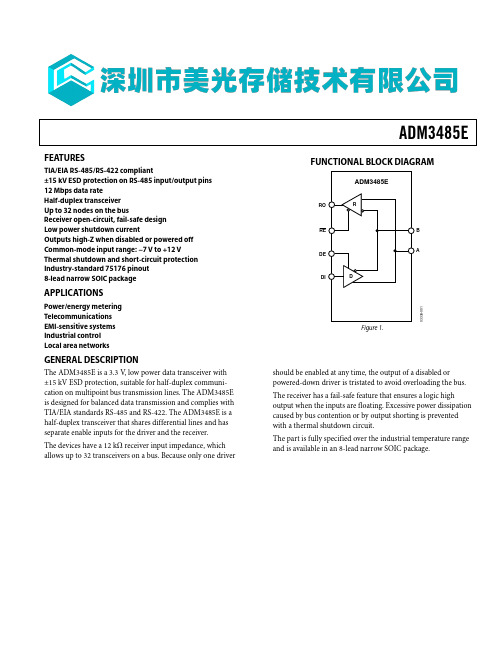

MEMORY存储芯片ADM3485EARZ-REEL7中文规格书

Logic Inputs Input Low Voltage Input High Voltage Logic Input Current

ADM3485E

RO

R

RE

B

A DE

DI

D

03338-001

Figure 1.

should be enabled at any time, the output of a disabled or powered-down driver is tristated to avoid overloading the bus. The receiver has a fail-safe feature that ensures a logic high output when the inputs are floating. Excessive power dissipation caused by bus contention or by output shorting is prevented with a thermal shutdown circuit. The part is fully specified over the industrial temperature range and is available in an 8-lead narrow SOIC package.

ADM3485E

SPECIFICATIONS

19245;中文规格书,Datasheet资料

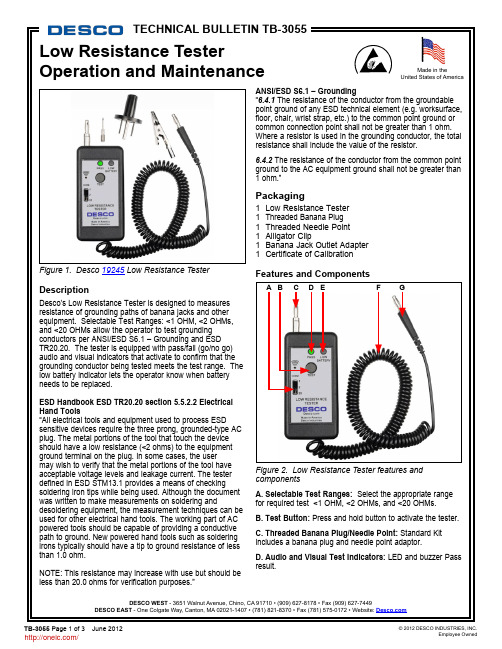

Made in theUnited States of AmericaDescriptionDesco’s Low Resistance Tester is designed to measures resistance of grounding paths of banana jacks and other equipment. Selectable Test Ranges: <1 OHM, <2 OHMs, and <20 OHMs allow the operator to test grounding Figure 1. Desco 19245 Low Resistance TesterANSI/ESD S6.1 – GroundingThe resistance of the conductor from the groundable point ground of any ESD technical element (e.g. worksurface, floor, chair, wrist strap, etc.) to the common point ground or common connection point shall not be greater than 1 ohm. Where a resistor is used in the grounding conductor, the total Figure 2. Low Resistance Tester features and componentsA. Selectable Test Ranges: Select the appropriate range for required test <1 OHM, <2 OHMs, and <20 OHMs.B. Test Button: Press and hold button to activate the tester.BCD EGFE. Low Battery LED: LED illuminates when the battery needs to be replaced.F. 6 Foot Coiled Cord: Insulation black color PVCG. Banana Plug: Industrial Standard .175 “(4.4 mm) Banana Plug, fits banana jack ≥ .157”.OperationUSING THE TESTER 1. Select test range.2. Connect coil cord banana plug end to known ground. Use adaptors where needed. Note: The Desco Low Resistance Tester may be used with an outlet polarity checker, such as Desco’s 19219, to determine a knownground.3. Connect or touch tester end to banana jack or other equipment that is being tested for resistance to ground.4. Press and hold test button.5. An audio and visual indication will activate for Pass result6. No audio or visual indication will indicate a Fail resultFigure 3. Testing banana jacks with 19245 tester.Example of Test Range Uses<1 OHM Range- ESD Technical element Grounding Conductors: Banana Jacks, Grounding Blocks, Mat Ground Cords ANSI/ESD S6.1 Grounding, sections 6.4 Technical Elements, 6.4.1, 6.4.2 and 6.4.3 - New AC Powered Hand ToolsESD Handbook ESD TR20.20 section 5.5.2.2 Electrical Hand Tools<2 OHM- Soldering IronsESD Handbook ESD TR20.20 section 5.5.2.2 Electrical Hand Tools- Other AC Powered Hand ToolsESD Handbook ESD TR20.20 section 5.5.2.2 Electrical Hand Tools<20 OHM- Soldering iron verificationESD Handbook ESD TR20.20 section 5.5.2.2 Electrical Hand Tools- Auxiliary grounds (ground rods) ANSI/ESD S20.20** ANSI/ESD S20.20 requires <25 ohms from the Auxiliary Ground to the Equipment Grounding Conductor. Desco’s Low Resistance Tester only tests to <20 ohms. In cases of a no pass result with the Low Resistance Tester when testing an Auxiliary Ground, an Ohm meter should used to determine the actual resistance from the Auxiliary Ground to the Equipment Grounding ConductorFigure 4. Testing soldering iron with 19245 tester.Figure 6. Testing auxiliary ground with 19245 tester.Remove the 2 screws located at the back of the tester.Remove and turn over the circuit board.4. Locate and replace the battery (3 Volt; Model CR2032).5. Re-assemble the tester.First, place battery under prongsNext, press here to snap battery in place分销商库存信息: DESCO19245。

atc中文手册

当所有64 字节接收完毕主器件发送停止信号内部编程周期开始此时所有接收到的数据在单

个写周期内写入CAT24WC256

应答查询

可以利用内部写周期时禁止数据输入这一特性一旦主器件发送停止位指示主器件操作结束时

CAT24WC256 启动内部写周期应答查询立即启动包括发送一个起始信号和进行写操作的从器件地址

数据的擦写在内部擦写过程中CAT24WC256 不再应答主器件的任何请求

页写

在页写模式下单个写周期内CAT24WC256 最多可以写入64 个字节数据页写操作的启动和字节

写一样不同在于传送了一字节数据后主器件允许继续发送63 个字节每发送一个字节后

CAT24WC256 将响应一个应答位且内部低6 位地址加1 高位地址保持不变如果主器件在发送停止

如果CAT24WC256 正在进行内部写操作将不会发送应答信号如果CAT24WC256 已经完成了内部写

操作将发送一个应答信号主器件可以继续对CAT24WC256 进行下一次读写操作

写保护

写保护操作特性可使用户避免由于不当操作而造成对存储区域内部数据的改写当WP 管脚接高时

整个寄存器区全部被保护起来而变为只可读取CAT24WC256 可以接收从器件地址和字节地址但是装

主器件通过发送一个起始信号启动发送过程然后发送它所要寻址的从器件的地址8 位从器件地

址的高5 位固定为10100 见图5 接下来的2 位A1 A0 为器件的地址位最多可以连接4 个器件

到同一总线上这些位必须与硬连线输入脚A1 A0 相对应从器件地址的最低位作为读写控制位1

表示对从器件进行读操作0 表示对从器件进行写操作在主器件发送起始信号和从器件地址字节后

ORH-YG35A(IF=20mA) 2.0x1.25x0.8mm(0805)标准包装的阿尔加韦伯

PLCC LED Series DatasheetORH-YG35A(IF=20mA)1.Features:⏹Chip material:AlGaInP/GaAs.⏹Emitted Color:Super Yellow Green.⏹Lens Appearance:Water Clear.⏹Mono-color type.⏹ 2.0x1.25x0.8mm(0805)standard package.⏹Suitable for all SMT assembly methods.⏹Compatible with infrared and vapor phase reflow solder process.⏹Compatible with automatic placement equipment.⏹This product doesn’t contain restriction substance,comply ROHS standard.2.Applications:⏹Automotive:Dashboards,stop lamps,turn signals.⏹Backlighting:LCDs,Key pads advertising.⏹Status indicators:Comsumer&industrial electronics.⏹General use.ORH-YG35A 3.Package Dimensions:4.Absolute Maximum Ratings(Ta=25℃)Parameter Symbol Rating Unit Power Dissipation Pd120mW Forward Current I F30mA Peak Forward Current*1I FP100mA Operating Temperature Topr-25℃~80℃-Storage Temperature Tstg-30℃~85℃-Soldering Temperature Tsol260℃-*1Condition for I FP is pulse of1/10duty and0.1msec width.5.Electrical and optical characteristics(Ta=25℃)Parameter Symbol Condition Min.Typ.Max.Unit Forward Voltage Vf I F=20mA 1.8- 2.4V Luminous Intensity Iv I F=20mA1840-mcd Peak Wave Lengthλp I F=20mA-570-nm Dominant Wave Lengthλd I F=20mA566-578nm Spectral Line Half-widthΔλI F=20mA-30-nm Veiwing Angle2θ1/2I F=20mA-120-degORH -YG35A6.Typical Electro-Optical Characteristics CurvesFig.5 Relative luminous intensity vs. forward currentR e l a t i v e l u m i n o u s i n t e n s i t y (@20m A )0.51.01.52.0F o r w a r d c u r r e n t (m A )20103040Forward voltage(V)Fig.3 Forward current vs. forward voltageFig.1 Relative intensity vs. wavelengthR e l a t i v e r a d i a n t i n t e n s i t y500.5Wavelength (nm)R e l a t i v e L u m i n o u s i n t e n s i t yAmbient temperature Ta( C)A(N o r m a l i z e d @20m A )0.51.002.02.51.5vs. ambient temperatureAmbient temperature Ta( C)F o r w a r d c u r r e n t (m A )3.0103040206050Fig.2 Forward current derating curveFig.4 Relative luminous intensity vs.ambient temperatureForward current (mA)R E L A T I V E R A D I A N T I N T E N S I T YRADIATION DIAGRAM0.90.70.890807060501.0020104030ORH-YG35A 7.Judgment criteria of failure for the reliabilityMeasuring items Symbol Measuring conditions Judgement criteria for failure Forward voltage V F(V)I F=20mA Over Ux1.2Reverse current I R(uA)V R=5V Over Ux2Luminous intensity Iv(mcd)I F=20mA Below SX0.5Note:1).U means the upper limit of specified characteristics.S means initial value.2).Measurment shall be taken between2hours and after the test pieces have been returned tonormal ambient conditions after completion of each test.8.Bin LimitsIntensity Bin Limits(At20mA)BIN CODE Min.(mcd)Max.(mcd)L1828M2842N4263P6394Tolerance for each Bin limit is±15%.Color Bin Limits(At20mA)BIN CODE Min.(v)Max.(v)4566569556957265725757575578Tolerance for each Bin limit is±1nm.ORH -YG35AV F Bin Limits (At 20mA)BIN CODEMin.(v)Max.(v)B 1.8 2.0C 2.0 2.2D2.22.4Tolerance for each Bin limit is ±0.05V.9.BIN :x x xV F BI N CO D E Co l o r BI N CO D E In t e n s i t y BI N CO D E10.Tapping and packaging specifications(Units:mm)FIXING TAPE0.3TRAILERLEADER2.26±0.171.0±1±±USER DIRECTION OF FEEDC A T H OD E4.0A N O D E5.3±0.05START1.420.38.0±NOTE: 4000 pcs PER REEL3.52.0±0.054.00.1±0.11.5±0.11.750.1±0.1END±0.05±13.00.5ORH-YG35A 11.Package Method:(unit:mm)12.Package and Label of Products:(1)Package:Products are packed in one bag of3000pcs(one taping reel)and a label is attached oneach bag.(2)Label:ORIENT LOGOPart No.QuantityBINSealing Datex xx xx xxYear Month DayManufacture LocationORH-YG35A 13.Reliability TestClassification Test Item Reference Standard Test Conditions ResultEnduranceTest Operation Life MIL-STD-750:1026MIL-STD-883:1005JIS-C-7021:B-1Connect with a power If=20mATa=Under room temperatureTest time=1,000hrs0/20HighTemperatureHigh HumidityStorageMIL-STD-202:103BJIS-C-7021:B-11Ta=+65℃±5℃RH=90%-95%Test time=240hrs0/20HighTemperatureStorageMIL-STD-883:1008JIS-C-7021:B-10High Ta=+85℃±5℃Test time=1,000hrs0/20LowTemperatureStorageJIS-C-7021:B-12Low Ta=-35℃±5℃Test time=1,000hrs0/20EnvironmentalTest TemperatureCyclingMIL-STD-202:107DMIL-STD-750:1051MIL-STD-883:1010JIS-C-7021:A-4-35℃~+25℃~+85℃~+25℃60min20min60min20minTest Time=5cycle0/20Thermal Shock MIL-STD-202:107DMIL-STD-750:1051MIL-STD-883:1011-35℃±5℃~+85℃±5℃20min20minTest Time=10cycle0/20SolderResistanceMIL-STD-202:201AMIL-STD-750:2031JIS-C-7021:A-1Preheating:140℃-160℃,within2minutes.Operation heating:260℃(Max.),within10seconds.(Max.)0/2014.Soldering:1).Manual Of SolderingThe temperature of the iron tip should not be higher than300℃(572℉)and Soldering within3 seconds per solder-land is to be observed.2).Reflow SolderingPreheating:140℃~160℃±5℃,within2minutes.Operation heating:260℃(Max.)within10seconds.(Max)Gradual Cooling(Avoid quenching).ORH -YG35A3).DIP soldering (Wave Soldering):Preheating :120℃~150℃,within 120~180sec.Operation heating :245℃±5℃within 5sec.260℃(Max)Gradual Cooling (Avoid quenching).15.Handling :Care must be taken not to cause to the epoxy resin portion of ORIENTLEDs while it is exposed to high temperature.Care must be taken not rub the epoxy resin portion of ORIENT LEDs with hard or sharp article such as the sand blast and the metal hook .16.Notes for designing:Care must be taken to provide the current limiting resistor in the circuit so as to drive the ORIENT LEDs within the rated figures.Also,caution should be taken not to overload ORIENT LEDs with instantaneous voltage at the turning ON and OFF of the circuit.When using the pulse drive care must be taken to keep the average current within the rated figures.Also,the circuit should be designed so as be subjected to reverse voltage when turning off the ORIENT LEDs.Temperature TimeOVER 2 MIN.4℃ /SEC. MAX. 4℃ /SEC. MAX.10 SEC. MAX.260℃ MAX.140~160℃TemperatureTime120~180 sec.Preheat 245 ±5℃ within 5 sec.Soldering heat Max. 260 ℃120~150℃ORH-YG35A17.Storage:In order to avoid the absorption of moisture,it is recommended to solder ORIENT LEDs as soon as possible after unpacking the sealed envelope.If the envelope is still packed,to store it in the environment as following:(1)Temperature:5℃-30℃(41℉)Humidity:RH60﹪Max.(2)After this bag is opened,devices that will be applied to infrared reflow,vapor-phase reflow,orequivalent soldering process must be:pleted within24hours.b....Stored at less than30%RH.(3)Devices require baking before mounting,if:(2)a or(2)b is not met.(4)If baking is required,devices must be baked under below conditions:12hours at60℃±3℃.。

ADP090 Electrical Signal Insert Adaptor Technical

ADP090 Electrical Signal Insert Adaptor Technical Reference ManualIADP090.1Technical Reference Manual Larson Davis ADP090 Electrical Signal Insert Adaptor1/2" Microphone EquivalentCopyrightCopyright 2008 by PCB Piezotronics, Inc. This manual is copyrighted, with all rights reserved. The manual may not be copied in whole or in part for any use without prior written consent of PCB Piezotronics, Inc.DisclaimerThe following paragraph does not apply in any state or country where such statements are not agreeable with local law:Even though PCB Piezotronics, Inc. has reviewed its documentation, PCB Piezotronics, Inc. makes no warranty or representation, either expressed or implied, with respect to this instrument and documentation, its quality, performance, merchantability, or fitness for a particular purpose. This documentation is subject to change without notice, and should not be construed as a commitment or representation by PCB Piezotronics, Inc.This publication may contain inaccuracies or typographical errors. PCB Piezotronics, Inc. will periodically update the material for inclusion in new editions. Changes and improvements to the information described in this manual may be made at any time.RecyclingPCB Piezotronics, Inc. is an environmentally friendly organization and encourages our customers to be environmentally conscious. When this product reaches its end of life, please recycle the product through a local recycling center or return the product to:PCB Piezotronics, Inc.Attn: Recycling Coordinator1681 West 820 NorthProvo, Utah, USA 84601-1341where it will be accepted for disposalADP090 Electrical Signal Insert Adaptor 1/2” Microphone EquivalentApplicationThe ADP090 is used in place of a 1/2” microphone for the following:•Electrical signal insert testing of sound level meters and preamplifiers •Noise floor testing of instrumentsDescriptionThe ADP090 contains a 12 pF Capacitor for electrical signal injection from a signal generator into a preamplifier in place of an acoustical signal. It has a female BNC connector on one end for connection to a signal generator and a ½" female microphone thread on the opposite end. This electrical adaptor is used to simulate the electrical characteristics of a microphone with a capacitance near 12 pF. A male BNC with an internal short is included for electrical noise floor testing.Dimensions: 63.5 mm (2.50") long x 12.7 mm (0.5") diameterThread for preamplifier mounting: 11.7 mm-60 UNS (0.4606-60 UNS)Capacitance: 12 pF ±5%Maximum microphone bias: 250 Volts BNC with ShortSignal Insert AdaptorExtra AttenuationThe rugged construction of the ADP090 means the there is a small capacitance at the preamplifier end of the adaptor. This capacitance results from the physical construction of the adaptor and has a value of about 0.3 pF. It will give added attenuation to the signal since it is in parallel (shunt) across the input of the preamplifier.When used with the following PCB microphone preamplifiers, there is an extra attenuation as shown in Table 1.Preamplifier Extra Attenuation (dB)Uncertainty k = 2 (dB) 426A100.210.04426A110.210.04426A120.210.04426A300.210.04426E010.210.04HT426E010.210.04PRM8310.210.04PRM900C0.210.04PRM9020.210.04PRMLxT10.150.04PRMLxT20.050.04Table 1 : ADP090 Extra Attenuation Measured at 1 kHzApplication ExampleExample: Using an ADP090, determine the effects of the 426E01 loading on a microphone with capacitance equal to 12 pF.Step 1Connect the ADP090 to a 426E01 preamplifierStep 2Remove the BNC shortStep 3Connect the output of a signal generator to the female BNC of the ADP090 and set it to generate a 1 kHz sine wave having an output of 0.500 Vrms.Step 4Measure the output signal of the 426E01 and note that it has amplitude of 0.482 Vrms.Step 5Compute the difference between the input signal and the measured output signal in dB. dB = 20*log10(VmeasuredOutput/Vinput) = -0.32 for this example. The negative sign indicates attenuation. The total attenuation would be 0.32 dB.Step 6Find the ADP090 extra attenuation from Table 1 : 'ADP090 Extra Attenuation Measured at 1 kHz' for the 426E01 preamplifier, which is 0.21 dB. Step 7426E01 loading is equal to the measured attenuation minus the losses due to the 0.3 pF capacitance in the ADP090. Thus, the loading is 0.32 - 0.21 dB = 0.11 dB.Other MicrophonesFor microphones with other capacitance values, use the PCB adaptors indicated in Table 2.Microphone Capacitance (pF)Appropriate Adaptor6.8ADP00218ADP00547ADP006Table 2 : Alternative AdaptorsT otal Customer Satisfaction Guaranteed 3425Walden A venue,Depe w NY USA14043 Phone:716-926-8243T oll Free:888-258-3222 FA X:716-926-8215。

ADP5065:兼容USB功率电能快速电池充电管理方案

•容错输入电压-0.5V~+20V(USBVBUS)

•电池和充电器输出之间的隔离FET

•电池热敏电阻输入,当电池温度超过限值时自动关闭充电器

•符合JEITA锂离子电池充电温度规范

•SYS_EN_OK标志,暂缓系统开通(直到电池要求的最低水

ADP5065:兼容USB功率电能快速电池充电管理方

案

ADI公司的ADP5065是一款内嵌互联直流电压充电输出端与电池端

的FET器件,通过FET可以实现电池隔离,当系统驱动电能来自于废电池或

没有电池时,系统会立即切换到USB供电模式。ADP5065的输入电压范围

为4V~5.5V,最大输入电压高达20V,不用担心USB总线断开或连接过程中

•手机

平)

•由最小电池电压和/或最小电池充电的要求水平启动系统

•EOC编程,C/20,C/10和选择特定的电流水平

表1ADP5065设计方案材料清单

图2ADP5065方框图

ADP5065应用

•数码相机

•数码摄像机

•单节锂离子电池的便携式设备

•PDA、音频、GPS设备

的峰值。ADP5065充电器兼容USB2.0、USB3.0和USB电池充电规范1.1。

ADP5065采用一个非常小的封装,20引脚WLCSP封装(0.5mm间距)。

ADP5065主要特性

•3MHz开关模式充电器

图1ADP5065设计原理图

CM6400A;中文规格书,Datasheet资料