TMS320DM6443ZWT中文资料

TMS320DM642中文资料

TMS320DM642中文资料1.2 概述TMS320C64x DSP芯片(包括TMS320DM642)是在TMS320C6000 DSP平台上的高性能定点DSP。

TMS320DM642(DM642)是基于有TI开发的第二代高性能,先进VelociTI技术的VLIW结构(VelociTI1.2),从而使得这些DSP芯片成为数字多媒体的极好的选择。

DM642在主频720MHz下处理速度达到5760MIPS,并且给高性能DSP规划提供了廉价的解决方案。

DM642操作灵活的高速处理器和用数字表达容量的阵列处理器。

C64x DSP核具有64个32位字长的通用寄存器和8个独立的功能单元——两个结果为32位的乘法器和6个ALUs——是VelociTI1.2的升级版。

VelociTI1.2升级版在8个功能单元里包括新的指令,可以在视频和图像应用方面提高性能,并能对VelociTI结构进行扩充。

DM642每周期能够提供4个16位MACs,每秒可提供2880百万个MACs,或者8个8位MACs,每秒5760MMACs。

DM642具有特殊应用的硬件结构,片上存储器和与其它的C6000系列DSP平台相似的额外的片上外围设备。

DM642使用两级缓存,有一个强大的多变的外围设置。

一级程序缓存L1P是一个128Kbit的直接映射缓存,另一级数据缓存L1D是一个128Kbit双路结合设置缓存。

L2存储器能被配置成映射存储器,高速缓存或者两者结合。

外围设置包括:3个可配置的视频端口;1个10/100Mb/s的以太网控制器(EMAC);1个管理数据输入输出(MDIO);1个内插VCXO控制接口;1个McASP0;1个I2C总线;2个McBSPs;3个32位通用定时器;1个用户配置的16位或32位主机接口(HPI16/HPI32);1个PCI;1个16引脚的通用输入输出口(GP0),具有可编程中断/事件产生模式;1个64位IMIFA,可以与同步和异步存储器和外围设备相连。

MEMORY存储芯片TMS32C6414TBGLZWA8中文规格书

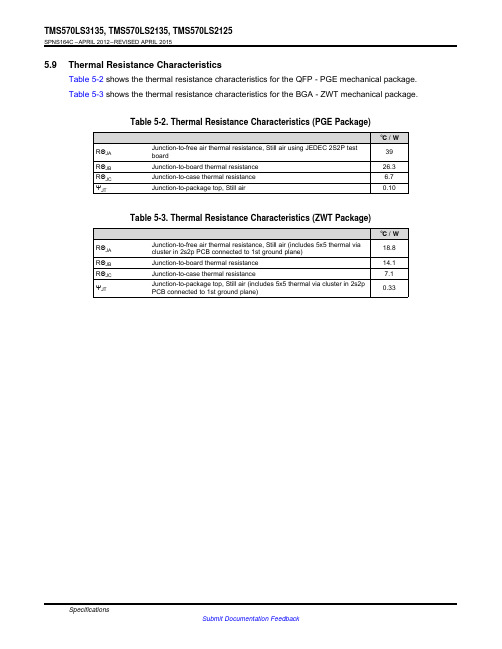

TMS570LS3135,TMS570LS2135,TMS570LS2125SPNS164C–APRIL2012–REVISED APRIL20155.9Thermal Resistance CharacteristicsTable5-2shows the thermal resistance characteristics for the QFP-PGE mechanical package.Table5-3shows the thermal resistance characteristics for the BGA-ZWT mechanical package.Table5-2.Thermal Resistance Characteristics(PGE Package)°C/WJunction-to-free air thermal resistance,Still air using JEDEC2S2P testRΘJA39boardRΘJB Junction-to-board thermal resistance26.3RΘJC Junction-to-case thermal resistance 6.7ΨJT Junction-to-package top,Still air0.10Table5-3.Thermal Resistance Characteristics(ZWT Package)°C/WJunction-to-free air thermal resistance,Still air(includes5x5thermal viaRΘJA18.8cluster in2s2p PCB connected to1st ground plane)RΘJB Junction-to-board thermal resistance14.1RΘJC Junction-to-case thermal resistance7.1Junction-to-package top,Still air(includes5x5thermal via cluster in2s2pΨJT0.33PCB connected to1st ground plane)SpecificationsTMS570LS3135,TMS570LS2135,TMS570LS2125SPNS164C–APRIL2012–REVISED APRIL2015 5.10Output Buffer Drive StrengthsTable5-4.Output Buffer Drive StrengthsLOW-LEVEL OUTPUT CURRENT,I OL for V I=V OLmaxor SIGNALSHIGH-LEVEL OUTPUT CURRENT,I OH for V I=V OHminFRAYTX2,FRAYTX1,FRAYTXEN1,FRAYTXEN2,MIBSPI5CLK,MIBSPI5SOMI[0],MIBSPI5SOMI[1],MIBSPI5SOMI[2],MIBSPI5SOMI[3],MIBSPI5SIMO[0],MIBSPI5SIMO[1],MIBSPI5SIMO[2],MIBSPI5SIMO[3],8mA TMS,TDI,TDO,RTCK,SPI4CLK,SPI4SIMO,SPI4SOMI,nERROR,N2HET2[1],N2HET2[3],All EMIF Outputs and I/Os,All ETM OutputsMIBSPI3SOMI,MIBSPI3SIMO,MIBSPI3CLK,MIBSPI1SIMO,MIBSPI1SOMI,MIBSPI1CLK, 4mAnRSTAD1EVT,CAN1RX,CAN1TX,CAN2RX,CAN2TX,CAN3RX,CAN3TX,DMM_CLK,DMM_DATA[0],DMM_DATA[1],DMM_nENA,DMM_SYNC,GIOA[0-7],GIOB[0-7],LINRX,LINTX,2mA zero-dominantMIBSPI1NCS[0],MIBSPI1NCS[1-3],MIBSPI1NENA,MIBSPI3NCS[0-3],MIBSPI3NENA,MIBSPI5NCS[0-3],MIBSPI5NENA,N2HET1[0-31],N2HET2[0],N2HET2[2],N2HET2[4],N2HET2[5],N2HET2[6],N2HET2[7],N2HET2[8],N2HET2[9],N2HET2[10],N2HET2[11],N2HET2[12],N2HET2[13],N2HET2[14],N2HET2[15],N2HET2[16],N2HET2[18],SPI2NCS[0],SPI2NENA,SPI4NCS[0],SPI4NENAECLK,selectable8mA/2mA SPI2CLK,SPI2SIMO,SPI2SOMIThe default output buffer drive strength is8mA for these signals.Table5-5.Selectable8mA/2mA ControlSIGNAL CONTROL BIT ADDRESS8mA2mAECLK SYSPC10[0]0xFFFF FF7801SPI2CLK SPI2PC9[9](1)0xFFF7F66801SPI2SIMO SPI2PC9[10](1)0xFFF7F66801SPI2SOMI SPI2PC9[11](1)0xFFF7F66801(1)Either SPI2PC9[11]or SPI2PC9[24]can change the output strength of the SPI2SOMI pin.In case of a32-bit write where these two bitsdiffer,SPI2PC9[11]determines the drive strength.SpecificationsTMS570LS3135,TMS570LS2135,TMS570LS2125SPNS164C–APRIL2012–REVISED APRIL20155.11Input TimingsFigure5-2.TTL-Level InputsTable5-6.Timing Requirements for Inputs(1)MIN MAX UNIT t pw Input minimum pulse width t c(VCLK)+10(2)ns(1)t c(VCLK)=peripheral VBUS clock cycle time=1/f(VCLK)(2)The timing shown in Figure5-2is only valid for pins used in GPIO mode.5.12Output TimingsTable5-7.Switching Characteristics for Output Timings versus Load Capacitance(C L)PARAMETER MIN MAX UNITCL=15pF 2.5CL=50pF4Rise time,t r nsCL=100pF7.2CL=150pF12.5 8mA low EMI pins(see Table5-4)CL=15pF 2.5CL=50pF4Fall time,t f nsCL=100pF7.2CL=150pF12.5CL=15pF 5.6CL=50pF10.4Rise time,t r nsCL=100pF16.8CL=150pF23.2 4mA low EMI pins(see Table5-4)CL=15pF 5.6CL=50pF10.4Fall time,t f nsCL=100pF16.8CL=150pF23.2 2mA-z low EMI pins CL=15pF8(see Table5-4)CL=50pF15Rise time,t r nsCL=100pF23CL=150pF33CL=15pF8CL=50pF15Fall time,t f nsCL=100pF23CL=150pF33 Specifications。

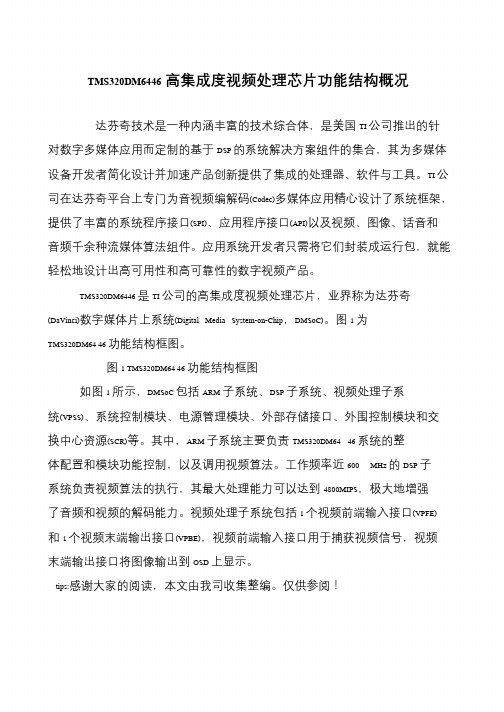

TMS320DM6446高集成度视频处理芯片功能结构概况

TMS320DM6446高集成度视频处理芯片功能结构概况达芬奇技术是一种内涵丰富的技术综合体,是美国TI 公司推出的针对数字多媒体应用而定制的基于DSP 的系统解决方案组件的集合,其为多媒体设备开发者简化设计并加速产品创新提供了集成的处理器、软件与工具。

TI 公司在达芬奇平台上专门为音视频编解码(Codec)多媒体应用精心设计了系统框架,提供了丰富的系统程序接口(SPI)、应用程序接口(API)以及视频、图像、话音和音频千余种流媒体算法组件。

应用系统开发者只需将它们封装成运行包,就能轻松地设计出高可用性和高可靠性的数字视频产品。

TMS320DM6446 是TI 公司的高集成度视频处理芯片,业界称为达芬奇(DaVinci)数字媒体片上系统(Digital Media System-on-Chip,DMSoC)。

图1 为TMS320DM64 46 功能结构框图。

图1 TMS320DM64 46 功能结构框图如图1 所示,DMSoC 包括ARM 子系统、DSP 子系统、视频处理子系统(VPSS)、系统控制模块、电源管理模块、外部存储接口、外围控制模块和交换中心资源(SCR)等。

其中,ARM 子系统主要负责TMS320DM64 46 系统的整体配置和模块功能控制,以及调用视频算法。

工作频率近600 MHz 的DSP 子系统负责视频算法的执行,其最大处理能力可以达到4800MIPS,极大地增强了音频和视频的解码能力。

视频处理子系统包括1 个视频前端输入接口(VPFE) 和1 个视频末端输出接口(VPBE),视频前端输入接口用于捕获视频信号,视频末端输出接口将图像输出到OSD 上显示。

tips:感谢大家的阅读,本文由我司收集整编。

仅供参阅!。

硬件接口体系结构及EVM板的使用.

L1P Cache

Video port-1 Video port-2 66MHz PCI 10/100 Ethernet MAC McASP EMIF

Enhanced DMA Controller

C64xTM DSP Core

L1D Cache

64-bit wide @ 133MHz SDRAM

Connects to IP packet networks McASP Multichannel audio serial port Up to 16 stereo lines (32 channels)

DM642的VIDEO PORT 及硬件连接 I2C

I2C

DM642的VIDEO PORT 及硬件连接

I2C

DM642的VIDEO PORT 及硬件连接 DM642的VP时序与SAA7105的时序

DM642

SAA7105

DM642的VIDEO PORT 及硬件连接

DM642的VIDEO PORT 及硬件连接

DM642的VIDEO PORT 及硬件连接

DM642的音频接口与音频CODEC的连接

UART与DSP的连接

I/O Device

DMA与EDMA

直接存储器访问(Direct Memory Access,DMA) 它可以在没有CPU参与的 情况下,由DMA控制寄存器完成DSP存储空间内的数据搬移。数据搬移的 源/目的可以是片内存储器、片内外设或外部器件。C6000的DMA控制器的 主要特点有以下几点:

提供了64个通道; 通道间的优先级可以设置; 支持不同结构数据传输的链接; 支持对8BIT、16BIT、32BIT数据的存取; 基于RAM的配置结构(PaRAM)--EDMA资料P119

2DSP芯片(TMS320DM642)概述

第 2 章TMS320C6000 DSP 芯片概述本章介绍了TI公司是DSP芯片和DSP芯片的命名规则,并着重介绍了TMS320DM642的器件特性及总体原理框图。

本章的知识要点为理解TMS320DM6 4的原理框图构成,本章建议安排 2 个课时进行学习。

2.1 DSP 芯片概述随着信息技术的高速发展,数字信号处理器(Digital Signal Processor,DSP)的应用范围越来越广,普及率越来越高。

DSP的应用领域主要包括:图形图像领域(如图形变换、图像压缩、图像传输、图像增强、图像识别等)、自动化控制领域(如导航和定位、振动分析、磁盘驱动、激光打印、机器人控制等)、消费电力领域(如智能玩具、扫描仪、机顶盒、VCD/DVD 可视电话、传真机等)、电子通信领域(如蜂窝电话、IP电话、无线调制解调器、数字语音嵌入等)、语音处理领域(如语音综合、语音增强、语音识别、语音编码等)、工业应用领域(如数字控制、机器人技术、在线监控等)、仪器仪表领域(如数字滤波器、函数发生器、瞬时分析仪、频谱分析仪、数据采集仪器等)、医疗器械领域(如诊断设备、助听器、病情监控器、心电图设备、超声设备等)、军事领域(如导弹制导、导航、雷达、保密通信等)。

因此,DSP 在当今电子通信类产品中起到了不可或缺的作用。

2.1.1 主要类型DSP 芯片主要分为以下两大类:(1)专用DSP芯片。

这类芯片被设计和加工成独立的电路模块,只能完成功能单一的任务,它们的使用场合比较特殊,通常应用于高速信号处理环境中,如执行FFT运算、数值滤波运算、卷积运算等,专用DSP芯片通过硬件逻辑实现信号处理算法,而不是采用内部编程的方法,这种机制保证了专用DSP芯片的执行效率、提高了其运算速度,专用DSP芯片在应用中无须程序设计。

只要根据其功能设计外围电路即可。

(2)通用可编程数字信号处理器(Programmable Digital Signal Processor)。

MEMORY存储芯片TMS320DM642AZDK中文规格书

87TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Peripheral Information and Electrical SpecificationsCopyright ©2008–2014,Texas Instruments Incorporated 6.10External Memory Interface A (EMIFA)EMIFA is one of two external memory interfaces supported on the C6745/6747.It is primarily intended to support asynchronous memory types,such as NAND and NOR flash and Asynchronous SRAM.However on C6745/6747EMIFA also provides a secondary interface to SDRAM.6.10.1EMIFA Asynchronous Memory SupportEMIFA supports asynchronous:•SRAM memories•NAND Flash memories•NOR Flash memoriesThe EMIFA data bus width is up to 16-bits on the ZKB packageand 8bits on the PTP package.Both devices support up to fifteen address lines and an external wait/interrupt input.Up to four asynchronous chip selects are supported by EMIFA (EMA_CS[5:2]).All four chip selects are available on the ZKB package.Two of the four are available on the PTP package (EMA_CS[3:2]).Each chip select has the following individually programmable attributes:•Data Bus Width•Read cycle timings:setup,hold,strobe•Write cycle timings:setup,hold,strobe•Bus turn around time•Extended Wait Option With Programmable Timeout•Select Strobe Option•NAND flash controller supports 1-bit and 4-bit ECC calculation on blocks of 512bytes.6.10.2EMIFA Synchronous DRAM Memory SupportThe C6745/6747ZKB package supports 16-bit SDRAM in addition to the asynchronous memories listed in Section 6.10.1.It has a single SDRAM chip select (EMA_CS[0]).SDRAM configurations that are supported are:•One,Two,and Four Bank SDRAM devices•Devices with Eight,Nine,Ten,and Eleven Column Address•CAS Latency of two or three clock cycles•Sixteen Bit Data Bus Width• 3.3V LVCMOS InterfaceAdditionally,the SDRAM interface of EMIFA supports placing the SDRAM in Self Refresh and Powerdown Modes.Self Refresh mode allows the SDRAM to be put into a low power state while still retaining memory contents;since the SDRAM will continue to refresh itself even without clocks from the DSP.Powerdown mode achieves even lower power,except the DSP must periodically wake the SDRAM up and issue refreshes if data retention is required.Finally,note that the EMIFA does not support Mobile SDRAM devices.Table 6-17below shows the supported SDRAM configurations for EMIFA.SDRAM Interface98TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Peripheral Information and Electrical Specifications Copyright ©2008–2014,Texas Instruments Incorporated6.11External Memory Interface B (EMIFB)Figure 6-20illustrates a high-level view of the EMIFB and its connections within the device.Multiple requesters have access to EMIFB through a switched central resource (indicated as crossbar in the figure).The EMIFB implements a split transaction internal bus,allowing concurrence between reads and writes from the various requesters.Figure 6-20.EMIFB Functional Block DiagramEMIFB supports a 3.3V LVCMOS Interface.6.11.1EMIFB SDRAM Loading LimitationsEMIFB supports SDRAM up to 152MHz with up to two SDRAM or asynchronous memory loads.Additional loads will limit the SDRAM operation to lower speeds and the maximum speed should be confirmed by board simulation using IBIS models.。

TMS320DM642简述

tms320dm642是TI公司C6000系列DSP中最新的顶点DSP,其核心是C6416型高性能数字信号处理器,具有极强的处理性能,高度的灵活性和可编程性,同时外围集成了非常完整的音频、视频和网络通信等设备及接口,特别适用于机器视觉、医学成像、网络视频监控、数字广播以及基于数字视频/图像处理的消费类电子产品等高速DSP应用领域。

笔者针对市场客户的需求,设计并实现了一款以TVP5150为视频输入解码器,以PCM1801为音频输入采集电路,以TMS320DM642型DSP为核心处理器的多路视频采集兼压缩处理PCI板卡,并将其应用于构建高稳定性、高鲁棒性和多媒体数字监控系统,取得了较好的社会效益和经济效益。

编辑本段TMS320DM642的硬件架构TMS320DM642采用第二代高性能、先进的超长指令字veloci T1.2结构的DSP核及增强的并行机制,在720M赫兹的时钟频率下,其处理性能为5760MI/s,使得该款DSP成为数字媒体解决方案的首选产品,它不仅拥有高速控制器的操作灵活性,而且具有阵列处理器的数字处理能力,TMS320DM642的外围集成了非常完整的音频、视频和网络通信接口,编辑本段主要构成3个可配置的视频端口(VPORT0-2)能够与通用的视频编、解码器实现无缝连接,支持多种视频分辨率及视频标准,支持RAW视频输入/输出,传输流模式;1个10/100Mb/s以太网接口(EMAC),符合IEEE 802.3标准;1个多通道带缓冲音频串行端口(McASP),支持I2S,DIT,S/PDIF,IEC60958-1,AES-3、CP-430等音频格式;2个多通道带缓冲串行端口(McBSP),采用RS232电平驱动;1个VCXO内插控制单元(VIC),支持音/视频同步;1个32位、66M赫兹、3.3V主/从PCI接口,遵循PCI2.2规范;1个用户可配置的16/32主机接口(HPI);1个16位通用输入/输出端口(GPIO);1个64位外部存储器接口(EMIF),能够与大多数异步存储器(SRAM、EPROM)及同步存储器(SDRAM,SBSRAM,ZBT SRAM,FIFO)无缝连接,最大可寻址外部存储器空间为1024MB;1个具有64路独立通道的增强型直接内存访问控制器(EDMA);1个数据管理输入/输出模块(MDIO);1个I2C总线模块;3个32位通用定时器;1个符合IEEE 1149.1标准的JTAG接口及子板接口等。

(第1讲)第2章 TMS320DM642的硬件资源1

• Two sets of data-addressing units (.D1 and .D2) are responsible for all data transfers between the register files and the memory. The data address driven by the .D units allows data addresses generated from one register file to be used to load or store data to or from the other register file.

通用寄存器组A和B支持16位、32位、40位、8

位、64位定点型数据格式;

32位的寄存器可以存放4个8位数据或存放2个16

位数据,64位寄存器可以存放4个16位数据。

2013-5-11

第2章 TMS320DM642的硬件资源

4

第2章 TMS320DM642的硬件资源

8个并行的处理单元

分为2组,L1, S1, M1, D1为1组,L2, S2, M2, D2为2组;

第1组功能单元直接对A组通用寄存器寻址

和操作,第2组功能单元直接对B组通用寄

存器寻址和操作;

8个功能单元进行逻辑、移位、乘法、加法

和数据寻址等操作。

2013-5-11 第2章 TMS320DM642的硬件资源 5

第2章 TMS320DM642的硬件资源

8个并行的处理单元 • The two .S and .L functional units perform a general set of arithmetic, logical, and branch functions with results available every clock cycle. • The two .M functional units perform all multiplication operations.

TMS320DM642中文资料_特点

TMS320DM642中文资料_特点TMS320DM642 视频/图像定点数字信号处理器1TMS320DM642视频/图像定点数字信号处理器1.1特点●高性能数字媒体处理器-2-,1.67-,1.39-ns 指令周期-500-,600-,720-MHz时钟频率-每周期执行8条32位指令-与C64x完全兼容●V elociT1.2是具有先进超长指令字(VLIW)TMS320C64x DSP核V elociT的升级版-8个独立的功能单元6个ALU(32/40bit),每个功能单元支持每时钟周期32位算术操作,双16位比特算术操作,或4个8位算术操作2个乘法器支持每时钟周期4个16×16位的乘法(结果是32位)或者8个8×8位乘法(结果是16位)-具有无需阵列支持的负载存储结构(1)-64/32位通用寄存器-指令打包技术,减少代码容量●指令设置特点-字节寻址(8/16/32/64位数据)-8位溢出保护-可位提取,设置,清除操作-标准化,饱和度(1),位计数-增强交互的V elociT1.2●L1/L2存储器结构-128Kbit(16Kbyte)L1P程序缓存(直接映射)-128Kbit(16Kbyte)L1D数据缓存(2路结合设置)-2Mbit(256Kbyte)L2标准映射RAM/缓存(灵活的RAM/缓存分配)●小端模式,大端模式●64位外部存储器接口(EMIF)-支持异步存储器(SRAM和EPROM)和同步存储器(SDRAM,SBSRAM,ZBT SRAM 和FIFO)直接接口-总共1024Mbyte可寻址外部存储空间●增强的直接存储器访问(EDMA)控制器(64个独立的通道)●10/100Mb/s以太网控制器(EMAC)-适应IEEE802.3-媒体独立接口(MII)-8个独立的发送通道和1个接收通道●管理数据输入输出(MDIO)●3个可配置视频接口-给公共的视频编码解码器件提供一个直接I/F接口-支持多种协议/视频标准●内插VCXO控制接口-支持同步音频/视频●主机接口(HPI)[32/16位]●符合PCI接口规范2.2版本,32位/66MHz,3.3V PCI主/从接口●多通道音频串行接口(McASP)-8个串行数据引脚-多种I2S和相似的比特流格式-完整的数字音频I/F发送器,支持P/DIF, IEC60958-1, AES-3, CP-430格式●I2C总线●2个多通道缓存串行接口●3个32位通用定时器●16个通用输入输出(GPIO)引脚●灵活的PLL时钟发生器●支持IEEE-1149.1(JTAG)边界扫描接口●548引脚球栅阵列(BGA)封装(GDK和ZDK为后缀),0.8mm Ball Picth(1) ●548引脚球栅阵列(BGA)封装(GNK和ZNK 为后缀),1.0mm Ball Picth(1) ●0.13μm/6等级CMOS工艺●I/O采用3.3V供电,内核采用1.2V供电(-500)●I/O采用3.3V供电,内核采用1.4V供电(A-500,A-600,-600,-720)注:红字为翻译有疑问的地方,()中的数字为相应pdf文档的页数。

HELLODSP TMS320DM642中文手册

前言《TMS320DM642中文手册》在DSP交流网()网友们的共同努力下,经过一个多月的翻译终于完成了,这是首次尝试,也是一次出色的合作。

此次翻译由网友亮亮发起,并全程负责,在这里对亮亮表示真诚的感谢和敬佩。

同时,非常感谢以下参与翻译的网友们:KaZE 虎妞Michael 碧鲨龙啸九天可可橘子Iceprince 田羽Steward Shayne ward 张焱翔Gaofeng_Q^_^ 风来的西林/$ JH DSP-F2812 方块糖流星~落梦另类爷们kelly 心中的天Embedded-A&D ☆星夜☆/yl 木头┳一人HELLODSP08-04-25DSP交流网联系方式:Email:hellodsp@QQ:778086555TMS320DM642中文手册第1章TMS320DM642 视频/图像定点数字信号处理器 (5)1.1特点(由亮亮翻译) (5)1.2概述(由亮亮翻译) (7)1.3原理框图(由亮亮翻译) (9)第2章器件纵览 (10)2.1器件特性(由亮亮翻译) (10)2.2C P U(D S P核)概述(由K a Z E翻译) (12)2.3存储器映射总结(由虎妞翻译) (18)2.4引导模式(由M i c h a e l翻译) (21)2.5引脚分配(由碧鲨翻译) (22)2.6T M S320D M642的发展(由龙啸九天翻译) (56)第3章器件配置 (59)3.1复位时的配置(由可可橘子翻译) (59)3.2复位后的配置(由l c e p r i n c e翻译) (62)3.3外设配置锁定(由虎妞翻译) (65)3.4器件状态寄存器描述(由田羽翻译) (67)3.5复用引脚配置(由S t e w a r d翻译) (69)3.6调试需要考虑的事项(由S h a y n e w a r d翻译) (71)3.7配置例子(由亮亮翻译) (72)第4章TMS320DM642运行状况 (75)4.1设备运行温度最大的额定值范围(由张焱翔翻译) (75)4.2推荐运行条件(由张焱翔翻译) (76)4.3超过推荐范围的电源电压和设备运行温度的电气特性(除非另有注明外)(由张焱翔翻译) (77)第5章DM642外设信息和电气特性 (79)5.1参数信息(由G a o f e n g_Q^_^翻译) (79)5.2推荐的时钟和控制信号转变行为(由K a Z E翻译) (82)5.3电源(由K a Z E翻译) (82)5.4增强的直接存取器访问(E D M A)控制器(由风来的西林/$翻译) (87)5.5中断(由J H翻译) (92)5.6复位(由J H翻译) (95)5.7时钟倍频P L L(由J H翻译) (100)5.8外部存取接口(E M I F)(由J H翻译) (106)5.9多声道音频串行端口( M c A S P0)外围设备(由D S P-F2812翻译) (121)5.10内部集成电路(I2C)(由方块糖翻译) (130)5.11主机接口(H P I)(由S t e w a r d翻译) (135)5.12外围部件互连标准(由流星~梦落翻译) (141)5.13多通道缓冲串口(M c B S P)(由亮亮翻译) (145)5.14视频端口(由另类爷们翻译) (156)5.15V I C(由K e l l y翻译) (164)5.16以太网媒体存取控制器 (E M A C)(由心中的天翻译) (166)5.17数据输入/输出管理(M D I O)(由l c e p r i n c e翻译) (174)5.18定时器(由E m b e d d e d-A&D翻译) (177)5.19通用输入/输出( G P I O)(由E m b e d d e d-A&D翻译) (179)5.20J T A G(由☆星夜☆/y l翻译) (182)第6章机械参数 (185)6.1热敏参数(由木头┳一人翻译) (185)6.2封装信息(由木头┳一人翻译) (187)第1章TMS320DM642 视频/图像定点数字信号处理器1.1特点l高性能数字媒体处理器-2-,1.67-,1.39-ns 指令周期-500-,600-,720-MHz时钟频率-每周期执行8条32位指令-与C64x完全兼容n V elociT1.2是具有先进超长指令字(VLIW)TMS320C64x DSP核V elociT的升级版-8个独立的功能单元n6个ALU(32/40bit),每个功能单元支持每时钟周期32位算术操作,双16位比特算术操作,或4个8位算术操作n2个乘法器支持每时钟周期4个16×16位的乘法(结果是32位)或者8个8×8位乘法(结果是16位)-具有无需阵列支持的负载存储结构(1)-64/32位通用寄存器-指令打包技术,减少代码容量l指令设置特点-字节寻址(8/16/32/64位数据)-8位溢出保护-可位提取,设置,清除操作-标准化,饱和度(1),位计数-增强交互的V elociT1.2l L1/L2存储器结构-128Kbit(16Kbyte)L1P程序缓存(直接映射)-128Kbit(16Kbyte)L1D数据缓存(2路结合设置)-2Mbit(256Kbyte)L2标准映射RAM/缓存(灵活的RAM/缓存分配)l小端模式,大端模式l64位外部存储器接口(EMIF)-支持异步存储器(SRAM和EPROM)和同步存储器(SDRAM,SBSRAM,ZBT SRAM 和FIFO)直接接口-总共1024Mbyte可寻址外部存储空间l增强的直接存储器访问(EDMA)控制器(64个独立的通道)l10/100Mb/s以太网控制器(EMAC)-适应IEEE802.3-媒体独立接口(MII)-8个独立的发送通道和1个接收通道l管理数据输入输出(MDIO)l3个可配置视频接口-给公共的视频编码解码器件提供一个直接I/F接口-支持多种协议/视频标准l内插VCXO控制接口-支持同步音频/视频l主机接口(HPI)[32/16位]l符合PCI接口规范2.2版本,32位/66MHz,3.3V PCI主/从接口l多通道音频串行接口(McASP)-8个串行数据引脚-多种I2S和相似的比特流格式-完整的数字音频I/F发送器,支持P/DIF, IEC60958-1, AES-3, CP-430格式l I2C总线l2个多通道缓存串行接口l3个32位通用定时器l16个通用输入输出(GPIO)引脚l灵活的PLL时钟发生器l支持IEEE-1149.1(JTAG)边界扫描接口l548引脚球栅阵列(BGA)封装(GDK和ZDK为后缀),0.8mm Ball Picth(1) l548引脚球栅阵列(BGA)封装(GNK和ZNK为后缀),1.0mm Ball Picth(1) l0.13μm/6等级CMOS工艺l I/O采用3.3V供电,内核采用1.2V供电(-500)l I/O采用3.3V供电,内核采用1.4V供电(A-500,A-600,-600,-720)注:红色标示的是翻译不确定的地方1.2概述TMS320C64x DSP芯片(包括TMS320DM642)是在TMS320C6000 DSP平台上的高性能定点DSP。

MEMORY存储芯片TMS320DM642AGNZ中文规格书

52TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Device Overview Copyright ©2008–2014,Texas Instruments IncorporatedTable 3-25.General Purpose Input Output Terminal Functions (continued)SIGNAL NAME PIN NOTYPE (1)PULL (2)MUXED DESCRIPTION PTPZKB (3)GP7[14]is initially configured as a reserved function after reset and will not be in a predictable state.This signal will only be stable afterthe GPIO configuration for this pin has been ers should carefully consider the system implications of this pin being in an unknown state after reset.GP6EMB_D[15]/GP6[15]74F13I/O IPD EMIFB GPIO Bank 6EMB_D[14]/GP6[14]76E`6I/O IPD EMB_D[13]/GP6[13]78E13I/O IPD EMB_D[12]/GP6[12]79D16I/O IPD EMB_D[11]/GP6[11]80D15I/O IPD EMB_D[10]/GP6[10]82D14I/O IPD EMB_D[9]/GP6[9]83D13I/O IPD EMB_D[8]/GP6[8]84C16I/O IPD EMB_D[7]/GP6[7]62J16I/O IPD EMB_D[6]/GP6[6]63J15I/O IPD EMB_D[5]/GP6[5]64J13I/O IPD EMB_D[4]/GP6[4]66H16I/O IPD EMB_D[3]/GP6[3]68H13I/O IPD EMB_D[2]/GP6[2]70G16I/O IPD EMB_D[1]/GP6[1]72G13I/O IPD EMB_D[0]/GP6[0]73F16I/O IPD GP7EMU[0]/GP7[15]-J5I/O IPU JTAG RTCK/GP7[14](3)157K1I/O IPD General-Purpose IO signal EMB_A[11]/GP7[13]91B12O IPD EMIFB GPIO Bank 7EMB_A[10]/GP7[12]105A9O IPD EMB_A[9]/GP7[11]92C12O IPD EMB_A[8]/GP7[10]94D12O IPD EMB_A[7]/GP7[9]95A11O IPD EMB_A[6]/GP7[8]96B11O IPD EMB_A[5]/GP7[7]97C11O IPD EMB_A[4]/GP7[6]98D11O IPD EMB_A[3]/GP7[5]100A10O IPD EMB_A[2]/GP7[4]101B10O IPD EMB_A[1]/GP7[3]102C10O IPD EMB_A[0]/GP7[2]103D10O IPD EMB_BA[0]/GP7[1]107C9O IPU EMB_BA[1]/GP7[0]106B9O IPU (1)PWR =Supply voltage.3.6.21Reserved and No ConnectTable 3-26.Reserved and No Connect Terminal FunctionsSIGNAL NAMEPIN NO TYPE (1)DESCRIPTION PTP ZKB RSV1-F7-Reserved.(Leave unconnected,do not connect to power orground.)59TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Device Configuration Copyright ©2008–2014,Texas Instruments Incorporated 4.3Pullup/Pulldown ResistorsProper board design should ensure that input pins to the device always be at a valid logic level and not floating.This may be achieved via pullup/pulldown resistors.The device features internal pullup (IPU)and internal pulldown (IPD)resistors on most pins to eliminate the need,unless otherwise noted,for external pullup/pulldown resistors.An external pullup/pulldown resistor needs to be used in the following situations:•Boot and Configuration Pins:If the pin is both routed out and 3-stated (not driven),an external pullup/pulldown resistor is strongly recommended,even if the IPU/IPD matches the desired value/state.•Other Input Pins:If the IPU/IPD does not match the desired value/state,use an external pullup/pulldown resistor to pull the signal to the opposite rail.For the boot and configuration pins,if they are both routed out and 3-stated (not driven),it is strongly recommended that an external pullup/pulldown resistor be implemented.Although,internal pullup/pulldown resistors exist on these pins and they may match the desired configuration value,providing external connectivity can help ensure that valid logic levels are latched on these device boot and configuration pins.In addition,applying external pullup/pulldown resistors on the boot and configuration pins adds convenience to the user in debugging and flexibility in switching operating modes.Tips for choosing an external pullup/pulldown resistor:•Consider the total amount of current that may pass through the pullup or pulldown resistor.Make sure to include the leakage currents of all the devices connected to the net,as well as any internal pullup or pulldown resistors.•Decide a target value for the net.For a pulldown resistor,this should be below the lowest V IL level of all inputs connected to the net.For a pullup resistor,this should be above the highest V IH level of all inputs on the net.A reasonable choice would be to target the V OL or V OH levels for the logic family of the limiting device;which,by definition,have margin to the V IL and V IH levels.•Select a pullup/pulldown resistor with the largest possible value;but,which can still ensure that the net will reach the target pulled value when maximum current from all devices on the net is flowing through the resistor.The current to be considered includes leakage current plus,any other internal and external pullup/pulldown resistors on the net.•For bidirectional nets,there is an additional consideration which sets a lower limit on the resistance value of the external resistor.Verify that the resistance is small enough that the weakest output buffer can drive the net to the opposite logic level (including margin).•Remember to include tolerances when selecting the resistor value.•For pullup resistors,also remember to include tolerances on the IO supply rail.•For most systems,a 1-k Ωresistor can be used to oppose the IPU/IPD while meeting the above ers should confirm this resistor value is correct for their specific application.•For most systems,a 20-k Ωresistor can be used to compliment the IPU/IPD on the boot and configuration pins while meeting the above ers should confirm this resistor value is correct for their specific application.•For more detailed information on input current (I I ),and the low-/high-level input voltages (V IL and V IH )for the device,see Section 5.3,Recommended Operating Conditions.•For the internal pullup/pulldown resistors for all device pins,see the peripheral/system-specific terminal functions table.。

MEMORY存储芯片TMS320DM640AZNZ4中文规格书

214TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Device and Documentation Support Copyright ©2008–2014,Texas Instruments Incorporated7Device and Documentation Support7.1Device Support 7.1.1Development SupportTI offers an extensive line of development tools for the TMS320C6745/47platform,including tools to evaluate the performance of the processors,generate code,develop algorithm implementations,and fully integrate and debug software and hardware modules.The tool's support documentation is electronically available within the Code Composer Studio™Integrated Development Environment (IDE).The following products support development of TMS320C6745/47applications:Software Development Tools:Code Composer Studio™Integrated Development Environment (IDE):including EditorC/C++/Assembly Code Generation,and Debug plus additional development toolsScalable,Real-Time Foundation Software (DSP/BIOS™),which provides the basic run-time target software needed to support any application.Hardware Development Tools:Extended Development System (XDS™)EmulatorFor a complete listing of development-support tools for TMS320C6745/47,visit the Texas Instruments web site on the Worldwide Web at uniform resource locator (URL).For information on pricing and availability,contact the nearest TI field sales office or authorized distributor.7.1.2Device and Development-Support Tool NomenclatureTo designate the stages in the product development cycle,TI assigns prefixes to the part numbers of all DSP devices and support tools.Each DSP commercial family member has one of three prefixes:TMX,TMP,or TMS (e.g.,TMS320C6745).Texas Instruments recommends two of three possible prefix designators for its support tools:TMDX and TMDS.These prefixes represent evolutionary stages of product development from engineering prototypes (TMX/TMDX)through fully qualified production devices/tools (TMS/TMDS).Device development evolutionary flow:TMXExperimental device that is not necessarily representative of the final device's electrical specifications.TMPFinal silicon die that conforms to the device's electrical specifications but has not completed quality and reliability verification.TMS Fully-qualified production device.Support tool development evolutionary flow:TMDXDevelopment-support product that has not yet completed Texas Instruments internal qualification testing.TMDS Fully qualified development-support product.TMX and TMP devices and TMDX development-support tools are shipped against the following disclaimer:"Developmental product is intended for internal evaluation purposes."TMS devices and TMDS development-support tools have been characterized fully,and the quality and reliability of the device have been demonstrated fully.TI's standard warranty applies.216TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Device and Documentation Support Copyright ©2008–2014,Texas Instruments Incorporatedand describes how the two-level cache-based internal memory architecture in the TMS320C674x digital signal processor (DSP)can be efficiently used in DSP applications.Shows how to maintain coherence with external memory,how to use DMA to reduce memory latencies,and how to optimize your code to improve cache efficiency.The internal memory architecture in the C674x DSP is organized in a two-level hierarchy consisting of a dedicated program cache (L1P)and a dedicated data cache (L1D)on the first level.Accesses by the CPU to the these first level caches can complete without CPU pipeline stalls.If the data requested by the CPU is not contained in cache,it is fetched from the next lower memory level,L2or external memory.7.3Support ResourcesTI E2E™support forums are an engineer's go-to source for fast,verified answers and design help —straight from the experts.Search existing answers or ask your own question to get the quick design help you need.Linked content is provided "AS IS"by the respective contributors.They do not constitute TI specifications and do not necessarily reflect TI's views;see TI's Terms of Use .7.4Related LinksThe table below lists quick access links.Categories include technical documents,support and community resources,tools and software,and quick access to sample or buy.Table 7-1.Related LinksPARTS PRODUCT FOLDERSAMPLE &BUY TECHNICAL DOCUMENTS TOOLS &SOFTWARE SUPPORT &COMMUNITY TMS320C6745Click hereClick here Click here Click here Click here TMS320C6747Click here Click here Click here Click here Click here 7.5TrademarksDSP/BIOS,PowerPAD,TMS320C6000,C6000,TI E2E are trademarks of Texas Instruments.All other trademarks are the property of their respective owners.7.6Electrostatic Discharge CautionThis integrated circuit can be damaged by ESD.Texas Instruments recommends that all integrated circuits be handled with appropriate precautions.Failure to observe proper handling and installation procedures can cause damage.ESD damage can range from subtle performance degradation to complete device failure.Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.7.7GlossaryTI Glossary This glossary lists and explains terms,acronyms,and definitions.。

MEMORY存储芯片TMS320DM642AZNZ720中文规格书

I2Cx_SCL I2Cx_SDA 177TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Peripheral Information and Electrical SpecificationsCopyright ©2008–2014,Texas Instruments Incorporated 6.23Inter-Integrated Circuit Serial Ports (I2C0,I2C1)6.23.1I2C Device-Specific InformationHaving two I2C modules on the C6745/6747simplifies system architecture,since one module may be used by the DSP to control local peripherals ICs (DACs,ADCs,etc.)while the other may be used to communicate with other controllers in a system or to implement a user interface.Figure 6-62is block diagram of the C6745/6747I2C Module.Each I2C port supports:•Compatible with Philips®I2C Specification Revision 2.1(January 2000)•Fast Mode up to 400Kbps (no fail-safe I/O buffers)•Noise Filter to Remove Noise 50ns or less•Seven-and Ten-Bit Device Addressing Modes•Master (Transmit/Receive)and Slave (Transmit/Receive)Functionality•Events:DMA,Interrupt,or Polling•General-Purpose I/O Capability if not used as I2CFigure 6-62.I2C Module Block Diagram184TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Peripheral Information and Electrical Specifications Copyright ©2008–2014,Texas Instruments Incorporated(1)Restrictions apply to the physical addresses used in these registers.(2)Connected to the integrated USB1.1phy pins (USB1_DM,USB1_DP).(3)Although the controller implements two ports,the second port cannot be used.6.25USB1Host Controller Registers (USB1.1OHCI)All the device USB interfaces are compliant with Universal Serial Bus Specification,Revision 1.1.Table 6-94is the list of USB Host Controller registers.Table B1Host Controller RegistersBYTE ADDRESSACRONYM REGISTER DESCRIPTION 0x01E25000HCREVISION OHCI Revision Number Register 0x01E25004HCCONTROL HC Operating Mode Register 0x01E25008HCCOMMANDSTATUS HC Command and Status Register 0x01E2500CHCINTERRUPTSTATUS HC Interrupt and Status Register 0x01E25010HCINTERRUPTENABLE HC Interrupt Enable Register 0x01E25014HCINTERRUPTDISABLE HC Interrupt Disable Register 0x01E25018HCHCCA HC HCAA Address Register (1)0x01E2501CHCPERIODCURRENTED HC Current Periodic Register (1)0x01E25020HCCONTROLHEADED HC Head Control Register (1)0x01E25024HCCONTROLCURRENTED HC Current Control Register (1)0x01E25028HCBULKHEADED HC Head Bulk Register (1)0x01E2502CHCBULKCURRENTED HC Current Bulk Register (1)0x01E25030HCDONEHEAD HC Head Done Register (1)0x01E25034HCFMINTERVAL HC Frame Interval Register 0x01E25038HCFMREMAINING HC Frame Remaining Register 0x01E2503CHCFMNUMBER HC Frame Number Register 0x01E25040HCPERIODICSTART HC Periodic Start Register 0x01E25044HCLSTHRESHOLD HC Low-Speed Threshold Register 0x01E25048HCRHDESCRIPTORA HC Root Hub A Register 0x01E2504CHCRHDESCRIPTORB HC Root Hub B Register 0x01E25050HCRHSTATUS HC Root Hub Status Register 0x01E25054HCRHPORTSTATUS1HC Port 1Status and Control Register (2)0x01E25058HCRHPORTSTATUS2HC Port 2Status and Control Register (3)(1)Low Speed:C L =200pF.High Speed:C L =50pF (2)t RFM =(t r /t f )x 100(3)t jr =t px(1)-t px(0)(4)f op =1/t perTable 6-95.Switching Characteristics Over Recommended Operating Conditions for USB1No.PARAMETER LOW SPEED FULL SPEED UNIT MIN MAX MIN MAX U1t r Rise time,USB1_DP and USB1_DM signals (1)75(1)300(1)4(1)20(1)ns U2t f Fall time,USB1_DP and USB1_DM signals (1)75(1)300(1)4(1)20(1)ns U3t RFM Rise/Fall time matching (2)80(2)120(2)90(2)110(2)%U4V CRS Output signal cross-over voltage (1) 1.3(1)2(1) 1.3(1)2(1)V U5t j Differential propagation jitter (3)-25(3)25(3)-2(3)2(3)ns U6f op Operating frequency (4) 1.512MHz 6.25.1USB1Unused Signal ConfigurationIf USB1is unused,then the USB1signals should be configured as shown in Section 3.6.23.。

MEMORY存储芯片TMS320DM6443ZWT中文规格书

8TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Device Overview Copyright ©2008–2014,Texas Instruments Incorporated3Device Overview3.1Device CharacteristicsTable 3-1provides an overview of the C6745/6747low power digital signal processor.The table shows significant features of the device,including the capacity of on-chip RAM,peripherals,and the package type with pin count.Table 3-1.Characteristics of the C6745/C6747ProcessorHARDWARE FEATURESC6745C6747PeripheralsNot all peripherals pinsare available at the same time (for moredetail,see the Device Configurations section).EMIFB16bit,up to 128MB SDRAM 16/32bit,up to 256MB SDRAM EMIFAAsynchronous (8-bit bus width)RAM,Flash,NOR,NAND Asynchronous (8/16-bit bus width)RAM,Flash,16bit up to 128MB SDRAM,NOR,NAND Flash Card InterfaceMMC and SD cards supported.EDMA332independent channels,8QDMA channels,2Transfer controllers Timers264-Bit General Purpose (each configurable as 2separate 32-bit timers,1configurable as Watch Dog)UART3(one with RTS and CTS flow control)SPI2(each with one hardware chip select)I 2C2(both Master/Slave)Multichannel AudioSerial Port [McASP]2(each with transmit/receive,FIFO buffer,16/9serializers)3(each with transmit/receive,FIFO buffer,16/9serializers)10/100Ethernet MAC with Management Data I/O 1(RMII Interface)eHRPWM 6Single Edge,6Dual Edge Symmetric,or 3Dual Edge Asymmetric Outputs eCAP 332-bit capture inputs or 332-bit auxiliary PWM outputs eQEP232-bit QEP channels with 4inputs/channel UHPI-1(16-bit multiplexed address/data)USB 2.0(USB0)Full Speed Host Or Device with On-Chip PHY High-Speed OTG Controller with on-chip OTG PHY USB 1.1(USB1)-Full-Speed OHCI (as host)with on-chip PHY General-PurposeInput/Output Port8banks of 16-bit LCD Controller-1RTC-1(32KHz oscillator and seperate power trail.Provides time and date tracking and alarm capability.)PRU Subsystem(PRUSS)2Programmable PRU Cores On-Chip Memory Size (Bytes)320KB RAM 448KB RAMOrganization DSP 32KB L1Program (L1P)/Cache (up to 32KB)32KB L1Data (L1D)/Cache (up to 32KB)256KB Unified Mapped RAM/Cache (L2)DSP Memories can be made accessible to EDMA3,and other peripherals.-ADDITIONAL MEMORY128KB RAMC674x CPU ID +CPU Rev ID Control Status Register (CSR.[31:16])0x1400C674x MegamoduleRevision Revision ID Register (MM_REVID[15:0])0x000011TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Device Overview Copyright ©2008–2014,Texas Instruments Incorporated 3.3.1C674x DSP CPU DescriptionThe C674x Central Processing Unit (CPU)consists of eight functional units,two register files,and two data paths as shown in Figure 3-2.The two general-purpose register files (A and B)each contain 3232-bit registers for a total of 64registers.The general-purpose registers can be used for data or can be data address pointers.The data types supported include packed 8-bit data,packed 16-bit data,32-bit data,40-bit data,and 64-bit data.Values larger than 32bits,such as 40-bit-long or 64-bit-long values are stored in register pairs,with the 32LSBs of data placed in an even register and the remaining 8or 32MSBs in the next upper register (which is always an odd-numbered register).The eight functional units (.M1,.L1,.D1,.S1,.M2,.L2,.D2,and .S2)are each capable of executing one instruction every clock cycle.The .M functional units perform all multiply operations.The .S and .L units perform a general set of arithmetic,logical,and branch functions.The .D units primarily load data from memory to the register file and store results from the register file into memory.The C674x CPU combines the performance of the C64x+core with the floating-point capabilities of the C67x+core.Each C674x .M unit can perform one of the following each clock cycle:one 32x 32bit multiply,one 16x 32bit multiply,two 16x 16bit multiplies,two 16x 32bit multiplies,two 16x 16bit multiplies with add/subtract capabilities,four 8x 8bit multiplies,four 8x 8bit multiplies with add operations,and four 16x 16multiplies with add/subtract capabilities (including a complex multiply).There is also support for Galois field multiplication for 8-bit and 32-bit data.Many communications algorithms such as FFTs and modems require complex multiplication.The complex multiply (CMPY)instruction takes four 16-bit inputs and produces a 32-bit real and a 32-bit imaginary output.There are also complex multiplies with rounding capability that produces one 32-bit packed output that contain 16-bit real and 16-bit imaginary values.The 32x 32bit multiply instructions provide the extended precision necessary for high-precision algorithms on a variety of signed and unsigned 32-bit data types.The .L Unit (or Arithmetic Logic Unit)now incorporates the ability to do parallel add/subtract operations on a pair of common inputs.Versions of this instruction exist to work on 32-bit data or on pairs of 16-bit data performing dual 16-bit add and subtracts in parallel.There are also saturated forms of these instructions.The C674x core enhances the .S unit in several ways.On the previous cores,dual 16-bit MIN2and MAX2comparisons were only available on the .L units.On the C674x core they are also available on the .S unit which increases the performance of algorithms that do searching and sorting.Finally,to increase data packing and unpacking throughput,the .S unit allows sustained high performance for the quad 8-bit/16-bit and dual 16-bit instructions.Unpack instructions prepare 8-bit data for parallel 16-bit operations.Pack instructions return parallel results to output precision including saturation support.Other new features include:•SPLOOP -A small instruction buffer in the CPU that aids in creation of software pipelining loops where multiple iterations of a loop are executed in parallel.The SPLOOP buffer reduces the code size associated with software pipelining.Furthermore,loops in the SPLOOP buffer are fully interruptible.•Compact Instructions -The native instruction size for the C6000™devices is 32bits.Many common instructions such as MPY,AND,OR,ADD,and SUB can be expressed as 16bits if the C674x compiler can restrict the code to use certain registers in the register file.This compression is performed by the code generation tools.•Instruction Set Enhancement -As noted above,there are new instructions such as 32-bit multiplications,complex multiplications,packing,sorting,bit manipulation,and 32-bit Galois field multiplication.•Exceptions Handling -Intended to aid the programmer in isolating bugs.The C674x CPU is able to detect and respond to exceptions,both from internally detected sources (such as illegal op-codes)and from system events (such as a watchdog time expiration).•Privilege -Defines user and supervisor modes of operation,allowing the operating system to give a basic level of protection to sensitive resources.Local memory is divided into multiple pages,each with read,write,and execute permissions.。

MEMORY存储芯片TMS320DM6446ZWT中文规格书

V ref = V IL MAX (or V OL MAX)V ref = V IH MIN (or V OH MIN)V refOutput Under Test Device Pin (see note)64TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Peripheral Information and Electrical Specifications Copyright ©2008–2014,Texas Instruments Incorporated6Peripheral Information and Electrical Specifications6.1Parameter Information 6.1.1Parameter Information Device-Specific InformationA.The data sheet provides timing at the device pin.For output timing analysis,the tester pin electronics and itstransmission line effects must be taken into account.A transmission line with a delay of 2ns or longer can be used toproduce the desired transmission line effect.The transmission line is intended as a load only.It is not necessary toadd or subtract the transmission line delay (2ns or longer)from the data sheet timings.Input requirements in this data sheet are tested with an input slew rate of <4Volts per nanosecond (4V/ns)at thedevice pin and the input signals are driven between 0V and the appropriate IO supply rail for the signal.Figure 6-1.Test Load Circuit for AC Timing MeasurementsThe load capacitance value stated is only for characterization and measurement of AC timing signals.This load capacitance value does not indicate the maximum load the device is capable of driving.6.1.1.1Signal Transition LevelsAll input and output timing parameters are referenced to V ref for both "0"and "1"logic levels.For 3.3V I/O,V ref =1.65V.For 1.8V I/O,V ref =0.9V.For 1.2V I/O,V ref =0.6V.Figure 6-2.Input and Output Voltage Reference Levels for AC Timing MeasurementsAll rise and fall transition timing parameters are referenced to V IL MAX and V IH MIN for input clocks,V OL MAX and V OH MIN for output clocks.Figure 6-3.Rise and Fall Transition Time Voltage Reference LevelsOSCIN RESET RESETOUTBoot PinsTRST67TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747Peripheral Information and Electrical SpecificationsCopyright ©2008–2014,Texas Instruments Incorporated (1)RESETOUT is multiplexed with other pin functions.See the Terminal Functions table,Table 3-6for details.(2)For power-on reset (POR),the reset timings in this table refer to RESET and TRST together.For warm reset,the reset timings in this table refer to RESET only (TRST is held high).(3)OSCIN cycles.•The RTC peripheral is not reset during a warm reset.A software sequence is required to reset the RTC.6.4.3Reset Electrical Data TimingsTable 6-1assumes testing over the recommended operating conditions.Table 6-1.Reset Timing Requirements (1)(2)No.MIN MAX UNIT 1t w(RSTL)Pulse width,RESET/TRST low 100ns 2t su(BPV-RSTH)Setup time,boot pins valid before RESET/TRST high 20ns 3t h(RSTH-BPV)Hold time,boot pins valid after RESET/TRST high 20ns 4t d(RSTH-RESETOUTH)RESET high to RESETOUT high;Warm reset 4096cycles (3)RESET high to RESETOUT high;Power-on Reset 6192Figure 6-4.Power-On Reset (RESET and TRST active)Timing。

MEMORY存储芯片TMS320DM6437ZWT4中文规格书

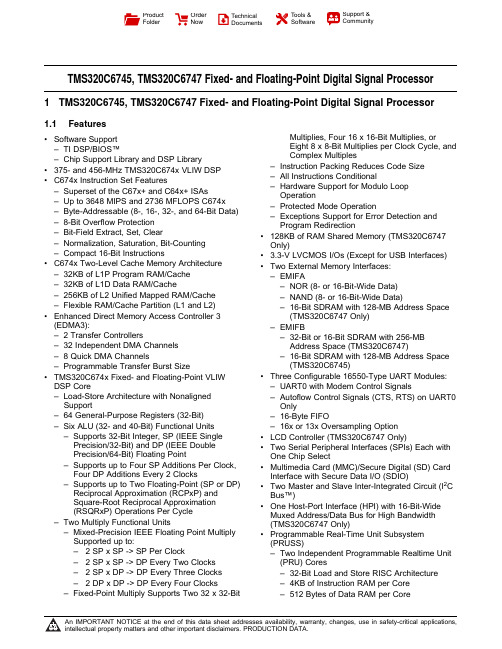

ProductFolder OrderNowTechnicalDocumentsTools &SoftwareSupport &CommunityTMS320C6745,TMS320C6747Fixed-and Floating-Point Digital Signal Processor 1TMS320C6745,TMS320C6747Fixed-and Floating-Point Digital Signal Processor 1.1Features•Software Support–TI DSP/BIOS™–Chip Support Library and DSP Library•375-and456-MHz TMS320C674x VLIW DSP•C674x Instruction Set Features–Superset of the C67x+and C64x+ISAs–Up to3648MIPS and2736MFLOPS C674x–Byte-Addressable(8-,16-,32-,and64-Bit Data)–8-Bit Overflow Protection–Bit-Field Extract,Set,Clear–Normalization,Saturation,Bit-Counting–Compact16-Bit Instructions•C674x Two-Level Cache Memory Architecture –32KB of L1P Program RAM/Cache–32KB of L1D Data RAM/Cache–256KB of L2Unified Mapped RAM/Cache–Flexible RAM/Cache Partition(L1and L2)•Enhanced Direct Memory Access Controller3 (EDMA3):–2Transfer Controllers–32Independent DMA Channels–8Quick DMA Channels–Programmable Transfer Burst Size•TMS320C674x Fixed-and Floating-Point VLIW DSP Core–Load-Store Architecture with Nonaligned Support–64General-Purpose Registers(32-Bit)–Six ALU(32-and40-Bit)Functional Units –Supports32-Bit Integer,SP(IEEE Single Precision/32-Bit)and DP(IEEE DoublePrecision/64-Bit)Floating Point–Supports up to Four SP Additions Per Clock, Four DP Additions Every2Clocks–Supports up to Two Floating-Point(SP or DP) Reciprocal Approximation(RCPxP)andSquare-Root Reciprocal Approximation(RSQRxP)Operations Per Cycle–Two Multiply Functional Units–Mixed-Precision IEEE Floating Point Multiply Supported up to:–2SP x SP->SP Per Clock–2SP x SP->DP Every Two Clocks–2SP x DP->DP Every Three Clocks–2DP x DP->DP Every Four Clocks –Fixed-Point Multiply Supports Two32x32-BitMultiplies,Four16x16-Bit Multiplies,orEight8x8-Bit Multiplies per Clock Cycle,andComplex Multiples–Instruction Packing Reduces Code Size–All Instructions Conditional–Hardware Support for Modulo LoopOperation–Protected Mode Operation–Exceptions Support for Error Detection and Program Redirection•128KB of RAM Shared Memory(TMS320C6747 Only)• 3.3-V LVCMOS I/Os(Except for USB Interfaces)•Two External Memory Interfaces:–EMIFA–NOR(8-or16-Bit-Wide Data)–NAND(8-or16-Bit-Wide Data)–16-Bit SDRAM with128-MB Address Space (TMS320C6747Only)–EMIFB–32-Bit or16-Bit SDRAM with256-MBAddress Space(TMS320C6747)–16-Bit SDRAM with128-MB Address Space (TMS320C6745)•Three Configurable16550-Type UART Modules:–UART0with Modem Control Signals–Autoflow Control Signals(CTS,RTS)on UART0 Only–16-Byte FIFO–16x or13x Oversampling Option•LCD Controller(TMS320C6747Only)•Two Serial Peripheral Interfaces(SPIs)Each with One Chip Select•Multimedia Card(MMC)/Secure Digital(SD)Card Interface with Secure Data I/O(SDIO)•Two Master and Slave Inter-Integrated Circuit(I2C Bus™)•One Host-Port Interface(HPI)with16-Bit-Wide Muxed Address/Data Bus for High Bandwidth(TMS320C6747Only)•Programmable Real-Time Unit Subsystem (PRUSS)–Two Independent Programmable Realtime Unit (PRU)Cores–32-Bit Load and Store RISC Architecture–4KB of Instruction RAM per Core–512Bytes of Data RAM per Core3TMS320C6745,TMS320C6747SPRS377F –SEPTEMBER 2008–REVISED JUNE 2014Submit Documentation FeedbackProduct Folder Links:TMS320C6745TMS320C6747TMS320C6745,TMS320C6747Fixed-and Floating-Point Digital Signal Processor Copyright ©2008–2014,Texas Instruments Incorporated The peripheral set includes:a 10/100Mbps Ethernet MAC (EMAC)with a management data input/output (MDIO)module;two I 2C Bus interfaces;3multichannel audio serial ports (McASPs)with 16/9serializers and FIFO buffers;two 64-bit general-purpose timers each configurable (one configurable as watchdog);a configurable 16-bit host-port interface (HPI)[TMS320C6747only];up to 8banks of 16pins of general-purpose input/output (GPIO)with programmable interrupt/event generation modes,multiplexed with other peripherals;3UART interfaces (one with both RTS and CTS);three enhanced high-resolution pulse width modulator (eHRPWM)peripherals;three 32-bit enhanced capture (eCAP)module peripherals which can be configured as 3capture inputs or 3auxiliary pulse width modulator (APWM)outputs;two 32-bit enhanced quadrature encoded pulse (eQEP)peripherals;and 2external memory interfaces:an asynchronous and SDRAM external memory interface (EMIFA)for slower memories or peripherals,and a higher speed memory interface (EMIFB)for SDRAM.The Ethernet Media Access Controller (EMAC)provides an efficient interface between the TMS320C6745/6747device and the network.The EMAC supports both 10Base-T and 100Base-TX,or 10Mbps and 100Mbps in either half-or full-duplex mode.Additionally,an MDIO interface is available for PHY configuration.The rich peripheral set provides the ability to control external peripheral devices and communicate with external processors.For details on each of the peripherals,see the related sections later in this document and the associated peripheral reference guides.(1)For more information on these devices,see Section 8,Mechanical Packaging and OrderableInformation.Device Information (1)PART NUMBERPACKAGE BODY SIZE TMS320C6745HLQFP (176)24.00mm x 24.00mm TMS320C6747BGA (256)17.00mm x 17.00mm。

MEMORY存储芯片TMS320C6455BZTZ中文规格书

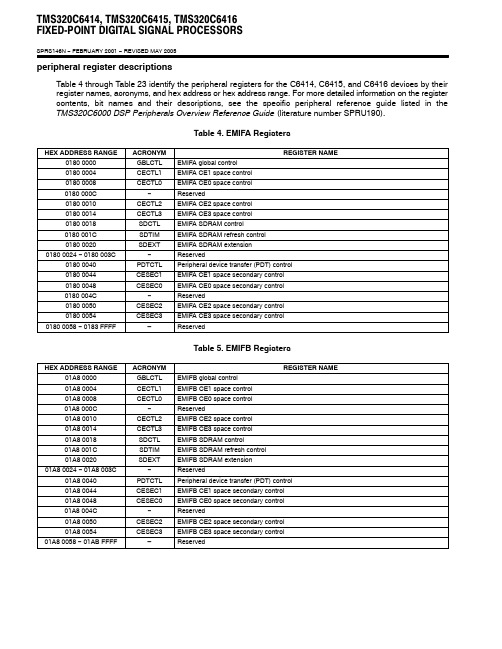

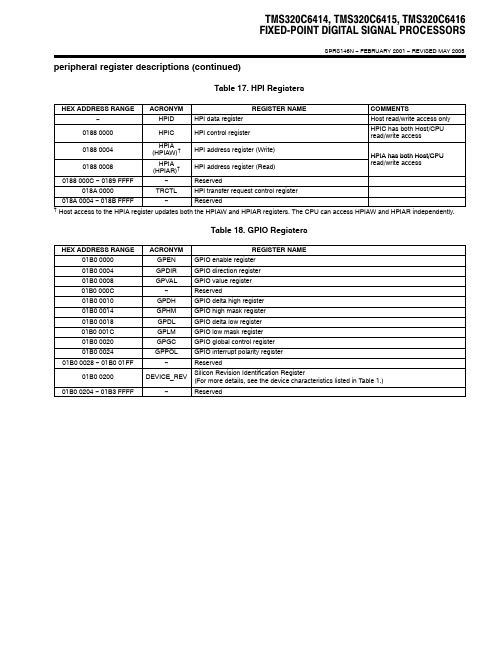

TMS320C6414, TMS320C6415, TMS320C6416FIXED-POINT DIGITAL SIGNAL PROCESSORSSPRS146N − FEBRUARY 2001 − REVISED MAY 2005peripheral register descriptionsTable 4 through Table 23 identify the peripheral registers for the C6414, C6415, and C6416 devices by their register names, acronyms, and hex address or hex address range. For more detailed information on the register contents, bit names and their descriptions, see the specific peripheral reference guide listed in the TMS320C6000 DSP Peripherals Overview Reference Guide (literature number SPRU190).Table 4. EMIFA RegistersHEX ADDRESS RANGE ACRONYM REGISTER NAME0180 0000GBLCTL EMIFA global control0180 0004CECTL1EMIFA CE1 space control0180 0008CECTL0EMIFA CE0 space control0180 000C−Reserved0180 0010CECTL2EMIFA CE2 space control0180 0014CECTL3EMIFA CE3 space control0180 0018SDCTL EMIFA SDRAM control0180 001C SDTIM EMIFA SDRAM refresh control0180 0020SDEXT EMIFA SDRAM extension0180 0024 − 0180 003C−Reserved0180 0040PDTCTL Peripheral device transfer (PDT) control0180 0044CESEC1EMIFA CE1 space secondary control0180 0048CESEC0EMIFA CE0 space secondary control0180 004C−Reserved0180 0050CESEC2EMIFA CE2 space secondary control0180 0054CESEC3EMIFA CE3 space secondary control0180 0058 − 0183 FFFF–ReservedTable 5. EMIFB RegistersHEX ADDRESS RANGE ACRONYM REGISTER NAME01A8 0000GBLCTL EMIFB global control01A8 0004CECTL1EMIFB CE1 space control01A8 0008CECTL0EMIFB CE0 space control01A8 000C−Reserved01A8 0010CECTL2EMIFB CE2 space control01A8 0014CECTL3EMIFB CE3 space control01A8 0018SDCTL EMIFB SDRAM control01A8 001C SDTIM EMIFB SDRAM refresh control01A8 0020SDEXT EMIFB SDRAM extension01A8 0024 − 01A8 003C−Reserved01A8 0040PDTCTL Peripheral device transfer (PDT) control01A8 0044CESEC1EMIFB CE1 space secondary control01A8 0048CESEC0EMIFB CE0 space secondary control01A8 004C−Reserved01A8 0050CESEC2EMIFB CE2 space secondary control01A8 0054CESEC3EMIFB CE3 space secondary control01A8 0058 − 01AB FFFF–ReservedTMS320C6414, TMS320C6415, TMS320C6416FIXED-POINT DIGITAL SIGNAL PROCESSORSSPRS146N − FEBRUARY 2001 − REVISED MAY 2005 peripheral register descriptions (continued)Table 6. L2 Cache RegistersHEX ADDRESS RANGE ACRONYM REGISTER NAME COMMENTS 0184 0000CCFG Cache configuration register0184 0004 − 0184 0FFC−Reserved0184 1000EDMAWEIGHT L2 EDMA access control register0184 1004 − 0184 1FFC−Reserved0184 2000L2ALLOC0L2 allocation register 00184 2004L2ALLOC1L2 allocation register 10184 2008L2ALLOC2L2 allocation register 20184 200C L2ALLOC3L2 allocation register 30184 2010 − 0184 3FFC−Reserved0184 4000L2WBAR L2 writeback base address register0184 4004L2WWC L2 writeback word count register0184 4010L2WIBAR L2 writeback invalidate base address register0184 4014L2WIWC L2 writeback invalidate word count register0184 4018L2IBAR L2 invalidate base address register0184 401C L2IWC L2 invalidate word count register0184 4020L1PIBAR L1P invalidate base address register0184 4024L1PIWC L1P invalidate word count register0184 4030L1DWIBAR L1D writeback invalidate base address register0184 4034L1DWIWC L1D writeback invalidate word count register0184 4038 − 0184 4044−Reserved0184 4048L1DIBAR L1D invalidate base address register0184 404C L1DIWC L1D invalidate word count register0184 4050 − 0184 4FFC−Reserved0184 5000L2WB L2 writeback all register0184 5004L2WBINV L2 writeback invalidate all register0184 5008 − 0184 7FFC−Reserved0184 8000 − 0184 817C MAR0 toMAR95Reserved0184 8180MAR96Controls EMIFB CE0 range 6000 0000 − 60FF FFFF0184 8184MAR97Controls EMIFB CE0 range 6100 0000 − 61FF FFFF0184 8188MAR98Controls EMIFB CE0 range 6200 0000 − 62FF FFFF0184 818C MAR99Controls EMIFB CE0 range 6300 0000 − 63FF FFFF0184 8190MAR100Controls EMIFB CE1 range 6400 0000 − 64FF FFFF0184 8194MAR101Controls EMIFB CE1 range 6500 0000 − 65FF FFFF0184 8198MAR102Controls EMIFB CE1 range 6600 0000 − 66FF FFFF0184 819C MAR103Controls EMIFB CE1 range 6700 0000 − 67FF FFFF0184 81A0MAR104Controls EMIFB CE2 range 6800 0000 − 68FF FFFF0184 81A4MAR105Controls EMIFB CE2 range 6900 0000 − 69FF FFFF0184 81A8MAR106Controls EMIFB CE2 range 6A00 0000 − 6AFF FFFF0184 81AC MAR107Controls EMIFB CE2 range 6B00 0000 − 6BFF FFFF。

MEMORY存储芯片TMS320C6421ZWT中文规格书

TMS320C6414, TMS320C6415, TMS320C6416FIXED-POINT DIGITAL SIGNAL PROCESSORSSPRS146N − FEBRUARY 2001 − REVISED MAY 2005I/O SupplyGNDFigure 11. Schottky Diode DiagramCore and I/O supply voltage regulators should be located close to the DSP (or DSP array) to minimize inductance and resistance in the power delivery path. Additionally, when designing for high-performance applications utilizing the C6000™ platform of DSPs, the PC board should include separate power planes for core, I/O, and ground, all bypassed with high-quality low-ESL/ESR capacitors.power-supply decouplingIn order to properly decouple the supply planes from system noise, place as many capacitors (caps) as possible close to the DSP. Assuming 0603 caps, the user should be able to fit a total of 60 caps, 30 for the core supply and 30 for the I/O supply. These caps need to be close to the DSP power pins, no more than 1.25 cm maximum distance to be effective. Physically smaller caps, such as 0402, are better because of their lower parasitic inductance. Proper capacitance values are also important. Small bypass caps (near 560 pF) should be closest to the power pins. Medium bypass caps (220 nF or as large as can be obtained in a small package) should be next closest. TI recommends no less than 8 small and 8 medium caps per supply (32 total) be placed immediately next to the BGA vias, using the “interior” BGA space and at least the corners of the “exterior”.Eight larger caps (4 for each supply) can be placed further away for bulk decoupling. Large bulk caps (on the order of 100 µF) should be furthest away (but still as close as possible). No less than 4 large caps per supply(8 total) should be placed outside of the BGA.Any cap selection needs to be evaluated from a yield/manufacturing point-of-view. As with the selection of any component, verification of capacitor availability over the product’s production lifetime should be considered.TMS320C6414, TMS320C6415, TMS320C6416FIXED-POINT DIGITAL SIGNAL PROCESSORSSPRS146N − FEBRUARY 2001 − REVISED MAY 2005IEEE 1149.1 JTAG compatibility statementThe TMS320C6414/15/16 DSP requires that both TRST and RESET be asserted upon power up to be properly initialized. While RESET initializes the DSP core, TRST initializes the DSP’s emulation logic. Both resets are required for proper operation.Note: TRST is synchronous and must be clocked by TCLK; otherwise, BSCAN may not respond as expected after TRST is asserted.While both TRST and RESET need to be asserted upon power up, only RESET needs to be released for the DSP to boot properly. TRST may be asserted indefinitely for normal operation, keeping the JTAG port interface and DSP’s emulation logic in the reset state. TRST only needs to be released when it is necessary to use a JTAG controller to debug the DSP or exercise the DSP’s boundary scan functionality. RESET must be released in order for boundary-scan JTAG to read the variant field of IDCODE correctly. Other boundary-scan instructions work correctly independent of current state of RESET.For maximum reliability, the TMS320C6414/15/16 DSP includes an internal pulldown (IPD) on the TRST pin to ensure that TRST will always be asserted upon power up and the DSP’s internal emulation logic will always be properly initialized. JTAG controllers from Texas Instruments actively drive TRST high. However, some third-party JTAG controllers may not drive TRST high but expect the use of a pullup resistor on TRST. When using this type of JTAG controller, assert TRST to intialize the DSP after powerup and externally drive TRST high before attempting any emulation or boundary scan operations.Following the release of RESET, the low-to-high transition of TRST must occur to latch the state of EMU1 and EMU0. The EMU[1:0] pins configure the device for either Boundary Scan mode or Normal/Emulation mode. For more detailed information, see the terminal functions section of this data sheet.Note: The DESIGN_WARNING section of the TMS320C6414/15/16 BSDL file contains information and constraints regarding proper device operation while in Boundary Scan Mode.EMIF device speedThe rated EMIF speed, referring to both EMIFA and EMIFB, of these devices only applies to the SDRAM interface when in a system that meets the following requirements:− 1 chip-enable (CE) space (maximum of 2 chips) of SDRAM connected to EMIF−up to 1 CE space of buffers connected to EMIF−EMIF trace lengths between 1 and 3 inches−166-MHz SDRAM for 133-MHz operation (applies only to EMIFA)−143-MHz SDRAM for 100-MHz operationOther configurations may be possible, but timing analysis must be done to verify all AC timings are met.Verification of AC timings is mandatory when using configurations other than those specified above. TI recommends utilizing I/O buffer information specification (IBIS) to analyze all AC timings.To properly use IBIS models to attain accurate timing analysis for a given system, see the Using IBIS Models for Timing Analysis application report (literature number SPRA839).To maintain signal integrity, serial termination resistors should be inserted into all EMIF output signal lines (see the Terminal Functions table for the EMIF output signals).。

MEMORY存储芯片TMS320C6455DZTZA中文规格书

TMS320C6414, TMS320C6415, TMS320C6416FIXED-POINT DIGITAL SIGNAL PROCESSORSSPRS146N − FEBRUARY 2001 − REVISED MAY 2005 peripheral register descriptions (continued)Table 17. HPI RegistersHEX ADDRESS RANGE ACRONYM REGISTER NAME COMMENTS −HPID HPI data register Host read/write access only0188 0000HPIC HPI control register HPIC has both Host/CPUread/write access0188 0004HPIA(HPIAW)†HPI address register (Write)HPIA has both Host/CPU0188 0008HPIA(HPIAR)†HPI address register (Read)read/write access 0188 000C − 0189 FFFF−Reserved018A 0000TRCTL HPI transfer request control register018A 0004 − 018B FFFF−Reserved†Host access to the HPIA register updates both the HPIAW and HPIAR registers. The CPU can access HPIAW and HPIAR independently.Table 18. GPIO RegistersHEX ADDRESS RANGE ACRONYM REGISTER NAME01B0 0000GPEN GPIO enable register01B0 0004GPDIR GPIO direction register01B0 0008GPVAL GPIO value register01B0 000C−Reserved01B0 0010GPDH GPIO delta high register01B0 0014GPHM GPIO high mask register01B0 0018GPDL GPIO delta low register01B0 001C GPLM GPIO low mask register01B0 0020GPGC GPIO global control register01B0 0024GPPOL GPIO interrupt polarity register01B0 0028 − 01B0 01FF−Reserved01B0 0200DEVICE_REV Silicon Revision Identification Register(For more details, see the device characteristics listed in Table 1.)01B0 0204 − 01B3 FFFF−ReservedTMS320C6414, TMS320C6415, TMS320C6416FIXED-POINT DIGITAL SIGNAL PROCESSORSSPRS146N − FEBRUARY 2001 − REVISED MAY 2005signal groups description TRSTGP7/EXT_INT7‡TDITDOTMSTCKEMU0EMU1NMI GP6/EXT_INT6‡GP5/EXT_INT5‡GP4/EXT_INT4‡RESET RSV RSV RSV RSV CLKINCLKMODE1CLKMODE0PLLV EMU2EMU3EMU4EMU5RSV GP7/EXT_INT7‡GP6/EXT_INT6‡GP5/EXT_INT5‡GP4/EXT_INT4‡GP3CLKOUT6/GP2†CLKOUT4/GP1†GP0CLKOUT6/GP2†CLKOUT4/GP1†EMU6EMU7EMU8EMU9EMU10GP15/PRST §GP14/PCLK §GP13/PINTA §GP12/PGNT §GP11/PREQ §GP10/PCBE3§GP9/PIDSEL §CLKS2/GP8†These pins are muxed with the GPIO port pins and by default these signals function as clocks (CLKOUT4 or CLKOUT6) or McBSP2clock source (CLKS2). To use these muxed pins as GPIO signals, the appropriate GPIO register bits (GPxEN and GPxDIR) must be properly enabled and configured. For more details, see the Device Configurations section of this data sheet.†These pins are GPIO pins that can also function as external interrupt sources (EXT_INT[7:4]). Default after reset is EXT_INTx or GPIO as input-only.‡RSV EMU11RSV RSV RSV •••PCI_EN MCBSP2_ENFor the C6415 and C6416 devices, these GPIO pins are muxed with the PCI peripheral pins. By default, these signals are set up to no function with both the GPIO and PCI pin functions disabled . For more details on these muxed pins, see the Device Configurations section of this data sheet. For the C6414 device, the GPIO peripheral pins are not muxed; the C6414 device does not support the PCI peripheral.§Figure 3. CPU and Peripheral Signals。

DM6446核心板

DM6446核心板介绍:FX-DM6446-1000开发板基于TI TMS320DM6446AZWT双核处理器,它包括一个以ARM926EJS为核的ARM和一个以DSP C64+为核的DSP,工业级内存DDR2-667或DDR2-800,容量达到256M-BYTE,工业级NAND 128M-BYTE,采用目前流行的2K-page 技术,可以同时开发基于达芬奇系列DSP图像算法应用程序和基于达芬奇系列ARM的应用程序,核心板可运行多种音频、视频编解码算法,支持高像素JPEG格式编码,H.264、MPEG-4格式视频全D1 编码标准,核心板集成了CCD接口(支持16位数据宽度或BT656(8~10 BITS))、CVBS或S-VIDEO视频输出接口、高速USB2.0接口、大容量SD卡接口、10/100M以太网、串口、实时时钟等。

软件包为montavista linux-2.6.18操作系统。

DM6446-SYS-V0.3A 核心板以最大限度方便客户进行功能扩展、集成应用,加快产品研发和上市。

主要应用:3G视频方案;安防设备方案;多路IVS智能视频分析方案;双目终端设备方案;机器人方案;机器视觉方案;车载3G方案;人脸识别方案;车牌识别方案;VOIP方案;1.2 核心板介绍:图-3 核心板正面图-4 核心板背面序号资源具体资源描述参数及作用说明1DM6446 TMS320DM6446AZWT 双核:ARM926EJS-300MHz,DSP(C64+)-600MHz2DDR2 DDR2-667(可选DDR2-800) 32bit总线,256M-byte3NAND NAND FLASH 1.8V,128M-byte,2K-page(支持JFFS2、SQUASHFS、Y AFFS2)4 3.3V电源由底板提供5 1.8V电源由底板提供6 1.2V电源DSP核心电压,由底板提供7图像采集VPFE CCD/CMOS接口,支持BT656(8~10-bit)接口,YCrCb 16-bit接口,行信号、场信号控制8USB USB2.0 可设置主从设备,默认为HOST9网口EMAC+MDIO(10M/100M)芯片内集成EMAC和MDIO,外接一个PHY网口芯片就满足网络传输10UART串口UART0,UART1,UART2 同时支持3个UART接口11SD卡接口TI提供的软件直接支持2G的SD卡12SPI接口标准SPI接口13音频接口ASP接口可以直接接音频采集芯片14I2C接口 1.8V的I2C接口15 JTAG接口提供仿真器调试接口16 BOOT MODE 可以控制主芯片从NAND FLASH BOOT,NOR FLASH BOOT,UART BOOT,HPI BOOT等方式17GPIO GPIO1,GPIO7,GPIO8,GPIO9, GPIO10,GPIO11, GPIO12, GPIO13, GPIO14,GPIO15, GPIO16, GPIO17, GPIO18,GPIO19, GPIO21, GPIO24, GPIO25,GPIO26, GPIO28, GPIO37, GPIO50,GPIO52, GPIO5323个独立控制的GPIO(不是复用),可以做很多控制,GPIO脚也可以用作中断信号输入18复合视频输出DAC_IOUT_A,DAC_IOUT_C A和C口可以独立作为复合视频输出,直接接电视机;或者A和C口组合成S-VIDEO输出或Y/C输出19输出时钟CLK_OUT0,CLK_OUT1 CLK_OUT0可输出13.5MHz或27MHz频率CLK_OUT1可输出12MHz或24MHz频率20功耗低功耗,均为1.8V芯片21LOGO 可以加入客户的LOGO22板子颜色绿色,蓝色,红色均可选23板子尺寸 75mm x 47mm24定位柱3个定位柱配合5个I/O插针座子,完全满足车载设备这种工作在颠簸振动的环境25板厚 1.6mm26工作温度-20°——70°可选(-40°——80°)27相对湿度 5%到95%,非凝结FX-DM6446-SYS-V0.3A核心板采用高精度工艺,低功耗芯片合理布局,使其具有最佳的电气性能和抗干扰性能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。