TE7751中文资料

T5557可复制卡中文资料

正 常 读 模 式 (Regular-read Mode)

第一个被传送数据的区是 1 区,当最后的区传送到位时,读从 1 区重新开始。但其中的 0 区一般不被传送, 然而模式寄存器不断用 EEPROM 0 区内容刷新。

④ 存储记忆体结构图 (Memory Map)

4

RF 读 / 写辨识 IC - T5557

可 追 溯 数 据 结 构 (Traceability Data Structure)

第 1 页的块 1 和块 2 包含可追溯数据,并且被 Atmel 在制造测试期间进行其数据规划并且锁定。块 1 最 开始的字节被选定到‘E0’hex,第二个字节是作为 Atmel 制造商的身份按 ISO/IEC 15963-1 所定义的配置分 类(ACL).(=‘15’hex)。第三字节的 8 bit 作为 IC 参考字节被使用( ICR 40~47 bit)。这 3 个部分是关系 到T5557的IC或制造版本的定义位。

RF 读 / 写辨识 IC - T5557

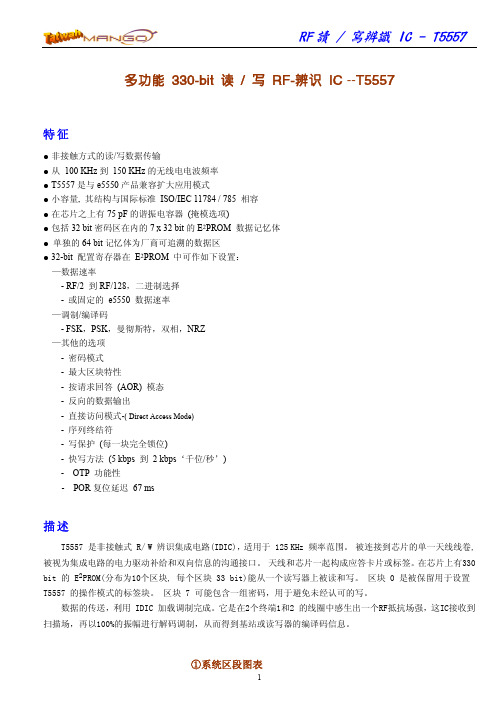

多功能 330-bit 读 / 写 RF-辨识 IC --T5557

特征

● 非接触方式的读/写数据传输 ● 从 100 KHz 到 150 KHz 的无线电电波频率 ● T5557 是与 e5550 产品兼容扩大应用模式 ● 小容量, 其结构与国际标准 ISO/IEC 11784 / 785 相容 ● 在芯片之上有 75 pF 的谐振电容器 (掩模选项) ● 包括 32 bit 密码区在内的 7 x 32 bit 的 E2PROM 数据记忆体 ● 单独的 64 bit 记忆体为厂商可追溯的数据区 ● 32-bit 配置寄存器在 E2PROM 中可作如下设置:

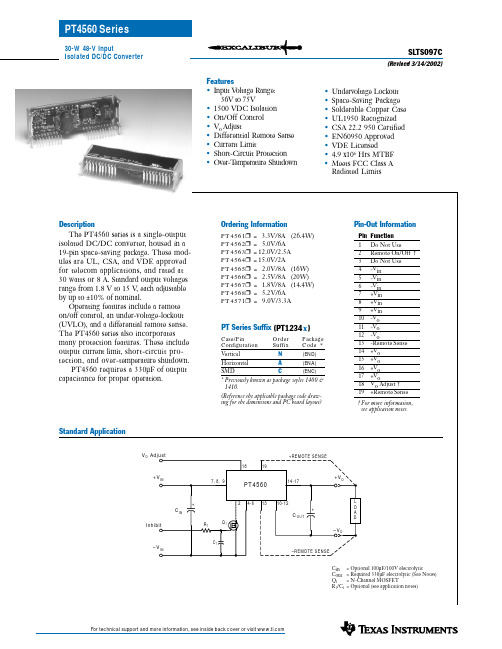

PT4561资料

For technical support and more information, see inside back cover or visit 30-W 48-V InputIsolated DC/DC ConverterFeatures•Input V oltage Range: 36V to 75V•1500 VDC Isolation •On/Off Control •V o Adjust•Differential Remote Sense •Current Limit•Short-Circuit Protection •Over-T emperature ShutdownSLTS097C(Revised 3/14/2002)•Undervoltage Lockout •Space-Saving Package •Solderable Copper Case •UL1950 Recognized •CSA 22.2 950 Certified •EN60950 Approved •VDE Licensed•4.9 x106 Hrs MTBF •Meets FCC Class A Radiated Limits(Unless otherwise stated, TNotes:(1)The DC/DC converter will operate at no load with reduced specifications.(2)The Remote On/Off input has an internal pull-up. If it is left open circuit the PT4560 will operate when input power is applied. A low-leakage(<100nA) MOSFET is recommended to control this input. The open-circuit voltage is less than 10V. See application notes for interface considerations.(3)Output capacitor values are absolute. Allowances must be made for any additional de-coupling capacitors and the total external capacitor tolerance.The value of external capacitance is limited due to regulator startup current requirements. Consult the factory for further details.(4)For operation below 0°C, the required external output capacitor must have temperature stable characteristics. E.g. T antalum or Oscon® types.(5)See Safe Operating Area curves or contact the factory for the appropriate thermal derating.For technical support and more information, see inside back cover or visit For technical support and more information, see inside back cover or visit Note A: All data listed in the above graphs has been developed from actual products tested at 25°C. This data is considered typical data for the DC-DC Converter.Note B: SOA curves represent operating conditions at which internal components are at or below manufacturer’s maximum rated operating temperature.PT4562, 5.0 VDC (See Note A)Efficiency vs Output CurrentRipple vs Output CurrentPower Dissipation vs Output CurrentSafe Operating Area, V in =48V (See Note B)PT4567, 1.8 VDC (See Note A)Efficiency vs Output CurrentRipple vs Output CurrentPower Dissipation vs Output CurrentSafe Operating Area, V in =48V(See Note B)50556065707580E f f i c i e n c y - %V IN2468Iout (A)P d - W a t t sV IN 04812162002468Iout (A)R i p p l e - m VV IN0123456Iout (A)E f f i c i e n c y - %V IN 0123456Iout (A)P d - W a t t sV IN 0123456Iout (A)R i p p l e - m V V IN 0.02.04.06.08.0Iout (A)A m b i e n t T e m p e r a t u r e (°C )Airflow 0123456Iout (A)A m b i e n t T e m p e r a t u r e (°C )For technical support and more information, see inside back cover or visit Efficiency vs Output CurrentRipple vs Output CurrentPower Dissipation vs Output CurrentSafe Operating Area, V in =48V (See Note B)PT4571, 9.0 VDC (See Note A)Note A: All data listed in the above graphs has been developed from actual products tested at 25°C. This data is considered typical data for the DC-DC Converter.Note B: SOA curves represent operating conditions at which internal components are at or below manufacturer’s maximum rated operating temperature.PT4564, 15 VDC (See Note A)0.00.51.01.52.0Iout (A)A m b i e n t T e m p e r a t u r e (°C )Airflow Efficiency vs Output CurrentRipple vs Output CurrentPower Dissipation vs Output CurrentSafe Operating Area, V in =48V (See Note B)0.511.522.53Iout (A)E f f i c i e n c y - %V IN 0123456700.511.522.53Iout (A)P d - W a t t sV IN 00.511.52Iout (A)E f f i c i e n c y - %V IN 00.511.52Iout (A)P d - W a t t sV IN 01002003004000.511.52Iout (A)R i p p l e - m VV IN 030609012015000.511.522.53Iout (A)R i p p l e - m VV IN0.00.51.01.52.02.53.0Iout (A)A m b i e n t T e m p e r a t u r e (°C )AirflowFor technical support and more information, see inside back cover or visit Adjusting the Output Voltage of Power Trends’30W Isolated DC/DC Converter SeriesThe factory pre-set output voltage of Power T rends’ 30W series of isolated DC/DC converters may be adjustedwithin a nominal ±10% range. This is accomplished with the addition of a single external resistor. For the input voltage range specified in the data sheet, T able 1 gives the allowable adjustment range for each model as V o (min)and V o (max).Adjust Up: An increase in the output voltage is obtained by adding a resistor, R 2 between V o adjust (pin 18), and -Remote Sense (pin 13). See note 4.Adjust Down: Add a resistor (R 1), between V o adjust (pin 18), and +Remote Sense (pin 19).Refer to Figure 1 and T ables 2 & 3 for both the placement and value of the required resistor, (R 1) or R 2.Notes:e only a single 1% resistor in either the (R 1) or R 2location. Place the resistor as close to the ISR as possible.2.Never connect capacitors to V o adjust. Any capacitance added to the V o adjust control pin will affect the stability of the ISR.Table 1DC/DC CONVERTER ADJUSTMENT RANGE AND FORMULA PARAMETERSSeries Pt #AL Case:24V Bus PT3341PT3342PT3343PT334448V Bus PT3327PT3325PT3326PT3321PT3322PT3323PT3324CU Case:24V Bus PT4585PT4581PT4582PT4583PT458448V Bus PT4567PT4565PT4566PT4561PT4562PT4571PT4563PT4564V o (nom) 1.8V 1.8V 2.0V 2.5V 3.3V 5.0V 9.0V 12.0V 15.0V Vo(min) 1.62V 1.62V 1.8V 2.25V 2.95V 4.5V 7.0V 10.8V 13.5V Vo(max) 2.5V 1.98V 2.2V 2.75V 3.65V 5.5V 10.0V 13.2V 16.5V V r1.225V 1.225V 1.225V 1.225V 1.225V 1.225V2.5V 2.5V 2.5V K o (V·k Ω)69.5869.5862.4742.3368.8968.71133.25135.9137.5R s (k Ω)80.680.6150.0121.0150.0121.011090.980.6Figure 1outout+V in-V in 3.If the remote sense pins are not being used, the resistors (R1) and R2 can be connected to +V out or -V out respectively.4.The adjusted output voltage, V a effectively sets the voltage across pins 13 and 19 (±Remote Sense). When using the remote sense pins, V out (measured directly across pins 10–12, and 14–17) can be significantly higher than V a , and may exceed V o (max). If V a is adjusted upward of V o (max), the the minimum input voltage is increased by the same percentage as V out exceeds V o (max).The values of (R 1) [adjust down], and R 2 [adjust up], can also be calculated using the following formulas.(R 1)=K o (V a – V r )– R s k ΩV r (V o – V a )R 2=K o – R sk Ω(V a – V o )WhereV o = Original output voltage V a = Adjusted output voltage V r = Reference voltage (T able 1)K o = Multiplier constant (T able 1)R s= Series resistance (T able 1)PT3320/3340/4560/4580 SeriesPT3320/3340/4560/4580 SeriesTable 2DC/DC CONVERTER ADJUSTMENT RESISTOR VALUESSeries Pt #AL Case24V Bus PT334148V Bus PT3327PT3325PT3326PT3321CU Case24V Bus PT4585PT458148V Bus PT4567PT4565PT4566PT4561Current8Adc8Adc8Adc8Adc8AdcV o(nom) 1.8V 1.8V 2.0V 2.5V 3.3VV a(req’d)1.65(80.3)kΩ(80.3)kΩ1.7(189.0)kΩ(189.0)kΩ1.75(516.0)kΩ(516.0)kΩ1.81.85 1.31MΩ 1.31MΩ(62.5)kΩ1.9615.0kΩ615.0kΩ(194.0)kΩ1.95383.0kΩ383.0kΩ(589.0)kΩ2.0267.0kΩ2.05198.0kΩ 1.1MΩ2.1151.0kΩ475.0kΩ2.15118.0kΩ266.0kΩ2.293.3kΩ162.0kΩ2.2574.0kΩ(20.7)kΩ2.358.6kΩ(64.7.0)kΩ2.3545.9kΩ(138.0)kΩ2.435.4kΩ(285.0)kΩ2.4526.4kΩ(726.0)kΩ2.518.8kΩ2.55726.0kΩ2.6302.0kΩ2.65161.0kΩ2.790.6kΩ2.7548.3kΩ2.95(127.0)kΩ3.0(183.0)kΩ3.05(261.0)kΩ3.1(377.0)kΩ3.15(572.0)kΩ3.2(961.0)kΩ3.25(2.13)MΩ3.33.35 1.23MΩ3.4539.0kΩ3.45309.0kΩ3.5194.0kΩ3.55126.0kΩ3.679.6kΩ3.6546.8kΩR1 = (Blue)R2 = BlackFor technical support and more information, see inside back cover or visit Table 3DC/DC CONVERTER ADJUSTMENT RESISTOR VALUESSeries Pt #R1 = (Blue)R2 = BlackFor technical support and more information, see inside back cover or visit Using Remote On/Off on Power Trends’30W Isolated DC-DC Converter SeriesPower T rends’ 30W isolated series of DC/DC converters incorporate a Remote On/Off function. This function may be used in applications for battery conservation, power-up/shutdown sequencing, or to co-ordinate the power-up of the regulator for active in-rush current control. (See TI application reports, SL TA021, and SLUA250).The Remote On/Off function is provided by pin 2. If pin 2 is left open-circuit, the converter provides a regu-lated output whenever a valid source voltage 1 is applied between +V in (pins 7-9), and –V in (pins 4-6). Applying a low voltage 2, with respect to –V in (pin 2), disables the regulator output 3. T able 1 details the control requirements for this input. Figure 1 shows how a discrete MOSFET (Q1) may be referenced to the negative input voltage rail to control the Remote On/Off pin.Table 1 Remote On/Off Control Requirements 2Parameter min maxEnable (V IH) 2.5V 515V(or open circuit) 4Disable (V IL)–0.3V0.8VNotes:1.These converters incorporate an “Under V oltage Lockout”(UVLO) function. This function automatically holds the converter output in the “Off” state until there is sufficient input voltage for the converter to produce a regulatedoutput. T able 2 gives the applicable UVLO thresholds.Table 2 UVLO ThresholdsSeries UVLO Threshold V in RangePT3320/456034± 2.0V36 – 75VPT3340/458016.5± 1.5V18 – 60V2.The Remote On/Off control pin uses –V in (pins 4-6) as itsground reference. All voltages specified are with respect to –V in.3.When the converter output is disabled the current drawnfrom the input supply is typically reduced to 8mA (16mA maximum).4.The internal circuitry comprises of a high impedance (3µA-10µA) current source. The open-circuit voltage is lessthan 10V.5.The Remote On/Off pin is ideally controlled using deviceswith an open-collector (or open-drain) output. A smalllow-leakage MOSFET (<100nA) is recommended. Apull-up resistor is not required, but may be necessary to ensure that the Remote On/Off pin exceeds V IH(min) (see T able 1). Do not use a pull-up resistor to the +V in input, or drive the pin above V IH(max).Figure 1Turn-On Time: When the Remote On/Off input is left open-circuit, the output of the converter is automatically enabled when a valid input voltage 1 is applied to the input power pins. The converter typically rises to full regulation within 30ms of the application of power (or after the release of the Remote On/Off pin with input power applied). The actual turn-on time will vary with the input voltage, output load, and the total amount of capacitance connected to the output. Using the circuit of Figure 1, Figure 2 shows the typical output voltage and input current waveforms for a PT3322/PT4562 after Q1 is turned off. The turn off of Q1 correlates with the fall of the Q1 Vgs waveform. The waveforms were measured with a 48Vdc input voltage, and 5-A resistive load. Figure 2+Vo–Vo +V-V6.Keep the on/off transition to less than 1ms. This preventserratic operation of the ISR, whereby the output voltagemay drift un-regulated between 0V and the rated outputvoltage during power-up.7.In Figure 1, Q1 is a low-threshold MOSFET. Thecomponents R1 and C1 are added to improve noisesusceptibility.Vo (2V/Div)Iin (0.5A/Div)Q1Vgs (10V/Div)For technical support and more information, see inside back cover or visit VDE Approved Installation Instructions (Installationsanleitung)Nennspannnug (Rated Voltage):PT4560 36 to 72 Vdc, T ransient to 75VdcPT4580 18 to 60 Vdc, PT4599 19 to 31 Vdc Nennaufnahme (Rated Input):PT4560 1.5 AdcPT4580, PT4599 3.0 AdcNennleistung (Rated Power):30 Watts MaximumAusgangsspannung (Sec. Voltage):PT4560 Series PT4580 SeriesPT4561, 3.3 Vdc, 8.0 Adc PT4581, 3.3 Vdc, 8.0 AdcPT4562, 5.0 Vdc, 6.0 Adc PT4582, 5.0 Vdc, 6.0 Adc Ausgangsstrom (Sec. Current):PT4563, 12.0 Vdc, 2.5 Adc PT4583,12.0 Vdc, 2.5 Adc oder (or)PT4564, 15.0 Vdc, 2.0 Adc PT4584,15.0 Vdc, 2.0 Adc Ausgangsleistung (Sec. Power):PT4565, 2.0 Vdc, 8.0 Adc PT4585, 1.8 Vdc, 8.0 AdcPT4566, 2.5 Vdc, 8.0 Adc PT4599, 5.0 Vdc, 6.0 AdcPT4567, 1.8 Vdc, 8.0 AdcPT4568, 5.2 Vdc, 6.0 AdcPT4569, 6.0 Vdc, 5.0 AdcPT4570, 8.0 Vdc, 3.75 AdcPT4571, 9.0 Vdc, 3.3 AdcAngabe der Umgebungstemperatur(Information on ambient temperature): +85°C Ambient or 100°C Case Maximum Besondere Hinweise (Special Instructions):Es ist vorzusehen, daß die Spannungsversorgung in einer Endanwendung über eine isolierte Sekundaerschaltung bereit gestellt wird. Die Eingangspannung der Spannungsversorgungsmodule muss eine verstaerkte Isolierung von der Wechselstromquelle aufweisen.Die Spannungsversorgung muss gemaess den Gehaeuse-, Montage-, Kriech- und Luftstrecken-, Markierungs- und Trennanforderungen der Endanwendung installiert werden. Bei Einsatz eines TNV-3-Einganges muss die SEL V-Schaltung ordnungsgemaess geerdet werden.(The power supply is intended to be supplied by isolated secondary circuitry in an end use application. The input power to these power supplies shall have reinforced insulation from the AC mains.The power supply shall be installed in compliance with the enclosure, mounting, creepage, clearance, casualty, markings, and segregation requirements of the end-use application. When the input is TNV-3, the SEL V circuitry must be reliably grounded.)Offenbach,VDE Pr üf- und Zertifizierungsinstitut Abteilung / Department TD(Jürgen Bärwinkel)Ort / Place:Datum / Date: (Stempel und Unterschrift des Herstellers / Stamp and signature of the manufacturer)For technical support and more information, see inside back cover or visit 元器件交易网IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,enhancements, improvements, and other changes to its products and services at any time and to discontinueany product or service without notice. Customers should obtain the latest relevant information before placingorders and should verify that such information is current and complete. All products are sold subject to TI’s termsand conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. Testing and other quality control techniques are used to the extent TIdeems necessary to support this warranty. Except where mandated by government requirements, testing of allparameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible fortheir products and applications using TI components. To minimize the risks associated with customer productsand applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right,copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or processin which TI products or services are used. Information published by TI regarding third–party products or servicesdoes not constitute a license from TI to use such products or services or a warranty or endorsement thereof.Use of such information may require a license from a third party under the patents or other intellectual propertyof the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is withoutalteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproductionof this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable forsuch altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for thatproduct or service voids all express and any implied warranties for the associated TI product or service andis an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Mailing Address:Texas InstrumentsPost Office Box 655303Dallas, Texas 75265Copyright 2002, Texas Instruments Incorporated。

EPM1270T144C5N中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

■ 更新 表1-2.

■ 更新"简介"一节. ■ 更新新文档格式. ■ 通过表1-5更新表1-1. ■ 增加"参考文献"部分. ■ 添加文档修订历史记录.

■ 次要更新功能列表.

■ 次要更新表.

更改摘要

增加信息速度等级-8 —

在256引脚EPM570,EPM1270和EPM2210设备之间迁移

FineLine BGA封装).垂直迁移意味着你可以迁移到设备

其专用引脚和JTAG引脚是相同电源引脚子集或

超集跨设备密度一个给定包.在任何最大密度

包具有最高数量电源引脚;你必须制定出最大

在一个包计划密度以提供必要电源引脚进行迁移.供

更新文件与MAX IIZ信息. — — —

芯片中文手册,看全文,戳

表 1-6. 文档修订历史记录

日期和修订

所做更改

2005年6月, 1.3版

2004年12月, 1.2版

2004年6月, 1.1版

■ 更新时间数字表1-1所示. ■ 更新时间数字表1-1所示. ■ 更新时间数字表1-1所示.

每一个速度等级和密度范围内数字,指是

特点

在本章

MAX II器件手册.

表1-2 显示MAX II器件速度等级产品.

DC和开关

表 1-2. MAX II速度等级

速度等级

器

EPM240 EPM240G EPM570 EPM570G EPM1270 EPM1270G EPM2210 EPM2210G EPM240Z EPM570Z

3.3 V / 2.5 V或1.8 V ■ 多电压I / O接口,支持3.3 V,2.5 V,1.8 V和1.5 V逻辑电平 ■ 总线型架构,包括可编程摆率,驱动能力,

ADE7757中文资料

ADE7757中文资料1. ADE7757功能及特点概述ADE7757是美国AD公司推出的高精度电能测量集成芯片。

与原有的同系列ADE7755相比,其芯片引脚较少,且内置了一个精确的振荡器电路来给芯片提供时钟。

该芯片的内部电路除了ADC和参考电路是模拟电路外,其余均为数字电路,因此芯片在长时间与极端工作条件下具有卓越的稳定性与精度。

ADE7757可在低频输出引脚F1、F2上输出平均有功功率,并可直接驱动一个机电计数器或与MCU的接口。

而高频CF逻辑则可输出用于校准的瞬时有功功率。

ADE7757的基本特性和参数如下:●带有片内振荡器,可作为时钟源;●精度高,且与50Hz/60Hz的IEC521/1036标准兼容;●逻辑输出引脚REVP可用来指示可能的接线错误或负功率;●带有片内电源监视器;●采用单5V电源,功耗较低;●采用交流输入。

2内部结构及引脚功能ADE7757是16脚SOIC封装,图1为其内部结构框图,各引脚的功能见表1所列。

表1 ADE7757的引脚功能引脚名称功能1VDD电源2,3V2P,V2N通道V2(电压通道)的模拟输入4,5V1P,V1N通道V1(电流通道)的模拟输入6AGND模拟地7REF IN/OUT片内参考电压8SCF选择校准频率9,10S1,S0频率选择11RCLKIN内部振荡器使能端12REVP负功率检测脚13DGND数字地14CF校准频率逻辑输出15,16F2,F1低频逻辑输出3ADE7757的原理特性图1所示是ADE7757的内部原理图,图中,两个ADC电路将电流传感器和电压传感器送入的电压信号进行数字化。

这个模拟输入结构大大简化了传感器接口电路,并提供了很大的动态范围,同时简化了滤波器的设计。

电流通道(V1通道)的高通滤波器(HPF)去掉了电流信号里的全部直流成分,从而减少了有功功率计算中由电压或电流信号偏移带来的不精确性。

有功功率的计算可由瞬时功率信号获得。

瞬时功率等于电流与电压信号的乘积。

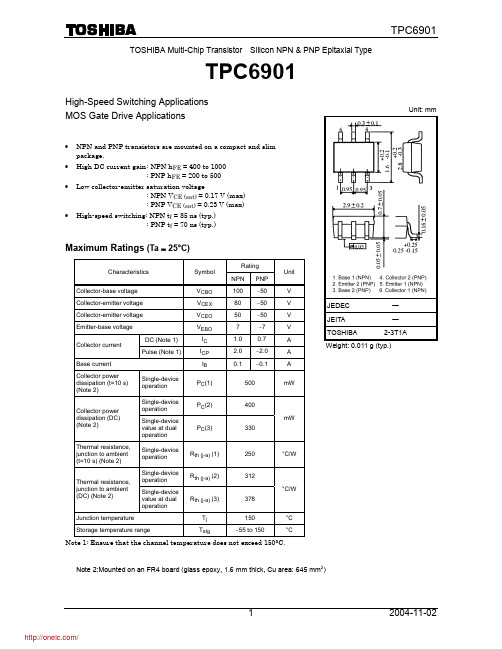

TPC6901(TE85L,F);中文规格书,Datasheet资料

Single-device operation

Single-device value at dual operation

PC(2) PC(3)

400

mW 330

Thermal resistance, junction to ambient (t=10 s) (Note 2)

Single-device operation

Collector-emitter saturation voltage

Base-emitter saturation voltage

Collector output capacitance

Rise time

Switching time

Storage time

Fall time

Symbol

Test Condition

JEDEC

―

JEITA

―

TOSHIBA

2-3T1A

Weight: 0.011 g (typ.)

Note 2:Mounted on an FR4 board (glass epoxy, 1.6 mm thick, Cu area: 645 mm2)

/

1

2004-11-02

0.1

0.01 0.001

Ta = 100°C

25°C

−55°C

0.01

0.1

1

Collector current IC (A)

IC – VBE

1.0 Common emitter VCE = 2 V Single nonrepetitive pulse

0.8

Ta = 100°C 0.6

0.4

0.2

Electrical Characteristics (Ta = 25°C) : NPN

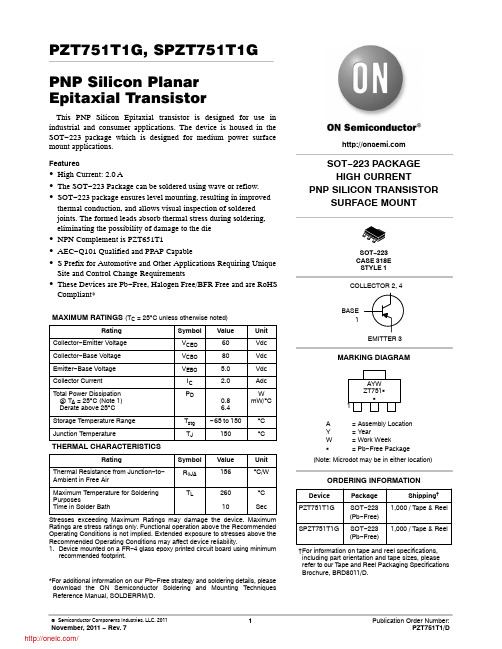

PZT751T1;PZT751T1G;中文规格书,Datasheet资料

thermal conduction, and allows visual inspection of soldered joints. The formed leads absorb thermal stress during soldering, eliminating the possibility of damage to the die NPN Complement is PZT651T1 AEC−Q101 Qualified and PPAP Capable S Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements These Devices are Pb−Free, Halogen Free/BFR Free and are RoHS Compliant*

PNP

VCE = -2.0 V

Figure 1. Typical DC Current Gain

Figure 2. Typical DC Current Gain

NPN

2.0 1.8 1.6 V, VOLTAGE (VOLTS) 1.4 1.2 1.0 0.8 0.6 0.4 0.2 0 50 100 200 500 1.0 A IC, COLLECTOR CURRENT (mA) 2.0 A 4.0 A VCE(sat) @ IC/IB = 10 VBE(on) @ VCE = 2.0 V VBE(sat) @ IC/IB = 10 V, VOLTAGE (VOLTS) -2.0 -1.8 -1.6 -1.4 -1.2 -1.0 -0.8 -0.6 -0.4 -0.2 0 -50 -100

CC2541中文资料

CC2541 有 2 个不同的版本:分别具有 128kB 和 256kB 闪存的的 CC2541F128/F256。

CC2541 的方框图请参见Figure 1。

2

Copyright © 2012–2013, Texas Instruments Incorporated

All supply pins must have the same voltage

All pins, excluding pins 25 and 26, according to human-body model, JEDEC STD 22, method A114 All pins, according to human-body model, JEDEC STD 22, method A114 According to charged-device model, JEDEC STD 22, method C101

支持 – 电池监视器和温度传感器 – 含 8 通道和可配置分辨率的 12 位模数转换器

(ADC) – 高级加密标准 (AES) 安全协处理器 – 2 个功能强大的支持几个串行协议的通用异步接

收发器 (UART) – 23 个通用 I/O 引脚

(21 × 4 mA,2 × 20 mA) – I2C 接口 – 2 个具有 LED 驱动功能的 I/O 引脚 – 安全装置定时器 – 集成的高性能比较器 • 开发工具 – CC2541 评估模块工具包 (CC2541EMK) – CC2541 小型开发工具包 (CC2541DK-MINI) – SmartRF™ 软件 – 提供 IAR 嵌入式 Workbench™

ADE7758+中文+82页+1.0M+高清版.

ADE7758是一种高精确度三相电能测量 IC功能特性:高精确性,支持国际电工委员会的60687,61036,61268,62053-21,62053-22,62053-23兼容三相/三线制,三相/四线制和其他的三相设备在25°C的常温下从1到1000动态范围的活动能量误差低于0.1%支持正相的、反相的、交互式的能量,电压和电流的均方根和采样数据的波形。

两个脉冲输出,一个是正相的电流,另一个是用可编程在正相和视在电源进行选择。

数字电源,相位和均方根的偏移标定。

一个芯片电压标准发生器用来可编程阈值限制和过压的检测,一个数字积分器芯片能够通过输入和输出接口作为直流变交流的传感器接口。

电流通道的一个管脚阵列允许直流变分路电流和交流互感器。

一个外围接口可以通过中断请求和外围接口兼容。

所有的模数转换器和数字信号处理提供了高精确性在外界环境条件变化和时间基准电压2.4V(偏差是百万分之三十)外部的驱使过度能量。

单一的5V电源,低功率(70兆瓦)。

综合的描述1数模转换器7758(以下简称ADE7758)是一个高精确性的三相电流源测量集成电路,有一个串行口和两个脉冲输出口,ADE7758合并了所有的数模转换的和的二次阶,数字积分器,基准电压源线路,温度传感器,和所有的信号处理器必须的执行的正相的,反相,和表观能量测量和均方根的计算。

ADE7758适合测量正相,反相和三相结构的各种表观能量,例如WYE或者是DELTA设备,都是三到四根线。

ADE7758为每个相位提供了系统校准特性,也就是均方根偏差校正,相位校准,和电源校准。

有源补偿滤波器(APCF)的逻辑输出提供了正相电源信息,复功率校准频率逻辑输出(VARCF)逻辑输出提供了瞬时的反相或者视在功率信息。

下图1为ADE7758的功能结构图概括描述ADE有一个波形采样寄存器,允许直接访问AD转换器的输出。

这部分为短周期的低或高电压变化集成了检测线路。

电压的阀值电平和周期(半线回路的条数)的变化都是用户可编程的。

mt9171中文资料_数据手册_IC数据表

1Features•Full duplex transmission over a single twisted pair •Selectable 80 or 160 kbit/s line rate •Adaptive echo cancellation •Up to 3km (9171) and 4 km (9172)•ISDN compatible (2B+D) data format •Transparent modem capability•Frame synchronization and clock extraction •Zarlink ST-BUS compatible•Low power (typically 50mW), single 5V supplyApplications•Digital subscriber lines•High speed data transmission over twisted wires •Digital PABX line cards and telephone sets •80 or 160kbit/s single chip modemDescriptionThe MT9171 (DSIC) and MT9172 (DNIC) are pin for pin compatible replacements for the MT8971 and MT8972, respectively. They are multi-function devices capable of providing high speed, full duplex digital transmission up to 160kbit/s over a twisted wire pair.They use adaptive echo-cancelling techniques and transfer data in (2B+D) format compatible to the ISDN basic rate. Several modes of operation allow an easy interface to digital telecommunication networks including use as a high speed limited distance modemMarch 2006Ordering InformationMT9171/72AE 22 Pin PDIP Tubes MT9171/72AN 24 Pin SSOP Tubes MT9171/72AP 28 Pin PLCC TubesMT9171/72APR 28 Pin PLCC Tape & Reel MT9171/72ANR 24 Pin SSOP Tape & Reel MT9171/72AE122 Pin PDIP*Tubes MT9171/72AP128 Pin PLCC*Tubes MT9171/72AN124 Pin SSOP*TubesMT9171/72APR128 Pin PLCC*Tape & Reel MT9171/72ANR124 Pin SSOP*Tape & Reel*Pb Free Matte Tin-40°C to +85°CISO 2-CMOS ST-BUS FAMILY MT9171/72Digital Subscriber Interface Circuit Digital Network Interface CircuitData SheetFigure 1 - Functional Block DiagramDSTi/Di CDSTi/F0/CLD C4/TCK F0o/RCKMS0MS1MS2RegCDSTo/Do CDSTo/CDoTransmit InterfacePrescrambler ScramblerControl Register Transmit/Clock Receive Timing &Control StatusTransmit Timing Master Clock Phase LockedSync Detect ReceiveDPLLReceive InterfaceDe -PrescramblerDescramblerDifferentially Encoded BiphaseReceiverDifferentially Encoded Biphase Transmitter Transmit Filter &Line DriverReceive Filter-1+2MUXAddressEcho Canceller Error Signal Echo EstimateV BiasV DD V SS V Bias V RefL OUTL OUTDISPrecanL INOSC2OSC1—+∑CDihttps://MT9171/72Data Sheetwith data rates up to 160kbit/s. Both devices function identically but with the DSIC having a shorter maximum loop reach specification. The generic "DNIC" will be used to reference both devices unless otherwise noted.The MT9171/72 is fabricated in Zarlink’s ISO 2-CMOS process.Figure 2 - Pin ConnectionsPin DescriptionPin # Name Description222428112L OUT Line Out. Transmit Signal output (Analog). Referenced to V Bias .223V Bias Internal Bias Voltage output. Connect via 0.33µF decoupling capacitor to V DD .334V RefInternal Reference Voltage output. Connect via 0.33µF decoupling capacitor to V DD .4,5,64,5,65,7,8MS2-MS0Mode Select inputs (Digital). The logic levels present on these pins select thevarious operating modes for a particular application. See Table 1 for the operating modes.779RegC Regulator Control output (Digital). A 512kHz clock used for switch mode power supplies. Unused in MAS/MOD mode and should be left open circuit.8910F0/CLDFrame Pulse/C-Channel Load (Digital). In DN mode a 244ns wide negative pulse input for the MASTER indicating the start of the active channel times of the device. Output for the SLAVE indicating the start of the active channel times of the device. Output in MOD mode providing a pulse indicating the start of the C-channel.1234567891011121314222120191817161522 PIN PDIPLOUT VBias VRef MS2MS1MS0RegC F0/CLD CDSTi/CDi CDSTo/CDoVSS VDD LIN TESTLOUT DIS Precan OSC1OSC2C4/TCK F0o/RCK DSTi/Di DSTo/Do28 PIN PLCC27432128265678910112524232221201917121314151618•L O U T V B i a s V R e f N C V D D L I N T E S TNCLOUT DIS Precan OSC1OSC2NC C4/TCKMS2NC MS1MS0RegC F0/CLDNCC D S T i /C D i C D S T o /C D o V S S D S T o /D o N C F 0o /R C K D S T i /D i 12345678910111213141516242322212019181724 PIN SSOPLOUT VBias VRef MS2MS1MS0RegC F0/CLD CDSTi/CDi CDSTo/CDoVSSNC VDD LIN TESTLOUT DIS Precan OSC1OSC2C4/TCK F0o/RCK DSTi/Di DSTo/DoNC https://MT9171/72Data Sheet91012CDSTi/CDi Control/Data ST-BUS In/Control/Data In (Digital). A 2.048Mbit/s serial control & signalling input in DN mode. In MOD mode this is a continuous bit stream at the bit rate selected.101113CDSTo/CDo Control/Data ST-BUS Out/Control/Data Out (Digital). A 2.048Mbit/s serial control & signalling output in DN mode. In MOD mode this is a continuous bit stream at the bit rate selected.111214V SSNegative Power Supply (0V).121315DSTo/Do Data ST-BUS Out/Data Out (Digital). A 2.048Mbit/s serial PCM/data output inDN mode. In MOD mode this is a continuous bit stream at the bit rate selected.131416DSTi/DiData ST-BUS In/Data In (Digital). A 2.048Mbit/s serial PCM/data input in DN mode. In MOD mode this is a continuous bit stream at the bit rate selected.141517F0o/RCK Frame Pulse Out/Receive Bit Rate Clock output (Digital). In DN mode a 244nswide negative pulse indicating the end of the active channel times of the device to allow daisy chaining. In MOD mode provides the receive bit rate clock to the system.151619C4/TCKData Clock/Transmit Baud Rate Clock (Digital). A 4.096MHz TTL compatible clock input for the MASTER and output for the SLAVE in DN mode. For MOD mode this pin provides the transmit bit rate clock to the system.161721OSC2Oscillator Output . CMOS Output.171922OSC1Oscillator Input . CMOS Input. D.C. couple signals to this pin. Refer to D.C. Electrical Characteristics for OSC1 input requirements.182023PrecanPrecanceller Disable. When held to Logic ’1’, the internal path from L OUT to the precanceller is forced to V Bias thus bypassing the precanceller section. When logic ’0’, the L OUT to the precanceller path is enabled and functions normally. An internal pulldown (50k Ω) is provided on this pin.8,181,6,11,18,20,25NCNo Connection. Leave open circuit192124L OUT DIS L OUT Disable. When held to logic “1”, L OUT is disabled (i.e., output = V Bias ). Whenlogic “0”, L OUT functions normally. An internal pulldown (50k Ω) is provided on this pin.202226TEST Test Pin. Connect to V SS .212327L IN Receive Signal input (Analog). 222428V DDPositive Power Supply (+5V) input.Pin Description (continued)Pin # Name Description222428https://MT9171/72Data SheetFigure 3 - DV Port - 80kbit/s (Modes 2, 3, 6)Figure 4 - DV Port - 160kbit/s (Modes 2, 3, 6)MT9171/72Data Sheet Functional DescriptionThe MT9171/72 is a device which may be used in practically any application that requires high speed data transmission over two wires, including smart telephone sets, workstations, data terminals and computers. The device supports the 2B+D channel format (two 64kbit/s B-channels and one 16kbit/s D-channel) over two wires as recommended by the CCITT. The line data is converted to and from the ST-BUS format on the system side of the network to allow for easy interfacing with other components such as the S-interface device in an NT1 arrangement, or to digital PABX components.Smart telephone sets with data and voice capability can be easily implemented using the MT9171/72 as a line interface. The device’s high bandwidth and long loop length capability allows its use in a wide variety of sets. This can be extended to provide full data and voice capability to the private subscriber by the installation of equipment in both the home and central office or remote concentration equipment. Within the subscriber equipment the MT9171/72 would terminate the line and encode/ decode the data and voice for transmission while additional electronics could provide interfaces for a standard telephone set and any number of data ports supporting standard data rates for such things as computer communications and telemetry for remote meter reading. Digital workstations with a high degree of networking capability can be designed using the DNIC for the line interface, offering up to 160 kbit/s data transmission over existing telephone lines. The MT9171/72 could also be valuable within existing computer networks for connecting a large number of terminals to a computer or for intercomputer links. With the DNIC, this can be accomplished at up to 160kbit/s at a very low cost per line for terminal to computer links and in many cases this bandwidth would be sufficient for computer to computer links.Figure 1 shows the block diagram of the MT9171/72. The DNIC provides a bidirectional interface between the DV (data/voice) port and a full duplex line operating at 80 or 160kbit/s over a single pair of twisted wires. The DNIC has three serial ports. The DV port (DSTi/Di, DSTo/Do), the CD (control/data) port (CDSTi/CDi, CDSTo/CDo) and a line port (L IN, L OUT). The data on the line is made up of information from the DV and CD ports. The DNIC must combine https://information received from both the DV and CD ports and put it onto the line. At the same time, the data received from the line must be split into the various channels and directed to the proper ports. The usable data rates are 72 and144kbit/s as required for the basic rate interface in ISDN. Full duplex transmission is made possible through on board adaptive echo cancellation.The DNIC has various modes of operation which are selected through the mode select pins MS0-2. The two major modes of operation are the MODEM (MOD) and DIGITAL NETWORK (DN) modes. MOD mode is a transparent 80 or 160kbit/s modem. In DN mode the line carries the B and D channels formatted for the ISDN at either 80 or 160 kbit/s. In the DN mode the DV and CD ports are standard ST-BUS and in MOD mode they are transparent serial data streams at 80 or 160kbit/s. Other modes include: MASTER (MAS) or SLAVE (SLV) mode, where the timebase and frame synchronization are provided externally or are extracted from the line and DUAL or SINGLE (SINGL) port modes, where both the DV and CD ports are active or where the CD port is inactive and all information is passed through the DV port. For a detailed description of the modes see “Operating Modes” section.In DIGITAL NETWORK (DN) mode there are three channels transferred by the DV and CD ports. They are the B, C and D channels. The B1 and B2 channels each have a bandwidth of 64kbit/s and are used for carrying PCM encoded voice or data. These channels are always transmitted and received through the DV port (Figures 3, 4, 5, 6). The C-channel, having a bandwidth of 64kbit/s, provides a means for the system to control the DNIC and for the DNIC to pass status information back to the system. The C-channel has a Housekeeping (HK) bit which is the only bit of the C-channel transmitted and received on the line. The 2B+D channel bits and the HK bit are double-buffered. The D-channel can be transmitted or received on the line with either an 8, 16 or 64kbit/s bandwidth depending on the DNIC’s mode of operation. Both the HK bit and the D-channel can be used for end-to-end signalling or low speed data transfer. In DUAL port mode the C and D channels are accessed via the CD port (Figure 7) while in SINGL port mode they are transferred through the DV port (Figures 5, 6) along with the B1 and B2 channels.MT9171/72Data SheetFigure 5 - DV Port - 80kbit/s (Modes 0,4)Figure 6 - DV Port - 160kbit/s (Modes 0,4)In DIGITAL NETWORK (DN) mode, upon entering the DNIC from the DV and CD ports, the B-channel data, D-channel D0 (and D1 for 160kbit/s), the HK bit of the C-channel (160kbit/s only) and a SYNC bit are combined in a serial format to be sent out on the line by the Transmit Interface (Figures 11, 12). The SYNC bit produces an alternating 1-0 pattern each frame in order for the remote end to extract the frame alignment from the line. It is possible for the remote end to lock on to a data bit pattern which simulates this alternating 1-0 pattern that is not the true SYNC. To decrease the probability of this happening the DNIC may be programmed to put the data through a prescrambler that scrambles the data according to a predetermined polynomial with respect to the SYNC bit. This greatly decreases the probability that the SYNC pattern can be reproduced by any data on the line. In order for the echo canceller to function correctly, a dedicated scrambler is used with a scrambling algorithm which is different for the SLV and MAS modes. These algorithms are calculated in such a way as to provide orthogonality between the near and far end data streams such that the correlation between the two signals is very low.For any two DNICs on a link, one must be in SLV mode with the other in MAS mode. The scrambled data is differentially encoded which serves to make the data on the line polarity-independent. It is then biphase encoded as shown in Figure 10. See “Line Interface” section for more details on the encoding. Before leaving the DNIC the differentially encoded biphase data is passed through a pulse-shaping bandpass transmit filter that filters out the high and low frequency components and conditions the signal for transmission on the line.MT9171/72Data SheetFigure 7 - CD Port (Modes 2,6)Figure 8 - CD Port (Modes 1,5)The composite transmit and receive signal is received at L IN . On entering the DNIC this signal passes through a Precanceller which is a summing amplifier and lowpass filter that partially cancels the near-end signal and provides first order antialiasing for the received signal. Internal, partial cancellation of the near end signal may be disabled by holding the Precan pin high. This mode simplifies the design of external line transceivers used for loop extension applications. The Precan pin features an internal pull-down which allows this pin to be left unconnected in applications where this function is not required. The resultant signal passes through a receive filter to bandlimit and equalize it. At this point, the echo estimate from the echo canceller is subtracted from the precancelled received signal. This difference signal is then input to the echo canceller as an error signal and also squared up by a comparator and passed to the biphase receiver. Within the echo canceller, the sign of this error signal is determined. Depending on the sign, the echo estimate is either incremented or decremented and this new estimate is stored back in RAM.The timebase in both SLV and MAS modes (generated internally in SLV mode and externally in MAS mode) is phase-locked to the received data stream. This phase-locked clock operates the Biphase Decoder, Descrambler and Deprescrambler in MAS mode and the entire chip in SLV mode. The Biphase Decoder decodes the received encoded bit stream resulting in the original NRZ data which is passed onto the Descrambler and Deprescrambler where the data is restored to its original content by performing the reverse polynomials. The SYNC bits areCLDTCKCDiCDoC 0C 1C 2C 3C 4C 5C 6C 7C 6C 7C 0C 1C 0C 1C 2C 3C 4C 5C 6C 7C 6C 7C 0C 1https://MT9171/72Data Sheetextracted and the Receive Interface separates the channels and outputs them to the proper ports in the proper channel times. The destination of the various channels is the same as that received on the input DV and CD ports.The Transmit/Receive Timing and Control block generates all the clocks for the transmit and receive functions and controls the entire chip according to the control register. In order that more than one DNIC may be connected to the same DV and CD ports an F0o signal is generated which signals the next device in a daisy chain that its channel times are now active. In this arrangement only the first DNIC in the chain receives the system F0 with the following devices receiving its predecessor’s F0o.In MOD mode, all the ports have a different format. The line port again operates at 80 or 160kbit/s, however, there is no synchronization overhead, only transparent data. The DV and CD ports carry serial data at 80 or 160kbit/s with the DV port transferring all the data for the line and the CD port carrying the C-channel only. In this mode the transfer of data at both ports is synchronized to the TCK and RCK clocks for transmit and receive data, respectively. The CLD signal goes low to indicate the start of the C-channel data on the CD port. It is used to load and latch the input and output C-channel but has no relationship to the data on the DV port.Operating Modes (MS0-2)The logic levels present on the mode select pins MS0, MS1 and MS2 program the DNIC for different operating modes and configure the DV and CD ports accordingly. Table 1 shows the modes corresponding to the state of MS0-2. These pins select the DNIC to operate as a MASTER or SLAVE, in DUAL or SINGLE port operation, in MODEM or DIGITAL NETWORK mode and the order of the C and D channels on the CD port. Table 2 provides a description of each mode and Table 3 gives a pin configuration according to the mode selected for all pins that have variable functions. These functions vary depending on whether it is in MAS or SLV, and whether DN or MOD mode is used.Table 1 - Mode Select Pins E=Enabled X=Not Applicable Blanks are disabledMode Select Pins Mode Operating ModeMS2MS1MS0SLVMAS DUALSINGL MODDN D-C C-D ODE 0000E EE E E 0011E E E X X E 0102E E E EE 0113EEE E E 1004E EE E E1015E E EX X E 1106EE E EE1117EEEEhttps://MT9171/72Data SheetTable 3 - Pin ConfigurationsThe overall mode of operation of the DNIC can be programmed to be either a baseband modem (MOD mode) or a digital network transceiver (DN mode). As a baseband modem, transmit/receive data is passed transparently through the device at 80 or 160kbit/s by the DV port. The CD port transfers the C-channel and D-Channel also at 80 or 160kbit/s.In DN mode, both the DV and CD ports operate as ST-BUS streams at 2.048Mbit/s. The DV port transfers data over pins DSTi and DSTo while on the CD port, the CDSTi and CDSTo pins are used. The SINGL port option only exists in DN mode.Mode FunctionSLVSLAVE - The chip timebase is extracted from the received line data and the external 10.24MHz crystal is phase locked to it to provide clocks for the entire device and are output for the external system to synchronize to.MASMASTER - The timebase is derived from the externally supplied data clocks and 10.24MHz clock which must be frequency locked. The transmit data is synchronized to the system timing with the receive data recovered by a clock extracted from the receive data and resynchronized to the system timing.DUAL DUAL PORT - Both the CD and DV ports are active with the CD port transferring the C&D channels and the DV port transferring the B1& B2 channels.SINGL SINGLE PORT - The B1& B2, C and D channels are all transferred through the DV port. The CD port is disabled and CDSTi should be pulled high.MODMODEM - Baseband operation at 80 or 160kbits/s. The line data is received and transmitted through the DV port at the baud rate selected. The C-channel is transferred through the CD port also at the baud rate and is synchronized to the CLD output.DN DIGITAL NETWORK - Intended for use in the digital network with the DV and CD ports operating at 2.048Mbits/s and the line at 80 or 160kbits/s configured according to the applicable ISDN recommendation.D-C D BEFORE C-CHANNEL - The D-channel is transferred before the C-channel following F0.C-D C BEFORE D-CHANNEL - The C-channel is transferred before the D-channel following F0.ODEOUTPUT DATA ENABLE - When mode 7 is selected, the DV and CD ports are put in highimpedance state. This is intended for power-up reset to avoid bus contention and possible damage to the device during the initial random state in a daisy chain configuration of DNICs. In all the other modes of operation DV and CD ports are enabled during the appropriate channel times.Mode #F0/CLDF0o/RCKC4/TCKName Input/OutputName Input/OutputName Input/Output0F0Input F0o Output C4Input 1CLD Output RCK Output TCK Output 2F0Input F0o Output C4Input 3F0Input F0o Output C4Input 4F0Output F0o Output C4Output 5CLD Output RCK Output TCK Output 6F0Output F0oOutputC4Output 7F0InputF0o OutputC4Inputhttps://MT9171/72Data SheetIn MOD mode, DUAL port operation must be used and the D, B1 and B2 channel designations no longer exist. The selection of SLV or MAS will determine which of the DNICs is using the externally supplied clock and which is phase locking to the data on the line. Due to jitter and end to end delay, one end must be the master to generate all the timing for the link and the other must extract the timing from the receive data and synchronize itself to this timing in order to recover the synchronous data. DUAL port mode allows the user to use two separate serial busses: the DV port for PCM/data (B channels) and the CD port for control and signalling information (C and D channels). In the SINGL port mode, all four channels are concatenated into one serial stream and input to the DNIC via the DV port.The order of the C and D channels may be changed only in DN/DUAL mode. The DNIC may be configured to transfer the D-channel in channel 0 and the C-channel in channel 16 or vice versa. One other feature exists; ODE,where both the DV and CD ports are tristated in order that no devices are damaged due to excessive loading while all DNICs are in a random state on power up in a daisy chain arrangement.DV Port (DSTi/Di, DSTo/Do)The DV port transfers data or PCM encoded voice to and from the line according to the particular mode selected by the mode select pins. The modes affecting the configuration of the DV port are MOD or DN and DUAL or SINGL. In DN mode the DV port operates as an ST-BUS at 2.048Mbit/s with 32, 8 bit channels per frame as shown in Figure 9. In this mode the DV port channel configuration depends upon whether DUAL or SINGL port is selected. When DUAL port mode is used, the C and D channels are passed through the CD port and the B1 and B2 channels are passed through the DV port. At 80kbit/s only one channel of the available 32 at the DV port is utilized, this being channel 0 which carries the B1-channel. This is shown in Figure 3. At 160kbit/s, two channels are used, these being 0 and 16 carrying the B1 and B2 channels, respectively. This is shown in Figure 4. When SINGL port mode is used, channels B1, B2, C and D are all passed via the DV port and the CD port is disabled. See CD port description for an explanation of the C and D channels.Figure 9 - ST-BUS FormatThe D-channel is always passed during channel time 0 followed by the C and B1 channels in channel times 1 and 2, respectively for 80kbit/s. See Figure 5. For 160kbit/s the B2 channel is added and occupies channel time 3 of the DV port. See Figure 6. For all of the various configurations the bit orders are shown by the respective diagram.In MOD mode the DV and CD ports no longer operate at 2.048Mbits/s but are continuous serial bit streams operating at the bit rate selected of 80 or 160kbit/s.While in the MOD mode only DUAL port operation can be used.In order for more than one DNIC to be connected to any one DV and CD port, making more efficient use of the busses, the DSTo and CDSTo outputs are put into high impedance during the inactive channel times of the DNIC.This allows additional DNICs to be cascaded onto the same DV and CD ports. When used in this way a signal called F0o is used as an indication to the next DNIC in a daisy chain that its channel time is now active. Only the first DNIC in the chain receives the system frame pulse and all others receive the F0o from its predecessor in the chain. This allows up to 16 DNICs to be cascaded.ChannelChannel1Channel2• • • • • • • •Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0125 µsecChannel 31Channel 30Channel 31ChannelChannel 29F0ST-BUSMost Significant Bit (First)LeastSignificant Bit (Last)3.9 µsechttps://MT9171/72Data SheetCD Port (CDSTi/CDi, CDSTo/CDo)The CD port is a serial bidirectional port used only in DUAL port mode. It is a means by which the DNIC receives its control information for things such as setting the bit rate, enabling internal loopback tests, sending status information back to the system and transferring low speed signalling data to and from the line.The CD port is composed of the C and D-Channels. The C-channel is used for transferring control and status information between the DNIC and the system. The D-channel is used for sending and receiving signalling information and lower speed data between the line and the system. In DN/DUAL mode the DNIC receives a C-channel on CDSTi while transmitting a C-channel on CDSTo. Fifteen channel times later (halfway through the frame) a D-channel is received on CDSTi while a D-channel is transmitted on CDSTo. This is shown in Figure 7.The order of the C and D bytes in DUAL port mode can be reversed by the mode select pins. See Table 1 for a listing of the byte orientations.The D-channel exists only in DN mode and may be used for transferring low speed data or signalling information over the line at 8, 16 or 64kbit/s (by using the DINB feature). The information passes transparently through the DNIC and is transmitted to or received from the line at the bit rate selected in the Control Register.If the bit rate is 80kbit/s, only D0 is transmitted and received. At 160kbit/s, D0 and D1 are transmitted and received. When the DINB bit is set in the Control Register the entire D-channel is transmitted and received in the B1-channel timeslot.The C-channel is used for transferring control and status information between the DNIC and the system. The Control and Diagnostics Registers are accessed through the C-channel. They contain information to control the DNIC and carry out the diagnostics as well as the HK bit to be transmitted on the line as described in Tables 4 and 5. Bits 0 and 1 of the C-channel select between the Control and Diagnostics Register. If these bits are 0, 0 then the C-channel information is written to the Control Register (Table 4). If they are 0, 1 the C-c hannel is written to the Diagnostics Register (Table 5).Bit Name Description0Reg Sel-1Register Select-1. Must be set to ’0’ to select the Control Register.1Reg Sel-2Register Select-2. Must be set to ’0’ to select the Control Register.2DRRDiagnostics Register Reset. Writing a "0" to this bit will cause a diagnostics register reset to occur coincident with the next frame pulse as in the MT8972A. When this bit is a logic "1", the Diagnostics Register will not be reset.3BRS Bit Rate Select. When set to ’0’ selects 80kbit/s. When set to ’1’, selects 160kbit/s.4DINB 2D-Channel in B Timeslot. When ’0’, the D-channel bits (D0 or D0 and D1) corresponding to the selected bit rate (80 or 160kbit/s) are transmitted during the normal D-channel bit times. When set to ’1’, the entire D-channel (D0-D7) is transmitted during the B1-channel timeslot on the line providing a 64kbit/s D-channel link.5PSEN 2Prescrambler/Deprescrambler Enable. When set to ’1’, the data prescrambler anddeprescrambler are enabled. When set to ’0’, the data prescrambler and deprescrambler are disabled.bit 0bit 1bit 2bit 3bit 4bit 5bit 6bit 7Reg Sel-1Reg Sel-2DRRBRSDINBPSENATTACKTxHKDefault Mode Selection (Refer to Table 4a)https://。

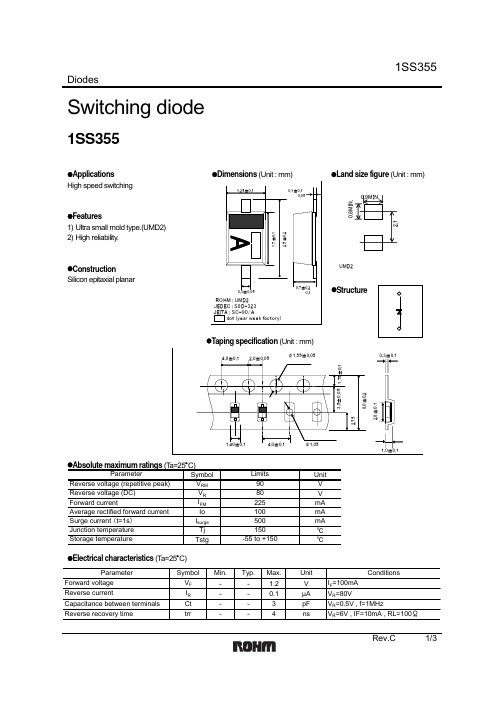

1SS355TE-17中文资料

D=1/2

15 AVE:9.4kV 10

Sin(θ=180)

0.1 0A 0V Io t T 0 VR D=t/T VR=40V Tj=150℃ 150

0.10

0A 0V Io t T VR D=t/T VR=40V Tj=150℃

0.05

0.05

5

AVE:2.4kV

1 0.001

0 0.01 1 10 100 TIME:t(s) Rth-t CHARACTERISTICS 0.1 1000 0 20 40 60 80 100 REVERSE VOLTAGE:VR(V) VR-PR CHARACTERISTICS 120

Rev.C

2/3

元器件交易网

1SS355

Diodes

0.2 DC AVERAGE RECTIFIED FORWARD CURRENT:Io(A) AVERAGE RECTIFIED FORWARD CURRENT:Io(A) 0.15

0.20

DC ELECTROSTATIC DDISCHARGE TEST ESD(KV)

20

0.15

The products listed in this document are designed to be used with ordinary electronic equipment or devices (such as audio visual equipment, office-automation equipment, communications devices, electrical appliances and electronic toys). Should you intend to use these products with equipment or devices which require an extremely high level of reliability and the malfunction of which would directly endanger human life (such as medical instruments, transportation equipment, aerospace machinery, nuclear-reactor controllers, fuel controllers and other safety devices), please be sure to consult with our sales representative in advance. It is our top priority to supply products with the utmost quality and reliability. However, there is always a chance of failure due to unexpected factors. Therefore, please take into account the derating characteristics and allow for sufficient safety features, such as extra margin, anti-flammability, and fail-safe measures when designing in order to prevent possible accidents that may result in bodily harm or fire caused by component failure. ROHM cannot be held responsible for any damages arising from the use of the products under conditions out of the range of the specifications or due to non-compliance with the NOTES specified in this catalog.

SG6841中文资料

GND

Green Mode Controller

Comp Comp

Slope Compensation 6V 2R R

6 SENSE 2 FB

©System General Corp.

-3-

Version 1.7 (IRO33.0001.B1)

JUL.25,2003

元器件交易网

-1-

Version 1.7 (IRO33.0001.B1)

JUL.25,2003

元器件交易网

High-integrated Green-mode PWM Controller

MARKING DIAGRAMS

8

SG6841T

XXXXXXXYYWWV

DESCRntegrated PWM controllers, SG6841 series, provides several features to enhance the performance of low power flyback converters. To minimize standby power consumption, the proprietary green-mode function provides off-time modulation to linearly decrease the switching frequency under light-load conditions. This green-mode function assists the power supply to easily meet the power conservation requirement. Due to BiCMOS process, the start-up current and operation current is reduced to 30uA and 3mA, respectively, to improve power conversion efficiency. Large start-up resistance can be used for further power saving. Built-in synchronized slope compensation ensures the stability of peak current mode control. A proprietary internal compensation ensures constant output power limit for universal AC input voltage from 90VAC to 264VAC.

SAE J775

SAE The Engineering SocietyFor Advancing MobilityLand Sea Air And Space SURFACE VEHICLE INFORMATION REPORTI N T E R N A T I O N A L400CommonwealthDrive. Warren dale. PA 15096-0001 SAEJ775REV.AUG93ISSUED 1961-06 Revised 1993-08-30 Superseding J775 JAN88ENGINE POPPET VALVE INFORMATION REPORTForeword-Poppet valves control combustion chamber induction and exhaust gas flow in reciprocating combustion engines. Poppet valves are manufactured from iron, nickel, titanium, and cobalt-base metallic alloys which are often welded together in various combinations.1.Scope and purpose- this specification supplies engineers and designers with:a.Poppet valve nomenclatureb.Poppet valve alloy designationsc.Chemical compositions of poppet valve alloysd. A guide to valve alloy metallurgy and heat treatmentse.General information on properties of valve alloysf. A guide to the application of valve alloysg. A description of valve design and construction, and their relation to valve alloy selectionh.Valve gear design considerations that affect valves2.References –There are no referenced publications specified herein.3.Valve nomenclature – Valve nomenclature and constructions are illustrated in Figures 1 to 54.Valve alloy designation4.1 UNS Designations – SAE, in conjunction with American Society for Testing and Material (ASTM), hasadopted the Unified Numbering System (UNS) for the identification of all metallic alloys. Tables 1A to 1E use UNS identification codes for valve alloys. These UNS numbers supersede the previous SAE functional numbering system, which is still included for reference purposes.SAE Technical Standards Board Rules provide that:” This report is published by SAE to advance the state of technical and engineering sciences. The use of this report is entirely voluntary, and its applicability and suitability for any particular use. Including any patent infringement arising there from, is the sole responsibility of the user”SAE reviews each technical report at least every five years at which time it may be reaffirmed, revised, or cancelled. SAE invites your written comments and suggestions.Copyright 1993 Society of Automotive Engineers. Inc.All rights reserved. Printed in U.S.A90-1202B EGCopyright by the SAE internationalCopyThe signyright by the SA majority of nificant usage AE internationa S f intake valv in spark igni FI al SAE J77ves for all a ition engine e IGURE 1-ON 75 Revise applications a exhaust valve NE-PIECE CO ed AUG9are one-piec es. ONSTRUCTI 93e constructio IONon which als s o hasCopyright by the SAE internationalWelded tip construction has significant usage in spark and compression ignition engine exhaust valvesFIGURE 2-WELDED TIP CONSTRUCTIONCopyright by the SAE internationalTwo-piece construction has significant usage in spark and compression ignition engine exhaust valveFIGURE 3-TWO-PIECE CONSTRUCTIONCopyright by the SAE internationalInternally-cooled construction is used in extreme duty truck, high performance, and aircraft spark ignition engine exhaust valves.FIGURE 4-INTERNALLY-COOLED CONSTRUCTIONCopyright by the SAE internationalWelded seat face construction predominates in compression ignition engine exhaust valves and has some usage in other valves. It supplements other types of valve construction.FIGURE 5-WELDED SEAT FACE CONSTRUCTIONCopyright by the SAE international Sun Apr 28 12:07:14 2002 TABLE 1A-CURRENT NORTH AMERICAN VALVE ALLOYS (MARTENSITIC STEELS)UNS NR/ ISO 683/15COMMERCIALFORMERSAEGRADEC MnP(max)S(max)Si Cr Ni W MoFe OtherH15410 1541H NV10.35/0.45 1.25/1.750.0400.0500.15/0.35 - - - - BaseG15470 1547 NV20.43/0.51 1.35/1.650.0400.050- - - - -BaseG31400 3140 NV40.38/0.430.70/0.900.0400.0400.15/0.35 0.55/0.75 1.10/1.40- - BaseG86450 8645 NV50.43/0.480.75/1.000.0350.0400.15/0.35 0.40/0.60 0.40/0.70- 0.15/0.25BaseH51500 5150H NV60.47/0.540.60/1.000.0350.0400.15/0.35 0.60/1.00 - - - BaseH41400 4140H NV70.37/0.440.65/1.100.0350.0400.15/0.35 0.75/1.20 - - 0.15/0.25BaseK14072 B16 0.36/0.440.45/0.700.0400.0400.15/0.35 0.80/1.15 - - 0.50/0.55Base V0.25/0.35GM-8440NV80.35/0.450.20/0.400.0300.040 3.60/4.20 1.85/2.50 0.25max- 0.10max Base Cu0.25max S65007/X45CrSi93Sil 1 HNV3 0.40/0.500.80max0.0400.030 2.70/3.30 8.00/10.000.60max- - BaseS65006 SilXB HNV60.75/0.900.80max0.0400.040 1.75/2.60 19.00/21.00 1.00/1.70- -BaseS42200 422SS HNV80.20/0.25 1.00max0.0400.0300.75max 11.00/12.500.50/1.000.75/1.250.75/1.25Base V 0.15/0.30 Cu 0.50 maxS64004 SUH11M 0.47/0.550.60max0.0300.030 1.00/2.00 7.50/9.50 0.60max- - Base All chemical contents are expressed in weight percent.Copyright by the SAE international Sun Apr 28 12:07:14 2002 TABLE 1B-CURRENT NORTH AMERICAN VALVE ALLOYS (SUPERALLOYS)UNS NR/ ISO 683/15 COMMERCIALFORMERSAEGRADEC MnP(max)S(max)Si Cr Ni N Fe OtherS63017 21-12NEV40.15/0.25 1.00/1.50 0.0450.0300.70/1.2520.00/22.0010.50/12.500.15/0.25-BaseS63008/X53CrMnNiN219 21-4N EV80.48/0.588.00/10.000.0500.0300.25max20.00/22.00 3.25/4.50 0.35/0.50BaseS63012 21-2NEV120.50/0.607.00/10.000.0500.0300.25max19.25/21.50 1.50/2.75 0.20/0.40Base S63013 GamanHEV130.47-0.5711.00/13.000.0300.050 2.00/3.0020.00/22.00- 0.40/0.50BaseS63018/X33CrMnNiNbN21923-8N EV160.28/0.38 1.50/3.500.0500.0300.50/1.0022.00/24.007.00/9.00 0.25/0.35BaseMo 0.50maxW 0.50 maxS30430 302HQEV170.10max 2.00max0.0450.030 1.00max17.00/19.008.00/10.00- Base Cu3.00/4.00S63019/X50CrMnNiNbN21921-4N+Nb+W XEV-F 0.45/0.558.00/10.000.0500.0300.45max20.00/22.00 3.50/5.50 0.40/0.60BaseW 0.80/1.50Nb+Ta 1.80/2.50All chemical contents are expressed in weight percent.Copyright by the SAE international Sun Apr 28 12:07:14 2002 TABLE 1C-CURRENT NORTH AMERICAN VALVE ALLOYS (AUSTENITIC STEELS)UNS NR/ ISO 683/15 COMMERCIALFORMERSAEGRADEC MnP(max)S(max)Si(max)Cr Ni Co Mo Fe OtherN07751/ NiCr15Fe7TiAl Inconel 751 HEV3 0.03/0.100.500.0150.0150.50 14.00/17.00Base 1.00max-0.50max 5.00/9.00Ti 2.00/2.60Al 1.10/1.35Nb+Ta 0.70/1.20Zr 0.04/0.10B 0.0015/0.009Cu 0.50 maxN07080/ NiCr20TiAl Nimonic80-AHEV5 0.04/0.10 1.000.0200.015 1.00 18.00/21.00Base 2.00max - 3.00maxB 0.008maxZr 0.04/0.10Ti 1.80/2.70Al 1.00/1.80Cr 0.20maxN07032 Pyromet31VHEV8 0.03/0.060.200.0150.0150.20 22.30/22.9055.00/58.00 1.00max 1.70/2.30BalanceTi 2.10/2.40Al 1.10/1.40Nb 0.70/1.00B 0.003/0.007Cu 0.50maxN07001 Waspaloy XEV-H0.03/0.10 1.000.0300.0300.75 18.00/21.00Base 12.00/15.00 3.50/5.00 2.00max Ti 2.75/3.25 Al 1.20/1.60 Zr 0.02/0.12 B 0.003/0.010 Cu 0.50maxCopyright by the SAE international Sun Apr 28 12:07:14 2002 TABLE 1D-CURRENT NORTH AMERICAN VALVE ALLOYS (AUSTENITIC STEELS)UNS NR COMMERCIAL FORMERSAEGRADECM n(max)P(max)S(max)Si Cr Ni Co W Mo FeOtherR30006 Stellite 6 VF2 0.90/1.401.000.0300.030 1.50m a x26.00/32.00 5.00m a x Base 3.50/5.50 1.50m a x 6.00max N06005 Eatonite VF3 2.00/2.750.500.0300.030 0.50/1.0027.00/31.00 Base 0.50mx8.00/9.50- 8.00max N06782 X-782 VF4 1.75/2.251.000.0300.030 0.50m a x25.00/27.00 Base 0.50max8.00/9.50- 4.00max R30002 Stellite F VF5 1.50/2.001.000.0300.030 0.80/1.5023.00/27.00 20.50/23.50Base 10.50/13.50 1.00m a x 6.00max R30001 Stellite 1 VF6 2.00/3.001.000.0300.030 0.40/2.0026.00/33.00 3.00max Base 11.00/14.00 1.00m a x 6.00max R30012 Stellite 12 VF7 110/1.701.000.0300.030 0.40/2.0026.00/33.00 3.00max Base 7.00/9.50 1.00m a x 3.00maxR30400TribaloyT-400VF8 0.08max- 0.0300.030 2.20/3.007.50/10.00 -61.00/63.00- 26.50/30.00-F e+N i3.00maxN06013 Eatonite 3 VF9 1.80/2.201.000.0300.030 0.80/1.2028.00/30.00 Base - - 4.00/6.00 1.00/8.00N06015 Eatonite 5 VF10 1.80/2.201.000.0300.030 0.80/1.2028.00/30.00 Base - - 7.00/9.00 1.00/8.00 VMS585 VF11 2.00/2.50- -- 0.80/1.3022.00/26.0010.00/12.00- -5.00/6.00BaseS68000 Eatonite 1.60/2.50 1.000.0250.0201.10/1.526.00/30.0015.00/18.00 - - 4.00/5.00BaseTribaloyT-8000.08max- 0.0300.030 3.00/3.8016.50/18.501.50m a x Base - 27.00/30.00 1.50max All chemical contents are expressed in weight percent.Copyright by the SAE international Sun Apr 28 12:07:14 2002 TABLE 1D-CURRENT NORTH AMERICAN VALVE ALLOYS (AUSTENITIC STEELS)UNS NR COMMERCIAL FORMERSAEGRADEC(max)Al V Zr Mo SnO(max)Fe(max)H(max)Y(max)TiOther(max)R56401 Ti6-4 XEV-J 0.10 5.25/6.75 3.35/4.65- --0.400.800.0200.005Base N0.10R54620 Ti6-2-4-2 0.05 5.50/6.50- 3.60/4.40 1.80/2.20 1.80/2.200.20 0.25 0.0150.005Base Si 0.20 N 0.07All chemical contents are expressed in weight percent.Copyright by the SAE international Sun Apr 28 12:07:14 2002TABLE 2A-ISO VALVE ALLOYSUNS NRISO 683/15CMnP(max)S (max)Si Cr Ni N W Mo Fe OtherS65007 X45CrSi93 040/0.500.80max 0.0400.030 2.7/3.3 8.0/10.0 0.60max - - - Base X50CrSi82 0.45/0.550.60max 0.0300.030 1.0/2.0 7.5/9.5 0.60max - --BaseX85CrMoV182 0.80/0.090 1.50max 0.0400.0301.0max16.5/18.5 - -- 2.0/2.5Base V 0.30/0.60S63008 X53CrMnNiN219 0.48/0.588.0/10.00.05 0.03 0.25max 20.0/22.0 3.25/4.50.35/0.45- - Base X55CrMnNiN219 0.50/0.607.0/10.00.0500.0300.25max 19.5/21.5 1.5/2.750.20/0.40- - BaseS63018 X33CrNiMnN238 0.28/0.38 1.5/3.50.0500.0300.50/1.0022.0/24.0 7.0/9.00.25/0.350.50nax 0.50maxBase S63019 X50CrMnNiNbN219 0.45/0.558.0/10.00.0500.0300.45max 20.0/22.0 3.5/5.50.40/0.600.80/1.50-Base Nb+Ta 1.80/2.50X53CrMnNiNbN219 0.48/0.588.0/10.00.0500.0300.45max20.0/22.03.25/4.50.38/0.50- - BaseC+N >0.90Nb+Ta 2.00/3.00N07080 NiCr20TiAl 0.04/0.10 1.0max 0.0200.015 1.0max 18.0/21.0 Base - - - 3.0max Al 1.0/1.8 Ti 1.8/2.7Co 2.0max Cu 0.2max B 0.008max N07751 NiCr15Fe7TiAl 0.03/0.100.50max 0.0150.0150.50max 14.0/17.0 Base - - 0.50max 5.0/9.0 Al 1.10/1.35Nb+Ta 0.70/1.20Ti 2.0/2.6 NiFe25Cr20NbTi 0.10max 1.0max 0.0300.015 1.0max 18.0/21.0 Base - - - 23.0/28.0Al 0.30/1.00 Nb+Ta 1.0/2.0 Ti 1.0/2.0 B 0.008maxCopyright by the SAE international Sun Apr 28 12:07:14 2002 TABLE 2-JIS HEAT RESISTING STEELS (VALVE ALLOYS)UNS NRJASOGRADEC MnP(max)S(max)Si Cr Ni Co W Mo Fe OtherR30001 CoCr1 2.00/3.00 1.0max - - 0.42/2.0026.0/33.0 3.00max Base11.00/14.00 1.00max 3.00max0.50maxR30006 CoCr6 0.90/1.40 1.0max - - 0.40/2.0026.0/32.0 3.00max Base 3.00/6.00 1.00max 3.00max0.50max R30012 CoCr12 1.20/1.70 1.00max - - 0.40/2.0026.0/33.0 3.00max Base7.00/9.50 1.00max 3.00max0.50maxUNS NRJISG4106GRADEC MnP(max)S(max)Si Cr Ni Co W Mo Fe OtherG15470 SMnC443 0.40/0.46 1.35/1.650.0300.0300.15/0.350.35/0.70- --- --UNS NRJISG4103GRADEC MnP(max)S(max)Si Cr Ni Co W Mo Fe OtherG86450 SNCM240 0.38/0.43 0.70/1.00 0.0300.030 0.15/0.350.40/0.65 0.40/0.70 - - 0.15/0.30-UNS NRJISG4311GRADEC MnP(max)S(max)Si Cr Ni Co W Mo Fe OtherS65007 SUH1 0.40/0.50 0.60max 0.0300.030 3.00/3.507.50/9.50 0.60max - - - -S65006 SUH4 0.75/0.85 0.20/0.60 0.0300.030 1.75/2.2519.00/20.50 1.15/1.65 - - - -S63008 SUH35 0.48/0.58 8.00/10.00 0.0400.030 0.35max20.00/22.00 3.25/4.50 - - - - N0.35/0.50S63017 SUH37 0.15/0.25 1.00/1.60 0.40 0.030 1.00max20.50/22.5010.00/12.00- - - -N0.15/0.30 S42200 SUH616 0.20/0.25 0.50/1.00 0.0400.030 0.50max11.00/13.00 0.50/1.00 - 0.75/1.25 0.75/1.25- V0.20/0.30All chemical contents expressed in weight percentCopyright by the SAE international Sun Apr 28 12:07:14 2002 TABLE 2C-JIS HEAT RESISTING STEELS (VALVE ALLOYS)UNS NRJISG4902GRADECMn(max)P(max)S(max)Si(max)Cr Ni Fe OtherN07080 NCF80A0.04/0.10 1.00 0.0300.015 1.00 18.00/21.00Base 1.50max Ti 1.80/2.70 Al 1.00/1.80 Cu 0.20maxNCF7510.10max 1.000.0300.015 0.50 14.00/17.0070.00min 5.00/9.00Ti 2.00/2.60Al 0.90/1.50 Nb+Ta 0.70/1.20 Cu 0.50 maxAll chemical contents expressed in weight percent.Copyright by the SAE international Sun Apr 28 12:07:14 2002TABLE 3-TYPICAL MECHANICAL PROPERTIES OF VALVE ALLOYSUNS NRISO 683/15SAE GRADETemperature℃Temperature℉TensileProperties Tensile Strength MPaTensile Properties Tensile Strength (ksi) Tensile Properties Yield Strength MPa Tensile Properties Yield Strength (ksi) Tensile Properties Elongation% Tensile Properties Reduction% Brinell Mutual Indentation BHN Hot Hardness Cold Ball 780℃ (1400℉)H15410 1541HRoom540 Room 1000 970 420 (141) (61) 910 330 (132) (48) - - 63 75 - - - - G154701547 Room Room 1240 (180) 1140 (165)- 40 - - G31400 3140 Room540650Room (1000) (1200)790 140 86(114) (21) (12.5)520 110 57(76) (16.1) (8.3)- - - - - - - - - - - - G864508645 Room Room 1240 (180) 1140 (165)- 40 - - H51500 5150H Room Room 990 (143) 910 (132) - 57 - - H41400 4140HRoom 540Room (1000) 900 500 (131) (72) 800 390 (116) (56) - - - - - - - - NV8 Room540650 Room (1000) (1200) 920 270 130 (134) (39) (18.2) 690 220 110 (100) (32) (16.1) - - - 53 44 97 - - - - - - S65007 X45CrSi93 HNV3 Room650760Room (1200) (1400)920 210 69(133) (31) (10)690 150 62(100) (22) (9)22 - -50 89 99- 63 31- - -Copyright by the SAE international Sun Apr 28 12:07:14 2002UNS NRISO 683/15SAE GRADETemperature℃Temperature℉TensileProperties Tensile Strength MPaTensile Properties Tensile Strength (ksi) Tensile Properties Yield Strength MPa Tensile Properties Yield Strength (ksi) Tensile Properties Elongation% Tensile Properties Reduction% Brinell Mutual Indentation BHN Hot Hardness Cold Ball 780℃ (1400℉)S65006 HNV6 Room650760Room (1200) (1400) 940 200 100 ((136) (29) (14.5) 840 160 75 (122) (23) (10.9) 15.5 - 72 10 62 80 - 85 40 - - 70 S42200 HNV8Room650Room (1200) 1030 360 (149) (52) 860 310 (125) (45) - - 52 83 - - - - S63017 EV4 Room650760 Room (1200) (1400) 820 420 300 (119) (61) (43) 430 230 220 (63) (34) (31) 26.2 - 13.3 20 18 18 - 100 80 - - 115 S63008 X53CrMnNiN219 EV8Room650 760 Room (1200) (1400) 1140 590 430 (166) (86) (62) 740 330 260 (107) (48) (37) - - 18 9 18 25 - 185 100 - - 193 S63012 EV13 Room650760 Room (1200) (1400) 1080 940 430 (157) (78) (62) 520 350 330 (75) (51) (48) - - - 5 49 22 - 220 130 - - - S63018 X33CrNiMnN238 EV16Room650 700 Room (1200) (1400) 1010 580 470 (147) (84) (68) 580 270 260 (84) (39) (37) - - - 33 32 30 - - - - - 190 S63019 X50CrMnNiNbN219 XEV-FRoom650 760Room (1200) (1400)1190 720 340(172) (105) (50)880 570 280(127) (82) (40)- - -6 8 13- - -- - -Copyright by the SAE international Sun Apr 28 12:07:14 2002UNS NRISO 683/15SAE GRADETemperature℃Temperature℉TensileProperties Tensile Strength MPaTensile Properties Tensile Strength (ksi) Tensile Properties Yield Strength MPa Tensile Properties Yield Strength (ksi) Tensile Properties Elongation% Tensile Properties Reduction% Brinell Mutual Indentation BHN Hot Hardness Cold Ball 780℃ (1400℉)N07751 NiCr15Fe7TiAl HEV3Room650 760 Room (1200) (1400) 1120 830 550 (162) (120) (80) 630 570 450 (92) (82) (65) - - 10 30 21 22 - 225 195 - - - N07080 NiCr20TiAl HEV5 Room650760 Room (1200) (1400) 1070 790 590 (155) (114) (86) 620 550 500 (90) (80) (73) 39 - - 38 17 20 - 200 150 - - - N07032 HEV8 Room650760Room (1200) (1400) 1300 1150 850 (189) (167) (123) 770 750 730 (112) (109) (106) - - - 45 15 23 - - - - - 227 N07001 XEV-HRoom650 Room (1200)1280 100(185) (145)1030 860(150) (125)- -15 12- -- 240These data are of unknown origin and their accuracy cannot be presumedThe data should be used only as a guidelineCopyright by the SAE international Sun Apr 28 12:07:14 2002TABLE 4-TYPICAL PHYSICAL PROPERTIES OF VALVE ALLOYSUNS NR ISO 683/15FORMER SAE GRADESpecific Gravity g/ccDensity Kg/m 3Density (1b/in 2)Coefficient of Thermal Expansion21 to 760℃ 1/℃×10-6Coefficient of Thermal Expansion (70 to 1400℉) (1/℉×10-6)S65007 X45CrSi93 HNV3 7.44 7442 0.27613.07.2 S65006 HNV6 7.42 7415 0.275 13.3 7.4 S42200 HNV8 7.55 7550 0.280 - - S63017 EV4 7.71 7712 0.286 18.5 10.30 S63008 X53CrMnNiN219EV8 7.60 7640 0.28218.4 10.25 S63012 EV12 7.63 7631 0.283 18.4 10.22 S63019 X50CrMnNiNbN219 XEV-F 7.87 7874 0.292 17.3 9.61 N07751 NiCr15Fe7TiAl HEV3 8.06 8062 0.299 14.9 8.30 N07080 NiCr20TiAl HEV5 8.06 8062 0.29914.98.30 N07032 HEV8 7.87 7874 0.292 15.7 8.73 R56401 XEV-J 4.34 4341 0.161 10.4 5.80 R546204.42 4422 0.164 9.75.40These data are of unknown origin and their accuracy cannot be presumed The data should be used only as a guidelineSAE J775 Revised AUG93Each UNS designation is a five-digit identification number preceded by a type identification prefix letter. Valve alloys have six identification prefixes:G- General purpose carbon and low alloy structural steelsH- Controlled harden ability and low alloy steelsK- Special purpose iron-base alloysN- Nickel-base alloysR- Cobalt, titanium, and other refractory alloysS- Stainless steels, heat-resistant steels, corrosion-resistant steels, and iron-base super alloysThe five-digit identification number often incorporates the most popular previous designation for the alloy. The UNS designations are controlled by individual SAE and ASTM committees which work in concert.4.2Obsolete SAE Functional Designation-The former SAE numbering system was based on thetype of valve for which the material was commonly used. Numbers were assigned on the following bases:a.Letter Prefix-Intake valves may be made of carbon, low alloy, or heat and corrosionresistant high-alloy steels. The prefix NV designated carbon and low alloy intake valve steels. HNV designated high alloy intake valve steels.Exhaust valves may be made of harden able martensitic steels, austenitic steels, or superalloys. Alloys used for exhaust valves may be iron, nickel, or cobalt-base alloys. The prefix letters EV designated austenitic exhaust valve steels. The letters HEV were used for high strength exhaust valve alloys in severe spark and compression ignition engine service.The prefix VF designated high alloy valve seat facing overlays used at critical points of wear or corrosion.The prefix X designated experimental and limited usage alloys preceding a conventional prefix, such as XEV.b.Number Suffix-A number was arbitrarily assigned, based on the order in which the alloywas codified.4.3Other designations-Tables 2A to 2C list other important national and international valve alloys,together with their specific chemistries.5.Valve Alloy Chemical Compositions5.1 General-There are many overlapping and conflicting specifications for the chemical compositions of valve alloys. This specification adopts the ISO chemical compositions from their Regulation 683/15. Unfortunately, a number of alloys in common use are not listed in this regulation, so lowest common denominator compositions, conforming with most specifications in common usage, were developed.5.2 UNS(SAE) Compositions-The compositions of other international valve alloys are listed in Tables 2A to 2C.Copyright by the SAE internationalSAE J775 Revised AUG936.Valve Alloy Metallurgy and Heat Treatment6.1 General-The performance characteristics of a valve alloy are a cross product of composition andheat treatment. Alloy selection depends upon stresses, corrosive agent, and temperaturesencountered in service, as well as the economic and durability objectives. Heat treatments used to improve the mechanical properties of valves depend upon the specific alloy, economics, and the level of properties desired. They can be general or selective, and it is not uncommon for a single valve to be subjective to two or more heat treatments in different locations.6.2 Martensitic Alloys-Pain carbon, low alloy, and high alloy martensitic steels are primarily usedfor intake. Extreme duty martensitic steels generally have the highest carbon and alloy content to resist wear, to resist seat face indention by deposits, and to provide increased strength.Elements such as chromium and silicon are added when increased oxidation or corrosionresistance is needed. Manganese and nickel are added as strengthening agents. Occasionally, refractory elements, such as molybdenum, tungsten, and vanadium are used to enhance certain elevated temperature properties.Martensitic valves are most often quench hardened and tempered to hardness readings in the 25 to 45 Rockwell “C” scale range. This is a compromise among good strength, adequate ductility, impact performance, and wear resistance along stem. In some less demanding applications, martensitic valves can be used in the annealed condition.Tips and seats are often selectively hardened to create high hardness and wear resistant surface.These surfaces are selectively hardened, generally to the greatest hardness practical for the alloy. Tip hardening may extend beyond the keeper groove to improve the fatigue strength and the wear resistance of this region.6.3 Austenitic Alloys-Austenitic alloys have a face-centered cubic crystal structure which is termedaustenite. The elements that stabilize the austenitic structure are carbon, manganese, nickel, copper, and nitrogen. Chromium, silicon, and sometimes, aluminum are added for oxidation or corrosion resistance. Refractory elements such as molybdenum, niobium, tantalum, tungsten, and vanadium may be added for high temperature strength. There alloys are termed steels when the base elements is iron. The cobalt and nickel-base austenitic base superalloys are hardened by precipitation of aluminum, nickel, niobium, tantalum, and titanium in the form of intermetallic compounds. The may be used in either wrought or cast form, although cast valves arediminishing in commercial importance.Austenitic valve alloys may be as simple in composition as 18-8 stainless steels, or ascomplicated as gas turbine alloys. The selection is strongly influenced by economicconsiderations, as well as mechanical, physical, and chemical attributes required satisfying specific engine requirements.Mechanical properties are improved in austenitic valve alloys precipitation hardening or strain hardening, rather than the martensitic transformation hardening of low alloy steels. The most Copyright by the SAE internationalcommon austenitic alloy hardening process are:a.High temperature forging followed by aging heat treatment(s)b.High temperature forging followed by a solution treatment and then aging heat treatmentc.Cold formingIn lower temperature applications, austenitic engine valves are frequently used in the forged and aged condition. More severe and higher temperature service generally requires solutiontreatment followed by one or more aging treatments. These operation produce hardness reading in the 20 to 40 Rockwell “C” scales range. The hardness developed depends upon the capability of the individual alloy. These alloys develop fatigue, creep, wear, and seat face indentation resistance from the heat treatments. The cold formed austenitic alloys (302HQ) are often in small light-duty engines.6.4 Titanium Alloys-Titanium alloys can be divided into three categories: alpha, alpha-beta, andbeta alloys. Alpha alloys have a close-packed hexagonal structure, beta alloys have abody-centered cubic structure, and alpha-beta alloys have mixtures of the two differentstructures. The alloying elements that stabilize the alpha structure include oxygen, nitrogen, aluminum, and carton. Alloying elements that stabilize the beta structure included vanadium and molybdenum. Zirconium and tin have minor effects upon phase stability, but are widely used as solid-solution strengtheners in both alpha and beta alloys.Most titanium intake valves are made from alpha-beta alloys which have superior lowtemperature strength. Exhaust valves are generally manufactured from alpha or near alpha alloys because they have better high temperature creep properties. Beta alloys have not been used in any engine valve applications of consequence.Titanium alloy heat treatments for engine valve applications are less established than the heat treatments for high volume production alloys. Most titanium alloys used in engine valves are precipitation harden able and receive some type of solution treatment and aging after forming.It is important to note that the development of titanium alloy engine valves has been primarily for high performance applications where extended durability is not a primary concern. Heat treatment procedures and precision are believed to be critical parameters in long-term titanium valve durability.Titanium aluminizes are being investigated on an experimental basis for passenger car exhaust valve applications.6.5 Ceramic materials-Although not yet used in any commercial applications, ceramic materials arebeing investigated for high temperature valve service. The primary material being investigated for this application is Si3N4. Much experimentation has been done to develop plasma sprayed cermets, but these are being used only on a limited basis.6.6 Seat Facing Alloys-Seat facing alloys are composed of hard precipitates in cobalt, nickel, or Copyright by the SAE internationaliron-base austenitic matrices. The hard precipitates are generally chromium, molybdenum, tungsten, or vanadium carbides. Some compositions use intermetallic compounds, such as Laves phase, as the hard precipitates. Chromium is added to the matrix to increase corrosionresistance. Silicon additions proved the fluidity necessary for welding the facing to the valve seat and can improve wear resistance.Seat facing alloys derive their wear resistance from the volume fraction of precipitates which possess great hot hardness and compressive strength. A significant portion of the adhesive wear resistance in these seat facing alloys, as well as other high chromium alloys, is derived from the tenacious chromium oxide layer formed on the wear surface by oxidation during service. When extremely severe conditions of corrosion are encountered such as those which occur whensulfur-containing fuels are used, cobalt or iron-base hard-facing alloys may be required to assure valve seat durability.Selection of a particular seat facing alloy usually depends upon temperatures, stresses, and corrodents encountered in service. Manufacturing considerations may preclude some seat facing alloy/valve head alloy combinations.7.Valve alloy physical and mechanical properties7.1 General-No single property can define the varying conditions encountered in different internalcombustion engines. Spark and compression ignition engines place different demands on engine valves, so the properties of interest vary.Common causes of valve failures include:a.Adhesive or abrasive wear(1)Of the stem surface(2)Of the seat surface(3)Of the tip surfaceb.General or Localized Corrosion(1)Primarily at elevated temperatures(2)Often combined with fatiguec.Fatigue(1)Head radial cracking by thermal fatigue(2)Head chordal cracking by mechanical fatigue(3)Fillet transverse cracking by mechanical fatigue(4)Keeper groove transverse cracking by mechanical fatigue(5)Often assisted by corrosion7.2 Wear properties-The wear resistance of valve materials cannot be adequately assessed by asingle type of wear or mechanical property test because of the different modes of wearencountered at different locations on the valve. Often a secondary mode of wear can be initiated Copyright by the SAE international。

士兰微电子 SDH7753 非隔离降压型LED恒流驱动芯片说明书

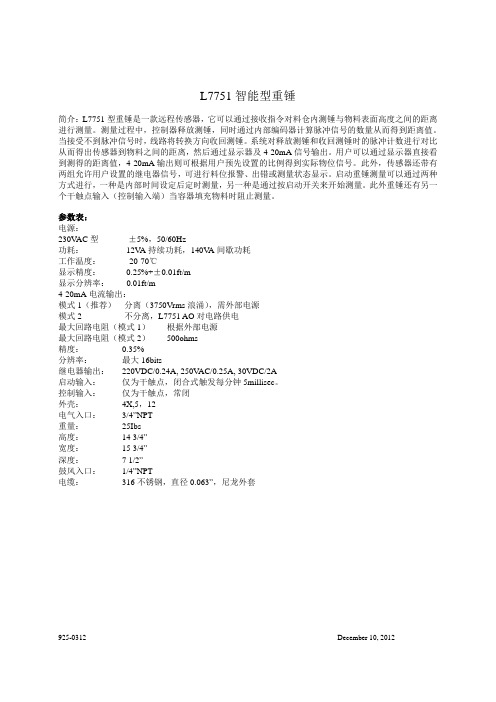

SDH7753说明书非隔离降压型LED 恒流驱动芯片描述SDH7753是一款高精度LED 恒流驱动控制芯片,适用于85VAC~265VAC 全范围交流输入电压的非隔离降压型LED 恒流电源系统。

SDH7753集成500V 高压功率MOS ,内置高压供电电路,无需启动电阻和辅助绕组即能实现芯片的自主供电,同时更省去了传统的外置电源电容,在加快系统启动的同时又极大地节省了系统成本。

SDH7753工作在电感电流临界导通模式,芯片采用特有的高精度电流采样技术,结合内部补偿,能获得高恒流精度和优异的线性/负载调整率。

SDH7753内部集成多种保护功能,包括输出短路保护、逐周期过流保护、过热调节、采样电阻开路保护等,增强了系统的安全性和可靠性。

特性♦ 内置500V 高压功率MOSFET ♦ 集成高压供电功能,无需外部电源电容 ♦ 精确恒定电流(<±3%)供给LED ♦ 输出短路保护 ♦ 过热调节功能♦ 逐周期过电流保护 ♦无辅助绕组应用♦ 球泡灯 ♦ 筒灯♦其他LED 照明应用产品规格分类内部框图CSGND极限参数=25°C)电气参数(除非特别说明,HV=30V,Tamb参数名称符号测试条件最小值典型值最大值单位电源芯片内部工作电压VCC V CC 6.8 V 工作电流I OP VH=30V 55 100 145 μA 电流采样电流检测阈值V cs_TH582 600 618 mV参数名称符号 测试条件最小值典型值 最大值单位芯片关断延时 T_DELAY200ns控制时间参数 最大导通时间 T ON,MAX 45 60 75 μs 前沿消隐时间 T LEB 0.5 μs 最大关断时间 T OFF,MAX 300 400 500 μs 最小关断时间 T OFF,MIN2.5μs功率管 导通电阻 R ON12 Ω 漏源击穿电压 BV DSSV GS =0V, I D =50uA500V温度特性 过热调节 T REG -- 140 -- °C 过温保护 T SD -- 160 -- °C 过温解除T RECOVERY--145--°C管脚排列图管脚描述管脚编号管脚名称I/O功能描述SDH7753SSDH7753J1 2 HV I 高压供电端 2~3 NC N 悬空4 4 CS O 采样脚、电流输出 5~6 3 GND G 地 71DRAINIMOS 漏端功能描述SDH7753是一款利用BUCK原理搭建的非隔离LED恒流驱动芯片,单芯片集成了500V高压功率MOSFET和高压启动电路。

HT78XX中文资料