EEVHD1A331P中文资料

HDSP-3351中文资料

Features• Low Power Consumption • Industry Standard Size• Industry Standard Pinout • Choice of Character Size7.6 mm (0.30 in), 10 mm (0.40 in), 10.9 mm (0.43 in), 14.2 mm (0.56 in), 20 mm (0.80 in)• Choice of ColorsAlGaAs Red, High Efficiency Red (HER), Yellow, Green• Excellent Appearance Evenly Lighted Segments±50° Viewing Angle• Design FlexibilityCommon Anode or Common CathodeSingle and Dual DigitLeft and Right Hand Decimal Points±1. Overflow Character• Categorized for Luminous IntensityYellow and Green Categorized for ColorUse of Like Categories Yields a Uniform Display• Excellent for Long Digit String Multiplexing DescriptionThese low current seven segment displays are designed for applica-tions requiring low power consumption. They are tested and selected for their excellent low current characteristics to ensure that the segments are matched at low currents. Drive currents as low as 1 mA per segment are available.Pin for pin equivalent displays are also available in a standard current or high light ambient design. The standard current displays are available in all colors and are ideal for most applica-tions. The high light ambient displays are ideal for sunlight ambients or long string lengths. For additional information see the 7.6 mm Micro Bright Seven Segment Displays, 10 mm Seven Segment Displays, 7.6 mm/10.9 mm Seven Segment Displays, 14.2 mm Seven Segment Displays, 20 mm Seven Segment Displays, or High Light Ambient Seven Segment Displays data sheets.Low Current Seven SegmentDisplays Technical Data HDSP-335x SeriesHDSP-555x SeriesHDSP-751x SeriesHDSP-A10x Series HDSP-A80x Series HDSP-A90x Series HDSP-E10x Series HDSP-F10x Series HDSP-G10x Series HDSP-H10x Series HDSP-K12x, K70x Series HDSP-N10x SeriesHDSP-N40x SeriesDevicesAlGaAs HER Yellow Green Package HDSP-HDSP-HDSP-HDSP-Description Drawing A1017511A801A9017.6 mm Common Anode Right Hand Decimal A A1037513A803A9037.6 mm Common Cathode Right Hand Decimal B A1077517A807A9077.6 mm Common Anode ±1. Overflow C A1087518A808A9087.6 mm Common Cathode ±1. Overflow D F10110 mm Common Anode Right Hand Decimal E F10310 mm Common Cathode Right Hand Decimal F F10710 mm Common Anode ±1. Overflow G F10810 mm Common Cathode ±1. Overflow H G10110 mm Two Digit Common Anode Right Hand Decimal X G10310 mm Two Digit Common Cathode Right Hand Decimal Y E100335010.9 mm Common Anode Left Hand Decimal I E101335110.9 mm Common Anode Right Hand Decimal J E103335310.9 mm Common Cathode Right Hand Decimal K E106335610.9 mm Universal ±1. Overflow[1]L H101555114.2 mm Common Anode Right Hand Decimal M H103555314.2 mm Common Cathode Right Hand Decimal N H107555714.2 mm Common Anode ±1. Overflow O H108555814.2 mm Common Cathode ±1. Overflow P K121K70114.2 mm Two Digit Common Anode Right Hand Decimal R K123K70314.2 mm Two Digit Common Cathode Right Hand Decimal S N10020 mm Common Anode Left Hand Decimal Q N101N40120 mm Common Anode Right Hand Decimal T N103N40320 mm Common Cathode Right Hand Decimal U N10520 mm Common Cathode Left Hand Decimal V N106N40620 mm Universal ±1. Overflow[1]W Note:1. Universal pinout brings the anode and cathode of each segment’s LED out to separate pins. See internal diagrams L or W.Part Numbering System5082-x xx x-x x x xxHDSP-x xx x-x x x xxMechanical Options[1]00: No mechanical optionColor Bin Options[1,2]0: No color bin limitationMaximum Intensity Bin[1,2]0: No maximum intensity bin limitationMinimum Intensity Bin[1,2]0: No minimum intensity bin limitationDevice Configuration/Color[1]G: GreenDevice Specific Configuration[1]Refer to respective datasheetPackage[1]Refer to Respective datasheetNotes:1. For codes not listed in the figure above, please refer to the respective datasheet or contact your nearest Agilent representative fordetails.2. Bin options refer to shippable bins for a part-number. Color and Intensity Bins are typically restricted to 1 bin per tube (excep-tions may apply). Please refer to respective datasheet for specific bin limit information.Package DimensionsPackage Dimensions (cont.)Package Dimensions (cont.)*The Side View of package indicates Country of Origin.Package Dimensions (cont.)Package Dimensions (cont.)Package Dimensions (cont.)Internal Circuit DiagramInternal Circuit Diagram (cont.)Absolute Maximum RatingsAlGaAs Red - HDSP-HERA10X/E10X/H10X HDSP-751X/Yellow GreenK12X/N10X/N40X335X/555X/HDSP-A80X HDSP-A90X Description F10X, G10X Series K70X Series Series Series Units Average Power per Segment or DP375264mW Peak Forward Current per 45mA Segment or DPDC Forward Current per15[1]15[2]mA Segment or DPOperating Temperature Range-20 to +100-40 to +100°C Storage Temperature Range -55 to +100°C Reverse Voltage per Segment 3.0V or DPWave Soldering Temperature for 3Seconds (1.60 mm [0.063 in.] below 250°C seating body)Notes:1. Derate above 91°C at 0.53 mA/°C.2. Derate HER/Yellow above 80°C at 0.38 mA/°C and Green above 71°C at 0.31 mA/°C.Electrical/Optical Characteristics at T A = 25°CAlGaAs RedDeviceSeriesHDSP-Parameter Symbol Min.Typ.Max.Units Test Conditions315600I F = 1 mA A10x3600I F = 5 mA330650I F = 1 mAF10x, G10x3900I F = 5 mA390650I F = 1 mA E10x Luminous Intensity/Segment[1,2]I Vµcd(Digit Average)3900I F = 5 mA400700I F = 1 mAH10x, K12x4200I F = 5 mA270590I F = 1 mAN10x, N40x3500I F = 5 mA1.6I F = 1 mAForward Voltage/Segment or DP V F 1.7V I F = 5 mA1.82.2I F = 20 mA PkAll Devices Peak WavelengthλPEAK645nmDominant Wavelength[3]λd637nmReverse Voltage/Segment or DP[4]V R 3.015V I R = 100 µATemperature Coefficient of∆V F/°C-2 mV mV/°CV F/Segment or DPA10x255F10x, G10x320E10x340Thermal Resistance LED RθJ-PIN°C/W/SegH10x, K12x Junction-to-Pin400N10x, N40x430High Efficiency RedDeviceSeriesHDSP-Parameter Symbol Min.Typ.Max.Units Test Conditions160270I F = 2 mA 751x1050I F = 5 mA200300I F = 2 mA Luminous Intensity/Segment[1,2]I V mcd(Digit Average)1200I F = 5 mA335x, 555x,K70x270370I F = 2 mA1480I F = 5 mA1.6I F = 2 mAForward Voltage/Segment or DP V F 1.7V I F = 5 mA2.1 2.5I F = 20 mA Pk All Devices Peak WavelengthλPEAK635nmDominant Wavelength[3]λd626nmReverse Voltage/Segment or DP[4]V R 3.030V I R = 100 µATemperature Coefficient of∆V F/°C-2mV/°CV F/Segment or DP751x200335x Thermal Resistance LED RθJ-PIN280°C/WJunction-to-Pin555x, K70x345YellowDeviceSeriesHDSP-Parameter Symbol Min.Typ.Max.Units Test Conditions Luminous Intensity/Segment[1,2]250420I F = 4 mA(Digit Average)I V mcd1300I F = 10 mA1.7I F = 4 mAForward Voltage/Segment or DP V F 1.8V I F = 5 mA A80x2.1 2.5I F = 20 mA PkPeak WavelengthλPEAK583nmDominant Wavelength[3,5]λd581.5585592.5nmReverse Voltage/Segment or DP[4]V R 3.030V I R = 100 µATemperature Coefficient of∆V F/°C-2mV/°CV F/Segment or DPThermal Resistance LED RθJ-PIN200°C/WJunction-to-PinGreenDeviceSeriesHDSP-Parameter Symbol Min.Typ.Max.Units Test Conditions Luminous Intensity/Segment[1,2]250475I F = 4 mA(Digit Average)I V mcd1500I F = 10 mA1.9I F = 4 mAForward Voltage/Segment or DP V F 2.0V I F = 10 mA A90x2.1 2.5I F = 20 mA PkPeak WavelengthλPEAK566nmDominant Wavelength[3,5]λd571577nmReverse Voltage/Segment or DP[4]V R 3.030V I R = 100 µATemperature Coefficient of∆V F/°C-2mV/°CV F/Segment or DPThermal Resistance LED RθJ-PIN200°C/WJunction-to-PinNotes:1. Device case temperature is 25°C prior to the intensity measurement.2. The digits are categorized for luminous intensity. The intensity category is designated by a letter on the side of the package.3. The dominant wavelength, λd, is derived from the CIE chromaticity diagram and is the single wavelength which defines the color of thedevice.4. Typical specification for reference only. Do not exceed absolute maximum ratings.5. The yellow (HDSP-A800) and Green (HDSP-A900) displays are categorized for dominant wavelength. The category is designated by anumber adjacent to the luminous intensity category letter.AlGaAs RedIntensity Bin Limits (mcd)AlGaAs RedHDSP-A10xIV Bin Category Min.Max.E0.3150.520F0.4280.759G0.621 1.16H0.945 1.71I 1.40 2.56J 2.10 3.84K 3.14 5.75L 4.708.55HDSP-E10x/F10x/G10xIV Bin Category Min.Max.D0.3910.650E0.5320.923F0.755 1.39G 1.13 2.08H 1.70 3.14HDSP-H10x/K12xIV Bin Category Min.Max.C0.4150.690D0.5650.990E0.810 1.50F 1.20 2.20G 1.80 3.30H 2.73 5.00I 4.097.50HDSP-N10xIV Bin Category Min.Max.A0.2700.400B0.3250.500C0.4150.690D0.5650.990E0.810 1.50F 1.20 2.20G 1.80 3.30H 2.73 5.00I 4.097.50Intensity Bin Limits (mcd), continued HERHDSP-751xIV Bin Category Min.Max.B0.1600.240C0.2000.300D0.2500.385E0.3150.520F0.4280.759G0.621 1.16HDSP-751xIV Bin Category Min.Max.B0.2400.366C0.3000.477D0.3910.650E0.5320.923F0.755 1.39G 1.13 2.08H 1.70 3.14HDSP-555x/K70xIV Bin Category Min.Max.A0.2700.400B0.3250.500C0.4150.690D0.5650.990E0.810 1.50F 1.20 2.20G 1.80 3.30H 2.73 5.00I 4.097.50Intensity Bin Limits (mcd), continued YellowHDSP-A80xIV Bin Category Min.Max.D0.2500.385E0.3150.520F0.4250.760G0.625 1.14H0.940 1.70I 1.40 2.56J 2.10 3.84K 3.14 5.76L 4.718.64M7.0713.00N10.6019.40O15.9029.20P23.9043.80Q35.8065.60GreenHDSP-A90xIV Bin Category Min.Max.E0.3150.520F0.4250.760G0.625 1.14H0.940 1.70I 1.40 2.56J 2.10 3.84K 3.14 5.76L 4.718.64M7.0713.00N10.6019.40O15.9029.20P23.9043.80Q35.8065.60Electrical/OpticalFor more information on electrical/optical characteristics, please see Application Note 1005.Contrast Enhancement For information on contrast enhancement, please see Application Note 1015.Soldering/Cleaning Cleaning agents from the ketone family (acetone, methyl ethyl ketone, etc.) and from the chorinated hydrocarbon family (methylene chloride, trichloro-ethylene, carbon tetrachloride, etc.) are not recommended for cleaning LED parts. All of these various solvents attack or dissolve the encapsulating epoxies used to form the package of plastic LED parts.For information on soldering LEDs, please refer to Application Note 1027.Note:All categories are established for classification of products. Productsmay not be available in all categories. Please contact your localAgilent representatives for further clarification/information.Color Categories/semiconductorsFor product information and a complete list ofdistributors, please go to our web site.For technical assistance call:Americas/Canada: +1 (800) 235-0312 or(916) 788 6763Europe: +49 (0) 6441 92460China: 10800 650 0017Hong Kong: (+65) 6271 2451India, Australia, New Zealand: (+65) 6271 2394Japan: (+81 3) 3335-8152(Domestic/International), or0120-61-1280(Domestic Only)Korea: (+65) 6271 2194Malaysia, Singapore: (+65) 6271 2054Taiwan: (+65) 6271 2654Data subject to change.Copyright © 2005 Agilent Technologies, Inc.Obsoletes 5988-8412ENJanuary 19, 20055989-0080EN。

单片机内的Flash与EEPROM作用及区别

单片机运行时的数据都存在于RAM(随机存储器)中,在掉电后RA M 中的数据是无法保留的,那么怎样使数据在掉电后不丢失呢?这就需要使用EEPR OM或F LASHR OM 等存储器来实现。

在传统的单片机系统中,一般是在片外扩展存储器,单片机与存储器之间通过IIC或SPI等接口来进行数据通信。

这样不光会增加开发成本,同时在程序开发上也要花更多的心思。

在ST C 单片机中内置了E EPROM(其实是采用IAP技术读写内部FLAS H 来实现EEPR OM),这样就节省了片外资源,使用起来也更加方便。

下面就详细介绍STC单片机内置EEP ROM 及其使用方法。

f lash是用来放程序的,可以称之为程序存储器,可以擦出写入但是基本都是整个扇区进行的.一般来说单片机里的f lash都用于存放运行代码,在运行过程中不能改;EEPR OM是用来保存用户数据,运行过程中可以改变,比如一个时钟的闹铃时间初始化设定为12:00,后来在运行中改为6:00,这是保存在EE PROM里,不怕掉电,就算重新上电也不需要重新调整到6:00下面是网上详细的说法,感觉不错:F LASH和EEPR OM的最大区别是FL ASH按扇区操作,E EPROM则按字节操作,二者寻址方法不同,存储单元的结构也不同,FLA SH的电路结构较简单,同样容量占芯片面积较小,成本自然比EE PROM低,因而适合用作程序存储器,EE PROM则更多的用作非易失的数据存储器。

当然用FL ASH做数据存储器也行,但操作比EEPR OM麻烦的多,所以更“人性化”的MCU设计会集成F LASH和EEPRO M两种非易失性存储器,而廉价型设计往往只有 FLA SH,早期可电擦写型MCU则都是EEPR M结构,现在已基本上停产了。

XP143 Specification-Chinese

种类 Side

Side

Side

Side

Side

Side

121212121212

供料平台

MFU-X10E 固定

○○○

○○○

○○○

废料带切刀

○○○

○○○Leabharlann 废料带BOX○○○

○○○

LCD触摸屏

○○○

○○○

○○○

对应AA模式

△

吸嘴自动更换器

△

△

△

△

△

△

对应BGA,CSP

△

△

△

真空支撑销

△

△

△

△

△

△

软件版本更新

IEC规格※4,UL规格,CE标记

※1.电源:可以选择200,210,220,230,380,400,415,460,480V (变压器组的插座切换方式) 为了避开杂讯、电压波动、高频失真等的影响,避免与其他机器共用,推荐使用专用的电源。

※2.气源应该在大气压露点:-17℃ 以下、微粉尘:粒径5μm以下、油的最高浓度:5mg/m3以下。 ※3.湿度是保持不结露。此外,本公司推介的环境条件是,温度15℃~30℃以及湿度50%~70%。 ※4.IP22:对应IEC规格(对于人体、固体杂物以及水的浸入的保护)

-3-

XP143-020505RS

1. 概 要

1.2.4 丰富的吸嘴配置

1) 小芯片专用的吸嘴配置例 在吸嘴尺寸φ0.37~φ2.5mm的配置上,可以吸取12个4532尺寸以内的元件 进行贴装。

φ0 .7 φ1 .0 φ1 .3 φ1 .8 φ2 .5

2) 贴装小芯片/中型元件的吸嘴配置例

吸取8个4532以内的元件贴装,贴装小芯片后,吸取4个超过4532 □10mm以内的元件进行贴装。

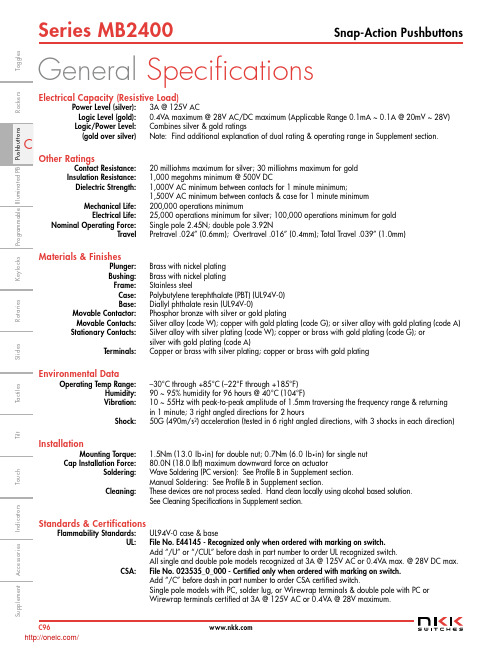

MB2411E1W01;MB2411E1W03;MB2411E1G01;MB2411S1W01;MB2411E1W03-FA;中文规格书,Datasheet资料

A

Rated 3A @ 125V AC & 0.4VA max @ 28V

Power Level (silver): 3A @ 125V AC Logic Level (gold): 0.4VA maximum @ 28V AC/DC maximum (Applicable Range 0.1mA ~ 0.1A @ 20mV ~ 28V)

Logic/Power Level: Combines silver & gold ratings (gold over silver) Note: Find additional explanation of dual rating & operating range in Supplement section.

To g g l e s

Rockers

Keylocks Programmable Illuminated PB Pushbuttons

Rotaries

Series MB2400

Snap-Action Pushbuttons

General Specifications

Electrical Capacity (Resistive Load)

Slides

Ta c t i l e s

Tilt

To u c h

Supplement Accessories Indicators

C96 /

w w

To g g l e s

Rockers

Keylocks Programmable Illuminated PB Pushbuttons

TYPICAL SWITCH ORDERING EXAMPLE

MB24 11 E1 W 01 F A

ATMEGA324P中文资料

(PCINT13/MOSI) PB5 (PCINT14/MISO) PB6

(PCINT15/SCK) PB7 RESET VCC GND XTAL2 XTAL1

(PCINT24/RXD0) PD0 (PCINT25/TXD0) PD1 (PCINT26/RXD1/INT0) PD2

PA4 (ADC4/PCINT4) PA5 (ADC5/PCINT5) PA6 (ADC6/PCINT6) PA7 (ADC7/PCINT7) AREF GND AVCC PC7 (TOSC2/PCINT23) PC6 (TOSC1/PCINT22) PC5 (TDI/PCINT21) PC4 (TDO/PCINT20)

PA0 (ADC0/PCINT0) PA1 (ADC1/PCINT1) PA2 (ADC2/PCINT2) PA3 (ADC3/PCINT3) PA4 (ADC4/PCINT4) PA5 (ADC5/PCINT5) PA6 (ADC6/PCINT6) PA7 (ADC7/PCINT7) AREF GND AVCC PC7 (TOSC2/PCINT23) PC6 (TOSC1/PCINT22) PC5 (TDI/PCINT21) PC4 (TDO/PCINT20) PC3 (TMS/PCINT19) PC2 (TCK/PCINT18) PC1 (SDA/PCINT17) PC0 (SCL/PCINT16) PD7 (OC2A/PCINT31)

Endurance: 10,000 Write/Erase Cycles – Optional Boot Code Section with Independent Lock Bits

In-System Programming by On-chip Boot Program True Read-While-Write Operation – 512B/1K/2K Bytes EEPROM Endurance: 100,000 Write/Erase Cycles – 1/2/4K Bytes Internal SRAM – Programming Lock for Software Security • JTAG (IEEE std. 1149.1 Compliant) Interface – Boundary-scan Capabilities According to the JTAG Standard – Extensive On-chip Debug Support – Programming of Flash, EEPROM, Fuses, and Lock Bits through the JTAG Interface • Peripheral Features – Two 8-bit Timer/Counters with Separate Prescalers and Compare Modes – One 16-bit Timer/Counter with Separate Prescaler, Compare Mode, and Capture Mode – Real Time Counter with Separate Oscillator – Six PWM Channels – 8-channel, 10-bit ADC Differential mode with selectable gain at 1x, 10x or 200x – Byte-oriented Two-wire Serial Interface – Two Programmable Serial USART – Master/Slave SPI Serial Interface – Programmable Watchdog Timer with Separate On-chip Oscillator – On-chip Analog Comparator – Interrupt and Wake-up on Pin Change • Special Microcontroller Features – Power-on Reset and Programmable Brown-out Detection – Internal Calibrated RC Oscillator – External and Internal Interrupt Sources – Six Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, Standby and Extended Standby • I/O and Packages – 32 Programmable I/O Lines – 40-pin PDIP, 44-lead TQFP, and 44-pad QFN/MLF • Operating Voltages – 1.8 - 5.5V for ATmega164P/324P/644PV – 2.7 - 5.5V for ATmega164P/324P/644P • Speed Grades – ATmega164P/324P/644PV: 0 - 4MHz @ 1.8 - 5.5V, 0 - 10MHz @ 2.7 - 5.5V – ATmega164P/324P/644P: 0 - 10MHz @ 2.7 - 5.5V, 0 - 20MHz @ 4.5 - 5.5V • Power Consumption at 1 MHz, 1.8V, 25°C for ATmega164P/324P/644P – Active: 338/398/TBD µA – Power-down Mode:0.035 /0.027/TBD µA – Power-save Mode:0.5 /0.5/TBD µA (Including 32 kHz RTC)

M38B51EEXXXFP资料

Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.Note : Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.Renesas Technology Corp.Customer Support Dept.April 1, 2003To all our customers元器件交易网DESCRIPTIONThe 38B5 group is the 8-bit microcomputer based on the 740 familycore technology.The 38B5 group has six 8-bit timers, a 16-bit timer, a fluorescent display automatic display circuit, 12-channel 10-bit A-D converter, a serial I/O with automatic transfer function, which are available for controlling musical instruments and household appliances.The 38B5 group has variations of internal memory size and packag-ing. For details, refer to the section on part numbering.For details on availability of microcomputers in the 38B5 group, refer to the section on group expansion.MITSUBISHI MICROCOMPUTERS38B5 GroupSINGLE-CHIP 8-BIT CMOS MICROCOMPUTERFEATURES•Basic machine-language instructions .......................................71•The minimum instruction execution time ..........................0.48 µs (at 4.19 MHz oscillation frequency)•Memory sizeROM.............................................24K to 60K bytes RAM ............................................512 to 2048 bytes•Programmable input/output ports .............................................55•High-breakdown-voltage output ports.......................................36•Software pull-up resistors ......(Ports P5, P61 to P65, P7, P84 to P87, P9)•Interrupts..................................................21 sources, 16 vectors •Timers ...........................................................8-bit ! 6, 16-bit ! 1•Serial I/O1 (Clock-synchronized)....................................8-bit ! 1......................(max. 256-byte automatic transfer function)•Serial I/O2 (UART or Clock-synchronized).....................8-bit ! 1•PWM .............................................................................14-bit ! 18-bit ! 1 (also functions as timer 6)•A-D converter..............................................10-bit ! 12 channels •Fluorescent display function ........................Total 40 control pins •Interrupt interval determination function .....................................1•Watchdog timer.............................................................20-bit ! 1•Buzzer output.............................................................................1•2 Clock generating circuitMain clock (X IN –X OUT ).........................Internal feedback resistor Sub-clock (X CIN –X COUT ).........Without internal feedback resistor (connect to external ceramic resonator or quartz-crystal oscillator )•Power source voltageIn high-speed mode ...................................................4.0 to 5.5 V (at 4.19 MHz oscillation frequency and high-speed selected)In middle-speed mode ...............................................2.7 to 5.5 V (at 4.19 MHz oscillation frequency and middle-speed selected)In low-speed mode ....................................................2.7 to 5.5 V (at 32 kHz oscillation frequency and low-speed selected)•Power dissipationIn high-speed mode ..........................................................35 mW (at 4.19 MHz oscillation frequency)In low-speed mode ............................................................60 µW (at 32 kHz oscillation frequency, at 3 V power source voltage)•Operating temperature range ...................................–20 to 85 °CAPPLICATIONMusical instruments, VCR, household appliances, etc.PR E L I M I N A R Y N o t i c e: T h i s i s no t a f i n a l s p e c i f i c a t i o n .So m e p a r am e t r i c l i m i t s a r e s u b j e c t t oc h a n g e .元器件交易网38B5 GroupSINGLE-CHIP 8-BIT CMOS MICROCOMPUTER2PR E L I M I N A R Y N o t i c e : T h i s i s n o t a f i n a l s p e c i f i c a t i o n .S om e p a r a m e t r i c l i mi t s a r e s u b j e c tt o c h a n g e .FUNCTIONAL BLOCK38B5 GroupSINGLE-CHIP 8-BIT CMOS MICROCOMPUTER3PR E L I M I N A R Y N o t i c e : T h i s i s n o t a f i n a l s p e c i f i c a t i o n .S om e p a r a m e t r i c l i mi t s a r e s u b j e c tt o c h a n g e .PIN DESCRIPTIONTable 1 Pin Description (1)Pin Name FunctionV CC , V SS Power source • Apply voltage of 4.0–5.5 V to V CC , and 0 V to V SS .V EE Pull-down • Apply voltage supplied to pull-down resistors of ports P0, P1, and P3.power sourceV REF Reference • Reference voltage input pin for A-D converter.voltage AV SSAnalog power • Analog power source input pin for A-D converter.source • Connect to V SS .______RESET Reset input • Reset input pin for active “L.”X INClock input• Input and output pins for the main clock generating circuit.• Feedback resistor is built in between X IN pin and X OUT pin.• Connect a ceramic resonator or quartz-crystal oscillator between the X IN and X OUT pins to set the oscillation frequency.• When an external clock is used, connect the clock source to the X IN pin and leave the X OUT pin open.• The clock is used as the oscillating source of system clock.P00/FLD 8–I/O port P0• 8-bit I/O port.• FLD automatic display P07/FLD 15• I/O direction register allows each pin to be individually programmed as either pinsinput or output.• At reset, this port is set to input mode.• A pull-down resistor is built in between port P0 and the V EE pin.• CMOS compatible input level.• High-breakdown-voltage P-channel open-drain output structure.• At reset, this port is set to V EE level.P10/FLD 16–Output port P1• 8-bit output port.• FLD automatic display P17/FLD 23• A pull-down resistor is built in between port P1 and the V EE pin.pins• High-breakdown-voltage P-channel open-drain output structure.• At reset, this port is set to V EE level.P20/B UZ02/I/O port P2• 8-bit I/O port with the same function as port P0.• FLD automatic display FLD 0–• Low-voltage input level.pinsP27/FLD 7• High-breakdown-voltage P-channel open-drain output structure.• Buzzer output pin (P20)P30/FLD 24–Output port P3• 8-bit output port.• FLD automatic display P37/FLD 31• A pull-down resistor is built in between port P3 and the V EE pin.pins• High-breakdown-voltage P-channel open-drain output structure.• At reset, this port is set to V EE level.P40/INT 0,I/O port P4• 7-bit I/O port with the same function as port P0.• Interrupt input pinsP41/INT 1,• CMOS compatible input level.P42/INT 3• N-channel open-drain output structure.P43/B UZ01• Buzzer output pin P44/PWM 1• PWM output pin (Timer output pin)P45/T 1OUT ,• Timer output pinP46/T 3OUT P47/INT 2Input port P4• 1-bit input port.• Interrupt input pin• CMOS compatible input level.Function except a port functionX OUT Clock output38B5 GroupSINGLE-CHIP 8-BIT CMOS MICROCOMPUTER4PR E L I M I N A R Y N o t i c e : T h i s i s n o t a f i n a l s p e c i f i c a t i o n .S om e p a r a m e t r i c l i mi t s a r e s u b j e c tt o c h a n g e .Table 2 Pin Description (2)Function except a port function Pin Name FunctionP50/S IN1,I/O port P5• 8-bit CMOS I/O port with the same function as port P0.• Serial I/O1 function pinsP51/S OUT1,• CMOS compatible input level.P52/S CLK11,• CMOS 3-state output structure.P53/S CLK12P54/R X D,• Serial I/O2 function pinsP55/T X D,P56/S CLK21,________P57/S RDY2/S CLK22P60/CNTR 1I/O port P6• 1-bit I/O port with the same function as port P0.• Timer input pin• CMOS compatible input level.• N-channel open-drain output structure.P61/CNTR 0/• 5-bit CMOS I/O port with the same function as port P0.• Timer I/O pinCNTR 2• CMOS compatible input level.________P62/S RDY1/• CMOS 3-state output structure.• Serial I/O1 function pin AN 8• A-D conversion input pin P63/AN 9• A-D conversion input pin P64/INT 4/• Serial I/O1 function pin S BUSY1/AN 10,• A-D conversion input pin P65/S STB1/• Interrupt input pin (P64)AN 11P70/AN 0–I/O port P7• 8-bit CMOS I/O port with the same function as port P0.• A-D conversion input pinP77/AN 7• CMOS compatible input level.• CMOS 3-state output structure.P80/FLD 32–I/O port P8• 4-bit I/O port with the same function as port P0.• FLD automatic display pins P83/FLD 35• Low-voltage input level.• High-breakdown-voltage P-channel open-drain output structure.P84/FLD 36• 4-bit CMOS I/O port with the same function as port P0.P85/RTP 0/• Low-voltage input level.• FLD automatic display pins FLD 37,P86/RTP 1/FLD 38P87/PWM 0/• FLD automatic display pins FLD 39• 14-bit PWM output P90/X CIN ,I/O port P9• 2-bit CMOS I/O port with the same function as port P0.• I/O pins for sub-clock generatingP91/X COUT• CMOS compatible input level. circuit (connect a ceramic resona-• CMOS 3-state output structure.tor or a quarts-crystal oscillator)38B5 GroupSINGLE-CHIP 8-BIT CMOS MICROCOMPUTER5PR E L I M I N A R Y N o t i c e : T h i s i s n o t a f i n a l s p e c i f i c a t i o n .S om e p a r a m e t r i c l i mi t s a r e s u b j e c tt o c h a n g e .PART NUMBERINGFig. 3 Part Numbering38B5 GroupSINGLE-CHIP 8-BIT CMOS MICROCOMPUTER6PR E L I M I N A R Y N o t i c e : T h i s i s n o t a f i n a l s p e c i f i c a t i o n .S om e p a r a m e t r i c l i mi t s a r e s u b j e c tt o c h a n g e .GROUP EXPANSIONMitsubishi plans to expand the 38B5 group as follows:Memory TypeSupport for Mask ROM, One Time PROM and EPROM versions.Memory SizeROM/PROM size ..................................................24K to 60K bytes RAM size ...........................................................1024 to 2048 bytesPackage80P6N-A .....................................0.8 mm-pitch plastic molded QFP 80D0........................0.8 mm-pitch ceramic LCC (EPROM version)Currently supported products are listed below.Table 3 List of Supported Products(P) ROM size (bytes)Product RAM size (bytes)Package RemarksROM size for User ( )As of Jan. 1998M38B57MC-XXXFP49152(49022)102480P6N-AMask ROM version38B5 GroupSINGLE-CHIP 8-BIT CMOS MICROCOMPUTER7PR E L I M I N A R Y N o t i c e : T h i s i s n o t a f i n a l s p e c i f i c a t i o n .S om e p a r a m e t r i c l i mi t s a r e s u b j e c tt o c h a n g e .FUNCTIONAL DESCRIPTION Central Processing Unit (CPU)The 38B5 group uses the standard 740 family instruction set. Refer to the table of 740 family addressing modes and machine instruc-tions or the 740 Family Software Manual for details on the instruction set.Machine-resident 740 Family instructions are as follows:•The FST and SLW instructions cannot be used.•The MUL, DIV, WIT and STP instructions can be used.Fig. 5 Structure of CPU Mode Register[CPU Mode Register] CPUMThe CPU mode register contains the stack page selection bit and internal system clock control bits. The CPU mode register is allo-cated at address 003B 16.38B5 GroupSINGLE-CHIP 8-BIT CMOS MICROCOMPUTER8PR E L I M I N A R Y N o t i c e : T h i s i s n o t a f i n a l s p e c i f i c a t i o n .S om e p a r a m e t r i c l i mi t s a r e s u b j e c tt o c h a n g e .MemorySpecial function register (SFR) areaThe special function register (SFR) area in the zero page contains control registers such as I/O ports and timers.RAMRAM is used for data storage and for stack area of subroutine calls and interrupts.ROMThe first 128 bytes and the last 2 bytes of ROM are reserved for device testing, and the other areas are user areas for storing pro-grams.Interrupt vector areaThe interrupt vector area contains reset and interrupt vectors.Zero pageThe 256 bytes from addresses 000016 to 00FF 16 are called the zero page area. The internal RAM and the special function registers (SFR)are allocated to this area.The zero page addressing mode can be used to specify memory and register addresses in the zero page area. Access to this area with only 2 bytes is possible in the zero page addressing mode.Special pageThe 256 bytes from addresses FF0016 to FFFF 16 are called the spe-cial page area. The special page addressing mode can be used to specify memory addresses in the special page area. Access to this area with only 2 bytes is possible in the special page addressing mode.Fig. 6 Memory Map Diagram38B5 GroupSINGLE-CHIP 8-BIT CMOS MICROCOMPUTER9PR E L I M I N A R Y N o t i c e : T h i s i s n o t a f i n a l s p e c i f i c a t i o n .S om e p a r a m e t r i c l i mi t s a r e s u b j e c tt o c h a n g e .Fig. 7 Memory Map of Special Function Register (SFR)I/O Ports[Direction Registers] PiD Array The 38B5 group has 55 programmable I/O pins arranged in eightindividual I/O ports (P0, P2, P40–P46, and P5–P9). The I/O portshave direction registers which determine the input/output direction ofeach individual pin. Each bit in a direction register corresponds toone pin, and each pin can be set to be input port or output port. When“0” is written to the bit corresponding to a pin, that pin becomes aninput pin. When “1” is written to that pin, that pin becomes an outputpin. If data is read from a pin set to output, the value of the portoutput latch is read, not the value of the pin itself. Pins set to input(the bit corresponding to that pin must be set to “0”) are floating andthe value of that pin can be read. If a pin set to input is written to, onlythe port output latch is written to and the pin remains floating.[High-Breakdown-Voltage Output Ports]The 38B5 group microprocessors have 5 ports with high-breakdown-voltage pins (ports P0–P3and P80–P83). The high-breakdown-volt-age ports have P-channel open-drain output with Vcc- 45 V of break-down voltage. Each pin in ports P0, P1, and P3 has an internal pull-down resistor connected to V EE. At reset, the P-channel output tran-sistor of each port latch is turned off, so that it goes to V EE level (“L”)by the pull-down resistor.Writing “1” (weak drivability) to bit 7 of the FLDC mode register (ad-dress 0EF416) shows the rising transition of the output transistors forreducing transient noise. At reset, bit 7 of the FLDC mode register isset to “0” (strong drivability).[Pull-up Control Register] PULLPorts P5, P61–P65, P7, P84–P87 and P9 have built-in programmablepull-up resistors. The pull-up resistors are valid only in the case thatthe each control bit is set to “1” and the corresponding port directionregisters are set to input mode.Fig. 8 Structure of Pull-up Control Registers (PULL1 and PULL2)SINGLE-CHIP 8-BIT CMOS MICROCOMPUTERTable 4 List of I/O Port Functions (1)Pin Name Input/Output I/O Format Non-Port Function Related SFRs Ref.No. P00/FLD8–Port P0Input/output,CMOS compatible input level FLD automatic display function FLDC mode register(1)P07/FLD15individual bits High-breakdown voltage P-Port P0FLD/port switch registerchannel open-drain outputwith pull-down resistorP10/FLD16–Port P1Output High-breakdown voltage P-FLDC mode register(2)P17/FLD23channel open-drain outputwith pull-down resistorP20/B UZ02/Port P2Input/output,Low-voltage input level Buzzer output (P20)FLDC mode register(3) FLD0individual bits High-breakdown voltage P-Port P2FLD/port switch registerP21/FLD1–channel open-drain output Buzzer output control register(1)P27/FLD7P30/FLD24–Port P3Output High-breakdown voltage P-FLDC mode register(2)P37/FLD31channel open-drain outputwith pull-down resistorP40/INT0,Port P4Input/output,CMOS compatible input level External interrupt input Interrupt edge selection register(4)P41/INT1,individual bits N-channel open-drain outputP42/INT3P43/B UZ01Buzzer output Buzzer output control register(5)P44/PWM1PWM output Timer 56 mode register(6)P45/T1OUT Timer output Timer 12 mode register(7)P46/T3OUT Timer output Timer 34 mode register(7)P47/INT2Input CMOS compatible input level External interrput input I nterrupt edge selection register(8)Interrupt interval determinationcontrol registerP50/SIN1Port P5Input/output,CMOS compatible input level Serial I/O1 function I/O Serial I/O1 control register 1, 2(9)P51/S OUT1,individual bits CMOS 3-state output(10)P52/S CLK11,P53/S CLK12P54/R X D,Serial I/O2 function I/O Serial I/O2 control register(9)P55/T X D,UART control register(10)P56/S CLK21________P57/S RDY2/(11)S CLK22P60/CNTR1Port P6CMOS compatible input level External count I/O Interrupt edge selection register(4)N-channel open-drain outputP61/CNTR0/CMOS compatible input level(12) CNTR2CMOS 3-state output________P62/S RDY1/Serial I/O1 function I/O Serial I/O1 control register 1, 2(13) AN8A-D conversion input A-D control registerP63/AN9A-D conversion input A-D control register(14)P64/INT4/Serial I/O1 function I/O Serial I/O1 control register 1, 2(15)S BUSY1/AN10A-D conversion input A-D control registerExternal interrupt input Interrupt edge selection registerP65/S STB1/Serial I/O1 function I/O Serial I/O1 control register 1, 2(16) AN11A-D conversion input A-D control registerP70/AN0–Port P7A-D conversion input A-D control register(14)P77/AN7Table 5 List of I/O Port Functions (2)Pin Name Input/Output I/O Format Non-Port Function Related SFRs Ref.No. P80/FLD32–Port P8Input/output,Low-voltage input level FLD automatic display function FLDC mode register(1)P83/FLD35individual bits High-breakdown voltage P-Port P8FLD/port switch registerchannel open-drain outputP84/FLD36Low-voltage input level(17) P85/RTP0/CMOS 3-state output FLD automatic display function FLDC mode register(18) FLD37,Real time port output Port P8FLD/port switch registerP86/RTP1/Timer X mode register 2FLD38P87/PWM0/FLD automatic display function FLDC mode register(19) FLD39PWM output Port P8FLD/port switch registerPWM control registerP90/X CIN Port P9CMOS compatible input level Sub-clock generating circuit I/O CPU mode register(20) P91/X COUT CMOS 3-state output(21) Notes 1 : How to use double-function ports as function I/O ports, refer to the applicable sections.2 : Make sure that the input level at each pin is either 0 V or Vcc during execution of the STP instruction.When an input level is at an intermediate potential, a current will flow from Vcc to Vss through the input-stage gate.SINGLE-CHIP 8-BIT CMOS MICROCOMPUTERSINGLE-CHIP 8-BIT CMOS MICROCOMPUTERInterruptsInterrupts occur by twenty one sources: five external, fifteen internal, and one software.(1) Interrupt ControlEach interrupt except the BRK instruction interrupt have both an interrupt request bit and an interrupt enable bit, and is controlled by the interrupt disable flag. An interrupt occurs if the corresponding interrupt request and enable bits are “1” and the interrupt disable flag is “0.” Interrupt enable bits can be set or cleared by software. Inter-rupt request bits can be cleared by software, but cannot be set by software. The BRK instruction interrupt and reset cannot be disabled with any flag or bit. The I flag disables all interrupts except the BRK instruction interrupt and reset. If several interrupts requests occurs at the same time the interrupt with highest priority is accepted first.(2) Interrupt OperationUpon acceptance of an interrupt the following operations are auto-matically performed:1. The contents of the program counter and processor statusregister are automatically pushed onto the stack.2. The interrupt disable flag is set and the correspondinginterrupt request bit is cleared.3. The interrupt jump destination address is read from the vectortable into the program counter.s Notes on UseWhen the active edge of an external interrupt (INT0–INT4) is set or when switching interrupt sources in the same vector address, the corresponding interrupt request bit may also be set. Therefore, please take following sequence:(1) Disable the external interrupt which is selected.(2) Change the active edge in interrupt edge selection register(3) Clear the set interrupt request bit to “0.”(4) Enable the external interrupt which is selected.SINGLE-CHIP 8-BIT CMOS MICROCOMPUTERTable 6 Interrupt Vector Addresses and PriorityVector Addresses (Note 1)Interrupt RequestInterrupt Source Priority RemarksHigh Low Generating ConditionsReset (Note 2)1FFFD16FFFC16At reset Non-maskableINT02FFFB16FFFA16At detection of either rising or falling edge of External interruptINT0 input(active edge selectable)INT13FFF916FFF816At detection of either rising or falling edge of External interruptINT1 input(active edge selectable)INT24FFF716FFF616At detection of either rising or falling edge of External interruptINT2 input(active edge selectable)Remort control/At 8-bit counter overflow Valid when interrupt interval counter overflow determination is operatingSerial I/O15FFF516FFF416At completion of data transfer Valid when serial I/O1 ordinarymode is selectedSerial I/O1 auto-At completion of the last data transfer Valid when serial I/O1 automatic matic transfer transfer mode is selectedTimer X6FFF316FFF216At timer X underflowTimer 17FFF116FFF016At timer 1 underflowTimer 28FFEF16FFEE16At timer 2 underflow STP release timer underflowTimer 39FFED16FFEC16At timer 3 underflowTimer 410FFEB16FFEA16At timer 4 underflowTimer 511FFE916FFE816At timer 5 underflowTimer 612FFE716FFE616At timer 6 underflowSerial I/O2 receive13FFE516FFE416At completion of serial I/O2 data receiveINT314FFE316FFE216At detection of either rising or falling edge of External interruptINT3 input(active edge selectable)Serial I/O2 transmit At completion of data transmitINT415FFE116FFE016At detection of either rising or falling edge of External interruptINT4 input(active edge selectable)Valid when INT4 interrupt is selectedA-D conversion At completion of A-D conversion Valid when A-D conversion is selected FLD blanking16FFDF16FFDE16At falling edge of the last timing immediately Valid when FLD blankingbefore blanking period starts interrupt is selectedFLD digit At rising edge of each digit Valid when FLD digit interrupt is selected BRK instruction17FFDD16FFDC16At BRK instruction execution Non-maskable software interrupt Notes 1 : Vector addresses contain interrupt jump destination addresses.2 : Reset function in the same way as an interrupt with the highest priority.SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER Timers Array 8-Bit TimerThe 38B5 group has six built-in timers : Timer 1, Timer 2, Timer 3,Timer 4, Timer 5, and Timer 6.Each timer has the 8-bit timer latch. All timers are down-counters.When the timer reaches “0016,” an underflow occurs with the nextcount pulse. Then the contents of the timer latch is reloaded into thetimer and the timer continues down-counting. When a timerunderflows, the interrupt request bit corresponding to that timer isset to “1.”The count can be stopped by setting the stop bit of each timer to “1.”The internal system clock can be set to either the high-speed modeor low-speed mode with the CPU mode register. At the same time,timer internal count source is switched to either f(X IN) or f(X CIN).q Timer 1, Timer 2The count sources of timer 1 and timer 2 can be selected by settingthe timer 12 mode register. A rectangular waveform of timer 1underflow signal divided by 2 is output from the P45/T1OUT pin. Thewaveform polarity changes each time timer 1 overflows. The activeedge of the external clock CNTR0 can be switched with the bit 6 ofthe interrupt edge selection register.At reset or when executing the STP instruction, all bits of the timer 12mode register are cleared to “0,” timer 1 is set to “FF16,” and timer 2is set to “0116.”q Timer 3, Timer 4The count sources of timer 3 and timer 4 can be selected by settingthe timer 34 mode register. A rectangular waveform of timer 3underflow signal divided by 2 is output from the P46/T3OUT pin. Thewaveform polarity changes each time timer 3 overflows. The activeedge of the external clock CNTR1 can be switched with the bit 7 ofthe interrupt edge selection register.q Timer 5, Timer 6The count sources of timer 5 and timer 6 can be selected by settingthe timer 56 mode register. A rectangular waveform of timer 6underflow signal divided by 2 is output from the P44/PWM1 pin. Thewaveform polarity changes each time timer 6 overflows.q Timer 6 PWM1 ModeTimer 6 can output a rectangular waveform with “H” duty cycle n/(n+m) from the P44/PWM1 pin by setting the timer 56 mode register(refer to Figure 16). The n is the value set in timer 6 latch (address002516) and m is the value in the timer 6 PWM register (address002716). If n is “0,” the PWM output is “L,” if m is “0,” the PWM outputis “H” (n = 0 is prior than m = 0). In the PWM mode, interrupts occurat the rising edge of the PWM output.38B5 GroupSINGLE-CHIP 8-BIT CMOS MICROCOMPUTER20PR E L I M I N A R Y N o t i c e : T h i s i s n o t a f i n a l s p e c i f i c a t i o n .S om e p a r a m e t r i c l i mi t s a r e s u b j e c tt o c h a n g e .38B5 GroupSINGLE-CHIP 8-BIT CMOS MICROCOMPUTER21PR E L I M I N A R Y N o t i c e : T h i s i s n o t a f i n a l s p e c i f i c a t i o n .S om e p a r a m e t r i c l i mi t s a r e s u b j e c tt o c h a n g e .116-Bit TimerTimer X is a 16-bit timer that can be selected in one of four modes by the Timer X mode register 1, 2 and can be controlled the timer X write and the real time port by setting the timer X mode registers. Read and write operation on 16-bit timer must be performed for both high- and low-order bytes. When reading a 16-bit timer, read from the high-order byte first. When writing to 16-bit timer, write to the low-order byte first. The 16-bit timer cannot perform the correct operation when reading during write operation, or when writing during read operation.q Timer XTimer X is a down-counter. When the timer reaches “000016,” an underflow occurs with the next count pulse. Then the contents of the timer latch is reloaded into the timer and the timer continues down-counting. When a timer underflows, the interrupt request bit corre-sponding to that timer is set to “1.”(1) Timer modeA count source can be selected by setting the Timer X count source selection bits (bits 1 and 2) of the Timer X mode register 1.(2) Pulse output modeEach time the timer underflows, a signal output from the CNTR2 pin is inverted. Except for this, the operation in pulse output mode is the same as in timer mode. When using a timer in this mode, set the port shared with the CNTR2 pin to output.(3) Event counter modeThe timer counts signals input through the CNTR2 pin. Except for this, the operation in event counter mode is the same as in timer mode. When using a timer in this mode, set the port shared with the CNTR2 pin to input.(4) Pulse width measurement modeA count source can be selected by setting the Timer X count source selection bits (bits 1 and 2) of the Timer X mode register 1. When CNTR2 active edge switch bit is “0,” the timer counts while the input signal of the CNTR2 pin is at “H.” When it is “1,” the timer counts while the input signal of the CNTR2 pin is at “L.” When using a timer in this mode, set the port shared with the CNTR2 pin to input.s Note•Timer X Write ControlIf the timer X write control bit is “0,” when the value is written in the address of timer X, the value is loaded in the timer X and the latch at the same time.If the timer X write control bit is “1,” when the value is written in the address of timer X, the value is loaded only in the latch. The value in the latch is loaded in timer X after timer X underflows.When the value is written in latch only, unexpected value may be set in the high-order counter if the writing in high-order latch and the underflow of timer X are performed at the same timing.•Real Time Port ControlWhile the real time port function is valid, data for the real time port are output from ports P85 and P86 each time the timer X underflows. (However, if the real time port control bit is changed from “0” to “1,”data are output without the timer X.) When the data for the real time port is changed while the real time port function is valid, the changed data are output at the next underflow of timer X.Before using this function, set the corresponding port direction regis-ters to output mode.22。

艾威图w系列伺服说明书

FG 43

19

机壳地

位置控制的标准接线

1

电机 4 芯插头

光电编码器 15 芯插头

编码器 信号输出 编码器 Z 信号 集电极开路输出 编码器信号地

PDF 文件使用 "pdfFactory Pro" 试用版本创建 w–w1w.0fi–

驱动器的连接

速度控制接线图

三相AC220V(≥1.0KW) 单相AC220V(<1.0KW)

功 率 零速转矩 额定转速 额定电流

(Kw) (Nm) (Rpm) (A)

0.4

2

3000

4

0.75

2

3000

4

0.6

2

3000

4

1.2

4

3000

5

1.5

5

3000

6

1.2

6

2000

6

1.8

6

3000

8

0.6

4

2500

4

1.0

4

2500

4

1.3

5

2500

5

1.5

6

2500

6

1.6

7.7

2000

6

2.4

7.7

3000

9

1.5

10

1500

6

2.6

10

2500

10

2.3

15

1500

10

PDF 文件使用 "pdfFactory Pro" 试用版本创建 ww–w7.f–

驱动器的使用

使用环境 防护

伺服驱动器自身结构无防护,因此必须安装在防护良好的电柜内,并防接触 腐蚀性、易燃性气体,防止导电物体、金属粉尘、油雾及液体进入内部。

EP1-3G1S中文资料

DESCRIPTIONThe NEC TOKIN EP2 / EP1 series are PC-board mount type automotive relays suitable for various motorcontrols and other applications that require a high level of quality and performance.EP2 series is a twin-relay and divided into two types for different usage.One is an H-bridge type designed for forward and reverse control of the motors, and the other, a separatetype containing two separated relays in one package.EP1 series is a 1 Form c relay equivalent to EP2 series in performance.FEATURESFor motor reversible control and solenoid controlApprox. 50% less relay space than conventional relayHigh performance and productivity by unique structureFlux tight housingAPPLICATIONSPower windowAntenna lifterAuto-seat positioningElectrical door lockPassive seat belt controlKeyless/Remote entry systemSliding roof controlThe information in this document is subject to change without notice.Date Published August 2002 MPrinted in Japan© NEC TOKIN Corporation 2002EP2 / EP1 SERIES2SCHEMATIC (BOTTOM VIEW)EP2 SERIESEP1 SERIESDIMENSIONS mm (inch)EP2 SERIESEP2/EP1 SERIES3EP1 SERIESPCB PAD LAYOUT mm (inch) (BOTTOM VIEW)EP2 SERIESEP1 SERIESEP2 / EP1 SERIES4SPECIFICATIONSat 25°C (77°F )Items EP2 EP1Contact Form1 Form c ×2 (H bridge type and separatetype)1 Form c Contact Material Silver oxide complex alloy(special type available) Contact Resistance 50 m Ω max. (measured at 7 A) initial Contact Switching Voltage 16 Vdc max. Contact Switching Current 25 A max. (at 16 Vdc) Contact Carrying Current 20 A max. (1 hour max.),25 A max. (2 minutes max.) at 12 Vdc25 A max. (1 hour max.),30 A max. (2 minutes max.) at 12 VdcOperate Time Approx. 5 ms (at 12 Vdc) initialRelease TimeApprox. 2 ms (at 12 Vdc) initial. without diode Normal Operate Power 0.48 W / 0.64 W (at 12 Vdc) Insulation Resistance 100 M Ω min. (at 500 Vdc) initial Breakdown Voltage 500 Vdc min. (for 1 minute) initialShock Resistance 98 m / s 2[10 G] min. (misoperating), 980 m / s 2[100 G] min. (destructive failure)Vibration Resistance10 to 300 Hz, 43 m/s 2[ 4.4 G] min. (misoperating)10 to 500 Hz, 43 m/s 2, [ 4.4 G] 200 hours (destructive failure) Ambient Temperature –40 °C to +85 °C (–40 °F to +185 °F)Coil Temperature50 °C / W (122 °F/W)(contact carrying current 0 A)Mechanical1 × 106operationsLife ExpectancyElectrical100 x 103operations (at 14 Vdc. Motor Load 20 A / 3 A) WeightApprox. 15 gn (0.53oz) Approx. 8 gr (0.28 oz)COIL RATINGEP2 SERIESat 25°C (77°F ) Part Number H Bridge Type Separate Type Nominal Voltage (Vdc) Coil Resistance (Ω±10%)Nominal Current (mA) Must Operate Voltage (Vdc max.)Must Release Voltage (Vdc min.)Nominal Operate Power (W) EP2-3L1 EP2-3L2 EP2-3L3 EP2-4L3 EP2-4L4 EP2-4L5EP2-3L1T EP2-3L2T EP2-3L3T EP2-4L3T EP2-4L4T EP2-4L5T12 12 12 12 12 12225 225 225 300 300 30053.5 53.5 53.5 40.0 40.0 40.06.57.0 7.5 7.58.0 8.50.9 0.9 0.9 0.9 0.9 0.90.64 0.64 0.64 0.48 0.48 0.48EP1 SERIESPart NumberRegularTypeHigh Carrying Current Type Nominal Voltage (Vdc) Coil Resistance (Ω±10%)Nominal Current (mA) Must Operate Voltage (Vdc max.)Must Release Voltage (Vdc min.)Nominal Operate Power (W) EP1-3L1EP1-3L2EP1-3L3EP1-4L3EP1-4L4EP1-4L5EP1-B3G1 EP1-B3G2 EP1-B3G3 EP1-B4G3 EP1-B4G4 EP1-B4G5 12 12 12 12 12 12225 225 225 300 300 30053.3 53.3 53.3 40.0 40.0 40.06.57.0 7.5 7.58.0 8.50.9 0.9 0.9 0.9 0.9 0.90.64 0.64 0.64 0.48 0.48 0.48EP2/EP1 SERIES5NUMBERING SYSTEMTYPICAL APPLICATION (H Bridge Type)MOTOR Tr1Tr2 STOP off off FORWARD on off REVERSE off onIt is necessary to take more than 100 ms intervals for on / off timing between driving Tr1 and Tr2. If the interval is less than 100 ms, an excessive current happen to flow to the relay contacts.EP2 / EP1 SERIES6TECHNICAL DATACoil Temperature Rise (EP2-3L1)Operate Time (EP2-3L1) Release time (EP2-3L1)EP2/EP1 SERIES7EP2 / EP1 SERIESPrinted on recycled paper。

Lorex MPX HDSe

3.

2. Clic Droit: • En mode visionnement en direct :

Contrôle des caméras PTZ (non incluses) Ajuste les réglages de la couleur et de l’image de la caméra Voir les informations du système Démarrer/arrêter le mode séquence Esactiver l’alarme sonore

6: EN MARCHE

Bip

Si le système émet un signal sonore au démarrage, le câble Ethernet n’est peut-être pas branché, ou le système n’est peut-être pas connecté à Internet. Pour arrêter le signal sonore : 1. Brancher un câble Ethernet du système au routeur et redémarrer le système. OU 2. Cliquer avec le bouton droit et cliquer sur Disable Beep.

Cliquer sur et sélectionner SETTING

4. Cliquer sur GENERAL et sélectionner l’onglet Date&Time.

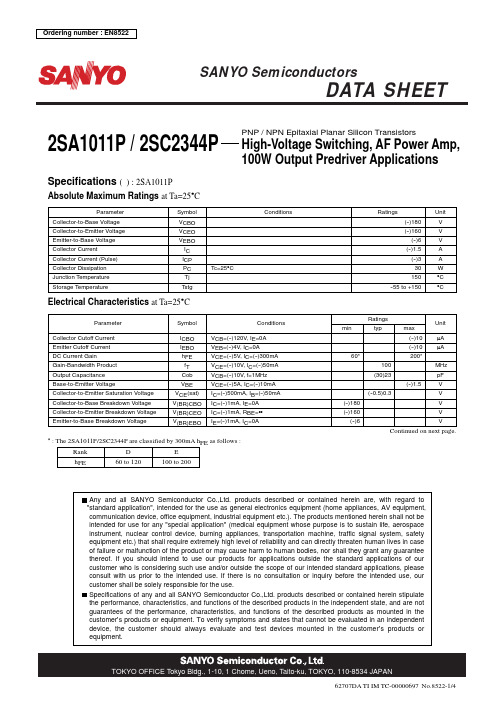

2SA1011P中文资料

Symbol

VCBO VCEO VEBO

IC ICP PC Tj

Tstg

Tc=25°C

Electrical Characteristics at Ta=25°C

Conditions

Current Emitter Cutoff Current DC Current Gain Gain-Bandwidth Product Output Capacitance Base-to-Emitter Voltage Collector-to-Emitter Saturation Voltage Collector-to-Base Breakdown Voltage Collector-to-Emitter Breakdown Voltage Emitter-to-Base Breakdown Voltage

* : The 2SA1011P/2SC2344P are classified by 300mA hFE as follows :

Rank

D

E

hFE

60 to 120

100 to 200

Ratings

Unit

(--)180

V

(--)160

V

(--)6

V

(--)1.5

A

(--)3

A

30

W

150

°C

--55 to +150

--5mA

--4mA

--3mA --2mA

--1mA

IB=0mA

--10

--20

--30

--40

--50

Collector to Emitter Voltage, VCE -- V IT02132

331P说明书

打电话 .................................................................................................................................................... 2.2 免提拨号 ................................................................................................................................................ 2.2 电话簿拨号 ........................................................................................................................................... 2.2

ii

目录

Rhine_UK.book Page iii Wednesday, August 28, 2002 1:57 PM

2 ᐺ ; ᒙਜ਼আ፝

功能 ........................................................................................................................................................ 1.2 熟悉您的新机器 ................................................................................................................................... 1.3

CDRH64BNP-331MC中文资料

1.外形1-1.寸法図(mm)* 公差のない寸法は参考値とする。

1-2.捺印表示例 O-3.推奨ランド図(mm)2.コイル仕様2-1.端子接続図(裏面図)電極(端子)間の隙間はシルク処理をして御使用下さい。

捺印位置不定製造密番頭部直捺印100電極側電極側compliance Cd:Max.0.01wt%others:Max.0.1wt%RoHS12-2.電気的特性Ⅰ(リール梱包の場合)NO. 品 名 表示 インダクタンス[以内]※1D.C.R.(Ω)[以下](at 20℃)※2定格電流(A)※3スミダコード0102 CDRH64BNP-1ØØMCCDRH64BNP-12ØMC10012010μH ± 20%12μH ± 20%0.12 (88m)0.13 (97m)1.351.204745-01454745-01460304 CDRH64BNP-15ØMCCDRH64BNP-18ØMC15018015μH ± 20%18μH ± 20%0.18 (0.13)0.24 (0.18)1.101.004745-01474745-01480506 CDRH64BNP-22ØMCCDRH64BNP-27ØMC22027022μH ± 20%27μH ± 20%0.27 (0.20)0.30 (0.22)0.910.824745-01494745-01500708 CDRH64BNP-33ØMCCDRH64BNP-39ØMC33039033μH ± 20%39μH ± 20%0.33 (0.25)0.37 (0.27)0.750.694745-01514745-01520910 CDRH64BNP-47ØMCCDRH64BNP-56ØMC47056047μH ± 20%56μH ± 20%0.52 (0.38)0.56 (0.41)0.620.584745-01544745-01551112 CDRH64BNP-68ØMCCDRH64BNP-82ØMC68082068μH ± 20%82μH ± 20%0.63 (0.47)0.71 (0.53)0.520.474745-01564745-01571314 CDRH64BNP-1Ø1MCCDRH64BNP-121MC101121100μH ± 20%120μH ± 20%1.03 (0.76)1.15 (0.85)0.430.394745-01584745-01591516 CDRH64BNP-151MCCDRH64BNP-181MC151181150μH ± 20%180μH ± 20%1.68 (1.29)1.87 (1.44)0.350.324745-01604745-01611718 CDRH64BNP-221MCCDRH64BNP-271MC221271220μH ± 20%270μH ± 20%2.08 (1.60)2.37 (1.82)0.290.264745-01624745-01631920 CDRH64BNP-331MCCDRH64BNP-391MC331391330μH ± 20%390μH ± 20%2.67 (2.05)2.94 (2.26)0.230.224745-01654745-01662122 CDRH64BNP-471MCCDRH64BNP-561MC471561470μH ± 20%560μH ± 20%3.93 (3.02)5.43 (4.18)0.200.184745-01674745-01682324 CDRH64BNP-681MCCDRH64BNP-821MC681821680μH ± 20%820μH ± 20%7.32 (5.63)8.24 (6.34)0.170.154745-01694745-017025 CDRH64BNP-1Ø2MC 102 1 mH ± 20% 9.26 (7.13) 0.14 4745-0171※1: 測定周波数 L at 1 kHz※2: ( )内は、標準値とする。

P3ec 系列软件应用参考手册

第 1 页 共 1 页

P3e/c 系列软件应用参考手册 (水电篇)

目 录

4.1 工程项目管理类型 -------------------------------------------------------------------------------------- 78 4.2 P3e/c 在水电工程建设领域的应用模式和作用 ---------------------------------------------------- 79 第五章 水电建设项目 P3e/c 应用案例 ------------------------------------------------------------------------ 84

P3e/c 系列软件应用参考手册 (水电篇)

目 录

目

录

Hale Waihona Puke 前 言 ------------------------------------------------------------------------------------------------------------------3 第一章 P3e/c 软件介绍 -------------------------------------------------------------------------------------------5 1.1 概述 ----------------------------------------------------------------------------------------------------------5 1.2 P3e/c 功能介绍 ---------------------------------------------------------------------------------------------6 1.2.1 P3e/c 组成及各组件使用对象-------------------------------------------------------------------6 1.2.2 P3e/c 主要功能特点 -------------------------------------------------------------------------------8 第二章 P3e/c 关键概念的理解和运用 ----------------------------------------------------------------------- 11 2.1 P3e/c 中体现的项目管理组织方式 ------------------------------------------------------------------- 12 2.1.1 工程项目管理组织结构形式 ------------------------------------------------------------------ 12 2.1.2 P3e/c 软件实现矩阵式项目管理组织方式的原理 ---------------------------------------- 14 2.1.3 权限传递中 OBS、用户及 EPS/WBS 之间的关系--------------------------------------- 17 2.2 建立合理的工作分解结构 --------------------------------------------------------------------------- 19 2.2.1 为什么要使用工作分解结构 ----------------------------------------------------------------- 19 2.2.2 工作分解结构的作用 -------------------------------------------------------------------------- 19 2.2.3 怎么应用工作分解结构 ----------------------------------------------------------------------- 20 2.2.4 常用的工作分解结构分解方法 --------------------------------------------------------------- 21 2.2.5 工作分解结构分解时应注意的问题: ----------------------------------------------------- 22 2.2.6 工作分解结构的重要规则-百分之百规则 -------------------------------------------------- 23 2.3 多级网络计划的应用 --------------------------------------------------------------------------------- 24 2.3.1 多级网络计划概述 ----------------------------------------------------------------------------- 24 2.3.2 多级网络的应用模式 -------------------------------------------------------------------------- 25 2.3.3 P3e/c 软件中多级网络的实现----------------------------------------------------------------- 26 2.4 P3e/c 中赢得值原理的运用 -------------------------------------------------------------------------- 38 2.4.1 关于赢得值 --------------------------------------------------------------------------------------- 38 2.4.2 赢得值各参数释义 ------------------------------------------------------------------------------ 39 2.4.3 运用赢得值方法进行项目投资控制 --------------------------------------------------------- 48 2.4.4 运用赢得值方法进行项目成本控制 --------------------------------------------------------- 59 2.4.5 总结 ------------------------------------------------------------------------------------------------ 64 第三章 水电工程建设项目管理信息化的总体构架 ------------------------------------------------------- 66 3.1 水电工程建设项目的特点分析 ----------------------------------------------------------------------- 66 3.2 水电建设工程项目管理信息化的模式(P3e/c+PIP) ------------------------------------------- 70 3.3 水电建设工程项目管理信息化的基本框架 ------------------------------------------------------- 72 3.3.1 P3e/c 项目管理软件 ----------------------------------------------------------------------------- 72 3.3.2 项目管理信息平台(PIP) ------------------------------------------------------------------- 72 3.4 水电建设工程项目管理信息化的实施建议 ------------------------------------------------------- 74 3.4.1 进一步理顺和完善适应工程项目管理信息化的工程管理制度和流程(组织件)75 3.4.2 组织各参与单位参加工程项目管理信息化强化研讨班(教育件) ------------------ 76 3.4.3 建立集成的水电建设工程项目管理信息化系统(软件) ----------------------------- 77 3.4.4 购置必要的硬件 -------------------------------------------------------------------------------- 77 第四章 P3e/c 在水电工程建设领域的应用模式 ----------------------------------------------------------- 78

HQxxxx-xxx-3AA中文资料

HQ SeriesSPECIFICATIONS STANDARD*SPECIAL ELECTRICALCenter Frequency (Fc)100 to 1000 Mhz80 to 1400 MHz 3dB Relative Bandwidth (% of FC) 4 to 40 4 to 50 Number of Sections Available 3 to 8 2 to 10 Nominal Impedance50 Ohms50 to 75 Ohms Maximum Insertion Loss See Curve See Curve Maximum VSWR 1.5/1 1.3/1 Attenuation in the Stopband See Graph See GraphMaximum Input Power (Average)(Watts to10,000 ft.)500 x 3dB BW (MHz)(Loss Factor)(Fc MHz)See StandardMaximum Input Power (Peak)(Watts to10,000 ft.)300 x 3dB BW (MHz)Fc (MHz)2,000ENVIRONMENTALShock15 G's25 G's Vibration 5 G's10 G's Humidity90% relative100% relativeINSERTION LOSS:The Maximum Insertion Loss at center frequency is equal to :LF x (N + 0.5) / % 3 dB BW + 0.2 Where:LF= Loss Factor, N= Number of Sections% 3dB BW:3dB BW (MHz) x 100divided byCenter Frequency (MHz) Example:A 3 section HQ with a center frequency of 400 MHz and a 3dB BW of 40 MHz would have,1.5 x 3.5 / 10 = 5.25 / 10 = 0.525 0.525 + 0.2 = 0.8 dBConnectors Available on HQ Series:Lark Code Type C DIM.Inches & MMLarkCodeType C DIM.Inches & MMA SMA JACK.800 & 20.3G N JACK 1.625 & 41.3B SMA PLUG.855 & 22.5H N PLUG 1.585 & 40.3C TNC JACK 1.350 & 34.3L SOLDER MPINAXIAL.625 & 15.9D TNC PLUG 1.280 & 32.5*M SOLDER PINRADIAL.625 & 15.9E BNC JACK 1.350 & 34.3S SPECIALF BNC PLUG 1.280 & 32.5*Not recommended for use with this series.LENGTH:The approximate length of a Lark HQ series filter can be determined by the formula:( 0.5 N + 2 / %BW ) x LC = LWhere N is the number of sections used, % BW is:3dB BW (MHz) x 100divided byCENTER FREQUENCY (MHz)LC is the length constant at the specified center frequency, L is the dimension between theconnectors; C1 and C2 are the connector lengths as shown above. All of the length information given here is approximate. Exact length specifications must be quoted by the factory. If a special length is needed,please submit all of your requirements - both electrical and mechanical. This will enable Lark Engineering to quote the optimum design for your application.Example:A 3 section HQ with a center frequency of 400 MHz a 3dB BW of 40 MHz and SMA jack input and output connectors would be:(1.5 + 0.2) x 1.38 = 2.35 + C1 + C2In most cases, the L dimension is rounded to the nearest 1/4 inch which in this instance would be 2.25inches and the O.A.L. is:2.25 + .800 + .800 =3.85 inches.To convert inches to millimeters multiply x 25.40.Lark Engineering HQ SERIES元器件交易网STOPBAND ATTENUATIONThe graph on the following pages defines the normal specification limits on attenuation Lark bandpass filter series HP, HQ, SF, and SM. The minimum level of attenuation in dB is shown as a "number of 3dB bandwidths from center frequency".Since the frequency characteristics vary for differing bandwidths, it is necessary to establishspecifications for each bandwidth of filter. The different graphs represent various 3dB percentage bandwidths. Intermediate values should be interpolated. The 3dB percentage bandwidth is defined asfollows:STOPATT5.HTM元器件交易网As the 3dB bandwidth is exactly 10% of the center frequency, the answer can be read directly from the 10% graph. Using the 5 section curve at the point -1.5 (255 MHz) we find the minimum level of attenuation is 36dB. At +1.6 (348 MHz) the minimum level of attenuation is 48dB.For special requirements, please contact our Application Engineering Department.STOPBAND ATTENUATIONSTOPBAND ATTENUATIONSTOPATT5.HTM元器件交易网STOPBAND ATTENUATIONSTOPBAND ATTENUATIONSTOPBAND ATTENUATION。

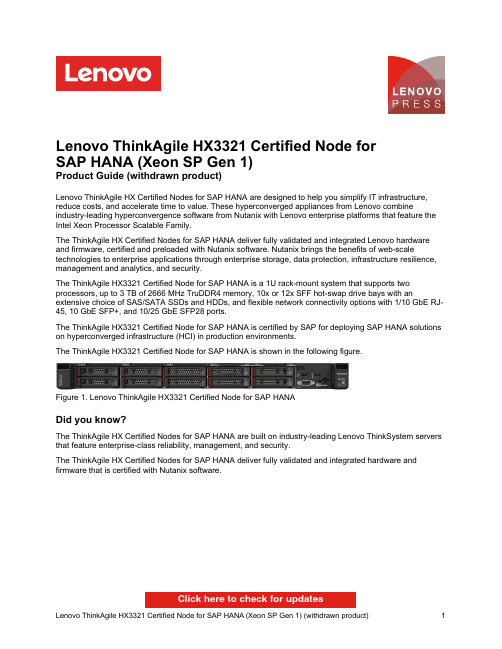

Lenovo ThinkAgile HX3321 Certified Node for SAP HA

Lenovo ThinkAgile HX3321 Certified Node forSAP HANA (Xeon SP Gen 1)Product Guide (withdrawn product)Lenovo ThinkAgile HX Certified Nodes for SAP HANA are designed to help you simplify IT infrastructure, reduce costs, and accelerate time to value. These hyperconverged appliances from Lenovo combine industry-leading hyperconvergence software from Nutanix with Lenovo enterprise platforms that feature the Intel Xeon Processor Scalable Family.The ThinkAgile HX Certified Nodes for SAP HANA deliver fully validated and integrated Lenovo hardware and firmware, certified and preloaded with Nutanix software. Nutanix brings the benefits of web-scale technologies to enterprise applications through enterprise storage, data protection, infrastructure resilience, management and analytics, and security.The ThinkAgile HX3321 Certified Node for SAP HANA is a 1U rack-mount system that supports two processors, up to 3 TB of 2666 MHz TruDDR4 memory, 10x or 12x SFF hot-swap drive bays with an extensive choice of SAS/SATA SSDs and HDDs, and flexible network connectivity options with 1/10 GbE RJ-45, 10 GbE SFP+, and 10/25 GbE SFP28 ports.The ThinkAgile HX3321 Certified Node for SAP HANA is certified by SAP for deploying SAP HANA solutions on hyperconverged infrastructure (HCI) in production environments.The ThinkAgile HX3321 Certified Node for SAP HANA is shown in the following figure.Figure 1. Lenovo ThinkAgile HX3321 Certified Node for SAP HANADid you know?The ThinkAgile HX Certified Nodes for SAP HANA are built on industry-leading Lenovo ThinkSystem servers that feature enterprise-class reliability, management, and security.The ThinkAgile HX Certified Nodes for SAP HANA deliver fully validated and integrated hardware and firmware that is certified with Nutanix software.Click here to check for updatesFigure 2. ThinkAgile HX3321 Certified Node for SAP HANA front viewFigure 3. ThinkAgile HX3321 Certified Node for SAP HANA 10-drive bay rear viewThe following figure shows the rear view of the ThinkAgile HX3321 Certified Node for SAP HANA with 12 drive bays.Figure 4. ThinkAgile HX3321 Certified Node for SAP HANA 12-drive bay rear viewThe rear of the ThinkAgile HX3321 Certified Node for SAP HANA includes the following components: Three (models with 10 drive bays) or one (models with 12 drive bays) PCIe expansion slotsTwo SFF SAS/SATA hot-swap rear drive bays (models with 12 drive bays)One LOM card slotOne 1 GbE port for XClarity ControllerOne VGA portTwo USB 3.0 portsTwo hot-swap power suppliesTable 4. Memory selection optionsDescription Part number Featurecode Quantity2666 MHz RDIMMsThinkSystem 8GB TruDDR4 2666 MHz (1Rx8 1.2V) RDIMM 7X77A01301AUU1-12+12------ThinkSystem 16GB TruDDR4 2666 MHz (2Rx8 1.2V) RDIMM 7X77A01303AUNC 12-12+12----ThinkSystem 32GB TruDDR4 2666 MHz (2Rx4 1.2V) RDIMM 7X77A01304AUND --1224---2666 MHz LRDIMMsThinkSystem 64GB TruDDR4 2666 MHz (4Rx4 1.2V) LRDIMM 7X77A01305AUNE ----1224--2666 MHz 3DS RDIMMsThinkSystem 64GB TruDDR4 2666MHz (4Rx4, 1.2V) 3DS RDIMM4ZC7A08716AUW5------12+12-ThinkSystem 128GB TruDDR4 2666 MHz (8Rx4 1.2V) 3DS RDIMM 7X77A01307AUNF-----1224192 G B288 G B384 G B576 G B768 G B1.5 T B2.25 T B 3 T B3m Cat6 Green Cable 00WE139AVG010m Cat6 Green Cable 90Y3718A1MT 25m Cat6 Green Cable90Y3727A1MWDescriptionPart number Feature code The following table lists transceivers and cables for the 10 GbE SFP+ ports.Table 11. Transceivers and cables for 10 GbE SFP+ portsDescriptionPart numberFeature code10 GbE SFP+ SR transceivers for 10 GbE SFP+ ports Lenovo 10GBASE-SR SFP+ Transceiver 46C34475053Lenovo 10GBASE-LR SFP+ Transceiver 00FE331B0RJOptical cables for 10 GbE SFP+ SR transceivers Lenovo 0.5m LC-LC OM3 MMF Cable 00MN499ASR5Lenovo 1m LC-LC OM3 MMF Cable 00MN502ASR6Lenovo 3m LC-LC OM3 MMF Cable 00MN505ASR7Lenovo 5m LC-LC OM3 MMF Cable 00MN508ASR8Lenovo 10m LC-LC OM3 MMF Cable 00MN511ASR9Lenovo 15m LC-LC OM3 MMF Cable 00MN514ASRA Lenovo 25m LC-LC OM3 MMF Cable00MN517ASRB Passive SFP+ DAC cables for 10 GbE SFP+ ports Lenovo 0.5m Passive SFP+ DAC Cable 00D6288A3RG Lenovo 1m Passive SFP+ DAC Cable 90Y9427A1PH Lenovo 1.5m Passive SFP+ DAC Cable 00AY764A51N Lenovo 2m Passive SFP+ DAC Cable 00AY765A51P Lenovo 3m Passive SFP+ DAC Cable 90Y9430A1PJ Lenovo 5m Passive SFP+ DAC Cable 90Y9433A1PK Lenovo 7m Passive SFP+ DAC Cable00D6151A3RHActive SFP+ DAC cables for 10 GbE SFP+ ports Lenovo 1m Active DAC SFP+ Cable 00VX111AT2R Lenovo 3m Active DAC SFP+ Cable 00VX114AT2S Lenovo 5m Active DAC SFP+ Cable00VX117AT2TSFP+ active optical cables for 10 GbE SFP+ ports Lenovo 1m SFP+ to SFP+ Active Optical Cable 00YL634ATYX Lenovo 3m SFP+ to SFP+ Active Optical Cable 00YL637ATYY Lenovo 5m SFP+ to SFP+ Active Optical Cable 00YL640ATYZ Lenovo 7m SFP+ to SFP+ Active Optical Cable 00YL643ATZ0Lenovo 15m SFP+ to SFP+ Active Optical Cable 00YL646ATZ1Lenovo 20m SFP+ to SFP+ Active Optical Cable00YL649ATZ2The following table lists transceivers and cables for the 25 GbE SFP28 ports. Table 12. Transceivers and cables for 25 GbE SFP28 portsDescription Part number Feature code25 GbE SFP28 SR transceivers for 25 GbE SFP28 portsLenovo 25GBASE-SR SFP28 Transceiver7G17A03537AV1B Optical cables for 25 GbE SFP28 SR transceiversLenovo 0.5m LC-LC OM3 MMF Cable00MN499ASR5 Lenovo 1m LC-LC OM3 MMF Cable00MN502ASR6 Lenovo 3m LC-LC OM3 MMF Cable00MN505ASR7 Lenovo 5m LC-LC OM3 MMF Cable00MN508ASR8 Lenovo 10m LC-LC OM3 MMF Cable00MN511ASR9 Lenovo 15m LC-LC OM3 MMF Cable00MN514ASRA Lenovo 25m LC-LC OM3 MMF Cable00MN517ASRB Passive copper cables for 25 GbE SFP28 portsLenovo 1m Passive 25G SFP28 DAC Cable7Z57A03557AV1W Lenovo 3m Passive 25G SFP28 DAC Cable7Z57A03558AV1X Lenovo 5m Passive 25G SFP28 DAC Cable7Z57A03559AV1Y Active optical cables for 25 GbE SFP28 portsLenovo 3m 25G SFP28 Active Optical Cable7Z57A03541AV1F Lenovo 5m 25G SFP28 Active Optical Cable7Z57A03542AV1G Lenovo 10m 25G SFP28 Active Optical Cable7Z57A03543AV1H Lenovo 15m 25G SFP28 Active Optical Cable7Z57A03544AV1J Lenovo 20m 25G SFP28 Active Optical Cable7Z57A03545AV1KPower supplies and cablesThe ThinkAgile HX3321 Certified Nodes for SAP HANA ship with two power supplies. The following table lists the power supply options that are available for selection.Table 13. Power supply selection optionsDescription Featurecode QuantityThinkSystem 750W (230/115V) Platinum Hot-Swap Power Supply AVWA2 ThinkSystem 750W (230V) Titanium Hot-Swap Power Supply AVW92 ThinkSystem 1100W (230V/115V) Platinum Hot-Swap Power Supply AVWB2Israel 2.8m, 10A/250V, C13 to SI 32 Line Cord 39Y79206218Israel 4.3m, 10A/250V, C13 to SI 32 Line Cord 81Y23816579Italy 2.8m, 10A/250V, C13 to CEI 23-16 Line Cord 39Y79216217Italy 4.3m, 10A/250V, C13 to CEI 23-16 Line Cord 81Y23806493Japan 2.8m, 12A/125V, C13 to JIS C-8303 Line cord 46M2593A1RE Japan 2.8m, 12A/250V, C13 to JIS C-8303 Line Cord 4L67A083575472Japan 4.3m, 12A/125V, C13 to JIS C-8303 Line Cord 39Y79266335Japan 4.3m, 12A/250V, C13 to JIS C-8303 Line Cord 4L67A083626495Korea 2.8m, 12A/250V, C13 to KS C8305 Line Cord 39Y79256219Korea 4.3m, 12A/250V, C13 to KS C8305 Line Cord 81Y23856494South Africa 2.8m, 10A/250V, C13 to SABS 164 Line Cord 39Y79226214South Africa 4.3m, 10A/250V, C13 to SABS 164 Line Cord 81Y23796576Switzerland 2.8m, 10A/250V, C13 to SEV 1011-S24507 Line Cord 39Y79196216Switzerland 4.3m, 10A/250V, C13 to SEV 1011-S24507 Line Cord 81Y23906578Taiwan 2.8m, 10A/125V, C13 to CNS 10917-3 Line Cord 23R71586386Taiwan 2.8m, 10A/250V, C13 to CNS 10917-3 Line Cord 81Y23756317Taiwan 2.8m, 15A/125V, C13 to CNS 10917-3 Line Cord 81Y23746402Taiwan 4.3m, 10A/125V, C13 to CNS 10917-3 Line Cord 4L67A08363AX8BTaiwan 4.3m, 10A/250V, C13 to CNS 10917-3 Line Cord 81Y23896531Taiwan 4.3m, 15A/125V, C13 to CNS 10917-3 Line Cord 81Y23886530United Kingdom 2.8m, 10A/250V, C13 to BS 1363/A Line Cord 39Y79236215United Kingdom 4.3m, 10A/250V, C13 to BS 1363/A Line Cord 81Y23776577United States 2.8m, 10A/125V, C13 to NEMA 5-15P Line Cord 90Y30166313United States 2.8m, 10A/250V, C13 to NEMA 6-15P Line Cord 46M2592A1RF United States 2.8m, 13A/125V, C13 to NEMA 5-15P Line Cord 00WH5456401United States 4.3m, 10A/125V, C13 to NEMA 5-15P Line Cord 4L67A083596370United States 4.3m, 10A/250V, C13 to NEMA 6-15P Line Cord 4L67A083616373United States 4.3m, 13A/125V, C13 to NEMA 5-15P Line Cord4L67A08360AX8ADescriptionPart number Feature code Configuration note: If the 1100 W AC power supplies in the certified node are connected to a low-voltage power source (100 - 125 V), the only supported power cables are those that are rated above 10 A; cables that are rated at 10 A are not supported.Rack installationRack installationThe ThinkAgile HX3321 Certified Nodes for SAP HANA ship with a rail kit. The following table lists the rail kit options that are available for selection.Table 15. Rack kit selection optionsDescription FeaturecodeQuantity(min / max)4-post rail kitsThinkSystem Tool-less Slide Rail AXCA0 / 1 ThinkSystem Tool-less Slide Rail Kit with 1U CMA AXCB0 / 1 Lockable front bezelThinkSystem 1U Security Bezel AUWR0 / 1Configuration note: One of the rail kits is required for selection.The following table summarizes the rail kit features and specifications.Table 16. Rail kit features and specifications summaryFeature Tool-less Slide RailWithout CMA With 1U CMACMA Not included IncludedRail length730 mm (28.74 in.)807 mm (31.8 in.)Rail type Full-out slide (ball bearing)Tool-less installation YesIn-rack maintenance Yes1U PDU support Yes0U PDU support Limited*Rack type IBM and Lenovo 4-post, IEC standard-compliant Mounting holes Square or roundMounting flange thickness 2 mm (0.08 in.) – 3.3 mm (0.13 in.)Distance between front and rear mounting flanges^609.6 mm (24 in.) – 863.6 mm (34 in.)* If a 0U PDU is used, the rack cabinet must be at least 1100 mm (43.31 in.) deep if no CMA is used, or at least 1200 mm (47.24 in.) deep if a CMA is used.^ Measured when mounted on the rack, from the front surface of the front mounting flange to the rear most point of the rail.TrademarksLenovo and the Lenovo logo are trademarks or registered trademarks of Lenovo in the United States, other countries, or both. A current list of Lenovo trademarks is available on the Web athttps:///us/en/legal/copytrade/.The following terms are trademarks of Lenovo in the United States, other countries, or both:Lenovo®AnyBay®Lenovo ServicesThinkAgile®ThinkSystem®TruDDR4XClarity®The following terms are trademarks of other companies:Intel® and Xeon® are trademarks of Intel Corporation or its subsidiaries.Linux® is the trademark of Linus Torvalds in the U.S. and other countries.Microsoft®, PowerShell, Windows PowerShell®, and Windows® are trademarks of Microsoft Corporation in the United States, other countries, or both.Other company, product, or service names may be trademarks or service marks of others.。

netgear-ag731f-1.0625gbd-fiber-channel-and-gigabit