M74HCT174RM13TR中文资料

M74HC7266RM13TR,M74HC7266RM13TR,M74HC7266RM13TR,M74HC7266RM13TR, 规格书,Datasheet 资料

1/9July 2001sHIGH SPEED:t PD = 9ns (TYP .) at V CC = 6V sLOW POWER DISSIPATION:I CC = 1µA(MAX.) at T A =25°C sHIGH NOISE IMMUNITY:V NIH = V NIL = 28 % V CC (MIN.)sSYMMETRICAL OUTPUT IMPEDANCE:|I OH | = I OL = 4mA (MIN)sBALANCED PROPAGATION DELAYS:t PLH ≅ t PHLsWIDE OPERATING VOLTAGE RANGE:V CC (OPR) = 2V to 6VsPIN AND FUNCTION COMPATIBLE WITH 74 SERIES 7266DESCRIPTIONThe M74HC7266 is an high speed CMOS QUAD EXCLUSIVE OR GATE fabricated with silicon gate C 2MOS technologyThe M74HC7266 has an output buffer which is CMOS structure.Input and Output ensure high noise immunity and stable outputs.All inputs are equipped with protection circuits against static discharge and transient excess voltage.M74HC7266QUAD EXCLUSIVE NOR GATEPIN CONNECTION AND IEC LOGIC SYMBOLSORDER CODESPACKAGE TUBE T & RDIP M74HC7266B1R SOP M74HC7266M1RM74HC7266RM13TR TSSOPM74HC7266TTRM74HC72662/9INPUT AND OUTPUT EQUIVALENT CIRCUITPIN DESCRIPTIONTRUTH TABLEABSOLUTE MAXIMUM RATINGSAbsolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied(*) 500mW at 65 °C; derate to 300mW by 10mW/°C from 65°C to 85°CRECOMMENDED OPERATING CONDITIONSPIN No SYMBOL NAME AND FUNCTION 1, 5, 8, 121A to 4A Data Inputs 2, 6, 9, 131B to 4B Data Inputs 3, 4, 10, 111Y to 4Y Data Outputs 7GND Ground (0V)14V CCPositive Supply VoltageA B Y L L H L H L H L L HHHSymbol ParameterValue Unit V CC Supply Voltage -0.5 to +7V V I DC Input Voltage -0.5 to V CC + 0.5V V O DC Output Voltage -0.5 to V CC + 0.5V I IK DC Input Diode Current ± 20mA I OK DC Output Diode Current ± 20mA I ODC Output Current± 25mA I CC or I GND DC V CC or Ground Current± 50mA P D Power Dissipation500(*)mW T stg Storage Temperature -65 to +150°C T LLead Temperature (10 sec)300°CSymbol ParameterValue Unit V CC Supply Voltage 2 to 6V V I Input Voltage 0 to V CC V V O Output Voltage 0 to V CC V T op Operating Temperature -55 to 125°C t r , t fInput Rise and Fall TimeV CC = 2.0V 0 to 1000ns V CC = 4.5V 0 to 500ns V CC = 6.0V0 to 400nsM74HC72663/9DC SPECIFICATIONSAC ELECTRICAL CHARACTERISTICS (C L = 50 pF, Input t r = t f = 6ns)SymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.V IHHigh Level Input Voltage2.0 1.5 1.5 1.5V 4.53.15 3.15 3.156.04.24.24.2V ILLow Level Input Voltage2.00.50.50.5V4.5 1.35 1.35 1.356.0 1.81.81.8V OHHigh Level Output Voltage2.0I O =-20 µA 1.9 2.0 1.9 1.9V4.5I O =-20 µA 4.4 4.5 4.4 4.46.0I O =-20 µA5.96.0 5.9 5.94.5I O =-4.0 mA 4.18 4.31 4.13 4.106.0I O =-5.2 mA 5.685.8 5.635.60V OLLow Level Output Voltage2.0I O =20 µA 0.00.10.10.1V 4.5I O =20 µA 0.00.10.10.16.0I O =20 µA 0.00.10.10.14.5I O =4.0 mA 0.170.260.330.406.0I O =5.2 mA 0.180.260.330.40I I Input Leakage Current6.0V I = V CC or GND ± 0.1± 1± 1µA I CCQuiescent Supply Current6.0V I = V CC or GND11020µA SymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.t TLH t THL Output TransitionTime 2.0307595110ns 4.581519226.07131619t PLH t PHL Propagation DelayTime2.03690115135ns4.5111823276.09152023M74HC72664/9CAPACITIVE CHARACTERISTICS1) C PD is defined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption without load. (Refer to Test Circuit). Average operating current can be obtained by the following equation. I CC(opr) = C PD x V CC x f IN + I CC /4 (per gate)TEST CIRCUITL R T = Z OUT of pulse generator (typically 50Ω)SymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.C IN Input Capacitance 5.05101010pF C PDPower Dissipation Capacitance (note 1)5.020pFM74HC72665/9WAVEFORM 1: PROPAGATION DELAY TIME(f=1MHz; 50% duty cycle)M74HC7266 Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.© The ST logo is a registered trademark of STMicroelectronics© 2001 STMicroelectronics - Printed in Italy - All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - MoroccoSingapore - Spain - Sweden - Switzerland - United Kingdom© 9/9。

74HC00中文资料_数据手册_参数

IO = −20 µA

2.0

IO = −20 µA

4.5

IO = −20 µA

6.0

IO = −4.0 mA

4.5

IO = −5.2 mA

6.0

VOL

LOW-level output voltage VI = VIH or VIL

IO = 20 µA

2.0

IO = 20 µA

4.5

IO = 20 µA

RECOMMENDED OPERATING CONDITIONS

SYMBOL

PARAMETER

VCC VI VO Tamb

supply voltage input voltage output voltage operating ambient temperature

tr, tf

input rise and fall times

74HC00; 74HCT00

handbook, halfpage

1B 2

1A VCC 1 14

13 4B

1Y 3

12 4A

2A 4 2B 5

GND(1)

11 4Y 10 3B

2Y 6 78

Top view GND 3Y

9 3A

MNA950

handbook, halfpage A B

Y

MNA211

(1) The die substrate is attached to this pad using conductive die attach material. It can not be used as a supply pin or input.

6.0

IO = 4.0 mA

CD74HC174中文资料

110

Maximum Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . 150oC

Maximum Storage Temperature Range . . . . . . . . . .-65oC to 150oC

Copyright © Harris Corporation 1997

1

File Number 1608.1

元器件交易网 Functional Diagram

CD74HC174, CD74HCT174

CP D0

D1

CP

D

Q0

R

Q1

D2

Q2

D3

Q3

D4

Q4

D5

Q5

MR

TRUTH TABLE

TEMP. RANGE

PART NUMBER

(oC)

PACKAGE

CD74HC174E

-55 to 125 16 Ld PDIP

CD74HCT174E

-55 to 125 16 Ld PDIP

CD74HC174M

-55 to 125 16 Ld SOIC

PKG. NO. E16.3 E16.3 M16.15

Maximum Lead Temperature (Soldering 10s) . . . . . . . . . . . . . 300oC

(SOIC - Lead Tips Only)

Operating Conditions

Temperature Range (TA) . . . . . . . . . . . . . . . . . . . . . -55oC to 125oC Supply Voltage Range, VCC

74HC74PW中文资料

74HC74; 74HCT74

handbook, halfpage handbook, halfpage

1RD 1

VCC 14 13 12 2RD 2D 2CP 2SD 2Q

1RD 1D 1CP 1SD 1Q 1Q GND

1 2 3 4 5 6 7

MNA417

14 VCC 13 2RD 12 2D

1D 1CP 1SD 1Q

Fig.1

Pin configuration DIP14, SO14 and (T)SSOP14.

Fig.2 Pin configuration DHVQFN14.

2003 Jul 10

4

元器件交易网

Philips Semiconductors

Product specification

元器件交易网

INTEGRATED CIRCUITS

DATA SHEET

74HC74; 74HCT74 Dual D-type flip-flop with set and reset; positive-edge trigger

Product specification Supersedes data of 1998 Feb 23 2003 Jul 10

2003 Jul 10

2

元器件交易网

Philips Semiconductors

Product specification

Dual D-type flip-flop with set and reset; positive-edge trigger

FUNCTION TABLES Table 1 See note 1 INPUT SD L H L Table 2 See note 1 INPUT SD H H Note 1. H = HIGH voltage level; L = LOW voltage level; X = don’t care; ↑ = LOW-to-HIGH CP transition; Qn+1 = state after the next LOW-to-HIGH CP transition. ORDERING INFORMATION PACKAGE TYPE NUMBER 74HC74N 74HCT74N 74HC74D 74HCT74D 74HC74DB 74HCT74DB 74HC74PW 74HCT74PW 74HC74BQ 74HCT74BQ TEMPERATURE RANGE −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C PINS 14 14 14 14 14 14 14 14 14 14 PACKAGE DIP14 DIP14 SO14 SO14 SSOP14 SSOP14 TSSOP14 TSSOP14 DHVQFN14 DHVQFN14 RD H H CP ↑ ↑ D L H RD H L L CP X X X D X X X

74系列芯片功能大全

74系列芯片功能大全同型号的74系列、74HC系列、74LS系列芯片,逻辑功能上是一样的。

74LSxx、74HCxx的使用说明可参阅74xx的使用说明。

有些型号里包含了几种型号,如74HC161资料里包含了74HC160、74HC161、74HC162、74HC163四种芯片的功能。

7400 TTL 2输入端四与非门7401 TTL 集电极开路2输入端四与非门7402 TTL 2输入端四或非门7403 TTL 集电极开路2输入端四与非门7404 TTL 六反相器7405 TTL 集电极开路六反相器7406 TTL 集电极开路六反相高压驱动器7407 TTL 集电极开路六正相高压驱动器7408 TTL 2输入端四与门7409 TTL 集电极开路2输入端四与门7410 TTL 3输入端3与非门74107 TTL 带清除主从双J-K触发器74109 TTL 带预置清除正触发双J-K触发器7411 TTL 3输入端3与门74112 TTL 带预置清除负触发双J-K触发器7412 TTL 开路输出3输入端三与非门74121 TTL 单稳态多谐振荡器74122 TTL 可再触发单稳态多谐振荡器74123 TTL 双可再触发单稳态多谐振荡器74125 TTL 三态输出高有效四总线缓冲门74126 TTL 三态输出低有效四总线缓冲门7413 TTL 4输入端双与非施密特触发器74132 TTL 2输入端四与非施密特触发器74133 TTL 13输入端与非门74136 TTL 四异或门74138 TTL 3-8线译码器/复工器74139 TTL 双2-4线译码器/复工器7414 TTL 六反相施密特触发器74145 TTL BCD—十进制译码/驱动器7415 TTL 开路输出3输入端三与门74150 TTL 16选1数据选择/多路开关74151 TTL 8选1数据选择器74153 TTL 双4选1数据选择器74154 TTL 4线—16线译码器74155 TTL 图腾柱输出译码器/分配器74156 TTL 开路输出译码器/分配器74157 TTL 同相输出四2选1数据选择器74158 TTL 反相输出四2选1数据选择器7416 TTL 开路输出六反相缓冲/驱动器74160 TTL 可预置BCD异步清除计数器74161 TTL 可予制四位二进制异步清除计数器74162 TTL 可预置BCD同步清除计数器74163 TTL 可予制四位二进制同步清除计数器74164 TTL 八位串行入/并行输出移位寄存器74165 TTL 八位并行入/串行输出移位寄存器74166 TTL 八位并入/串出移位寄存器74169 TTL 二进制四位加/减同步计数器7417 TTL 开路输出六同相缓冲/驱动器74170 TTL 开路输出4×4寄存器堆74173 TTL 三态输出四位D型寄存器74174 TTL 带公共时钟和复位六D触发器74175 TTL 带公共时钟和复位四D触发器74180 TTL 9位奇数/偶数发生器/校验器74181 TTL 算术逻辑单元/函数发生器74185 TTL 二进制—BCD代码转换器74190 TTL BCD同步加/减计数器74191 TTL 二进制同步可逆计数器74192 TTL 可预置BCD双时钟可逆计数器74193 TTL 可预置四位二进制双时钟可逆计数器74194 TTL 四位双向通用移位寄存器74195 TTL 四位并行通道移位寄存器74196 TTL 十进制/二-十进制可预置计数锁存器74197 TTL 二进制可预置锁存器/计数器7420 TTL 4输入端双与非门7421 TTL 4输入端双与门7422 TTL 开路输出4输入端双与非门74221 TTL 双/单稳态多谐振荡器74240 TTL 八反相三态缓冲器/线驱动器74241 TTL 八同相三态缓冲器/线驱动器74243 TTL 四同相三态总线收发器74244 TTL 八同相三态缓冲器/线驱动器74245 TTL 八同相三态总线收发器74247 TTL BCD—7段15V输出译码/驱动器74248 TTL BCD—7段译码/升压输出驱动器74249 TTL BCD—7段译码/开路输出驱动器74251 TTL 三态输出8选1数据选择器/复工器74253 TTL 三态输出双4选1数据选择器/复工器74256 TTL 双四位可寻址锁存器74257 TTL 三态原码四2选1数据选择器/复工器74258 TTL 三态反码四2选1数据选择器/复工器74259 TTL 八位可寻址锁存器/3-8线译码器7426 TTL 2输入端高压接口四与非门74260 TTL 5输入端双或非门74266 TTL 2输入端四异或非门7427 TTL 3输入端三或非门74273 TTL 带公共时钟复位八D触发器74279 TTL 四图腾柱输出S-R锁存器7428 TTL 2输入端四或非门缓冲器74283 TTL 4位二进制全加器74290 TTL 二/五分频十进制计数器74293 TTL 二/八分频四位二进制计数器74295 TTL 四位双向通用移位寄存器74298 TTL 四2输入多路带存贮开关74299 TTL 三态输出八位通用移位寄存器7430 TTL 8输入端与非门7432 TTL 2输入端四或门74322 TTL 带符号扩展端八位移位寄存器74323 TTL 三态输出八位双向移位/存贮寄存器7433 TTL 开路输出2输入端四或非缓冲器74347 TTL BCD—7段译码器/驱动器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74352 TTL 双4选1数据选择器/复工器74353 TTL 三态输出双4选1数据选择器/复工器74365 TTL 门使能输入三态输出六同相线驱动器74366 TTL 门使能输入三态输出六反相线驱动器74367 TTL 4/2线使能输入三态六同相线驱动器74368 TTL 4/2线使能输入三态六反相线驱动器7437 TTL 开路输出2输入端四与非缓冲器74373 TTL 三态同相八D锁存器74374 TTL 三态反相八D锁存器74375 TTL 4位双稳态锁存器74377 TTL 单边输出公共使能八D锁存器74378 TTL 单边输出公共使能六D锁存器74379 TTL 双边输出公共使能四D锁存器7438 TTL 开路输出2输入端四与非缓冲器74380 TTL 多功能八进制寄存器7439 TTL 开路输出2输入端四与非缓冲器74390 TTL 双十进制计数器74393 TTL 双四位二进制计数器7440 TTL 4输入端双与非缓冲器7442 TTL BCD—十进制代码转换器74447 TTL BCD—7段译码器/驱动器7445 TTL BCD—十进制代码转换/驱动器74450 TTL 16:1多路转接复用器多工器74451 TTL 双8:1多路转接复用器多工器74453 TTL 四4:1多路转接复用器多工器7446 TTL BCD—7段低有效译码/驱动器74460 TTL 十位比较器74461 TTL 八进制计数器74465 TTL 三态同相2与使能端八总线缓冲器74466 TTL 三态反相2与使能八总线缓冲器74467 TTL 三态同相2使能端八总线缓冲器74468 TTL 三态反相2使能端八总线缓冲器74469 TTL 八位双向计数器7447 TTL BCD—7段高有效译码/驱动器7448 TTL BCD—7段译码器/内部上拉输出驱动74490 TTL 双十进制计数器74491 TTL 十位计数器74498 TTL 八进制移位寄存器7450 TTL 2-3/2-2输入端双与或非门74502 TTL 八位逐次逼近寄存器74503 TTL 八位逐次逼近寄存器7451 TTL 2-3/2-2输入端双与或非门74533 TTL 三态反相八D锁存器74534 TTL 三态反相八D锁存器7454 TTL 四路输入与或非门74540 TTL 八位三态反相输出总线缓冲器7455 TTL 4输入端二路输入与或非门74563 TTL 八位三态反相输出触发器74564 TTL 八位三态反相输出D触发器74573 TTL 八位三态输出触发器74574 TTL 八位三态输出D触发器74645 TTL 三态输出八同相总线传送接收器74670 TTL 三态输出4×4寄存器堆7473 TTL 带清除负触发双J-K触发器7474 TTL 带置位复位正触发双D触发器7476 TTL 带预置清除双J-K触发器7483 TTL 四位二进制快速进位全加器7485 TTL 四位数字比较器7486 TTL 2输入端四异或门7490 TTL 可二/五分频十进制计数器7493 TTL 可二/八分频二进制计数器7495 TTL 四位并行输入\输出移位寄存器7497 TTL 6位同步二进制乘法器常用74系列标准数字电路的中文名称资料器件代号器件名称 74 74LS 74HC00 四2输入端与非门√√√01 四2输入端与非门(OC) √√02 四2输入端或非门√√√03 四2输入端与非门(OC) √√04 六反相器√√√05 六反相器(OC) √√06 六高压输出反相器(OC,30V) √√07 六高压输出缓冲,驱动器(OC,30V) √√√08 四2输入端与门√√√09 四2输入端与门(OC) √√√10 三3输入端与非门√√√11 三3输入端与门√√12 三3输入端与非门(OC) √√√13 双4输入端与非门√√√14 六反相器√√√15 三3输入端与门 (OC) √√16 六高压输出反相器(OC,15V) √17 六高压输出缓冲,驱动器(OC,15V) √20 双4输入端与非门√√√21 双4输入端与门√√√22 双4输入端与非门(OC) √√25 双4输入端或非门(有选通端) √√√26 四2输入端高压输出与非缓冲器√√√27 三3输入端或非门√√√28 四2输入端或非缓冲器√√√30 8输入端与非门√√√32 四2输入端或门√√√33 四2输入端或非缓冲器(OC) √√37 四2输入端与非缓冲器√√38 四2输入端与非缓冲器(OC) √√40 双4输入端与非缓冲器√√√42 4线-10线译码器(BCD输入) √√43 4线-10线译码器(余3码输入) √44 4线-10线译码器(余3葛莱码输入) √48 4线-7段译码器√49 4线-7段译码器√50 双2路2-2输入与或非门√√√51 2路3-3输入,2路2-2输入与或非门√√√52 4路2-3-2-2输入与或门√53 4路2-2-2-2输入与或非门√54 4路2-3-3-2输入与或非门√√55 2路4-4输入与或非门√60 双4输入与扩展器√√61 三3输入与扩展器√62 4路2-3-3-2输入与或扩展器√64 4路4-2-3-2输入与或非门√65 4路4-2-3-2输入与或非门(OC) √70 与门输入J-K触发器√71 与或门输入J-K触发器√72 与门输入J-K触发器√74 双上升沿D型触发器√√78 双D型触发器√√85 四位数值比较器√86 四2输入端异或门√√√87 4位二进制原码/反码√95 4位移位寄存器√101 与或门输入J-K触发器√102 与门输入J-K触发器√107 双主-从J-K触发器√108 双主-从J-K触发器√109 双主-从J-K触发器√110 与门输入J-K触发器√111 双主-从J-K触发器√√112 双下降沿J-K触发器√113 双下降沿J-K触发器√114 双下降沿J-K触发器√116 双4位锁存器√120 双脉冲同步驱动器√121 单稳态触发器√√√122 可重触发单稳态触发器√√√123 可重触发双稳态触发器√√√125 四总线缓冲器√√√126 四总线缓冲器√√√128 四2输入端或非线驱动器√√√132 四2输入端与非门√√√。

HD74HC174中文资料

Q CLR

D CK

Q CLR

CK D

16 VCC 15 6Q 14 6D

D CK CLR

Q

CK D CLR

Q

13 5D 12 5Q

D CK CLR

Q

CK D CLR

Q

11 4D 10 4Q

9 Clock

(Top view)

Clock 1D

Clear 2D

3D

4D

5D

6D

CK

Q

1Q

D CL

CK Q

3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi’s sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

Unit: mm

7.80

+ –

74HCT174资料

5

5

ns 2.0 Fig.7 4.5

5 −3

5

5

6.0

tsu

set-up time

Dn to CP

60 6 12 2

75

90

15

18

ns 2.0 Fig.8 4.5

10 2

13

15

6.0

th

hold time

Dn to CP

3 −6

3

3

3 −2

3

3

ns 2.0 Fig.8 4.5

3 −2

3

3

6.0

fmax

Product specification

74HC/HCT174

DC CHARACTERISTICS FOR 74HCT For the DC characteristics see “74HC/HCT/HCU/HCMOS Logic Family Specifications”. Output capability: standard ICC category: MSI

元器件交易网

INTEGRATED CIRCUITS

DATA SHEET

For a complete data sheet, please also download:

• The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications • The IC06 74HC/HCT/HCU/HCMOS Logic Package Information • The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

SYMBOL

MR Q0 to Q5 D0 to D5 GND CP VCC

MC74ACT174中文资料

LOGIC DIAGRAM

MR CP D5 D4 D3 D2 D1 D0

D CP CD

Q

D CP CD

Q

D CP CD

Q

D CP CD

Q

D CP CD

Q

D CP CD

Q

Q5

Q4

Q3

Q2

Q1

Q0

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

The MC74AC174/74ACT174 consists of six edge-triggered D flip-flops with individual D inputs and Q outputs. The Clock (CP) and Master Reset (MR) are common to all flip-flops. Each D input’s state is transferred to the corresponding flip-flop’s output following the LOW-to-HIGH Clock (CP) transition. A LOW input to the Master Reset (MR) will force all outputs LOW independent of Clock or Data inputs. The MC74AC174/ 74ACT174 is useful for applications where the true output only is required and the Clock and Master Reset are common to all storage elements.

74HC123中文资料

Product specification

74HC/HCT123

ORDERING INFORMATION

TYPE NUMBER

74HC123N; 74HCT123N 74HC123D; 74HCT123D 74HC123DB; 74HCT123DB 74HC123PW; 74HCT123PW

NAME DIP16

26 26 ns

nRD to nQ, nQ

REXT = 5 kΩ; CEXT = 0 pF

20

23

ns

CI

input capacitance

3.5 3.5 pF

CPD

power dissipation

capacitance per

notes 1 and 2 54 56 pF

monostable

Notes

An internal connection from nRD to the input gates makes it possible to trigger the circuit by a positive-going signal at input nRD as shown in the function table. Figures 7 and 8 illustrate pulse control by retriggering

2. For HC the condition is VI = GND to VCC For HCT the condition is VI = GND to VCC − 1.5 V

1998 Jul 08

2

元器件交易网

Philips Semiconductors

Dual retriggerable monostable multivibrator with reset

74HCT14中文资料

Fig.4 IEC logic symbol.

2003 Oct 30

4

元器件交易网

Philips Semiconductors

Product specification

Hex inverting Schmitt trigger

74HC14; 74HCT14

handbook, halfpage

2003 Oct 30

2

元器件交易网

Philips Semiconductors

Product specification

Hex inverting Schmitt trigger

FUNCTION TABLE INPUT nA L H Note 1. H = HIGH voltage level; L = LOW voltage level. ORDERING INFORMATION PACKAGE TYPE NUMBER TEMPERATURE RANGE 74HC14D 74HCT14D 74HC14DB 74HCT14DB 74HC14N 74HCT14N 74HC14PW 74HCT14PW 74HC14BQ 74HCT14BQ PINNING PIN 1 2 3 4 5 6 7 8 9 10 11 12 13 14 1A 1Y 2A 2Y 3A 3Y GND 4Y 4A 5Y 5A 6Y 6A VCC SYMBOL data input data output data input data output data input data output ground (0 V) data output data input data output data input data output data input supply voltage −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C −40 to +125 °C PINS 14 14 14 14 14 14 14 14 14 14 PACKAGE SO14 SO14 SSOP14 SSOP14 DIP14 DIP14 TSSOP14 TSSOP14 DHVQFN14 DHVQFN14

M74HCT74RM13TR中文资料

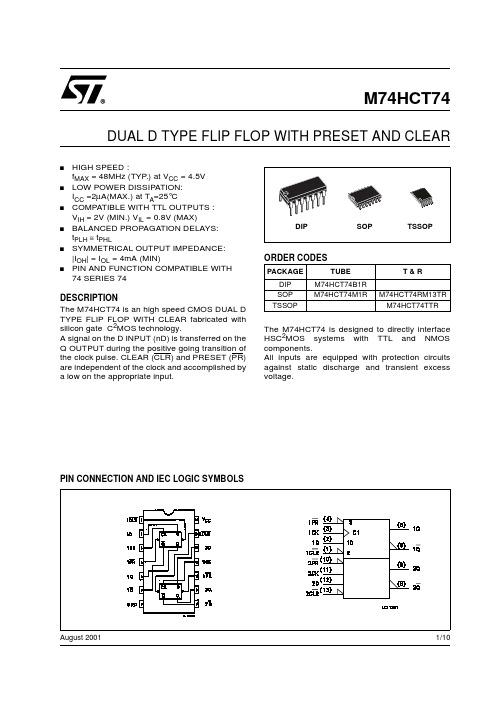

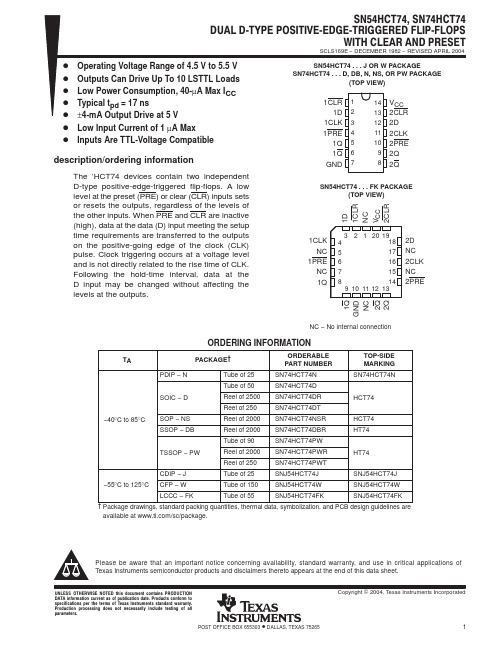

1/10August 2001sHIGH SPEED : f MAX = 48MHz (TYP.) at V CC = 4.5V sLOW POWER DISSIPATION:I CC =2µA(MAX.) at T A =25°CsCOMPATIBLE WITH TTL OUTPUTS : V IH = 2V (MIN.) V IL = 0.8V (MAX)sBALANCED PROPAGATION DELAYS:t PLH ≅ t PHLsSYMMETRICAL OUTPUT IMPEDANCE:|I OH | = I OL = 4mA (MIN)sPIN AND FUNCTION COMPATIBLE WITH 74 SERIES 74DESCRIPTIONThe M74HCT74 is an high speed CMOS DUAL D TYPE FLIP FLOP WITH CLEAR fabricated with silicon gate C 2MOS technology.A signal on the D INPUT (nD) is transferred on the Q OUTPUT during the positive going transition of the clock pulse. CLEAR (CLR) and PRESET (PR)are independent of the clock and accomplished by a low on the appropriate input.The M74HCT74 is designed to directly interface HSC 2MOS systems with TTL and NMOS components.All inputs are equipped with protection circuits against static discharge and transient excess voltage.M74HCT74DUAL D TYPE FLIP FLOP WITH PRESET AND CLEARPIN CONNECTION AND IEC LOGIC SYMBOLSORDER CODESPACKAGE TUBE T & RDIP M74HCT74B1R SOP M74HCT74M1RM74HCT74RM13TR TSSOPM74HCT74TTRM74HCT742/10INPUT AND OUTPUT EQUIVALENT CIRCUITPIN DESCRIPTIONTRUTH TABLELOGIC DIAGRAMPIN No SYMBOL NAME AND FUNCTION 1,131CLR, 2CLR Asynchronous Reset - Direct Input 2, 121D, 2D Data Inputs 3, 111CK, 2CK Clock Input (LOW-to-HIGH, Edge-Triggered)4, 101PR, 2PR Asynchronous Set - Direct Input5, 91Q, 2Q True Flip-Flop Outputs 6, 81Q, 2Q Complement Flip-Flop Outputs 7GND Ground (0V)14VccPositive Supply VoltageM74HCT743/10ABSOLUTE MAXIMUM RATINGSAbsolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied(*) 500mW at 65 °C; derate to 300mW by 10mW/°C from 65°C to 85°CRECOMMENDED OPERATING CONDITIONSDC SPECIFICATIONSSymbol ParameterValue Unit V CC Supply Voltage -0.5 to +7V V I DC Input Voltage -0.5 to V CC + 0.5V V O DC Output Voltage -0.5 to V CC + 0.5V I IK DC Input Diode Current ± 20mA I OK DC Output Diode Current ± 20mA I O DC Output Current ± 25mA I CC or I GND DC V CC or Ground Current± 50mA P D Power Dissipation 500(*)mW T stg Storage Temperature -65 to +150°C T LLead Temperature (10 sec)300°CSymbol ParameterValue Unit V CC Supply Voltage 4.5 to 5.5V V I Input Voltage 0 to V CC V V O Output Voltage 0 to V CC V T op Operating Temperature-55 to 125°C t r , t fInput Rise and Fall Time (V CC = 4.5 to 5.5V)0 to 500nsSymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.V IH High Level Input Voltage4.5 to5.5 2.02.02.0V V IL Low Level Input Voltage4.5 to5.50.80.80.8V V OH High Level Output Voltage4.5I O =-20 µA 4.4 4.5 4.4 4.4VI O =-4.0 mA 4.184.31 4.134.10V OL Low Level Output Voltage4.5I O =20 µA 0.00.10.10.1V I O =4.0 mA 0.170.260.330.40I I Input Leakage Current5.5V I = V CC or GND ± 0.1± 1± 1µA I CC Quiescent Supply Current5.5V I = V CC or GND 22040µA ∆ I CCAdditional Worst Case Supply Current5.5Per Input pin V I = 0.5V or V I = 2.4V Other Inputs at V CC or GND I O = 02.02.93.0mAM74HCT744/10AC ELECTRICAL CHARACTERISTICS (C L = 50 pF, Input t r = t f = 6ns)CAPACITIVE CHARACTERISTICS1) C PD is defined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption without load. (Refer to Test Circuit). Average operating current can be obtained by the following equation. I CC(opr) = C PD x V CC x f IN + I CC /2 (per FLIP/FLOP)SymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.t TLH t THL Output TransitionTime4.58151922ns t PLH t PHL Propagation DelayTime (CLOCK-Q)4.521334150ns t PLH t PHL Propagation DelayTime (CL,PR - Q,Q)4.518303845ns f MAX Maximum ClockFrequency4.527482218MHz t W(H) t W(L)Minimum PulseWidth (CLOCK) 4.56151923ns t W(L)Minimum Pulse Width (CLR, PR) 4.58151923ns t s Minimum Set-Up Time4.57151923ns t h Minimum Hold Time4.5000ns t REMMinimum Removal Time (CLR, PR to CLOCK)4.5155658ns SymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.C IN Input Capacitance 5101010pF C PDPower Dissipation Capacitance (note 1)32pFM74HCT745/10TEST CIRCUITL R T = Z OUT of pulse generator (typically 50Ω)WAVEFORM 1 : PROPAGATION DELAY, MINIMUM SETUP AND HOLD TIME, CK MINIMUM PULSE WIDTH AND MAXIMUM FREQUENCY(f=1MHz; 50% duty cycle)M74HCT746/10WAVEFORM 2 : MINIMUM PULSE WIDTH, PROPAGATION DELAY (f=1MHz; 50% duty cycle)WAVEFORM 3 : MINIMUM PULSE WIDTH AND REMOVAL TIME(f=1MHz; 50% duty cycle)M74HCT74Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.© The ST logo is a registered trademark of STMicroelectronics© 2001 STMicroelectronics - Printed in Italy - All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - MoroccoSingapore - Spain - Sweden - Switzerland - United Kingdom© 10/10。

HCT74资料

PACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)JM38510/65352B2A ACTIVE LCCC FK201TBD POST-PLATE N/A for Pkg Type JM38510/65352BCA ACTIVE CDIP J141TBD A42SNPB N/A for Pkg Type JM38510/65352BDA ACTIVE CFP W141TBD A42N/A for Pkg Type SN74HCT74D ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HCT74DBR ACTIVE SSOP DB142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HCT74DBRE4ACTIVE SSOP DB142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HCT74DE4ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HCT74DG4ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HCT74DR ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HCT74DRE4ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HCT74DRG4ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HCT74DT ACTIVE SOIC D14250Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HCT74DTE4ACTIVE SOIC D14250Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HCT74N ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeSN74HCT74NE4ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeSN74HCT74NSR ACTIVE SO NS142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HCT74NSRE4ACTIVE SO NS142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HCT74PW ACTIVE TSSOP PW1490Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HCT74PWE4ACTIVE TSSOP PW1490Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM SN74HCT74PWLE OBSOLETE TSSOP PW14TBD Call TI Call TISN74HCT74PWR ACTIVE TSSOP PW142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HCT74PWRE4ACTIVE TSSOP PW142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HCT74PWT ACTIVE TSSOP PW14250Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMSN74HCT74PWTE4ACTIVE TSSOP PW14250Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS),Pb-Free(RoHS Exempt),or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free(RoHS Exempt):This component has a RoHS exemption for either1)lead-based flip-chip solder bumps used between the die and package,or2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free(RoHS compatible)as defined above.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.元器件交易网元器件交易网IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications,enhancements, improvements, and other changes to its products and services at any time and to discontinueany product or service without notice. Customers should obtain the latest relevant information before placingorders and should verify that such information is current and complete. All products are sold subject to TI’s termsand conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale inaccordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TIdeems necessary to support this warranty. Except where mandated by government requirements, testing of allparameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible fortheir products and applications using TI components. T o minimize the risks associated with customer productsand applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right,copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or processin which TI products or services are used. Information published by TI regarding third-party products or servicesdoes not constitute a license from TI to use such products or services or a warranty or endorsement thereof.Use of such information may require a license from a third party under the patents or other intellectual propertyof the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is withoutalteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproductionof this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable forsuch altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for thatproduct or service voids all express and any implied warranties for the associated TI product or service andis an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Following are URLs where you can obtain information on other Texas Instruments products and applicationsolutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetworkMicrocontrollers Security /securityLow Power Wireless /lpw Telephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2006, Texas Instruments Incorporated。

M74HCT373RM13TR,M74HCT373RM13TR,M74HCT373RM13TR,M74HCT373TTR,M74HCT373B1R, 规格书,Datasheet 资料

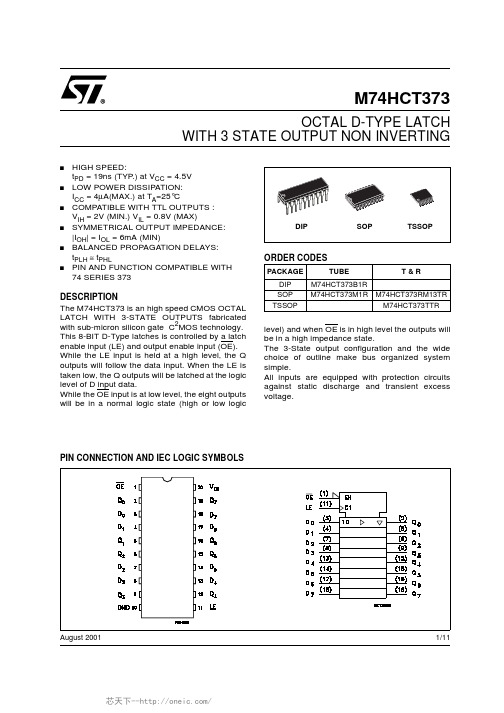

1/11August 2001sHIGH SPEED:t PD = 19ns (TYP .) at V CC = 4.5V sLOW POWER DISSIPATION:I CC = 4µA(MAX.) at T A =25°CsCOMPATIBLE WITH TTL OUTPUTS : V IH = 2V (MIN.) V IL = 0.8V (MAX)sSYMMETRICAL OUTPUT IMPEDANCE:|I OH | = I OL = 6mA (MIN)sBALANCED PROPAGATION DELAYS:t PLH ≅ t PHLsPIN AND FUNCTION COMPATIBLE WITH 74 SERIES 373DESCRIPTIONThe M74HCT373 is an high speed CMOS OCTAL LATCH WITH 3-STATE OUTPUTS fabricated with sub-micron silicon gate C 2MOS technology.This 8-BIT D-Type latches is controlled by a latch enable input (LE) and output enable input (OE).While the LE input is held at a high level, the Q outputs will follow the data input. When the LE is taken low, the Q outputs will be latched at the logic level of D input data.While the OE input is at low level, the eight outputs will be in a normal logic state (high or low logiclevel) and when OE is in high level the outputs will be in a high impedance state.The 3-State output configuration and the wide choice of outline make bus organized system simple.All inputs are equipped with protection circuits against static discharge and transient excess voltage.M74HCT373OCTAL D-TYPE LATCHWITH 3 STATE OUTPUT NON INVERTINGPIN CONNECTION AND IEC LOGIC SYMBOLSORDER CODESPACKAGE TUBE T & RDIP M74HCT373B1R SOP M74HCT373M1RM74HCT373RM13TR TSSOPM74HCT373TTRM74HCT3732/11INPUT AND OUTPUT EQUIVALENT CIRCUITPIN DESCRIPTIONTRUTH TABLEX: Don’t CareZ: High Impedance(*): Q Outputs are latched at the time when the LE input is taken low logic level.LOGIC DIAGRAMPIN No SYMBOL NAME AND FUNCTION 1OE 3 State Output Enable Input (Active LOW)2, 5, 6, 9, 12, 15, 16, 19 Q0 to Q7 3 State Outputs 3, 4, 7, 8, 13, 14, 17, 18D0 to D7Data Inputs11LE Latch Enable Input 10GND Ground (0V)20V CCPositive Supply VoltageINPUTSOUTPUTSOE LE D QH X X ZL L X NO CHANGE (*)L H L L LHHHM74HCT3733/11ABSOLUTE MAXIMUM RATINGSAbsolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied(*) 500mW at 65 °C; derate to 300mW by 10mW/°C from 65°C to 85°CRECOMMENDED OPERATING CONDITIONSSymbol ParameterValue Unit V CC Supply Voltage -0.5 to +7V V I DC Input Voltage -0.5 to V CC + 0.5V V O DC Output Voltage -0.5 to V CC + 0.5V I IK DC Input Diode Current ± 20mA I OK DC Output Diode Current ± 20mA I O DC Output Current ± 35mA I CC or I GND DC V CC or Ground Current± 70mA P D Power Dissipation 500(*)mW T stg Storage Temperature -65 to +150°C T LLead Temperature (10 sec)300°CSymbol ParameterValue Unit V CC Supply Voltage 4.5 to 5.5V V I Input Voltage 0 to V CC V V O Output Voltage 0 to V CC V T op Operating Temperature-55 to 125°C t r , t fInput Rise and Fall Time (V CC = 4.5 to 5.5V)0 to 500nsM74HCT3734/11DC SPECIFICATIONSSymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.V IHHigh Level Input Voltage4.5 to5.5 2.02.02.0V V IL Low Level Input Voltage4.5 to5.50.80.80.8V V OH High Level Output Voltage4.5I O =-20 µA 4.4 4.5 4.4 4.4VI O =-6.0 mA 4.184.31 4.134.10V OL Low Level Output Voltage4.5I O =20 µA 0.00.10.10.1V I O =6.0 mA 0.170.260.330.40I I Input Leakage Current5.5V I = V CC or GND ± 0.1± 1± 1µA I OZ High Impedance Output Leakage Current5.5V I = V IH or V IL V O = V CC or GND ± 0.5± 5± 10µA I CC Quiescent Supply Current5.5V I = V CC or GND 44080µA ∆ I CCAdditional Worst Case Supply Current5.5Per Input pin V I = 0.5V or V I = 2.4V Other Inputs at V CC or GNDI O = 02.02.93.0mAM74HCT3735/11AC ELECTRICAL CHARACTERISTICS (C L = 50 pF, Input t r = t f = 6ns)CAPACITIVE CHARACTERISTICS1) C PD is defined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption without load. (Refer to Test Circuit). Average operating current can be obtained by the following equation. I CC(opr) = C PD x V CC x f IN + I CC /8 (per Flip Flop) and the C PD when n pcs of Flip Flop operate, can be gained by the following equation: C PD(TOTAL) = 32 + 34 x n (pF)SymbolParameterTest ConditionValue UnitV CC (V)C L (pF)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.t TLH t THL Output TransitionTime4.5507121518ns t PLH t PHL Propagation DelayTime (LE - Q)4.55020303845ns 150********t PLH t PHL Propagation DelayTime (D - Q)4.55019303845ns 150********t PZL t PZH High ImpedanceOutput Enable Time4.550R L = 1 K Ω20303845ns 150********t PLZ t PHZ High ImpedanceOutput Disable Time4.550R L = 1 K Ω20303845ns t W(H)Minimum PulseWidth (LE)4.5508151922ns t sMinimum Set-up Time4.5504101315ns t hMinimum Hold Time4.550558ns SymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.C IN Input Capacitance 5101010pF C PDPower Dissipation Capacitance (note 1)66pFM74HCT3736/11TEST CIRCUITC L = 50pF/150pF or equivalent (includes jig and probe capacitance)R 1 = 1K Ω or equivalentR T = Z OUT of pulse generator (typically 50Ω)WAVEFORM 1: LE TO Qn PROPAGATION DELAYS, LE MINIMUM PULSE WIDTH, Dn TO LE SETUP AND HOLD TIMES (f=1MHz; 50% duty cycle)TESTSWITCH t PLH , t PHL Open t PZL , t PLZ V CC t PZH , t PHZGNDM74HCT3737/11WAVEFORM 2: OUTPUT ENABLE AND DISABLE TIMES (f=1MHz; 50% duty cycle)WAVEFORM 3: PROPAGATION DELAY TIMES(f=1MHz; 50% duty cycle)M74HCT373 Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.© The ST logo is a registered trademark of STMicroelectronics© 2000 STMicroelectronics - Printed in Italy - All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - MoroccoSingapore - Spain - Sweden - Switzerland - United Kingdom© 11/11芯天下--/。

回收背光驱动IC

回收背光驱动IC深圳宝博电子商行,长期收购库存电子元器件:{香港交货.台湾付款香港交货均可}1.SMDDIP集成电路,单片机,二三极管钽电容,存储器,红外接收发射,霍尔元件可调电位器MOSFE管法拉电容继电器等等。

2.手机内配件:字库,中频,电源,功放,FLASH,摄像头,CPU,光板,主板,液晶屏,原装外壳,原装按键等。

3.电脑:主芯片,南北桥,CPU,内存条,硬盘,主板,网卡,显卡,声卡,闪存等。

4.用于数码相机,监控,网络摄象头,等数码产品的电子元器件。

5.蓝牙DVD,VCD,MP3MP4电视机,显示器等家电常用器件。

6.高科技产品及军工等专用器件。

74LVC14APW74HCT257DSN74AHC08DRCD4001BCMXHCF4024M013TRTC74LCX86FTTC74VHC393FTTC74AC157FTTC74VHC126FT100EL56TC74VHC11FTSN74LS09NSR74LVT273PWL4931ABD35-TRTC7SH32FUECMF02-2AMX6CD3301BRHHRSKY77198-12AO4496LLV5065VB-TLM-HM74HC02RM13TRM74HC04RM13TRM74HC08RM13TRM74HC125RM13TRM74HC132RM13TRM74HC4066RM13TRM74HC4066TTRM74HC74RM13TRMC33079DR2G74F51DLM833DR2GRJP4005ANS-01#Q1LM431ACMXAT25F1024AN-10SU-2.7。

74HC07中文资料

1/10May 2003sHIGH SPEED:t PD =6ns (TYP .)at V CC =6V sLOW POWER DISSIPATION:I CC =1µA(MAX.)at T A =25°C sHIGH NOISE IMMUNITY:V NIH =V NIL =28%V CC (MIN.)sWIDE OPERATING VOLTAGE RANGE:V CC (OPR)=2V to 6VsPIN AND FUNCTION COMPATIBLE WITH 74SERIES 07DESCRIPTIONThe M74HC07is an high speed CMOS HEX OPEN DRAIN BUFFER fabricated with silicon gate C 2MOS technology.The internal circuit is composed of 2stages including buffer output,which enables high noise immunity and stable output.All inputs are equipped with protection circuits against static discharge and transient excess voltage.M74HC07HEX BUFFER (OPENDRAIN)PIN CONNECTION AND IEC LOGIC SYMBOLSORDER CODESPACKAGE TUBE T &R DIP M74HC07B1R SOP M74HC07M1RM74HC07RM13TR TSSOPM74HC07TTRM74HC072/10INPUT AND OUTPUT EQUIVALENT CIRCUITPIN DESCRIPTIONTRUTH TABLEZ :High ImpedanceABSOLUTE MAXIMUM RATINGSAbsolute Maximum Ratings are those values beyond which damage to the device may occur.Functional operation under these conditions isnot implied(*)500mW at 65°C;derate to 300mW by 10mW/°C from 65°C to 85°CRECOMMENDED OPERATING CONDITIONSPIN No SYMBOL NAME AND FUNCTION 1,3,5,9,11,131A to 6A Data Inputs 2,4,6,8,10,121Y to 6Y Data Outputs 7GND Ground (0V)14V CCPositive Supply VoltageA Y L L HZSymbol ParameterValue Unit V CC Supply Voltage -0.5to +7V V I DC Input Voltage -0.5to V CC +0.5V V O DC Output Voltage -0.5to V CC +0.5V I IK DC Input Diode Current ±20mA I OK DC Output Diode Current ±20mA I ODC Output Current±25mA I CC or I GND DC V CC or Ground Current±50mA P DPower Dissipation 500(*)mW T stg Storage Temperature -65to +150°C T LLead Temperature (10sec)300°CSymbol ParameterValue Unit V CC Supply Voltage 2to 6V V I Input Voltage 0to V CC V V O Output Voltage 0to V CC V T op Operating Temperature -55to 125°C t r ,t fInput Rise and Fall TimeV CC =2.0V 0to 1000ns V CC =4.5V 0to 500ns V CC =6.0V0to 400nsM74HC073/10DC SPECIFICATIONSAC ELECTRICAL CHARACTERISTICS (C L =50pF,Input t r =t f =6ns)SymbolParameterTest ConditionValue UnitV CC (V)T A =25°C -40to 85°C -55to 125°C Min.Typ.Max.Min.Max.Min.Max.V IHHigh Level Input Voltage 2.0 1.5 1.5 1.5V 4.5 3.15 3.15 3.156.0 4.24.24.2V ILLow Level Input Voltage2.00.50.50.5V4.5 1.35 1.35 1.356.0 1.81.8 1.8V OLLow Level Output Voltage2.0I O =20µA 0.00.10.10.1V4.5I O =20µA 0.00.10.10.16.0I O =20µA 0.00.10.10.14.5I O =4.0mA 0.170.260.330.406.0I O =5.2mA 0.180.260.330.40I I Input Leakage Current6.0V I =V CC or GND ±0.1±1±1µA I OZ Output Leakage Current6.0V I =V IH or V IL V O =V CC or GND ±0.5±5±10µA I CCQuiescent Supply Current6.0V I =V CC or GND11020µA SymbolParameterTest ConditionValue UnitV CC (V)T A =25°C -40to 85°C -55to 125°C Min.Typ.Max.Min.Max.Min.Max.t THLOutput Transition Time2.0307595110ns 4.581519226.07131619t PLZPropagation Delay Time2.0R L =1K Ω1090115135ns4.571823276.06152023t PZLPropagation Delay Time2.0R L =1K Ω1790115135ns4.571823276.05152023M74HC074/10CAPACITIVE CHARACTERISTICS1)C PD is defined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption without load.(Refer to Test Circuit).Average operating current can be obtained by the following equation.I CC(opr)=C PD x V CC x f IN +I CC /6(per gate)TEST CIRCUITL R T =Z OUT of pulse generator (typically 50Ω)WAVEFORM :PROPAGATION DELAY TIME (f=1MHz;50%duty cycle)SymbolParameterTest ConditionValue UnitV CC (V)T A =25°C -40to 85°C -55to 125°C Min.Typ.Max.Min.Max.Min.Max.C IN Input Capacitance 5.05101010pF C OUT OutputCapacitance5.03pF C PDPower Dissipation Capacitance (note 1)5.04pFM74HC07Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.© The ST logo is a registered trademark of STMicroelectronics© 2003 STMicroelectronics - Printed in Italy - All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco Singapore - Spain - Sweden - Switzerland - United Kingdom - United States.© 10/10。

M74HC123中文资料

sHIGH SPEED : t PD = 23 ns (TYP.) at V CC = 6V sLOW POWER DISSIPATION:STAND BY STATE :I CC =4µA (MAX.) at T A =25°C ACTIVE STATE :I CC =200µA (MAX.) at V CC = 5V sHIGH NOISE IMMUNITY:V NIH = V NIL = 28 % V CC (MIN.)sSYMMETRICAL OUTPUT IMPEDANCE:|I OH | = I OL = 4mA (MIN)sBALANCED PROPAGATION DELAYS:t PLH ≅ t PHLsWIDE OPERATING VOLTAGE RANGE:V CC (OPR) = 2V to 6VsWIDE OUTPUT PULSE WIDTH RANGE : t WOUT = 120 ns ~ 60 s OVER AT V CC = 4.5 V sPIN AND FUNCTION COMPATIBLE WITH 74 SERIES 123DESCRIPTIONThe M74HC123 is an high speed CMOS MONOSTABLE MULTIVIBRATOR fabricated with silicon gate C 2MOS technology.There are two trigger inputs, A INPUT (negative edge) and B INPUT (positive edge). These inputs are valid for slow rising/falling signals, (tr=tf=l sec).The device may also be triggered by using the CLR input (positive-edge) because of the Schmitt-trigger input; after triggering the output maintains the MONOSTABLE state for the time period determined by the external resistor Rx and capacitor Cx. When Cx > 10nF and Rx > 10K Ω,the output pulse width value is approsimatively given by the formula : tW(OUT) = K · Cx · Rx.(K ≅ 0.45).Taking CLR low breaks this MONOSTABLE STATE. If the next trigger pulse occurs during the MONOSTABLE period it makes the MONOSTABLE period longer. Limit for values of Cx and Rx : Cx : NO LIMIT Rx : V cc < 3.0V 5K Ω to 1M Ω V cc > 3.0V 1K Ω to 1M ΩAll inputs are equipped with protection circuits against static discharge and transient excess voltage.M74HC123DUAL RETRIGGERABLE MONOSTABLE MULTIVIBRATORPIN CONNECTION AND IEC LOGIC SYMBOLSORDER CODESPACKAGE TUBE T & RDIP M74HC123B1R SOP M74HC123M1RM74HC123RM13TR TSSOPM74HC123TTRM74HC1232/12INPUT AND OUTPUT EQUIVALENT CIRCUITPIN DESCRIPTIONTRUTH TABLEPIN No SYMBOL NAME AND FUNCTION 1,91A, 2A Trigger Inputs (Negative Edge Triggered)2, 101B, 2B Trigger Inputs (Positive Edge Triggered)3, 11 1 CLR 2 CLR Direct Reset LOW and trigger Action at Positive Edge4, 121Q, 2Q Outputs (Active Low)72R X /C X External ResistorCapacitor Connection 13, 51Q, 2Q Outputs (Active High)14, 6 1C X 2C X External Capacitor Connection151R X /C X External ResistorCapacitor Connection 8GND Ground (0V)16VccPositive Supply VoltageM74HC123 SYSTEM DIAGRAMThis logic diagram has not be used to estimate propagation delaysTIMING CHART3/12M74HC1234/12BLOCK DIAGRAM(2) Dx is a clamping diode.The external capacitor is charged to Vcc in the stand-by-state, i.e. no trigger. When the supply voltage is turned off Cx is di scharged mainly trough an internal parasitic diode(see figures). If Cx is sufficiently large and Vcc decreases rapidly, there will be some possibility of damaging the I.C. with a surge current or latch-up. If the voltage supply filter capacitor is large enough and Vcc decrease slowly, the surge current is automatically limited and damage to the I.C. is avoided. The maximum forward current of the parasitic diode is approximately 20 mA. In cases where Cx is large the time taken for the supply voltage to fall to 0.4 Vcc can be calculated as follows : t f > (Vcc - 0.7) x Cx/20mAIn cases where t f is too short an external clamping diode is required to protect the I.C. from the surge current.FUNCTIONAL DESCRIPTION STAND-BY STATEThe external capacitor,Cx, is fully charged to Vcc in the stand-by state. Hence, before triggering,transistor Qp and Qn (connected to the Rx/Cx node) are both turned-off. The two comparators that control the timing and the two reference voltage sources stop operating. The total supply current is therefore only leakage current.TRIGGER OPERATION Triggering occurs when :1 st) A is "LOW" and B has a falling edge;2 nd) B is "HIGH" and A has a rising edge;3 rd) A is "LOW" and B is HIGH and C1 has a rising edge;After the multivibrator has been retriggered comparator C1 and C2 start operating and Qn is turned on. Cx then discharges through Qn. The voltage at the node R/C external falls.When it reaches V REFL the output of comparator C1 becomes low. This in turn reset the flip-flop and Qn is turned off.At this point C1 stops functioning but C2 continues to operate.The voltage at R/C external begins to rise with a time constant set by the external components Rx,Cx.Triggering the multivibrator causes Q to go high after internal delay due to the flip-flop and the gate. Q remains high until the voltage at R/C external rises again to V REFH . At this point C2output goes low and O goes low. C2 stop operating. That means that after triggering when the voltage R/C external returns to V REFH the multivibrator has returned to its MONOSTABLE STATE. In the case where Rx · Cx are large enough and the discharge time of the capacitor and the delay time in the I.C. can be ignored, the width of the output pulse tw (out) is as follows :tW(OUT) = 0.45 Cx · RxRE - TRIGGERED OPERATIONWhen a second trigger pulse follows the first its effect will depend on the state of the multivibrator.If the capacitor Cx is being charged the voltage level of R/C external falls to V REFL again and Q remains High i.e. the retrigger pulse arrives in a time shorter than the period Rx · Cx seconds, the capacitor charging time constant. If the second trigger pulse is very close to the initial trigger pulse it is ineffective ; i.e. the second trigger must arrive in the capacitor discharge cycle to be ineffective;Hence the minimum time for a second trigger to be effective depends on Vcc and Cx RESET OPERATIONCL is normally high. If CL is low, the trigger is not effective because Q output goes low and trigger control flip-flop is reset.Also transistor Op is turned on and Cx is charged quickly to Vcc. This means if CL input goes low the IC becomes waiting state both in operating and non operating state.M74HC1235/12ABSOLUTE MAXIMUM RATINGSAbsolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied(*) 500mW at 65 °C; derate to 300mW by 10mW/°C from 65°C to 85°CRECOMMENDED OPERATING CONDITIONSThe Maximum allowable values of Cx and Rx are a function of leakage of capacitor Cx, the leakage of device and leakage due to the board layout and surface resistance. Susceptibility to externally induced noise may occur for Rx > 1M ΩSymbol ParameterValue Unit V CC Supply Voltage -0.5 to +7V V I DC Input Voltage -0.5 to V CC + 0.5V V O DC Output Voltage -0.5 to V CC + 0.5V I IK DC Input Diode Current ± 20mA I OK DC Output Diode Current ± 20mA I O DC Output Current ± 25mA I CC or I GND DC V CC or Ground Current± 50mA P D Power Dissipation 500(*)mW T stg Storage Temperature -65 to +150°C T LLead Temperature (10 sec)300°CSymbol ParameterValue Unit V CC Supply Voltage 2 to 6V V I Input Voltage 0 to V CC V V O Output Voltage 0 to V CC V T op Operating Temperature -55 to 125°C t r , t f Input Rise and Fall TimeV CC = 2.0V 0 to 1000ns V CC = 4.5V 0 to 500ns V CC = 6.0V 0 to 400ns Cx External Capacitor NO LIMITATIONpFRxExternal Resistor Vcc < 3V 5K to 1M ΩVcc > 3V1K to 1MM74HC1236/12DC SPECIFICATIONS(1) : Per CircuitSymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.V IHHigh Level Input Voltage2.0 1.5 1.5 1.5V 4.53.15 3.15 3.156.04.24.24.2V ILLow Level Input Voltage2.00.50.50.5V4.5 1.35 1.35 1.356.0 1.81.81.8V OHHigh Level Output Voltage2.0I O =-20 µA 1.9 2.0 1.9 1.9V4.5I O =-20 µA 4.4 4.5 4.4 4.46.0I O =-20 µA5.96.0 5.9 5.94.5I O =-4.0 mA 4.18 4.31 4.13 4.106.0I O =-5.2 mA 5.685.8 5.635.60V OLLow Level Output Voltage2.0I O =20 µA 0.00.10.10.1V 4.5I O =20 µA 0.00.10.10.16.0I O =20 µA 0.00.10.10.14.5I O =4.0 mA 0.170.260.330.406.0I O =5.2 mA 0.180.260.330.40I I Input Leakage Current6.0V I = V CC or GND ± 0.1± 1± 1µA I CC Quiescent Supply Current6.0V I = V CC or GND 44080µA I CC’Active StateSupply Current (1)2.0V I = V CC or GND Pin 7 or 15V IN = V CC /245200260320µA 4.5500600780960µA 6.00.711.31.6mAM74HC1237/12AC ELECTRICAL CHARACTERISTICS (C L = 50 pF, Input t r = t f = 6ns)CAPACITIVE CHARACTERISTICS1) C PD is defined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption without load. (Refer to Test Circuit). Average operating current can be obtained by the following equation. I CC(opr) = C PD x V CC x f IN + I CC ’ Duty/100 + Ic/2(per monostable) (I cc ’ : Active Supply current) (Duty : %)SymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.t TLH t THL Output TransitionTime 2.0307595110ns 4.581519226.07131619t PLH t PHL Propagation DelayTime(A, B - Q, Q)2.0102210265315ns4.5294253636.022364554t PLH t PHL Propagation DelayTime(CLRTRIGGER - Q, Q) 2.0102235295355ns4.5314759716.023405060t PLH t PHL Propagation DelayTime(CLR - Q, Q)2.068160200240ns4.5203240486.016273441t WOUTOutput Pulse Width2.0Cx = 100 pF Rx = 10K Ω 1.4µs4.5 1.26.0 1.12.0Cx = 0.1µF Rx = 100K Ω4.6ms4.5 4.46.04.3∆t WOUTOutput Pulse Width Error Between Circuits in Same Package±1%t W(H) t W(L)Minimum Pulse Width2.07595110ns4.51519226.0131619t W(L)Minimum Pulse Width (CLR) 2.07595110ns4.51519226.0131619t rrMinimum Retrigger Time2.0Cx = 100 pF Rx = 10K Ω325ns4.51086.0782.0Cx = 0.1µF Rx = 100K Ω5µs4.5 1.46.01.2SymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.C IN Input Capacitance 5.05101010pF C PDPower Dissipation Capacitance (note 1)5.0162pFM74HC1238/12TEST CIRCUITL R T = Z OUT of pulse generator (typically 50Ω)WAVEFORM : SWITCIHNG CHARACTERISTICS TEST WAVEFORM(f=1MHz; 50% duty cycle)M74HC123Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.© The ST logo is a registered trademark of STMicroelectronics© 2001 STMicroelectronics - Printed in Italy - All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - MoroccoSingapore - Spain - Sweden - Switzerland - United Kingdom© 12/12。

74HC174中文资料

74HC/HCT174 Hex D-type flip-flop with reset; positive-edge trigger

Product specification Supersedes data of September 1993 File under Integrated Circuits, IC06

DC CHARACTERISTICS FOR 74HC

For the DC characteristics see “74HC/HCT/HCU/HCMOS Logic Family Specifications”.

Output capability: standard ICC category: MSI

AC CHARACTERISTICS FOR 74HC GND = 0 V; tr = tf = 6 ns; CL = 50 pF

Tamb (°C)

TEST CONDITIONS

SYMBOL PARAMETER

74HC

+25

−40 to +85

−40 to +125

UNIT

VCC (V)

WAVEFORMS

Note

1. H = HIGH voltage level h = HIGH voltage level one set-up time prior to the LOW-to-HIGH CP transition L = LOW voltage level I = LOW voltage level one set-up time prior to the LOW-to-HIGH CP transition X = don’t care ↑= LOW-to-HIGH CP transition

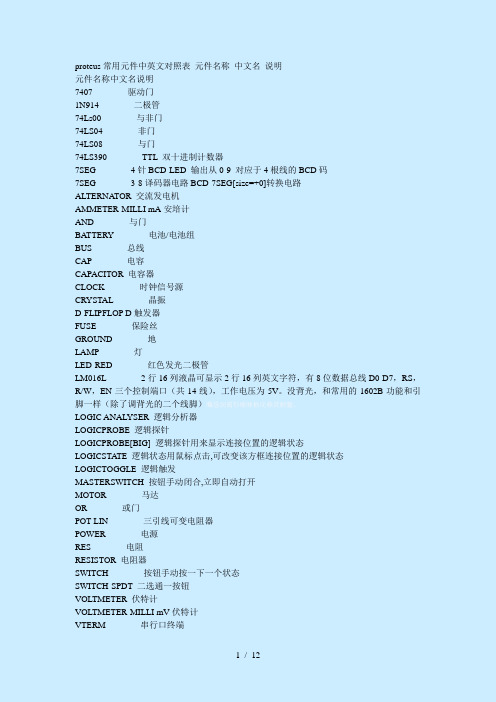

proteus常用元件中英文对照表元件名称中文名说明

proteus常用元件中英文对照表元件名称中文名说明元件名称中文名说明7407 驱动门1N914 二极管74Ls00 与非门74LS04 非门74LS08 与门74LS390 TTL 双十进制计数器7SEG 4针BCD-LED 输出从0-9 对应于4根线的BCD码7SEG 3-8译码器电路BCD-7SEG[size=+0]转换电路ALTERNATOR 交流发电机AMMETER-MILLI mA安培计AND 与门BA TTERY 电池/电池组BUS 总线CAP 电容CAPACITOR 电容器CLOCK 时钟信号源CRYSTAL 晶振D-FLIPFLOP D触发器FUSE 保险丝GROUND 地LAMP 灯LED-RED 红色发光二极管LM016L 2行16列液晶可显示2行16列英文字符,有8位数据总线D0-D7,RS,R/W,EN三个控制端口(共14线),工作电压为5V。

没背光,和常用的1602B功能和引脚一样(除了调背光的二个线脚)矚慫润厲钐瘗睞枥庑赖賃軔朧。

LOGIC ANAL YSER 逻辑分析器LOGICPROBE 逻辑探针LOGICPROBE[BIG] 逻辑探针用来显示连接位置的逻辑状态LOGICSTATE 逻辑状态用鼠标点击,可改变该方框连接位置的逻辑状态LOGICTOGGLE 逻辑触发MASTERSWITCH 按钮手动闭合,立即自动打开MOTOR 马达OR 或门POT-LIN 三引线可变电阻器POWER 电源RES 电阻RESISTOR 电阻器SWITCH 按钮手动按一下一个状态SWITCH-SPDT 二选通一按钮VOLTMETER 伏特计VOLTMETER-MILLI mV伏特计VTERM 串行口终端Electromechanical 电机Inductors 变压器Laplace Primitives 拉普拉斯变换Memory IcsMicroprocessor IcsMiscellaneous 各种器件AERIAL-天线;ATAHDD;ATMEGA64;BATTERY;CELL;CRYSTAL-晶振;FUSE;METER-仪表;聞創沟燴鐺險爱氇谴净祸測樅。

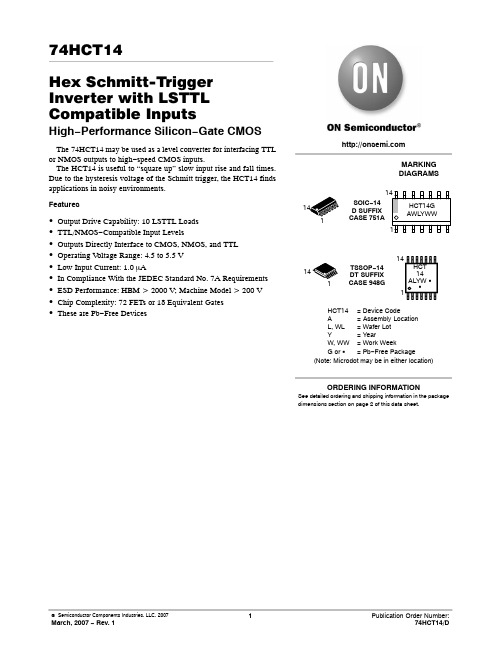

信号调理芯片 74HCT14

74HCT14Hex Schmitt−Trigger Inverter with LSTTL Compatible InputsHigh−Performance Silicon−Gate CMOSThe 74HCT14 may be used as a level converter for interfacing TTL or NMOS outputs to high−speed CMOS inputs.The HCT14 is useful to “square up” slow input rise and fall times. Due to the hysteresis voltage of the Schmitt trigger, the HCT14 finds applications in noisy environments.Features•Output Drive Capability: 10 LSTTL Loads•TTL/NMOS−Compatible Input Levels•Outputs Directly Interface to CMOS, NMOS, and TTL •Operating V oltage Range: 4.5 to 5.5 V•Low Input Current: 1.0 m A•In Compliance With the JEDEC Standard No. 7A Requirements •ESD Performance: HBM > 2000 V; Machine Model > 200 V •Chip Complexity: 72 FETs or 18 Equivalent Gates•These are Pb−Free DevicesMARKINGDIAGRAMSHCT14= Device CodeA= Assembly LocationL, WL= Wafer LotY= YearW, WW= Work WeekG or G= Pb−Free PackageTSSOP−14DT SUFFIXCASE 948GSOIC−14D SUFFIXCASE 751AHCT14ALYW GG114See detailed ordering and shipping information in the package dimensions section on page 2 of this data sheet.ORDERING INFORMATION(Note: Microdot may be in either location)PIN ASSIGNMENTPIN 14 = V CC PIN 7 = GNDY = AA1Y1A2Y2A3Y3A4Y4A5Y5A6Y6FUNCTION TABLEInput A Output YLOGIC DIAGRAMY5A5Y6A6V CC Y4A4Y2A2Y1A1GNDY3A3L HH LORDERING INFORMATIONDevicePackage Shipping †74HCT14DR2G SOIC −14(Pb −Free)2500 / Tape & Reel74HCT14DTR2GTSSOP −14*†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.*This package is inherently Pb −Free.MAXIMUM RATINGSSymbol Parameter Value Unit V CC DC Supply Voltage(Referenced to GND)*0.5 to )7.0V V I DC Input Voltage(Referenced to GND)*0.5 to V CC)0.5V V O DC Output Voltage(Referenced to GND)*0.5 to V CC)0.5VI IK DC Input Diode Current$20mA I OK DC Output Diode Current$25mAI O DC Output Sink Current$25mA I CC DC Supply Current per Supply Pin$50mA I GND DC Ground Current per Ground Pin$50mA T STG Storage Temperature Range*65 to )150_C T L Lead Temperature, 1 mm from Case for 10 Seconds260_C T J Junction Temperature under Bias)150_Cq JA Thermal Resistance SOICTSSOP 125170_C/WP D Power Dissipation in Still Air at 85_C SOICTSSOP 500450mWMSL Moisture Sensitivity Level 1F R Flammability Rating Oxygen Index: 30% − 35%UL 94 V−0 @ 0.125 inV ESD ESD Withstand Voltage Human Body Model (Note 1)Machine Model (Note 2)>2000>200VI Latchup Latchup Performance Above V CC and Below GND at 85_C (Note 3)$300mA Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above theRecommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.1.Tested to EIA/JESD22−A114−A.2.Tested to EIA/JESD22−A115−A.3.Tested to EIA/JESD78.4.For high frequency or heavy load considerations, see the ON Semiconductor High−Speed CMOS Data Book (DL129/D). RECOMMENDED OPERATING CONDITIONSSymbol Parameter Min Max Unit V CC DC Supply Voltage(Referenced to GND) 4.5 5.5VV I, V O DC Input Voltage, Output Voltage(Referenced to GND)0V CC V T A Operating Temperature, All Package Types*55)125_C t r, t f Input Rise and Fall Time (Figure 1)−(Note 5)ns5.No Limit when V I[ 50% V CC, I CC > 1 mA.6.Unused inputs may not be left open. All inputs must be tied to a high−logic voltage level or a low−logic input voltage level.DC ELECTRICAL CHARACTERISTICS (Voltages Referenced to GND)Temperature LimitV CC*55_C to 25_C v85_C v125_C Symbol Parameter Test Conditions(V)Min Max Min Max Min Max UnitV T)max Maximum Positive−GoingInput Threshold Voltage V O = 0.1 V or V CC – 0.1 V|I out| v 20 m A4.55.51.92.11.92.11.92.1VV T)min Minimum Positive−GoingInput Threshold Voltage V O = 0.1 V or V CC – 0.1 V|I out| v 20 m A4.55.51.21.41.21.41.21.4VV T*max Maximum Negative−GoingInput Threshold Voltage V O = 0.1 V or V CC – 0.1 V|I out| v 20 m A4.55.51.21.41.21.41.21.4V T*min Minimum Negative−GoingInput Threshold Voltage V O = 0.1 V or V CC – 0.1 V|I out| v 20 m A4.55.50.50.60.50.60.50.6V H max Maximum HysteresisVoltage V O = 0.1 V or V CC – 0.1 V|I out| v 20 m A4.55.51.41.51.41.51.41.5V H min Minimum HysteresisVoltage V O = 0.1 V or V CC – 0.1 V|I out| v 20 m A4.55.50.40.40.40.40.40 4V OH Minimum High−LevelOutput Voltage V I < V T*min|I out| v 20 m A4.55.54.45.44.45.44.45.4VV I < V T*min|I out| v 4.0 mA4.5 3.98 3.84 3.7V OL Maximum Low−LevelOutput Voltage V I≥ V T)max|I out| v 20 m A4.55.50.10.10.10.10.10.1VV I≥ V T)max|I out| v 4.0 mA4.50.260.330.4I IK Maximum InputLeakage CurrentV I = V CC or GND 5.5$0.1$1.0$1.0m AI CC Maximum QuiescentSupply Current(per package)V I = V CC or GNDI out = 0 m A5.5 2.02040m Aw*55_C25_C to 125_CD I CC Additional QuiescentSupply Current V I = 2.4 V, Any One InputV I = V CC or GND, Other Inputsl out = 0 m A5.5 2.9 2.4mArmation on typical parametric values can be found in the ON Semiconductor High−Speed CMOS Data Book (DL129/D).AC CHARACTERISTICS (C L = 50 pF; Input t r = t f= 6.0 ns)Guaranteed Limit*55_C to 25_C v85_C v125_C Symbol Parameter Test Conditions Figures Min Max Min Max Min Max Unitt PLH, t PHL Maximum PropagationDelay, Input A to OutputY (L to H)V CC = 5.0 V $10%C L = 50 pF, Input t r = t f = 6.0 ns1 & 2324048nst TLH, t THL Maximum OutputTransition Time, AnyOutputV CC = 5.0 V $10%C L = 50 pF, Input t r = t f = 6.0 ns1 & 2151922ns8.For propagation delays with loads other than 50 pF, and information on typical parametric values, see the ON Semiconductor High−SpeedCMOS Data Book (DL129/D).Typical @ 25°C, V CC = 5.0 VC PD Power Dissipation Capacitance, per Inverter (Note 9)32pFed to determine the no−load dynamic power consumption: P D = C PD V CC f + I CC V CC. For load considerations, see the ONSemiconductor High−Speed CMOS Data Book (DL129/D).*Includes all probe and jig capacitance.C L *Figure 1. Switching WaveformsFigure 2. Test CircuitINPUT A OUTPUT Y3 V GNDSOIC −14CASE 751A −03ISSUE HNOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.4.MAXIMUM MOLD PROTRUSION 0.15 (0.006)PER SIDE.5.DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127(0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.DIM MIN MAX MIN MAX INCHESMILLIMETERS A 8.558.750.3370.344B 3.80 4.000.1500.157C 1.35 1.750.0540.068D 0.350.490.0140.019F 0.40 1.250.0160.049G 1.27 BSC 0.050 BSC J 0.190.250.0080.009K 0.100.250.0040.009M 0 7 0 7 P 5.80 6.200.2280.244R0.250.500.0100.019____DIMENSIONS: MILLIMETERS*For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.TSSOP −14CASE 948G −01ISSUE BDIM MIN MAX MIN MAX INCHESMILLIMETERS A 4.90 5.100.1930.200B 4.30 4.500.1690.177C −−− 1.20−−−0.047D 0.050.150.0020.006F 0.500.750.0200.030G 0.65 BSC 0.026 BSC H 0.500.600.0200.024J 0.090.200.0040.008J10.090.160.0040.006K 0.190.300.0070.012K10.190.250.0070.010L 6.40 BSC 0.252 BSC M0 8 0 8 NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.4.DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.5.DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08(0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.6.TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY .7.DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE −W −.____14X REF K14X0.360.65PITCHSOLDERING FOOTPRINT**For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1/10August 2001sHIGH SPEED : f MAX = 56MHz (TYP.) at V CC = 4.5V sLOW POWER DISSIPATION:I CC =4µA(MAX.) at T A =25°CsCOMPATIBLE WITH TTL OUTPUTS : V IH = 2V (MIN.) V IL = 0.8V (MAX)sSYMMETRICAL OUTPUT IMPEDANCE:|I OH | = I OL = 4mA (MIN)sBALANCED PROPAGATION DELAYS:t PLH ≅ t PHLsPIN AND FUNCTION COMPATIBLE WITH 74 SERIES 174DESCRIPTIONThe M74HCT174 is an high speed CMOS HEX D-TYPE FLIP FLOP WITH CLEAR fabricated with silicon gate C 2MOS technology.Information signals applied to D inputs are transferred to the Q output on the positive going edge of the CLOCK (CK) pulse. When the CLEAR(CLR) input is held low, the Q outputs are held low independently of the other inputs.All inputs are equipped with protection circuits against static discharge and transient excess voltage.M74HCT174HEX D-TYPE FLIP FLOP WITH CLEARPIN CONNECTION AND IEC LOGIC SYMBOLSORDER CODESPACKAGE TUBE T & RDIP M74HCT174B1R SOP M74HCT174M1RM74HCT174RM13TR TSSOPM74HCT174TTRM74HCT1742/10INPUT AND OUTPUT EQUIVALENT CIRCUITPIN DESCRIPTIONTRUTH TABLELOGIC DIAGRAMPIN No SYMBOL NAME AND FUNCTION 1CLEAR Asynchronous Master Reset (Active Low)2, 5, 7, 10, 12, 15Q0 to Q5Flip-Flop Outputs 3, 4, 6, 11, 13, 14D0 to D5 Data Inputs9CLOCK Clock Input (LOW to HIGH, edge triggered)8GND Ground (0V)16VccPositive Supply VoltageM74HCT1743/10ABSOLUTE MAXIMUM RATINGSAbsolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied(*) 500mW at 65 °C; derate to 300mW by 10mW/°C from 65°C to 85°CRECOMMENDED OPERATING CONDITIONSDC SPECIFICATIONSSymbol ParameterValue Unit V CC Supply Voltage -0.5 to +7V V I DC Input Voltage -0.5 to V CC + 0.5V V O DC Output Voltage -0.5 to V CC + 0.5V I IK DC Input Diode Current ± 20mA I OK DC Output Diode Current ± 20mA I O DC Output Current ± 25mA I CC or I GND DC V CC or Ground Current± 50mA P D Power Dissipation 500(*)mW T stg Storage Temperature -65 to +150°C T LLead Temperature (10 sec)300°CSymbol ParameterValue Unit V CC Supply Voltage 4.5 to 5.5V V I Input Voltage 0 to V CC V V O Output Voltage 0 to V CC V T op Operating Temperature-55 to 125°C t r , t fInput Rise and Fall Time (V CC = 4.5 to 5.5V)0 to 500nsSymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.V IH High Level Input Voltage4.5 to5.5 2.02.02.0V V IL Low Level Input Voltage4.5 to5.50.80.80.8V V OH High Level Output Voltage4.5I O =-20 µA 4.4 4.5 4.4 4.4VI O =-4.0 mA 4.184.31 4.134.10V OL Low Level Output Voltage4.5I O =20 µA 0.00.10.10.1V I O =4.0 mA 0.170.260.330.40I I Input Leakage Current5.5V I = V CC or GND ± 0.1± 1± 1µA I CC Quiescent Supply Current5.5V I = V CC or GND 44080µA ∆ I CCAdditional Worst Case Supply Current5.5Per Input pin V I = 0.5V or V I = 2.4V Other Inputs at V CC or GND I O = 02.02.93.0mAM74HCT1744/10AC ELECTRICAL CHARACTERISTICS (C L = 50 pF, Input t r = t f = 6ns)CAPACITIVE CHARACTERISTICS1) C PD is defined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption without load. (Refer to Test Circuit). Average operating current can be obtained by the following equation. I CC(opr) = C PD x V CC x f IN + I CC /6 (per FLIP/FLOP)And the total CPD when N pcs of FLIP-FLOP operate can be gained by the following equation : CPD (total) = 38 + 15 x nSymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.t TLH t THL Output TransitionTime4.58151922ns t PLH t PHL Propagation DelayTime (CLOCK - Q)4.5182835ns t PLH t PHL Propagation DelayTime (CLEAR - Q)4.518283542ns f MAX Maximum ClockFrequency4.5305624MHz t W(H) t W(L)Minimum PulseWidth (CLOCK) 4.58151922ns t W(L)Minimum Pulse Width (CLEAR) 4.58151922ns t s Minimum Set-up Time4.52101315ns t h Minimum Hold Time4.5568ns t REMMinimum Removal Time4.55555ns SymbolParameterTest ConditionValue UnitV CC (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.C IN Input Capacitance 5101010pF C PDPower Dissipation Capacitance (note 1)68pFM74HCT1745/10TEST CIRCUITL R T = Z OUT of pulse generator (typically 50Ω)WAVEFORM 1 : PROPAGATION DELAY TIME, MINIMUM PULSE WIDTH (CLOCK), SETUP AND HOLD TIME (nD TO CLOCK), CLOCK MAXIMUM FREQUENCY(f=1MHz; 50% duty cycle)M74HCT1746/10WAVEFORM 2 : PROPAGATION DELAY TIME (nQ TO CLEAR)(f=1MHz; 50% duty cycle)WAVEFORM 3 : MINIMUM PULSE WIDTH (CLEAR), MINIMUM REMOVAL TIME (CLEAR TO CLOCK)(f=1MHz; 50% duty cycle)M74HCT174Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.© The ST logo is a registered trademark of STMicroelectronics© 2001 STMicroelectronics - Printed in Italy - All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - MoroccoSingapore - Spain - Sweden - Switzerland - United Kingdom© 10/10。