ATMEGA16M1中文资料

ATmega16单片机定时器讲解资料

位6: TOIE2:T/C2溢出中断使能位。 0:溢出中断禁止; 1:溢出中断使能。

位5: TICIE1:T/C1输入捕捉中断使能位。 0:输入捕捉中断禁止; 1:输入捕捉中断使能。

Page 16

R1 10K

4 /RE T

C0 4.7u

ATm eg a1 6

AJ1

C7 33 OSC1 C6 33

12 PD .3(/INT1)

8 XTAL1

7 XTAL2

L1 R21~28

L2 R29~36

L3 R37~44

L4 R45~52

dp g f e d c b a

dp g f e d c b a

dp g f e d c b a

Page 2

3.1、单片机定时器的基本应用、原理及要素

1、单片机定时器的基本应用 2、单片机定时器的基本原理图 3、单片机定时器的基本要素

Page 3

3.1.1、单片机定时器的基本应用

基本应用:

定时计数器是单片机中最基本的接口之一, 它的用途非常广泛,常用于计数、延时、测量 周期、频率、脉宽、提供定时脉冲信号等。在 实际应用中,对于转速,位移、速度、流量等 物理量的测量,通常也是由传感器转换成脉冲 电信号,通过使用定时计数器来测量其周期或 频率,再经过计算处理获得

Page 11

3.2.1、ATmega16单片机定时器T/C0的组成原理

TC0的比较匹配单元:

Page 12

在引脚的方向寄存器DDRB.3定 义为输出时,当寄存器TCCR0中 的标志位COM0[1:0]中任何一位为 1时,或门M1输出为1,多路数据 选择器S3的通道1被选中,如果端 口PB.3定义为输出时,三态门F2 被打开,OC0将替代引脚PB3原来 的I/O功能,端口PB.3上输出的就 是波形发生器产生的波形。当 COM0[1:0]都为0时,选择器S3的通 道0被选中,PB.3口输出的则是端 口PORT之值。

ATmega16寄存器详述

5

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ @ 珠联璧合 xlzhu xlzhu@

ega1 6 寄存器详述 ATm ATmega1 ega16

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

表2 端口引脚配置 DDRXn 0 0 0 1 1 PORTXn 0 1 1 0 1 PUD × 0 1 × × I/O 输入 输入 输入 输出 输出 上拉电阻 否 是 否 否 否 说明 I/O 三态输入 I/O 口带上拉电阻输入 高阻态 推免0输出 推免1输出

点,可直接驱动LED、SSR或继电器。 � � 40引脚PDIP封装,44引脚TQFP 封装,与44引脚MLF封装。

工作电压 � � ATmega16L:2.7 - 5.5V ATmega16:4.5 - 5.5V

�

速度等级 � � 0 ~8 MHz ATmega16L 0 ~16 MHz ATmega16

3. I/O 端口 3.1 I/O 端口特性 � � � � 共有PA~PD四组通用I/O口,每组I/O都是8位寄存器。 作为通用数字I/O 使用时,所有AVR I/O 端口都具有真正的读-修改-写功能。 输出缓冲器具有对称的驱动能力,可以输出或吸收大电流,直接驱动LED。 所有的端口引脚都具有与电压无关的上拉电阻。并有保护二极管与VCC 和地相连。

◎输入引脚地址 PINA

BIT PINA 读/写 初始值 7 PINA7 R N/A 6 PINA6 R N/A 5 PINA5 R N/A 4 PINA4 R N/A 3 PINA3 R N/A 2 PINA2 R N/A 1 PINA1 R N/A 0 PINA0 R N/A

5 PB 口寄存器 3. 3.5 ◎数据方向寄存器 DDRB

ATmega16 数据手册

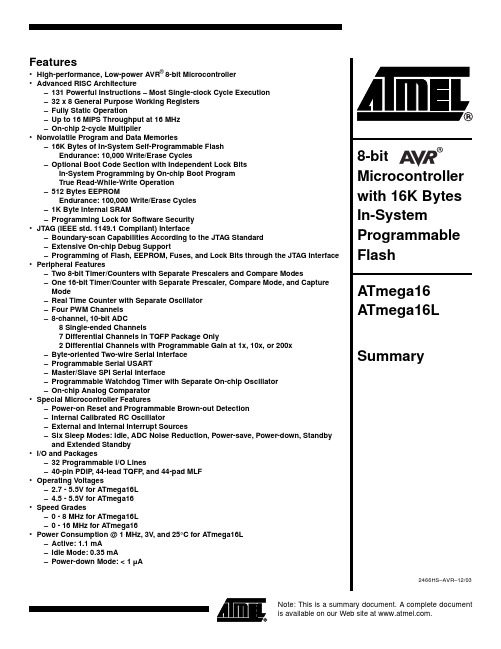

Features•High-performance, Low-power AVR® 8-bit Microcontroller •Advanced RISC Architecture–131 Powerful Instructions – Most Single-clock Cycle Execution –32 x 8 General Purpose Working Registers–Fully Static Operation–Up to 16 MIPS Throughput at 16 MHz–On-chip 2-cycle Multiplier•Nonvolatile Program and Data Memories–16K Bytes of In-System Self-Programmable FlashEndurance: 10,000 Write/Erase Cycles–Optional Boot Code Section with Independent Lock BitsIn-System Programming by On-chip Boot ProgramTrue Read-While-Write Operation–512 Bytes EEPROMEndurance: 100,000 Write/Erase Cycles–1K Byte Internal SRAM–Programming Lock for Software Security•JTAG (IEEE std. 1149.1 Compliant) Interface–Boundary-scan Capabilities According to the JTAG Standard–Extensive On-chip Debug Support–Programming of Flash, EEPROM, Fuses, and Lock Bits through the JTAG Interface •Peripheral Features–Two 8-bit Timer/Counters with Separate Prescalers and Compare Modes–One 16-bit Timer/Counter with Separate Prescaler, Compare Mode, and Capture Mode–Real Time Counter with Separate Oscillator–Four PWM Channels–8-channel, 10-bit ADC8 Single-ended Channels7 Differential Channels in TQFP Package Only2 Differential Channels with Programmable Gain at 1x, 10x, or 200x–Byte-oriented Two-wire Serial Interface–Programmable Serial USART–Master/Slave SPI Serial Interface–Programmable Watchdog Timer with Separate On-chip Oscillator–On-chip Analog Comparator•Special Microcontroller Features–Power-on Reset and Programmable Brown-out Detection–Internal Calibrated RC Oscillator–External and Internal Interrupt Sources–Six Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, Standby and Extended Standby•I/O and Packages–32 Programmable I/O Lines–40-pin PDIP, 44-lead TQFP, and 44-pad MLF•Operating Voltages–2.7 - 5.5V for ATmega16L–4.5 - 5.5V for ATmega16•Speed Grades–0 - 8 MHz for ATmega16L–0 - 16 MHz for ATmega16•Power Consumption @ 1 MHz, 3V, and 25°C for ATmega16L–Active: 1.1 mA–Idle Mode: 0.35 mA–Power-down Mode: < 1 µA 8-bit Microcontrollerwith 16K BytesNote: This is a summary document. A complete document is available on our Web site at .2ATmega16(L)2466HS–AVR–12/03Pin ConfigurationsFigure 1. Pinouts ATmega16DisclaimerTypical values contained in this datasheet are based on simulations and characteriza-tion of other AVR microcontrollers manufactured on the same process technology. Min and Max values will be available after the device is characterized.3ATmega16(L)2466HS–AVR–12/03OverviewThe ATmega16 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATmega16 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.Block DiagramFigure 2. Block Diagram4ATmega16(L)2466HS–AVR–12/03The AVR core combines a rich instruction set with 32 general purpose working registers.All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.The ATmega16 provides the following features: 16K bytes of In-System Programmable Flash Program memory with Read-While-Write capabilities, 512 bytes EEPROM, 1K byte SRAM, 32 general purpose I/O lines, 32 general purpose working registers, a JTAG interface for Boundary-scan, On-chip Debugging support and programming, three flexible Timer/Counters with compare modes, Internal and External Interrupts, a serial programmable USART, a byte oriented Two-wire Serial Interface, an 8-channel, 10-bit ADC with optional differential input stage with programmable gain (TQFP package only),a programmable Watchdog Timer with Internal Oscillator, an SPI serial port, and six software selectable power saving modes. The Idle mode stops the CPU while allowing the USART, Two-wire interface, A/D Converter, SRAM, Timer/Counters, SPI port, and interrupt system to continue functioning. The Power-down mode saves the register con-tents but freezes the Oscillator, disabling all other chip functions until the next External Interrupt or Hardware Reset. In Power-save mode, the Asynchronous Timer continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping.The ADC Noise Reduction mode stops the CPU and all I/O modules except Asynchro-nous Timer and ADC, to minimize switching noise during ADC conversions. In Standby mode, the crystal/resonator Oscillator is running while the rest of the device is sleeping.This allows very fast start-up combined with low-power consumption. In Extended Standby mode, both the main Oscillator and the Asynchronous Timer continue to run. The device is manufactured using Atmel’s high density nonvolatile memory technology.The On-chip ISP Flash allows the program memory to be reprogrammed in-system through an SPI serial interface, by a conventional nonvolatile memory programmer, or by an On-chip Boot program running on the AVR core. The boot program can use any interface to download the application program in the Application Flash memory. Soft-ware in the Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega16 is a powerful microcontroller that provides a highly-flexible and cost-effective solution to many embedded control applications.The ATmega16 AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, in-circuit emulators, and evaluation kits.Pin DescriptionsVCC Digital supply voltage.GNDGround.Port A (PA7..PA0)Port A serves as the analog inputs to the A/D Converter.Port A also serves as an 8-bit bi-directional I/O port, if the A/D Converter is not used.Port pins can provide internal pull-up resistors (selected for each bit). The Port A output buffers have symmetrical drive characteristics with both high sink and source capability.When pins PA0 to PA7 are used as inputs and are externally pulled low, they will source current if the internal pull-up resistors are activated. The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not running.5ATmega16(L)2466HS–AVR–12/03Port B (PB7..PB0)Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.Port B also serves the functions of various special features of the ATmega16 as listed on page 56.Port C (PC7..PC0)Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running. If the JTAG interface is enabled, the pull-up resistors on pins PC5(TDI), PC3(TMS) and PC2(TCK) will be acti-vated even if a reset occurs.Port C also serves the functions of the JTAG interface and other special features of the ATmega16 as listed on page 59.Port D (PD7..PD0)Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.Port D also serves the functions of various special features of the ATmega16 as listed on page 61.RESETReset Input. A low level on this pin for longer than the minimum pulse length will gener-ate a reset, even if the clock is not running. The minimum pulse length is given in Table 15 on page 36. Shorter pulses are not guaranteed to generate a reset.XTAL1Input to the inverting Oscillator amplifier and input to the internal clock operating circuit.XTAL2Output from the inverting Oscillator amplifier.AVCCAVCC is the supply voltage pin for Port A and the A/D Converter. It should be externally connected to V CC , even if the ADC is not used. If the ADC is used, it should be con-nected to V CC through a low-pass filter.AREFAREF is the analog reference pin for the A/D Converter.6ATmega16(L)2466HS–AVR–12/03Register Summary7ATmega16(L)2466HS–AVR–12/03Notes:1.When the OCDEN Fuse is unprogrammed, the OSCCAL Register is always accessed on this address. Refer to the debug-ger specific documentation for details on how to use the OCDR Register.2.Refer to the USART description for details on how to access UBRRH and UCSRC.3.For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addressesshould never be written.4.Some of the Status Flags are cleared by writing a logical one to them. Note that the CBI and SBI instructions will operate onall bits in the I/O Register, writing a one back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers $00 to $1F only.$01 ($21)TWSR TWS7TWS6TWS5TWS4TWS3–TWPS1TWPS0179$00 ($20)TWBRTwo-wire Serial Interface Bit Rate Register178AddressNameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Page8ATmega16(L)2466HS–AVR–12/03Instruction Set SummaryMnemonicsOperandsDescriptionOperationFlags#ClocksARITHMETIC AND LOGIC INSTRUCTIONSADD Rd, Rr Add two RegistersRd ← Rd + Rr Z,C,N,V,H 1ADC Rd, Rr Add with Carry two Registers Rd ← Rd + Rr + C Z,C,N,V,H 1ADIW Rdl,K Add Immediate to Word Rdh:Rdl ← Rdh:Rdl + K Z,C,N,V,S 2SUB Rd, Rr Subtract two RegistersRd ← Rd - Rr Z,C,N,V,H 1SUBI Rd, K Subtract Constant from Register Rd ← Rd - K Z,C,N,V,H 1SBC Rd, Rr Subtract with Carry two Registers Rd ← Rd - Rr - C Z,C,N,V,H 1SBCI Rd, K Subtract with Carry Constant from Reg.Rd ← Rd - K - C Z,C,N,V,H 1SBIW Rdl,K Subtract Immediate from Word Rdh:Rdl ← Rdh:Rdl - K Z,C,N,V,S 2AND Rd, Rr Logical AND RegistersRd ← Rd • Rr Z,N,V 1ANDI Rd, K Logical AND Register and Constant Rd ← Rd • K Z,N,V 1OR Rd, Rr Logical OR RegistersRd ← Rd v Rr Z,N,V 1ORI Rd, K Logical OR Register and Constant Rd ← Rd v K Z,N,V 1EOR Rd, Rr Exclusive OR Registers Rd ← Rd ⊕ Rr Z,N,V 1COM Rd One’s Complement Rd ← $FF − Rd Z,C,N,V 1NEG Rd Two’s Complement Rd ← $00 − Rd Z,C,N,V,H 1SBR Rd,K Set Bit(s) in Register Rd ← Rd v K Z,N,V 1CBR Rd,K Clear Bit(s) in Register Rd ← Rd • ($FF - K)Z,N,V 1INC Rd Increment Rd ← Rd + 1Z,N,V 1DEC Rd DecrementRd ← Rd − 1 Z,N,V 1TST Rd Test for Zero or Minus Rd ← Rd • Rd Z,N,V 1CLR Rd Clear Register Rd ← Rd ⊕ Rd Z,N,V 1SER Rd Set Register Rd ← $FF None 1MUL Rd, Rr Multiply Unsigned R1:R0 ← Rd x Rr Z,C 2MULS Rd, Rr Multiply SignedR1:R0 ← Rd x Rr Z,C 2MULSU Rd, Rr Multiply Signed with Unsigned R1:R0 ← Rd x Rr Z,C 2FMUL Rd, Rr Fractional Multiply Unsigned R1:R0 ← (Rd x Rr) << 1Z,C 2FMULS Rd, Rr Fractional Multiply SignedR1:R0 ← (Rd x Rr) << 1Z,C 2FMULSU Rd, Rr Fractional Multiply Signed with Unsigned R1:R0 ← (Rd x Rr) << 1Z,C 2BRANCH INSTRUCTIONSRJMP kRelative Jump PC ← PC + k + 1None 2IJMP Indirect Jump to (Z)PC ← ZNone 2JMP k Direct JumpPC ← kNone 3RCALL kRelative Subroutine Call PC ← PC + k + 1None 3ICALL Indirect Call to (Z)PC ← Z None 3CALL k Direct Subroutine Call PC ← kNone 4RET Subroutine Return PC ← STACK None 4RETI Interrupt Return PC ← STACKI 4CPSE Rd,Rr Compare, Skip if Equal if (Rd = Rr) PC ← PC + 2 or 3None 1 / 2 / 3CP Rd,Rr CompareRd − Rr Z, N,V,C,H 1 CPC Rd,Rr Compare with CarryRd − Rr − C Z, N,V,C,H 1CPI Rd,K Compare Register with Immediate Rd − KZ, N,V,C,H 1SBRC Rr, b Skip if Bit in Register Cleared if (Rr(b)=0) PC ← PC + 2 or 3 None 1 / 2 / 3SBRS Rr, b Skip if Bit in Register is Set if (Rr(b)=1) PC ← PC + 2 or 3None 1 / 2 / 3SBIC P, b Skip if Bit in I/O Register Cleared if (P(b)=0) PC ← PC + 2 or 3 None 1 / 2 / 3SBIS P, b Skip if Bit in I/O Register is Set if (P(b)=1) PC ← PC + 2 or 3None 1 / 2 / 3BRBS s, k Branch if Status Flag Set if (SREG(s) = 1) then PC ←PC+k + 1None 1 / 2BRBC s, k Branch if Status Flag Cleared if (SREG(s) = 0) then PC ←PC+k + 1None 1 / 2BREQ k Branch if Equal if (Z = 1) then PC ← PC + k + 1None 1 / 2BRNE k Branch if Not Equal if (Z = 0) then PC ← PC + k + 1None 1 / 2BRCS k Branch if Carry Set if (C = 1) then PC ← PC + k + 1None 1 / 2BRCC k Branch if Carry Cleared if (C = 0) then PC ← PC + k + 1None 1 / 2BRSH k Branch if Same or Higher if (C = 0) then PC ← PC + k + 1None 1 / 2BRLO k Branch if Lower if (C = 1) then PC ← PC + k + 1None 1 / 2BRMI k Branch if Minus if (N = 1) then PC ← PC + k + 1None 1 / 2BRPL k Branch if Plusif (N = 0) then PC ← PC + k + 1None 1 / 2BRGE k Branch if Greater or Equal, Signed if (N ⊕ V= 0) then PC ← PC + k + 1None 1 / 2BRLT k Branch if Less Than Zero, Signed if (N ⊕ V= 1) then PC ← PC + k + 1None 1 / 2BRHS k Branch if Half Carry Flag Set if (H = 1) then PC ← PC + k + 1None 1 / 2BRHC k Branch if Half Carry Flag Cleared if (H = 0) then PC ← PC + k + 1None 1 / 2BRTS k Branch if T Flag Set if (T = 1) then PC ← PC + k + 1None 1 / 2BRTC k Branch if T Flag Cleared if (T = 0) then PC ← PC + k + 1None 1 / 2BRVS k Branch if Overflow Flag is Set if (V = 1) then PC ← PC + k + 1None 1 / 2BRVCk Branch if Overflow Flag is Clearedif (V = 0) then PC ← PC + k + 1None1 / 29ATmega16(L)2466HS–AVR–12/03BRIE k Branch if Interrupt Enabled if ( I = 1) then PC ← PC + k + 1None 1 / 2BRID k Branch if Interrupt Disabled if ( I = 0) then PC ← PC + k + 1None 1 / 2DATA TRANSFER INSTRUCTIONSMOV Rd, Rr Move Between Registers Rd ← RrNone 1MOVW Rd, Rr Copy Register Word Rd+1:Rd ← Rr+1:RrNone 1LDI Rd, K Load Immediate Rd ← KNone 1LD Rd, X Load IndirectRd ← (X)None 2LD Rd, X+Load Indirect and Post-Inc.Rd ← (X), X ← X + 1None 2LD Rd, - X Load Indirect and Pre-Dec.X ← X - 1, Rd ← (X)None 2LD Rd, Y Load IndirectRd ← (Y)None 2LD Rd, Y+Load Indirect and Post-Inc.Rd ← (Y), Y ← Y + 1None 2LD Rd, - Y Load Indirect and Pre-Dec.Y ← Y - 1, Rd ← (Y)None 2LDD Rd,Y+q Load Indirect with Displacement Rd ← (Y + q)None 2LD Rd, Z Load IndirectRd ← (Z)None 2LD Rd, Z+Load Indirect and Post-Inc.Rd ← (Z), Z ← Z+1None 2LD Rd, -Z Load Indirect and Pre-Dec.Z ← Z - 1, Rd ← (Z)None 2LDD Rd, Z+q Load Indirect with Displacement Rd ← (Z + q)None 2LDS Rd, k Load Direct from SRAM Rd ← (k)None 2ST X, Rr Store Indirect(X) ← RrNone 2ST X+, Rr Store Indirect and Post-Inc.(X) ← Rr, X ← X + 1None 2ST - X, Rr Store Indirect and Pre-Dec.X ← X - 1, (X) ← Rr None 2ST Y, Rr Store Indirect(Y) ← RrNone 2ST Y+, Rr Store Indirect and Post-Inc.(Y) ← Rr, Y ← Y + 1None 2ST - Y, Rr Store Indirect and Pre-Dec.Y ← Y - 1, (Y) ← Rr None 2STD Y+q,Rr Store Indirect with Displacement (Y + q) ← Rr None 2ST Z, Rr Store Indirect(Z) ← RrNone 2ST Z+, Rr Store Indirect and Post-Inc.(Z) ← Rr, Z ← Z + 1None 2ST -Z, Rr Store Indirect and Pre-Dec.Z ← Z - 1, (Z) ← Rr None 2STD Z+q,Rr Store Indirect with Displacement (Z + q) ← Rr None 2STS k, RrStore Direct to SRAM (k) ← Rr None 2LPM Load Program Memory R0 ← (Z)None 3LPM Rd, Z Load Program MemoryRd ← (Z)None 3LPM Rd, Z+Load Program Memory and Post-Inc Rd ← (Z), Z ← Z+1None 3SPM Store Program Memory (Z) ← R1:R0None -IN Rd, P In Port Rd ← PNone 1OUT P, Rr Out PortP ← Rr None 1PUSH Rr Push Register on Stack STACK ← Rr None 2POP Rd Pop Register from Stack Rd ← STACKNone 2BIT AND BIT-TEST INSTRUCTIONSSBI P,b Set Bit in I/O Register I/O(P,b) ← 1None 2CBI P,b Clear Bit in I/O Register I/O(P,b) ← 0None 2LSL Rd Logical Shift Left Rd(n+1) ← Rd(n), Rd(0) ← 0Z,C,N,V 1LSR Rd Logical Shift Right Rd(n) ← Rd(n+1), Rd(7) ← 0Z,C,N,V 1ROL Rd Rotate Left Through Carry Rd(0)←C,Rd(n+1)← Rd(n),C ←Rd(7)Z,C,N,V 1ROR Rd Rotate Right Through Carry Rd(7)←C,Rd(n)← Rd(n+1),C ←Rd(0)Z,C,N,V 1ASR Rd Arithmetic Shift Right Rd(n) ← Rd(n+1), n=0..6Z,C,N,V 1SWAP Rd Swap Nibbles Rd(3..0)←Rd(7..4),Rd(7..4)←Rd(3..0)None 1BSET s Flag Set SREG(s) ← 1SREG(s)1BCLR s Flag ClearSREG(s) ← 0 SREG(s)1BST Rr, b Bit Store from Register to T T ← Rr(b)T 1BLD Rd, b Bit load from T to Register Rd(b) ← TNone 1SEC Set Carry C ← 1C 1CLC Clear Carry C ← 0C 1SEN Set Negative Flag N ← 1N 1CLN Clear Negative Flag N ← 0N 1SEZ Set Zero Flag Z ← 1Z 1CLZ Clear Zero Flag Z ← 0Z 1SEI Global Interrupt Enable I ← 1I 1CLI Global Interrupt Disable I ← 0I 1SES Set Signed Test Flag S ← 1S 1CLS Clear Signed Test FlagS ← 0S 1SEVSet Twos Complement Overflow.V ← 1V1CLVClear Twos Complement Overflow V ← 0 V1SET Set T in SREG T ← 1T 1CLT Clear T in SREG T ← 0 T 1SEH Set Half Carry Flag in SREG H ← 1H 1MnemonicsOperandsDescriptionOperationFlags#Clocks10ATmega16(L)2466HS–AVR–12/03CLHClear Half Carry Flag in SREG H ← 0H1MCU CONTROL INSTRUCTIONS NOP No Operation None 1SLEEP Sleep(see specific descr. for Sleep function)None 1WDR Watchdog Reset (see specific descr. for WDR/timer)None 1BREAKBreakFor On-Chip Debug OnlyNoneN/AMnemonics Operands DescriptionOperationFlags#Clocks11ATmega16(L)2466HS–AVR–12/0312ATmega16(L)2466HS–AVR–12/03Packaging Information44A13ATmega16(L)2466HS–AVR–12/0340P614ATmega16(L)2466HS–AVR–12/0344M115ATmega16(L)2466HS–AVR–12/03ErrataThe revision letter in this section refers to the revision of the ATmega16 device.ATmega16(L) Rev. I•IDCODE masks data from TDI input 1.IDCODE masks data from TDI inputThe JTAG instruction IDCODE is not working correctly. Data to succeeding devices are replaced by all-ones during Update-DR.Problem Fix / Workaround –If A Tmega16 is the only device in the scan chain, the problem is not visible.–Select the Device ID Register of the A Tmega16 by issuing the IDCODE instruction or by entering the T est-Logic-Reset state of the T AP controller to read out the contents of its Device ID Register and possibly data from succeeding devices of the scan chain. Issue the BYP ASS instruction to the ATmega16 while reading the Device ID Registers of preceding devices of the boundary scan chain.–If the Device IDs of all devices in the boundary scan chain must be captured simultaneously, the A Tmega16 must be the fist device in the chain.ATmega16(L) Rev. H•IDCODE masks data from TDI input 1.IDCODE masks data from TDI inputThe JTAG instruction IDCODE is not working correctly. Data to succeeding devices are replaced by all-ones during Update-DR.Problem Fix / Workaround –If A Tmega16 is the only device in the scan chain, the problem is not visible.–Select the Device ID Register of the A Tmega16 by issuing the IDCODE instruction or by entering the T est-Logic-Reset state of the T AP controller to read out the contents of its Device ID Register and possibly data from succeeding devices of the scan chain. Issue the BYP ASS instruction to the ATmega16 while reading the Device ID Registers of preceding devices of the boundary scan chain.–If the Device IDs of all devices in the boundary scan chain must be captured simultaneously, the A Tmega16 must be the fist device in the chain.ATmega16(L) Rev. G•IDCODE masks data from TDI input 1.IDCODE masks data from TDI inputThe JTAG instruction IDCODE is not working correctly. Data to succeeding devices are replaced by all-ones during Update-DR.Problem Fix / Workaround –If A Tmega16 is the only device in the scan chain, the problem is not visible.–Select the Device ID Register of the A Tmega16 by issuing the IDCODE instruction or by entering the T est-Logic-Reset state of the T AP controller to read out the contents of its Device ID Register and possibly data from succeeding devices of the scan chain. Issue the BYP ASS instruction to the ATmega16 while reading the Device ID Registers of preceding devices of the boundary scan chain.16ATmega16(L)2466HS–AVR–12/03–If the Device IDs of all devices in the boundary scan chain must be captured simultaneously, the A Tmega16 must be the fist device in the chain.17ATmega16(L)2466HS–AVR–12/03Datasheet Change Log for ATmega16This section contains a log on the changes made to the datasheet for ATmega16.Changes from Rev. 2466G-10/03 to Rev. 2466H-12/03All page numbers refer to this document.1.Updated “Calibrated Internal RC Oscillator” on page 27.Changes from Rev. 2466F-02/03 to Rev. 2466G-10/03All page numbers refer to this document.1.Removed “Preliminary” from the datasheet.2.Changed ICP to ICP1 in the datasheet.3.Updated “JTAG Interface and On-chip Debug System” on page 34.4.Updated assembly and C code examples in “Watchdog Timer Control Regis-ter – WDTCR” on page 41.5.Updated Figure 46 on page 101.6.Updated Table 15 on page 36, Table 82 on page 215 and Table 115 on page274.7.Updated “Test Access Port – TAP” on page 220 regarding JTAGEN.8.Updated description for the JTD bit on page 229.9.Added note 2 to Figure 126 on page 251.10.Added a note regarding JTAGEN fuse to Table 105 on page 259.11.Updated Absolute Maximum Ratings* and DC Characteristics in “ElectricalCharacteristics” on page 289.12.Updated “ATmega16 Typical Characteristics” on page 297.13.Fixed typo for 16 MHz MLF package in “Ordering Information” on page 11.14.Added a proposal for solving problems regarding the JTAG instructionIDCODE in “Errata” on page 15.Changes from Rev. 2466E-10/02 to Rev. 2466F-02/03All page numbers refer to this document.1.Added note about masking out unused bits when reading the ProgramCounter in “Stack Pointer” on page 10.2.Added Chip Erase as a first step in “Programming the Flash” on page 286 and“Programming the EEPROM” on page 287.3.Added the section “Unconnected pins” on page 53.18ATmega16(L)2466HS–AVR–12/034.Added tips on how to disable the OCD system in “On-chip Debug System” onpage 34.5.Removed reference to the “Multi-purpose Oscillator” application note and“32kHz Crystal Oscillator” application note, which do not exist.6.Added information about PWM symmetry for Timer0 and Timer2.7.Added note in “Filling the Temporary Buffer (Page Loading)” on page 252about writing to the EEPROM during an SPM Page Load.8.Removed ADHSM completely.9.Added Table 73, “TWI Bit Rate Prescaler,” on page 180 to describe the TWPSbits in the “TWI Status Register – TWSR” on page 179.10.Added section “Default Clock Source” on page 23.11.Added note about frequency variation when using an external clock. Noteadded in “External Clock” on page 29. An extra row and a note added in Table 118 on page 291. 12.Various minor TWI corrections.13.Added “Power Consumption” data in “Features” on page 1.14.Added section “EEPROM Write During Power-down Sleep Mode” on page 20.15.Added note about Differential Mode with Auto Triggering in “Prescaling andConversion Timing” on page 205.16.Added updated “Packaging Information” on page 12.Changes from Rev. 2466D-09/02 to Rev. 2466E-10/02All page numbers refer to this document.1.Updated “DC Characteristics” on page 289.Changes from Rev. 2466C-03/02 to Rev. 2466D-09/02All page numbers refer to this document.1.Changed all Flash write/erase cycles from 1,000 to 10,000.2.Updated the following tables: Table 4 on page 24, Table 15 on page 36, Table42 on page 83, Table 45 on page 110, Table 46 on page 110, Table 59 on page 141, Table 67 on page 165, Table 90 on page 233, Table 102 on page 257, “DC Characteristics” on page 289, Table 119 on page 291, Table 121 on page 293,and Table 122 on page 295.3.Updated “Errata” on page 15.Changes from Rev. 2466B-09/01 to Rev. 2466C-03/02All page numbers refer to this document.1.Updated typical EEPROM programming time, Table 1 on page 18.19ATmega16(L)2466HS–AVR–12/032.Updated typical start-up time in the following tables:Table 3 on page 23, Table 5 on page 25, Table 6 on page 26, Table 8 on page 27,Table 9 on page 27, and Table 10 on page 28.3.Updated Table 17 on page 41 with typical WDT Time-out.4.Added Some Preliminary Test Limits and Characterization Data.Removed some of the TBD's in the following tables and pages:Table 15 on page 36, Table 16 on page 40, Table 116 on page 272 (table removed in document review #D), “Electrical Characteristics” on page 289, Table 119 on page 291, Table 121 on page 293, and Table 122 on page 295.5.Updated TWI Chapter.Added the note at the end of the “Bit Rate Generator Unit” on page 176.6.Corrected description of ADSC bit in “ADC Control and Status Register A –ADCSRA” on page 217.7.Improved description on how to do a polarity check of the ADC doff results in“ADC Conversion Result” on page 214.8.Added JTAG version number for rev. H in Table 87 on page 227.9.Added not regarding OCDEN Fuse below Table 105 on page 259.10.Updated Programming Figures:Figure 127 on page 261 and Figure 136 on page 272 are updated to also reflect that AVCC must be connected during Programming mode. Figure 131 on page 268added to illustrate how to program the fuses.11.Added a note regarding usage of the “PROG_PAGELOAD ($6)” on page 278and “PROG_PAGEREAD ($7)” on page 278.12.Removed alternative algortihm for leaving JTAG Programming mode.See “Leaving Programming Mode” on page 286.13.Added Calibrated RC Oscillator characterization curves in section “ATmega16Typical Characteristics” on page 297.14.Corrected ordering code for MLF package (16MHz) in “Ordering Information”on page 11.15.Corrected Table 90, “Scan Signals for the Oscillators (1)(2)(3),” on page 233.Disclaimer: Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company’s standard warranty which is detailed in Atmel’s Terms and Conditions located on the Company’s web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel’s products are not authorized for use as critical components in life support devices or systems.Atmel CorporationAtmel Operations2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 487-2600Regional HeadquartersEuropeAtmel SarlRoute des Arsenaux 41Case Postale 80CH-1705 Fribourg SwitzerlandTel: (41) 26-426-5555Fax: (41) 26-426-5500AsiaRoom 1219Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong KongTel: (852) 2721-9778Fax: (852) 2722-1369Japan9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTel: (81) 3-3523-3551Fax: (81) 3-3523-7581Memory2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 436-4314Microcontrollers2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 436-4314La Chantrerie BP 7060244306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18Fax: (33) 2-40-18-19-60ASIC/ASSP/Smart CardsZone Industrielle13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00Fax: (33) 4-42-53-60-011150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300Fax: 1(719) 540-1759Scottish Enterprise Technology Park Maxwell BuildingEast Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000Fax: (44) 1355-242-743RF/AutomotiveTheresienstrasse 2Postfach 353574025 Heilbronn, Germany Tel: (49) 71-31-67-0Fax: (49) 71-31-67-23401150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300Fax: 1(719) 540-1759Biometrics/Imaging/Hi-Rel MPU/High Speed Converters/RF DatacomAvenue de Rochepleine BP 12338521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00Fax: (33) 4-76-58-34-80Literature Requests/literature2466HS–AVR–12/03© Atmel Corporation 2003. All rights reserved. Atmel ® and combinations thereof, AVR ®, and AVR Studio ® are the registered trademarks of Atmel Corporation or its subsidiaries. Microsoft ®, Windows ®, Windows NT ®, and Windows XP ® are the registered trademarks of Microsoft Corpo-ration. Other terms and product names may be the trademarks of others。

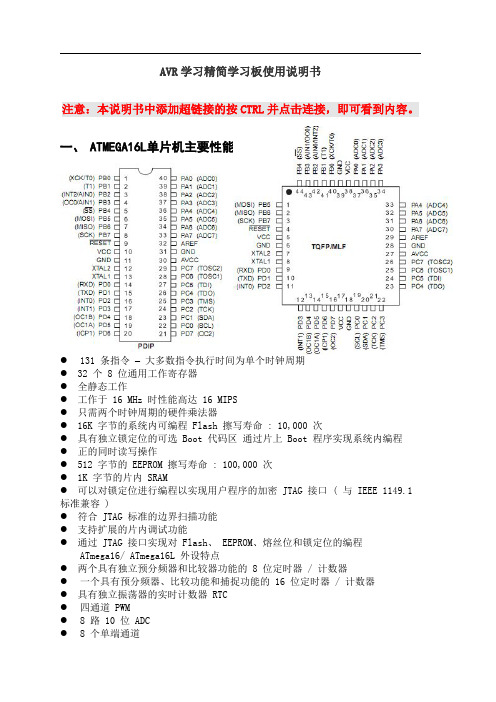

ATmega16实验板使用说明书

Atmega16实验板说明书硬件资料介绍 (2)调试软件安装 (3)编译环境的使用 (8)建立新的工程 (15)资料和例程 (18)注意:使用时先把调试器和开发板用数据线连起来,再插上USB线;停止使用时应先断开USB线切断电源,才能拔下数据线,否则可能会损坏调试器。

硬件资料介绍实验套件共分3部分,开发板,调试器,数据线(1根usb线,1根串口线)。

开发板文件夹图片/原理图里面有开发板的原理图图片和protel dxp 原理图文件。

如果开发板是没有焊好的套件可以对照元器件参数表和已焊好的图片(图片文件夹里有)先把开发板焊接完成。

焊接完成后先用万用表测量一下5V 与GND 之间是否短路,确定没有短路之后,插上USB 线接到电脑上,弹上开关SW1电源指示灯D1亮,说明电源已接通。

调试器调试软件安装要实现开发调试需要安装三个软件:PL2303驱动,avr studio 4,WinAVR。

这三个软件都在软件这个文件夹里。

首先安装usb驱动PL2303,如图点下一步。

点完成就可以了。

然后把调试器和电脑通过USB线联机。

如图这时调试器上的电源指示灯和信号指示灯都亮,而且电脑开始发现新硬件,新硬件可以安装使用。

这说明已经建立起连接,然后右击我的电脑—>属性—>硬件—>设备管理器,打开设备管理器界面,点开端口(COM和LPT)的“+”如图。

其中的Prolific usb-to-Serial Comm Port(COMx)就是调试器的usb设备。

端口号是多少根据个人电脑情况可能有差异。

下面我们要修改端口号,因为调试器里只提供COM1-COM3的通讯。

双击Prolific usb-to-Serial Comm Port(COMx)选项,弹出端口设置对话框,如图然后选端口设置—>高级,在端口号中选一个没有被占用且3以内的COM口,我的电脑上没有串口,我选的是COM1,如图然后点确定,重新打开设备管理器再看一下端口情况。

ATmega16单片机芯片资料

ATmega16单片机芯片资料产品特性• 高性能、低功耗的8 位AVR® 微处理器• 先进的RISC 结构– 131 条指令–大多数指令执行时间为单个时钟周期– 32个8 位通用工作寄存器–全静态工作–工作于16 MHz 时性能高达16 MIPS–只需两个时钟周期的硬件乘法器• 非易失性程序和数据存储器– 16K 字节的系统内可编程Flash擦写寿命: 10,000 次–具有独立锁定位的可选Boot 代码区通过片上Boot 程序实现系统内编程真正的同时读写操作– 512 字节的EEPROM擦写寿命: 100,000 次– 1K字节的片内SRAM–可以对锁定位进行编程以实现用户程序的加密• JTAG 接口( 与IEEE 1149.1 标准兼容)–符合JTAG 标准的边界扫描功能–支持扩展的片内调试功能–通过JTAG 接口实现对Flash、EEPROM、熔丝位和锁定位的编程• 外设特点–两个具有独立预分频器和比较器功能的8 位定时器/ 计数器–一个具有预分频器、比较功能和捕捉功能的16 位定时器/ 计数器–具有独立振荡器的实时计数器RTC–四通道PWM– 8路10 位ADC8 个单端通道TQFP 封装的7 个差分通道2 个具有可编程增益(1x, 10x, 或200x)的差分通道–面向字节的两线接口–两个可编程的串行USART–可工作于主机/ 从机模式的SPI 串行接口–具有独立片内振荡器的可编程看门狗定时器–片内模拟比较器• 特殊的处理器特点–上电复位以及可编程的掉电检测–片内经过标定的RC 振荡器–片内/ 片外中断源– 6种睡眠模式: 空闲模式、ADC 噪声抑制模式、省电模式、掉电模式、Standby 模式以及扩展的Standby 模式• I/O 和封装– 32 个可编程的I/O 口– 40引脚PDIP 封装, 44 引脚TQFP 封装, 与44 引脚MLF 封装• 工作电压:– ATmega16L:2.7 - 5.5V– ATmega16:4.5 - 5.5V• 速度等级– 0 - 8 MHz ATmega16L– 0 - 16 MHz ATmega16• ATmega16L 在1 MHz, 3V, 25°C 时的功耗–正常模式: 1.1 mA–空闲模式: 0.35 mA–掉电模式: < 1 μAAVR 内核具有丰富的指令集和32 个通用工作寄存器。

ATMEGA16A中文资料#(精选.)

ATMEGA16A中文资料高性能,低功耗AVR 8-bit微控制器•高级RISC建筑– 131条指令–绝大多数为单时钟周期执行– 32 x 8通用工作寄存器–全静态工作–高达16吞吐量在MIPS 16 MHz–片2-cycle乘数高耐久性非易失性内存段– 16K字节的程序存储器,在系统内可编程Flash– 512字节的EEPROM– 1K字节内部SRAM–写/擦除周期:10,000闪光/ 100,000的EEPROM–数据保存:在20年85°C/100年在25°C(1)–可选引导具有独立锁定Bits代码段•在系统编程的片上引导程序•真Read-While-Write操作–锁编程软件安全JTAG (IEEE std. 1149.1兼容)接口–边界扫描功能根据JTAG标准–广泛的片上调试支持–编程闪存,EEPROM,熔丝位和锁定Bits通过JTAG接口外设特点–两个8-bit定时器/计数器具有独立预分频器和比较模式–一个16-bit定时器/计数器具有独立预分频器,比较功能和捕捉模式–实时计数器具有独立振荡器–四PWM频道– 8-channel, 10-bit ADC• 8单端通道• 7在TQFP 包装差分通道只有• 2在1x, 10x,差分通道具有可编程增益或200x–面向字节的两线串行接口可编程串行USART的––主/从串行接口SPI–可编程看门狗定时器具有独立片内振荡器–片内模拟比较器单片机的特殊功能–上电复位和可编程的掉电检测–内部振荡器校准RC–外部和内部中断源– 6种睡眠模式:空闲,ADC降噪,省电,省电,待机和扩展待机I / O和封装– 32可编程I / O线– 40-pin PDIP, 44-lead TQFP,和44-pad QFN/MLF 工作电压– 2.7为- 5.5V ATmega16A速度等级– 0 -为16 MHz ATmega16A功耗@ 1 MHz, 3V,和25°C为ATmega16A–活动:0.6 mA–空闲模式:0.2 mA–掉电模式:< 1µA1.引脚配置图1-1.接脚分布 ATmega16A2.概述该ATmega16A是一种低功耗微控制器CMOS 8-bit关于加强AVR基础的RISC 架构.通过执行在一个时钟周期,ATmega16A强大的指令实现吞吐量接近每1 MIPS MHz允许系统设计师能够优化功耗与处理速度.2.1 框图该AVR内核具有丰富的指令与32一般工作寄存器的设置.所有32寄存器都直接连接到算术逻辑单元(ALU),允许两个独立寄存器进行访问的,单一的在一个时钟周期执行的指令.由此产生的建筑是提高了代码效率,同时实现吞吐量达快十倍con-ventional CISC微控制器.该ATmega16A提供了以下功能:16K字节的系统内可编程Flash程序存储器Read-While-Write能力,512字节EEPROM,1K字节SRAM, 32 通用I / O线,32通用工作寄存器,用于边界JTAG接口扫描,片上调试支持和编程,三个灵活定时器/计数器与com-削减模式,内部和外部中断,串行可编程的USART,一个字节为导向两线串行接口,一个8-channel, 10-bit ADC可选差分输入级与可编程增益(TQFP 包装只),一个可编程看门狗定时器内部振荡器的振荡器,一个SPI串行端口,以及六个软件设置省电模式.空闲模式停止在CPU同时允许的USART,两线接口,A / D转换器,SRAM,定时器/计数器,SPI口,外中断系统继续工作.掉电模式,保存寄存器内容,但冻结振荡器,禁用,直到下一个外部间的所有其他芯片功能,rupt或硬件复位.在省电模式下,异步定时器继续运行,允许用户保持一个时间基准,而其余的设备正在睡觉.该ADC降噪模式停止CPU和所有的I /除了异步定时器和O模块ADC,以最大限度地降低开关噪声在ADC转换.在待机模式下,crystal/reso- nator振荡器运行,而在器件其它部分在睡觉.这允许非常快速启动结合低功耗.在扩展待机模式下,主振荡器和异步定时器继续运行.该设备是采用Atmel的高密度非易失性内存技术.在上闪存芯片ISP允许程序存储器进行重新编程,通过SPI串行在系统接口,由传统的非易失性存储器编程,或者通过片内引导程序运行在AVR核心.引导程序可以使用任何下载的应用程序接口在应用程序闪存方案.在Boot区软件将继续运行而应用Flash区更新,提供真正的Read-While-Write操作.通过结合一8-bit RISC CPU与系统内可编程闪存集成在一个芯片,Atmel的ATmega16A是一个功能强大的单片机,它提供了高度灵活和成本有效解决了许多嵌入式控制应用.该ATmega16A AVR是支持了若干方案和系统开发工具套件包括:C编译器,宏汇编,程序调试器/模拟器,在线仿真器,和评价kits.2.22.2.1引脚说明VCC数字供电电压.2.2.2GND地面.2.2.3端口A (PA7:PA0)作为一个港口的A / D转换器的模拟输入.端口A也可作为8-bit双向I / O端口,如果A / D转换器不使用.港口pins 可提供内部上拉电阻(每个位选中). PA口输出缓冲器具有sym-既吸收大电流驱动器和源能力韵律特征.当pins PA0到PA7作为投入使用的和被外部拉低,将输出电流,如果他们的内部上拉电阻器被激活.港口是一个pins三态时,复位过程中,即使系统时钟没有运行.港口B (PB7:PB0)港口B是8-bit双向I /内部上拉电阻(每个位选中)O端口.该港口B输出缓冲器具有高汇和源对称的驱动特性能力.作为输入,端口B pins被外部拉低时将输出电流若拉电阻器被激活.港口B pins为三态时,复位过程中,即使系统时钟没有运行.港口B也可以用不同的特殊功能的ATmega16A作为上市职能页面57.2.2.5港口C (PC7:PC0)港口C是8-bit双向I /内部上拉电阻(每个位选中)O端口.该港口C输出缓冲器具有高汇和源对称的驱动特性能力.作为输入,端口C pins被外部拉低时将输出电流若拉电阻器被激活.港口C pins为三态时,复位过程中,即使系统时钟没有运行.如果JTAG接口使能,上拉电阻器pins PC5(TDI), PC3(TMS)和PC2(TCK)将被激活,即使发生复位.港口C还担任了JTAG接口功能和其他的特殊功能ATmega16A作为上市页面60.2.2.6港口D (PD7:PD0)港口D是8-bit双向I /内部上拉电阻(每个位选中)O端口.该港口D输出缓冲器具有高汇和源对称的驱动特性能力.作为输入,端口D pins被外部拉低时将输出电流若拉电阻器被激活.港口D pins为三态时,复位过程中,即使系统时钟没有运行.港口D也可以用不同的特殊功能的ATmega16A作为上市职能页面622.2.7复位复位输入.此管脚上出现了比最小脉冲长度较长的低级别将产生复位,即使系统时钟没有运行.最小脉冲宽度是由于在表27-2页296.更短的脉冲则不能保证可靠复位.2.2.8XTAL1输入到反相振荡放大器和输入到内部时钟工作电路.2.2.9XTAL2振荡器的输出反相放大器.AVCCAVCC是端口A和A / D转换的电源.它应该从外部con- 连接到VCC,即使ADC不使用.如果ADC使用,它应该连接到VCC通过一个低通滤波器.2.2.11AREFAREF是为A / D转换器的模拟参考引脚.3.资源一个开发工具,应用手册和说明书一整套可供下载/avr.注意:1.4.数据保留可靠性鉴定结果表明,该预测数据保留故障率要少得多比1 PPM对在20或85°C年100年在25°C5. 寄存器摘要注释:1.当OCDEN保险丝未编程,OSCCAL的寄存器总是访问该地址.请参阅调试ger具体文件的详细信息如何使用OCDR 寄存器.2.请参考详细的USART如何访问UBRRH与UCSRC寄存器的描述.3.对于未来的产品兼容,保留bits应写入零,如果访问.保留的I / O内存地址不应该被写入.4.状态标志清零记录一些人对他们的逻辑.请注意,CBI和SBI指示将操作所有在我bits / O的寄存器,记录一旗一回任何内容设置,从而扫清了国旗.指令的CBI和SBI 与寄存器$00工作$1F只.6.指令集汇总8.包装信息44A40P644M19.勘误表本节中的版本号是指该ATmega16A器件版本.9.1ATmega16A牧师. N的转速. Q••••第一个模拟比较器的转换可能会推迟中断可能会丢失记录在异步定时器定时器寄存器IDCODE的面具输入数据TDI读数使用ST或STS设置EERE位EEPROM触发意外的中断请求1.第一个模拟比较器的转换可能会推迟如果该设备是由一个缓慢上升VCC,第一个模拟比较器转换将需要更长的时间比预期的一些设备.问题的修复程序/解决方法当器件上电或复位,禁用然后启用theAnalog比较在第一次转换.2.中断可能会丢失记录在异步定时器定时器寄存器中断将被丢失,如果是一个计时器寄存器定时器时钟同步时写入异步定时器/计数器寄存器(TCNTx)是0x00.问题的修复程序/解决方法务必检查异步定时器/计数器寄存器也没有,也不值0xFF前记录 0x00到异步定时器控制寄存器(TCCRx),异步定时器计数器寄存器(TCNTx),或异步输出比较寄存器 (OCRx).3. IDCODE的面具输入数据TDI该JTAG指令IDCODE的是不能正常工作.数据到成功的设备在更新取代由all-ones - DR的.解决方法问题的修正/––如果ATmega16A是唯一的设备在扫描链,问题是不可见的.选择通过发出IDCODE指令的ID设备ATmega16A 寄存器或通过输入TAP控制器Test-Logic-Reset读出状态它的设备ID 寄存器和可能的数据内容从设备的成功扫描链.发出指示,而旁路读数的ATmega16A设备ID的边界扫描链上的设备寄存器.如果在边界所有设备的设备IDs扫描链必须被捕获同时,ATmega16A必须拳头链中的设备.–4. 读数 EEPROM的使用ST或STS设置EERE位触发意外的中断请求.读数 EEPROM的使用ST或STS命令设置在EERE EECR reg-位ister触发一个意想不到的EEPROM的中断请求.解决方法问题的修正/始终使用OUT或SBI要在EERE EECR10.修订历史数据表请注意,本节所指页码提及这个文件.该本节中提到的修订是指对文件的修改.致8154B – 07/091.2.更新“勘误表”第343.更新了与 Atmel的新地址的最后一页.致8154A – 06/081.初始的版本(在ATmega16 / L的基于数据表的修订2466R-AVR-05/08)变化做comparted ATmega16 / L的数据表修改2466R-AVR-05/08: -更新的说明“堆栈指针”页上12.-所有的电气特性会移至“电气特性”页上293.- 寄存器描述转移到分节在每章末尾.-新增“速度等级”第295.-在新图“典型特征”页上305.-新“订购信息”13.最新文件仅供参考已改成word文本。

ATmega16中文手册

产品特性•高性能、低功耗的 8位AVR®微处理器•先进的RISC结构–131 条指令 – 大多数指令执行时间为单个时钟周期–32个8位通用工作寄存器–全静态工作–工作于16 MHz时性能高达16 MIPS–只需两个时钟周期的硬件乘法器•非易失性程序和数据存储器–16K 字节的系统内可编程Flash擦写寿命: 10,000次–具有独立锁定位的可选Boot代码区通过片上Boot程序实现系统内编程真正的同时读写操作–512字节的EEPROM擦写寿命: 100,000次–1K字节的片内SRAM微控制器–可以对锁定位进行编程以实现用户程序的加密•JTAG 接口(与IEEE 1149.1标准兼容)–符合JTAG标准的边界扫描功能–支持扩展的片内调试功能–通过JTAG接口实现对Flash、EEPROM、熔丝位和锁定位的编程•外设特点–两个具有独立预分频器和比较器功能的8位定时器/计数器–一个具有预分频器、比较功能和捕捉功能的16位定时器/计数器–具有独立振荡器的实时计数器RTC–四通道PWM–8路10位ADC8 个单端通道TQFP封装的7个差分通道2个具有可编程增益(1x, 10x, 或200x)的差分通道–面向字节的两线接口–两个可编程的串行USART–可工作于主机/从机模式的SPI串行接口–具有独立片内振荡器的可编程看门狗定时器–片内模拟比较器•特殊的处理器特点–上电复位以及可编程的掉电检测–片内经过标定的RC振荡器–片内/片外中断源–6种睡眠模式: 空闲模式、ADC噪声抑制模式、省电模式、掉电模式、Standby模式以及扩展的Standby模式•I/O和封装–32 个可编程的I/O口–40引脚PDIP封装, 44引脚TQFP封装,与44引脚MLF封装•工作电压:–ATmega16L:2.7 - 5.5V–ATmega16:4.5 - 5.5V•速度等级–0 - 8 MHz ATmega16L–0 - 16 MHz ATmega16•ATmega16L在1 MHz, 3V, 25°C时的功耗–正常模式: 1.1 mA–空闲模式: 0.35 mA–掉电模式: < 1 µA2ATmega16(L)2466G–AVR–10/03引脚配置Figure 1. ATmega16的引脚声明本数据手册的典型值来源于对器件的仿真,以及其他基于相同产生工艺的 AVR 微控制器的标定特性。

AVR教程系列一(6):ATmega16 简介(一)

ATmega16 简介ATmega16是基于增强的AVR RISC结构的低功耗8 位CMOS微控制器。

由于其先进的指令集以及单时钟周期指令执行时间,ATmega16 的数据吞吐率高达1 MIPS/MHz,从而可以缓减系统在功耗和处理速度之间的矛盾。

ATmega16 AVR 内核具有丰富的指令集和32 个通用工作寄存器。

所有的寄存器都直接与算逻单元(ALU) 相连接,使得一条指令可以在一个时钟周期内同时访问两个独立的寄存器。

这种结构大大提高了代码效率,并且具有比普通的CISC 微控制器最高至10 倍的数据吞吐率。

ATmega16 有如下特点:16K字节的系统内可编程Flash(具有同时读写的能力,即RWW),512 字节EEPROM,1K 字节SRAM,32 个通用I/O 口线,32 个通用工作寄存器,用于边界扫描的JTAG 接口,支持片内调试与编程,三个具有比较模式的灵活的定时器/ 计数器(T/C),片内/外中断,可编程串行USART,有起始条件检测器的通用串行接口,8路10位具有可选差分输入级可编程增益(TQFP 封装) 的ADC ,具有片内振荡器的可编程看门狗定时器,一个SPI 串行端口,以及六个可以通过软件进行选择的省电模式。

工作于空闲模式时CPU 停止工作,而USART、两线接口、A/D 转换器、SRAM、T/C、SPI 端口以及中断系统继续工作;掉电模式时晶体振荡器停止振荡,所有功能除了中断和硬件复位之外都停止工作;在省电模式下,异步定时器继续运行,允许用户保持一个时间基准,而其余功能模块处于休眠状态; ADC 噪声抑制模式时终止CPU 和除了异步定时器与ADC 以外所有I/O 模块的工作,以降低ADC 转换时的开关噪声; Standby 模式下只有晶体或谐振振荡器运行,其余功能模块处于休眠状态,使得器件只消耗极少的电流,同时具有快速启动能力;扩展Standby 模式下则允许振荡器和异步定时器继续工作。

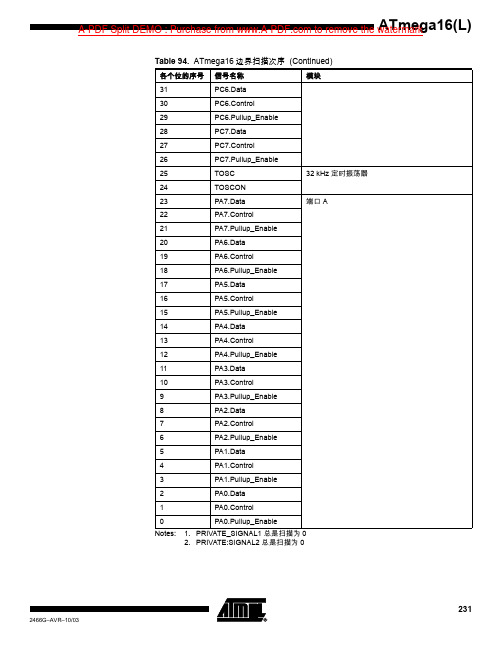

atmega16中文资料.0004

29

PC6.Pullup_Enable

28

PC7.Data

27

PC7.Control

26

PC7.Pullup_Enable

25

TOSC

32 kHz 定时振荡器

24

TOSCON

23

PA7.Data

端口 A

22

PA7.Control

21

PA7.Pullup_Enable

20

PA6.Data

19

PA6.Control

RWW 区

如果 Boot Loader 软件是对 RWW 区内的某一页进行编程,则可以从 Flash 中读取代码, 但只限于 NRWW 区内的代码。在 Flash 编程期间,用户软件必须保证没有对 RWW 区的 读访问。如果用户软件在编程过程中试图读取位于 RWW 区的代码 ( 如通过 call/jmp/lpm 指令或中断 ),软件可能会终止于一个未知状态。为了避免这种情况的发生,需要禁止中 断或将其转移到 Boot Loader 区。 Boot Loader 总是位于 NRWW 存储区。只要 RWW 区 处于不能读访问的状态,存储程序存储器控制和状态寄存器 (SPMCSR) 的 RWW 区忙标 志位 RWWSB 置位。编程结束后,要在读取 位于 RWW 区的代码之前通过软件清除 RWWSB。具体如何清除RWWSB请参见P238 “保存程序存储器控制寄存器 – SPMCR” 。

No Read-While-Write (NRWW) Section

Z-pointer Addresses NRWW Section

CPU is Halted during the Operation

234 ATmega16(L)

第二章 ATmega16芯片资源

•支持在线编程(In-System Programming)

•1K字节的片内SRAM

•512字节的在线可编程EEPROM •可编程的程序加密位

外围资源

•2个带预分频器、具有比较、PWM功能的8位定时器/计数器 •1个带预分频器、具有比较、捕获和PWM功能的16位定时器 /计数器 •1个具有独立振荡器的异步实时时钟(RTC) •4个PWM通道 •8通道10位ADC •1个I2C的串行口 •1个可编程的串行USART接口 •1个主/从收/发的SPI同步串行接口 •带片内RC振荡器的可编程看门狗定时器WDT •片内模拟比较器

ATmega16 封装---PDIP40封装

ATmega16 封装---TQFP44封装

2.ATmega16 资源及性能

AVR RISC 结构

• 高性能、低功耗RISC的结构 • 130条指令,大多数为单周期指令 • 32×8的通用(工作)寄存器+外设控制寄 存器 • 工作在16MHz时具有16MIPS的性能 • 片内集成硬件乘法器(执行速度为2个时钟 周期)

程序和数据存储器、工作寄存器

ATmega16具有16K字节的 在线编程Flash,用于存放程 序指令代码。因为所有的AVR 指令为16 位或32 位,故而 Flash 组织成8K x 16 位的 形式。 Flash存储器至少可以擦 写10,000次。ATmega16的程 序计数器(PC)为13位,因此 可以寻址8K 字的程序存储器 空间。 用SPI 或JTAG 接口实现 对Flash 的串行下载。

•/RESRT:复位输入。在该引脚上,一个超过系统规定长 度的低电平信号,将引起系统复位。低于系统规定长度的 低电平信号脉冲,不能保证可靠复位。 •XTAL1:内部反转晶振放大器的输入端和向内部时钟操作 电路的输入端。 •XTAL2:内部反转晶振放大器的输出端。

AVR ATmega16寄存器(修订版)

ATmega16寄存器说明修订版v1.1 本版修订了很多原版存在的错误同时使其更加清晰易懂原作者:未知修订:拉拉和瑶瑶SREG | I | T | H | S | V | N | Z | C |// 状态寄存器SREGI : 全局中断使能T : 位复制存储位H : 半进位标志位表示算术运算发生了半进位S : 符号位S为负数标志N与2的补码溢出标志V的异或V : 2的补码溢出标志位N : 负数标志位Z : 零标志位C : 进位标志位OSCCAL |CAL7 | CAL6 | CAL5 | CAL4 | CAL3 | CAL2 | CAL1 | CAL0 |//振荡器标定寄存器OSCCAL OSCAL数值最小频率,标称频率的百分比(%)最大频率,标称频率的百分比(%)0x00 50 1000x7F 75 1500xFF 100 200(编者注:一般可使用0x7F)MCUCR | SM2 | SE | SM1 | SM0 | ISC11 | ISC10 | ISC01 | ISC00 | //MCU控制寄存器MCUCR SM2:0 休眠模式000 空闲模式(停止CPU_clk 和FLASH_clk)001 ADC噪声抑制模式(停止IO_clk CPU_clk 和FLASH_clk)010 掉电模式(停止所有时钟,只有异步模块可以继续工作)011 省电模式100 --101 --110 Standby 模式(仅在使用外部晶振或谐振器时,Standby模式才可用)111 扩展Stabdby模式SE 休眠使能ISCx1:0 说明00 INTx为低电平产生中断请求01 INTx上的任意跳变产生中断请求10 INTx上的下降沿产生中断请求11 INTx上的上升沿产生中断请求(编者注:外部中断0,1触发模式在此设置)MCUCSR | JTD | ISC2 | -- | JTRF | WDRF | BORF | EXTRF | PORF |//MCU控制和状态寄存器MCUCSR JTD 禁止JTAG 接口ISC2 中断2触发方式控制位(0-下降沿中断1-上升沿中断)JTRF JTAG 复位标志WDRF 看门狗复位标志BORF 掉电检测复位标志EXTRF 外部复位标志PORF 上电复位标志GICR | INT1 | INT0 | INT2 | -- | -- | -- | IVSEL | IVCE |// 通用中断控制寄存器INT1 使能外部中断请求1INT0 使能外部中断请求0INT2 使能外部中断请求2IVSEL 中断向量选择IVCE 中断向量修改使能GIFR | INTF1 | INTF0 | INTF2 | -- | -- | -- | -- | -- | // 通用中断标志寄存器INTF1 外部中断标志1INTF0 外部中断标志0INTF2 外部中断标志2(编者注:GICR表明能否中断而GIFR则是是否中断)SPMCR | SPMIE | RWWSB | -- | RWWSRE | BLBSET | PGWRT | PGERS | SPMEN |//保存程序存储器控制寄存器SPMIE SPM 中断使能RWWSB RWW 区忙标志RWWSRE RWW 区读使能BLBSET Boot 锁定位设置PGWRT 页写入PWERS 页擦除SPMEN 存贮程序存储器使能OCDR | MSB/IDRD | | | | | | | LSB | // 片上调试寄存器SFIOR | ADTS2 | ADTS1 | ADTS0 | -- | ACME | PUD | PSR2 | PSR10 | // 特殊功能I/O寄存器ADTS[2:0] ADC自动触发源位000 连续转换模式001 模拟比较器010 外部中断请求0011 定时器/计数器0比较匹配100 定时器/ 计数器1溢出101 定时器/计数器比较匹配B110 定时器/计数器1溢出111 定时器/计数器1捕捉事件ACME 模拟比较器多路复用器使能0 AIN1 连接到比较器的负极输入端1 ADC 多路复用器为模拟比较器选择负极输入PUD 禁用上拉电阻PSR2 预分频复位T/C2PSR10 T/C1 与T/C0 预分频器复位//***********************// PORT端口相关寄存器//******************************// PORTA | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | // 数据寄存器DDRA | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | // 数据方向寄存器PINA | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | // 端口输入引脚PORTB | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |DDRB | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |PINB | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |PORTC | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |DDRC | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |PINC | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |PORTD | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |DDRD | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |PIND | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |(编者注:DDRx为数据方向寄存器,1为输出,0为输入;PORTx为数据寄存器:作为输入时,若允许上//***********************// USART串口相关寄存器//**************************// UDR | RXB7 | RXB6 | RXB5 | RXB4 | RXB3 | RXB2 | RXB1 | RXB0 | // 接收数据缓冲寄存器| TXB7 | TXB6 | TXB5 | TXB4 | TXB3 | TXB2 | TXB1 | TXB0 |// 发送数据缓冲寄存器UCSRA| RXC | TXC | UDRE | FE | DOR | PE | U2X | MPCM | // USART 控制和状态寄存器A RXC USART 接收结束标志TXC USART 发送结束标志UDRE USART 数据寄存器空标志FE 帧错误标志DOR 数据溢出标志PE 奇偶校验错误标志U2X 倍速发送MPCM 多处理器通信模式UCSRB | RXCIE | TXCIE | UDRIE | RXEN | TXEN | UCSZ2 | RXB8 | TXB8 |//USART 控制和状态寄存器B RXCIE 接收结束中断使能TXCIE 发送结束中断使能UDRIE USART 数据寄存器空中断使能RXEN 接收使能TXEN 发送使能UCSZ2 字符长度[2]RXB8 接收数据位8TXB8 发送数据位8UCSRC | URSEL | UMSEL | UPM1 | UPM0 | USBS | UCSZ1 | UCSZ0 | UCPOL |//USART控制和状态寄存器CURSEL 寄存器选择0 UBRRH1 UCSRCUMSEL USART 模式选择0 异步模式1 同步模式UPM1 UPM00 0 禁止0 1 保留1 0 偶校验1 1 奇校验USBS 停止位选择0 停止位数为11 停止位数为2UCSZ2 UCSZ1 UCSZ0 字符长度0 0 1 60 1 0 70 1 1 81 0 0 保留1 0 1 保留1 1 0 保留1 1 1 9//UCPOL为时钟极性选择:UCPOL 发送数据的改变(TxD 引脚的输出) 接收数据的采样(RxD 引脚的输入)0 XCK上升沿XCK下降沿1 XCK下降沿XCK上升沿(编者注:一般如果使用的是查询发,中断收,应打开RXCIE,RXEN,TXEN)UBBRH | U2X | ——| ——| ——| Bit11 | Bit10 | Bit9 | Bit8 | //波特率寄存器高4位UBBRL | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | //波特率寄存器第8位使用模式波特率计算公式UBBR值计算公式异步正常模式(U2X=0)Baud = F(osc)/16(UBBR+1) UBBR = F(osc)/16Baud - 1异步倍速模式(U2X=1)Baud = F(osc)/8(UBBR+1) UBBR = F(osc)/8Baud - 1同步主机模式Baud = F(osc)/2(UBBR+1) UBBR = F(osc)/2Baud – 1//***********************// SPI相关寄存器 //******************************//SPCR | SPIE | SPE | DORD | MSTR | CPOL | CPHA | SPR1 | SPR0 | //SPI控制寄存器SPIE 使能SPI中断位SPE 使能SPI位DORD 数据次序0 数据的MSB首先发送1 数据的LSB首先发送MSTR 主从选择0 从机模式1 主机模式CPOL 时钟极性CPOL 起始沿结束沿空闲时的SCK0 上升沿下降沿低电平1 下降沿上升沿高电平CPHA 时钟相位CPHA 起始沿结束沿0 采样设置1 设置采样SPR[1:0] SPI时钟速率选择位SPR2x SPR1 SPR0 SCK频率0 0 0 focs/40 0 1 fosc/160 1 0 fosc/640 1 1 fosc/1281 0 0 fosc/21 1 0 fosc/321 1 1 fosc/64SPSR | SPIF | WCOL | -- | -- | -- | -- | -- | SPI2X | // SPI状态寄存器SPIF SPI中断标志WCOL 写碰撞标志SPI2X SPI倍速位(若为主机SCK可达fosc/2 若为从机则只能保证fosc/4)SPDR | MSB | -- | -- | -- | -- | -- | -- | LSB | //SPI数据寄存器写寄存器将启动数据传输,读寄存器将读取寄存器的接收缓存器//***********************// ADC串口相关寄存器//**************************// ADMUX | REFS1 | REFS0 | ADLAR | MUX4 | MUX3 | MUX2 | MUX1 | MUX0 | //ADC 多工选择寄存器REFS1 REFS0 参考电压选择0 0 AREF 、内部Vref关闭0 1 A Vcc AREF 引脚外加滤波电容1 0 保留1 1 2.56V 片内基准电压源,AREF引脚外加滤波电容ADLAR ADC转换结果左对齐0 转换结果右对齐1 转换结果左对齐(编者注:当对精度要求低时可以采取右对齐,只读低8位即可;否则采取左对齐,通过将数据左移2位+低八位&&0x03即可)MUX[4:0] 单端输入正差分输入负差分输入增益00000 ADC000001 ADC100010 ADC200011 ADC300100 ADC400101 ADC500110 ADC600111 ADC701000 ADC0 ADC0 10x01001 ADC1 ADC0 10x01010 ADC0 ADC0 200x01011 ADC1 ADC0 200x01100 ADC2 ADC2 10x01101 ADC3 ADC2 10x01110 ADC2 ADC2 200x01111 ADC3 ADC2 200x10000 ADC0 ADC1 1x10001 ADC1 ADC1 1x10010 ADC2 ADC1 1x10011 ADC3 ADC1 1x10100 ADC4 ADC1 1x10101 ADC5 ADC1 1x10110 ADC6 ADC1 1x10111 ADC7 ADC1 1x11000 ADC0 ADC2 1x11001 ADC1 ADC2 1x11010 ADC2 ADC2 1x11011 ADC3 ADC2 1x11100 ADC4 ADC2 1x11101 ADC5 ADC2 1x11110 1.22V(VBG)11111 0V(GND)ADCSRA | ADEN | ADSC | ADATE | ADIF | ADIE | ADPS2 | ADPS1 | ADPS0 | //ADC控制和状态寄存器A ADEN ADC使能位ADSC ADC开始转换位ADATE ADC自动触发使能位ADIF ADC中断标志位ADIE ADC中断使能位ADPS[2:0] 为ADC预分频选择位ADPS[2:0] 分频因子000 2001 2010 4011 8100 16101 32110 64111 128ADCH | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | // ADC数据寄存器高位ADCL | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | // ADC数据寄存器低位SFIOR | ADTS2 | ADTS1 | ADTS0 | -- | ACME | PUD | PSR2 | PSR10 | // 特殊功能I/O寄存器ADTS[2:0] 为ADC自动触发源位ADTS[2:0] 触发源000 连续转换模式001 模拟比较器010 外部中断请求0011 定时器/计数器0比较匹配100 定时器/ 计数器1溢出101 定时器/计数器比较匹配B110 定时器/计数器1溢出111 定时器/计数器1捕捉事件//***********************// 模拟比较器相关寄存器//**********************// SFIOR | ADTS2 | ADTS1 | ADTS0 | -- | ACME | PUD | PSR2 | PSR10 | // 特殊功能I/O寄存器ACME 模拟比较器多路复用器使能0 AIN1 连接到比较器的负极输入端1 ADC 多路复用器为模拟比较器选择负极输入ACSR | ACD | ACBG | ACO | ACI | ACIE | ACIC | ACIS1 | ACIS0 | // 模拟比较器控制和状态寄存器ACD 模拟比较器禁用ACD 置位时,模拟比较器的电源被切断ACBG 选择模拟比较器的能隙基准源ACBG 置位后,模拟比较器的正极输入由能隙基准源所取代ACO 模拟比较器输出ACI 模拟比较器中断标志ACIE 模拟比较器中断使能ACIC 模拟比较器输入捕捉使能ACIS[1:0] 模拟比较器中断模式选择ACIS1 ACIS0 中断模式0 0 比较器输出变化即可触发中断0 1 保留1 0 比较器输出的下降沿产生中断1 1 比较器输出的上升沿产生中断模拟比较器复用输入ACME ADEN MUX[2:0] 模拟比较器负极输入0 x xxx AIN11 1 xxx AIN11 0 000 ADC01 0 001 ADC11 0 010 ADC21 0 011 ADC31 0 100 ADC41 0 101 ADC51 0 110 ADC61 0 111 ADC7//***********************// 外部中断相关寄存器//**************************// MCUCR | SM2 | SE | SM1 | SM0 | ISC11 | ISC10 | ISC01 | ISC00 | // MCU控制寄存器ISx1 ISx0 说明0 0 INTx为低电平产生中断请求0 1 INTx上的任意跳变产生中断请求1 0 INTx上的下降沿产生中断请求1 1 INTx上的上升沿产生中断请求MCUCSR | JTD | ISC2 | -- | JTRF | WDRF | BORF | EXTRF | PORF | // MCU控制和状态寄存器ISC2 中断2触发方式控制位0 下降沿触发中断1 上升沿触发中断GICR | INT1 | INT0 | INT2 | -- | -- | -- | IVSEL | IVCE | // 通用中断控制寄存器INT1 使能外部中断请求1INT0 使能外部中断请求0INT2 使能外部中断请求2GIFR | INTF1 | INTF0 | INTF2 | -- | -- | -- | -- | -- | // 通用中断标志寄存器INTF1 外部中断标志1INTF0 外部中断标志0INTF2 外部中断标志2//***********************// Timer0相关寄存器//**************************//TCCR0 | FOC0 | WGM00 | COM01 | COM00 | WGM01 | CS02 | CS01 | CS00 | //T/C0 控制寄存器FOC0 强制输出比较WGM01:0为波形产生模式(编者注:普通模式下,一直加到0xFF,然后从0开始;CTC模式下一直加到OCR0,然后从0开始;快速PWM从零开始加到OCR0再加到0xFF,然后再从0开始;相位修正PWM从0加到OCR0然后加到0XFF然后减计数到OCR0再减到0)WGM01:0 T/C的波形产生模式TOP OCR0更新时间TOV0的置位时刻00 普通0XFF 立即更新MAX01 PWM,相位修正0xFF TOP BOTTOM10 CTC OCR0 立即更新MAX11 快速PWM 0xFF TOP MAXCOM01:0选择T/C0工作模式COM1:0 CTC 快速PWM 相位修正PWM00 ----------------- 正常的端口操作,不与OC0 相连接--------------------------01 比较匹配时OC0 取反保留保留10 比较匹配时OC0 清零比较匹配时OC0清零,计到TOP时OC0置位升序计数匹配清零OC0;降序计数匹配置位OC011 比较匹配发生时OC0 置位比较匹配OC0置位,计到TOP时OC0清零升序计数匹配置位OC0;降序计数匹配清零OC0CS2:0 时钟选择000 无时钟,T/C 不工作001 clk/1 ( 没有预分频)010 clk/8011 clk/64100 clk/256101 clk/1024110 时钟由T0 引脚输入,下降沿触发111 时钟由T0 引脚输入,上升沿触发TCNT0 | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | // T/C0寄存器OCR0 | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | // 输出比较寄存器(存储比较值) TIMSK | OCIE2 | TOIE2 | TICIE1 | OCIE1A | OCIE1B | TOIE1 | OCIE0 | TOIE0 | // T/C中断屏蔽寄存器OCIE0 T/C0 输出比较匹配中断使能TOIE0 T/C0 溢出中断使能TIFR | OCF2 | TOV2 | ICF1 | OCF1A | OCF1B | TOV1 | OCF0 | TOV0 | // T/C中断标志寄存器OCF0 输出比较标志0TOV0 T/C0 溢出标志SFIOR | ADTS2 | ADTS1 | ADTS0 | -- | ACME | PUD | PSR2 | PSR10 | // 特殊功能I/O寄存器PSR10 T/C1 与T/C0 预分频器复位//***********************// Timer1相关寄存器//**************************//TCCR1A | COM1A1 | COM1A0 | COM1B1 | COM1B0 | FOC1A | FOC1B | WGM11 | WGM10 |//T/C1 控制寄存器ACOM1A1:0 通道A 的比较输出模式COM1B1:0 通道B 的比较输出模式WGM1 3:0 为波形发生模式WGM1[3:0] T/ C1工作模式TOP OCR1x 更新时刻TOV1 置位时刻0000 普通模式0xFFFF 立即更新MAX0001 8位相位修正PWM 0x00FF TOP BOTTOM0010 9位相位修正PWM 0x01FF TOP BOTTOM0011 10位相位修正PWM 0x03FF TOP BOTTOM0100 CTC OCR1A 立即更新MAX0101 8位快速PWM 0x00FF TOP TOP0110 9位快速PWM 0x01FF TOP TOP0111 10位快速PWM 0x03FF TOP TOP1000 相位与频率修正PWM ICR1 BOTTOM BOTTOM1001 相位与频率修正PWM OCR1A BOTTOM BOTTOM1010 相位修正PWM ICR1 TOP BOTTOM1011 相位修正PWM OCR1A TOP BOTTOM1100 CTC ICR1 立即更新MAX1101 保留–––1110 快速PWM ICR1 TOP TOP1111 快速PWM OCR1A TOP TOP COM1A1:0/COM1B1:0为某一模式下工作方式的选择CTC模式COM1A1:0/COM1B1:0 说明00 普通端口操作,非OC1A/OC1B 功能01 比较匹配时OC1A/OC1B 电平取反10 比较匹配时清零OC1A/OC1B( 输出低电平)11 比较匹配时置位OC1A/OC1B ( 输出高电平)快速PWMCOM1A(B)1:0 说明00 普通端口操作,非OC1A/OC1B 功能01 WGM13:0=15:匹配时OC1A 取反,OC1B不占用物理引脚.WGM13:0为其它值时为普通端口操作,非OC1A/OC1B功能10 比较匹配时清零OC1A/OC1B,OC1A/OC1B在TOP 时置位11 比较匹配时置位OC1A/OC1B,OC1A/OC1B在TOP 时清零相位修正及相频修正PWM 模式COMA(B)1:0 说明00 普通端口操作,非OC1A/OC1B 功能01 WGM13:0=9或14: 比较匹配OC1A取反,OC1B不占用物理引脚.WGM13:0为其它值时为普通端口操作,非OC1A/OC1B功能10 升序记数比较匹配清零OC1A/OC1B,降序记数比较匹配置位OC1A/OC1B11 升序记数比较匹配置位OC1A/OC1B,降序记数比较匹配清零OC1A/OC1BFOC1A 通道A 强制输出比较FOC1B 通道B 强制输出比较FOC1A/FOC1B只有当WGM13:0指定为非PWM模式时被激活TCCR1B | ICNC1 | ICES1 | –| WGM13 | WGM12 | CS12 | CS11 | CS10 | // T/C1 控制寄存器BICNC1 输入捕捉噪声抑制器ICES1 输入捕捉触发沿选择0 下降沿触发1 上升沿触发WGM13:2 波形发生模式见TCCR1A 寄存器中的描述CS12:0 时钟选择000 无时钟源(T/C停止工作)001 clk(无预分频)010 clk/8011 clk/64100 clk/256101 clk/1024110 外部T1 引脚,下降沿驱动111 外部T1 引脚,上升沿驱动TCNT1H | Bit15 | Bit14 | Bit13 | Bit12 | Bit11 | Bit10 | Bit9 | Bit8 | // T/C1 技术寄存器TCNT1L | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |OCR1AH | Bit15 | Bit14 | Bit13 | Bit12 | Bit11 | Bit10 | Bit9 | Bit8 | // 输出比较寄存器1AOCR1AL | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |OCR1BH | Bit15 | Bit14 | Bit13 | Bit12 | Bit11 | Bit10 | Bit9 | Bit8 | // 输出比较寄存器1BOCR1BL | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |ICR1H | Bit15 | Bit14 | Bit13 | Bit12 | Bit11 | Bit10 | Bit9 | Bit8 | // 输入捕捉寄存器1ICR1L | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |TIMSK | OCIE2 | TOIE2 | TICIE1 | OCIE1A | OCIE1B | TOIE1 | OCIE0 | TOIE0 | //T/C中断屏蔽寄存器TICIE1 T/C1 输入捕捉中断使能OCIE1A 输出比较A 匹配中断使能OCIE1B T/C1 输出比较B 匹配中断使能TOIE1 T/C1 溢出中断使能TIFR | OCF2 | TOV2 | ICF1 | OCF1A | OCF1B | TOV1 | OCF0 | TOV0 | //T/C中断标志寄存器ICF1 T/C1 输入捕捉标志位OCF1A T/C1 输出比较A 匹配标志位OCF1B T/C1 输出比较B 匹配标志位TOV1 T/C1 溢出标志SFIOR | ADTS2 | ADTS1 | ADTS0 | -- | ACME | PUD | PSR2 | PSR10 | // 特殊功能I/O寄存器PSR10 T/C1 与T/C0 预分频器复位//***********************// Timer2相关寄存器//**************************//TCCR2 | FOC2 | WGM20 | COM21 | COM20 | WGM21 | CS22 | CS21 | CS20 |FOC2 强制输出比较WGM2[1:0] 波形产生模式WGM2[1:0] T/C工作模式TOP OCR2的更新时间TOV2的职位时刻00 普通0xFF 立即更新MAX01 相位修正PWM 0xFF TOP BOTTOM10 CTC OCR2 立即更新MAX11 快速PWM 0xFF TOP MAXCOM2[1:0 ] 比较匹配输出模式CTC模式COM21:0 说明00 正常的端口操作,不与OC0 相连接01 比较匹配发生时OC0 取反10 比较匹配发生时OC0 清零11 比较匹配发生时OC0 置位快速PWM 模式COM21:0 说明00 正常的端口操作,不与OC0 相连接01 保留10 比较匹配发生时OC0 清零,计数到TOP 时OC0 置位11 比较匹配发生时OC0 置位,计数到TOP 时OC0 清零相位修正PWMCOM21:0 说明00 正常的端口操作,不与OC2 相连接01 保留10 在升序计数时发生比较匹配将清零OC2 ;降序计数时发生比较匹配将置位OC211 在升序计数时发生比较匹配将置位OC2 ;降序计数时发生比较匹配将清零OC2CS2 2:0 时钟选择000 无时钟,T/C不工作001 clk(t2s)(无预分频)010 clk(t2s)/8011 clk(t2s)/32100 clk(t2s)/64101 clk(t2s)/128110 clk(t2s)/256111 clk(t2s)/1024TCNT2 | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | // 定时器/ 计数器寄存器OCR2 | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | // 输出比较寄存器ASSR | -- | -- | -- | -- | AS2 | TCN2UB | OCR2UB | TCR2UB | // 异步状态寄存器AS2 异步T/C2AS2为"0”时T/C2由I/O时钟clkI/O驱动;AS2为"1”时T/C2由连接到TOSC1引脚的晶体振荡器驱动TCN2UB T/C2 更新中OCR2UB 输出比较寄存器2 更新中TCR2UB T/C2 控制寄存器更新中TIMSK | OCIE2 | TOIE2 | TICIE1 | OCIE1A | OCIE1B | TOIE1 | OCIE0 | TOIE0 | //T/C2中断屏蔽寄存器OCIE2 T/C2 输出比较匹配中断使能TOIE2 T/C2 溢出中断使能TIFR | OCF2 | TOV2 | ICF1 | OCF1A | OCF1B | TOV1 | OCF0 | TOV0 | //T/C2中断标志寄存器OCF2 输出比较标志2TOV2 T/C2 溢出标志SFIOR | ADTS2 | ADTS1 | ADTS0 | -- | ACME | PUD | PSR2 | PSR1 | // 特殊功能IO寄存器PSR2 预分频复位T/C2//***********************// EEPROM相关寄存器//**************************// EEARH | ----- | ----- | ----- | ----- | ----- | ----- | ----- | EEAR8 | // EEPROM 地址寄存器EEARL | EEAR7 | EEAR6 | EEAR5 | EEAR4 | EEAR3 | EEAR2 | EEAR1 | EEAR0 |EEDR | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | // EEPROM数据寄存器EECR | -- | -- | -- | -- | EERIE | EEMWE | EEWE | EERE | // EEPROM 控制寄存器EERIE 使能EEPROM 准备好中断EEMWE EEPROM 主机写使能EEWE EEPROM 写使能EERE EEPROM 读使能//***********************// TWI相关寄存器//******************************// TWBR | TWBR7 | TWBR6 | TWBR5 | TWBR4 | TWBR3 | TWBR2 | TWBR1 | TWBR0 |// TWI比特率寄存器TWCR | TWINT | TWEA | TWSTA | TWSTO | TWWC | TWEN | ---- | TWIE |// TWI控制寄存器TWINT TWI中断标志TWEA 使能TWI应答TWSTA TWI START状态标志TWSTO TWI STOP状态标志TWWC TWI写碰撞标志TWEN TWI使能TWIE 使能TWI中断TWSR | TWS7 | TWS6 | TWS5 | TWS4 | TWS3 | –| TWPS1 | TWPS0 | // TWI状态寄存器TWS7:3 TWI状态TWPS:0 TWI 预分频位00 101 410 1611 64TWDR | TWD7 | TWD6 | TWD5 | TWD4 | TWD3 | TWD2 | TWD1 | TWD0 |// TWI 数据寄存器TWAR | TWA6 | TWA5 | TWA4 | TWA3 | TWA2 | TWA1 | TWA0 | TWGCE |// TWI 从机地址寄存器TWA6:0 TWI 从机地址寄存器TWGCE 使能TWI广播识别//***************************************************************************************//。

ATmega16单片机中文技术资料

ATmega16单片机中文技术资料一、概述ATmega16是一款高性能、低功耗的8位微控制器,由Atmel公司推出。

它基于AVR增强型RISC结构,拥有丰富的外设资源和灵活的编程特性,广泛应用于工业控制、消费电子、通信设备等领域。

二、主要特性1. 内核:AVR增强型RISC结构,最高工作频率为16MHz。

2. 存储:16KB的程序存储器(Flash)、512B的EEPROM和1KB 的SRAM。

3. 外设接口:32个通用I/O口、8个通道的10位ADC、2个8位定时器/计数器、1个16位定时器/计数器、1个串行通信接口(USART)、1个串行外设接口(SPI)和1个两线接口(TWI)。

4. 工作电压:2.7V至5.5V,支持低功耗模式。

5. 封装:采用TQFP和PDIP封装,便于嵌入式系统设计。

三、引脚功能1. VCC:电源正极,接2.7V至5.5V电压。

2. GND:电源负极,接地。

3. PA0PA7:端口A,具有通用I/O、模拟输入和外围设备功能。

4. PB0PB7:端口B,具有通用I/O、JTAG接口和外围设备功能。

5. PC0PC7:端口C,具有通用I/O、模拟输入和外围设备功能。

6. PD0PD7:端口D,具有通用I/O和外围设备功能。

7. XTAL1/XTAL2:晶振输入/输出,用于外部晶振或陶瓷谐振器。

8. AVCC:模拟电源,为ADC和模拟电路提供电源。

10.RESET:复位输入,低电平有效。

四、编程与开发1. 编程语言:支持C语言和汇编语言编程。

2. 开发工具:可使用Atmel Studio、AVR Studio等集成开发环境进行程序编写、编译和调试。

3. 烧录方式:通过ISP、JTAG、HVPP等接口进行程序烧录。

本文档旨在为您提供ATmega16单片机的中文技术资料,帮助您更好地了解这款微控制器,为您的项目开发提供支持。

后续内容将详细介绍ATmega16的外设功能、编程方法及应用实例。

AVR教程系列一(12):ATmega16 简介(六)

A VR教程系列一(12):ATmega16 简介(六) ATmega16 操纵与状态寄存器MCUCSRAVR 操纵与状态寄存器提供了有关引起AVR复位的复位源的信息。

Bit 4 – JTRF: JTAG 复位标志通过JTAG 指令AVR_RESET 能够使JTAG 复位寄存器置位,并引发MCU 复位,并使JTRF 置位。

上电复位将使其清零,也能够通过写”0” 来清除。

Bit 3 – WDRF: 看门狗复位标志看门狗复位发生时置位。

上电复位将使其清零,也能够通过写”0” 来清除。

Bit 2 – BORF: 掉电检测复位标志掉电检测复位发生时置位。

上电复位将使其清零,也能够通过写”0” 来清除。

Bit 1 – EXTRF: 外部复位标志外部复位发生时置位。

上电复位将使其清零,也能够通过写”0” 来清除。

Bit 0 – PORF: 上电复位标志上电复位发生时置位。

只能通过写”0” 来清除。

为了使用这些复位标志来识别复位条件,用户应该尽早读取此寄存器的数据,然后将其复位。

假如在其他复位发生之前将此寄存器复位,则后续复位源能够通过检查复位标志来熟悉。

ATmega16 基准电压使能信号与启动时间ATmega16 具有片内能隙基准源,用于掉电检测,或者者是作为模拟比较器或者ADC的输入。

ADC 的2.56V 基准电压由此片内能隙基准源产生。

电压基准的启动时间可能影响其工作方式。

启动时间列于Table 16。

为了降低功耗,能够操纵基准源仅在如下情况打开:1. BOD 使能 ( 熔丝位BODEN 被编程)2. 能隙基准源连接到模拟比较器(ACSR 寄存器的ACBG 置位)3. ADC 使能因此,当BOD 被禁止时,置位ACBG 或者使能ADC 后要启动基准源。

为了降低掉电模式的功耗,用户能够禁止上述三种条件,并在进入掉电模式之前关闭基准源。

ATmega16 看门狗定时器看门狗定时器由独立的1 Mhz 片内振荡器驱动。

ATMEGA16单片机数码管学习板资料

{ horse(j); DelayMS(10);//延时时间约 10MS } for(j=9;j!=0;j--) { horse(j); DelayMS(10); } DelayMS(50); PORTB=0X00; PORTA=Table[0];//显示 0; PORTC=0x0F; DelayMS(100); PORTA=Table[1];//显示 1; PORTC=0x0F; DelayMS(100); PORTA=Table[2];//显示 2; PORTC=0x0F; DelayMS(100); PORTA=Table[3];//显示 3; PORTC=0x0F; DelayMS(100); PORTA=Table[4];//显示 4; PORTC=0x0F; DelayMS(100); PORTA=Table[5];//显示 5; PORTC=0x0F; DelayMS(100); PORTA=Table[6];//显示 6; PORTC=0x0F; DelayMS(100); PORTA=Table[7];//显示 7; PORTC=0x0F; DelayMS(100); PORTA=Table[8];//显示 8; PORTC=0x0F; DelayMS(100); PORTA=Table[9];//显示 9; PORTC=0x0F; DelayMS(100); while(1) { Key_Process();//按键扫描

ATmega16/ ATmega16L 在 1 MHz, 3V, 25°C 时的功耗 正常模式 : 1.1 mA 空闲模式 : 0.35 mA

掉电模式 : < 1 µA

二、功能特性描述

三、板子的功能特点

简要说明: 一、尺寸:83mmX77mm 二、主要芯片:AVR 单片机 三、工作电压:直流 4~6 伏 四、单片机标准十针下载接口。(可使用并口下载线和 USB 下载线下载) 五、特点:1、具有电源指示。 2、所以 I/O 口以引出。 3、四位数码管显示、四位按键输入、八位 LED 发光二极管显示。 4、标准的 7.3728M 晶振。 5、具有上电复位和手动复位。 6、支持 ATMEGAXX 系列单片机 六、有详细使用说明书 七、提供相关软件 八、提供例程及其学习资料

ATmega16寄存器

ATmega16寄存器状态寄存器——SREGI:全局中断触发禁⽌位,为中断总控制开关。

T:通⽤标志位,⽤户⾃定义。

H:半进位标志位。

S:符号标志位。

V:溢出标志位。

N:负数标志位。

Z:零标志位。

C:进/借位标志位。

通⽤中断控制寄存器——GICRINT1:外部中断1使能。

INT0:外部中断0使能。

INT2:外部中断2使能。

IVSEL:中断向量表选择。

当IVSEL=0时,中断向量区的位置定义在FLASH的开始处;当IVSEL=1时,定义在引导程序载⼊区的起始处。

IVCE:中断向量表转移允许位。

必须在IVCE位被写⼊1后的4个时钟周期内,修改IVSEL。

4个时钟周期后,或IVSEL位写⼊后,IVCE位由硬件⾃动清零。

OCIE2:T/C2输出⽐较匹配中断使能位。

TOIE2:T/C2溢出中断使能位。

TICIE1:T/C1输⼊捕获中断使能位。

OCIE1A:T/C1输出⽐较A中断使能位。

OCIE1B:T/C1输出⽐较B匹配中断使能位;TOIE1:T/C1溢出中断使能位。

OCIE0:T/C0输出⽐较中断使能位。

TOIE0:T/C0溢出中断使能位。

TIFR寄存器中的各个中断标志是与TIMSK中的使能位⼀⼀对应。

当SPMIE位被置位,若状态寄存器中的I位也被置位时,SPM完成中断即被使能。

只要SPMCSR寄存器中的SPMEN位被清零(程序存储器操作完成),SPM中断服务将被执⾏(避免轮询占⽤较多机时)。

RWWSB:RWW区忙标志当开始对RWW区进⾏⾃编程(页擦除或页写⼊)操作时,RWWSB位将被硬件置位,RWWSB ⼀旦被置位,对RWW区的读操作将被禁⽌。

在⾃编程操作完成后,向RWWSRE位写⼊1,会将RWWSB位清除。

此外,如果开始⼀个页读取操作,也会将RWWSB位清零。

RWWSRE:读RWW区允许当启动对RWW区⾃我编程(页擦除或页写⼊)操作时,RWWSB位被硬件置1,禁⽌对RWW区的读操作。

在⾃我编程操作完成后(SPMEN=0),同时将RWWSRE位和SPMEN 位置为1,在其后的4个时钟周期内的SPM指令将使RWW区重新开放。

atmega16中文资料.0003

154

ATmega16(L)

2466G–AVR–10/03

ATmega16(L)

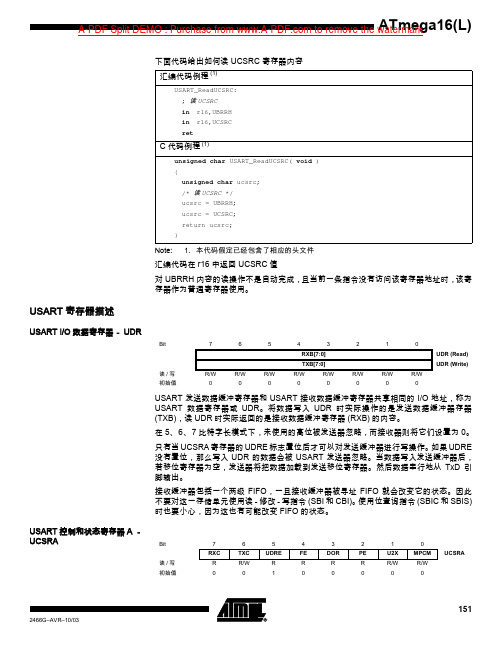

USART 波特率寄存器- UBRRL 和 UBRRH

UCSRC寄存器与UBRRH寄存器共用相同的I/O地址。 对该寄存器的访问, 请参见P151“访 问 UBRRH/ UCSRC 寄存器 ” 。 • Bit 15 – URSEL: 寄存器选择 通过该位选择访问 UCSRC 寄存器或 UBRRH 寄存器。当读 UBRRH 时,该位为 0 ;当 写 UBRRH 时, URSEL 为 0。 • Bit 14:12 – 保留位 这些位是为以后的使用而保留的。为了与以后的器件兼容,写 UBRRH 时将这些位清零。 • Bit 11:0 – UBRR11:0: USART 波特率寄存器 这个 12 位的寄存器包含了 USART 的波特率信息。其中 UBRRH 包含了 USART 波特率 高 4 位, UBRRL 包含了低 8 位。波特率的改变将造成正在进行的数据传输受到破坏。写 UBRRL 将立即更新波特率分频器。

ATmega16(L) A-PDF Split DEMO : Purchase from to remove the watermark

下面代码给出如何读 UCSRC 寄存器内容 汇编代码例程 (1)

USART_ReadUCSRC: ; 读 UCSRC in in ret r16,UBRRH r16,UCSRC

Bit 读/写 初始值

7 RXCIE R/W 0

6 TXCIE R/W 0

5 UDRIE R/W 0

AVR教程系列一(10):ATmega16 简介(9)

ATmega16 简介〔四〕ATmega16 时钟系统及其分布时钟系统及其分布Figure 11为AVR的主要时钟系统及其分布。

这些时钟并不需要同时工作。

为了降低功耗,可以通过使用不同的睡眠模式来禁止无需工作的模块的时钟。

时钟系统详见Figure 11。

CPU 时钟- clkCPUCPU时钟与操作AVR内核的子系统相连,如通用存放器文件、状态存放器及保留仓库指针的数据存储器。

终止CPU 时钟将使内核遏制工作和计算。

I/O 时钟- clkI/OI/O时钟用于主要的I/O 模块,如按时器/ 计数器、SPI 和USART。

I/O 时钟还用于外部中断模块。

要注意的是有些外部中断由异步逻辑检测,因此即使I/O 时钟遏制了这些中断仍然可以得到监控。

此外, USI 模块的起始条件检测在没有clkI/O 的情况下也是异步实现的,使得这个功能在任何睡眠模式下都可以正常工作。

Flash 时钟- clkFLASHFlash 时钟控制Flash 接口的操作。

此时钟通常与CPU 时钟同时挂起或激活。

异步按时器时钟- clkASY异步按时器时钟允许异步按时器/ 计数器与LCD 控制器直接由外部32 kHz 时钟晶体驱动。

使得此按时器/ 计数器即使在睡眠模式下仍然可以为系统提供一个实不时钟。

ADC 时钟- clkADCADC具有专门的时钟。

这样可以在ADC工作的时候遏制CPU和I/O时钟以降低数字电路产生的噪声,从而提高ADC 转换精度。

ATmega16 时钟源ATmega16芯片有如下几种通过Flash熔丝位进行选择的时钟源。

时钟输入到AVR时钟发生器,再分配到相应的模块。

不同的时钟选项将在后续局部进行介绍。

当CPU 自掉电模式或省电模式唤醒之后,被选择的时钟源用来为启动过程按时,包管振荡器在开始执行指令之前进入不变状态。

当CPU从复位开始工作时,还有额外的延迟时间以包管在MCU 开始正常工作之前电源达到不变电平。

这个启动时间的按时由看门狗振荡器完成。

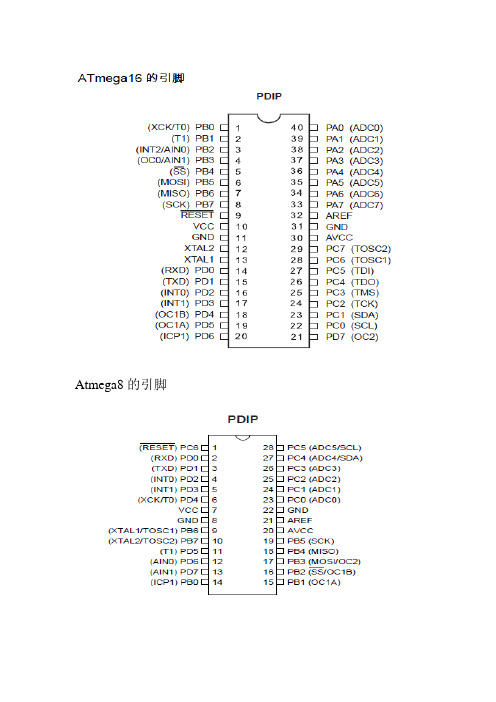

Atmega8&16引脚图与中文资料

Atmega8的引脚ATmega8中文资料ATmega8 是ATMEL公司在2002年第一季度推出的一款新型AVR高档单片机。

在AVR家族中,ATmega8是一种非常特殊的单片机,它的芯片内部集成了较大容量的存储器和丰富强大的硬件接口电路,具备AVR高档单片机MEG E系列的全部性能和特点。

但由于采用了小引脚封装(为DIP 28和TQFP/ML F32),所以其价格仅与低档单片机相当,再加上AVR单片机的系统内可编程特性,使得无需购买昂贵的仿真器和编程器也可进行单片机嵌入式系统的设计和开发,同时也为单片机的初学者提供了非常方便和简捷的学习开发环境。

ATmega8的这些特点,使其成为一款具有极高性能价格比的单片机,深受广大单片机用户的喜爱,在产品应用市场上极具竞争力,被很多家用电器厂商和仪器仪表行业看中,从而使ATmega8迅速进入大批量的应用领域。

ATmega系列单片机属于AVR中的高档产品,它承袭了AT90所具有的特点,并在AT90(如AT9058515、AT9058535)的基础上,增加了更多的接口功能,而且在省电性能。

稳定性、抗干扰性以及灵活性方面考虑得更加周全和完善。

ATmega8 是一款采用低功耗CMOS工艺生产的基于AVR RISC结构的8位单片机。

AVR单片机的核心是将32个工作寄存器和丰富的指令集联结在一起,所有的工作寄存器都与ALU(算术逻辑单元)直接相连,实现了在一个时钟周期内执行的一条指令同时访问(读写)两个独立寄存器的操作。

这种结构提高了代码效率,使得大部分指令的执行时间仅为一个时钟周期。

因此,ATmega8可以达到接近1MIPS/MHz的性能,运行速度比普通CISC单片机高出10倍。

ATmega8的主要性能如下:*高性能、低功耗的8位AVR微控制器,先进的RISC精简指令集结构130条功能强大的指令,大多数为单时钟周期指令32个8位通用工作寄存器工作在16MHz时,具有16MIPS的性能片内集成硬件乘法器(执行速度为2个时钟周期)*片内集成了较大容量的非易失性程序和数据存储器以及工作存储器8K字节的Flash程序存储器,擦写次数:>10000次支持可在线编程(ISP)、可在应用自编程(IAP)带有独立加密位的可选BOOT区,可通过BOOT区内的引导程序区(用户自己写入)来实现IAP编程。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。