ST2302中文资料

ST2301中文资料

-2.8ADESCRIPTIONThe ST2301 is the P-Channel logic enhancement mode power field effect transistor are produced using high cell density, DMOS trench technology.This high density process is especially tailored to minimize on-state resistance.These devices are particularly suited for low voltage application such as cellular phone and notebook computer power management and other batter powered circuits, and low in-line power loss are needed in a very small outine surface mount package.PIN CONFIGURATION SOT-23-3L1.Gate2.Source3.DrainS: Subcontractor Y: Year Code A: Process CodeFEATUREz -20V/-2.8A, R DS(ON) = 120m-ohm@VGS = -4.5Vz -20V/-2.0A, R DS(ON) = 170m-ohm@VGS = -2.5Vz Super high density cell design forextremely low R DS(ON)z Exceptional on-resistance and maximumDC current capabilityz SOT-23-3L package design-2.8AABSOULTE MAXIMUM RATINGS (Ta = 25J Unless otherwise noted )Parameter Symbol Typical Unit Drain-Source Voltage V DSS -20 V Gate-Source VoltageV GSS +12V Continuous Drain Current (TJ=150J ) T A =25¢JT A =70J I D-2.5 -1.5A Pulsed Drain CurrentI DM -10 A Continuous Source Current (Diode Conduction) I S -1.6 A Power DissipationT A =25¢J T A =70JP D 1.250.8W Operation Junction Temperature T J 150 J Storgae Temperature RangeT STG -55/150 J Thermal Resistance-Junction to AmbientR cJA 120J /W-2.5AELECTRICAL CHARACTERISTICS ( Ta = 25J Unless otherwise noted )Parameter Symbol Condition Min Typ Max UnitStaticDrain-Source Breakdown Voltage V (BR)DSS V GS =0V,I D =-250uA -20VGate Threshold Voltage V GS(th) V DS =V GS ,I D =-250uA -0.45 -1.5VGate Leakage CurrentI GSS V DS =0V,V GS =+8V +100nAV DS =-30V,V GS =0V -1Zero Gate Voltage Drain CurrentI DSS V DS =-30V,V GS =0V T J =55J-10uAOn-State Drain Current I D(on) V DS -5V,V GS =-4.5V V DS -5V,V GS =-2.5V -6 -3ADrain-source On-Resistance R DS(on)V GS =-4.5V,I D =-2.8AV GS =-2.5V,I D =-2.0A0.09 0.1450.120.17Forward Transconductance g fsV DS =-5V,I D =-2.8V 6.5 S Diode Forward Voltage V SD I S =-1.6A,V GS =0V -0.8 -1.2VDynamicTotal Gate Charge Qg 5.8 10 Gate-Source Charge Qgs 0.85Gate-Drain Charge Qgd V DS =-6V,V GS =-4.5VI D -2.8A 1.7nC Input Capacitance Ciss 415Output CapacitanceCoss 223Reverse Transfer Capacitance CrssV DS =-6V,V GS =0VF=1MHz 23pF 13 25Turn-On Timet d(on) t r 36 60 42 70 Turn-Off Timet d(off) t fV DD =-6V,R L =6 I D =-1A,V GEN =-4.5VR G =634 60nS-2.5ASOT-23-3L PACKAGE OUTLINE-2.5ATYPICAL CHARACTERICTICS (25J Unless noted)-2.5ATYPICAL CHARACTERICTICS (25J Unless noted)。

常用的功率场效应管(5V逻辑电平驱动)(贴片封装)

常用的功率场效应管( 5V逻辑电平驱动)(贴片封装) 在由单片机、数字集成块等组成的电路中,当被控制电路部分也用5V电源供电时,我们选用的功率场效应管就要求其阀值电压不超过3V,以便由5V的逻辑电平直接驱动它们。

型号生产公司封装沟道主要特性参数备注沟道 20V/7A/24mΩ双管NAO8822 AOS TSSOP-8APM4953 ANPEC茂达 SO-8 P 沟道 -30V/-4.9A/80mΩ双管沟道 30V/52A/20mΩCEB6030L CET华瑞 TO-263 N沟道 30V/60A/15mΩCEB6031L CET华瑞 TO-263 N沟道 30V/25A/40mΩCEB603AL CET华瑞 TO-263 NFDS4953 FAIRCHILD沟道 -30V/-5A/95mΩ双管SO-8 PTO-252 N沟道 30V/67A/10mΩFDD6644 FAIRCHILDTO-252 N沟道 30V/54A/14mΩFDD6692 FAIRCHILD沟道 30V/51A/0.017ΩFQB60N03L FAIRCHILD TO-263 N沟道 -30V/-5A/80mΩSO-8 PSI9435DY FAIRCHILD沟道 30V/67A/10mΩTO-252 NFDD6644 FAIRCHILDTO-252 N沟道 30V/54A/14mΩFDD6692 FAIRCHILD沟道 -30V/-10A/0.02ΩIRF7416 IR SO-8 P沟道 30V/13A/9mΩIRF7823PbF IR SO-8 NIRF7832ZPbF IR SO-8 N沟道 30V/21A/4mΩ沟道 60V/210A/300W/3mΩIRFS3206PbF IR TO-263 NIRFS3306PbF IR TO-263 N沟道 60V/160A/300W/4mΩ沟道 25v/50A/12mΩIPD09N03LA Infineon TO-252 N沟道 16V/6A/20mΩ双管NNK8810 NANKERTSSOP-8沟道 20V/10A/24mΩ双管PMWD20XN PHILIPS SOT530 N沟道 55V/58A/20mΩPHB60N06LT PHILIPS SOT-404 NPHB66NQ03LT PHILIPS SOT-404 N 沟道 25V/66A/16mΩPHD66NQ03LT PHILIPS SOT-428 N 沟道 25V/66A/16mΩ沟道 -20V/-2.8A/120mΩSOT-23-3L PST2301 STANSON沟道 20V/2.8A/80mΩSOT-23-3L NST2302 STANSON沟道 -30V/-2.0A/180mΩSOT-23-3L PST2303 STANSONSOT-23-3L N沟道 30V/2.0A/105mΩST2304 STANSON沟道 -10V/-3.5A/50mΩSOT-23-3L PST2305 STANSONSOT-23-3L N沟道 30V/2.8A/95mΩST2306 STANSONSOT-23-3L P沟道 -30V/-2.5A/115mΩST3403 STANSONSUD30N03-30 VISHAY TO-252 N沟道 30V/30A/0.045ΩSTB60N03L-10 ST TO-263 N 沟道 30V/60A/10mΩ沟道 30V/60A/9mΩSTD60NH03L ST TO-252 N。

AM2302中文资料

数字温湿度传感器AM2302数字温湿度传感器AM2302小体积AM2302►相对湿度和温度测量►全部校准,数字输出►卓越的长期稳定性►无需额外部件►超长的信号传输距离►超低能耗►4 引脚安装►完全互换AM2302产品概述AM2302数字温湿度传感器是一款含有已校准数字信号输出的温湿度复合传感器。

它应用专用的数字模块采集技术和温湿度传感技术,确保产品具有极高的可靠性与卓越的长期稳定性。

传感器包括一个电容式感湿元件和一个NTC测温元件,并与一个高性能8位单片机相连接。

因此该产品具有品质卓越、超快响应、抗干扰能力强、性价比极高等优点。

每个AM2302传感器都在极为精确的湿度校验室中进行校准。

校准系数以程序的形式储存在OTP内存中,传感器内部在检测信号的处理过程中要调用这些校准系数。

单线制串行接口,使系统集成变得简易快捷。

超小的体积、极低的功耗,信号传输距离可达20米以上,使其成为各类应用甚至最为苛刻的应用场合的最佳选则。

产品为 4 针单排引脚封装。

连接方便,特殊封装形式可根据用户需求而提供。

应用领域►暖通空调►测试及检测设备►汽车►数据记录器►消费品►自动控制►气象站►家电►湿度调节器►医疗3、接口说明建议连接线长度短于20米时用5K上拉电阻,大于20米时根据实际情况使用合适的上拉电阻AM2302的接线图如下图所示。

3、电源引脚AM2302的供电电压为3.3-6V。

传感器上电后,要等待1s 以越过不稳定状态在此期间无需发送任何指令。

电源引脚(VDD,GND)之间可增加一个100nF 的电容,用以去耦滤波。

4、单总线接口DATA 用于微处理器与AM2302之间的通讯和同步,采用单总线数据格式,一次通讯时间5ms左右,具体格式在下面说明,当前数据传输为40bit,高位先出。

数据格式: 40bit数据=16bit湿度数据+16bit温度数据+8bit校验和例子:接收40bit数据如下:0000 0010 1000 1100 0000 0001 0101 1111 1110 1110湿度数据温度数据校验和湿度高8位+湿度低8位+温度高8位+温度低8位=的末8位=校验和例如:0000 0010+1000 1100+0000 0001+0101 1111=1110 1110湿度=65.2%RH 温度=35.1℃当温度低于0℃时温度数据的最高位置1。

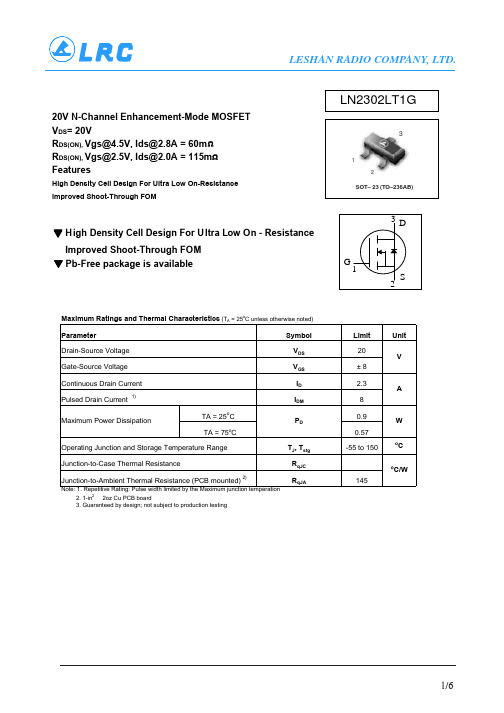

LN2302LT1G中文资料

Size 8 mm 12mm 16mm 24 mm

A Max

330mm (12.992’’) 330mm (12.992’’) 360mm (14.173’’) 360mm (14.173’’)

G

8.4mm+1.5mm, -0.0 (.33’’+.059’’, -0.00) 12.4mm+2.0mm, -0.0 (.49 ’’+ .079’’, -0.00) 16.4mm+2.0mm, -0.0 (.646’’+.078’’, -0.00) 24.4mm+2.0mm, -0.0 (.961’’+.070’’, -0.00)

▼ Pb-Free package is available

LN2302LT1G

3

1 2

SOT– 23 (TO–236AB)

3D

G 1 S 2

Maximum Ratings and Thermal Characteristics (TA = 25oC unless otherwise noted)

Parameter

VGS = 0V, ID = -10uA VGS = 4.5V, ID = 2.8A VGS = 2.5V, ID = 2.0A VDS =VGS, ID = 250uA VDS = 9.6V, VGS = 0V VGS = ±8V, VDS = 0V

VDS = 5V, ID = 4.0A

VDS = 6V, ID = 2.8A VGS = 4.5V

0.0177 0.0236 0.45

0.60

0.037 0.95

0.035 0.9

0.037 0.95

0.079 2.0

SI2302-TP;中文规格书,Datasheet资料

Revision: A

/

3 of 5

2011/01/01

VGS, Gate to Source Voltage (V) ID, Drain Current (A)

VTH, Normalized Gate-Source Threshold Voltage

RDS(ON), Normalized RDS(ON), On-Resistance(Ohms)

IS, Source-drain current (A)

ID, Drain Current (A)

SI2302

10 25 C

Maximum Ratings @ 25OC Unless Otherwise Specified

Symbol VDS ID IDM VGS

PD R©JA

TJ

TSTG

Parameter Drain-source Voltage Drain Current-Continuous Drain Current-Pulsed a Gate-source Voltage

MCC

TM

Micro Commercial Components

5 VDS=10V ID=3.6A

4

3

2

1

0

0

2

4

6

Qg, Total Gate Charge (nC)

Figure 7. Gate Charge

VDD

RL VIN

D

VOUT

VGS

RGEN G

S

Figure 9. Switching Test Circuit

LTC2302资料

123026fT YPICAL APPLICATIONF EATURESA PPLICATIONSD ESCRIPTION 1-/2-Channel, 12-Bit ADCsThe L TC ®2302/L TC2306 are low noise, 500ksps, 1-/2-chan-nel, 12-bit ADCs with an SPI/MICROWIRE compatible serial interface. These ADCs include a fully differential sample-and-hold circuit to reduce common mode noise. The internal conversion clock allows the external serial output data clock (SCK) to operate at any frequency up to 40MHz.The L TC2302/L TC2306 operate from a single 5V supply and draw just 2.8mA at a sample rate of 500ksps. The auto-shutdown feature reduces the supply current to 14μA at a sample rate of 1ksps.The L TC2302/L TC2306 are packaged in a tiny 10-pin 3mm × 3mm DFN. The low power consumption and small size make the L TC2302/L TC2306 ideal for battery-operated and portable applications, while the 4-wire SPI compat-ible serial interface makes these ADCs a good match for isolated or remote data acquisition systems.8192 Point FFT , f IN = 1kHz (L TC2306)n12-Bit Resolutionn 500ksps Sampling Rate n Low Noise: SINAD = 72.8dB n Guaranteed No Missing Codes n Single 5V SupplynAuto-Shutdown Scales Supply Current with Sample Raten Low Power: 14mW at 500ksps 70μW at 1ksps 35μW Sleep Moden 1-Channel (L TC2302) and 2-Channel (L TC2306) Versionsn Unipolar or Bipolar Input Ranges (Software Selectable)n Internal Conversion Clockn SPI/MICROWIRE ™ Compatible Serial Interface n Separate Output Supply OV DD(2.7V to 5.25V)n Software Compatible with the L TC2308n 10-Pin (3mm × 3mm) DFN PackagenHigh Speed Data Acquisition n Industrial Process Control n Motor Control n Accelerometer Measurements n Battery-Operated Instrumentsn Isolated and/or Remote Data AcquisitionTYPENUMBER OF INPUT CHANNELS128Int Reference L TC2308Ext ReferenceL TC2302L TC2306L , L T , L TC and L TM are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.CH0 (IN +CH1 (IN –ANALOG INPUTS 0V TO 4.096V UNIPOLAR±2.048V BIPOLAR REFFREQUENCY (kHz)0–40–20020023026 TA01b–60–8050100150250–100–120–50–30–10–70–90–110–130–140M A G N I T U D E (d B )f SMPL = 500kHz SINAD = 72.8dB THD = –88.7dB223026fA BSOLUTE MAXIMUM RATINGS Supply Voltage (V DD , OV DD ) .........................–0.3V to 6V Analog Input Voltage (Note 3) C H0(IN +)-CH1(IN –),REF ..............................(GND – 0.3V) to (V DD + 0.3V)Digital Input Voltage (Note 3) .............................(GND – 0.3V) to (V DD + 0.3V)(Notes 1, 2)LEAD FREE FINISH TAPE AND REEL PART MARKING*PACKAGE DESCRIPTIONTEMPERATURE RANGE L TC2302CDD#PBF L TC2302CDD#TRPBF LDGV 10-Lead (3mm × 3mm) Plastic DFN 0°C to 70°C L TC2302IDD#PBF L TC2302IDD#TRPBF LDGV 10-Lead (3mm × 3mm) Plastic DFN –40°C to 85°C L TC2306CDD#PBF L TC2306CDD#TRPBF LDGW 10-Lead (3mm × 3mm) Plastic DFN 0°C to 70°C L TC2306IDD#PBFL TC2306IDD#TRPBFLDGW10-Lead (3mm × 3mm) Plastic DFN–40°C to 85°CConsult L TC Marketing for parts specifi ed with wider operating temperature ranges. *The temperature grade is identifi ed by a label on the shipping container .Consult L TC Marketing for information on non-standard lead based fi nish parts.For more information on lead free part marking, go to: http://www.linear .com/leadfree/ For more information on tape and reel specifi cations, go to: http://www.linear .com/tapeandreel/ORDER INFORMATIONTOP VIEW11L TC2302DD PACKAGE10-LEAD (3mm s 3mm) PLASTIC DFN10967845321OV DD SCK SDI GND V REFSDO CONVST V DD IN +IN –T JMAX = 150°C, θJA = 43°C/WEXPOSED PAD (PIN 11) IS GND, MUST BE SOLDERED TO PCBTOP VIEW11L TC2306DD PACKAGE10-LEAD (3mm s 3mm) PLASTIC DFN10967845321OV DD SCK SDI GND V REFSDO CONVST V DD CH0CH1T JMAX = 150°C, θJA = 43°C/WEXPOSED PAD (PIN 11) IS GND, MUST BE SOLDERED TO PCBP IN CONFIGURATION Digital Output Voltage ...(GND – 0.3V) to (OV DD + 0.3V)Power Dissipation ...............................................500mW Operating Temperature RangeL TC2302C/L TC2306C ...............................0°C to 70°C L TC2302I/L TC2306I ..............................–40°C to 85°C Storage Temperature Range ...................–65°C to 150°C323026fCONVERTER AND MULTIPLEXER CHARACTERISTICS SYMBOL PARAMETERCONDITIONS MIN TYP MAX UNITSV IN +Absolute Input Range (CH0, CH1, IN +)(Note 9)l –0.05V DD V V IN –Absolute Input Range (CH0, CH1, IN –)Unipolar (Note 9)Bipolar (Note 9)l l –0.05–0.05V DD /2V DDV V V IN + – V IN –Input Differential Voltage Range V IN = V IN + – V IN – (Unipolar)V IN = V IN + – V IN – (Bipolar)l l 0 to V REF ±V REF /2V VI IN Analog Input Leakage Current l±1μA C IN Analog Input CapacitanceSample Mode Hold Mode555pF pF CMRRInput Common Mode Rejection Ratio70dBThe l denotes the specifi cations which apply over the full operating temperature range, otherwise specifi cations are at T A = 25°C. (Notes 4, 5)PARAMETERCONDITIONSMIN TYP MAX UNITS Resolution (No Missing Codes)l12Bits Integral Linearity Error (Note 6)l ±0.3±1LSB Differential Linearity Error l±0.25±1LSB Bipolar Zero Error (Note 7)l±1±6LSB Bipolar Zero Error Drift 0.002LSB/°C Unipolar Zero Error (Note 7)l±1±6LSB Unipolar Zero Error Drift0.002LSB/°C Unipolar Zero Error Match (L TC2306)±0.3±3LSB Bipolar Full-Scale Error (Note 8)l ±1.5±8LSB Bipolar Full-Scale Error Drift 0.05LSB/°C Unipolar Full-Scale Error (Note 8)l±1.2±6LSB Unipolar Full-Scale Error Drift0.05LSB/°C Unipolar Full-Scale Error Match (L TC2306)±0.3±3LSBANALOG INPUT The l denotes the specifi cations which apply over the full operating temperature range, otherwisespecifi cations are at T A = 25°C. (Note 4)SYMBOLPARAMETER CONDITIONSMIN TYP MAX UNITSV REF Input Rangel 0.1V DD V I REF Reference Input Current f SMPL = 0ksps, V REF = 4.096Vf SMPL = 500ksps, V REF = 4.096Vl l5023080260μA μA C REFReference Input Capacitance55pFREFERENCE INPUT The l denotes the specifi cations which apply over the full operating temperature range,otherwise specifi cations are at T A = 25°C. (Note 4)423026fSYMBOL PARAMETERCONDITIONS MIN TYP MAX UNITSV IH High Level Input Voltage V DD = 5.25V l 2.4V V IL Low Level Input Voltage V DD = 4.75V l 0.8V I IN High Level Input Current V IN = V DDl±10μA C IN Digital Input Capacitance 5pF V OH High Level Output Voltage OV DD = 4.75V , I OUT = –10μAOV DD = 4.75V , I OUT = –200μA l 44.74V VV OL Low Level Output Voltage OV DD = 4.75V , I OUT = 160μA OV DD = 4.75V , I OUT = 1.6mA l 0.050.4V V I OZ Hi-Z Output Leakage V OUT = 0V to OV DD , CONVST High l±10μA C OZ Hi-Z Output Capacitance CONVST High 15pF I SOURCE Output Source Current V OUT = 0V –10mA I SINKOutput Sink CurrentV OUT = OV DD10mADIGITAL INPUTS AND DIGITAL OUTPUTS The l denotes the specifi cations which apply over thefull operating temperature range, otherwise specifi cations are at T A = 25°C. (Note 4)SYMBOL PARAMETER CONDITIONSMIN TYP MAX UNITSV DD Supply Voltagel 4.755 5.25V OV DD Output Driver Supply Voltage l 2.75.25V I DD Supply CurrentSleep Mode C L = 25pFCONVST = 5V , Conversion Done l l2.873.515mA μA P DPower Dissipation Sleep Mode1435mW μWPOWER REQUIREMENTS The l denotes the specifi cations which apply over the full operating temperaturerange, otherwise specifi cations are at T A = 25°C. (Note 4)SYMBOL PARAMETERCONDITIONS MIN TYP MAX UNITS SINAD Signal-to-(Noise + Distortion) Ratio f IN = 1kHz l 7172.8dB SNR Signal-to-Noise Ratio f IN = 1kHzl 7173.2dBTHD Total Harmonic Distortion f IN = 1kHz, First 5 Harmonics l –88–78dB SFDRSpurious Free Dynamic Range f IN = 1kHz l7989dB Channel-to-Channel Isolation f IN = 1kHz –109dB Full Linear Bandwidth (Note 11)700kHz –3dB Input Linear Bandwidth 25MHz Aperature Delay 13ns T ransient ResponseFull-Scale Step 240nsDYNAMIC ACCURACY The l denotes the specifi cations which apply over the full operating temperature range,otherwise specifi cations are at T A = 25°C. A IN = –1dBFS. (Notes 4, 10)TIMING CHARACTERISTICSThel denotes the specifi cations which apply over the full operating temperature range, otherwise specifi cations are at T A = 25°C. (Note 4)SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS f SMPL(MAX)Maximum Sampling Frequency l500kHz f SCK Shift Clock Frequency l40MHz t WHCONV CONVST High Time(Note 9)l20ns t HD Hold Time SDI After SCK↑l 2.5ns t SUDI Setup Time SDI Stable Before SCK↑l0ns t WHCLK SCK High Time f SCK = f SCK(MAX)l10ns t WLCLK SCK Low Time f SCK = f SCK(MAX)l10ns t WLCONVST CONVST Low Time During Data T ransfer(Note 9)l410ns t HCONVST Hold Time CONVST Low After Last SCK↓(Note 9)l20ns t CONV Conversion Time l 1.3 1.6μs t ACQ Acquisition Time7th SCK↑ to CONVST↑ (Note 9)l240ns t dDO SDO Data Valid After SCK↓C L = 25pF (Note 9)l10.812.5ns t hDO SDO Hold Time SCK↓C L = 25pF l4ns t en SDO Valid After CONVST↓C L = 25pF l1115ns t dis Bus Relinquish Time C L = 25pF l1115ns t r SDO Rise Time C L = 25pF4ns t f SDO Fall Time C L = 25pF4ns t CYC Total Cycle Time2μsNote 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.Note 2: All voltage values are with respect to ground with V DD and OV DD wired together (unless otherwise noted).Note 3: When these pin voltages are taken below ground or above V DD, they will be clamped by internal diodes. These products can handle input currents greater than 100mA below ground or above V DD without latchup. Note 4: V DD = 5V, OV DD = 5V, V REF = 4.096V, f SMPL = 500ksps, unless otherwise specifi ed.Note 5: Linearity, offset and full-scale specifi cations apply for a single-ended analog input with respect to GND for the L TC2306 and IN+ with respect to IN– tied to GND for the L TC2302.Note 6: Integral nonlinearity is defi ned as the deviation of a code from a straight line passing through the actual endpoints of the transfer curve. The deviation is measured from the center of the quantization band.Note 7: Bipolar zero error is the offset voltage measured from –0.5LSB when the output code fl ickers between 0000 0000 0000 and 1111 1111 1111. Unipolar zero error is the offset voltage measured from +0.5LSB when the output code fl ickers between 0000 0000 0000 and 0000 0000 0001.Note 8: Full-scale bipolar error is the worst-case of –FS or +FS untrimmed deviation from ideal fi rst and last code transitions and includes the effect of offset error. Unipolar full-scale error is the deviation of the last code transition from ideal and includes the effect of offset error.Note 9: Guaranteed by design, not subject to test.Note 10: All specifi cations in dB are referred to a full-scale ±2.048V input with a 4.096V reference voltage.Note 11: Full linear bandwidth is defi ned as the full-scale input frequency at which the SINAD degrades to 60dB or 10 bits of accuracy.523026f623026fT YPICAL PERFORMANCE CHARACTERISTICS Integral Nonlinearity vs Output CodeDifferential Nonlinearity vsOutput Code1kHz Sine Wave 8192 Point FFT PlotSNR vs Input FrequencySINAD vs Input FrequencyTHD vs Input FrequencySupply Current vs Sampling FrequencySupply Current vs Temperature(L TC2302) T A = 25°C, V DD = OV DD = 5V , V REF = 4.096V , f SMPL= 500ksps, unless otherwise noted.OUTPUT CODEI N L (L S B )00.250.50409623026 G01–0.25–0.50–1.00102420483072–0.751.000.75OUTPUT CODED N L (L S B )0.250.50409623026 G02–0.25–0.50–1.00102420483072–0.751.000.75FREQUENCY (kHz)0–40–20020023026 G03–60–8050100150250–100–120–50–30–10–70–90–110–130–140M A G N I T U D E (d B )SNR = 73.2dB SINAD = 72.8dBTHD = –89.5dBFREQUENCY (kHz)150S N R (d B )70758010100100023026 G04656055FREQUENCY (kHz)150S I N A D (d B )70758010100100023026 G05656055FREQUENCY (kHz)1–80T HD (d B )–70–6010100100023026 G06–90–85–75–65–95–100SAMPLING FREQUENCY (ksps)12.0S U P P L Y C U RR E N T (m A )2.53.03.510100100023026 G071.51.00.50TEMPERATURE (°C)–502.0SU P P L Y C U R R E N T (m A )2.22.62.83.04.03.40507523026 G082.43.63.83.2–2525100125723026fSleep Current vs TemperatureTYPICAL PERFORMANCE CHARACTERISTICSAnalog Input Leakage Current vs TemperatureOffset Error vs TemperatureFull-Scale Error vs Temperature(L TC2302) T A = 25°C, V DD = OV DD = 5V , V REF = 4.096V , f SMPL = 500ksps, unless otherwise noted.TEMPERATURE (°C)–500S L E E P C U R R E N T (μA )13451070507523026 G092896–2525100125TEMPERATURE (°C)–500I N P U T L E A K A G E C U R R E N T (n A )10030040050010007000507523026 G10200800900600–2525100125TEMPERATURE (°C)–50–1.0–1.5–2.0–2.5O F F S E T E R R O R (L S B )–0.50.51.01.52.50507523026 G1102.0–2525100125TEMPERATURE (°C)–50F U L L -S C A L E E R R O R (L S B )1.52523026 G120–1.0–2550–1.5–2.02.01.00.5–0.575100125823026fT YPICAL PERFORMANCE CHARACTERISTICS Integral Nonlinearity vs Output CodeDifferential Nonlinearity vsOutput Code1kHz Sine Wave 8192 Point FFT PlotSNR vs Input FrequencySINAD vs Input FrequencyTHD vs Input FrequencySupply Current vs Sampling FrequencySupply Current vs Temperature(L TC2306) T A = 25°C, V DD = OV DD = 5V , V REF = 4.096V , f SMPL = 500ksps, unless otherwise noted.OUTPUT CODEI N L (L S B)00.250.50409623026 G13–0.25–0.50–1.00102420483072–0.751.000.75–0.751.000.75M A G N I T U D E (d B )FREQUENCY (kHz)150S N R (d B )70758010100100023026 G16656055FREQUENCY (kHz)150S I N A D (d B )70758010100100023026 G17656055FREQUENCY (kHz)1–80T H D (d B )–70–6010100100023026 G18–90–85–75–65–95–100SAMPLING FREQUENCY (ksps)12.0S U P P L Y C U R R E N T (m A )2.53.03.510100100023026 G191.51.00.5TEMPERATURE (°C)–502.0S U P P L Y C U R R E N T (m A )2.22.62.83.04.03.40507523026 G202.43.63.83.2–2525100125923026fSleep Current vs TemperatureTYPICAL PERFORMANCE CHARACTERISTICSAnalog Input Leakage Current vs TemperatureOffset Error vs TemperatureFull-Scale Error vs Temperature(L TC2306) T A = 25°C, V DD = OV DD = 5V , V REF = 4.096V , f SMPL = 500ksps, unless otherwise noted.TEMPERATURE (°C)–500S L E E P C U R R E N T (μA )13451070507523026 G212896–2525100125TEMPERATURE (°C)–500I N P U T L E A K A G E C U R R E N T (n A )10030040050010007000507523026 G22200800900600–2525100125TEMPERATURE (°C)–50O F F S E T E R R O R (L S B )1.52523026 G230–1.0–2550–1.5–2.02.01.00.5–0.575100125TEMPERATURE (°C)–50F U L L -S C A L E E R R O R (L S B )1.52523026 G240–1.0–2550–1.5–2.02.01.00.5–0.575100125P IN FUNCTIONSL TC2302SDO (Pin 1): Three-State Serial Data Out. SDO outputs the data from the previous conversion. SDO is shifted out serially on the falling edge of each SCK pulse. SDO is enabled by a low level on CONVST.CONVST (Pin 2): Conversion Start. A rising edge at CONVST begins a conversion. For best performance, ensure that CONVST returns low within 40ns after the conversion starts or after the conversion ends.V DD (Pin 3): 5V Supply. The range of V DD is 4.75V to 5.25V. Bypass V DD to GND with a 0.1μF ceramic capacitor and a 10μF tantalum capacitor in parallel.IN+, IN– (Pin 4, Pin 5): Positive (IN+) and Negative (IN–) Differential Analog Inputs.V REF (Pin 6): Reference Input. Connect an external refer-ence at V REF . The range of the external reference is 0.1V to V DD. Bypass to GND with a minimum 10μF tantalum capacitor in parallel with a 0.1μF ceramic capacitor. GND (Pin 7): Ground. All GND pins must be connected to a solid ground plane.SDI (Pin 8): Serial Data Input. The SDI serial bit stream confi gures the ADC and is latched on the rising edge of the fi rst 6 SCK pulses.SCK (Pin 9): Serial Data Clock. SCK synchronizes the serial data transfer. The serial data input at SDI is latched on the rising edge of SCK. The serial data output at SDO transitions on the falling edge of SCK.OV DD (Pin 10): Output Driver Supply. Bypass OV DD to GND with a 0.1μF ceramic capacitor close to the pin. The range of OV DD is 2.7V to 5.25V.Exposed Pad (Pin 11): Exposed Pad Ground. Must be soldered directly to ground plane.L TC2306SDO (Pin 1): Three-State Serial Data Out. SDO outputs the data from the previous conversion. SDO is shifted out serially on the falling edge of each SCK pulse. SDO is enabled by a low level on CONVST.CONVST (Pin 2): Conversion Start. A rising edge at CONVST begins a conversion. For best performance, ensure that CONVST returns low within 40ns after the conversion starts or after the conversion ends.V DD (Pin 3): 5V Supply. The range of V DD is 4.75V to 5.25V. Bypass V DD to GND with a 0.1μF ceramic capacitor and a 10μF tantalum capacitor in parallel.CH0, CH1 (Pin 4, Pin 5): Channel 0 and Channel 1 Analog Inputs. CH0, CH1 can be confi gured as single-ended or differential input channels. See the Analog Input Multi-plexer section.V REF (Pin 6): Reference Input. Connect an external refer-ence at V REF .The range of the external reference is 0.1V to V DD. Bypass to GND with a minimum 10μF tantalum capacitor in parallel with a 0.1μF ceramic capacitor. GND (Pin 7): Ground. All GND pins must be connected to a solid ground plane.SDI (Pin 8): Serial Data Input. The SDI serial bit stream confi gures the ADC and is latched on the rising edge of the fi rst 6 SCK pulses.SCK (Pin 9): Serial Data Clock. SCK synchronizes the serial data transfer. The serial data input at SDI is latched on the rising edge of SCK. The serial data output at SDO transitions on the falling edge of SCK.OV DD (Pin 10): Output Driver Supply. Bypass OV DD to OGND with a 0.1μF ceramic capacitor close to the pin. The range of OV DD is 2.7V to 5.5V.Exposed Pad (Pin 11): Exposed Pad Ground. Must be soldered directly to ground plane.1023026f1123026fB LOCK DIAGRAM TEST CIRCUITSTIMING DIAGRAMSVoltage Waveforms for SDO Delay Times, t dDO and t hDOVoltage Waveforms for t disLoad Circuit for t dis Waveform 1Load Circuit for t dis Waveform 2, t enSDISDO SCK CONVSTCH0 (IN +CH1 (IN –REFV OVVSCKSDOOH OLSDOWAVEFORM 1(SEE NOTE 1)SDOWAVEFORM 2(SEE NOTE 2)CONVST NOTE 1: WAVEFORM 1 IS FOR AN OUTPUT WITH INTERNAL CONDITIONS SUCH THAT THE OUTPUT IS HIGH UNLESS DISABLED BY THE OUTPUT CONTROL NOTE 2: WAVEFORM 2 IS FOR AN OUTPUT WITH INTERNAL CONDITIONS SUCH THAT THE OUTPUT IS LOW UNLESS DISABLED BY THE OUTPUT CONTROL23026 TD021223026fTIMING DIAGRAMSt WLCLK (SCK Low Time)t WHCLK (SCK High Time)t HD (Hold Time SDI After SCK ↑)t SUDI (Setup Time SDI Stable Before SCK ↑)Voltage Waveforms for t enVoltage Waveforms for SDO Rise and Fall Times t r , t fA PPLICATIONS INFORMATIONSCKSDICONVSTSDOOH OLOverviewThe L TC2302/L TC2306 are low noise, 500ksps, 1-/2-chan-nel, 12-bit successive approximation register (SAR) A/D converters. The L TC2306 includes a 2-channel analog input multiplexer (MUX) while the L TC2302 includes an input MUX that allows the polarity of the differential input to be selected. Both ADCs include an SPI-compatible se-rial port for easy data transfers and can operate in either unipolar or bipolar mode. Unipolar mode should be used for single-ended operation with the L TC2306, since single-ended input signals are always referenced to GND. The L TC2302/L TC2306 can be put into a power-down sleep mode during idle periods to save power .Conversions are initiated by a rising edge on the CONVST input. Once a conversion cycle has begun, it cannot be restarted. Between conversions, a 6-bit input word (D IN ) at the SDI input confi gures the MUX and programs vari-ous modes of operation. As the D IN bits are shifted in, data from the previous conversion is shifted out on SDO. After the 6 bits of the D IN word have been shifted in, the ADC begins acquiring the analog input in preparation for the next conversion as the rest of the data is shifted out.The acquire phase requires a minimum time of 240ns for the sample-and-hold capacitors to acquire the analog input signal.During the conversion, the internal 12-bit capacitive charge-redistribution DAC output is sequenced through a successive approximation algorithm by the SAR starting from the most signifi cant bit (MSB) to the least signifi cant bit (LSB). The sampled input is successively compared with binary weighted charges supplied by the capacitive DAC using a differential comparator . At the end of a conver-sion, the DAC output balances the analog input. The SAR contents (a 12-bit data word) that represent the sampled analog input are loaded into 12 output latches that allow the data to be shifted out.Programming the L TC2306 and L TC2302The software compatible L TC2302/L TC2306/L TC2308 fam-ily features a 6-bit D IN word to program various modes of operation. Don’t care bits (X) are ignored. The SDI data bits are loaded on the rising edge of SCK, with the S/D bit loaded on the fi rst rising edge (see Figure 6 in the Timing1323026fA PPLICATIONS INFORMATION Figure 1a. Example MUX Confi gurationsFigure 1b. Changing the MUX Assignment “On the Fly”and Control section). The input data word for the L TC2306 is defi ned as follows:S/D O/SXXUNIXS/D = SINGLE-ENDED/DIFFERENTIAL BIT O/S = ODD/SIGN BIT UNI = UNIPOLAR/BIPOLAR BIT X = DON’ T CAREFor the L TC2302, the input data word is defi ned as:XO/SXXUNIXAnalog Input MultiplexerThe analog input MUX is programmed by the S/D and O/S bits of the D IN word for the L TC2306 and the O/S bit of the D IN word for the L TC2302. Table 1 and Table 2 list MUX confi gurations for all combinations of the confi guration bits. Figure 1a shows several possible MUX confi gurations and Figure 1b shows how the MUX can be reconfi gured from one conversion to the next.Driving the Analog InputsThe analog inputs of the L TC2302/L TC2306 are easy to drive. Each of the analog inputs of the L TC2306 (CH 0 and CH1) can be used as a single-ended input relative to GND or as a differential pair . The analog inputs of theL TC2302 (IN +, IN –) are always configured as a differential pair . Regardless of the MUX confi guration, the “+” and “–” inputs are sampled at the same instant. Any unwanted signal that is common to both inputs will be reduced by the common mode rejection of the sample-and-hold cir-cuit. The inputs draw only one small current spike while2 Single-Ended1 Differential+(–)–(+) 1 Differential+(–)–(+)2nd Conversion1st Conversion+–S/D 0011O/S 0101CH0+–+CH1–++WITH RESPECT TO GNDNOTE: UNIPOLAR MODE SHOULD BE USEDFOR SINGLE-ENDED OPERATION, SINCE INPUT SIGNALS ARE ALWAYS REFERENCED TO GNDTable 1. Channel Configurationfor the L TC2306O/S 01IN ++–IN ––+Table 2. Channel Configuration for the L TC23021423026fA PPLICATIONS INFORMATION Figure 2b. Analog Input Equivalent Circuit for Large Filter CapacitancesFigure 2a. Analog Input Equivalent Circuitcharging the sample-and-hold capacitors during the acquire mode. In conversion mode, the analog inputs draw only a small leakage current. If the source impedance of the driving circuit is low, the ADC inputs can be driven directly. Otherwise, more acquisition time should be allowed for a source with higher impedance.ReferenceA low noise, stable reference is required to ensure full performance. The L T ®1790 and L T6660 are adequate for most applications. The L T6660 is available in 2.5V , 3V , 3.3V and 5V versions, and the L T1790 is available in 1.25V , 2.048V , 2.5V , 3V , 3.3V , 4.096V and 5V versions. The exceptionally low input noise allows the input range to be optimized for the application by changing the reference voltage. The V REF input must be decoupled with a 10μF capacitor in parallel with a 0.1μF capacitor , so verify that the device providing the reference voltage is stable with capacitive loads.If the voltage reference is 5V and can supply 5mA, it can be used for both V REF and V DD . V DD must be connected to a clean analog supply, and a quiet 5V reference voltage makes a convenient supply for this purpose.Input FilteringThe noise and distortion of the input amplifi er and other circuitry must be considered since they will add to the ADC noise and distortion. Therefore, noisy input circuitryshould be fi ltered prior to the analog inputs to minimize noise. A simple 1-pole RC fi lter is suffi cient for many applications.The analog inputs of the L TC2302/L TC2306 can be modeled as a 55pF capacitor (C IN ) in series with a 100Ω resistor (R ON ) as shown in Figure 2a. C IN gets switched to the selected input once during each conversion. Large fi lter RC time constants will slow the settling of the inputs. It is important that the overall RC time constants be short enough to allow the analog inputs to completely settle to 12-bit resolution within the acquisition time (t ACQ ) if DC accuracy is important.When using a fi lter with a large C FIL TER value (e.g., 1μF), the inputs do not completely settle and the capacitive input switching currents are averaged into a net DC current (I DC ). In this case, the analog input can be modeled by an equivalent resistance (R EQ = 1/(f SMPL • C IN )) in series with an ideal voltage source (V REF /2) as shown in Figure 2b. The magnitude of the DC current is then approximately I DC = (V IN – V REF /2)/R EQ , which is roughly proportional to V IN . To prevent large DC drops across the resistorR FIL TER , a filter with a small resistor and large capacitor should be chosen. When running at the minimum cycle time of 2μs, the input current equals 106μA at V IN = 5V , which amounts to a full-scale error of 0.5LSB when using a fi lter resistor (R FIL TER ) of 4.7Ω. Applications requiring lower sample rates can tolerate a larger fi lter resistor for the same amount of full-scale error .V IN23026 F02aV IN23026 F02bA PPLICATIONS INFORMATIONFigure 3a. Optional RC Input Filtering for Single-Ended Input Figure 3b. Optional RC Input Filtering for Differential Inputs Figure 4. 1kHz Sine Wave 8192 Point FFT Plot (L TC2306)Figures 3a and 3b show respective examples of input fi ltering for single-ended and differential inputs. For the single-ended case in Figure 3a, a 50Ω source resistor and a 2000pF capacitor to ground on the input will limit the input bandwidth to 1.6MHz. High quality capacitors and resistors should be used in the RC fi lter since these components can add distortion. NPO and silver mica type dielectric capacitors have excellent linearity. Carbon surface mount resistors can generate distortion from self heating and from damage that may occur during soldering. Metal fi lm surface mount resistors are much less susceptible to both problems.Dynamic PerformanceFFT (fast fourier transform) test techniques are used to test the ADC’s frequency response, distortion and noise at the rated throughput. By applying a low distortion sine wave and analyzing the digital output using an FFT algorithm, the ADC’s spectral content can be examined for frequencies outside the fundamental.Signal-to-Noise and Distortion Ratio (SINAD)The signal-to-noise and distortion ratio (SINAD) is the ratio between the RMS amplitude of the fundamental input frequency to the RMS amplitude of all other frequency components at the A/D output. The output is band-limited to frequencies from above DC and below half the sampling frequency. Figure 4 shows a typical SINAD of 72.8dB with a 500kHz sampling rate and a 1kHz input. A SNR of 73.2dB can be achieved with the L TC2302/L TC2306.Total Harmonic Distortion (THD)Total Harmonic Distortion (THD) is the ratio of the RMS sum of all harmonics of the input signal to the fundamental itself. The out-of-band harmonics alias into the frequency band between DC and half the sampling frequency(f SMPL/2). THD is expressed as:THDV V V VVN=+++2022324221log...where V1 is the RMS amplitude of the fundamental fre-quency and V2 through V N are the amplitudes of the second through Nth harmonics.40206080002050307090103040MAGNITUDE(dB)SNR = 73.2dBSINAD = 72.8dBTHD = –88.7dB1523026f。

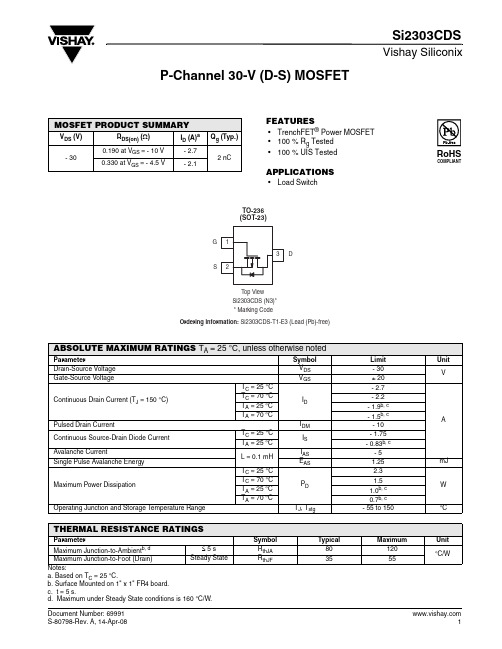

SI2303CDS中文资料

Vishay SiliconixSi2303CDSP-Channel 30-V (D-S) MOSFETFEATURES•TrenchFET ® Power MOSFET •100 % R g Tested •100 % UIS TestedAPPLICATIONS•Load SwitchMOSFET PRODUCT SUMMARYV DS (V)R DS(on) (Ω)I D (A)aQ g (Typ.)- 300.190 at V GS = - 10 V - 2.7 2 nC0.330 at V GS = - 4.5 V- 2.1Notes:a. Based on T C = 25 °C.b. Surface Mounted on 1" x 1" FR4 board.c. t = 5 s.d. Maximum under Steady State conditions is 160 °C/W.ABSOLUTE MAXIMUM RATINGS T A = 25°C, unless otherwise notedParameter Symbol Limit UnitDrain-Source Voltage V DS - 30VGate-Source Voltage V GS± 20Continuous Drain Current (T J = 150 °C)T C = 25 °C I D- 2.7AT C = 70 °C - 2.2T A = 25 °C - 1.9b, c T A = 70 °C - 1.5b, cPulsed Drain Current I DM - 10Continuous Source-Drain Diode CurrentT C = 25 °C I S - 1.75T A = 25 °C - 0.83b, cAvalanche Current L = 0.1 mHI AS - 5Single Pulse Avalanche Energy E AS 1.25mJ Maximum Power Dissipation T C = 25 °C P D 2.3WT C = 70 °C 1.5T A = 25 °C 1.0b, c T A = 70 °C 0.7b, cOperating Junction and Storage T emperature Range T J , T stg - 55 to 150°C THERMAL RESISTANCE RATINGSParameter Symbol Typical Maximum UnitMaximum Junction-to-Ambient b, d ≤ 5 s R thJA 80120°C/WMaximum Junction-to-Foot (Drain)Steady State R thJF 3555Vishay SiliconixSi2303CDSNotes:a. Pulse test; pulse width ≤ 300 µs, duty cycle ≤ 2 %.b. Guaranteed by design, not subject to production testing.Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.MOSFET SPECIFICATIONS T J = 25°C, unless otherwise notedParameter Symbol Test Conditions Min.Typ.Max.U nit StaticDrain-Source Breakdown Voltage V DS V DS = 0 V , I D = - 250 µA- 30VV DS Temperature Coefficient ΔV DS /T J I D = - 250 µA - 27mV/°C V GS(th) T emperature Coefficient ΔV GS(th)/T J 3.8Gate-Source Threshold Voltage V GS(th) V DS = V GS , I D = - 250 µA - 1- 3V Gate-Source LeakageI GSS V DS = 0 V, V GS = ± 20 V ± 100nA Zero Gate Voltage Drain Current I DSS V DS = - 30 V , V GS = 0 V - 1µA V DS = - 30 V , V GS = 0 V , T J = 55 °C- 10On-State Drain Current aI D(on) V DS ≤ - 5 V, V GS = - 10 V - 10A Drain-Source On-State Resistance aR DS(on) V GS = - 10 V , I D = - 1.9 A 0.1580.190ΩV GS = - 4.5 V , I D = - 1.4 A 0.2750.330Forward T ransconductance a g fsV DS = - 5 V, I D = - 1.9 A2SDynamic bInput Capacitance C iss V DS = - 15 V , V GS = 0 V, f = 1 MHz155pFOutput CapacitanceC oss 35Reverse Transfer Capacitance C rss 25Total Gate Charge Q g V DS = - 15 V , V GS = - 10 V , ID = - 1.9 A 48nC V DS = - 15 V , V GS = - 4.5 V , I D = - 1.9 A 24Gate-Source Charge Q gs 0.6Gate-Drain Charge Q gd 1Gate Resistance R g f = 1 MHz1.78.517ΩTurn-On Delay Time t d(on) V DD = - 15 V , R L = 10 ΩI D = - 1.5 A, V GEN = - 10 V, R G = 1 Ω48nsRise Timet r 1118Turn-Off Delay Time t d(off) 1118Fall Timet f 816Turn-On Delay Time t d(on) V DD = - 15 V , R L = 10 ΩI D ≅ - 1.5 A, V GEN = - 4.5 V , R G = 1 Ω3644Rise Timet r 3745Turn-Off Delay Time t d(off) 1218Fall Timet f914Drain-Source Body Diode Characteristics Continuous Source-Drain Diode Current I S T C = 25 °C- 1.75A Pulse Diode Forward Current a I SM - 10Body Diode VoltageV SD I S = - 1.5 A- 0.8- 1.2V Body Diode Reverse Recovery Time t rr I F = - 1.5 A, di/dt = 100 A/µs, T J = 25 °C1726ns Body Diode Reverse Recovery Charge Q rr 914nC Reverse Recovery Fall Time t a 12nsReverse Recovery Rise Timet b5On-Resistance vs. Drain Current and Gate VoltageCapacitanceOn-Resistance vs. Junction TemperatureThreshold VoltageSafe Operating AreaVishay SiliconixSi2303CDSTYPICAL CHARACTERISTICS 25°C, unless otherwise noted* The power dissipation P D is based on T J(max) = 150 °C, using junction-to-case thermal resistance, and is more useful in settling the upper dissipation limit for cases where additional heatsinking is used. It is used to determine the current rating, when this rating falls below the package limit.Vishay SiliconixSi2303CDSTYPICAL CHARACTERISTICS 25°C, unless otherwise notedVishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see /ppg?69991.Normalized Thermal Transient Impedance, Junction-to-FootDisclaimer Legal Disclaimer NoticeVishayAll product specifications and data are subject to change without notice.Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, “Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay’s terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.Product names and markings noted herein may be trademarks of their respective owners.元器件交易网。

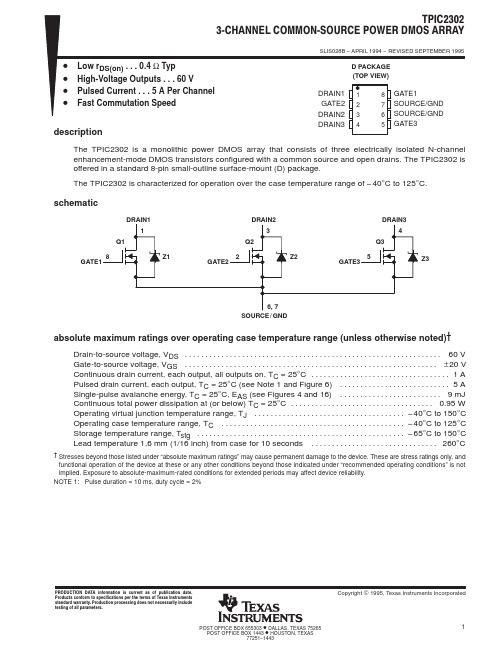

TPIC2302D资料

I RM †Reverse di/dt = 100 A/µst rr(SD)T J = 25°C Time − ns25507510012515017520022525025% of I RM †PACKAGING INFORMATIONOrderable DeviceStatus (1)Package Type Package DrawingPins Package Qty Eco Plan (2)Lead/Ball FinishMSL Peak Temp (3)TPIC2302D OBSOLETE SOIC D 8TBD Call TI Call TI TPIC2302DROBSOLETESOICD8TBDCall TICall TI(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan -The planned eco-friendly classification:Pb-Free (RoHS)or Green (RoHS &no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS):TI's terms "Lead-Free"or "Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all 6substances,including the requirement that lead not exceed 0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Green (RoHS &no Sb/Br):TI defines "Green"to mean Pb-Free (RoHS compatible),and free of Bromine (Br)and Antimony (Sb)based flame retardants (Br or Sb do not exceed 0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemicalanalysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.PACKAGE OPTION ADDENDUM8-Apr-2005Addendum-Page 1IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers AudioData Converters AutomotiveDSP BroadbandClocks and Timers Digital ControlInterface MedicalLogic MilitaryPower Mgmt Optical NetworkingMicrocontrollers SecurityRFID TelephonyRF/IF and ZigBee®Solutions Video&ImagingWirelessMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2008,Texas Instruments Incorporated。

2SK2902中文资料(fuji)中文数据手册「EasyDatasheet - 矽搜」

VGS [V]

典型漏源通态电阻

RDS(ON)= F(ID):为80μs脉冲试验,总胆固醇= 25°C

gfs [s]

] RDS(on) [m

ID [A]

ID [A]

2

芯片中文手册,看全文,戳

2SK2902-01MR

漏源通态电阻

RDS(on)=f(Tch):ID=22.5A,VGS=10V

] RDS(on)[m

富士功率MOSFET

栅极阈值电压与总胆固醇

VGS(th)=f(Tch):VDS=VGS,ID=10mA

VGS(th) [V]

Tch [°C]

典型栅极电荷特性

VGS=f(Qg):ID=45A,Tch=25°C

Tch [°C] 典型电容

C=f(VDS):VGS=0V,f=1MHz

VGS [V] C [F]

c = 25°C除非另有说明)

符号

BV DSS VGS(th)

IDSS

IGSS RDS(on) gf s Ciss Coss Crss td(on) tr td (of f ) tf IAV VSD trr Qrr

测试条件

ID=1mA VGS=0V ID=10mAV DS=VGS V DS=60V VGS=0V VGS=±30VV DS=0V ID=22.5AV GS=10V ID=22.5AV DS=25V V DS=25V V GS =0V f=1MHz VCC=30VI D=45A VGS=10V

RGS=10

Tch=25°C Tch=125°C

L=100 µH T ch=25°C IF=45AV GS=0VT ch=25°C IF=45AV GS=0V -di/dt=100A/µs T ch=25°C

MKP3384X2中文资料

• 15 to 55 mm lead pitch • Supplied loose in box • Consists of a low-inductive wound cell of metallized polypropylene film, potted in a flame-retardant case • Fixed and insulated leads.

BCcomponents

DATA SHEET

MKP 338 4 X2 Interference suppression film capacitors

Product Specification NEW File under BCcomponents, BC05 2001 Jun 22

BCcomponents

MKP 338 4 X2

MULTIPLIER (nF) 1 10 100 1000 3 4 5 6

X2

Example: 104 = 10 x 10 = 100 nF

2222

338

4.

XX X

TYPE 338 4

PACKAGING loose in box taped

LEAD CONFIGURATION lead length 3.5 mm lead length 5.0 mm lead length 25.0 mm 15.0 mm bent back to 7.5 mm insulated leads stranded Cu-wire 0.5 mm2 for 37.5 and 55 mm pitch lead length 3.5 mm

• For X2 electromagnetic interference suppression • Specially designed to meet the requirements of the “IEC 60384-14 2nd edition and EN 132400”, requiring a 2.5 kV peak pulse voltage test, and the UL1283 specifications.

si2302中文资料_数据手册_参数

Unit

V

A

W oC oC/W

- 1-

2018-5-7

SI2302

ELECTRICAL CHARACTERISTICS

Parameter

Symbol

Test Condition

Static

Drain-Source Breakdown Voltage Drain-Source On-State Resistance 1)

Vdd

Rl

Vin

D

Vout

Vgs

Rgen

G

S

td(on)

VOUT

VIN

10%

ton

toff

tr

td(off)

tf

90%

INVERTED

10%

90% 10%

90%

50%

50%

PULSE WIDTH

Figure 1:Switching Test Circuit

Figure 2:Switching Waveforms

SOT-23

D

G

S

REF.

A B C D E

F

Millimeter

Min. Max.

2.80 3.00

2.30 2.50

1.20 1.40

0.30 0.50

0

0.10

0.45 0.55

REF.

G H K J L

M

Millimeter

Min. Max. 1.80 2.00 0.90 1.1 0.10 0.20 0.35 0.70 0.92 0.98

TA = 25o TA = 75oC

Symbol

VDS VGS ID IDM

2SD2400中文资料(Inchange Semiconductor)中文数据手册「EasyDatasheet - 矽搜」

VBEsat

基地发射极饱和电压

ICBO

集电极截止电流

I EBO

发射极截止电流

hFE

DC电流增益

fT

转换频率

COB

集电极输出电容

hFE 分类

D

E

F

60-120 100-200 160-320

产品规格

2SD2400

条件

IC=1mA ;I B=0 IC=50μA ;I E=0 IE=50μA ;I C=0 IC=1A ;I B=0.1A IC=1A ;I B=0.1A VCB=120V; I E=0 VEB=4V; I C=0 IC=0.1A ; V CE=5V IC=0.1A ; V CE=5V;f=30MHz IE=0; V CB=10V; f=1MHz

A

3AΒιβλιοθήκη 2.0 W20150

℃

-55~150

℃

芯片中文手册,看全文,戳

硅 NPN功 率 晶 体 管

特性 除非另有说明 TJ = 25℃

符号

参数

V(BR)CEO 集电极 - 发射极击穿电压

V(BR)CBO 集电极基击穿电压

V(BR)EBO 发射基地击穿电压

VCEsat

集电极 - 发射极饱和电压

绝对最大额定值(Ta = 25

符号

参数

VCBO

集电极基极电压

VCEO VEBO

IC

集电极 - 发射极电压

发射极基极电压 集电极电流

ICM

集电极电流峰值

PC

集电极耗散

Tj

结温

T stg

储存温度

℃)

条件 打开发射器 开基 集电极开路

T a=25℃ T C=25℃

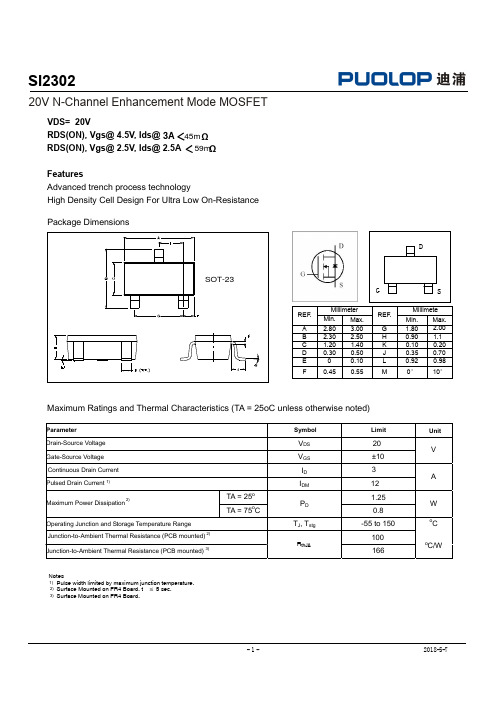

2302(MOS管封装资料)中文版

20V N 沟道增强型 MOS 场效应管

电特性

参数

符号

测试条件

静电

漏源击穿电压 漏源电阻

BVDSS RDS(on)

VGS = 0V, ID = 250uA VGS = 4.5V, ID = 2.8A VGS = 2.5V, ID = 2.0A

栅极阈值电压 栅源短路时,漏极电流 漏极短路时截止栅电流 漏源二极管

0.079

0.022 REF.

0.012

0.020

0°

8°

第3页共3页

典型

-40.0 50.0 0.7

---

--

最大

单位

--

V

60.0 mΩ

70.0

1.2

V

1

uA

±100

nA

1.3

V

V DD

S wi tc h in g

V IN

Test Circuit

RD D

V OU T

S wi tc hi ng Waveforms td (o n)

to n

tr

td (o ff )

9 0%

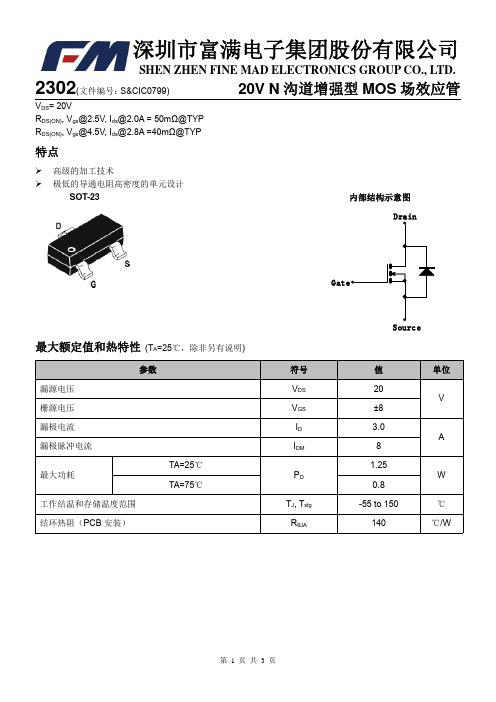

2302(文件编号:S&CIC0799)

20V N 沟道增强型 MOS 场效应管

符号

A A1 A2 b c D E E1 e e1 L L1 θ

毫米

最小

最大

0.900

1.150

0.000

0.100

0.900

1.050

0.300

0.500

0.080

0.150

2.800

3.000

1.200

1.400

2.250

VGS(th) IDSS IGSS

YB1230ST23X210资料

Applications

PDA, Palmtops and Notebook

Computers DSC, Handset Camera Modules PCMCIA Cards, PC Cameras USB Based Portable Devices (MP3, PMP) GSM/GPRS/3G RF Transceiver Modules Wireless LANs Bluetooth Portable Radios

Iground = Iin - Iout Vin = (Vout + 1V) to 6V, Iout = 10 mA Iout = 1mA to 600 mA EN = 0.4V f = 100 Hz, Iout = 10 mA

μA %/V % μA

Ripple Rejection (PSRR)

f = 1KHz, Iout = 10 mA f = 10 KHz, Iout = 10 mA

Features

2.0% Accuracy Output Voltage Output Voltage range 1.8V~3.1V Low-Noise Low-Drop-Out Stable with 2.2μF Ceramic Capacitor for Any Load Typical Output Current : 600 mA Low Quiescent Current : ~90μA 500mV Dropout at 600mA Load (3.1V) Only Need Input and Output Capacitors Power Saving Shutdown Mode (<1μA) Thermal Protection Shutdown Built-In Internal Soft-Start Output Short-circuit Current Limit Protection Green package (RoHS) available

2302中文资料

GHz TECHNOLOGY INC. RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE. GHz RECOMMENDS THAT BEFORE THE PRODUCT(S) DESCRIBED HEREIN ARE WRITTEN INTO SPECIFICATIONS, OR USED IN CRITICAL APPLICATIONS,THAT THE PERFORMANCE CHARACTERISTICS BE VERIFIED BY CONTACTING THE FACTORY.GHz Technology Inc. 3000 Oakmead Village Drive, Santa Clara, CA 95051-0808 Tel. 408 / 986-8031 Fax 408 / 986-812023022.0 Watt - 20 Volts, Class CMicrowave 2300 MHzGENERAL DESCRIPTIONThe 2302 is a COMMON BASE transistor capable of providing 2 Watts ClassC, RF output power at 2300 MHz. Gold metalization and diffused ballastingare used to provide high reliability and supreme ruggedness. The transistoruses a fully hermetic High Temperature Solder Sealed package. CASE OUTLINE 55 BT- Style 1ABSOLUTE MAXIMUM RATINGSMaximum Power Dissipation @ 25C 7.0 Wattso Maximum Voltage and CurrentBVces Collector to Emitter Voltage 45 VoltsBVebo Emitter to Base Voltage 3.5 VoltsIc Collector Current 0.5 AmpsMaximum TemperaturesStorage Temperature - 65 to + 200Co Operating Junction Temperature + 200CoELECTRICAL CHARACTERISTICS @ 25 CO SYMBOLCHARACTERISTICS TEST CONDITIONS MIN TYP MAX UNITS PoutPinPg ηcVSWR 1Power Out Power Input Power GainCollector EfficiencyLoad Mismatch Tolerance F = 2.3 GHz Vcb = 20 Volts Po = 2.0Watts As Above F = 2.3 GHz, Po = 2.0W 2.08.0400.320:1Watt Watt dB %BVcesBVeboh FE Cobθjc Collector to Emitter Breakdown Emitter to Base Breakdown Current Gain Output Capacitance Thermal Resistance Ic = 10 mA Ie = 1.0 mA Vce = 5 V, Ic = 100 mA F = 1.0 MHz, Vcb = 22 V 453.510 4.025Volts Volts pF C/W o Initial Issue August 1994。

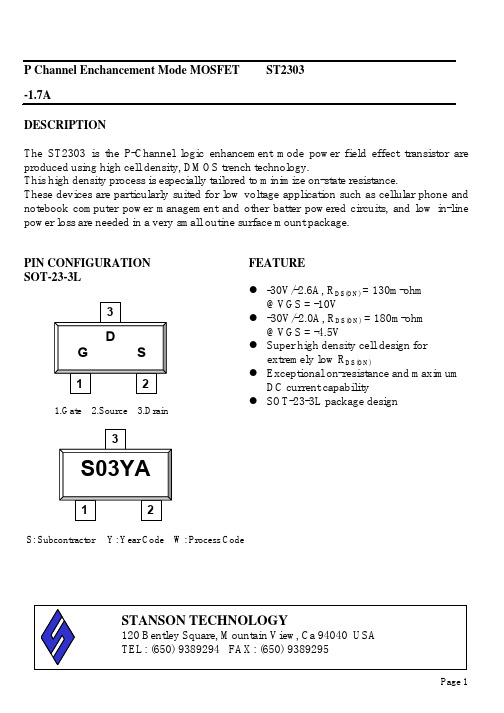

ST2303中文资料

-1.7ADESCRIPTIONThe ST2303 is the P-Channel logic enhancement mode power field effect transistor are produced using high cell density, DMOS trench technology.This high density process is especially tailored to minimize on-state resistance.These devices are particularly suited for low voltage application such as cellular phone and notebook computer power management and other batter powered circuits, and low in-line power loss are needed in a very small outine surface mount package.PIN CONFIGURATION SOT-23-3L1.Gate2.Source3.DrainS: Subcontractor Y: Year Code W: Process CodePage 1FEATUREz -30V/-2.6A, R DS(ON) = 130m-ohm@VGS = -10Vz -30V/-2.0A, R DS(ON) = 180m-ohm@VGS = -4.5Vz Super high density cell design forextremely low R DS(ON)z Exceptional on-resistance and maximumDC current capabilityz SOT-23-3L package design-1.7AABSOULTE MAXIMUM RATINGS (Ta = 25J Unless otherwise noted )Parameter Symbol Typical Unit Drain-Source Voltage V DSS -30 V Gate-Source VoltageV GSS +20V Continuous Drain Current (TJ=150J ) T A =25¢JT A =70J I D-2.6 -2.0A Pulsed Drain CurrentI DM -10 A Continuous Source Current (Diode Conduction) I S -1.25 A Power DissipationT A =25¢J T A =70JP D 1.250.8W Operation Junction Temperature T J 150 J Storgae Temperature RangeT STG -55/150 J Thermal Resistance-Junction to AmbientR cJA 100J /WPage2-1.7AELECTRICAL CHARACTERISTICS ( Ta = 25J Unless otherwise noted )Parameter Symbol Condition Min Typ Max UnitStaticDrain-Source Breakdown Voltage V (BR)DSS V GS =0V,I D =-10uA -30 VGate Threshold Voltage V GS(th) V DS =V GS ,I D =-250uA -1.0 -3.0VGate Leakage CurrentI GSS V DS =0V,V GS =+20V+100nAV DS =-30V,V GS =0V -1Zero Gate Voltage Drain CurrentI DSS V DS =-30V,V GS =0V T J =55J-10 uAOn-State Drain Current I D(on) V DS -5V,V GS =-10V -6 A Drain-source On-Resistance R DS(on)V GS =-10V,I D =-2.6A V GS =-4.5V,I D =-2.0A 0.0950.1250.1300.180Forward Transconductance g fsV DS =-10V,I D =-1.7V2.4 SDiode Forward Voltage V SDI S =-1.25A,V GS =0V -0.8 -1.2VDynamicTotal Gate Charge Qg 5.8 10 Gate-Source Charge Qgs 0.8Gate-Drain Charge Qgd V DS =-15V,V GS =-10VI D -1.7A 1.5nC Input Capacitance Ciss 226Output CapacitanceCoss 87Reverse Transfer Capacitance CrssV DS =-15V,V GS =0VF=1MHz 19PF 9 20Turn-On Timet d(on)t r 9 20 18 35 Turn-Off Timet d(off) t fV DD =-15V,R L =15I D =-1.0A,V GEN =-10VR G =66 20nSPage3-1.7ASOT-23-3L PACKAGE OUTLINEPage4-1.7ATYPICAL CHARACTERICTICS (25J Unless noted)Page 5-1.7ATYPICAL CHARACTERICTICS (25J Unless noted)Page 6。

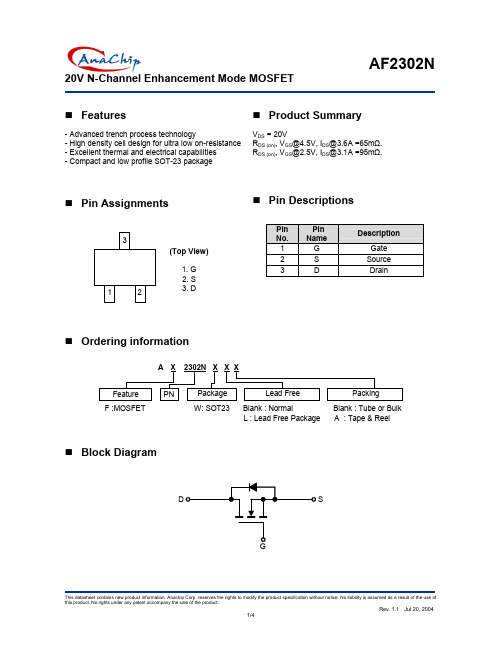

AF2302N中文资料

AF2302N20V N-Channel Enhancement Mode MOSFETFeatures- Advanced trench process technology- High density cell design for ultra low on-resistance - Excellent thermal and electrical capabilities - Compact and low profile SOT-23 packagePin Assignments321(Top View)1. G2. S3. DProduct SummaryV DS = 20VR DS (on), V GS @4.5V, I DS @3.6A =65m Ω. R DS (on), V GS @2.5V, I DS @3.1A =95m Ω.Pin DescriptionsPin No. Pin NameDescription 1 GGate 2 S Source 3 DDrainOrdering informationF :MOSFETW: SOT23Blank : NormalL : Lead Free PackageBlank : Tube or Bulk A : Tape & ReelBlock DiagramSDAF2302N20V N-Channel Enhancement Mode MOSFETAbsolute Maximum Ratings (T A =25ºC unless otherwise noted)Symbol Parameter Rating Units V DS Drain-Source Voltage 20 V V GS Gate-Source Voltage ±8 V I D Continuous Drain Current 2.4 A I DM Pulsed Drain Current 10 A T A =25ºC 1.25 P D Maximum Power Dissipation T A =70ºC 0.8W T J Operating Junction Temperature +150 ºC T J , T STG Operating Junction and Storage Temperature Range -55 to +150 ºCThermal PerformanceSymbol ParameterLimit Units T L Lead Temperature (1/8” from case)5 S R θJA Junction to Ambient Thermal Resistance (PCB mounted) 100 ºC/WNote: Surface mounted on FR4 board t < 5 sec.Electrical Characteristics Rate I D =2.4A, (T A =25oC unless otherwise noted)LimitsSymbol Parameter Test ConditionsMin.Typ. Max.UnitStaticBV DSS Drain-Source Breakdown Voltage V GS =0V, I D =250uA 20 - - VV GS =4.5V, I D = 3.6A - 50 65R DS(ON) Drain-Source On-State ResistanceV GS =2.5V, I D = 3.1A -75 95 m Ω V GS(TH) Gate Threshold Voltage V DS = V GS , I D =250uA 0.45- - V I DSS Zero Gate Voltage Drain Current V DS =20V, V GS =0V - - 1.0 uA I GSS Gate Body Leakage V GS =±8V, V DS =0V - - ±100nA I D(ON) On-State Drain Current V DS =5V, V GS =4.5V 6 - - A g fs Forward Tranconductance V DS =5V, I D = 3.6A - 10 - S DynamicQ g Total Gate Charge - 5.2 10Q gs Gate-Source Charge - 0.65 - Q gd Gate-Drain Charge V DS =10V, I D =3.6A,V GS =4.5V- 1.5 - nCt d(on) Turn-On Delay Time - 7 15t r Turn-On Rise Time - 55 80t d(off) Turn-Off Delay Time - 16 60 t f Turn-Off Fall-Time V DD =10V, R L =10Ω,I D =1A, V GEN =4.5V, R G =6Ω - 10 25 nSC iss Input Capacitance - 450 -C oss Output Capacitance - 70 - C rss Reverse Transfer Capacitance V DS =10V, V GS =0V,f=1.0MHz- 43 - pFSource-Drain DiodeI S Max. Diode Forward Current - - 1.6 A V SD Diode Forward Voltage I S =1.0A, V GS =0V - 0.75 1.2 VNote: Pulse test: pulse width < 300uS, duty cycle < 2%20V N-Channel Enhancement Mode MOSFET Marking InformationAppendixPart Number Package Device CodeAF2302N SOT23-3 02Switching Test CircuitVOUTSwitching WaveformstOutput, VOUTInput, VIN20V N-Channel Enhancement Mode MOSFETPackage InformationLDimensions In Millimeters Dimensions In InchesSymbolMin. Nom. Max. Min. Nom. Max.0.0550.0390.0471.401.20A 1.000.000 - 0.004A1 0.00 - 0.100.0510.045A2 1.00 1.15 1.300.0390.014 - 0.020b 0.35 - 0.50C 0.10 0.175 0.25 0.004 0.007 0.0100.1140.1060.122D 2.703.102.900.0710.0630.055E 1.401.601.800.0790.0910.0672.002.30e 1.700.1060.1180.094HE 2.40 2.70 3.000.012 - 0.022L 0.30 - 0.55。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3.6A

DESCRIPTION

The ST2302 is the N-Channel logic enhancement mode power field effect transistor are produced using high cell density, DMOS trench technology.

This high density process is especially tailored to minimize on-state resistance.

These devices are particularly suited for low voltage application such as cellular phone and notebook computer power management and other batter powered circuits, and low in-line power loss are needed in a very small outine surface mount package.

PIN CONFIGURATION SOT-23-3L

1.Gate

2.Source

3.Drain

S: Subcontractor Y: Year Code A: Process Code

FEATURE

z 20V/3.6A, R DS(ON) = 80m-ohm

@VGS = 4.5V

z 20V/2.4A, R DS(ON) = 95m-ohm

@VGS = 2.5V

z Super high density cell design for

extremely low R DS(ON)

z Exceptional on-resistance and maximum

DC current capability

z SOT-23-3L package design

3.6A

ABSOULTE MAXIMUM RATINGS (Ta = 25J Unless otherwise noted )

Parameter Symbol Typical Unit Drain-Source Voltage V DSS 20 V Gate-Source Voltage

V GSS +/-12

V Continuous Drain Current (TJ=150J ) T A =25¢J

T A =70J I D

2.8 2.2

A Pulsed Drain Current

I DM 10 A Continuous Source Current (Diode Conduction) I S 1.6 A Power Dissipation

T A =25¢J T A =70J

P D 1.25

0.8

W Operation Junction Temperature T J 150 J Storgae Temperature Range

T STG -55/150 J Thermal Resistance-Junction to Ambient

R c

JA 100

J /W

3.6A

ELECTRICAL CHARACTERISTICS ( Ta = 25J Unless otherwise noted )

Parameter Symbol Condition Min Typ Max Unit

Static

Drain-Source Breakdown Voltage V (BR)DSS V GS =0V,I D =10uA 20 V Gate Threshold Voltage V GS(th) V DS =V GS ,I D =50uA 0.45

1.2 V

Gate Leakage Current

I GSS V DS =0V,V GS =8V 100nA

V DS =20V,V GS =0V 1

Zero Gate Voltage Drain Current

I DSS V DS =20V,V GS =0V T J =55J

10 uA

On-State Drain Current I D(on) V DS 5V,V GS =4.5V V DS 5V,V GS =2.5V

6 4 A

Drain-source On-Resistance R DS(on)

V GS =4.5V,I D =3.6A

V GS =2.5V,I D =3.1A

0.05 0.07 0.080.095Forward Transconductance g fs

V DS =5V,I D =3.6V 10 S

Diode Forward Voltage V SD

I S =-1.6A,V GS =0V 0.85 1.2 V

Dynamic

Total Gate Charge Qg 5.4 10 Gate-Source Charge Qgs 0.65

Gate-Drain Charge Qgd V DS =10V,V GS =4.5V

I D -3.6A 1.4

nC Input Capacitance Ciss 340

Output Capacitance

Coss 115

Reverse Transfer Capacitance Crss

V DS =10V,V GS =0V

F=1MHz 33

pF 12 25

Turn-On Time

t d(on)

t r 36 60 34 60 Turn-Off Time

t d(off) t f

V DD =10V,R L =5.5I D =3.6A,V GEN =4.5V

R G =6

10 25

nS

N Channel Enchancement Mode MOSFET ST2302 3.6A

SOT-23-3L PACKAGE OUTLINE

N Channel Enchancement Mode MOSFET ST2302 3.6A

TYPICAL CHARACTERISTICS

N Channel Enchancement Mode MOSFET ST2302 3.6A

TYPICAL CHARACTERISTICS(25J Unless noted)。