AD401M168VLB-5中文资料

LED Strobe USER MANUAL ST-401说明书

LED Strobe USER MANUALST-401CATALOG1.Safety Warning (1)2. Technical Specification (4)3. Hanger Installation (5)4. Dimension (5)5. Channel function (6)6.Technical Specification (9)1.Safety WarningWarning : This product is only for professional use, not for domestic use!ST-401 Causes of injury or severe trauma may be caused by light, heat,collision, ultraviolet or falling.lmportant statementsEvery person involved with the installation, operation and maintenance of this devicehas to know:1)This product must be installed by a qualified professional.2)This product left the place of manufacture in perfect condition. In order tomaintain this condition and for safe operation, the user must always follow theinstructions and safety warnings described in this user manual.3)Manufacturer will not with responsibility for those operations not according to thisInstruction.4)Do not connect power cable of other electric products with this unit.5)Do not connect DMX512 Signal cable of other electric products with this unit.6)Always make sure that you are connecting to the proper voltage, and that the linevoltage you are connecting to is not higher than that stated on the decal or rear panel of the fixture.7)Always ground (earth) the fixture electrically.8)During long periods of non-use, disconnect the unit’s main power.9)Do not place the lamp in a damp place.10)Lamp damage or life expires, to replace the lamp in time. Before replacing the lampor fuse, turn off the power for 1 minute.11)Before opening the lamp or servicing it, make sure that the power is disconnectedand wait about fifteen minutes until the fixture is complete12)cool down.13)Do not bypass the fuse, replace the broken fuse, the fuse must be the same size fuse.14)Make sure the power cord is not curled or broken by sharp objects.15)Always check the equipment and power cord.16)Do not use the lamps and lanterns when the lightning strikes, and disconnect thepower,17)Do not open the back cover, there is no available accessories18)Maximum operating ambient temperature 40 ° C (104 ° F). Do not use the lamp whenthe glass front cover is open or damaged.19)Where to use lamps must be well ventilated. Do not look directly at the light source,because sensitive people may cause epilepsy (especially for patients with epilepsy).20)Please do not use the staircase near the use of the need to inform the strobe lightis to make use of its harmful.21)Make sure there are no items in the range of 1 M (39 in.) Of the lamp. Nopermissible items (such as cloth, wood, paper, etc.) in the range of 0.5M (20 inches) are allowed to reach a maximum temperature of 120 ° C (248 ° F), allow the lamp to cool for at least 15 minutes before touching the lamp.22)Lamps can not be covered by objects within 0.3 meters. When the lamp hanging on topof the ground, you must verify that the above can withstand 10 times the weight of the device hanging. To ensure that the external protection, rope, hardware safe and secure, and then use one or more protective measures to be protected. Installation:WARNING: Please read the safety instructions carefully before installation1.Put the light hook on the hole of the lamp handle.2.Install the light hook with light on the truss and lock it.e safety rope to hold the lamp and and truss to prevent the lamp from falling。

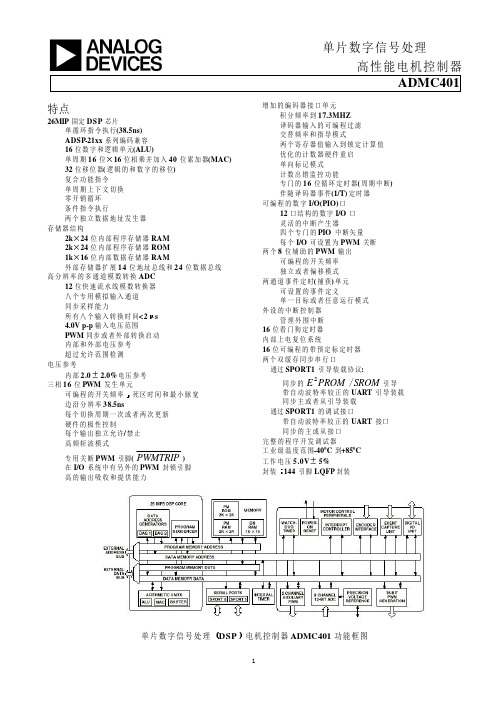

ADMC401使用手册(中文)

注释 1 由于温度变化 T MIN到T MAX 而引起的相对误差 参数说明有变化不再声明

上电复位

参数 VRST VHYST

GND=AGND=0V

TAMB =-400 C +850 C CLKIN=13MHz

测试条件 最小 3.25 典型 75

除非另有说明

最大 4.0 单位 V mV

复位阈值电压 滞环电压

2 2 3 3 3 4 5 6

低电平输出电压 1 3 4 高电平输出电压 5 低电平输出电流 5 高电平输入电流 7 高电平输入电流 8 高电平输入电流 9 低电平输入电流 7 低电平输入电流 8 低电平输入电流 9 高电平三态漏电流 10 低电平三态漏电流 10 数字电源电流(静态)11 数字电源电流(动态)12 模拟电源电流 输入引脚电容 13 输出引脚电容 13

参数 VDD AVDD T AMB 最小 4.75 4.75 -40 单位 V V O C

数字电源电压 模拟电源电压 环境工作温度

电气特性

参数 VIH VIL VOH VOL VOH VOL IIH IIH IIH IIL IIL IIL IOZH IOZL IDD IDD IDD CI CO 注释 1 双向引脚: D0-D23, RFS0, RFS1, TFS0, TFS1, SCLK0 and SCLK1, PIO0-PIO11 2 仅作为输入引脚: PWMTRIP, PWMPOL, PWMSR, RESET , EIA, EIB, EIZ, EIS, ETU0, ETU1, DR1A, DR1B, DR0, CLKIN, CONVST, MMAP, BMODE, BR 和 PWD 3 可编程输入/输出引脚 (PIO0-PIO11) 4 输出引脚: PWMSYNC, AUX0, AUX1, CLKOUT, DT0, DT1, BG , BGH, PMS, DMS, BMS, RD , WR, PWDACK 和 A0-A13 5 输出引脚: AH, AL, BH, BL, CH 和 CL 6 虽然指定是TTL输出,但所有ADMC401芯片输出是CMOS兼容的 并驱动VDD-0.3 V 和 GND+0.3 V 假设没有直流负载 7 只有输入引脚 RESET , EIA, EIB, EIZ, EIS, ETU0, ETU1, DR1A, DR1B, DR0, CLKIN, CONVST, MMAP, BMODE, BR 和 PWD 8 内部下拉电阻输入引脚 PIO0-PIO11 和 PWMTRIP 9 内部上拉电阻输入引脚 PWMPOL 和 PWMSR 10 三态引脚: A0-A13, D0-D23, PMS, DMS, BMS, RD , WR, DT0, DT1, RFS0, RFS1, TFS0, TFS1, SCLK0, SCLK1 11 静态是指IDLE指令执行 取消的引脚接电源VDD 或地 电流反映器件在无输出时钟状态下工作 12 电流反映器件无输出负载时的工作状态 13 确保正常工作 但不是测试结果 14 输出引脚电容是任何三态输出引脚上的电容性负载 参数说明有变化不再声明 高电平输入电压 1 低电平输入电压 1 高电平输出电压 1

AD4001 AD4005 数据手册说明书

16位、2 MSPS/1 MSPS 、精密差分SAR ADC数据手册AD4001/AD4005Rev. ADocument FeedbackInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks andregistered trademarks are the property of their respective owners.One Technology Way, P .O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781.329.4700 ©2017 Analog Devices, Inc. All rights reserved. Technical Support /cnADI 中文版数据手册是英文版数据手册的译文,敬请谅解翻译中可能存在的语言组织或翻译错误,ADI 不对翻译中存在的差异或由此产生的错误负责。

如需确认任何词语的准确性,请参考ADI 提供的最产品特性吞吐速率:2 MSPS/1 MSPS 可选INL :±0.4 LSB (最大值) 保证16位无失码 低功耗9.5 mW (2 MSPS),4.9 mW (1 MSPS)(仅VDD ) 80 μW (10 kSPS),16 mW (2 MSPS)(总计)SNR :典型值96.2 dB (1 kHz, V REF = 5 V);典型值95.5 dB (100 kHz) THD :典型值−123 dB (1 kHz, V REF = 5 V);典型值−99 dB (100 kHz) 易用特性可降低系统功耗和复杂性 输入过压箝位电路减少了非线性输入电荷反冲 高阻态模式 长采集阶段 输入范围压缩快速转换时间支持很低的SPI 时钟速率 SPI 可编程模式、读/写能力、状态字 差分模拟输入范围:±V REF0 V 至V REF (V REF 在2.4 V 至5.1 V 之间)单电源工作:1.8 V ,逻辑接口电压:1.71 V 至5.5 V SAR 架构:无延迟/流水线延迟,首次转换有效 精确的首次转换保证工作:−40°C 至+125°CSPI/QSPI/MICROWIRE/DSP 兼容串行接口以菊花链形式连接多个ADC ,并能提供繁忙指示10引脚封装:3 mm × 3 mm LFCSP 、3 mm × 4.90 mm MSOP 封装应用自动测试设备 机器自动化 医疗设备 电池供电设备 精密数据采集系统概述AD4001/AD4005是低噪声、低功耗、高速、16位精密逐次逼近型寄存器(SAR)模数转换器(ADC)。

CTA51BO4018VDC1.6S中文资料

CTA5

CTA5 1A C 40 12VDC 1.6 S

ORDERING INFORMATION

DIMENSIONS: (Units = mm)

PCB Layout

Standard

European

Schematic

CIT RELAY Website:

Tel: 763-535-2339

GENERAL DATA

Electrical Life @ rated load Mechanical Life Insulation Resistance Dielectric Strength, Coil to Contact Contact to Contact Shock Resistance Vibration Resistance Terminal (Copper Alloy) Strength Operating Temperature Storage Temperature Solderability Weight 100K cycles, typical 10M cycles, typical 100MΩ min @ 500VDC 750V rms min. @ sea level 500V rms min. @ sea level 200m/s2 for 11ms 1.27mm double amplitude 10-40Hz 10N -40 °C to + 85 °C -40 °C to + 155 °C 230 °C ± 2 °C for 10 ± 0.5s 19g open. 21g covered

COIL DATA

Coil Voltage VDC Coil Resistance Ω ± 10% Pick Up Voltage VDC (max) 75% of rated voltage Release Voltage VDC (min) 10% of rated voltage Coil Power W Operate Time ms Release Time ms

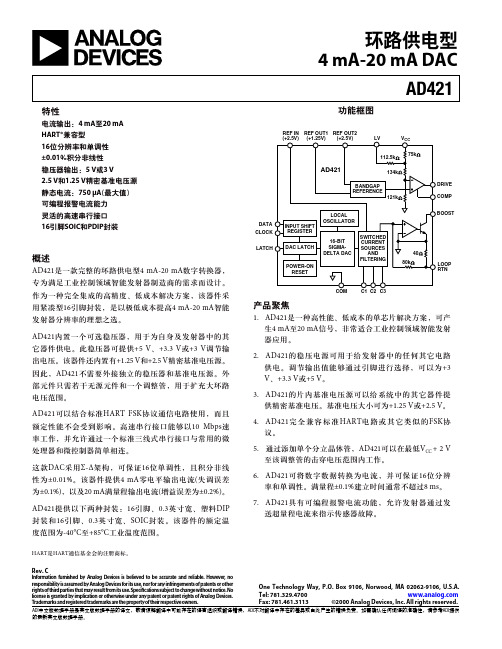

AD421中文资料

这款DAC采用Σ-Δ架构,可保证16位单调性,且积分非线 性为±0.01%。该器件提供4 mA零电平输出电流(失调误差 为±0.1%),以及20 mA满量程输出电流(增益误差为±0.2%)。

单位

条件/注释

精度 分辨率 单调性 积分非线性 失调(4 mA)(+25°C时)4 失调漂移 典型输出误差(20 mA) (+25°C时)4 总输出漂移 VCC电源灵敏度

16 16 ± 0.01 ± 0.1 ± 25 ± 0.2 ± 50 50

位 位(最小值) % FS(最大值) % FS(最大值) ppm FS/°C(最大值) % FS(最大值) ppm FS/°C(最大值) nA/mV(最大值)

FS = 满量程输出电流 VCC = 5 V 包括片内基准电压漂移 VCC = 5 V 包括片内基准电压漂移 25 nA/mV(典型值)

基准电压源 REF OUT2 输出电压 温漂

外部电流 VCC电源灵敏度 输出阻抗 噪声(0.1 Hz–10 Hz) REF OUT1

输出电压 温漂

外部电流 VCC电源灵敏度 输出阻抗 噪声(0.1 Hz–10 Hz) REF IN 输入电阻

7. AD421具有可编程报警电流功能,允许发射器通过发 送超量程电流来指示传感器故障。

HART是HART通信基金会的注册商标。

Rev. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rightsofthirdpartiesthatmayresultfromitsuse.Speci cationssubjecttochangewithoutnotice.No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

冷冻干燥机 DC401 800 型 使用说明书

冷冻干燥机DC401/800型使用说明书第2版● 真诚的感谢您本次购买重庆雅马拓科技有限公司所生产的DC401/800冷冻干燥机。

● 为了保证您对本产品的正确使用,请您在使用本产品前仔细阅读本产品的使用说明书和保证书,并请您在阅读后妥善保管,以便今后随时阅读使用。

警告:请在使用本产品前充分理解本说明书中的重要警告事项的内容。

雅马拓科学株式会社3.操作面板序号名称操作/动作① 冷冻机开关 此开关设为[ON]时,开关灯亮,冷冻机动作。

② 泵开关 可运行泵。

③ 泵开始开关 让泵气动。

④ 皮拉尼真空计 显示真空度。

⑤ 除霜开关 解除冷阱槽内冻结的冰。

⑥ 冷冻机异常灯 冷冻机超负荷时亮灯。

④⑤①②③4.关于准备冻结直到内部为止进行预备冻结,请按比样品的共晶点※低很多的温度全部进行急速冻结。

另外,冻结时,如果冰层厚,干燥中容易产生融冰,请尽量将冰层做薄。

请注意,当样品的共晶点低时,如果容器壁面大面积冻结时,容易受到外部温度的热而导致融冰。

请注意,处理量过多、样品的共晶点低时,会产生融冰现象,导致样品突沸、飞散发生。

准备冻结后,安装容器开始干燥时,到下次的样品干燥为止请以3~4分钟为间隔目标。

(但是,根据容器、样品的种类而有差异)如果间隔短,可能会发生融冰。

※ 关于共晶点纯净的水在0℃冻结,但是,溶液在0℃以下并非马上全部冻结,已冻结的纯水和没有冻结的浓缩溶液混合在一起,整体上形成柔软状态的冰。

再则,继续冷却时,包含溶质的所有溶液同样冻结,整体形成硬冰。

这个温度叫做该溶液的共晶点。

操作方法运行前,请准备干燥腔、真空泵、真空软管、异径管等。

真空泵 : PD52(本公司商品)排气量 50ℓ/min、到达真空度 6.7×10-2Pa、吸气管径 18㎜ (同等品)操作方法操作方法操作方法除霜操作方法5.除霜操作方法。

AD408M182VBB-5中文资料

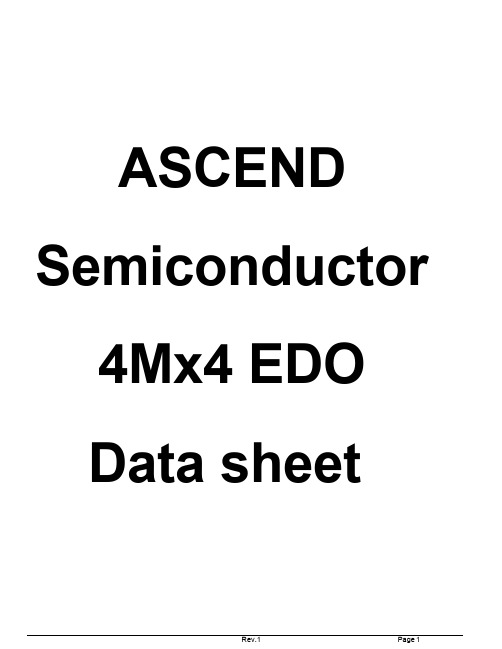

ASCEND Semiconductor 4Mx4 EDO Data sheetDescriptionThe device CMOS Dynamic RAM organized as 4,194,304 words x 4 bits with extended data out access mode. It is fabricated with an advanced submicron CMOS technology and designed to operate from a single 3.3V oniy power supply. Low voltage operation is more suitable to be used on battery backup, portable elec-tronic application. lt is packaged in JEDEC standard 26/24-pin plastic SOJ or TSOP(II).Features• Single 3.3V(%) only power supply • High speed t RAC acess time: 50/60ns • Low power dissipation- Active mode : 432/396 mW (Mas) - Standby mode: 0.54 mW (Mas)• Extended - data - out(EDO) page mode access • I/O level: CMOS level (Vcc = 3.3V)• 2048 refresh cycle in 32 ms(Std.) or 128 ms(S-version)• 4 refresh modesh: - RAS only refresh- CAS - before - RAS refresh - Hidden refresh - Self-refresh(S-version)10±Pin Name FunctionA0-A10Address inputs- Row address - Column address - Refresh address DQ1~DQ4Data-in / data-out RAS Row address strobe CAS Column address strobe WE Write enable OE Output enable Vcc Power (+ 3.3V)VssGroundVCC 1DQ12DQ23DQ34DQ45VCC6891011 NC 12 WE 13A0 A117 A218 A319VSS RAS CAS OE A8A7A6A5A4VSSAD404M42VSPin Description Pin Configuration21222324 2526151416 A1026/24-PIN 300mil Plastic SOJA9VCC 1DQ12DQ23DQ34DQ45VCC6891011 NC 12 WE 13A0 A117 A218 A319VSS RAS CAS OE A8A7 A6A5 A4VSSAD404M42VT212223242526151416 A1026/24-PIN 300mil Plastic TSOP (ll)A9A0-A10A0-A10A0-A10WECASNO. 2 CLOCK GENERATORCOLUMN ADDRESS BUFFERS (11)REFRESH CONTROLLERREFRESH COUNTERBUFFERS (11)ADDRESS ROW NO. 1 CLOCK GENERATORA0RASA1A2A3A4A5A6A7A8CONTROLLOGICDATA-IN BUFFERDATA-OUT BUFFEROEDQ1.DQ4.COLUMN DECODER2048SENSE AMPLIFIERSI/O GATING2048x42048x2048x4MEMORY ARRAY2048R O W D E C O D E RVcc VssBlock DiagramA9A10TRUTH TABLENotes: 1. EARLY WRITE only.FUNCTIONRASCAS WE OE ADDRESSESDQ SNotesROW COL STANDBY H X X X X High-Z READL L H L ROW COL Data-Out WRITE: (EARLY WRITE )L L L X ROW COL Data-lnREAD WRITE L L ROW COL Data-Out,Data-ln EDO-PAGE-MODE READ1st Cycle L H L ROW COL Data-Out 2nd CycleL H L n/a COL Data-Out EDO-PAGE MODE WRITE1st CycleL L X ROW COL Data-In 2nd Cycle L L Xn/a COL Data-InEDO-PAGE-MODEREAD-WRITE 1st Cycle L ROW COL Data-Out, Data-In 2nd Cycle L n/a COL Data-Out, Data-In HIDDEN REFRESHREAD L H L ROW COL Data-Out WRITEL L X ROW COL Data-In 1RAS-ONLY REFRESH L H X X ROW n/a High-Z CBR REFRESHLHXXXHigh-ZH X →H L →L H →H L →H L →H L →H L →H L →H L →L H →H L →H L →L H→L H L →→L H L→→H L→Absolute Maximum RatingsRecommended DC Operating ConditionsCapacitanceTa = 25°C, V CC = 3.3V%, f = 1MHz Note: 1. Capacitance measured with effective capacitance measuring method. 2. RAS, CAS = V IH to disable Dout.ParameterSymbol Value Unit Voltage on any pin relative to Vss V T -0.5 to + 4.6V Supply voltage relative to Vss V CC -0.5 to + 4.6V Short circuit output current I OUT 50mA Power dissipation P D 1.0WOperating temperature T OPT 0 to + 70°C Storage temperatureT STG-55 to + 125°CParameter/Condition Symbol3.3 Volt VersionUnitMinTyp MaxSupply VoltageV CC 3.0 3.33.6V Input High Voltage, all inputs V IH 2.0-V CC + 0.3V Input Low Voltage, all inputsV IL-0.3-0.8VParameterSymbol Typ Max Unit Note Input capacitance (Address)C I1 -5pF 1Input capacitance (RAS, CAS, OE, WE)C I2-7pF 1Output capacitance(Data-in, Data-out)C I/O-7pF1, 210±DC Characteristics :(T a = 0 to 70°C, V CC = + 3.3V%, V SS = 0V)Parameter Symbol Test Conditions AD404M42V Unit Notes-5-6Min Max Min MaxOperating current I CC1RAS cyclingCAS, cyclingt RC = min-120-110mA1, 2Standby Current LowpowerS-versionI CC2LVTTL interfaceRAS, CAS = V IHDout = High-Z-0.5-0.5mACMOS interfaceRAS, -0.2VDout = High-Z-0.15-0.15mAStandardpowerversionLVTTL interfaceRAS, CAS = V IHDout = High-Z-2-2mACMOS interfaceRAS,-0.2VDout = High-Z-0.5-0.5mARAS- only refresh current I CC3RAS cycling, CAS = V IHt RC = min-120-110mA1, 2 EDO page mode current I CC4t PC = min-90-80mA1, 3CAS- before- RAS refresh current I CC5t RC = minRAS, CAS cycling-120-110mA1, 2Self- refresh current (S-Version)I CC8 - 550 - 55010±CAS V CC≥CAS V CC≥t RASS100µs≥µADC Characteristics :(T a = 0 to 70°C , V CC = +3.3V %, V SS = 0V)Notes:1. I CC is specified as an average current. It depends on output loading condition and cycle rate when the device is selected. I CC max is specified at the output open condition.2. Address can be changed once or less while RAS = V IL .3. For I CC4, address can be changed once or less within one EDO page mode cycle time.Parameter Symbol Test Conditions AD404M42VUnitNotes-5-6Min MaxMin MaxInput leakage current I LI + 0.3V -55-55Output leakage current I LO + 0.3V Dout = Disable -55-55Output high Voltage V OH I OH = -2mA 2.4- 2.4-V Output low voltage V OLI OL = +2mA-0.4-0.4V10±0V Vin V CC ≤≤µA 0V Vout V CC ≤≤µAAC Characteristics(T a = 0 to + 70°C , V cc = 3.3V %, V ss = 0V) *1, *2, *3, *4Test conditions• Output load: one TTL Load and 100pF (V CC = 3.3V %)• Input timing reference levels:V IH = 2.0V, V IL = 0.8V (V CC = 3.3V %)• Output timing reference levels:V OH = 2.0V, V OL = 0.8V10±10±10±Read, Write, Read- Modify- Write and Refresh Cycles (Common Parameters)ParameterSymbol AD404M42V UnitNotes-5-6Min MaxMin MaxRandom read or write cycle time t RC 84-104-ns RAS precharge timet RP 30-40-ns CAS precharge time in normal mode t CPN 10-10-ns RAS pulse width t RAS 50100006010000ns 5CAS pulse width t CAS 8100001010000ns 6Row address setup time t ASR 0-0-ns Row address hold time t RAH 8-10-ns Column address setup time t ASC 0-0-ns 7Column address hold time t CAH 8-10-ns RAS to CAS delay timet RCD 12371445ns 8RAS to column address delay time t RAD 10251230ns 9Column address to RAS lead time t RAL 25-30-ns RAS hold time t RSH 8-10-ns CAS hold timet CSH 38-40-ns CAS to RAS precharge time t CRP 5-5-ns 10OE to Din delay time t OED 12-15-ns Transition time (rise and fall)t T 150150ns 11Refresh periodt REF -32-32ms Refresh period (S- Version)t REF -128-128ms CAS to output in Low- Z t CLZ 0-0-ns CAS delay time from Din t DZC 0-0-ns OE delay time from Dint DZO-0-nsRead CycleWrite Cycle Parameter SymbolAD404M42V Unit Notes-5-6Min Max Min MaxAccess time from RAS t RAC-50-60ns12 Access time from CAS t CAC-14-15ns13, 14 Access time from column address t AA-25-30ns14, 15 Access time from OE t OEA-12-15nsRead command setup time t RCS0-0-ns7 Read command hold time to CAS t RCH0-0-ns10, 16 Read command hold time to RAS t RRH0-0-ns16 Output buffer turn-off time t OFF012015ns17 Output buffer turn-off time from OE t OEZ012015ns17Parameter SymbolAD404M42V Unit Notes -5-6Min Max Min MaxWrite command setup time t WCS0-0-ns7, 18 Write command hold time t WCH8-10-nsWrite command pulse width t WP8-10-nsWrite command to RAS lead time t RWL13-15-nsWrite command to CAS lead time t CWL8-10-nsData-in setup time t DS0-0-ns19 Data-in hold time t DH8-10-ns19 WE to Data-in delay t WED10-10-nsRead- Modify- Write CycleRefresh Cycle Parameter SymbolAD404M42V Unit Notes-5-6Min Max Min MaxRead-modify- write cycle time t RWC108-133-nsRAS to WE delay time t RWD64-77-ns18 CAS to WE dealy time t CWD26-32-ns18 Column address to WE delay time t AWD39-47-ns18 OE hold time from WE t OEH8-10-nsParameter SymbolAD404M42VUnit Notes -5-6Min Max Min MaxCAS setup time (CBR refresh) t CSR5-5-nsCAS hold time (CBR refresh)t CHR8-10-ns10 RAS precharge to CAS hold time t RPC5-5-ns7 RAS pulse width (self refresh)t RASS100-100-RAS precharge time (self refresh)t RPS90-110-nsCAS hold time (CBR self refresh)t CHS-50--50-nsWE setup time t WSR0-0-nsWE hold time t WHR10-10-nsµsEDO Page Mode CycleEDO Page Mode Read Modify Write CycleParameterSymbol AD404M42VUnit Notes-5-6Min MaxMin MaxEDO page mode cycle timet PC 20-25-ns EDO page mode CAS precharge time t CP 10-10-ns EDO page mode RAS pulse width t RASP 5010560105ns 20Access time from CAS precharge t CPA -30-35ns 10, 14RAS hold time from CAS precharge t CPRH 30-35-ns OE high hold time from CAS high t OEHC 5-5-ns OE high pulse widtht OEP 10-10-ns Data output hold time after CAS low t COH 5-5-ns Output disable delay from WEt WHZ 310310ns WE pulse width for output disable whenCAS hight WPZ7-7-nsParameterSymbol AD404M42V Unit Notes -5-6Min MaxMin MaxEDO page mode read- modify- write cycle CAS precharge to WE delay timet CPW 45-55-ns 10EDO page mode read- modify- write cycle timet PRWC56-68-nsNotes :1. AC measurements assume t T = 2ns.2. An initial pause of 100 is required after power up, and it followed by a minimum of eightinitialization cycles (RAS - only refresh cycle or CAS - before - RAS refresh cycle). If the internal refresh counter is used, a minimun of eight CAS - before - RAS refresh cycles are required.3. In delayed write or read-modify-write cycles, OE must disable output buffer prior to applying data to the device.4. All the V CC and V SS pins shall be supplied with the same voltages.5. t RAS (min) = t RWD (min)+t RWL (min)+t T in read-modify-write cycle.6. t CAS (min) = t CWD (min)+t CWL (min)+t T in read-modify-write cycle.7. t ASC (min), t RCS (min), t WCS (min), and t RPC are determined by the falling edge of CAS .8. t RCD (max) is specified as a reference point only, and t RAC (max) can be met with the t RCD (max) limit.Otherwise, t RAC is controlled exclusively by t CAC if t RCD is greater than the specified t RCD (max) limit. 9. t RAD (max) is specified as a reference point only, and t RAC (max) can be met with the t RAD (max) limit.Otherwise, t RAC is controlled exclusively by t AA if t RAD is greater than the specified t RAD (max) limit. 10. t CRP , t CHR , t RCH , t CPA and t CPW are determined by the rising edge of CAS .11. V IH (min) and V IL (max) are reference levels for measuring timing or input signals. Therefore, transitiontime is measured between V IH and V IL .12. Assumes that t RCD tRCD (max) and t RAD t RAD (max). If t RCD or t RAD is greater than the maximum recommended value shown in this table, t RAC exceeds the value shown. 13. Assumes that (max) and (max).14. Access time is determined by the maximum of t AA , t CAC , t CPA . 15. Assumes that (max) and (max). 16. Either t RCH or t RRH must be satisfied for a read cycle.17. t OFF (max) and t OEZ (max) define the time at which the output achieves the open circuit condition (highimpedance). t OFF is determined by the later rising edge of RAS or CAS.18. t WCS , t RWD , t CWD , and t AWD are not restrictive operating parameters. They are included in the datasheet as electrical characteristics only. If (min), the cycle is an early write cycle and the data out will remain open circuit (high impedance) throughout the entire cycle. If (min),(min), (min) and (min), the cycle is a read-modify-write and the data output will contain data read from the selected cell. If neither of the above sets of conditions is satisfied, the condition of the data output (at access time) is indeterminate.19. These parameters are referenced to CAS separately in an early write cycle and to WE edge in adelayed write or a read-modify-write cycle.20. t RASP defines RAS pulse width in EDO page mode cycles.µs ≤≤t RCD t RCD ≥t RADt RAD ≤t RCD t RCD ≤t RAD t RAD ≥t WCS t WCS ≥t RWD t RWD ≥t CWDt CWD ≥t AWD t AWD ≥t CPW t CPW≥Timing Waveforms• Read Cyclet RC t RASt RPtCRPtCPNtRRHtRCHt OEZ t OFF tOEA tCACt AAtRACt CLZD OUTtRCS t ASR tRAH tASC tCAH tRAD t RALtCAStRSH tRCDt TtCSHRASCASADDRESSWEDQ1~DQ4Note : = don’t care OEt OFFRowColumn= Invalid Dout•Early Write CycletRC t RASt RPt WCHt DSt DHt WCS t RALtCAStRSH tRCDt TtCSHRASCASWEDQ1~DQ4tCRPtASRtRAH tASCtCAH ADDRESSColumnRowtCPND INtRADt RAL• Delayed Write CycletRC t RASt RPt RWL t RCSt CAStRSH tRCDt TtCSHRASCAStASR tRAH tCAHADDRESSColumnRow tASC D INDQ1~DQ4WEtCRPtCPNt DHt DSt OEHt OEDOEt DSOPENt WPt CWL• Read - Modify - Write CycletRWC t RASt RPtRWDt WPtRADtRWL tCAStCWL tRCDt TtCPNRASCASWEtCRP t ASRtRAHtASCtCAHADDRESS Column RowDQ1~DQ4t DHt DSOEtRCStAWD tCWD D INt OEDt OEHt OEZt OEA t CAC t RACt AADQ1~DQ4D OUTOPENtDZCtDZO• EDO Page Mode Read CycletRASPtCPRHt RCStCAStRSH tRCDt OEAtCSHRASCAStASRtRAHtCAHADDRESStCASWEtCRPt CPOEDQ1~DQ4OPENtOEPD OUT 1t PCt CPtCAStCPNtCRPtRADtCAHtASCt ASCtCAHt ASCt RAL Row Column 1t OEAt OEHCtRRH tRCHt RACt AAt AAt AA t CPA t CPA t OEZt OFFt OFFt CACt OEZt CAC t CACt COHD OUT NWE OE Column 2Column N Rowt RPD OUT 2• EDO Page Mode Early Write CycletRASPtRPt WCSt CAStRSH tRCDRASCAStASRtRAHtCAHADDRESStCASWEt CPDQ1~DQ4t PCt CPt CAStCPNtCRP tCAH tASCtASC tCAH tASC Row Column 1t DS WE Column 2Column Nt WCH t WCS t WCH t WCS t WCHt DH t DS t DH t DS t DHD IN 1D IN 2D IN Nt TtCSH• EDO Page Mode Read-Early-Write Cyclet RASPtCPRHt RCStCAStRSH tRCDt OEAtCSHRASCAStASRtRAHtCAHADDRESStCASWEtCRPt CPOEDQ1~DQ4OPENtWEDt PCt CPtCAStCPNtCRPtRADtRAHtASCt ASCtCAHt ASCt RAL Row Column 1tWCStRCHt RACt AAt AAt CPA t DHt WHZt CACt CACt COHWE OE Column 2Column N Rowt RPt CAL tWCHDataDoutput 2Data Input NDataDoutput 1t DStCSH• EDO Page Mode Read-Modify-Write Cyclet RASPt CPRHt RCStCASt WP RASCASt ASRtRAHtCAHADDRESSt CASWEtRCDCPDQ1~DQ4tPRWCt CPtCAStCRPtRADtCAHtASCt ASCtCAH tASC Row Column 1tRWLtRCSt OEDt DZOt CAC WE OEt RPt RAL D OUT 2D OUT ND OUT 1tTt Column NColumn 2Column 1tRWD tAWD tCWDtCWLtRCStCWDtAWD tCPW tCWL tCPW tAWD tCWDtCWL t OEDt OEDt OEHt OEHt OEHt CAC t CAC t OEA t AAt RACt OEZt OEAt AA t CPAt OEZt OEAt AA t CPAt OEZ t DSt DHt WP t DSt DHt WP t DSt DHOPENOPENOPEN D IN 1D IN ND IN 2DQ1~DQ4t DZCt DZOt DZCt DZCt DZO• Read Cycle with WE Controlled Disablet WPZt RCStCAStRCDt TtCSHRASCASt ASRtRAHtCAHADDRESSColumnRow tASCD DQ1~DQ4WEt OEZt DSt WHZOEt RCH t OEA t CACt AAt RACt CLZOUTtRADRASADDRESSt RC t CRPt ASRt RAHt Tt RPCROWt OFFCAS t RASt RPOPENt CRPDQ1~DQ4RASt CSRt WSRt RPt T t RPCt OFFCAS t RASt RPOPENt CRPDQ1~DQ4t RPCt CHRt RASt RPt RCt RCt CHRt CSRt WHRt WSRt WHRWECAS-Before-RAS Refresh CycleRASWEt RPCt OFFt CSRt CHSt WSRCASt RASS t RPSOPENDQ1~DQ4t WHRHigh lmpedance• Hidden Refresh Cyclet RPt RASRASt RCDt CRPADDRESSWEt CHRt CASt RSHt RAHt ASRt ASCt CAHt RAL ROW t RCHt OEZCASDQ1~DQ4t Tt RCSD t RASt RASt RPt RPt RC t RCt RCt RADt RRHt OFF t OFFt OEA t CACt AAt RACCOlumnOUTOE(READ)(REFRESH)(REFRESH)Ordering informationAD404M42VSA-5• AD• Ascend Memory Product • 40 • Device Type• 4M4 • Density and Organization • 2• Refresh Rate, 2: 2K Refresh • V• T: 5V, V: 3.3V• S • Package Type (S : SOJ, T : TSOP II)• A• Version• 5• Speed (5: 50 ns, 6: 60 ns)Part Number Access time PackageAD404M42VSA-5AD404M42VSA-6AD404M42VTA-5AD404M42VTA-650 ns 60 ns 50 ns 60 ns300mil 26/24-Pin Plastic SOJTSOP IIPackaging information • 300 mil, 26/24-Pin Plastic SOJ• 300 mil, 26/24-Pin TSOP II。

AD8005中文资料

TMIN to TMAX Offset Drift +Input Bias Current TMIN to TMAX –Input Bias Current Input Bias Current Drift (± ) Open-Loop Transimpedance INPUT CHARACTERISTICS Input Resistance Input Capacitance Input Common-Mode Voltage Range Common-Mode Rejection Ratio OUTPUT CHARACTERISTICS Output Voltage Swing Output Current Short Circuit Current POWER SUPPLY Quiescent Current Power Supply Rejection Ratio OPERATING TEMPERATURE RANGE

元器件交易网

a

FEATURES Ultralow Power 400 A Power Supply Current (4 mW on ؎5 VS) Specified for Single Supply Operation High Speed 270 MHz, –3 dB Bandwidth (G = +1) 170 MHz, –3 dB Bandwidth (G = +2) 280 V/ s Slew Rate (G = +2) 28 ns Settling Time to 0.1%, 2 V Step (G = +2) Low Distortion/Noise –63 dBc @ 1 MHz, V O = 2 V p-p –50 dBc @ 10 MHz, VO = 2 V p-p 4.0 nV/√Hz Input Voltage Noise @ 10 MHz Good Video Specifications (RL = 1 k⍀, G = +2) Gain Flatness 0.1 dB to 30 MHz 0.11% Differential Gain Error 0.4؇ Differential Phase Error APPLICATIONS Signal Conditioning A/D Buffer Power-Sensitive, High-Speed Systems Battery Powered Equipment Loop/Remote Power Systems Communication or Video Test Systems Portable Medical Instruments PRODUCT DESCRIPTION

APDA03-41MBWA资料

Recommended Soldering Pattern (Units : mm)

SPEC NO: DSAB2967 APPROVED: J.Lu

REV NO: V.3 CHECKED:Joe Lee

DATE:DEC/07/2002 DRAWN:Y.H.LI

PAGE: 4 OF 5

元器件交易网

SPEC NO: DSAB2967 APPROVED: J.Lu

REV NO: V.3 CHECKED:Joe Lee

DATE:DEC/07/2002 DRAWN:Y.H.LI

PAGE: 1 OF 5

元器件交易网

Selection Guide

P ar t N o . Dic e L en s Ty p e Iv (u c d ) @ 10m A Min . APDA03-41MBWA BLUE(GaN) WHITE DIFFUSED 1200 Ty p . 5000 Common Anode,Rt. Hand Decimal D es c r i p t i o n

元器件交易网SURΒιβλιοθήκη ACE MOUNT DISPLAY

APDA03-41MBWA BLUE

Features

!0.3INCH

Description

The Blue source color devices are made with GaN on SiC Light Emitting Diode. Static electricity and surge damage the LEDS. It is recommended to use a wrist band or anti-electrostatic glove when handling the LEDs. All devices, equipment and machinery must be electrically grounded.

ADI电路笔记 CN-0359说明书

电路笔记CN-0359Circuits from the Lab® reference designs are engineered and tested for quick and easy system integration to help solve today’s analog, mixed-signal, and RF design challenges. For more information and/or support, visit /CN0359.连接/参考器件AD825310 MHz、20 V/μs、G = 1、10、100、1000、i CMOS可编程增益仪表放大器ADuCM360集成双通道Σ-Δ型ADC和ARM Cortex-M3的低功耗精密模拟微控制器ADA4627-1 30 V、高速、低噪声、低偏置电流JFET运算放大器AD8542CMOS轨到轨通用放大器ADA4000-1 低成本、精密JFET输入运算放大器ADP2300 1.2 A、20 V、700 kHz/1.4 MHz异步降压型稳压器ADA4638-1 30 V、零漂移、轨到轨输出精密放大器ADP1613 650 kHz/1.3 MHz升压PWM DC-DC开关转换器ADA4528-2 精密、超低噪声、RRIO、双通道、零漂移运算放大器ADG1211低电容、低电荷注入、±15 V/+12 V iCMOS四通道单刀单掷开关ADA4077-2 4 MHz、7 nV/√Hz、低失调和漂移、高精度放大器ADG1419 2.1 Ω导通电阻、±15 V/+12 V/±5 V、iCMOS单刀双掷开关AD8592 CMOS、单电源、轨到轨输入/输出运算放大器,具有关断功能ADM3483 3.3 V限摆率、半双工、RS-485/RS-422收发器全自动高性能电导率测量系统Rev. 0Circuits from the Lab® reference designs from Analog Devices have been designed and built by AnalogDevices engineers. Standard engineering practices have been employed in the design andconstruction of each circuit, and their function and performance have been tested and veri ed in a labenvironment at room temperature. However, you are solely responsible for testing the circuit and determining its suitability and applicability for your use and application. Accordingly, in no event shall Analog Devices be liable for direct, indirect, special, incidental, consequential or punitive damages due to any cause whatsoever connected to the use of any Circuits from the Lab circuits. (Continued on last page)One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 Fax: 781.461.3113 ©2015 Analog Devices, Inc. All rights reserved.评估和设计支持电路评估板CN-0359电路评估板(EVAL-CN0359-EB1Z)设计和集成文件原理图、源代码、布局文件、物料清单电路功能与优势图1中的电路是一个完全独立自足、微处理器控制的高精度电导率测量系统,适用于测量液体的离子含量、水质分析、工业质量控制以及化学分析。

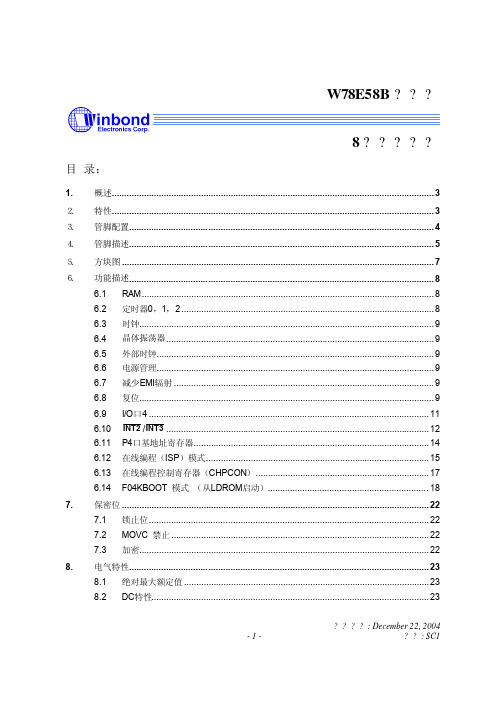

W78E58B中文资料

8.3.1 时钟输入波形...................................................................................................................... 25 8.3.2 程序读取周期...................................................................................................................... 26 8.3.3 数据读取周期...................................................................................................................... 26 8.3.4 数据写周期.......................................................................................................................... 27 8.3.5 端口访问周期...................................................................................................................... 27

TI ADS7038 8通道12位ADC模块中文说明书

AIN0 / GPIO0AIN1 / GPIO1AIN2 / GPIO2AIN3 / GPIO3AIN4 / GPIO4AIN5 / GPIO5AIN6 / GPIO6AIN7 / GPIO7GNDDVDDSCLK SDI CS Device Block DiagramSDOExample System ArchitectureOVP: Over voltage protection OCP: Over current protectionProduct Folder Order Now Technical Documents Tools &SoftwareSupport &CommunityADS7038ZHCSJX6A –JUNE 2019–REVISED DECEMBER 2019具有SPI 接口、GPIO 和CRC 的ADS7038小型8通道12位ADC1特性•小封装尺寸:–WQFN 3mm ×3mm•8通道,可配置为以下任意组合:–最多8个模拟输入、数字输入或数字输出•用于I/O 扩展的GPIO :–开漏、推挽数字输出•模拟监控:–每个通道的可编程阈值–用于瞬态抑制的事件计数器•宽工作范围:–AVDD :2.35V 至5.5V –DVDD :1.65V 至5.5V–温度范围:-40°C 至+125°C •增强型SPI 数字接口:–高速60MHz 接口–使用>13.5MHz SPI 实现最大吞吐量•用于读取/写入操作的CRC :–数据读取/写入CRC –上电配置CRC •可编程均值滤波器:–用于求平均值的可编程样本大小–利用内部转换求平均值–16位分辨率2应用•宏远程无线电单元(RRU)•电池管理系统(BMS)•串式逆变器•中央逆变器3说明ADS7038是一款易于使用的8通道多路复用12位1MSPS 逐次逼近寄存器模数转换器(SAR ADC)。

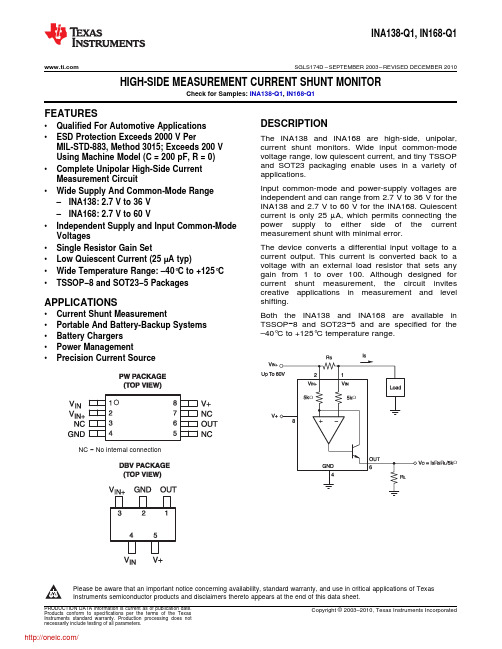

INA168QDBVRQ1;INA168QPWRG4Q1;中文规格书,Datasheet资料

INA138-Q1,IN168-Q1 SGLS174D–SEPTEMBER2003–REVISED DECEMBER2010 HIGH-SIDE MEASUREMENT CURRENT SHUNT MONITORCheck for Samples:INA138-Q1,IN168-Q1FEATURESDESCRIPTION•Qualified For Automotive Applications•ESD Protection Exceeds2000V Per The INA138and INA168are high-side,unipolar,current shunt monitors.Wide input common-mode MIL-STD-883,Method3015;Exceeds200Vvoltage range,low quiescent current,and tiny TSSOP Using Machine Model(C=200pF,R=0)and SOT23packaging enable uses in a variety of •Complete Unipolar High-Side Currentapplications.Measurement CircuitInput common-mode and power-supply voltages are •Wide Supply And Common-Mode Rangeindependent and can range from2.7V to36V for the –INA138:2.7V to36V INA138and2.7V to60V for the INA168.Quiescent–INA168:2.7V to60V current is only25m A,which permits connecting thepower supply to either side of the current •Independent Supply and Input Common-Modemeasurement shunt with minimal error.VoltagesThe device converts a differential input voltage to a •Single Resistor Gain Setcurrent output.This current is converted back to a •Low Quiescent Current(25µA typ)voltage with an external load resistor that sets any •Wide Temperature Range:–40°C to+125°C gain from1to over100.Although designed forcurrent shunt measurement,the circuit invites •TSSOP−8and SOT23−5Packagescreative applications in measurement and levelshifting.APPLICATIONS•Current Shunt Measurement Both the INA138and INA168are available inTSSOP−8and SOT23−5and are specified for the •Portable And Battery-Backup Systems–40°C to+125°C temperature range.•Battery Chargers•Power Management•Precision Current SourceNC−No internal connectionPlease be aware that an important notice concerning availability,standard warranty,and use in critical applications of TexasInstruments semiconductor products and disclaimers thereto appears at the end of this data sheet.Copyright©2003–2010,Texas Instruments Incorporated Products conform to specifications per the terms of the TexasINA138-Q1,IN168-Q1SGLS174D–SEPTEMBER2003–REVISED ORDERING INFORMATION(1)SPECIFIEDPACKAGE PACKAGE TRANSPORT PRODUCT PACKAGE−LEAD TEMPERATUREDESIGNATOR(2)MARKING MEDIA,QUANTITYRANGEINA138QPWRQ1TSSOP−8PW−40°C to+125°C INA138Tape and Reel,2000 INA168QPWRQ1TSSOP−8PW−40°C to+125°C INA168Tape and Reel,2000 INA168QDBVRQ1SOT23-5DBV−40°C to+125°C LUIQ Tape and Reel,3000 (1)For the most current package and ordering information,see the Package Option Addendum at the end of this document,or see the TIweb site at .(2)Package drawings,thermal data,and symbolization are available at /packaging.This integrated circuit can be damaged by ESD.Texas Instruments recommends that all integrated circuits be handled with appropriate precautions.Failure to observe proper handling and installation procedures can cause damage.ESD damage can range from subtle performance degradation to complete device failure.Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.ABSOLUTE MAXIMUM RATINGS(1)over operating free-air temperature range(unless otherwise noted)VALUESupply voltage,V+INA138-Q1−0.3V to60VINA168-Q1−0.3V to75V Analog inputs,V IN+,V IN−,Common mode INA138-Q1−0.3V to60VINA168-Q1−0.3V to75V Analog inputs,(V IN+)−(V IN−),Differential−40V to2V Analog output,out−0.3V to40V Operating temperature−55°C to150°C Storage temperature−65°C to150°C Junction temperature150°CThermal resistance,junction-to-ambient,RΘJA PW150°C/WDBV200°C/WLead temperature(soldering,10seconds)260°C(1)Stresses beyond those listed under"absolute maximum ratings"may cause permanent damage to the device.These are stress ratingsonly,and functional operation of the device at these or any other conditions beyond those indicated under"recommended operating conditions"is not implied.Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.ELECTRICAL CHARACTERISTICS=−40°C to125°C,V S=5V,V IN+=12V,and R OUT=125kΩunless otherwise notedTAPARAMETER TEST CONDITIONS MIN TYP MAX UNIT InputFull-scale sense voltage V SENSE=V IN+−V IN−100500mV Common-mode input range INA138 2.736VINA168 2.760Common-mode rejection V IN+=2.7V to36V,V SENSE INA138100120=50mVdBV IN+=2.7V to60V,V SENSE INA168100120=50mVOffset voltage(1)±0.2±2mV Offset voltage vs temperature1m V/°COffset voltage vs power supply,V+V+=2.7V to36V,V SENSE=INA1380.11050mVm V/VV+=2.7V to60V,V SENSE=INA1680.11050mV(1)Defined as the amount of input voltage,V SENSE,to drive the output to zero.2Submit Documentation Feedback Copyright©2003–2010,Texas Instruments IncorporatedINA138-Q1,IN168-Q1 SGLS174D–SEPTEMBER2003–REVISED DECEMBER2010ELECTRICAL CHARACTERISTICS(continued)=−40°C to125°C,V S=5V,V IN+=12V,and R OUT=125kΩunless otherwise notedTAPARAMETER TEST CONDITIONS MIN TYP MAX UNIT Input bias current VI N+=V IN−=12V10m A OutputTransconductance V SENSE=10mV−150mV194206m A/V Transconductance vs temperature V SENSE=100mV10nA/°C Nonlinearity error V SENSE=10mV to150mV±0.01%±0.2%Total output error V SENSE=100mV±0.5±3.2% Output impedance1GΩ5pFVoltage output swing to power(V+)−0.8(V+)−1.2V supply,V+Voltage output swing to commonV CM−0.5V CM−1.2V mode,V CMFrequency ResponseBandwidth R OUT=5kΩ800kHzR OUT=125kΩ32Settling time(0.1%)5V step R OUT=5kΩ 1.8m sR OUT=125kΩ30NoiseOutput-current noise density T A=25°C9pA/√Hz Total output-current noise BW=100kHz3nA RMS Power SupplyOperating range,V+INA138 2.736VINA168 2.760Quiescent current V SENSE=0,IO=02560m A Copyright©2003–2010,Texas Instruments Incorporated Submit Documentation Feedback3––G a i n (d B )C o m m o n -M o d e R e j e c t i o n (d B )COMMON-MODE REJECTION vs FREQUENCYP o w e r -S u p p l y R e j e c t i o n (d B )POWER-SUPPLY REJECTION vs FREQUENCY–––T o t a l O u t p u t E r r o r (%)––T o t a l O u t p u t E r r o r (%)Power-Supply Voltage (V)TOTAL OUTPUT ERROR vs POWER-SUPPL YVOLTAGEQ u i e s c e n t C u r r e n t (A )Power-Supply Voltage (V)INA138-Q1,IN168-Q1SGLS174D –SEPTEMBER 2003–REVISED DECEMBER 2010TYPICAL CHARACTERISTICST A =+25°C,V +=5V,V IN+=12V,and R L =125k Ω,unless otherwise noted.Figure 1.Figure 2.Figure 3.Figure 4.Figure 5.Figure 6.4Submit Documentation Feedback Copyright ©2003–2010,Texas Instruments Incorporatedmm INA138-Q1,IN168-Q1SGLS174D –SEPTEMBER 2003–REVISED DECEMBER 2010TYPICAL CHARACTERISTICS (continued)T A =+25°C,V +=5V,V IN+=12V,and R L =125k Ω,unless otherwise noted.Figure 7.Figure 8.Copyright ©2003–2010,Texas Instruments Incorporated Submit Documentation Feedback 5INA138-Q1,IN168-Q1SGLS174D–SEPTEMBER2003–REVISED APPLICATION INFORMATIONFigure9illustrates the basic circuit diagram for both the INA138and INA168.Load current I S is drawn from supply V S through shunt resistor R S.The voltage drop in shunt resistor V S is forced across R G1by the internal op amp,causing current to flow into the collector of Q1.External resistor R L converts the output current to a voltage, V OUT,at the OUT pin.The transfer function for the INA138is:I O=g m(V IN+−V IN−)where g m=200m A/V.In the circuit of Figure9,the input voltage,(V IN+−V IN−),is equal to IS x RS and the output voltage,V OUT,is equal to I O x R L.The transconductance,g m,of the INA138is200m A/V.The complete transfer function for the current measurement amplifier in this application is:V OUT=(I S)(R S)(200m A/V)(R L)The maximum differential input voltage for accurate measurements is0.5V,which produces a10m A output current.A differential input voltage of up to2V will not cause damage.Differential measurements(pins3and4) must be unipolar with a more-positive voltage applied to pin3.If a more-negative voltage is applied to pin3,the output current,I O,will be zero,but it will not cause damage.BASIC CONNECTIONFigure9shows the basic connection of the INA138.The input pins,V IN+and V IN−,should be connected as closely as possible to the shunt resistor to minimize any resistance in series with the shunt resistance.The output resistor,RL,is shown connected between pin1and ground.Best accuracy is achieved with the output voltage measured directly across R L.This is especially important in high-current systems where load current could flow in the ground connections,affecting the measurement accuracy.No power-supply bypass capacitors are required for stability of the INA138.However,applications with noisy or high-impedance power supplies may require decoupling capacitors to reject power-supply noise.Connect bypass capacitors close to the device pins.POWER SUPPLIESThe input circuitry of the INA138can accurately measure beyond its power-supply voltage,V+.For example,the V+power supply can be5V,whereas the load power supply voltage is up to+36V(or+60V with the INA168). The output voltage range of the OUT terminal,however,is limited by the lesser of the two voltages(see Output Voltage Range section).SELECTING R S AND R LThe value chosen for the shunt resistor,R S,depends on the application and is a compromise between small-signal accuracy and maximum permissible voltage loss in the measurement line.High values of R S provide better accuracy at lower currents by minimizing the effects of offset,while low values of RS minimize voltage loss in the supply line.For most applications,the best performance is attained with an R S value that provides a full-scale shunt voltage range of50mV to100mV.Maximum input voltage for accurate measurements is500 mV.R L is chosen to provide the desired full-scale output voltage.The output impedance of the INA138OUT terminal is very high which permits using values of R L up to500kΩwith excellent accuracy.The input impedance of any additional circuitry at the output should be much higher than the value of R L to avoid degrading accuracy.Some analog-to-digital(A/D)converters have input impedances that significantly affects measurement gain.The input impedance of the A/D converter can be included as part of the effective R L if its input can be modeled as a resistor to ground.Alternatively,an op amp can be used to buffer the A/D converter input.Figure9shows the recommended values of R L.6Submit Documentation Feedback Copyright©2003–2010,Texas Instruments IncorporatedINA138-Q1,IN168-Q1 SGLS174D–SEPTEMBER2003–REVISED DECEMBER2010Figure9.Basic Circuit ConnectionsOUTPUT VOLTAGE RANGEThe output of the INA138is a current,which is converted to a voltage by the load resistor,RL.The output current remains accurate within the compliance voltage range of the output circuitry.The shunt voltage and the input common-mode and power-supply voltages limit the maximum possible output swing.The maximum output voltage compliance is limited by the lower of the two equations below:V out max=(V+)−0.7V−(VIN+−V IN−)orV out max=V IN−−0.5V(whichever is lower)BANDWIDTHMeasurement bandwidth is affected by the value of the load resistor,R L.High gain produced by high values of R L yields a narrower measurement bandwidth(see the Typical Characteristics section).For widest possible bandwidth,keep the capacitive load on the output to a minimum.Reduction in bandwidth due to capacitive load is shown in the Typical Characteristics section.If bandwidth limiting(filtering)is desired,a capacitor can be added to the output(see Figure12).This will not cause instability.APPLICATIONSThe INA138is designed for current shunt measurement circuits,as shown in Figure9,but its basic function is useful in a wide range of circuitry.An engineer may find many unforeseen uses in measurement and level shifting circuits.A few ideas are illustrated in Figure10through Figure15.Copyright©2003–2010,Texas Instruments Incorporated Submit Documentation Feedback7INA138-Q1,IN168-Q1SGLS174D –SEPTEMBER 2003–REVISED DECEMBER 2010Figure 10.Buffering Output to Drive and A/DFigure 11.Output FilterFigure 12.Offsetting the Output Voltage8Submit Documentation Feedback Copyright ©2003–2010,Texas Instruments IncorporatedINA138-Q1,IN168-Q1 SGLS174D–SEPTEMBER2003–REVISED DECEMBER2010Figure13.Bipolar Current MeasurementCopyright©2003–2010,Texas Instruments Incorporated Submit Documentation Feedback9INA138-Q1,IN168-Q1SGLS174D–SEPTEMBER2003–REVISED Figure14.Bipolar Current Measurement Using Differential Input of A/D Converter10Submit Documentation Feedback Copyright©2003–2010,Texas Instruments Incorporated分销商库存信息:TIINA168QDBVRQ1INA168QPWRG4Q1。

瑜杰YuJieRM-168B万能电视机遥控器使用说明书精品文档16页

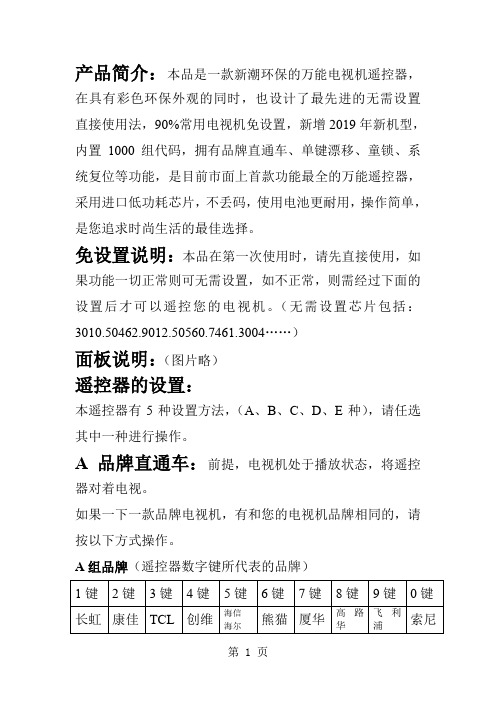

产品简介:本品是一款新潮环保的万能电视机遥控器,在具有彩色环保外观的同时,也设计了最先进的无需设置直接使用法,90%常用电视机免设置,新增2019年新机型,内置1000组代码,拥有品牌直通车、单键漂移、童锁、系统复位等功能,是目前市面上首款功能最全的万能遥控器,采用进口低功耗芯片,不丢码,使用电池更耐用,操作简单,是您追求时尚生活的最佳选择。

免设置说明:本品在第一次使用时,请先直接使用,如果功能一切正常则可无需设置,如不正常,则需经过下面的设置后才可以遥控您的电视机。

(无需设置芯片包括:3010.50462.9012.50560.7461.3004……)面板说明:(图片略)遥控器的设置:本遥控器有5种设置方法,(A、B、C、D、E种),请任选其中一种进行操作。

A品牌直通车:前提,电视机处于播放状态,将遥控器对着电视。

如果一下一款品牌电视机,有和您的电视机品牌相同的,请按以下方式操作。

A组品牌(遥控器数字键所代表的品牌)按住您电视机品牌相应的数字键不放(假如您家电视机是创维品牌,就按住4号键),5秒后指示灯开始闪烁,当电视机出现音量符号时,立即松开此键,设置结束。

※检查如有功能键不符,可重新设置。

B品牌直通车1+1:前提:让电视机处于播放状态,将遥控器对着电视如果一下十款品牌电视机,有和您电视机品牌相同的,请按以下方式操作。

B组品牌(遥控器数字键所代表的品牌)按住设置键不放,再按住代表您电视机品牌的数字键不放,(假如您家里电视机是金星牌,先按住设置键不放,再按住6号键),5秒后指示灯开始闪烁,当电视机出现音量符号时,立即松开两键,设置结束。

※检查如有功能键不符,可重新设置。

C“单键漂移”一键通数码搜索:前提:让电视机处于播放状态,约3秒指示灯亮起并闪烁,当电视机出现静音符号时,立即松开设置键,此时遥控器仍要对准电视机,当静音消失,即电视机出现音量符号时,立即按一下设置键,指示灯熄灭,设置结束。

※检查如有功能键不符,可重新设置D经典半自动搜索:前提:让电视机处于播放状态,将遥控器对着电视按住设置键不放,再按下电源键,指示灯亮起后松开两键,每按一下“音量+”(或“音量-”)键,遥控器会发射一次码,且指示灯会闪烁一次,反复此操作,直至电视机上出现音量符号时,立即停止操作,然后按一下设置键完成,此时指示灯熄灭,设置结束。

VGC401 中文手册

单通道控制器VGC 401使用说明书产品标识与INFICON联系时,请告知产品名牌上的信息。

为便于参考,现将名牌上的信息表示如下:有效性本说明书用于件号为398-010的产品。

件号(PN)可从产品名牌上看到。

本说明书件基于固件版号302-519-A。

如你的仪器工作与本文件的说明不符,请检查是否与上述固件版号(48)相符。

我们保留本说明书不事先通知的技术修改权。

全部尺寸均用毫米表示。

用途V GC401与INFICON生产的规管同时使用,用于真空系统的总压强测量。

全部产品必须按产品说明书使用。

供货范围1件单通道控制器1根电源电缆1根橡皮条2个橡皮脚4个凹槽螺丝4个塑料套管产品标识有效性用途供货范围1 安全1.1 使用符号1.2 人员要求1.3 一般安全规则1.4 责任与保修2 技术参数3 安装3.1 人员3.2 安装,设置3.2.1 机架安装3.2.2 安装在控制屏内3.2.3 用作桌上式仪器3.3 电源连接3.4 传感器连接3.5 控制器连接3.6 RS232接口连接4 运行4.1 面板4.2 VGC401的On和Off 4.3 工作模式4.4 测量模式4.5 参数模式4.5.1 参数4.6 测试模式4.6.1 参数4.6.2 测试程序5 维护6 故障查找7 检修8 附件9 储存10 废物处理附录A. 转换表提供的压强传感器B. 缺省参数C. 软件升级D. 文献E. 索引质量保证书参考在本说明书内的内容使用符号(XY)。

参考“文献”中的内容使用符号([Z])。

1.1 使用符号其它符号灯亮灯闪灯黑按此键(例:’para’键)不要按任何键.1.2 人员要求1.3 一般安全规则对于全部要进行的工作,必须遵守规章制度和采取必要的预防措施和考虑本说明书中的安全规则。

向所有其他用户通报安全信息。

1.4 责任与保修如最终用户或第三方发生以下情况,INFICON将不承担赔偿责任和保修将不再有效。

●不顾本说明书中的信息。

AD404M186RLB-5中文资料

ASCEND Semiconductor 4Mx4 EDO Data sheetDescriptionThe device CMOS Dynamic RAM organized as 4,194,304 words x 4 bits with extended data out access mode. It is fabricated with an advanced submicron CMOS technology and designed to operate from a single 3.3V oniy power supply. Low voltage operation is more suitable to be used on battery backup, portable elec-tronic application. lt is packaged in JEDEC standard 26/24-pin plastic SOJ or TSOP(II).Features• Single 3.3V(%) only power supply • High speed t RAC acess time: 50/60ns • Low power dissipation- Active mode : 432/396 mW (Mas) - Standby mode: 0.54 mW (Mas)• Extended - data - out(EDO) page mode access • I/O level: CMOS level (Vcc = 3.3V)• 2048 refresh cycle in 32 ms(Std.) or 128 ms(S-version)• 4 refresh modesh: - RAS only refresh- CAS - before - RAS refresh - Hidden refresh - Self-refresh(S-version)10±Pin Name FunctionA0-A10Address inputs- Row address - Column address - Refresh address DQ1~DQ4Data-in / data-out RAS Row address strobe CAS Column address strobe WE Write enable OE Output enable Vcc Power (+ 3.3V)VssGroundVCC 1DQ12DQ23DQ34DQ45VCC6891011 NC 12 WE 13A0 A117 A218 A319VSS RAS CAS OE A8A7A6A5A4VSSAD404M42VSPin Description Pin Configuration21222324 2526151416 A1026/24-PIN 300mil Plastic SOJA9VCC 1DQ12DQ23DQ34DQ45VCC6891011 NC 12 WE 13A0 A117 A218 A319VSS RAS CAS OE A8A7 A6A5 A4VSSAD404M42VT212223242526151416 A1026/24-PIN 300mil Plastic TSOP (ll)A9A0-A10A0-A10A0-A10WECASNO. 2 CLOCK GENERATORCOLUMN ADDRESS BUFFERS (11)REFRESH CONTROLLERREFRESH COUNTERBUFFERS (11)ADDRESS ROW NO. 1 CLOCK GENERATORA0RASA1A2A3A4A5A6A7A8CONTROLLOGICDATA-IN BUFFERDATA-OUT BUFFEROEDQ1.DQ4.COLUMN DECODER2048SENSE AMPLIFIERSI/O GATING2048x42048x2048x4MEMORY ARRAY2048R O W D E C O D E RVcc VssBlock DiagramA9A10TRUTH TABLENotes: 1. EARLY WRITE only.FUNCTIONRASCAS WE OE ADDRESSESDQ SNotesROW COL STANDBY H X X X X High-Z READL L H L ROW COL Data-Out WRITE: (EARLY WRITE )L L L X ROW COL Data-lnREAD WRITE L L ROW COL Data-Out,Data-ln EDO-PAGE-MODE READ1st Cycle L H L ROW COL Data-Out 2nd CycleL H L n/a COL Data-Out EDO-PAGE MODE WRITE1st CycleL L X ROW COL Data-In 2nd Cycle L L Xn/a COL Data-InEDO-PAGE-MODEREAD-WRITE 1st Cycle L ROW COL Data-Out, Data-In 2nd Cycle L n/a COL Data-Out, Data-In HIDDEN REFRESHREAD L H L ROW COL Data-Out WRITEL L X ROW COL Data-In 1RAS-ONLY REFRESH L H X X ROW n/a High-Z CBR REFRESHLHXXXHigh-ZH X →H L →L H →H L →H L →H L →H L →H L →H L →L H →H L →H L →L H→L H L →→L H L→→H L→Absolute Maximum RatingsRecommended DC Operating ConditionsCapacitanceTa = 25°C, V CC = 3.3V%, f = 1MHz Note: 1. Capacitance measured with effective capacitance measuring method. 2. RAS, CAS = V IH to disable Dout.ParameterSymbol Value Unit Voltage on any pin relative to Vss V T -0.5 to + 4.6V Supply voltage relative to Vss V CC -0.5 to + 4.6V Short circuit output current I OUT 50mA Power dissipation P D 1.0WOperating temperature T OPT 0 to + 70°C Storage temperatureT STG-55 to + 125°CParameter/Condition Symbol3.3 Volt VersionUnitMinTyp MaxSupply VoltageV CC 3.0 3.33.6V Input High Voltage, all inputs V IH 2.0-V CC + 0.3V Input Low Voltage, all inputsV IL-0.3-0.8VParameterSymbol Typ Max Unit Note Input capacitance (Address)C I1 -5pF 1Input capacitance (RAS, CAS, OE, WE)C I2-7pF 1Output capacitance(Data-in, Data-out)C I/O-7pF1, 210±DC Characteristics :(T a = 0 to 70°C, V CC = + 3.3V%, V SS = 0V)Parameter Symbol Test Conditions AD404M42V Unit Notes-5-6Min Max Min MaxOperating current I CC1RAS cyclingCAS, cyclingt RC = min-120-110mA1, 2Standby Current LowpowerS-versionI CC2LVTTL interfaceRAS, CAS = V IHDout = High-Z-0.5-0.5mACMOS interfaceRAS, -0.2VDout = High-Z-0.15-0.15mAStandardpowerversionLVTTL interfaceRAS, CAS = V IHDout = High-Z-2-2mACMOS interfaceRAS,-0.2VDout = High-Z-0.5-0.5mARAS- only refresh current I CC3RAS cycling, CAS = V IHt RC = min-120-110mA1, 2 EDO page mode current I CC4t PC = min-90-80mA1, 3CAS- before- RAS refresh current I CC5t RC = minRAS, CAS cycling-120-110mA1, 2Self- refresh current (S-Version)I CC8 - 550 - 55010±CAS V CC≥CAS V CC≥t RASS100µs≥µADC Characteristics :(T a = 0 to 70°C , V CC = +3.3V %, V SS = 0V)Notes:1. I CC is specified as an average current. It depends on output loading condition and cycle rate when the device is selected. I CC max is specified at the output open condition.2. Address can be changed once or less while RAS = V IL .3. For I CC4, address can be changed once or less within one EDO page mode cycle time.Parameter Symbol Test Conditions AD404M42VUnitNotes-5-6Min MaxMin MaxInput leakage current I LI + 0.3V -55-55Output leakage current I LO + 0.3V Dout = Disable -55-55Output high Voltage V OH I OH = -2mA 2.4- 2.4-V Output low voltage V OLI OL = +2mA-0.4-0.4V10±0V Vin V CC ≤≤µA 0V Vout V CC ≤≤µAAC Characteristics(T a = 0 to + 70°C , V cc = 3.3V %, V ss = 0V) *1, *2, *3, *4Test conditions• Output load: one TTL Load and 100pF (V CC = 3.3V %)• Input timing reference levels:V IH = 2.0V, V IL = 0.8V (V CC = 3.3V %)• Output timing reference levels:V OH = 2.0V, V OL = 0.8V10±10±10±Read, Write, Read- Modify- Write and Refresh Cycles (Common Parameters)ParameterSymbol AD404M42V UnitNotes-5-6Min MaxMin MaxRandom read or write cycle time t RC 84-104-ns RAS precharge timet RP 30-40-ns CAS precharge time in normal mode t CPN 10-10-ns RAS pulse width t RAS 50100006010000ns 5CAS pulse width t CAS 8100001010000ns 6Row address setup time t ASR 0-0-ns Row address hold time t RAH 8-10-ns Column address setup time t ASC 0-0-ns 7Column address hold time t CAH 8-10-ns RAS to CAS delay timet RCD 12371445ns 8RAS to column address delay time t RAD 10251230ns 9Column address to RAS lead time t RAL 25-30-ns RAS hold time t RSH 8-10-ns CAS hold timet CSH 38-40-ns CAS to RAS precharge time t CRP 5-5-ns 10OE to Din delay time t OED 12-15-ns Transition time (rise and fall)t T 150150ns 11Refresh periodt REF -32-32ms Refresh period (S- Version)t REF -128-128ms CAS to output in Low- Z t CLZ 0-0-ns CAS delay time from Din t DZC 0-0-ns OE delay time from Dint DZO-0-nsRead CycleWrite Cycle Parameter SymbolAD404M42V Unit Notes-5-6Min Max Min MaxAccess time from RAS t RAC-50-60ns12 Access time from CAS t CAC-14-15ns13, 14 Access time from column address t AA-25-30ns14, 15 Access time from OE t OEA-12-15nsRead command setup time t RCS0-0-ns7 Read command hold time to CAS t RCH0-0-ns10, 16 Read command hold time to RAS t RRH0-0-ns16 Output buffer turn-off time t OFF012015ns17 Output buffer turn-off time from OE t OEZ012015ns17Parameter SymbolAD404M42V Unit Notes -5-6Min Max Min MaxWrite command setup time t WCS0-0-ns7, 18 Write command hold time t WCH8-10-nsWrite command pulse width t WP8-10-nsWrite command to RAS lead time t RWL13-15-nsWrite command to CAS lead time t CWL8-10-nsData-in setup time t DS0-0-ns19 Data-in hold time t DH8-10-ns19 WE to Data-in delay t WED10-10-nsRead- Modify- Write CycleRefresh Cycle Parameter SymbolAD404M42V Unit Notes-5-6Min Max Min MaxRead-modify- write cycle time t RWC108-133-nsRAS to WE delay time t RWD64-77-ns18 CAS to WE dealy time t CWD26-32-ns18 Column address to WE delay time t AWD39-47-ns18 OE hold time from WE t OEH8-10-nsParameter SymbolAD404M42VUnit Notes -5-6Min Max Min MaxCAS setup time (CBR refresh) t CSR5-5-nsCAS hold time (CBR refresh)t CHR8-10-ns10 RAS precharge to CAS hold time t RPC5-5-ns7 RAS pulse width (self refresh)t RASS100-100-RAS precharge time (self refresh)t RPS90-110-nsCAS hold time (CBR self refresh)t CHS-50--50-nsWE setup time t WSR0-0-nsWE hold time t WHR10-10-nsµsEDO Page Mode CycleEDO Page Mode Read Modify Write CycleParameterSymbol AD404M42VUnit Notes-5-6Min MaxMin MaxEDO page mode cycle timet PC 20-25-ns EDO page mode CAS precharge time t CP 10-10-ns EDO page mode RAS pulse width t RASP 5010560105ns 20Access time from CAS precharge t CPA -30-35ns 10, 14RAS hold time from CAS precharge t CPRH 30-35-ns OE high hold time from CAS high t OEHC 5-5-ns OE high pulse widtht OEP 10-10-ns Data output hold time after CAS low t COH 5-5-ns Output disable delay from WEt WHZ 310310ns WE pulse width for output disable whenCAS hight WPZ7-7-nsParameterSymbol AD404M42V Unit Notes -5-6Min MaxMin MaxEDO page mode read- modify- write cycle CAS precharge to WE delay timet CPW 45-55-ns 10EDO page mode read- modify- write cycle timet PRWC56-68-nsNotes :1. AC measurements assume t T = 2ns.2. An initial pause of 100 is required after power up, and it followed by a minimum of eightinitialization cycles (RAS - only refresh cycle or CAS - before - RAS refresh cycle). If the internal refresh counter is used, a minimun of eight CAS - before - RAS refresh cycles are required.3. In delayed write or read-modify-write cycles, OE must disable output buffer prior to applying data to the device.4. All the V CC and V SS pins shall be supplied with the same voltages.5. t RAS (min) = t RWD (min)+t RWL (min)+t T in read-modify-write cycle.6. t CAS (min) = t CWD (min)+t CWL (min)+t T in read-modify-write cycle.7. t ASC (min), t RCS (min), t WCS (min), and t RPC are determined by the falling edge of CAS .8. t RCD (max) is specified as a reference point only, and t RAC (max) can be met with the t RCD (max) limit.Otherwise, t RAC is controlled exclusively by t CAC if t RCD is greater than the specified t RCD (max) limit. 9. t RAD (max) is specified as a reference point only, and t RAC (max) can be met with the t RAD (max) limit.Otherwise, t RAC is controlled exclusively by t AA if t RAD is greater than the specified t RAD (max) limit. 10. t CRP , t CHR , t RCH , t CPA and t CPW are determined by the rising edge of CAS .11. V IH (min) and V IL (max) are reference levels for measuring timing or input signals. Therefore, transitiontime is measured between V IH and V IL .12. Assumes that t RCD tRCD (max) and t RAD t RAD (max). If t RCD or t RAD is greater than the maximum recommended value shown in this table, t RAC exceeds the value shown. 13. Assumes that (max) and (max).14. Access time is determined by the maximum of t AA , t CAC , t CPA . 15. Assumes that (max) and (max). 16. Either t RCH or t RRH must be satisfied for a read cycle.17. t OFF (max) and t OEZ (max) define the time at which the output achieves the open circuit condition (highimpedance). t OFF is determined by the later rising edge of RAS or CAS.18. t WCS , t RWD , t CWD , and t AWD are not restrictive operating parameters. They are included in the datasheet as electrical characteristics only. If (min), the cycle is an early write cycle and the data out will remain open circuit (high impedance) throughout the entire cycle. If (min),(min), (min) and (min), the cycle is a read-modify-write and the data output will contain data read from the selected cell. If neither of the above sets of conditions is satisfied, the condition of the data output (at access time) is indeterminate.19. These parameters are referenced to CAS separately in an early write cycle and to WE edge in adelayed write or a read-modify-write cycle.20. t RASP defines RAS pulse width in EDO page mode cycles.µs ≤≤t RCD t RCD ≥t RADt RAD ≤t RCD t RCD ≤t RAD t RAD ≥t WCS t WCS ≥t RWD t RWD ≥t CWDt CWD ≥t AWD t AWD ≥t CPW t CPW≥Timing Waveforms• Read Cyclet RC t RASt RPtCRPtCPNtRRHtRCHt OEZ t OFF tOEA tCACt AAtRACt CLZD OUTtRCS t ASR tRAH tASC tCAH tRAD t RALtCAStRSH tRCDt TtCSHRASCASADDRESSWEDQ1~DQ4Note : = don’t care OEt OFFRowColumn= Invalid Dout•Early Write CycletRC t RASt RPt WCHt DSt DHt WCS t RALtCAStRSH tRCDt TtCSHRASCASWEDQ1~DQ4tCRPtASRtRAH tASCtCAH ADDRESSColumnRowtCPND INtRADt RAL• Delayed Write CycletRC t RASt RPt RWL t RCSt CAStRSH tRCDt TtCSHRASCAStASR tRAH tCAHADDRESSColumnRow tASC D INDQ1~DQ4WEtCRPtCPNt DHt DSt OEHt OEDOEt DSOPENt WPt CWL• Read - Modify - Write CycletRWC t RASt RPtRWDt WPtRADtRWL tCAStCWL tRCDt TtCPNRASCASWEtCRP t ASRtRAHtASCtCAHADDRESS Column RowDQ1~DQ4t DHt DSOEtRCStAWD tCWD D INt OEDt OEHt OEZt OEA t CAC t RACt AADQ1~DQ4D OUTOPENtDZCtDZO• EDO Page Mode Read CycletRASPtCPRHt RCStCAStRSH tRCDt OEAtCSHRASCAStASRtRAHtCAHADDRESStCASWEtCRPt CPOEDQ1~DQ4OPENtOEPD OUT 1t PCt CPtCAStCPNtCRPtRADtCAHtASCt ASCtCAHt ASCt RAL Row Column 1t OEAt OEHCtRRH tRCHt RACt AAt AAt AA t CPA t CPA t OEZt OFFt OFFt CACt OEZt CAC t CACt COHD OUT NWE OE Column 2Column N Rowt RPD OUT 2• EDO Page Mode Early Write CycletRASPtRPt WCSt CAStRSH tRCDRASCAStASRtRAHtCAHADDRESStCASWEt CPDQ1~DQ4t PCt CPt CAStCPNtCRP tCAH tASCtASC tCAH tASC Row Column 1t DS WE Column 2Column Nt WCH t WCS t WCH t WCS t WCHt DH t DS t DH t DS t DHD IN 1D IN 2D IN Nt TtCSH• EDO Page Mode Read-Early-Write Cyclet RASPtCPRHt RCStCAStRSH tRCDt OEAtCSHRASCAStASRtRAHtCAHADDRESStCASWEtCRPt CPOEDQ1~DQ4OPENtWEDt PCt CPtCAStCPNtCRPtRADtRAHtASCt ASCtCAHt ASCt RAL Row Column 1tWCStRCHt RACt AAt AAt CPA t DHt WHZt CACt CACt COHWE OE Column 2Column N Rowt RPt CAL tWCHDataDoutput 2Data Input NDataDoutput 1t DStCSH• EDO Page Mode Read-Modify-Write Cyclet RASPt CPRHt RCStCASt WP RASCASt ASRtRAHtCAHADDRESSt CASWEtRCDCPDQ1~DQ4tPRWCt CPtCAStCRPtRADtCAHtASCt ASCtCAH tASC Row Column 1tRWLtRCSt OEDt DZOt CAC WE OEt RPt RAL D OUT 2D OUT ND OUT 1tTt Column NColumn 2Column 1tRWD tAWD tCWDtCWLtRCStCWDtAWD tCPW tCWL tCPW tAWD tCWDtCWL t OEDt OEDt OEHt OEHt OEHt CAC t CAC t OEA t AAt RACt OEZt OEAt AA t CPAt OEZt OEAt AA t CPAt OEZ t DSt DHt WP t DSt DHt WP t DSt DHOPENOPENOPEN D IN 1D IN ND IN 2DQ1~DQ4t DZCt DZOt DZCt DZCt DZO• Read Cycle with WE Controlled Disablet WPZt RCStCAStRCDt TtCSHRASCASt ASRtRAHtCAHADDRESSColumnRow tASCD DQ1~DQ4WEt OEZt DSt WHZOEt RCH t OEA t CACt AAt RACt CLZOUTtRADRASADDRESSt RC t CRPt ASRt RAHt Tt RPCROWt OFFCAS t RASt RPOPENt CRPDQ1~DQ4RASt CSRt WSRt RPt T t RPCt OFFCAS t RASt RPOPENt CRPDQ1~DQ4t RPCt CHRt RASt RPt RCt RCt CHRt CSRt WHRt WSRt WHRWECAS-Before-RAS Refresh CycleRASWEt RPCt OFFt CSRt CHSt WSRCASt RASS t RPSOPENDQ1~DQ4t WHRHigh lmpedance• Hidden Refresh Cyclet RPt RASRASt RCDt CRPADDRESSWEt CHRt CASt RSHt RAHt ASRt ASCt CAHt RAL ROW t RCHt OEZCASDQ1~DQ4t Tt RCSD t RASt RASt RPt RPt RC t RCt RCt RADt RRHt OFF t OFFt OEA t CACt AAt RACCOlumnOUTOE(READ)(REFRESH)(REFRESH)Ordering informationAD404M42VSA-5• AD• Ascend Memory Product • 40 • Device Type• 4M4 • Density and Organization • 2• Refresh Rate, 2: 2K Refresh • V• T: 5V, V: 3.3V• S • Package Type (S : SOJ, T : TSOP II)• A• Version• 5• Speed (5: 50 ns, 6: 60 ns)Part Number Access time PackageAD404M42VSA-5AD404M42VSA-6AD404M42VTA-5AD404M42VTA-650 ns 60 ns 50 ns 60 ns300mil 26/24-Pin Plastic SOJTSOP IIPackaging information • 300 mil, 26/24-Pin Plastic SOJ• 300 mil, 26/24-Pin TSOP II。

AD420中文资料

AD420中文资料摘要:AD420是具有灵活串行数字接口的16住数模转换器,它带有SPI和Microwire总线接口,使用方便、性价比高。

介绍了AD420的引脚功能、电气特性,阐述了AD420与MSP430的接口技术,并给出了在MSP430控制下的实际应用电路及程序。

关键词:AD420;D/A转换;MSP430;电流环1 概述AD420是ADI公司生产的高精度、低功耗全数字电流环输出转换器。

AD420的输出信号可以是电流信号,也可以是电压信号。

其中电流信号的输出范围为4mA~20mA,0mA~20mA或0mA~24mA,具体可通过引脚RANGE SELECTl,RANGE SELECT2进行配置。

当需要输出电压信号时,它也能从一个隔离引脚提供电压输出,这时需外接一个缓冲放大器,可输出0V~5V,0V~10V,±5V 或±10V电压。

AD420具有灵活的串行数字接口(最大速率可达3.3 Mb/s),使用方便、性价比高、抑制干扰能力强,非常适合用于高精度远程控制系统。

AD420与单片机的接口方式有2种:3线制和异步制。

单片机系统通过AD420可实现连续的模拟量输出。

其主要特点如下:宽泛的电源电压范围为12 V~32 V,输出电压范围为0V~-2.5 V;带有3线模式的SPI或Microwire接口,可采集连续的模拟输入信号,采用异步模式时仅需少量的信号线;数据输出引脚可将多个AD420器件连接成菊链型;上电初始化时,其输出最小值为0 mA,4 mA或O V;具有异步清零引脚,可将输出复位至最小值(0mA、4 mA或0V);BOOST引脚可连接一个外部晶体管来吸收回路电流,降低功耗;只需外接少量的外部器件,就能达到较高的精度。

AD420采用24引脚SOIC和PDIP封装,表1是其引脚功能说明。

2 工作原理在AD420中,二阶调节器用于保持最小死区。

从调节器发出的单字节流控制开关电流源,两个连续的电阻电容装置进行过滤。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ASCEND Semiconductor 4Mx4 EDO Data sheetDescriptionThe device CMOS Dynamic RAM organized as 4,194,304 words x 4 bits with extended data out access mode. It is fabricated with an advanced submicron CMOS technology and designed to operate from a single 3.3V oniy power supply. Low voltage operation is more suitable to be used on battery backup, portable elec-tronic application. lt is packaged in JEDEC standard 26/24-pin plastic SOJ or TSOP(II).Features• Single 3.3V(%) only power supply • High speed t RAC acess time: 50/60ns • Low power dissipation- Active mode : 432/396 mW (Mas) - Standby mode: 0.54 mW (Mas)• Extended - data - out(EDO) page mode access • I/O level: CMOS level (Vcc = 3.3V)• 2048 refresh cycle in 32 ms(Std.) or 128 ms(S-version)• 4 refresh modesh: - RAS only refresh- CAS - before - RAS refresh - Hidden refresh - Self-refresh(S-version)10±Pin Name FunctionA0-A10Address inputs- Row address - Column address - Refresh address DQ1~DQ4Data-in / data-out RAS Row address strobe CAS Column address strobe WE Write enable OE Output enable Vcc Power (+ 3.3V)VssGroundVCC 1DQ12DQ23DQ34DQ45VCC6891011 NC 12 WE 13A0 A117 A218 A319VSS RAS CAS OE A8A7A6A5A4VSSAD404M42VSPin Description Pin Configuration21222324 2526151416 A1026/24-PIN 300mil Plastic SOJA9VCC 1DQ12DQ23DQ34DQ45VCC6891011 NC 12 WE 13A0 A117 A218 A319VSS RAS CAS OE A8A7 A6A5 A4VSSAD404M42VT212223242526151416 A1026/24-PIN 300mil Plastic TSOP (ll)A9A0-A10A0-A10A0-A10WECASNO. 2 CLOCK GENERATORCOLUMN ADDRESS BUFFERS (11)REFRESH CONTROLLERREFRESH COUNTERBUFFERS (11)ADDRESS ROW NO. 1 CLOCK GENERATORA0RASA1A2A3A4A5A6A7A8CONTROLLOGICDATA-IN BUFFERDATA-OUT BUFFEROEDQ1.DQ4.COLUMN DECODER2048SENSE AMPLIFIERSI/O GATING2048x42048x2048x4MEMORY ARRAY2048R O W D E C O D E RVcc VssBlock DiagramA9A10TRUTH TABLENotes: 1. EARLY WRITE only.FUNCTIONRASCAS WE OE ADDRESSESDQ SNotesROW COL STANDBY H X X X X High-Z READL L H L ROW COL Data-Out WRITE: (EARLY WRITE )L L L X ROW COL Data-lnREAD WRITE L L ROW COL Data-Out,Data-ln EDO-PAGE-MODE READ1st Cycle L H L ROW COL Data-Out 2nd CycleL H L n/a COL Data-Out EDO-PAGE MODE WRITE1st CycleL L X ROW COL Data-In 2nd Cycle L L Xn/a COL Data-InEDO-PAGE-MODEREAD-WRITE 1st Cycle L ROW COL Data-Out, Data-In 2nd Cycle L n/a COL Data-Out, Data-In HIDDEN REFRESHREAD L H L ROW COL Data-Out WRITEL L X ROW COL Data-In 1RAS-ONLY REFRESH L H X X ROW n/a High-Z CBR REFRESHLHXXXHigh-ZH X →H L →L H →H L →H L →H L →H L →H L →H L →L H →H L →H L →L H→L H L →→L H L→→H L→Absolute Maximum RatingsRecommended DC Operating ConditionsCapacitanceTa = 25°C, V CC = 3.3V%, f = 1MHz Note: 1. Capacitance measured with effective capacitance measuring method. 2. RAS, CAS = V IH to disable Dout.ParameterSymbol Value Unit Voltage on any pin relative to Vss V T -0.5 to + 4.6V Supply voltage relative to Vss V CC -0.5 to + 4.6V Short circuit output current I OUT 50mA Power dissipation P D 1.0WOperating temperature T OPT 0 to + 70°C Storage temperatureT STG-55 to + 125°CParameter/Condition Symbol3.3 Volt VersionUnitMinTyp MaxSupply VoltageV CC 3.0 3.33.6V Input High Voltage, all inputs V IH 2.0-V CC + 0.3V Input Low Voltage, all inputsV IL-0.3-0.8VParameterSymbol Typ Max Unit Note Input capacitance (Address)C I1 -5pF 1Input capacitance (RAS, CAS, OE, WE)C I2-7pF 1Output capacitance(Data-in, Data-out)C I/O-7pF1, 210±DC Characteristics :(T a = 0 to 70°C, V CC = + 3.3V%, V SS = 0V)Parameter Symbol Test Conditions AD404M42V Unit Notes-5-6Min Max Min MaxOperating current I CC1RAS cyclingCAS, cyclingt RC = min-120-110mA1, 2Standby Current LowpowerS-versionI CC2LVTTL interfaceRAS, CAS = V IHDout = High-Z-0.5-0.5mACMOS interfaceRAS, -0.2VDout = High-Z-0.15-0.15mAStandardpowerversionLVTTL interfaceRAS, CAS = V IHDout = High-Z-2-2mACMOS interfaceRAS,-0.2VDout = High-Z-0.5-0.5mARAS- only refresh current I CC3RAS cycling, CAS = V IHt RC = min-120-110mA1, 2 EDO page mode current I CC4t PC = min-90-80mA1, 3CAS- before- RAS refresh current I CC5t RC = minRAS, CAS cycling-120-110mA1, 2Self- refresh current (S-Version)I CC8 - 550 - 55010±CAS V CC≥CAS V CC≥t RASS100µs≥µADC Characteristics :(T a = 0 to 70°C , V CC = +3.3V %, V SS = 0V)Notes:1. I CC is specified as an average current. It depends on output loading condition and cycle rate when the device is selected. I CC max is specified at the output open condition.2. Address can be changed once or less while RAS = V IL .3. For I CC4, address can be changed once or less within one EDO page mode cycle time.Parameter Symbol Test Conditions AD404M42VUnitNotes-5-6Min MaxMin MaxInput leakage current I LI + 0.3V -55-55Output leakage current I LO + 0.3V Dout = Disable -55-55Output high Voltage V OH I OH = -2mA 2.4- 2.4-V Output low voltage V OLI OL = +2mA-0.4-0.4V10±0V Vin V CC ≤≤µA 0V Vout V CC ≤≤µAAC Characteristics(T a = 0 to + 70°C , V cc = 3.3V %, V ss = 0V) *1, *2, *3, *4Test conditions• Output load: one TTL Load and 100pF (V CC = 3.3V %)• Input timing reference levels:V IH = 2.0V, V IL = 0.8V (V CC = 3.3V %)• Output timing reference levels:V OH = 2.0V, V OL = 0.8V10±10±10±Read, Write, Read- Modify- Write and Refresh Cycles (Common Parameters)ParameterSymbol AD404M42V UnitNotes-5-6Min MaxMin MaxRandom read or write cycle time t RC 84-104-ns RAS precharge timet RP 30-40-ns CAS precharge time in normal mode t CPN 10-10-ns RAS pulse width t RAS 50100006010000ns 5CAS pulse width t CAS 8100001010000ns 6Row address setup time t ASR 0-0-ns Row address hold time t RAH 8-10-ns Column address setup time t ASC 0-0-ns 7Column address hold time t CAH 8-10-ns RAS to CAS delay timet RCD 12371445ns 8RAS to column address delay time t RAD 10251230ns 9Column address to RAS lead time t RAL 25-30-ns RAS hold time t RSH 8-10-ns CAS hold timet CSH 38-40-ns CAS to RAS precharge time t CRP 5-5-ns 10OE to Din delay time t OED 12-15-ns Transition time (rise and fall)t T 150150ns 11Refresh periodt REF -32-32ms Refresh period (S- Version)t REF -128-128ms CAS to output in Low- Z t CLZ 0-0-ns CAS delay time from Din t DZC 0-0-ns OE delay time from Dint DZO-0-nsRead CycleWrite Cycle Parameter SymbolAD404M42V Unit Notes-5-6Min Max Min MaxAccess time from RAS t RAC-50-60ns12 Access time from CAS t CAC-14-15ns13, 14 Access time from column address t AA-25-30ns14, 15 Access time from OE t OEA-12-15nsRead command setup time t RCS0-0-ns7 Read command hold time to CAS t RCH0-0-ns10, 16 Read command hold time to RAS t RRH0-0-ns16 Output buffer turn-off time t OFF012015ns17 Output buffer turn-off time from OE t OEZ012015ns17Parameter SymbolAD404M42V Unit Notes -5-6Min Max Min MaxWrite command setup time t WCS0-0-ns7, 18 Write command hold time t WCH8-10-nsWrite command pulse width t WP8-10-nsWrite command to RAS lead time t RWL13-15-nsWrite command to CAS lead time t CWL8-10-nsData-in setup time t DS0-0-ns19 Data-in hold time t DH8-10-ns19 WE to Data-in delay t WED10-10-nsRead- Modify- Write CycleRefresh Cycle Parameter SymbolAD404M42V Unit Notes-5-6Min Max Min MaxRead-modify- write cycle time t RWC108-133-nsRAS to WE delay time t RWD64-77-ns18 CAS to WE dealy time t CWD26-32-ns18 Column address to WE delay time t AWD39-47-ns18 OE hold time from WE t OEH8-10-nsParameter SymbolAD404M42VUnit Notes -5-6Min Max Min MaxCAS setup time (CBR refresh) t CSR5-5-nsCAS hold time (CBR refresh)t CHR8-10-ns10 RAS precharge to CAS hold time t RPC5-5-ns7 RAS pulse width (self refresh)t RASS100-100-RAS precharge time (self refresh)t RPS90-110-nsCAS hold time (CBR self refresh)t CHS-50--50-nsWE setup time t WSR0-0-nsWE hold time t WHR10-10-nsµsEDO Page Mode CycleEDO Page Mode Read Modify Write CycleParameterSymbol AD404M42VUnit Notes-5-6Min MaxMin MaxEDO page mode cycle timet PC 20-25-ns EDO page mode CAS precharge time t CP 10-10-ns EDO page mode RAS pulse width t RASP 5010560105ns 20Access time from CAS precharge t CPA -30-35ns 10, 14RAS hold time from CAS precharge t CPRH 30-35-ns OE high hold time from CAS high t OEHC 5-5-ns OE high pulse widtht OEP 10-10-ns Data output hold time after CAS low t COH 5-5-ns Output disable delay from WEt WHZ 310310ns WE pulse width for output disable whenCAS hight WPZ7-7-nsParameterSymbol AD404M42V Unit Notes -5-6Min MaxMin MaxEDO page mode read- modify- write cycle CAS precharge to WE delay timet CPW 45-55-ns 10EDO page mode read- modify- write cycle timet PRWC56-68-nsNotes :1. AC measurements assume t T = 2ns.2. An initial pause of 100 is required after power up, and it followed by a minimum of eightinitialization cycles (RAS - only refresh cycle or CAS - before - RAS refresh cycle). If the internal refresh counter is used, a minimun of eight CAS - before - RAS refresh cycles are required.3. In delayed write or read-modify-write cycles, OE must disable output buffer prior to applying data to the device.4. All the V CC and V SS pins shall be supplied with the same voltages.5. t RAS (min) = t RWD (min)+t RWL (min)+t T in read-modify-write cycle.6. t CAS (min) = t CWD (min)+t CWL (min)+t T in read-modify-write cycle.7. t ASC (min), t RCS (min), t WCS (min), and t RPC are determined by the falling edge of CAS .8. t RCD (max) is specified as a reference point only, and t RAC (max) can be met with the t RCD (max) limit.Otherwise, t RAC is controlled exclusively by t CAC if t RCD is greater than the specified t RCD (max) limit. 9. t RAD (max) is specified as a reference point only, and t RAC (max) can be met with the t RAD (max) limit.Otherwise, t RAC is controlled exclusively by t AA if t RAD is greater than the specified t RAD (max) limit. 10. t CRP , t CHR , t RCH , t CPA and t CPW are determined by the rising edge of CAS .11. V IH (min) and V IL (max) are reference levels for measuring timing or input signals. Therefore, transitiontime is measured between V IH and V IL .12. Assumes that t RCD tRCD (max) and t RAD t RAD (max). If t RCD or t RAD is greater than the maximum recommended value shown in this table, t RAC exceeds the value shown. 13. Assumes that (max) and (max).14. Access time is determined by the maximum of t AA , t CAC , t CPA . 15. Assumes that (max) and (max). 16. Either t RCH or t RRH must be satisfied for a read cycle.17. t OFF (max) and t OEZ (max) define the time at which the output achieves the open circuit condition (highimpedance). t OFF is determined by the later rising edge of RAS or CAS.18. t WCS , t RWD , t CWD , and t AWD are not restrictive operating parameters. They are included in the datasheet as electrical characteristics only. If (min), the cycle is an early write cycle and the data out will remain open circuit (high impedance) throughout the entire cycle. If (min),(min), (min) and (min), the cycle is a read-modify-write and the data output will contain data read from the selected cell. If neither of the above sets of conditions is satisfied, the condition of the data output (at access time) is indeterminate.19. These parameters are referenced to CAS separately in an early write cycle and to WE edge in adelayed write or a read-modify-write cycle.20. t RASP defines RAS pulse width in EDO page mode cycles.µs ≤≤t RCD t RCD ≥t RADt RAD ≤t RCD t RCD ≤t RAD t RAD ≥t WCS t WCS ≥t RWD t RWD ≥t CWDt CWD ≥t AWD t AWD ≥t CPW t CPW≥Timing Waveforms• Read Cyclet RC t RASt RPtCRPtCPNtRRHtRCHt OEZ t OFF tOEA tCACt AAtRACt CLZD OUTtRCS t ASR tRAH tASC tCAH tRAD t RALtCAStRSH tRCDt TtCSHRASCASADDRESSWEDQ1~DQ4Note : = don’t care OEt OFFRowColumn= Invalid Dout•Early Write CycletRC t RASt RPt WCHt DSt DHt WCS t RALtCAStRSH tRCDt TtCSHRASCASWEDQ1~DQ4tCRPtASRtRAH tASCtCAH ADDRESSColumnRowtCPND INtRADt RAL• Delayed Write CycletRC t RASt RPt RWL t RCSt CAStRSH tRCDt TtCSHRASCAStASR tRAH tCAHADDRESSColumnRow tASC D INDQ1~DQ4WEtCRPtCPNt DHt DSt OEHt OEDOEt DSOPENt WPt CWL• Read - Modify - Write CycletRWC t RASt RPtRWDt WPtRADtRWL tCAStCWL tRCDt TtCPNRASCASWEtCRP t ASRtRAHtASCtCAHADDRESS Column RowDQ1~DQ4t DHt DSOEtRCStAWD tCWD D INt OEDt OEHt OEZt OEA t CAC t RACt AADQ1~DQ4D OUTOPENtDZCtDZO• EDO Page Mode Read CycletRASPtCPRHt RCStCAStRSH tRCDt OEAtCSHRASCAStASRtRAHtCAHADDRESStCASWEtCRPt CPOEDQ1~DQ4OPENtOEPD OUT 1t PCt CPtCAStCPNtCRPtRADtCAHtASCt ASCtCAHt ASCt RAL Row Column 1t OEAt OEHCtRRH tRCHt RACt AAt AAt AA t CPA t CPA t OEZt OFFt OFFt CACt OEZt CAC t CACt COHD OUT NWE OE Column 2Column N Rowt RPD OUT 2• EDO Page Mode Early Write CycletRASPtRPt WCSt CAStRSH tRCDRASCAStASRtRAHtCAHADDRESStCASWEt CPDQ1~DQ4t PCt CPt CAStCPNtCRP tCAH tASCtASC tCAH tASC Row Column 1t DS WE Column 2Column Nt WCH t WCS t WCH t WCS t WCHt DH t DS t DH t DS t DHD IN 1D IN 2D IN Nt TtCSH• EDO Page Mode Read-Early-Write Cyclet RASPtCPRHt RCStCAStRSH tRCDt OEAtCSHRASCAStASRtRAHtCAHADDRESStCASWEtCRPt CPOEDQ1~DQ4OPENtWEDt PCt CPtCAStCPNtCRPtRADtRAHtASCt ASCtCAHt ASCt RAL Row Column 1tWCStRCHt RACt AAt AAt CPA t DHt WHZt CACt CACt COHWE OE Column 2Column N Rowt RPt CAL tWCHDataDoutput 2Data Input NDataDoutput 1t DStCSH• EDO Page Mode Read-Modify-Write Cyclet RASPt CPRHt RCStCASt WP RASCASt ASRtRAHtCAHADDRESSt CASWEtRCDCPDQ1~DQ4tPRWCt CPtCAStCRPtRADtCAHtASCt ASCtCAH tASC Row Column 1tRWLtRCSt OEDt DZOt CAC WE OEt RPt RAL D OUT 2D OUT ND OUT 1tTt Column NColumn 2Column 1tRWD tAWD tCWDtCWLtRCStCWDtAWD tCPW tCWL tCPW tAWD tCWDtCWL t OEDt OEDt OEHt OEHt OEHt CAC t CAC t OEA t AAt RACt OEZt OEAt AA t CPAt OEZt OEAt AA t CPAt OEZ t DSt DHt WP t DSt DHt WP t DSt DHOPENOPENOPEN D IN 1D IN ND IN 2DQ1~DQ4t DZCt DZOt DZCt DZCt DZO• Read Cycle with WE Controlled Disablet WPZt RCStCAStRCDt TtCSHRASCASt ASRtRAHtCAHADDRESSColumnRow tASCD DQ1~DQ4WEt OEZt DSt WHZOEt RCH t OEA t CACt AAt RACt CLZOUTtRADRASADDRESSt RC t CRPt ASRt RAHt Tt RPCROWt OFFCAS t RASt RPOPENt CRPDQ1~DQ4RASt CSRt WSRt RPt T t RPCt OFFCAS t RASt RPOPENt CRPDQ1~DQ4t RPCt CHRt RASt RPt RCt RCt CHRt CSRt WHRt WSRt WHRWECAS-Before-RAS Refresh CycleRASWEt RPCt OFFt CSRt CHSt WSRCASt RASS t RPSOPENDQ1~DQ4t WHRHigh lmpedance• Hidden Refresh Cyclet RPt RASRASt RCDt CRPADDRESSWEt CHRt CASt RSHt RAHt ASRt ASCt CAHt RAL ROW t RCHt OEZCASDQ1~DQ4t Tt RCSD t RASt RASt RPt RPt RC t RCt RCt RADt RRHt OFF t OFFt OEA t CACt AAt RACCOlumnOUTOE(READ)(REFRESH)(REFRESH)Ordering informationAD404M42VSA-5• AD• Ascend Memory Product • 40 • Device Type• 4M4 • Density and Organization • 2• Refresh Rate, 2: 2K Refresh • V• T: 5V, V: 3.3V• S • Package Type (S : SOJ, T : TSOP II)• A• Version• 5• Speed (5: 50 ns, 6: 60 ns)Part Number Access time PackageAD404M42VSA-5AD404M42VSA-6AD404M42VTA-5AD404M42VTA-650 ns 60 ns 50 ns 60 ns300mil 26/24-Pin Plastic SOJTSOP IIPackaging information • 300 mil, 26/24-Pin Plastic SOJ• 300 mil, 26/24-Pin TSOP II。