IDT7204L35D中文资料

35 SERIES HN35 PRO 美国易观技术全功能通道数NVR系列商品说明书

35 SERIES HN35 PROFULL Y-FEATURED NVRS• View 16/32/64 channels simultaneously with synchronized real-time playback on your monitor (depending on your model) .32/64CH support 16 channels simultaneously with synchronizedreal-time playback.• Up to 8 MP (4K) resolution live view and playback.• Supports H.265 HEVC, H.264, Smart Codec.• Notify on triggering built-in video analytic alarms from 35S cameras: Crowd, Multi Loitering, Intrusion, Tampering, Motion and SmartMotion Detection (SMD).• Two-way audio/push notification.• Supports up to 16 alarm input channels and 6 alarm relay output channels. (8 SATA).• Maximum incoming bandwidth is 400 Mbps,and Maximum outgoing bandwidth is 400 Mbps.*• Supports redundancy Failover N+1 (Maximum N =10).• Supports people counter feature to accurately automate the gathering of data relating to people entering and exiting a certainarea.DYNAMIC, ACCESSIBLE MONITORING• Global P2P/TUTK service with reliable connection and mobile apps for both Apple® and Android™ devices for anytime, anywhere access.• P2P integration to manage remote configuration and firmware updating.CONVENIENT, FLEXIBLE, REDUNDANT STORAGE OPTIONS• Internal storage supports 8 HDDs expandable up to 80 TB (8 bays) of internal storage.• Store video clips and snapshots to external storage, such as USB device on local side or PC client on web side.• Supports RAID** 1/5/6 storage options.EASY TO SETUP AND USE• Plug and play feature together with 35 Series cameras for rapid and simple setup.• Dual network ports, making it easy to connect local IPCs and remote control.• Intuitive NVR design, quick installation wizard and easy-to-understand installation guide for fast and easy setup.Introducing Honeywell’s 35 Series HN35 PRO NVRs, a robustly-featured, cost-effective, NDAA Section 889 compliant NVR solution delivering 4K HD (UHD) video resolution perfect for small/medium businesses and enterprises. Choose a 16 , 32 or 64 channelNVR with multiple hard drive options and up to 80 TB (8 bays) of internal storage with fail-over and RAID redundancy features fora flexible and reliable solution that grows with your business.• H.265/H.264• HDMI/VGAsimultaneous videooutput• USB ports support Keyboard andMouse• Supports recording avideo clip of events fordistribution• Supports uploadingstill images at the timeof the event throughemail• Supports visual orauditory notificationssuch as a flashinglight, bell, or siren• Support RAID ** 1/5/6 • Supports alarm inputand alarm output• Supports sendingevents through email,FTP, alarm out or pushnotification• Configurable toautomatically detectand respond tomotion in the scene,alarm inputs, andnetwork failure ortamperingFEATURES SECURE AND COMPLIANT SOLUTION• For use as part of video systems which comply with NDAA Section 889.• The TPM (Trusted Platform Module) provides end-to-end stream and command encryption through integrated cryptographic keys.• Together with 35 Series cameras, provides an end-to-end encrypted solution with video streaming and control encryptedbetween NVR and web client / viewer / mobile app.• PCI-DSS compliance.• Secure boot feature combined with Honeywell cybersecurity standards helps ensure data protection.•Support secure NTP.HN351604xxR/HN353204xxNR/HN356404xxNRHN356408xxDRHN353208xxNR/HN356408xxNR16 / 32 /64 Ch 4K Embedded NVR*400Mbps is achievable when video streams are not encrypted. It is needed to split the HDD array into at least two equal storage groups.* * For optimum performance, RAID functionality requires models with Enterprise Hard Disk Drives.35 SERIES HN35 PRO, 16 / 32 / 64 CH 4KHard Disk Drives.**400Mbps is achievable when video streams are not encrypted. It is needed to split the HDD array into at least two equal storage groups.SYSTEM DIAGRAMHN351604XXR1. PoE Ports2. Audio Out3. Audio In4. eSATA Port5. LAN Port6. WAN Port7. RS232 Port8. HDMI 2 Port9. HDMI 1 Port 10. VGA Port 11. USB Port 12. Alarm Input/Output 13. Power Input 14. Power SwitchHN353204xxNR1. Alarm Input/Output2. Audio Out3. Audio In4. LAN Port5. WAN Port6. HDMI 2 Port7.VGA Port8. HDMI 1 Port9. RS232 Port 10. USB Port 11. eSATA Port 12. Power Input 13. Power SwitchHN356404xxNR1. Audio Out2. Audio In3. LAN Port4. WAN Port5. HDMI 1 Port6. HDMI 2 Port7.VGA Port8. RS232 Port9. USB Port 10. eSATA Port 11. Alarm Input/Output 12. Power Input 13. Power SwitchHN353208xxNR/HN356408xxNRHN356408xxDR (Dual Power Supply)1. Audio Out2. Audio In3. LAN Port4. WAN Port5. HDMI 1 Port6. HDMI 2 Port7.VGA Port8. RS232 Port9. USB Port 10. eSATA Port 11. Alarm Input/Output 12. Power Input 13. Power Switch1. Audio Out2. Audio In3. LAN Port4. WAN Port5. HDMI 1 Port6. HDMI 2 Port7.VGA Port8. RS232 Port9. USB Port 10. eSATA Port 11. Alarm Input/Output 12. Power Switch 13. Power InputSYSTEM DIAGRAMHN351604xxR/HN353204xxNR/HN356404xxNR”))”)DIMENSIONSDIMENSIONS HN353208xxNR/HN356408xxNRFor More Information/uk /securityHoneywell Commercial Security Building 5 Carlton ParkKing Edward Avenue Narborough, LeicesterLE19 0ALTel: +44 (0)1163 500714 HBT-SEC-HN35ENVRPRO-01-UK(0923)DS-Y© 2023 Honeywell International Inc.ONVIF and the ONVIF logo are trademarks of ONVIF Inc.HEVC Advance logo is a trademark of HEVC AdvanceHoneywell reserves the right, without notification, tomake changes in product design or specifications.HN35 16 04 00 xR16 = 16 CHANNELS32 = 32 CHANNELS64=64 CHANNELS00 = 0 TB35 = 35 SERIES04 = 4 SATA08= 8 SATA x=N, N means non-PoEx=D, D means redundant power supply R Suffix = Fail-over and RAID software*PART NUMBER LOOKUP* For optimum performance, RAID functionality requires models with Enterprise Hard Disk Drives.。

聚四氟压力表垫型号

237 238 239 240 241 242 243 244 245 246 247 248 249 250 251 252 253 254 255 256 257 258 259 260 261 262 263 264 265 266 267 268

269 270 271 272 273 274 275 276 277 278 279 280 281 282 283 284 285 286 287 288 289 290 291 292

刘涛

2012.5.8 王时睿

2012.5.8 刘涛

低温低压用 高温高压用 铠装温度计用 铠装温度计用 变送器用 双金属温度表用 双金属温度表用 双金属温度表用

办人:

办人:

生技部:

负责人:

经办人:

92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107

108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139

表

2012年 05月 01日

备注

紧急计划

月计划

紧急计划 紧急计划 月计划 锅炉定排电动门 锅炉定排电动门 #1吸收塔pH1 #11脱硫系统#1-A石膏排出泵出口PH

钢灰库提升机

时间 2012.5.8 2012.5.8

申报人

王时睿

2012.5.2

2012.5.2 2012.5.2 2012.5.2

21

聚四氟垫

22

聚四氟垫

24

LPD64 产品技术资料说明书

6系列紧凑型数字化仪模数转换器LPD64产品技术资料用数字说话输入通道4 个 SMA输入每个 SMA 输入都支持模拟、频谱(使用 DDC)或同时支持两者每条通道的性能采样率: 25GS/s 带宽: DC ~ 8 GHz(选配)垂直分辨率: 12 位ADC 实时 2 GHz DDC(选配)记录长度: 125 M 点 (标配), 250 M 点(选配)同类最低的噪声同类最高的ENOB同类最优秀的通道间隔离度实时数字下变频器(DDC)已获专利的时域和频域单独控制功能高达 2 GHz 捕获带宽(选配)IQ 数据传送到 PC 进行分析(选配)频率相对于时间关系图、相位相对于时间关系图、幅度相对于时间关系图 (选配)杰出的低噪声、垂直分辨率和精度全新 TEK061 前端 ASICs实现了低输入噪声噪声 @ 1mV/div: 54.8 uV @ 1GHz 输入范围: 10mV ~ 10 V满刻度DC 增益精度: +/-1.0%, 在所有 >1 mV/div的增益设置下有效位数(ENOB):8.2 位 @ 1GHz 7.6 位 @ 2.5GHz 7.25 位 @ 4GHz 6.8 位 @ 6GHz 6.5 位 @ 8 GHz远程通信和连接以太网 10/100/1000端口USB 3.0 设备端口 (USBTMC),高达 800Mb/s LXI 1.5 认证(VXI-11)使用 e*Scope 简便地实现远程访问,只需在浏览器中输入仪器的 IP地址。

屡获大奖的用户界面驱动程序: IVI-C, IVI-COM,LabVIEW支持 VISA, MATLAB, Python, C/C++/C#, 套接字测量分析36种标准测量抖动测量(选配)DDR 测量(选配)功率测量 (选配)操作系统封闭 Linux 嵌入式操作系统 (标配)安全和解密 (选项6-SEC)密码保护所有用户可接入的端口给模数转换器上锁,防止在仪器上存储用户数据满足顶级机密和高安全环境需求外观尺寸2U (3.5 英寸/89 mm) 高,开箱即可装入机架(标配)17 英寸(432 mm)宽适合标准 24 - 32 英寸(610 - 813 mm)机架机架环境中左右通风产品技术资料由于最低的输入噪声和高达 8 GHz 的模拟带宽,6 系列紧凑型数字化仪模数转换器 LPD64 为在紧凑的 2U 机架空间中分析和调试信号提供了最佳的信号保真度。

DTSD720-L 三相导轨式电能表使用说明书V1.1

参数项 通信参数 普通参数

描述 通信地址、波特率、校验位 密码、轮显模式、日期、时间、电能清零

其它参数设置和测量统计数据读取都通过通信实ห้องสมุดไป่ตู้。

部分显示页面示例:

数据显示页面

正向有功总电能(kWh)

反向无功总电能(kvarh)

正向有功尖电能(kWh)

正向有功谷电能(kWh)

平均电压(V)

平均电流(A)

总有功功率(W / kW)

DTSD720-L 电子式电能表

DTSD720-L 采用 35mm 标准导轨式安装方式,如下图:

35mm

导轨

3.3 接线图

图 3 安装图

固定卡

DTSD720-L 支持直接接入和经电流互感器(CT)接入两种接入方式,如下图:

图 4 直接接入 3

DTSD720-L 电子式电能表

图 5 经 CT 接入

3.4 安装注意事项

版本 V1.1 2012.9

DTSD720-L 电子式电能表

1 概述

1.1 产品特点

DTSD720-L 电子式电能表是科陆电子根据多年的电表设计经验,推出的一款全新 的微型三相电能表,体积小巧,安装方便,可轻松放入各类配电箱和配电柜,集成工业 通信接口,可轻松实现与各种智能配电系统的集成,极大地方便了能效管理。

总无功功率(var / kvar)

自带实时时钟,具有复费率功能,可设置 4 个时区,每个时区可设 10 个时段,并 按尖、峰、平、谷四种费率累计、存储电能。

具有接点、光电两种电能脉冲输出(有功、无功),用于校表和远程电能采集。 可使用面板和通信两种方式对装置参数进行设置。 装置使用 RS485 通信,波特率最高可达 9600bps。

EDX720(中文)-1

Pb EDX-700HS2 EDX-720

Cd EDX-700HS2 EDX-720

EDX-720の特長 の

硬件方面( )~两硬件组合使用使检测灵敏度大大提高~ )~两硬件 检测灵敏度大大提高 硬件方面(3)~两硬件组合使用使检测灵敏度大大提高~ 与过去机型检测灵敏度的比较 去机型检测灵敏度的比较 检测灵敏度的比

岛津最新能量色散型X射线荧光分析 线荧光分析 装置登场 装置登场

EDXEDX-720介绍

分析计测事业部 分析计测事 计测

X线/表面ビジネスユニット课 ビジネスユニット课 表面ビジネスユニット

能量色散型X 线荧光分析装置的特 能量色散型X射线荧光分析装置的特长 光分析装置的特长 无需前 非破坏・ 无需前处理,非破坏・迅速分析 分~5分) 非破坏 迅速分析(1分 分 定的元素范围 的全部元素 测定的元素范围广( 从Na~U的全部元素) ~ 的全部元素) 定的浓度范围 测定的浓度范围广( 从数 ppm~100 %) ~ 可定性分析 行无标样简 标样简易分析 可进行无标样简易分析 可用标样对 标样对被 可用标样对被测物进行精密定量分析 近年来被广泛应用的膜厚测定法 近年来被广泛应用的膜厚测定法 可在大气环境下进 可在大气环境下进行测定 全元素同 可对全元素同时进行测定 外型小巧,电压为 V电源 电压为100V 外型小巧 电压为

No.

D4DL中文资料

Compact Guard-locking Interlock Safety Door SwitchD4DLPolymer housing, IP65, and slow-action contacts with positive opening →.2 versions•Mechanical lock/Solenoid release •Solenoid lock/Mechanical releaseRotatable operating head provides four possible key entry slots.Incorporates an indicator that shows operation status at a glance.Double-insulation structure requires no grounding terminals. (with mark)Three types of Operation Key are available:•Horizontal mounting •Vertical mounting•Angle-adjustable vertical mounting Safety StandardsConformity:Machinery Directive, Low-voltage Directive, EN1088, SUV A Approval:Note:Approval for CSA C22.2 No. 14 is authorized by c mark.ESwitchesD4DL-jjjj -j123451.Conduit Size (2-conduit)1:Pg13.52:G 1/22.Built-in Switch (with Safety Switch and Lock Monitor Switch Contacts)C:1NC/1NO slow-action contacts plus 1NC slow-actioncontactD:2NC slow-action contacts plus 1NC slow-action contact 3.Head Mounting Direction F:Front4.Door Lock and ReleaseA:Mechanical lock / 24-VDC solenoid release (see note)B:Mechanical lock / 110-V AC solenoid release C:Mechanical lock / 230-V AC solenoid releaseG:24-VDC solenoid lock / mechanical release (see note)H:110-V AC solenoid lock / mechanical release J:230-V AC solenoid lock / mechanical release 5.IndicatorB:10 to 115 V AC/VDC (with orange LED indicator)E:100 to 250 V AC (with orange neon lamp indicator)Operation KeysD4DS-K j11.Key T ype1:Horizontal mounting 2:V ertical mounting3:Horizontal-adjustable vertical mounting5:V ertical/Horizontal-adjustable vertical mountingNote:Models marked with “∗” are recommendedHorizontal mountingTÜV (EN60947-5-1)Note:Use a 10-A fuse type gI or gG as a short-circuit protection device that conforms to IEC269.UL/CSA (UL508, CSA C22.2 No. 14)A300CharacteristicsNote: 1.The above values are initial values.2.Although the switch box is protected from dust or water penetration, do not use the D4DL in places where foreign material maypenetrate through the key hole on the head, otherwise switch damage or malfunctioning may occur.3.The above mechanical or electrical life is ensured at an ambient temperature of 5°C to 35°C and an ambient humidity of 40% to 70%.4.These values must be satisfied to ensure safe operation.Solenoid CharacteristicsIndicatorOperation key hole Terminal E3Terminal E4Operation key holeCamTerminal 11Terminal 12Terminal 23Terminal 24Main switchIndicator Release key Conduit opening SolenoidLock monitor switch Terminal E1 ( ) Terminal E2 ( ) Conduit openingTerminal 32 Terminal 31+~–~GuardInside equipmentLock spring112324123132Door closedAccess to machine is not allowed.Lock spring locks the door .Power to solenoid Door can be opened.Lock releasing springIndicates conditions where the Key is inserted and the lock is applied. Connect the terminals 12 to 31 to conform to BIA GS-ET-19.ONTravelKey fullyinserted.Key fullyextracted.Lock positionONTravelKey fullyinserted.Key fullyextracted.Internal Circuit DiagramLED T ype (10 to 115 V AC/DC)Constant-current diodeLED (orange)Neon Lamp T ype (100 to 250 V AC)R=130 KΩNeon lamp (orange)Circuit Connection ExampleCircuit is to be connected by user.•Connect terminals 12 to 31. (T o conform to BIA GS-ET-19.)•Do not connect the indicator in parallel to the contacts.Doing so may allow short-circuit current to flow while theindicator is damaged, causing equipment malfunction.•The 24-VDC solenoid has polarity. Be sure not to make wiringmistakes.•In the following connection example, the indicator will be lit whenthe door is open. (D4DL-1CF A-B)Power supply sideSolenoidAuxiliarycircuitSafetycircuit Ground+~–~(Orange)G9S-321-T j (24 VDC)+D4DL-j CFA-j /-j CFB-j /-CFC-j (Mechanical Lock T ype)+D4D-j 520N T 11T 12T 22T 21G9SINPCS1:Safety Switch (D4D-j 520N)S2:Safety Door Switch with solenoid lock (D4DL-j CFA-B)S3:Pushbutton switch for solenoid E S SW:Emergency-stop switch (A22E)KM1, KM2:Magnet Contactor (LC1-D)M:3-phase motorFeed back loop(Operation instruction) Emergency stop or standbyMotor control systemOff delay timerOUTc 12C 12G9S-301 (24 VDC)+D4DL-j CFG-j/-j CFH-j/-j CFJ-j (Solenoid Lock T ype)+D4D-j520 NINPCOUT c12C1SwitchD4DL-jjjj -jPre-travel distanceThree, 4.3-dia. holesIndicatorThree, cover counting screwsConduit capRelease keyConduit openingOperation KeyD4DS-K1Horizontal MountingFour, R2.15D4DS-K2Vertical MountingFour, R2.15D4DS-K3Horizontal-adjustable V ertical Mounting9 dia.4.5 dia.8 dia.Note:Each dimension has a tolerance of ±0.4 mm unless otherwise specified.D4DS-K5Horizontal/V ertical-adjustable V ertical MountingOperation Key InsertedD4DL + D4DS-K1D4DL + D4DS-K2D4DL + D4DS-K3NOTICEIf the D4DL is applied to an emergency stop circuit or safety circuit for prevention of injury, use the NC contact, which incorporates a positive opening mechanism, and make sure that the D4DL oper-ates in positive mode. Furthermore, secure the D4DL with screws or equivalent parts that are tightened in a single direction so that the D4DL or operation key cannot be easily removed or provide a protection cover to the D4DL and post a warning label near the D4DL.To protect the D4DL from damage due to short-circuits, connect the D4DL in parallel to a fuse that has a breaking current 1.5 to 2 times the rated current of the D4DL. If the D4DL is used under EN-ap-proved rating conditions, use a 10 A fuse, type gI or gG conforming to IEC 269.Do not supply power to the D4DL while wiring the D4DL.In order to prevent the D4DL from burning due to overvoltage, inser -tion of a protection fuse into the solenoid circuits is recommended.Do not use the D4DL in locations subject to explosive or flammable gases.Makesure that the load current does not exceed the rated current and that the load terminals are wired correctly .Pay utmost attention to correctly wire each terminal.After mounting and adjusting the D4DL, make sure that the D4DL operates properly .If the D4DL is imposed with force exceeding the lock strength, the D4DL may break and the equipment may continue operating.Do not drop or disassemble the D4DL.Release KeyThe release key is used to unlock the D4DL in case of emergency or if the power supply to the D4DL fails.Use an appropriate tool to set the release key to UNLOCK so that the lock will be released and the door can be opened.The release key is set at the UNLOCK position. Set the release key to the LOCK position before use.Mechanical Lock T ypeRelease keyThe release key applied to the door of a machine room ensures the safety of people adjusting the equipment in the machine room. If therelease key is set to UNLOCK, the door will not be locked when the door is closed and no power will be supplied to the equipment.Do not use the release key to start or stop machines.To prevent the release key from being used carelessly by unautho -rized people, set the release key of the D4DL in normal operation to UNLOCK and seal the release key with seal wax.MountingBe sure to mount the D4DL with a stopper as shown in the following illustration. Do not use the D4DL Switch as a stopper .Door StopperOperation keySwitchSet zone (0.5 to 3 mm)Solenoid Lock T ypeThe solenoid lock locks the door only when power is supplied to the solenoid. Therefore, the door will be unlocked if the power supply to the solenoid fails. Therefore, do not use the solenoid lock type for machines that may be operating and dangerous even after the ma -chine stops operating because of inertia.Life ExpectancyThe life of the D4DL will vary with the switching conditions. Before applying the D4DL, test the D4DL under actual operating conditions and be sure to use the D4DL in actual operation within switching times that will not lower the performance of the D4DL.Operating EnvironmentThe D4DL is for indoor use only. Do not use the D4DL outdoors.Otherwise, the D4DL may malfunction.Do not use the D4DL in the following locations:Locations with severe changes in temperatureLocations with excessive humidity that may cause condensation Locations with excessive vibrationLocations where metal dust, oil, or chemical may be sprayed onto the D4DLOperation KeyBe sure to use the dedicated Operation Key only .Do not operate the D4DL with anything other than the dedicated Operation Key. Otherwise, the safety of the system may not be maintained.Do not impose excessive force on the Operation Key inserted into the D4DL or drop the D4DL with the Operation Key inserted. Other -wise, the Operation Key may be deformed or broken.Force imposedDropSecure the Operation Key with a one-way screw , or an equivalent,so that the Operation Key cannot be easily removed.Locking the DoorThe D4DL may eventually break if the door opens accidentally due to the weight of the door , the vibration of the machine, or the bounc -ing of the door against the rubber bumper .Furthermore, the door may not unlocked if force is imposed on the operation key.Do not use the casing of the D4DL as a locking mechanism for the doorin such cases and be sure to prepare a special lock within the lock range of the D4DL (i.e., 0.5 to 3 mm).MountingReferto page 10 for the mounting dimensions of the Operation Key .Be sure that the Operation Key can be inserted properly with a toler -ance of ±1 mm in the upward, downward, left, or right direction,otherwise the D4DL may be damaged.±1 min.±1 min.Tightening T orqueBe sure to tighten each screw of the D4DL properly , otherwise the D4DL may malfunction.(3)(5)(1)(7)(6)(2)(4)Note:Tighten each screw together with a washer to the specified torque.MountingBe sure the that D4DL operates properly after mounting and adjust -ing the D4DL.Use M4 screws (one-way screws, etc.) and washers to mount the D4DL and Operation Key securely .Switch Mounting HolesThree, M4Operation Key Mounting Holes •Horizontal/V ertical Mounting D4DSK1/D4DS-K2OMRON CorporationIndustrial Control Components Division 28th Fl., Crystal T ower Bldg.,1-2-27, Shiromi, Chuo-ku,Osaka 540-6028 JapanPhone: (81)6-949-6025 Fax: (81)6-949-6029ALL DIMENSIONS SHOWN ARE IN MILLIMETERS.To convert millimeters into inches, multiply by 0.03937. T o convert grams into ounces, multiply by 0.03527.Cat. No. C107-E1-2In the interest of product improvement, specifications are subject to change without notice.Printed in Japan 1198-1M (0497) a。

澳德玛产品使用说明书样本

电子防潮箱的技术说明● 数码显示箱内温度湿度, 红色为温度, 绿色为湿度, 其中温度湿度显示为箱内的实际情况, 温度会比环境温度高1~3度。

In the digital cabinet, red means temperature, green means humidity.● ADMA 表示中湿度电子防潮箱, ADMB 表示低湿度电子防潮箱, ADMC 表示超低湿电子防潮箱,ADMD 表示氮气柜。

所有型号后面带”F ”为防静电电子防潮箱。

ADMAshows middle humidity dry cabinet. ADMB shows low humidity dry cabinet. ADMC shows ultra-low humidity dry cabinet. ADMD shows nitrogen gas cabinet.● 本产品箱体表面涂层已经经过ROHS 认证。

The surface coating has acquired ROHS certificate.● 如型号变动增加, 恕另不通知。

If we design a new style, please understand that we will not notice.1. 防潮箱须放置在水平坚固的表面Place the dry-cabinet on a level and strong surface. Turn the adjuster to be balance.2. 放置好箱体内搁板, 高度可根据存放物品调至适合, 搁板扣如图放入。

The height of the shelf is adjustable for the convenient of storage, and the shelf clasp should be put as drawing.3. 防潮箱背面留一定空间, 距离墙或其它物品必须5CM 以上。

常用IC技术参数

常用IC技术参数常用IC技术参数公司型号功能简介MAX MAX1482EPD RS-485/RS-422接口的低功耗收发器。

有斜率抑制功能,速率高达250kbps,工作电流20uA。

MAX1482为全双工工作模式,MAX1483为半双工。

MAX MAX1483EPAMAX MAX1487MJA RS-485/RS-422接口的低功耗收发器。

发送速率高达2.5Mbps,半双工通信MAX MAX485MJAMAX MAX488MJAMAX MAX489EPDMAX MAX490MJAMAX MAX1489EEPD +/-15KV ESD保护,四心线,低功耗RS-232接口接收器。

速率120kbps,工作电流350uA.MAX MAX202ECPE +/-15kv ESD保护,RS-232接口收发器。

工作电压+5V,速率120KbpsMAX MAX202EEPEMAX MAX241ECWIMAX MAX233EPP 多通道的RS-232接口主接收机。

MAX MAX238ENGMAX MAX3244EEAI 工作电压3.0--5.5V,工作电流1uA,速率1Mbps,RS-232接口,可自动关断正极的收发机。

MAX MAX354MJE 出错保护类似多路器MAX MAX354EPEMAX MAX355EPEMAX MAX382EWN 低电压,8信道/双4信道,多路器,可关闭输入MAX MAX391MJE 精度高,四心线,单刀单掷开关MAX MAX4501EPA 低电压,SPST(单刀单掷开关),COMSMAX MAX469EPE RGB视频缓冲器,2-信道,三芯绞线MAX MAX690AEPA 微处理器管理电路MAX MAX692AMJAMAX MAX805LMJAMAX MAX690MJA 有监测系统和电池转换功能的uP重置ICMAX MAX691MJE/883MAX MAX695MJEMAX MAX702EPA 有重置功能的可调整门限载噪比的电源监控器MAX MAX705MJA 低消耗,uP管理电路MAX MAX706MJAMAX MAX708MJAMAX MAX708ESAMAX MAX813LMJAMAX MAX730AEPA 5V,下降的,电流模式,PWM DC-DC变频器MAX MAX732MJA +12V/+15V,上升的,电流模式,PWM调整器MAX MAX776EPA -5V/-12V/-15V或可调整,高效,低IQ转换DC-DC-控制器MAX MAX791MJE 微处理器管理电路MAX MAX799EPE 提供给CPU电源的有同步整流器的下降控制器MAX MAX8212MJA 有可编程电压监控功能的微处理电压监控器MAX MAX840ESA 低噪音调节,GaAsFET标准-2V偏压MAX MAX865EUA 简单紧密,双输出电荷泵MAX MAX909EPA 单/双/四心线,高速率,低功率,5V TTL比较器MAX MAX942ESA 高速率,低功耗,3V/5V,Rail-to-Rail单一供电比较器MAX MAX954EPA 极低功耗,单一供电Op Amp+比较器+参考AD AD3703AD AD518SH 宽带,低成本,运算放大器AD AD5539SQ 宽频精密运算放大器AD AD571SD/883 10-bit,包括定位和时钟的A/D转换器AD AD574ASD/883B 12-bit,完整的A/D转换器AD AD7502SQ/883 4-信道,微分多路器AD AD7503SQ/883 8-信道,多路器AD AD843SQ/883 34MHz,CBFET快速稳定运算放大器AD AD9617SQ/883B 低配电,精密,宽带运算放大器AD ADSP-21062CS160 SHARC,40MHz,120MFLOPS,5V,浮点数字信号处理器AD ADSP-21062KS160AD ADG528ATQ/883 可关闭,8-信道多路器NS ADC0808CJ 8-bit,兼容微处理器,含8通道多路器的A/D转换器NS ADC0804LCJ 8-bit,uP 可兼容,A/D转换器NS DAC1230LCJ 12-bit,兼容微处理器,双缓冲D/A转换器NS DAC0832LCJ 12-bit,兼容微处理器,双缓冲D/A转换器NS DAC0802LCJ 8-bit,D/A转换器AD DAC8143FP 12-bit,串行输入,系列数模转换器DATEL ADC-500BMM A/D转换器DATEL ADC-505BMM A/D转换器DATEL ADC-815MM A/D转换器DATEL ADC-HS12BMM A/D转换器DATEL DAC-HK12BMM D/A转换器DATEL DAC-HZ12BMM D/A转换器DATEL DAC-HF12BMM D/A转换器DATEL SHM-6MC 微电子,同步采样放大器DATEL SHM-7MC 视频,高速,同步采样放大器DATEL SHM-45MM 高速合成,精密,同步采样放大器DATEL MX1616C COMS 多路器CYP CY7C128A-35DMB 8-bit,高性能,CMOS静态存储器CYP CY7C168-45DMB 4-bit,高性能,CMOS静态存储器CYP CY7C185A-35DMB 8-bit,高性能,CMOS静态存储器CYP CY7C194-25DMB 4-bit,高性能,CMOS静态存储器CYP CY7C197-25DMB 1-bit,高性能,CMOS静态存储器CYP CY7C197-35DMBCYP CY7C199-15DMB 异步静态存储器(Async SRAM)CYP CY7C199-25DMBCYP CY7C199-35DMBCYP CY7C244-45WC 可擦可编程只读存储器CYP CY7C245A-15WC 高性能,2K*8,电子可编程只读存储器CYP CY7C245A-25WMBCYP CY7C245A-25DMBCYP CY7C245A-35WMBCYP CY7C256-45WMB 32K*8 电源可编程只读存储器CYP CY7C261-25WMB 可编程只读存储器(FROM)CYP CY7C261-25DMBCYP CY7C261-35WCCYP CY7C261-45DMBCYP CY7C263-35WCCYP CY7C263-35DMBCYP CY7C263-55DMBCYP CY7C263-20WCCYP CY7C263-25WCCYP CY7C263-55WMBCYP CY7C264-20WCCYP CY7C264-45WCCYP CY7C264-55WCCYP CY7C264-55WMBCYP CY7C265-18WC 可编程只读存储器(FROM)CYP CY7C271-55WMB 可编程只读存储器(FROM)CYP CY7C277-40DMB 可改编程序的可编程只读存储器CYP CY7C291A-25WC 可编程只读存储器(FROM)CYP CY7C291-35WMB 高性能,2K*8,可编程只读存储器CYP CY7C342-30HC 128个宏单位,可改编程序逻辑驱动器CYP CY7C344-20WC MAX340系列高密度可编程逻辑器件(EPLD)CYP VIC64-UMB 含D64功能的VME bus界面控制器CYP CY7C964A-UMB VME busWSI WS57C291B-35T 可擦除可编程只读存储器WSI WS57C45-25T 军用2k*8已注册CMOS可编程只读存储器PROM WSI WS57C49C-35T 军用高速8K*8CMOS可编程只读存储器PROM WSI WS57C49C-35DPSD PSD313A-20L 低成本微控制器外围设备IDT IDT7134LA35CB *8,5V,异步双信道静态存储器IDT IDT7164L35TDB 64K异步静态存储器IDT IDT7187L25DB 64K异步静态存储器IDT IDT7201LA20TDB 512*9异步FIFO,5VIDT IDT7201LA25TPIIDT IDT7202LA50TDB 1K*9,异步FIFO,5VIDT IDT7202LA30TDBIDT IDT7202LA25TPIIDT IDT7203L25TPI 2K*9,异步FIFO,5VIDT IDT7204L25TPI 4K*9,异步FIFO,5VIDT IDT7205L25TPI 8K*9,异步FIFO,5VIDT IDT49FCT805APY 输出端磁盘缓存块,1:5双重时钟驱动,w/CMOS 输出IDT IDT49FCT805BTDBIDT IDT49FCT805BTEBIDT IDT54FCT139TDB 5V,8进制,高激励TLL电平IDT IDT54FCT161DB 5V,8进制,TLL,高标准驱动器,同步可调二进制计数器IDT IDT54FCT16244TEB 5V,双精度,高驱动器,16-bit缓冲器/线路激励器IDT IDT54FCT163ATDB 5V,八进制,高激励TLL电平IDT IDT54FCT244TDB 5V,8进制CMOS缓冲器/线路激励器IDT IDT54FCT245ADB 5V,CMOS标准,8进制双向收发器IDT IDT54FCT245TDB 5V,CMOS标准,8进制双向收发器IDT IDT54FCT245ATLB 八进制,CMOS双向收发器IDT IDT54FCT273TDB D型,变址浮点运算,边缘触发IDT IDT54FCT373ATDB CMOS,八进制,快速开关IDT IDT54FCT373ATLBIDT IDT54FCT521TDB 5V,CMOS标准,8-bit恒等式比较仪IDT IDT54FCT573TDB 5V,8进制,CMOS标准,可穿透寄存器IDT IDT54FCT574DB 5V,CMOS标准,8进制IDT IDT54FCT2245TDB 3-状态,八进制,总线收发器IDT IDT54FCT2245ATLBAD OP07AJ/883 超低偏移电压运算放大器AD OP07AZ/883AD OP07EZPMI OP27AJ/883 低噪声,精密运算放大器PMI OP10CY 双重,匹配仪器运算放大器XIL XC1701LP8I 扩展内存,可编程门控系统XIL XC3030-70PG84IBB OPA111AM 低噪声,高精度,运算放大器BB OPA111BMBB OPA501AM 高电流,高功率,运算放大器BB OPA541BM 高功率单片运算放大器BB OPA541SMBB SHC298AM 单片机采样/控制放大器HAR DG308AAK/883 单刀单掷,CMOS,模拟开关SI DG403DJ 低功耗,高速,模拟开关LIN SG1524BJ 脉宽调节器UC UC1526J 脉宽调节器UC UC1611J 四心线,肖特基二极管阵列UC UC2543N 电源管理电路UC UC2637N 直流发动机驱动器的开关控制器UC UC1706J 限流,高速MOSFET驱动器UC UC1708J 非转换高速电源驱动器UC UC1825J 高速PWM控制器UC UC2825N 高速PWM控制器UC UC1833J 精密低失真线性控制器UC UC1836J 高功率校准控制器UC UC1842J 电流模式PWM控制器LIN SG1842J PWM电流模式脉宽调节器UC UC1843J 电流模式PWM控制器UC UC1875J 相移谐振控制器MOT UC2842AN PWM电流模式脉宽调节器LIN SG1843Y PWM电流模式脉宽调节器UC UC1844J 电流模式PWM控制器LIN SG1844Y PWM电流模式脉宽调节器LIN SG2003/883 外围设备驱动器UC UC2844N PWM电流模式脉宽调节器UC UC1845J 电流模式PWM控制器LIN SG1845J PWM电流模式脉宽调节器UC UC1846J 电流模式PWM控制器UC UC1879J 相移谐振控制器UC UC1907J 负载共享控制器TI UC2580D-4UC UCC2803J 低功率,BiCMOS电流模式PWM UC UCC2804J 低功率,BiCMOS电流模式PWM UC UCC283T-5 低功率,3A,低失真调整器UC UC283T-ADJTI UC2832DW 精密低失真线性控制器TI UC2832NTI UC2836N 高功率调整控制器UC UC2875N 相移谐振控制器UC UC2902N 负载共享控制器UC UC2907N 负载共享控制器LIF SG3503M 电压参考电路TI UC3837N 相移谐振控制器LIN SG7812AT/883B 电压调整器TI SN55107AJ 双重线性接收机TI SN55110AJ 双重线性激励器TI SN55113J 双微分线性激励器TI SN55114J 双微分线性激励器TI SN55121J 双重单端,普通用线性激励器TI SNJ55121JTI SNJ55138J 四总线收发器TI SN55173J 四倍微分线路接收机TI SN55182J 双重微分线路接收机TI SNJ55182JTI SN55183J 双重微分线路激励器TI SN55188J 四倍线路激励器TI SNJ55188JTI SN55189J 四倍线路激励器TI SNJ55189JTI SN55451BJG 双重,极高速,高电流,外围激励器TI SN55452BJG 双重,极高速,高电流,外围激励器TI SNJ55462JG 双重,高电压,高电流,外围激励器TI SN55463JG 双重,高电压,高电流,外围激励器TI SN65176 双向线路收发器TI SN55ALS195J 四倍微分线路接收机TI PAL16L8-15MJB 高性能脉冲电路AMD PAL16L8-BMJ/883 TTL,可编程阵列逻辑电路LAT GAL16V8D-7LD/883 高性能,ECMOS 可编程逻辑电路PLDLAT GAL16V8D-10LD/883 高性能,ECMOS 可编程逻辑电路PLDLAT GAL16V8D-15LD/883 高性能,ECMOS 可编程逻辑电路PLDLAT GAL16V8D-20LD/883 高性能,ECMOS 可编程逻辑电路PLDLAT GAL16V8-10LPILAT GAL16V8D-15LJI 高性能,ECMOS 可编程逻辑电路PLDLAT GAL16V8-20QPI 通用可编程逻辑电路LAT GAL20V8B-10LD/883 高性能,ECMOS 可编程逻辑电路PLD(普通用)LAT GAL20V8B-15LD/883 高性能,ECMOS 可编程逻辑电路PLD(普通用)LAT GAL20V8B-20LD/883 高性能,ECMOS 可编程逻辑电路PLD(普通用)LAT GAL20V8-10LPI 通用可编程逻辑电路LAT GAL20V8B-15LJI 高性能,ECMOS 可编程逻辑电路PLDLAT GAL22V10D-15LD/883 高性能,ECMOS 可编程逻辑电路PLDLAT GAL22V10D-10LPI 高性能,ECMOS 可编程逻辑电路PLD LAT GAL22V10D-15LJI 高性能,ECMOS 可编程逻辑电路PLD LAT ISPLSI1016-60LH/883 系统内高密度可编程逻辑电路PLD LAT ISPLSI1024-60LH/883 系统内高密度可编程逻辑电路PLD LAT ISPLSI1016E-80LJI 系统内高密度可编程逻辑电路PLD LAT ISPLSI1024-60LJI 系统内高密度可编程逻辑电路PLD LAT ISPLSI1032-60LG/883 系统内高密度可编程逻辑电路PLD LAT ISPLSI1032E-70LJI 系统内高密度可编程逻辑电路PLD LAT ISPLSI1048C-50LG/883 系统内高密度可编程逻辑电路PLD LAT ISPLSI2032-80LJINS DS26LS31MJ/883 高速,四重微分线路激励器NS DS26LS32MJ/883 四重微分线路激励器AMD AM26LS33/BEA RS-422/423串口,数字传输线路激励器PHL 26LS33/BEA 3-状态,四心线,线路激励器ALT EPF10K10TI144-4 内置可编程逻辑驱动器ALT EPM7032SLI44-7 可编程逻辑电路AGILEN 6N134/883 密封,高速,高CMR,逻辑门光耦合器HP 6N140A 密封,低中频,宽Vcc,高增益光耦合器AGILEN AT41435 低噪声,6GHz,双极硅晶体管AGILEN AT42070 功率高达6GHz,双极硅晶体管AGILEN AT64020 4GHz,双向硅晶体管,线性电源AGILEN ATF-34143BLK 低噪声,高电迁移率晶体管AGILEN HCPL3150 0.5A输出电流,IGBT门驱动器HP HCPL-5631 密封,高速,高CMR逻辑门光耦合器AGILEN HDSP7511 七节数字,发光二极管显示器AGILEN HDSP7513 七节数字,发光二极管显示器AGILEN MSA-0370 6V固定增益,10dbm通用型放大器AGILEN MSA-1110 6V固定增益,高动力测距放大器AMD AM25LS2519DC 四心线,双重3状态输出,变址浮点运算,寄存器AMD AM25S08DMB 十六进制,四心线,平行串口,D寄存器AMD AM25S09/BEA 四心线,2输出,高速寄存器AMD AM25S10/BEA 4-bit开关,3-状态移相器AMD AM25S10DCAMD AM25S18/BEA 四心线,D类型,3状态输出,变址浮点运算AMD AM27C010-120DI 1M, CMOS 电子可编程只读存储器(EPROM)AMD AM27C020-120DI 2M,CMOS 电子可编程只读存储器(EPROM) AMD AM27C040-90DI 4M,CMOS 电子可编程只读存储器(EPROM)AMD AM27C256-90DI 256K,CMOS EPROMAMD AM27C512-90DI 512K,CMOS EPROMAMD AM27C64-90DI 64K,CMOS EPROMAMD AM27S13/BEA 可编程只读存储器AMD AM27S15DC 可编程只读存储器AMD AM27S181DC 可编程只读存储器AMD AM27S191DC 可编程只读存储器AMD AM27S19DC 可编程只读存储器AMD AM27S21DC 可编程只读存储器AMD AM27S25DC 可编程只读存储器AMD AM27S281ADC 双极可编程只读存储器AMD AM27S291/BLA 可编程只读存储器AMD AM27S29/BRA 可编程只读存储器AMD AM27S29DC 可编程只读存储器AMD AM27S30DC 可编程只读存储器AMD AM27S35DC 可编程初始化输入双向可编程只读存储器AMD AM27S45ADC 可编程初始化输入双向可编程只读存储器AMD AM2855DMB 128-bit,四心线,移位寄存器AMD AM29000-25GC 3地址总线,微处理器AMD AM2901C-BQA 4-bit算术逻辑部件运算器AMD AM2901CDC 4-bit,双极微处理器AMD AM2902ADMB 进位发生器AMD AM2902ADC 高速进位发生器AMD AM2903ADC 4-bit,级联的微处理器AMD AM2909ADC 微程序系列发生器AMD AM2910ADCB 微程序系列发生器AMD AM29116DC 16-bit ,微处理器AMD AM2911ADC 可编微程序的微处理器AMD AM29130DC 8-bit套管移向器AMD AM2914DCB 优先级中断控制器AMD AM2917ADC 总线收发器AMD AM2922DC 8-输入,含控制寄存器的多路器AMD AM2925ADC 时序发生器和微周期长度控制的时钟脉冲电路AMD AM2925DCREI AM2946/BRA 总线收发器AMD AM2950DC I/O端口,8-bit,双向信号交换AMD AM29517DC 乘法器AMD AM2954DC 3状态,八进制寄存器AMD AM2961DC 4-bit,错误校正多路总线缓冲器AMD AM2964BDC 动态存储控制器AMD AM29705A/BXA 16-word,4-bit,随机存储器AMD AM29705ADCAMD AM2971DC 可编程发生器AMD AM29818ADC 流水线寄存器AMD AM29821DMB 10-bit,串行输入/输出,3-状态,正边缘触发,D-类型,相移寄存器AMD AM29826DC 八进制,变址浮点运算AMD AM29833A/BLA 总线收发器AMD AM29843DC 9-bit,D-类型,3-状态寄存器AMD AM29F400BT-55SI 电可擦除只读存储器AMD AM7910DC 调制解调器电路AMD AM79533IDC 用户电路接口电路AMD AM8177DC CRT阴极射线管,视频数据串行器AMD AM8151DC D/A转换器AMD AM9060CDC 非多用户地址,动态随机存取存储器AMD AM9122-35DC 静态存储器NS NMC27C16BQ-250 存储器INT TS80C186EB20 微处理器INT D80287-6 浮点处理器INT LD82289A 同步,多总线判定器INT LD8259A 中断信号处理器INT LD8086 微处理器INT LD8087-2 算术处理器TI SMJ27C128-20JM 131072-bit,UV可擦除的,可编程只读存储器INT MD27256-35B 可擦可编程只读存储器TI SMJ4416-15JDS 动态随机存取存储器INT MD2764-35BAMD MD8226B 总线收发器INT MD82288-10 总线控制器INT MD87C51FB/B 微控制器ATM AT89C52-24JI 8-bit,微控制器ATM AT28C64-15DM/883 平行串口EEPROMATM AT28C64-25DM/883ATM AT28C256-25DM/883 256K平行串口EEPROMATM ATV2500BQL-30DM/883 高速,高密度,UV可擦除可编程逻辑驱动器NS LM105H/883 基准电压运算放大器NS LM108AH/883 基准电压运算放大器NS LM108J/883 基准电压运算放大器NS LM110J 电压跟随器TI LM111JGB 单精度型,选通脉冲差动比较器ST LM117H 正极电压调整器NS LM120H-5V 串联的,3-终端,阴极板调整器ST LM123K 三总线,3A-5V,正电压调整器ST LM137H 负极电压调整器NS LM137H/883 3-终端,可调阴极板调整器ST LM137K 三总线负电压调整器TI LM148J 四心线,普通用,运算放大器NS LM148J/883 串联,四心线,741Op Amp NS LM1558H/883 双重运算放大器TI LM158JG 普通用,双重运算放大器NS LM160H 高速差动比较器TI LM193JG 四心线,普通用,差动比较器TI LM193JGBNS LM311J 电压比较器TI SA555P 精密定时器TI SE555JG 单精度定时器NS LM723J/883 稳压器F UA733DC 微分放大器NS LM741H/883 SPI/MICROWIRE数字温度传感器NS LM747H SPI/MICROWIRE数字温度传感器NS LM747H/883NS LF155H JFET输入运算放大器NS LF155H/883NS LF255H 双极,JFET运算放大器NS LF157H/883 运算放大器NS LF411MH/883 低补偿,低漂移,JFET输入运算放大器NS LF412MJ/883 低补偿,低漂移,双重JFET输入运算放大器MOT MC10107L 异或/非或门径系统MOT MC10505BEAJCMOT MC10507BEAJCMOT MC10525BEAJCMOT MC10531BEAJCMOT MC14174BAL 十六进制,D-类型,变址浮点运算MOT MC14403L2 脉冲编码调制,多媒体数字信号编解码器(PCM CODEC)MOT MC1403U 电压参考系统MOT MC145146P2 4-bit,数据总线输入,频率合成器,相位锁定回路MOT MC1503AU 电压参考系统TI MC1558JG 双重,普通用,运算放大器MOT MC1590G 双极,TV视频信号电路,TV音频接收电路MOT MC1651L 双重,A/D转换器MOT MC1658L 电压控制多频振荡器,相位锁定回路MOT MC1664L 四心线,2输入,“或”逻辑门MOT MC1668L 双重时钟寄存器MOT MC1670L RS-类型,变址浮点运算MOT MC1692L 四心线,含偏压驱动器的线路接收机MOT MC4344BCAJC 相频检波器MOT MC3419-1L 线路接口电路ACTEL A1020B-PG84M datasheetAMD AM685DL 双向电压比较器EDI EDI8L32512C15AI 512K*32 CMOS高速,静态存储器TI JBP18S030MJ 32*8,双极可编程只读存储器FROM TI JBP28L22MJ 256*8,双即可编程只读存储器FROM HAR ICL7650SMJD 超稳定-断路运算放大器HAR ICL8038AMJD 精密定波形发生器/压控振荡器NS DP8304BJ 双向总线驱动器HAR HI1-201-5HAR HA2-5033/883 250MHz 视频缓冲器HAR HFA3127MJ/883 超高频晶体管阵列HAR HFA3763IN 应用于正交调制的高整合度基带转换器PHL HEF4750VD 频率合成器PHL HEF4751VD 通用分频器HAR CA3100T 38MHz,运算放大器HAR CA3140AT 集高电压PMOS和双极晶体管优势于一体的运算放大器HAR CA3193AT 高稳定度,高精密度的运算放大器NS LH0033CG 快速和极端快速缓冲器LIN LT1001ACH 高精度运算放大器LIN LTC1562IG-2 低噪声,无失真,主动RC四心线通用滤波器IMS IMS1423P-25 高性能,CMOS静态存储器PMM8713PIMIC PIC16C65B-04IP 强大而易于编辑的CMOS,OTP-基准,8-bit微控制器TOS TC524258BZ-80 门控,硅CMOS,多通道,动态随机存取存储器DRAMST T1616MJFAIR UA3045DMQBSIS T133G-883B(960.000KHZ) 振荡器SIS T133G-883B(5.120MHZ)SIS T133G-883B(1.000MHZ)FAIR UA9640DC/(26S10) 总线收发器MOT MRF314ASI MRF315A NPN RF电源硅晶体管MOT MRF323MOT MRF6414 RF电源NPN硅晶体管MOT MRF658PMI SMP10AY 放大器SD1524-04 微波电源晶体管,IFF,DME,TACAN AD AD2S83AP 可互换的分辨率分解器和数字转换器DVSI AMBE1000 声音合成芯片DVSI AMBE2000 声音合成芯片TI TCM1520AP 振铃检波器。

LM3524D中文资料

RT = 5.6k, CT = 0.01 µF

RT = 5.6k, CT = 0.01 µF

25 50

180 40 20

550

17.5

20

22.5

Supply Voltage Collector Supply Voltage

(LM2524D) (LM3524D) Output Current DC (each) Oscillator Charging Current (Pin 7)

40V

55V 40V 200 mA 5 mA

Internal Power Dissipation Operating Junction Temperature

∆fOSC ∆fOSC

VOSC tPW

Freq. Change with VIN Freq. Change with Temp.

Output Amplitude (Pin 3) (Note 8) Output Pulse Width (Pin 3) Sawtooth Peak Voltage

VIN = 8 to 40V

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

% VMin µsMax VMax

3

元器件交易网

DVD技术参数范文

DVD技术参数范文DVD容量是指一张DVD光盘可以存储的数据量。

DVD分为一层和双层两种类型,一层DVD可以存储4.7GB的数据,而双层DVD可以存储8.5GB 的数据。

容量的提升使得DVD成为传统CD盘和VHS磁带的绝佳替代品。

DVD分辨率是指DVD视频的显示质量,以水平像素和垂直像素的数量来表示。

标准DVD的分辨率为720×480,用于NTSC制式的视频系统;720×576用于PAL制式的视频系统。

而高清DVD(HD-DVD)的分辨率可以达到1920×1080,提供更清晰、更细腻的图像。

DVD音频规格是指DVD支持的不同音频格式和规格。

主要有两种音频规格:线性脉冲编码(LPCM)和压缩音频。

LPCM是无损音频,提供高质量的音频输出,通常是以48kHz采样率和16位或24位深度进行编码。

而压缩音频采用Dolby Digital、DTS或者MPEG-2音频编码格式,以较小的文件大小实现声音的压缩,但稍稍降低了音质。

DVD音频编码格式是指音频数据的压缩和解码技术。

DVD支持多种音频编码格式,包括Dolby Digital(AC-3)、DTS(Digital Theater System)、MPEG-2和LPCM编码。

Dolby Digital是最常用的编码格式,以5.1声道环绕声音质输出。

而DTS提供更高的比特率,能够提供更高的音质,但需要更高的传输速度和解码能力。

DVD还具备多种特殊功能,包括多角度播放、多声道音频、字幕、多条语音轨道和菜单功能等。

多角度播放可用于在同一场景下观看不同角度的影像。

多声道音频可以提供更具立体感的环绕声效果。

字幕可以在不同语言之间切换,以满足不同受众的需求。

多条语音轨道允许在不同语言之间切换,以满足不同用户的语言选择。

而菜单功能则提供了用户友好的导航和交互体验。

此外,DVD还支持区域编码,以限制不同地区的DVD播放器只能播放特定区域的DVD光盘。

新普特 INFINITY 'D' 系列程式化微处理基础数字面板仪表说明书

IDT-00/N IDP-4,BLߜVery Easy Scaling ߜ4-Digit LED Display ߜMax or Min RecallߜShort Case 4.1" (104 mm)ߜRed or Green LED Display ߜPower 115 Vac, 230 Vac or 10-32 VdcThe NEWPORT ®INFINITY ®"D" Family of programmable Microprocessor-Based digital panel meters are simple andreliable. Models are available for process (DC Voltage and Current), Thermocouple and pH.IDpH METERThe IDPH is an economical, user-friendly panel meter for pH measurement. Its small size allows for easy installation and will accommodate any pH electrode with BNC connector. Temperature compensation is either manual or automatic with use of any 1000Ω platinum RTD.IDpH SPECIFICATIONSAccuracy: ±0.02 pHInput: Impedance > 1012ohmsTemp. Compensation: Manual fixed resistors; Automatic 1000Ω RTD Display Range: 0-14 pH Connections: BNCProcess, Thermocouple, and pH MetersTHERMOCOUPLE METER IDTߜSingle Button °C/°FSelectionߜMin and Max Recall ߜDisplay HoldThe model IDT is an economical digital panel meter for use with thermocouples J,K, T, E, R, S, N, or J DIN. Simple front panel programming allows selection of MAX or MIN (peak or valley) temperatures. Connections forthermocouple input, power or external display hold switch made with plug-in screw terminal connectors.IDT SPECIFICATIONSAccuracy: (@ 25°C) ±0.5 °C Resolution:1.0 or 0.1 degree (100-1000)Input: J, K, T , E, R, S, N, J DINCOMMON SPECIFICATIONSOperating Temp:0 to 50°C (32 to 122°F)Display: 4-digit, red or green LED,14.2 mm (0.56") highVoltage: 115 Vac ±10% standard (230 Vac or 10-32 Vdc, optional)Frequency:50 or 60 HzPower Consumption: 3.5 watts max.(IDP), 2.5 watts max. (IDT , IDpH)Dimensions:96 W x 48 H x 104mm D (3.78 x 1.89" x 4.10")Panel Cutout:92 W x 45 mm H (1/8 DIN, 3.62 x 1.77")Depth Behind Panel: 100 mm (3.94")Weight:312 g (11 oz)PROCESS METERIDPߜVery Easy Scaling ߜ4-20 mA, 0-5 V, 1-5 Vor 0-10 V Selectable Input ߜ4-Digit LED Display ߜBuilt-In ExcitationߜFront Panel Digital Tare ߜMax or Min RecallVery easy scaling via the front-panel pushbuttons provides an economicalsolution for monitoring a variety of process parameters. The model IDP accepts voltage or current inputs and provides a 4-digit scaled indication of the measured value. Standard features include a front panel activated, digital tare function, recall of the maximum or minimummeasurement and a space saving short case.IDP SPECIFICATIONSInput: 4-20 mA (20 Ohm), 0-5 Vdc, 1-5 Vdc, 0-10 VdcDisplay Range:-1999 to 9999Accuracy: ±0.05 % of reading ±1 lsd Excitation: 10 Vdc @ 50 mA or 24 Vdc @ 25 mA82Ordering Example:IDP-0,FS:4-20 mA = 0-2000®IDT-00/N IDP-4,BL。

FEDL7204-001DIGEST-01资料

OKI Semiconductor FEDL7204-001DIGEST-01Issue Date: Aug. 12, 2004 ML7204-001VoIP CODECGENERAL DESCRIPTIONThe ML7204-001 is a speech CODEC for VoIP. As a speech CODEC, this LSI allows selection of G.729.A/G711 and supports the PLC (Packet Loss Concealment) function.With an echo canceler that handles 32 ms-delay and FSK detection/generation, DTMF detection/generation, and tone detection/generation functions, the ML7204-001 is the most suitable LSI for adding the VoIP function to TAs and routers.FEATURES• Power supply voltageDigital power supply voltage (DVDD0, 1, 2): 3.0 to 3.6 VAnalog power supply voltage (AVDD): 3.0 to 3.6 V• Speech CODEC:G.729.A (8 kbps)/G.711 (64 kbps) µ-law and A-law (supports individual setting for transmission and reception)Supports ITU-T G.711 Appendix 1 compliant PLC (Packet Loss Concealment) functionSupports the 2-channel processing function (for 3-way communication)• Built-in FIFO buffer (640 bytes) for transmission/reception data transferAllows selection of Frame/DMA (slave) interface• Echo canceler for handling 32 ms delay• DTMF detection• DTMF generation (the tone generation function enables generation of DTMF signals)• Tone detection: 2 types (1650 Hz and 2100 Hz: Detection frequency can be changed)• Tone generation: 2 types• FSK detection• FSK generation• Built-in 16-bit timer: 1 channel• Dial pulse detection function (secondary function of general-purpose I/O ports)• Dial pulse transmission function (secondary function of general-purpose I/O ports)• General-purpose I/O ports64-pin package: Equipped with 7 ports (with some of them having secondary function allocation)100-pin package: Equipped with 21 ports (with some of them having secondary function allocation)• Two types of built-in linear PCM CODEC (CODEC_A and CODEC_B)• Analog interfaceCODEC_A side: Incorporates one type each of input amplifier and output amplifier (10 kΩ driving)CODEC_B side: Incorporates one type each of input amplifier and output amplifier (10 kΩ driving)• PCM interface coding format:Allows selection of 16-bit linear/G.711 (64 kbps) µ-law or A-law• PCM serial transmission rate: 64 kHz to 2.048 MHz (fixed to 2.048 MHz for output)• PCM time slot assignment function (allows up to 2 slots for input and 1 slot for output individually) When set to µ-law/A-law: Supports up to 32 slots (BCLK: 2.048 MHz)When set to 16-bit linear: Supports up to 16 slots (BCLK: 2.048 MHz)OKI Semiconductor ML7204-001• Master clock frequency:12.288 MHz (crystal; external input)• Supports hardware and software power down• Package:64-pin plastic QFP (QFP64-P-1414-0.80-BK) (ML7204-001GA)100-pin plastic TQFP (TQFP100-P-1414-0.50-BK) (ML7204V-001TB)OKI Semiconductor ML7204-001BLOCK DIAGRAMV F R O A I N 0N G S X A I N 0P V F R O A I N 1N G S X D V D D D G N D A G N D V D D D G N D D V D D G N A V D V R E G O U V G A V R E I N T B / G P I O A [6]A 0-A 7 D 0-D 15C S BR D BW R BF R 0BF R 1BY N CC L K S E LB C L KC M OP C M IA C K 0B / G P I O A [4] AC K 1B / G P I O A [5]OKI Semiconductor ML7204-001PIN CONFIGURATION (TOP VIEW)D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0D G N D 0D G N D 1T S T 1T S T 0P C M O P C M I B C L K S Y N CD V D D 1R D B W R B C S B F R 0B F R 1B D V D D 0A 0A 1A 2A 3A 4A 5A 6A 7G P I O A [0]/D P IG P I O A [1]G P I O A [2]/D P OG P I O A [3]P D N BI N T B /G P I O A [6]A C K 0B /G P I O A [4]AC K 1B /G P I O A [5]C L K S E L64-Pin Plastic QFPOKI Semiconductor ML7204-001AVDDD15D14D13D12D11D10D9D8D7D6D5D4D3D2D1D0G N D 1P I O A [0]/D P IG P I O A [1]G P I O A [2]/D P OP I O A [3]D N BC L K S E LAIN1N R D B W R B C S BD G N D 0NC XO NC N CNC NC NC NC NC NC NC NC NC G P I O B [0]G P I O B [1]G P I O B [2]G P I O B [3]G P I O B [4]G P I O B [5]N CT S T 1T S T 0 P C M OP C M I B C L KS Y N CF R 0B F R 1B D V D D 0I N T B /G P I O A [A C K 0B /G P I O A [4]A C K 1B /G P I O A [5]G P I O C [0]G P I O C [1]G P I O C [2]G P I O C [3]G P I O C [4]G P I O C [5]G P I O C [6]G P I O C [7]C L K O U TNC A 01234567V D D 1C100-Pin Plastic TQFPOKI Semiconductor ML7204-001PIN DESCRIPTIONSPinTQFP100 QFP64Symbol I/O WhenPDNB= “0”Description1 — CLKOUT O “L” 12.288 MHz clock output2 1 TST1 I “0” Test control input 1: Normally, input “0”.3 2 TST0 I “0” Test control input 0: Normally, input “0”.4 — GPIOC[0] I/O I General-purpose I/O port C [0]5 — GPIOC[1] I/O I General-purpose I/O port C [1]6 3 PCMO O “Hi-z”PCM data output [Open drain output pin] 74PCMI I IPCM data input ICLKSEL = ”0” PCM shift clock input 8 5 BCLKI/O “L”CLKSEL = ”1”PCM shift clock output I CLKSEL = ”0” PCM synchronous signal 8 kHz input9 6 SYNCI/O“L”CLKSEL = ”1”PCM synchronous signal 8 kHz output10 — GPIOC[2] I/O I General-purpose I/O port C[2] 11 — GPIOC[3] I/O I General-purpose I/O port C[3] 12 7 DVDD0 — — Digital power supply 13 — GPIOC[4] I/O I General-purpose I/O port C[4] 14 — GPIOC[5] I/O I General-purpose I/O port C[5]15 8ACK0B/GPIOA[4]I/O I Transmit buffer DMA access acknowledge signal input (primary function) General-purpose I/O port A[4] (secondary function) [5 V tolerant pin]16 9ACK1B/GPIOA[5]I/O I Receive buffer DMA access acknowledge signal input (primary function) General-purpose I/O port A [5] (secondary function) [5 V tolerant pin]17 — GPIOC[6] I/O I General-purpose I/O port C [6] 18 — GPIOC[7] I/O I General-purpose I/O port C [7]19 10FR0B(DMARQ0B)O ”H” FR0B:(FD_SEL = ”0”)Transmit buffer frame signal output DMARQ0B: (FD_SEL = ”1”) Transmit buffer DMA access request signal 20 11FR1B(DMARQ1B)O “H” FR1B: (FD_SEL = ”0”)Receive buffer frame signal output DMARQ1B: (FD_SEL = ”1”) Receive buffer DMA access request signal output 21 12 INTB/GPIOA[6] I/O “H” Interrupt request output (primary function)General-purpose I/O port A [6] (secondary function) [5 Vtolerant pin]22 13 CSB I I Chip select control input 23 14 RDB I I Read control input 24 15 WRB I I Write control input 25 16 DGND0 — — Digital ground (0.0 V)OKI Semiconductor ML7204-001PinTQFP100 QFP64Symbol I/O WhenPDNB= “0”Description 26 — NC — — (Unused) 27 17 D0 I/O I Data input-output 28 18 D1 I/O I Data input-output 29 — NC — — (Unused) 30 19 D2 I/O I Data input-output 31 20 D3 I/O I Data input-output 32 — NC — — (Unused) 33 21 D4 I/O I Data input-output 34 22 D5 I/O I Data input-output 35 — NC — — (Unused) 36 23 D6 I/O I Data input-output 37 24 D7 I/O I Data input-output 38 — NC — — (Unused)39 25 D8 I/O IData input-output. Fix the input to “L” or “H” when usingthe pin in 8-bit bus access (BW_SEL = ”1”).40 26 D9 I/O IData input-output. Fix the input “L” or “H” when using thepin in 8-bit bus access (BW_SEL = ”1”).41 — NC — — (Unused)42 27 D10 I/O IData input-output. Fix the input “L” or “H” when using thepin in 8-bit bus access (BW_SEL = ”1”).43 28 D11 I/O IData input-output. Fix the input “L” or “H” when using thepin in 8-bit bus access (BW_SEL = ”1”).44 — NC — — (Unused)45 29 D12 I/O IData input-output. Fix the input “L” or “H” when using thepin in 8-bit bus access (BW_SEL = ”1”).46 30 D13 I/O IData input-output. Fix the input “L” or “H” when using thepin in 8-bit bus access (BW_SEL = ”1”).47 — NC — — (Unused)48 31 D14 I/O IData input-output. Fix the input “L” or “H” when using thepin in 8-bit bus access (BW_SEL = ”1”).49 32 D15 I/O IData input-output. Fix the input “L” or “H” when using thepin in 8-bit bus access (BW_SEL = ”1”).50 — NC — — (Unused) 51 — NC — — (Unused) 52 33DVDD1 — — Digital power supply 53 34 A0 I I Address input 54 35 A1 I I Address input 55 36 A2 I I Address input 56 37 A3 I I Address input 57 38 A4 I I Address input 58 39 A5 I I Address input 59 40 A6 I I Address input 60 41A7 I I Address inputOKI Semiconductor ML7204-001PinTQFP100 QFP64Symbol I/O WhenPDNB= “0”Description61 42 PDNB I “0” Power-down input“0”: Power-down reset”1”: Normal operation62 — GPIOB[0] I/O I General-purpose I/O port B[0] 63 — GPIOB[1] I/O I General-purpose I/O port B[1]64 43 CLKSEL I I SYNC/BCLK input-output control input“0”: SYNC/BCLK are configured to be input“1”: SYNC/BCLK are configured to be output65 — GPIOB[2] I/O I General-purpose I/O port B[2] 66 — GPIOB[3] I/O I General-purpose I/O port B[3] 67 44 DGND1 — — Digital ground (0.0 V) 68 — GPIOB[4] I/O I General-purpose I/O port B[4] 69 — GPIOB[5] I/O I General-purpose I/O port B[5]70 45 GPIOA[0]/DPI I/O IGeneral-purpose I/O port A[0] [5 V tolerant pin]Secondary function: Input pin for dial pulse detection71 46 GPIOA[1] I/O I General-purpose I/O port A[1] [5 V tolerant pin] 72 — NC — — (Unused) 73 — NC — — (Unused)74 47GPIOA[2]/DPOI/O I General-purpose I/O port A[2] [5 V tolerant pin] Secondary function: Output pin for dial pulse transmission 75 48 GPIOA[3] I/O I General-purpose I/O port A[3] [5 V tolerant pin] 76 49 AVDD — — Analog power supply 77 — NC — — (Unused) 78 50 AIN0P I I AMP0 non-inverting input 79 51 AIN0N I I AMP0 inverted input 80 52 GSX0 O “Hi-z”AMP0 output (10 k Ω driving) 81 — NC — — (Unused) 82 53 GSX1 O “Hi-z”AMP1 output (10 k Ω driving) 83 54 AIN1N I I AMP1 inverted input 84 — NC — — (Unused) 85 55 AVREF O “L” Analog signal ground (1.4 V) 86 56 VFRO0 O “Hi-z”AMP2 output (10 k Ω driving) 87 57 VFRO1 O “Hi-z”AMP3 output (10 k Ω driving) 88 58 AGND — — Analog ground (0.0 V) 89 — NC — — (Unused) 90 — NC — — (Unused) 91 59 DGND2 — — Digital ground (0.0 V) 92 60 XI I I 12.288 MHz crystal interface, 12.288 MHz clock input 93 — NC — — (Unused) 94 61 XO O “H” 12.288 MHz crystal interfaceOKI Semiconductor ML7204-001 PinTQFP100 QFP64 Symbol I/OWhenPDNB= “0”Description95 62 DVDD2 — — Digital power supply96 — NC — —(Unused)97 — NC — —(Unused)98 63 VREGOUT — — Internal regulator voltage output pin (approx. 2.5 V)99 64 VBG — — Internal regulator reference voltage output pin100 — NC — —(Unused)OKI Semiconductor ML7204-001ABSOLUTE MAXIMUM RATINGSParameter Symbol ConditionRating Unit Analog power supplyvoltageAVDD —–0.3 to +4.6 V Digital power supplyvoltageDVDD —–0.3 to +4.6 V Analog input voltage VAIN Analog pin–0.3 to AVDD+0.3V VDIN1 Normal digital pin–0.3 to DVDD+0.3 V DVDD = 3.0 to 3.6 V–0.3 to +6.0 V Digital input voltage VDIN2 5 V tolerant pinDVDD < 3.0 V–0.3 to DVDD+0.3V Output current IO — –20 to +20mA Power dissipation PD Ta = 60 °C, per package 350 mW Storage temperature Tstg —–65 to +150°CRECOMMENDED OPERATING CONDITIONS(AVDD = 3.0 to 3.6 V, DVDD0, 1, 2 = 3.0 to 3.6 V, AGND = DGND0, 1, 2 = 0.0 V, Ta = –20 to 60°C unless otherwise specified)Parameter Symbol Condition Min. Typ. Max. UnitAnalog power supply voltage AVDD — 3.0 3.3 3.6 V Digital power supply voltage DVDD — 3.0 3.3 3.6 V Operating temperature range Ta — –20 — 60 °CVIH1 Normal digital pin0.75 ×DVDD— DVDD+ 0.3 V Digital high-level input voltageVIH2 5 V tolerant pin0.75 ×DVDD— 5.5 V Digital low-level input voltage VIL Digital pin –0.3 —0.19 ×DVDDV Digital input rise time tIR Digital pin — 2 20 ns Digital input fall time tIF Digital pin — 2 20 ns Digital output load capacitance CDL Digital pin — — 50 pF Digital output load resistance RDL Pull-up resistance, PCMO 500 — — Ω AVREF bypass capacitor Cvref Between AVREF-AGND 2.2+0.1— 4.7+0.1 µF VREGOUT bypass capacitor Cvout Between VREGOUT-DGND — 10+0.1 — µF VBG bypass capacitor CVBG Between VBG-DGND — 150 — pF Master clock frequency Fmck MCK –0.01%12.288 +0.01% MHz PCM shift clock frequency Fbclk BCLK (at input) 64 — 2048 kHz PCM synchronous signalfrequencyFsync SYNC (at input) — 8.0 — kHzClock duty ratio DRCLK MCK, BCLK (at input) 40 50 60 %tBS BCLK to SYNC (at input) 100 — — nsPCM synchronous timingtSB SYNC to BCLK (at input) 100 — — nsPCM synchronous signal width tWS SYNC (at input) 1BCLK — 100 µs(Note) On power-on/shut-down sequenceFor the analog power supply voltage (AVDD) and the digital power supply voltage (DVDD) to be supplied to this LSI, it is recommended that power be applied to them simultaneously. However, if simultaneous power-up is difficult due to the power supply circuit configuration, power them up in the order of DVDD → AVDD. The power supplies should be shut down in the reverse order of power-on sequence.OKI Semiconductor ML7204-001ELECTRICAL CHARACTERISTICSDC Characteristics(AVDD = 3.0 to 3.6V, DVDD0, 1, 2 = 3.0 to 3.6 V, AGND = DGND0, 1, 2= 0.0 V, Ta = –20 to 60°C unless otherwise specified) Parameter Symbol Condition Min.Typ.Max.UnitISSStandby state(PDNB = ”0”, DVDD = AVDD=3.3 V, Ta = 25°C)— 200 500 µAIDD1 Operating status 1Speech CODEC activated/PCM I/F not usedSC_EN = ”1”, AFEA_EN = ”0”, AFEB_EN = ”1”,XI, XO: 12.288 MHz crystal connected— 45 55 mAPower supply currentIDD2 Operating status 2Speech CODEC activated/PCM I/F usedSC_EN = ”1”,PCMI1_EN = ”1”, PCMO1_EN= ”1”,AFEA_EN=”0”, AFEB_EN=”0”XI, XO: 12.288 MHz crystal connected— 50 65 mAIIH Vin = DVDD — 0.01 10 µA Digital input pinInput leakage current IIL Vin = DGND –10 –0.01 — µA IOZH Vou = DVDD — 0.01 10 µA Digital I/O pinOutput leakagecurrentIOZL Vout = DGND –10 — — µAHigh-level output voltage VOHDigital input pins, I/O pinIOH = 4.0 mAIOH = 0.5 mA (XO pin)IOH = 1 2.0 mA (CLKOUT pin)0.78 ×DVDD— — V VOL1Digital output pins, I/O pinIOL = –4.0 mAIOL = –0.5 mA (XO pin)IO = –12.0 mA (CLKOUT pin)— — 0.4 VLow-level output voltageVOL2 Open drain output pinsIOL = –12.0 mA— — 0.4 VCIN1 Inputpins —6—pFInput capacitance (*1)CIN2 I/Opins —10—pF*1 Design guaranteed valueOKI Semiconductor ML7204-001Analog Interface(AVDD = 3.0 to 3.6 V, DVDD0, 1 ,2 = 3.0 to 3.6 V, AGND = DGND0, 1, 2= 0.0 V, Ta = –20 to 60°C unless otherwise specified)Parameter Symbol Condition Min.Typ.Max.Unit Input resistance (*1) RIN AIN0N, AIN0P, AIN1N 10 — — MΩOutput load resistance RL GSX0, GSX1, VFRO0, VFRO110 — — kΩOutput load capacitance CL Analog output pins — — 50 pFOffset voltage VOF VFRO0, VFRO1 –40 — 40 mVOutput voltage level (*2) VO GSX0, GSX1, VFRO0, VFRO1RL = 10kΩ, AMP input 1.3 Vpp1.158 1.3 1.458 Vpp*1 Design guaranteed value*2 –7.7 dBm (600Ω) = 0 dBm0, +3.17 dBm0 = 1.3 VppOKI Semiconductor ML7204-001AC Characteristics in Speech CODEC = G.711 (µ-law) Mode(AVDD = 3.0 to 3.6V, DVDD0, 1, 2 = 3.0 to 3.6 V, AGND = DGND0, 1, 2 = 0.0 V, Ta = –20 to 60°C unless otherwise specified)ConditionParameter Symbol Frequency (Hz) Level (dBm0)Min.Typ. Max. UnitLT1 0 to 60 25 — — dB LT2 300 to 3000 –0.15— 0.20 dB LT3 1020 Reference — LT4 3300 –0.15— 0.80 dBLT5 3400 0 — 0.80 dB Transmit frequencycharacteristics LT6 3968.75 013 — — dB LR2 0 to 3000 –0.15— 0.20 dB LR3 1020 Reference —LR4 3300 –0.15— 0.80 dBLR5 3400 0 — 0.80 dB Receive frequencycharacteristicsLR6 3968.75 0 13 — — dB SDT1 3 35 — — dBp SDT2 0 35 — — dBp SDT3 –30 35 — — dBp SDT4 –40 28 — — dBpTransmitsignal-to-noise ratio (*1) SDT5 1020 –45 23 — — dBp SDR1 3 35 — — dBp SDR2 0 35 — — dBp SDR3 –30 35 — — dBpSDR4 –40 28 — — dBpReceivesignal-to-noise ratio (*1) SDR5 1020 –45 23 — — dBp GTT1 3 –0.2— 0.2 dB GTT2 –10 Reference —GTT3 –40 –0.2— 0.2 dBGTT4 –50 –0.6— 0.6 dB Transmit inter-levelloss errorsGTT5 1020 –55 –1.2— 1.2 dB GTR1 3 –0.2— 0.2 dB GTR2 –10 Reference —GTR3 –40 –0.2— 0.2 dBGTR4 –50 –0.6— 0.6 dB Receive inter-levelloss errorsGTR5 1020 –55 –1.2— 1.2 dBNIDLT —Analog input =AVREF— — –70 dBm0p Idle channel noise (*1)NIDLR — PCMI = ”1” — — –70 dBm0pTransmit absolutelevel (*2)AVT 1020 0 0.2850.320 0.359 VrmsReceive absolute level(*2)AVR 1020 0 0.2850.320 0.359 Vrms*1 P-message weighted filter used*2 0.320 Vrms = 0 dBm0 = –7.7 dBm (600Ω)OKI Semiconductor ML7204-001AC Characteristics (Gain Setting) in Speech CODEC = G.711 (µ-law) mode(AVDD = 3.0 to 3.6 V, DVDD0, 1, 2 = 3.0 to 3.6 V, AGND = DGND0, 1, 2 = 0.0 V, Ta = –20 to 60°C unless otherwise specified)Parameter Symbol Condition Min.Typ. Max. UnitTransmit/receive gainsetting accuracyGAC For all gain set values –1.0— 1.0 dBAC Characteristics (Tone Output) in Speech CODEC = G.711 (µ-law) Mode(AVDD = 3.0 to 3.6 V, DVDD0, 1, 2 = 3.0 to 3.6 V, AGND = DGND0, 1, 2 = 0.0 V, Ta = –20 to 60°C unless otherwise specified)Parameter Symbol Condition Min.Typ. Max. UnitFrequency deviation fDFT For all frequency set values –1.5— 1.5 % Output level oLEV For all gain set values –2.0— 2.0 dBAC characteristics (DTMF Detector and Other Detectors) in Speech CODEC = G.711 (µ-law) Mode(AVDD = 3.0 to 3.6 V, DVDD0, 1, 2 = 3.0 to 3.6 V, AGND = DGND0, 1, 2 = 0.0 V, Ta = –20 to 60°C unless otherwise specified)Parameter Symbol Condition Min.Typ. Max. UnitDetection level accuracy dLAC For all detection level set values –2.5— 2.5 dBAC characteristics (Echo Canceler)(AVDD = 3.0 to 3.6 V, DVDD0, 1, 2 = 3.0 to 3.6 V, AGND = DGND0, 1, 2 = 0.0 V, Ta = –20 to 60°C unless otherwise specified)Parameter Symbol Condition Min.Typ. Max. UnitEcho attenuation eRES — — 35 — dB Erasable echo delay time tECT — — — 32 msMeasuring methodOKI Semiconductor ML7204-001 Timings of PDNB, XO, and AVREF(AVDD = 3.0 to 3.6 V, DVDD0, 1, 2 = 3.0 to 3.6 V, AGND = DGND0, 1, 2= 0.0 V, Ta = –20 to 60°C unless otherwise specified)Parameter Symbol Condition Min.Typ.Max.UnitPower-down signal pulse width tPDNB PDNBpin 250——µsAVDD supply delay time tAVDDON — 0 — — ns Oscillation activation time txtal — — — 20 msAVREF = 1.4 (90%)C5 = 4.7 µF, C6 = 0.1 µF (See Figure 9) — — 600 msAVREF rise time tAVREFAVREF = 1.4 (90%)C5 = 2.2 µF, C6 = 0.1 µF(See Figure 9)— — 300 msFigure 1 Timings of PDNB, XO, and AVREF(Note)The capacitance of the AVREF capacitor (C5) affects the AVREF rise time and analog characteristics. If weight is given to the analog characteristics, specify 4.7 µF, and if it is given to the AVREF rise time, specify 2.2 µF. The electrical characteristics for the analog characteristics that are described above are guaranteed in both capacitances.OKI Semiconductor ML7204-001PCM interface(AVDD = 3.0 to 3.6 V, DVDD0, 1, 2 = 3.0 to 3.6 V, AGND = DGND0, 1, 2 = 0.0 V, Ta = –20 to 60°C unless otherwise specified)Parameter Symbol Condition Min. Typ. Max. UnitBit clock frequency fBCLK CDL = 20 pF (during output) –0.1% 2.048 +0.1% MHz Bit clock duty ratio dBCLK CDL = 20 pF (during output) 45 50 55 % Synchronous signal frequency fSYNC CDL = 20 pF (during output) –0.1%8 +0.1% kHzSynchronous signal duty ratiodSYNC1 CDL = 20 pF (during output)BCLK = 2.048 MHz At output45 50 55 % tBS BCLK to SYNC (during output)100 — — ns Transmit/receive synchronous timing tSB SYNC to BCLK (during output)100 — — ns Input setup time tDS 50 — — nsInput hold time tDH PCMI pin50 — — nstSDX — — 100nsDigital output delay time tXD1 — — 100 nstXD2 — — 100 nsDigital output hold timetXD3PCMO pinPull-up resistance RDL = 500ΩCDL = 50 pF — — 100 nsBCLKSYNCPCMIFigure 2 PCM Interface Input Timing (Long Frame)BCLKSYNCPCMIFigure 3 PCM Interface Input Timing (Short Frame)OKI Semiconductor ML7204-001BCLKSYNCPCMOFigure 4 PCM Interface Output Timing (Long Frame)BCLKSYNCPCMOFigure 5 PCM Interface Output Timing (Short Frame)OKI Semiconductor ML7204-001Control Register Interface(AVDD = 3.0 to 3.6 V, DVDD0, 1, 2 = 3.0 to 3.6 V, AGND = DGND0, 1, 2 = 0.0 V, Ta= –20 to 60°C unless otherwise specified)Parameter Symbol Condition Min.Typ. Max. UnitAddress setup time (at Read) tRAS 10 — — ns Address hold time (at Read)) tRAH 0 — — ns Address setup time (at Write) tWAS 10 — — ns Address hold time (at Write) tWAH 10 — — ns Write data setup time tWDS 20 — — ns Write data hold time tWDH 10 — — ns CSB setup time (at Read) tRCS 10 — — nsCSB hold time (at Read) tRCH 0 — — nsCSB setup time (at Write) tWCS 10 — —ns CSB hold time (at Write) tWCH 10 — — ns WRB pulse width tWW 10 — — ns Read data output delay time tRDD — — 20 ns Read data output hold time tRDH 3 — — ns RDB pulse width tRW 25 — — ns CSB disable time tCD CL = 50 pF 10 — — nsFigure 6 Control Register InterfaceOKI Semiconductor ML7204-001Transmit/Receive Buffer Interface (Frame Mode)(AVDD = 3.0 to 3.6 V, DVDD0, 1, 2 = 3.0 to 3.6 V, AGND = DGND0, 1, 2 = 0.0 V, Ta = –20 to 60°C unless otherwise specified)Parameter Symbol Condition Min.Typ. Max. UnitFR1B setup time tF1S 3 — — ns FR1B output delay time tF1D — — 20 ns Address setup time (at Read) tRAS 10 — — ns Address hold time (at Read)) tRAH 0 — — ns Address setup time (at Write) tWAS 10 — — ns Address hold time (at Write) tWAH 10 — — ns Write data setup time tWDS 20 — — ns Write data hold time tWDH 10 — — ns CSB setup time (at Read) tRCS 10 — — nsCSB hold time (at Read) tRCH 0 — — nsCSB setup time (at Write) tWCS 10 — — ns CSB hold time (at Write) tWCH 10 — —ns WRB pulse width tWW 10 — — ns FR0B setup time tF0S 3 — — ns FR0B output delay time tF0D — — 20 ns Read data output delay time tRDD — — 30 ns Read data output hold time tRDH 3 — — ns RDB pulse width tRW 35 — — ns CSB disable time tCD CL = 50 pF 10 — — nsFigure 7 Transmit/Receive Buffer Interface (Frame Mode)OKI Semiconductor ML7204-001Transmit/Receive Buffer Interface (DMA Mode)(AVDD = 3.0 to 3.6V, DVDD0, 1, 2 = 3.0 to 3.6 V, AGND = DGND0, 1, 2 = 0.0 V, Ta = –20 to 60°C unless otherwise specified)Parameter Symbol Condition Min.Typ. Max. UnitDMARQ1B setup time tDR1S 3 — — nstDR1RD — — 30 nsDMARQ1B output delay timetDR1FD — — 30 nsAddress setup time (at Read) tRAS 10 — — ns Address hold time (at Read)) tRAH 0 — — ns Address setup time (at Write) tWAS 10 — — ns Address hold time (at Write) tWAH 10 — — ns Write data setup time tWDS 20 — — ns Write data hold time tWDH 10 — — ns ACK0B setup time tAK0S 10 — — nsACK0B hold time tAK0H 0 — — nsACK1B setup time tAK1S 10 — — ns ACK1B hold time tAK1H 10 — — ns WRB pulse width tWW 10 — —ns DMARQ0B setup time tDR0S 3 — — nstDR0RD — — 30 nsDMARQ0B output delay timetDR0FD — — 30 nsRead data output delay time tRDD — — 30 ns Read data output hold time tRDH 3 — — ns RDB pulse width tRW 35 — — ns ACKB disable time tAD CL = 50 pF 10 — — nsFigure 8 Transmit/Receive Buffer Interface (DMA Mode)OKI Semiconductor ML7204-001PIN FUNCTIONAL DESCRIPTIONAIN0N, AIN0P, GSX0, AIN1N, and GSX1These are transmit analog input and transmit gain adjustment pins. AIN0N and AIN1N are connected to inverted input pins of internal transmission amplifiers AMP0 and AMP1, and AIN0P is connected to a noninverting input pin of AMP0. GSX0 and GSX1 are connected to output pins of AMP0 and AMP1. See Figure 9 for the gain adjustment.At power down (PDNB = “0” or SPDN = “1”), outputs of GSX0 and GSX1 are in a high impedance state. When the application does not use AMP0, short-circuit GSX0 and AIN0N and connect AIN0P with AVREF. When not using AMP1, short-circuit GSX1 and AIN1N.VFRO0 and VFRO1These are receive analog output pins. VFRO0 and VFRO1 are connected to output pins of amplifiers AMP2 and AMP3. Output of output signals, VFRO0 and VFRO1, can be selected using the VFRO0 selection register (VFRO0_SEL) and VFRO1 selection register (VFRO1_SEL): When output is selected (“1”), the receive signal is output and when output is not selected (“0”), AVREF (about 1.4 V) is output. In power down mode, these output pins are set to a high impedance state. It is recommended to use output signals through a DC coupling capacitor.(Note)If output selection is changed while the conversation is in progress, a micronoise is generated. Therefore, it is recommended to select output before starting a call and then start a call.Before canceling reset or resetting, it is recommended to select output of VFRO0 and VFRO1 to the AVREF output side.Figure 9 Analog InterfaceOKI Semiconductor ML7204-001 AVREFThis is an output pin of an analog signal ground potential. With the output potential of about 1.4 V, insert bypass capacitors of 2.2 to 4.7 µF (aluminum electrolysis type) and 0.1 µF (ceramic type) in parallel. AVREF outputs 0.0 V at power down. AVREF starts being powered up after power-down reset, the system restarts from ( PDNB = “1” and SPDN = “0”).XI and XOThese are the master clock input pin (XI) and the crystal connection pins for the master clock (XI and XO). Oscillation stops at power down by PDNB or software power down by SPDN. Oscillation starts after power-down is reset and the clock is supplied to the LSI internal section after oscillation stabilization delay time has elapsed (about 21.3 ms). Figure 10 shows a master clock input example.Figure 10 Example of an Oscillation Circuit and Clock InputCLKOUTThis is a 12.288 MHz master clock output pin. (Provided for 100-pin packages only)Since output is disabled in the initial state, set the 12.288 MHz clock output enable control register (CLKOUT_EN) to “1” when clock output is required.PDNBThis is a power-down control input pin. A power-down state can be set by setting this pin to “0”. This pin also functions as an LSI reset pin. To prevent an LSI operation error, use PDNB for the initial power-down reset after power is applied. To put the LSI into a power-down state, fix PDNB to “0” for 250 µs or more.LSI power-down reset can be performed by setting the software power down reset control register SPDN to “0” → “1” → “0”.Power-down is released, the initial mode display register (READY) is set to “1” after 200 ms, and various function setting modes (initial modes) are entered.See Figure 1 for the timings of PDNB, AVREF, XO, and the initial mode.(Note)Turn on the power in a power-down state by PDNB.When using the LSI by inputting a master clock to the XI pin, first maintain the power-down state (PDNB = 0) until power is applied to the digital power supply (DVD0, 1, and 2) and the analog power supply (AVDD) (90% or more) and the master clock is input to the XI pin, then release the power-down state (PDNB = 0 → 1) . In this case also, fix PDNB to “0” for 250 µs or more.OKI Semiconductor ML7204-001 DVDD0, DVDD1, DVDD2, and AVDDThese are power supply pins. DVDD0, DVDD1, and DVDD2 are connected to the power supply of a digital circuit and AVDD is connected to a power supply of an analog circuit. Connect these pins near the LSI and insert bypass capacitors of 10 µF (electrolysis type) and 0.1 µF (ceramic type) between DGND and AGND in parallel.DGND0, DGND1, DGND2, and AGNDThese are ground pins. DGND0, DGND1, and DGND2 are connected to grounds of digital circuits and AGND is connected to a ground of an analog circuit. Connect these pins near the LSI.VREGOUTThis is an output pin of an internal regulator voltage (about 2.5 V).Connect a capacitor of about 0.1 µF (ceramic type) in parallel to about 10 µF (ceramic or tantalum type) between this pin and a ground pin.VBGThis is a reference output pin for an internal regulator.Connect a laminated ceramic capacitor of about 150 pF between this pin and a ground pin.TST0 and TST1These are input pins for testing. At normal use, input “0”.。

IDT7207L35J资料

MILITARY AND COMMERCIAL TEMPERATURE RANGESDECEMBER 1996©1996 Integrated Device Technology, Inc.DSC-3140/25.051The IDT logo is a registered trademark of Integrated Device Techology, Inc.The IDT7207 is a monolithic dual-port memory buffer with internal pointers that load and empty data on a first-in/first-out basis. The device uses Full and Empty flags to prevent data overflow and underflow and expansion logic to allow for unlimited expansion capability in both word size and depth. Data is toggled in and out of the device through the use of the Write (W ) and Read (R ) pins.The devices 9-bit width provides a bit for a control or parity at the user’s option. It also features a Retransmit (RT ) capa-bility that allows the read pointer to be reset to its initial position when RT is pulsed LOW. A Half-Full Flag is available in the single device and width expansion modes.The IDT7207 is fabricated using IDT’s high-speed CMOS technology. It is designed for applications requiring asynchro-nous and simultaneous read/writes in multiprocessing, rate buffering, and other applications.Military grade product is manufactured in compliance with the latest revision of MIL-STD-883, Class B.•32768 x 9 storage capacity •High-speed: 15ns access time •Low power consumption — Active: 660mW (max.)— Power-down: 44mW (max.)•Asynchronous and simultaneous read and write •Fully expandable in both word depth and width•Pin and functionally compatible with IDT720x family •Status Flags: Empty, Half-Full, Full •Retransmit capability•High-performance CMOS technology•Military product compliant to MIL-STD-883, Class B •Industrial temperature range (-40o C to +85o C) is avail-able, tested to military electrical specificationsWRXIDATA INPUTS FUNCTIONAL BLOCK DIAGRAMFor latest information contact IDT's web site at or fax-on-demand at 408-492-8391.5.052PIN CONFIGURATIONSDIP TOP VIEWPLCC/LCC TOP VIEWABSOLUTE MAXIMUM RATINGS (1)NOTE:3140 tbl 011.Stresses greater than those listed under ABSOLUTE MAXIMUM RAT-INGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.RECOMMENDED DC OPERATINGNOTE:3140 tbl 021. 1.5V undershoots are allowed for 10ns once per cycle.DC ELECTRICAL CHARACTERISTICS FOR THE 72073140 tbl 041.Measurements with 0.4 ≤ V IN ≤ V CC .2.R ≥ V IH , 0.4 ≤ V OUT ≤ V CC .3.I CC measurements are made with outputs open (only capacitive loading).4.Tested at f = 20MHz.FF D 2D 1D 0XI Q 0Q 1GNDQ 2Q 3EF XO/HF Vcc FL/RT RS D 3D 8W Q 8D 6D 5D 4D 7Q 5Q 6Q 7Q 43140 drw 02D D D Q Q EF XO /HF 67NC FL /RT RS 76NC Q C c G N Q Q 8N C Q Q R 3140 drw 03AC ELECTRICAL CHARACTERISTICS(1)NOTES:3140 tbl 051.Timings referenced as in AC Test Conditions.2.Pulse widths less than minimum are not allowed.3.Values guaranteed by design, not currently tested.4.Only applies to read data flow-through mode.5.0535.054CAPACITANCE (1)(T A = +25°C, f = 1.0 MHz)1.This parameter is sampled and not 100% tested.2.With output deselected.READ ENABLE (R ) — A read cycle is initiated on the falling edge of the Read Enable (R ), provided the Empty Flag (EF ) is not set. The data is accessed on a First-In/First-Out basis, inde-pendent of any ongoing write operations. After Read Enable (R )goes HIGH, the Data Outputs (Q 0 through Q 8) will return to a high-impedance condition until the next Read operation. When all the data has been read from the FIFO, the Empty Flag (EF )will go LOW, allowing the “final” read cycle but inhibiting further read operations, with the data outputs remaining in a high-impedance state. Once a valid write operation has been accom-plished, the Empty Flag (EF ) will go HIGH after t WEF and a valid Read can then begin. When the FIFO is empty, the internal read pointer is blocked from R so external changes will not affect the FIFO when it is empty.FIRST LOAD/RETRANSMIT (FL /RT ) — This is a dual-purpose input. In the Depth Expansion Mode, this pin is grounded to indicate that it is the first device loaded (see Operating Modes). The Single Device Mode is initiated by grounding the Expansion In (XI ).The IDT7207 can be made to retransmit data when the Retransmit Enable Control (RT ) input is pulsed LOW. A retrans-mit operation will set the internal read pointer to the first location and will not affect the write pointer. The status of the Flags will change depending on the relative locations of the read and write pointers. Read Enable (R ) and Write Enable (W ) must be in the HIGH state during retransmit. This feature is useful when less than 32,768 writes are performed between resets. The retrans-mit feature is not compatible with the Depth Expansion Mode.EXPANSION IN (XI ) — This input is a dual-purpose pin.Expansion In (XI ) is grounded to indicate an operation in the single device mode. Expansion In (XI ) is connected to Expan-sion Out (XO ) of the previous device in the Depth Expansion or Daisy-Chain Mode.Figure 1. Output Load *Includes jig and scope capacitances.SIGNAL DESCRIPTIONS Inputs:DATA IN (D 0–D 8) — Data inputs for 9-bit wide data.Controls:RESET (RS ) — Reset is accomplished whenever the Reset (RS ) input is taken to a LOW state. During reset, both internal read and write pointers are set to the first location. A reset is required after power-up before a write operation can take place.Both the Read Enable (R ) and Write Enable (W ) inputs must be in the HIGH state during the window shown in Figure 2(i.e. t RSS before the rising edge of RS ) and should not change until t RSR after the rising edge of RS .WRITE ENABLE (W ) — A write cycle is initiated on the falling edge of this input if the Full Flag (FF ) is not set. Data set-up and hold times must be adhered-to, with respect to the rising edge of the Write Enable (W ). Data is stored in the RAM array sequentially and independently of any on-going read operation.After half of the memory is filled, and at the falling edge of the next write operation, the Half-Full Flag (HF ) will be set to LOW,and will remain set until the difference between the write pointer and read pointer is less-than or equal to one-half of the total memory of the device. The Half-Full Flag (HF ) is reset by the rising edge of the read operation.To prevent data overflow, the Full Flag (FF ) will go LOW on the falling edge of the last write signal, which inhibits further write operations. Upon the completion of a valid read operation, the Full Flag (FF ) will go HIGH after t RFF , allowing a new valid write to begin. When the FIFO is full, the internal write pointer is blocked from W , so external changes in W will not affect the FIFO when it is full.1.1K Ω30pF*5VD.U.T.OR EQUIVALENT CIRCUIT3140 drw 045.055Outputs:FULL FLAG (FF ) — The Full Flag (FF ) will go LOW, inhibiting further write operations, when the device is full. If the read pointer is not moved after Reset (RS ), the Full Flag (FF ) will go LOW after 32,768 writes.EMPTY FLAG (EF ) — The Empty Flag (EF ) will go LOW,inhibiting further read operations, when the read pointer is equal to the write pointer, indicating that the device is empty.EXPANSION OUT/HALF-FULL FLAG (XO /HF ) — This is a dual-purpose output. In the single device mode, when Expan-sion In (XI ) is grounded, this output acts as an indication of a half-full memory.After half of the memory is filled, and at the falling edge of the next write operation, the Half-Full Flag (HF ) will be set to LOWFigure 2. ResetFigure 3. Asynchronous Write and Read OperationNOTE:1. W and R = V IH around the rising edge of RS .and will remain set until the difference between the write pointer and read pointer is less than or equal to one half of the total memory of the device. The Half-Full Flag (HF ) is then reset by the rising edge of the read operation.In the Depth Expansion Mode, Expansion In (XI ) is con-nected to Expansion Out (XO ) of the previous device. This output acts as a signal to the next device in the Daisy Chain by providing a pulse to the next device when the previous device reaches the last location of memory. There will be an XO pulse when the Write pointer reaches the last location of memory, and an additional XO pulse when the Read pointer reaches the last location of memory.DATA OUTPUTS (Q 0-Q 8) — Q 0-Q 8 are data outputs for 9-bit wide data. These outputs are in a high-impedance condition whenever Read (R ) is in a HIGH state.WRSREFHF , FFt RSCt RSt RSSt RSSt RSRt EFLt HFH , t FFH3140 drw 05RWD0–D 8Q 0–Q 85.056Figure 4. Full FlagTiming From Last Write to First ReadNOTE:1. EF , FF and HF may change status during Retransmit, but flags will be valid at t RTC .Figure 6. RetransmitFigure 5. Empty Flag Timing From Last Read to First WriteRWFFWREFDATA OUTtRTCt RTt RTSRTW ,RHF , EF , FFt RTRFLAG VALID3140 drw 09RTF5.057Figure 8. Minimum Timing for an Full Flag Coincident Write Pulse.Figure 9. Half-Full Flag TimingFigure 10. Expansion OutEFWRFigure 7. Minimum Timing for an Empty Flag Coincident Read Pulse.FFRW3140 drw 11WRHF3140 drw 12WRXO5.058Figure 11. Expansion Incorresponding input control signals of multiple devices. Sta-tus flags (EF , FF and HF ) can be detected from any one device.Figure 13 demonstrates an 18-bit word width by using two IDT7207s. Any word width can be attained by adding addi-tional IDT7207s (Figure 13).Bidirectional OperationApplications which require data buffering between two systems (each system capable of Read and Write operations)can be achieved by pairing IDT7207s as shown in Figure 16.Both Depth Expansion and Width Expansion may be used in this mode.Data Flow-ThroughTwo types of flow-through modes are permitted, a read flow-through and write flow-through mode. For the read flow-through mode (Figure 17), the FIFO permits a reading of a single word after writing one word of data into an empty FIFO.The data is enabled on the bus in (t WEF + t A ) ns after the rising edge of W , called the first write edge, and it remains on the bus until the R line is raised from LOW-to-HIGH, after which the bus would go into a three-state mode after t RHZ ns. The EF line would have a pulse showing temporary deassertion and then would be asserted.In the write flow-through mode (Figure 18), the FIFO permits the writing of a single word of data immediately after reading one word of data from a full FIFO. The R line causes the FF to be deasserted but the W line being LOW causes it to be asserted again in anticipation of a new data word. On the rising edge of W , the new word is loaded in the FIFO. The W line must be toggled when FF is not asserted to write new data in the FIFO and to increment the write pointer.Compound ExpansionThe two expansion techniques described above can be applied together in a straightforward manner to achieve large FIFO arrays (see Figure 15).WRXI3140 drw 14OPERATING MODES:Care must be taken to assure that the appropriate flag is monitored by each system (i.e. FF is monitored on the device where W is used; EF is monitored on the device where R is used). For additional information, refer to Tech Note 8: Oper-ating FIFOs on Full and Empty Boundary Conditions and Tech Note 6: Designing with FIFOs.Single Device ModeA single IDT7207 may be used when the application requirements are for 32,768 words or less. The IDT7207 is in a Single Device Configuration when the Expansion In (XI )control input is grounded (see Figure 12).Depth ExpansionThe IDT7207 can easily be adapted to applications when the requirements are for greater than 32,768 words. Figure 14demonstrates Depth Expansion using three IDT7207s. Any depth can be attained by adding additional IDT7207s. The IDT7207 operates in the Depth Expansion mode when the following conditions are met:1.The first device must be designated by grounding the First Load (FL ) control input.2.All other devices must have FL in the HIGH state.3.The Expansion Out (XO ) pin of each device must be tied to the Expansion In (XI ) pin of the next device. See Figure 14.4.External logic is needed to generate a composite Full Flag (FF ) and Empty Flag (EF ). This requires the ORing of all EF s and ORing of all FF s (i.e. all must be set to generate the correct composite FF or EF ). See Figure 14.5.The Retransmit (RT ) function and Half-Full Flag (HF ) are not available in the Depth Expansion Mode.For additional information, refer to Tech Note 9: Cascading FIFOs or FIFO Modules.USAGE MODES:Width ExpansionWord width may be increased simply by connecting the5.059Figure 12. Block Diagram of 32,768 x 9 FIFO Used in Single Device ModeNOTE:1.Flag detection is accomplished by monitoring the FF , EF and HF signals on either (any) device used in the width expansion configuration.Do not connect any output signals together.Figure 13. Block Diagram of 32,768 x 18 FIFO Memory Used in Width Expansion ModeWRITE (W )FULL FLAG (FF )RESET (RS )READ (R )DATA OUT (Q)EMPTY FLAG (EF )RETRANSMIT (RT )3140 drw 15WRITE (W )FULL FLAG (FF )RESET (RS )DATA (D)IN READ (R )EMPTY FLAG (EF )RETRANSMIT (RT )DATA (Q)OUT 3140 drw 165.0510TRUTH TABLESTABLE I – RESET AND RETRANSMITTABLE II – RESET AND FIRST LOADFigure 14. Block Diagram of 98,304 x 9 FIFO Memory (Depth Expansion)3140 tbl 101. XI is connected to XO of previous device. See Figure 14.2. RS = Reset Input, FL/RT = First Load/Retransmit, EF = Empty Flag Output, FF = Full Flag Output, XI = Expansion Input, HF = Half-Full Flag Output3140 tbl 091. Pointer will Increment if flag is HIGH.DW RSFULLEMPTYV CCR QFigure 17. Read Data Flow-Through ModeFigure 16. Bidirectional FIFO OperationR , W , RS••••D 0–D ND 9-D N D 18-D ND (N-8)-D N••Q 9–Q 17Q 0–Q 83140 drw 18NOTES:1. For depth expansion block see section on Depth Expansion and Figure 14.2. For Flag detection see section on Width Expansion and Figure 13.Figure 15. Compound FIFO ExpansionSYSTEM A SYSTEM BWDATA RINEFDATA OUT3171 drw 20Figure 18. Write Data Flow-Through ModeORDERING INFORMATIONRDATA WINFFDATAOUTX PowerXX SpeedX PackageX Process/Blank Commercial (0°C to +70°C)BMilitary (–55°C to +125°C)Compliant to MIL-STD-883, Class B P D J L Plastic DIP Ceramic DIPPlastic Leaded Chip CarrierLeadless Chip Carrier (Military only)152025303550Commercial Only Commercial Only Military OnlyCommercial Only XXXX Device 720732,768 x 9 FIFOIDTL Low Power Access Time (t A ) Speed in ns3140 drw 22。

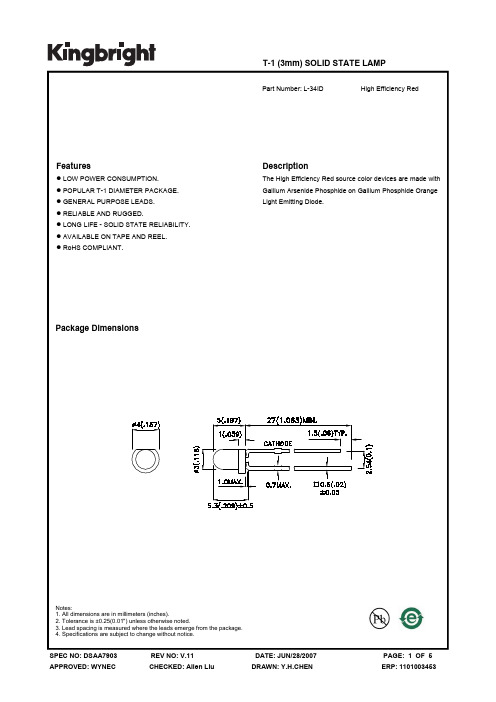

L-34ID资料

元器件交易网

SPEC NO: DSAA7903 APPROVED: WYNEC

REV NO: V.11 CHECKED: Allen Liu

DATE: JUN/28/2007 DRAWN: Y.H.CHEN

PAGE: 4 OF 5 ERP: 1101003453

元器件交易网

Units mW mA mA V

SPEC NO: DSAA7903 APPROVED: WYNEC

REV NO: V.11 CHECKED: Allen Liu

DATE: JUN/28/2007 DRAWN: Y.H.CHEN

PAGE: 2 OF 5 ERP: 1101003453

元器件交易网

Notes: 1.Wavelength: +/-1nm. 2. Forward Voltage: +/-0.1V.

Absolute Maximum Ratings at TA=25°C

Parameter Power dissipation DC Forward Current Peak Forward Current [1] Reverse Voltage Operating/Storage Temperature Lead Solder Temperature [2] Lead Solder Temperature [3]

SPEC NO: DSAA7903 APPROVED: WYNEC

REV NO: V.11 CHECKED: Allen Liu

DATE: JUN/28/2007 DRAWN: Y.H.CHEN

PAGE: 5 OF 5 ERP: 1101003453

Description

The High Efficiency Red source color devices are made with Gallium Arsenide Phosphide on Gallium Phosphide Orange Light Emitting Diode.

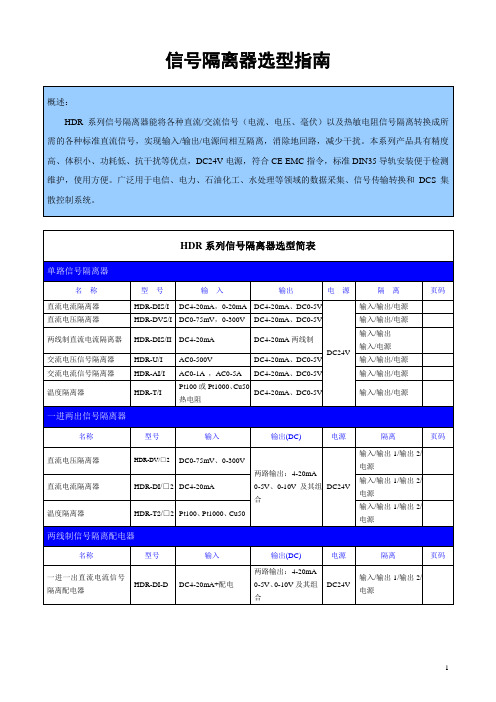

信号隔离器器选型指南

输入/输出1/输出2/电源

HDR-DIS/II

DC4-20mA

DC4-20mA两线制

输入/输出

输入/电源

交流电压信号隔离器

HDR-U/I

AC0-500V

DC4-20mA、DC0-5V输入/输出/电源Fra bibliotek交流电流信号隔离器

HDR-AI/I

AC0-1A,AC0-5A

DC4-20mA、DC0-5V

输入/输出/电源

温度隔离器

HDR-T/I

信号隔离器选型指南

概述:

HDR系列信号隔离器能将各种直流/交流信号(电流、电压、毫伏)以及热敏电阻信号隔离转换成所需的各种标准直流信号,实现输入/输出/电源间相互隔离,消除地回路,减少干扰。本系列产品具有精度高、体积小、功耗低、抗干扰等优点,DC24V电源,符合CE EMC指令,标准DIN35导轨安装便于检测维护,使用方便。广泛用于电信、电力、石油化工、水处理等领域的数据采集、信号传输转换和DCS集散控制系统。

Pt100或Pt1000、Cu50热电阻

DC4-20mA、DC0-5V

输入/输出/电源

一进两出信号隔离器

名称

型号

输入

输出(DC)

电源

隔离

页码

直流电压隔离器

HDR-DV/□2

DC0-75mV、0-300V

两路输出:4-20mA

0-5V、0-10V及其组合

DC24V

输入/输出1/输出2/电源

直流电流隔离器

HDR系列信号隔离器选型简表

单路信号隔离器

名称

型号

输入

输出

电源

隔离

页码

直流电流隔离器

HDR-DIS/I

Badger 35 电子管电路驱动器用户指南说明书

Drive:

Tone controls:

Bass, Middle and Treble tone controls for each channel are postgain and passive cut-style. We recommend starting around 5 and dialing to taste. As you increase Gain and/or Drive we recommend dialing back the Bass to retain clarity and definition in the low-end.

Speaker Outputs: Includes two speaker outputs in parallel and a 3-way selector switch for 4Ω, 8Ω & 16Ω.

Tube-buffered Effects Loop: Performs equally well with pedals and line-level rack gear. For best results ensure that the effects unit is set to unity gain.

On The Edge: Power: 7, Drive: 8, Bass: 4, Middle: 7, Treble: 7, Gain: 4-5

Crunch: Power: 6, Drive: 6, Bass: 4, Middle: 5, Treble: 5, Gain: 6-7

Saturated Lead: Power: 10, Drive: 4, Bass: 3, Middle: 6, Treble: 6, Gain: 8-10

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。