第一版 射频及高速器件 MT_high_speed_compilation

LTE_3GPP_36.213-860(中文版)

3GPP

Release 8

3

3GPP TS 36.213 V8.6.0 (2009-03)

Contents

Foreword ...................................................................................................................................................... 5 1 2 3

Internet

Copyright Notification No part may be reproduced except as authorized by written permission. The copyright and the foregoing restriction extend to reproduction in all media.

© 2009, 3GPP Organizational Partners (ARIB, ATIS, CCSA, ETSI, TTA, TTC). All rights reserved. UMTS™ is a Trade Mark of ETSI registered for the benefit of its members 3GPP™ is a Trade Mark of ETSI registered for the benefit of its Members and of the 3GPP Organizational Partners LTE™ is a Trade Mark of ETSI currently being registered for the benefit of i ts Members and of the 3GPP Organizational Partners GSM® and the GSM logo are registered and owned by the GSM Association

MT3339

Pin Assignment and Descriptions .............................................................................................. 9 2.1 2.2 Pin assignment (top view) .................................................................................................... 9 Pin descriptions .................................................................................................................... 9

ห้องสมุดไป่ตู้

Description Update TFBGA ball map and pin description Update pin-mux and strap information Update RF part description Update System overview Update RF part electrical characteristics Update analog part electrical characteristics Update RF LDO electrical characteristics Update power scheme Add RTC domain power scheme Modify according to YC Chien’s suggestion Update by JN Yang about UART baud rate and SPI/I2C clock rate Update RF related description Update system overview by Andy Lee Update host interface related description Update power scheme Update block diagram Update crystal frequency range Update external LNA related information Update power scheme diagram and EEPROM I2C interface timing diagram Update power related description Update footprint size Change minimum input power to 2.7V Sync PIN naming of DC characteristic table and change minimum input power to 2.8V Update power scheme and RF information Update description of 32K_OUT pin Add ECLK and SYNC description Add 1.2V IO characteristic for TIMER and 32K_OUT and update serial flash size to 128Mb Remove description about factory testing and internal SRAM size Remove description about strap function tcxo on/off 1. Update RTC leakage information to typ 2. Update package dimensions information Update RF related descriptions 1. Remove Vcc description in 6.3.1 2. Add strap pin tldo_sw_sel description Change MAX of VIH for TIMER and 32K_OUT to 3.6V Change description in 5.20 about CLDO off Add RF LNA MIN of VGA gain and MAX of noise figure © 2011 MediaTek Inc. Page 2 of 37

西格玛泰克说明书

C-DIAS PROCESSOR MODULECCP 521C-DIAS Processor ModuleThe CCP 521 processor module runs the control program and thereby represents an essential component of an automation system. The internal DC/DC converter powers all modules on a C-DIAS module carrier. The VARAN bus, the CAN bus, an Ethernet interface or the USB device (Mini USB) can be used as the online interface connection. A 7-segment display and 2 status LEDs provide information on the actual status of the CPU. For program updates, the integrated USB Host interface can be used (USB stick, keyboard). With help from the exchangeable SD card, the entire control program can be easily exchanged. The CCP 521 processor module is designed to be mounted in the control cabinet.CCP 521Compatibility Completely PC-compatible. The CCP 521 works with standard PC BIOS and therefore no SIGMATEK-specific BIOS is needed; the LASAL operating system in provided.26.05.2010Page 1CCP 521C-DIAS PROCESSOR MODULETechnical DataPerformance dataProcessor Addressable I/O/P modules EDGE-Technology X86 compatible VARAN bus: 65,280 CAN bus: 32 C-DIAS bus: 8 No 32-kbyte L1 Cache 256-kbyte L2 Cache AMI 64 Mbytes 512 Kbytes 1-Gbyte micro SD card 1 x USB Host 2.0 (full speed 12 Mbit/s) 1 x USB Device 1.1 1 x Ethernet 1 x CAN 1 x VARAN 1 x C-DIAS Yes Yes Yes Yes (buffering approximately 10 days)Internal I/O Internal cache BIOS Internal program and data memory (DDR2 RAM) Internal remnant data memory Internal storage device (IDE) Interface connectionsData buffer Status display Status LEDs Real-time clockPage 2 a26.05.2010C-DIAS PROCESSOR MODULE Electrical requirementsSupply voltage Current consumption of (+24 V) power supply Starting current Power supply on the C-DIAS bus Current load on C-DIAS bus (power supply for I/O/P modules). Typically 150 mA +18 –30 V DCCCP 521Maximum 500 mAFor a very short time (~20 ms) : 30 A Supplied by the CCP 521 Maximum 1.2 AStandard configurationEthernet 1 CAN bus IP: 10.10.150.1 Station: 00 Subnet-Mask:255.0.0.0 Baud rate: 01 = 500 kBaudProblems can arise if a control is connected to an IP network, which contains modules that do not contain a SIGMATEK operating system. With such devices, Ethernet packets could be sent to the control with such a high frequency (i.e. broadcasts), that the high interrupt load could cause a real-time runtime error. By configuring the packet filter (Firewall or Router) accordingly however, it is possible to connect a network with SIGMATEK hardware to a third party network without triggering the error mentioned above.26.05.2010Page 3CCP 521 MiscellaneousArticle number Hardware version Project back-up StandardC-DIAS PROCESSOR MODULE12-104-521 1.x Internally on the micro SD card UL in preparationEnvironmental conditionsStorage temperature Operating temperature Humidity EMV stabilityShock resistance Protection Type -10 –+85 °C 0 –+50 °C 10 - 90 %, uncondensed According to EN 61000-6-2 (industrial area) EN 60068-2-27 EN 60529 150 m/s? IP 20Page 426.05.2010C-DIAS PROCESSOR MODULECCP 521Mechanical Dimensions104.10 (dimensioning incl. covers)109.212924.9026.05.2010Page 5CCP 521C-DIAS PROCESSOR MODULEConnector LayoutPC通讯底层通讯电源Page 626.05.2010C-DIAS PROCESSOR MODULE X1: USB Device 1.1CCP 521Pin 1 2 3 4 5Assignment +5 V DD+ GNDX2: USB Host 2.0Pin 1 2 3 4 Assignment +5 V DD+ GNDIt should be noted that many USB devices on the market do not comply with the relevant EMC standards for industrial environments. Connecting such a device can lead to malfunctions.X3: EthernetPin 1 2 3 4-5 6 7-8 Assignment TX+ TXRX+ RX-X4: VARANPin 1 2 3 4-5 6 7-8 Assignment TX+ / RX+ TX- / RXRX+ / TX+ RX- / TX-26.05.2010Page 7CCP 521 X5: CAN-BusC-DIAS PROCESSOR MODULE12Pin 1 2 3 4 5 6Assignment CAN A (CAN LOW) CAN B (High) CAN A (CAN LOW) CAN B (High) GND -56X6: Power plug1Pin 1 2Assignment +24 V supply GNDX7: micro SD card Sandisk SDSDQ-1024-KPage 826.05.2010C-DIAS PROCESSOR MODULE Exchanging the micro SD cardCCP 521The micro SD card is located under the LED cover.To exchange the micro SD card, carefully lift the LED cover.The micro SD card is located on the left side and can be disengaged by lightly pressing on the card itself.Remove the micro SD card.26.05.2010Page 9CCP 521C-DIAS PROCESSOR MODULEApplicable connectors USB Device: USB Host: Ethernet: VARAN: CAN-Bus: Supply: 5-pin, type mini B 4-pin, type A 8-pin, RJ45 8-pin, RJ45 6-pin Weidmüller plug, B2L3, 5/6 2-pin Phoenix plug with screw terminal technology MC1, 5/2-ST-3,5 2-pin Phoenix plug with spring terminal FK-MCP1, 5/2-ST-3Page 10 a26.05.2010C-DIAS PROCESSOR MODULECCP 521Status DisplaysEthernet LED Active Link Color Yellow Green Description Lights when data is exchanged over Ethernet Lights when the connection betweenthe two PHYs is established VARAN LED Active Link Color Yellow Green Description Lights when data is exchanged over the VARAN bus Lights when the connection between the two PHYs is established Control LED ERROR DCOK Color Red Green Description Lights when an error occurs (defective USV) Lights when the power supply is OK26.05.2010Page 11CCP 521C-DIAS PROCESSOR MODULEDisplayThe CCP 521 processor module has a 2-digit decimal display (7 segment display) for the following functions:- When configuring the processor module, the parameters are shown in the display. - If an error occurs while running the program or no valid user program is found, the displayshows an error message. Thereby, "Er" (error) and the error code aredisplayed alternatingly. The same error code is also shown in the LASAL status line.- While running the program, the display can be used to show digits using the system vari-able _cpuDisplay. Valid values are 0 to 255; values over 99, however, are not shown and the display remains dark.Page 1226.05.2010C-DIAS PROCESSOR MODULECCP 521CAN Bus SetupThis section explains how to configure a CAN bus correctly. The following parameters must first be set: Station number and data transfer rate. CAN bus station number Each CAN bus station is assigned its own station number. With this station number, data can be exchanged with other stations connected to the bus. Up to 31 stations can be installed in a CANbus system. However, each station number can only be assigned once. CAN bus data transfer rate The data transfer rate (baud rate) for the CAN bus can be set. However, the longer the length of the bus, the smaller the transfer rate that must be selected.Value 00 01 02 03 04 05 06 07Baud rate 615 kBit/s 500 kbit/s 250 kBit/s 125 kBit/s 100 kBit/s 50 kBit/s 20 kBit/s 1 Mbit / sMaximum length 60 m 80 m 160 m 320 m 400 m 800 m 1200 m 30 mThese values are valid for the following cable: 120 ?, Twisted Pair. NOTE: the following is valid for the CAN bus protocol: 1 kBit/s = 1 kBaud.26.05.2010Page 13CCP 521C-DIAS PROCESSOR MODULEConfiguration of the Process ModulePage 1426.05.2010C-DIAS PROCESSOR MODULECCP 521To enter the mode for setting changes, press and hold the SETbutton while the C-IPC is booting. When the following appears in the display:the SET button can be released. After releasing the SET button, the first menu appears in the display.With several short presses of the SET button, it is possible to switch through the various menu points. By pressing the SET button for approximately 1.5 s, the menu is accessed and the setting can be changed with short presses. Once the desired changes are made, press the SET button for about 5 seconds to end the process. If the changes areto be discarded, press the RESET button to restart the C-IPC. The settings for the IP address, subnet mask and gateway are hexadecimal, whereas in the left and right digits, 0 - F must be entered separately. The switch occurs when the SET button is pressed for about 1.5 s. The values from AUTOEXEC.LSL are used as the standard settings; changes are written back to this file. Before this, the original content of the file is written to AUTOEXEC.BAK.26.05.2010Page 15 aCCP 521C-DIAS PROCESSOR MODULEC1 ... CAN PLC station 00 –30 ... Station numberC2 ... CAN PLC baud rate 00 ... 615.000 01 …500.000 02 …250.000 03 …125.000 04 …100.000 05 …50.000 06 …20.000 07 …1.000.000 I1, I2, I3, I4 IP address I1.I2.I3.I4, Hexadecimal 00 –FF respectivelyS1,S2,S3,S4 Subnet Mask S1.S2.S3.S4, hexadecimal 00 –FFrespectivelyG1,G2,G3,G4 Gateway G1,G2.G3.G4, hexadecimal 00 –FF respectivelyPage 16 a26.05.2010C-DIAS PROCESSOR MODULECCP 521CAN Bus TerminationIn a CAN bus system, both end modules must be terminated. This is necessary to avoid transmission errors caused by reflections in the line.Device 1e.g. CPU DCP 080 CAN-Bustermination on terminal moduleDevice 2e.g. Terminal ET 081Device 3Device ne.g. Terminal ET 805 D-SUB-plug with terminating resistorsCAN-Bus-ConnectionsIf the CCP 521 processor module is an end module, it can be terminated by placing a 150Ohm resistor between CAN-A (Low) and CAN-B (High).1 x 150-Ohm resistor26.05.2010Page 17CCP 521C-DIAS PROCESSOR MODULEWiring and Mounting InstructionsEarth ConnectionThe CCP 521 must be connected to earth over the mounting on the back wall of the control cabinet or over the earth terminal provided (C-DIAS module carrier). It is important to create a low-ohm earth connection, only then can error-free operation be guaranteed. The earth connection should have the maximum cross section and the largest electrical surface possible. Any noise signals that reach the CCP 521 over external cables must be filtered out over the earth connection. With a large (electrical) surface, high frequency noise can also be well dissipated.Page 1826.05.2010C-DIAS PROCESSOR MODULECCP 521ShieldingThe wiring for the CAN bus, Ethernet and VARAN bus must be shielded. The low-ohm shielding is either connected at the entry to the control cabinet or directly before the CCP 521 processor module over a large surface (cable grommets, grounding clamps)! Noise signals can thereforebe prohibited from reaching the electronics and affecting the function.ESD ProtectionBefore any device is connected to or disconnected from the CCP 521, the potential with ground should be equalized (by touching the control cabinet or earth terminal). Static electricity (from clothing, footwear) can therefore be reduced.26.05.2010Page 19CCP 521C-DIAS PROCESSOR MODULEProcess DiagramMain voltage onOnline with Lasal Software?noyes Output of a reset of the peripheral modules Output of a reset of the peripheral modulesDeletion of specific data areasDeletion of specific data areasStatus RESETProgram in external memory module functional?noyes Copy program into application program memory Program in internal memory module functional? noyes Status RUN ROM Copy program into application program memory Status CHKSUM or POINTERCall of application programStatus RUN ROMCall of application programPage 2026.05.2010C-DIAS PROCESSOR MODULECCP 521Status and Error MessagesStatus and error messages are shown in the status test of the Lasal Class software. If the CPU has a status display, the status or error number is also show here as well. POINTER or CHKSUM messages can also be shown on the terminal screen.Number 00 Message RUN RAM Definition The user program is currently running in RAM. The display is not affected. 01 RUN ROM The user program in the program memory module was loaded into the RAM and is currently being run. The display is not affected. 02 RUNTIME The total duration of all cyclic objects exceeds the maximum time; the time can beconfigured using 2 system variables: -Runtime: time remaining -SWRuntime: pre-selected value for the runtime counter 03 POINTER Incorrect program pointers were detected before running the user program Possible Causes: Cause/solution- The program memory module ismissing, not programmed or defect.- The program in the user programmemory (RAM) is not executable.- The user program is overwriting asoftware error Solution:- Reprogram the memory module, if theerror reoccurs exchange the module.- Correct programming error04 CHKSUM An invalid checksum was detected before running the user program. Cause/solution: s. POINTER26.05.2010Page 21CCP 52105C-DIAS PROCESSOR MODULEWatchdog The program was interrupted through the watchdog logic. Possible Causes:- User program interrupts blockedover a longer period of time (STI command forgotten)- Programming error in a hardwareinterrupt.- INB, OUTB, INW, OUTW instructions used incorrectly.- The processor is defect.Solution:- Correct programming error.- Exchange CPU. 06 07 GENERAL ERROR PROM DEFECT General error An error has occurred while programming the memory module. Cause:- The program memory module isdefect.- The user program is too large. - The program memory module is missing. Solution:- Exchange the program memorymodule 08 Reset The CPU has received the reset signal and is waiting for further instructions. The user program is not processed. 09 WD DEFEKT The hardware monitoring circuit (watchdog logic) is defect. After power-up, the CPU checks the watchdog logic function. If an error occurs during this test, the CPU deliberately enters an infinite loop from which no further instructions are accepted. 10 11 12 13 14 STOP PROG BUSYS PROGRAM LENGTH PROG END PROG MEMO The memory module was successfully completed. The CPU is currently programming the memory module. Solution: Exchange CPU.Page 2226.05.2010C-DIAS PROCESSOR MODULE15 16 17 STOP BRKPT CPU STOP INT ERROR The CPU was stopped by a breakpoint in the program. The CPU was stopped by the PG software (F6 HALT in status test). The CPU has triggered a false interrupt and stopped the user program or has encountered an unknown instruction while running the program. Cause:CCP 521- A nonexistent operating system wasused.- Stack error (uneven number of PUSHand POP instructions).- The user program was interrupted bya software error. Solution: - Correct programming error. 18 19 2021 22 SINGLE STEP Ready LOAD UNZUL. Modul MEMORY FULL The CPU is insingle step mode and is waiting for further instructions. A module or project has been sent to the CPU and it is ready to run the program. Theprogram has stopped and is receiving a module or project. The CPU has received a module, which does not belong to the project. The operating system memory /Heap) is too small. No more memory could be reserved, when an internal or interface function was called from theapplication. When starting the CPU, a missing module or a module that does not belong to the project was detected. A division error has occurred. Possible Causes:23NOT LINKED24DIV BY 0- Division by 0. - The result of a division does not fit inthe result register. Solution: - Correct programming error.26.05.2010Page 23CCP 52125C-DIAS PROCESSOR MODULEDIAS ERROR An error has occurred accessing a DIAS module. while Possible Causes:- An attempt is made to accessa nonexistent DIAS module.- DIAS bus error.Solution:- Check the DIAS bus - Check the termination resistors. 26 27 28 29 30 WAIT OP PROG OP INSTALLED OS TOO LONG NO OPERATING SYSTEM The CPU is busy. The operating system is currently being reprogrammed. The operating system has been reinstalled. The operating system cannot be loaded; too little memory. Boot loader message. No operating system found in RAM. 31 32 33 34 SEARCH FOR OS NO DEVICE UNUSED CODE MEM ERROR The operating system loaded does not match the hardware configuration. The boot loader is searching for the operating system inRAM.35 36 37MAX IO MODULE LOAD ERROR GENERELLER BS-FEHLER The LASAL Module or project cannot be loaded. A general error has occurred while loading the operating system. An error has occurred in the application memory (user heap).38 39 40 41APPLMEM ERROR OFFLINE APPL LOAD APPL SAVEPage 2426.05.2010C-DIAS PROCESSOR MODULE46 47 50 APPL-LOAD-ERROR APPL-SAVE-ERROR ACCESS-EXCEPTIONERROR BOUND EXCEEDED PRIVILEDGED INSTRUCTION An error has occurred loading the application. whileCCP 521An error has occurred while attempting to save the application. Read or write access of a restricted memory area. (I.e. writing to the NULL pointer). An exception error caused by exceeding the memory limits An unauthorized instruction for the current CPU level was given. For example, setting the segment register. An error has occurred during a floating-point operation. Error from ASMaster. the Intelligent DIRestart; report error to Sigmatek.51 5253 60 64 65 66 67FLOATING POINT ERROR DIAS-RISC-ERROR INTERNAL ERROR FILE ERROR DEBUG ASSERTION FAILED REALTIME RUNTIMEAn internal error has occurred, all applications are stopped. An error has occurred during a file operation. Internal error. The total duration of all real-time objects exceeds the maximum time; the time cannot be configured. 2 ms for 386 CPUs 1 ms for all other CPUsRestart; report error to Sigmatek. Starting from Version 1.1.768BACKGROUND RUNTIMEThe total time for all background objects exceed the maximum time; the time can be configured using two system variables: -BTRuntime: time remaining -SWBTRuntime: pre-selected value for the runtime counter95 96 97 98USER DEFINED 0 USER DEFINED 1 USER DEFINED 2 USER DEFINED 3User-definable code. User-definable code. User-definable code.User-definable code.26.05.2010Page 25CCP 52199 100 101 102 103 104 105 106C-DIAS PROCESSOR MODULEUSER DEFINED 4 C_INIT C_RUNRAM C_RUNROM C_RUNTIME C_READY C_OKC_UNKNOWN_CID The CPU is ready for operation. The CPU is ready for operation. An unknown class from a standalong or embedded object: unknown base class. The operating system class cannot be created; the operating system is probably wrong. Reference to an unknown object in an interpreter program, creation of more than one DCC080 object. The hardware module number is greater than 60. No connection to the required channels. Wrong server attribute. No specific error, recompile all and reload project components. An attempt was made to open an unknown table.Memory allocation error Memory allocation error User-definable code. Initialization start; the configuration is run. The LASAL project was successfully started from RAM. The LASAL project was successfullystarted from ROM.107C_UNKNOWN_CONSTR108C_UNKNOWN_OBJECT109 110 111 112 113 114 115C_UNKNOWN_CHNL C_WRONG_CONNECT C_WRONG_ATTR C_SYNTAX_ERRORC_NO_FILE_OPEN C_OUTOF_NEAR C_OUT OF_FARPage 2626.05.2010C-DIAS PROCESSOR MODULE116 117 224 225 C_INCOMAPTIBLE C_COMPATIBLE LINKING LINKING ERROR An object with the same name exists but has another class. An object with the same name and class exists but must be updated. The application is currently linking. An error has occurred while linking. An error messaged is generated in the LASAL status window. Linking is complete. The operating system is currently being burned into the Flash memory. An error has occurred while burning the operating system. The operatingsystem is currently being installed. The power supply was disconnected; the UPS is active. The operating system is restarted.CCP 521226 230 231 232 240 241 242 243 252 253 254 255LINKING DONE OP BURN OP BURN FAIL OP INSTALL USV-WAIT Reboot LSL SAVE LSL LOAD CONTINUE PRERUN PRERESET CONNECTION BREAKThe application is started. The application is ended.26.05.2010Page 27CCP 521C-DIAS PROCESSOR MODULEApplication exceptionsSRAM and IRQ routines Writing remnant data during interruptroutines is not allowed and leads to a system crash. SRAM and consistency of changed data If more than 32 different sectors are changed (512 byteseach) shortly before shutting down the voltage supply while the user program is writing to the micro SD card, this can sometimes lead to partial loss of remnant data. The file system does not support safe writing through SRAM If files are stored, modified or written on the micro SD card from the user program, these files must always be storedwith a fixed maximum size. Since changes in size and the simultaneous shutdown of the voltage supply can corrupt the file system, a later change in the file size is not allowed. Data Breakpoint This CPU does not support the data breakpoint is a feature.Page 2826.05.2010C-DIAS PROCESSOR MODULECCP 521Recommended Shielding for VARANThe real-time VARAN Ethernet bus system exhibits very robust characteristics in industrial environments. Through the use of IEEE 802.3 standard Ethernet physics, the potentials between an Ethernet line andsending/receiving components are separated. Messages to a bus participant are immediately repeated by the VARAN Manager in the event of an error. The shielding described below is principally recommended. For applications in which the bus is run outside the control cabinet, the correct shielding is required. Especially when for structural reasons, the bus line must be placed next to strong electromagnetic interference. It is recommended to avoid placing Varan bus linesparallel to power cables whenever possible. SIGMATEK recommends the use of CAT5e industrial Ethernet bus cables. For the shielding, an S-FTP cable should be used. An S-FTP bus is a symmetric, multi-wire cable withunshielded pairs. For the total shielding, a combination of foil and braiding is used. A non-laminated variant is recommended.The VARAN cable must be secured at a distance of 20 cm from the connector for protection against vibration!26.05.2010Page 29CCP 521C-DIAS PROCESSOR MODULE1. Wiring from the Control Cabinet to an External VARAN ComponentIf the Ethernet lines are connected from a VARAN component to a VARAN node located outside the control cabinet, the shielding should be placed at the entry point to the control cabinet housing. All noise can then be dissipated before reaching the electronic components.Page 3026.05.2010C-DIAS PROCESSOR MODULECCP 5212. Wiring Outside of the Control CabinetIf a VARAN bus cable must be placed outside of the control cabinet, additional shielding is not required. Outside of the control cabinet,IP67 modules and connectors are used exclusively. These components are very robust and noise resistant. The shielding for all sockets in IP67modules is electrically connected internally or over the housing, whereby voltage spikes are not deflected through the electronics.26.05.2010Page 31CCP 521C-DIAS PROCESSOR MODULE3. Shielding for Wiring Within the Control CabinetSources of strong electromagnetic noise located within the control cabinet (drives, Transformers, etc.) can induce interference in a VARAN bus line. Voltage spikes are dissipated over the metallic housing of aRJ45 connector. Noise is conducted over the control cabinet without additional measures needed on the circuit board of electronic components. To avoid error sources with data exchange, it is recommended that shielding be placed before any electronic components in the control cabinet.Page 3226.05.2010C-DIAS PROCESSOR MODULECCP 5214. Connecting Noise-Generating Components.When connecting power lines to the bus that generate strong electromagnetic noise, the correct shielding is also important. The shielding should be placed before a power element (or group of power elements).26.05.2010Page 33CCP 521C-DIAS PROCESSOR MODULE5. Shielding Between Two Control CabinetsIf two control cabinets must be connected over a VARAN bus, it is recommended that the shielding be located at the entry points of each cabinet. Noise is therefore prevented from reaching the electronic components in both cabinets.Page 3426.05.2010。

MH1Q资料

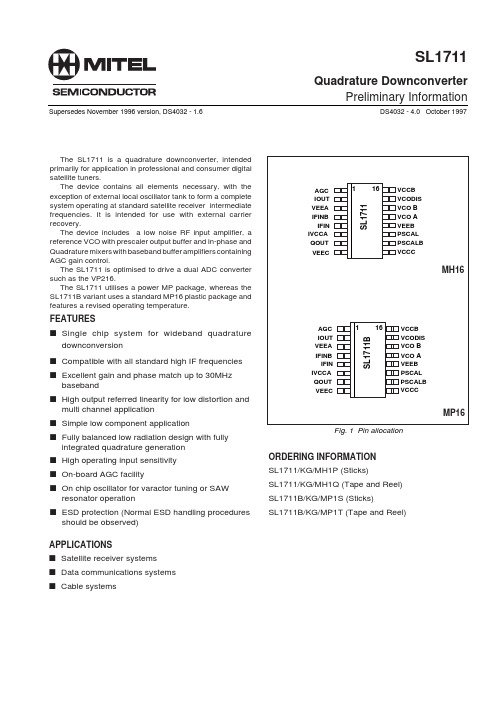

s Single chip system for wideband quadrature downconversion

s Compatible with all standard high IF frequencies

s Excellent gain and phase match up to 30MHz baseband

s High operating input sensitivity

s On-board AGC facility

s On chip oscillator for varactor tuning or SAW resonator operation

s ESD protection (Normal ESD handling procedures should be observed)

Quadrature

÷32

generator

Fig. 2 SL1711 block diagram

2

I OUT Q OUT

PSCAL PSCALB

元器件交易网

SL1711

FUNCTIONAL DESCRIPTION

The SL1711 is a wideband quadrature downconverter, optimised for application in both professional and consumer digital satellite receiver systems and requiring a minimum external component count. It contains all the elements required for constructitor, with the exception of tank circuit for the local oscillator.

常用通信术语缩写解析

缩写中文全称英文全称2G 第二代移动通信系统Second Generation of Wireless Communications Systems 3G 第三代移动通信系统 Third Generation of Wireless Communications Systems 3G-MSC 第三代移动交换中心3G Mobile Switch Center3GPP 第三代合作项目3G Partnership Project3G-SGSN 第三代服务GPRS节点3G Service GPRS NodeA/D 模数转换Analog-to-DigitalAAA 认证、鉴权和计费Authentication、Authorization and AccountingAB 地址总线Address BusABB 模拟基带Anolog BasebandAC 天线校准Antenna CalibrationAC 交流电Alternating CurrentACLR 邻道泄漏比Adjacent Channel Leakage RatioACPR 邻道功率比Adjacent-Channel Power RatioACS 邻道选择性Adjacent Channel SelectivityADC 模数转换器Analog-to-Digital ConverterADI 美国模拟器件公司Analog Devices InstrumentsAEP 有源方向图法Active Element PatternAFC 自动频率控制Auto Frequency ControlAFMS来音频信号AFPCB 音频电路板AGC 自动增益控制Automatic Gain ControlA-GPS 辅助全球定位系统AHB Advanced High Performance BusALC自动电平控制Automatic Level ControlALEV自动电平ALPS 高级线性规划系统Advanced Linear Programming System ALPS 相关逻辑并行运算系统Associative Logic Parallel System AMP放大器AMPS 先进移动电话业务Advanced Mobile Phone Service AMR Adaptive Multi-rate CodecAM-SAP 确认业务接入点ANT天线ANT/SW 天线开关AOA 到达的角度APC自动功率控制API Application Program InterfaceAPI 应用编程接口Application Programming InterfaceARFCH 绝对信道号ARQ 自动请求重发ASIC 专用集成电路Application Specific Integrated Circuit ASIC专用接口集成电路ASK amplifier shift keyingASM Antenna Switch ModuleASP application service providerAST-DET 饱和度检测ATM asynchronous transfer modeATM 异步转移模式ATMS到移动台音频信号ATPC 自动发送功率控制Automatic Transmit Power Control AUC 身份鉴定中心AUX 辅助数据通道Auxiliary Data ChannelAWGN additive white Gaussian noiseBAI Baseband and Audio InterfaceBAP 基带模拟处理器BB 基带BasebandBCCH 广播控制信道BCFE 广播控制功能实体BCH 广播信道Broadcast ChannelBER 误码率Bit Error RateBH 接力切换Baton HandoverBIAS-PA 功放信置BIAS-PD 推动偏置BIC 总线接口BLIGHT 背景灯BMC 广播/多播控制BPSK 二进制相移键控binary phase shift keying BS 基站Base StationBSC 基站控制器Base Site ControllerBT 高斯滤波器带宽与比特率之比BTS 基站收发器base transceiver stationBUZZ 蜂鸣器C/I 载干比CA 码分配CAI 公共空间接口CAMEL 移动网定制应用增强逻辑CBCH 小区广播信道CC 呼叫控制CCBS 用户忙呼叫完成CCH 公共传输信道Common Transport ChannelsCCITT 国际电话与电报咨询委员会International Telephone and Telegraph consultative committeeCCPCH 公共控制物理信道CCRR co-channel rejection ratioCCTrCH 编码复用传输信道Coded Composite Transport ChannelCDMA 码分多址code-division multiple accessCDPD Cellular Digital Packet DataCEPT 欧洲邮电管理委员会CG 计费网管Change Gate WayCIR 允许的信息速率Committed Information RateCM 连接管理模块CM 交叉调制Cross ModulationCMD California Micro DevicesCMM 控制管理维护模块CMOS 互补金属氧化物半导体complementary metal-oxide semiconductor CMRR common-mode rejection ratioCN 核心网子系统CNAP 主叫名显示CODEC 编码器/解码器COFDM 编码正交频分复用Code Or-thogonal Frequency Division Multiplexing CORBA Common Object Request Broker ArchitectureCPCH 公共物理信道CPLD 复杂可编程逻辑设备Complex Programmable Logical DeviceCQI 信道质量指示Channel Quality IndicatorCRC 循环冗余校验CTCH 公共业务信道CW 连续波continuous waveCWDM 粗波分复用Coarse Wavelength Division MultiplexingCWTS 中国无线通信标准Chinese Wireless Telecommunication StandardsDAB 数字音频广播Digital Audio BroadcastingDAI 数字音频接口Digital Audio InterfaceDARPA 美国国防部高级研究计划署DCA 动态信道分配技术Dynamic Channel AllocationDCCH 专用控制信道DCH 专用传输信道Dedicated Transport ChannelsDCIN 外接电源输入DCS distributed communications system or digital cellular system DCS1800 Digital Cellular System at 1800MHzDCU 数据计算单元Data Computation UnitDDC 数字下变频DDS 直接数字频率合成技术Dirrect Digital SynthesisDEC 网络范围内的数据保密性机制DECODER 解码器DECT 数字增强无绳通信系统digital European cordless telephone DEM 解调DemodulationDEMUX 分接DeMutiplexDF 抽取滤波器Decimation FilterDF 判决反馈Decision FeedbackDFMEA Design Failure Mode Effect and AnalysisDFMS 来数据信号DIF 数字中频DIO DSP I/O intercore blockDM 双模Dual ModelsDMA Direct Memory AccessDMAC DMA ControllerDOA 到达的方向Direction Of ArrivalDPCH 专用物理信道DPT 动态分组传输技术Dynamic Packet Transport DRA 动态资源分配Dynamic Resource Allocation DRNC 漂移无线网络控制器DRNS 漂移无线网络子系统DRP 数字射频DSCH 下行共享信道Downlink Shared Channel DSP 数字信号处理Digital Signal ProcessorDSS 数字信号处理子系统DSP Subsystem DTCH 专用业务信道DTMS 到数据信号DTV 数字电视Digital TVDUT device under testDVB-C 数字有线节目DVB-S 数字卫星节目DWDM 密集波分复用Dense Wavelength Division MultiplexingDwPTS 下链导引时隙Downlink Pilot Timeslot Physical ChannelEBI 外部总线接口External Bus InterfaceEBMM External Baseband Memory ModuleECC Emergency Call CodeECT 直接呼叫转移EDGE 改进数据率GSM服务Enhanced Data rate for GSM Evolution EEPROM 电擦除可编程只读存储器electrically erasable programmable read-only memoryEER Envelope Eliminaton RestorationEFR Enhanced Full-rate codecE-GSM Extended GSM frequency bandEIR 移动设备识别寄存器Equipment Identify RegisterEMC 电磁适应性electromagnetic compatibilityEMI 电磁接口electromagnetic interferenceEMI 电磁干扰External Memory InterfaceEPROM 电编程只读存贮器ESD 静电漏电Electro-static dischargeETACS 增强的全接入通信系统ETSI 欧洲电信标准委员会European Telecommunications Standards Institute EUIC 增强用户身份保密性EVITA+ 评估验证集成测试应用平台Evaluation Verification Integration Test Application PlatformEVM 矢量幅度误差EWC 增强无线联盟FACCH 快速随路控制信道FACH 前向接入信道Forward Access ChannelFCA 固定信道分配技术FCC 联邦通信委员会federal communications commissionFCH 频率校正信道FDD 频分复用frequency division duplexFEC 前向纠错Forward Error Correction.FEM 前端模块FER 误帧率frame error rateFET 场效应管field-effect transistorFH 跳频Frequency HoppingFHSS 跳频扩频frequency-hopping, spread spectrumFIFO 先进先出first-in, first-outFIR 有限冲激响应finite impulse responseFM 调频Frequency ModulationFN 闪烁噪声Flicker NoiseFPACH 快速物理接入信道FPLMTS 未来公共陆地移动通信系统Future Public Land Mobile Telecom System FSA 全球IC设计委外代工协会Fabless Semiconductor AssociationFSK frequency shift keyingFSM 有限状态机Finite State MachineFTA Final Type ApprovalFTMS Field Trial Mobile StationFU 功能单元Functional UnitGaAs 砷化镓gallium arsenideGaN gallium nitrideGDA Gate Way Design AutomstitionGFSK Gaussian filtered frequency shift keyingGGSN 通用分组无线业务网关支持节点GIF-SYN 双工中频GMM 通用分组无线业务移动性管理GMSC 网关移动交换中心GMSK Gaussian minimum shift keyingGP 保护时隙GPIB general-purpose interface busGPIO 通用输入输出General Purpose Input/OutputGPRS 通用分组无线业务General Packet Radio ServiceGPS 全球定位系统global positioning systemGSM 全球移动通信系统Global System for Mobile communication GTP 通用分组无线业务隧道协议HBT heterojunction bipolar transistorHDB3 三阶高密度双极性码Trinodal high density bipolar code HDR hardware defined radioHDTV 高清晰度电视High-definition TelevisionHEMT high electron mobility transistorHLR 归属用户位置寄存器HLR 归属位置寄存器HOOK 外接免提状态HPA 高功率线性放大器High Power AmplifierHRF 高通滤波器HRPD High Rate Packet DataHSCSD 高速电路交换数据high-speed circuit-switched dataHSDPA 高速下行链路分组接入High Speed Downlink Package Access HS-DSCH 高速下行共享信道High Speed Downlink Shared Channel HS-SCCH 高速下行共享信道的共享信息信道HTTP 超文本传输协议hypertext transfer protocolHW 硬件HardwareIC 干扰抵消(算法Interference CancellationIC 集成电路integrated circuitICD In-Circuit DebuggerICE In-Circuit EmulatorICTRL 供电电流大小控制端IDU 室内单元Indoor UnitIEMF 感应电动势法Induced Electromotive ForceIF 中频intermediate frequencyIIC/I2C Inter-Integrated Circuit (BusIM 互调intermodulationIM IP多媒体IM 相互调制Inter ModulationIMD 互调失真intermodulation distortionIMEI 国际移动设备识别码IM-MGW IP多媒体媒体网关功能IMS IP多媒体核心网子系统IMSI International Mobile Subscriber IdentityIMT-2000国际移动通信—2000 International Mobile Telecommunication for the 21st centuryInGaP indium gallium phosphideInP indium phosphideIOT Inter operability testIP 知识产权Intellectual PropertyIP internet protocolIPTV 互联网协议电视Internet Protocol TelevisionISCP 干扰信号码功率ISDN 综合业务数字网ISI 多径干扰ISM industrial, scientific, and medicalISUP 综合业务数字网用户部分ITS Incompatible Time Sharing SystemITU 国际电信联盟International Telecommunication UnionIWF 互通功能JD 联合检测Joint DetectionJPEG Joint Photographic Expert Group; glossy image compression format JTAG 标准检测访问接口与边界扫描结构LAC 位置区号LAL 位置区域识别码LAN 本地网络Local Area NetworkLCD 液晶显示器Liquid Crystal DisplayLCR 低码片速率Low Chip RateLDMOS laterally diffused metal oxide siliconLDO 低压差线性稳压器Low Drop Out RegulatorLINC Linear Amplification with Nonlinear ComponentsLLC Logical Link ControlLMDS 本地多点分配业务系统Local Multipoint Distribution ServiceLNA 低噪音放大器low-noise amplifierLO 本机振荡器local oscillatorLOG 逻辑LOGKED 锁机LOMC 本地操作维护中心LOS 信号丢失Loss of SignalLPF 低通滤波器low-pass filterLSI large scale integrationLTCC low-temperature co-fired ceramicLTE 本地终端模拟器Local Terminal EmulatorLTP 长期预测器LTPS 低温多晶硅Low Temperature Poly Silicon LVDS 低压差分技术Low Voltage Differential Signaling M&C 监控Monitor and ControlMAC 媒体访问控制(媒体接入层Media Access Control MAC 测量与控制Measurement and ControlMAI 多址干扰MAP 移动应用部分MBOA 多频段OFDM联盟MCC Mobile Country CodeMCP Multi Chip PackageMDM 调制解调MDS multipoint distribution systemsMDU 调制解调单元Modem UnitME Mobile EquipmentMexE 移动执行环境MF 匹配滤波器Matching FilterMGW 媒体网关MIPS Mega Instructions Per SecondMM 移动性功能管理模块MMDS multichannel multipoint distribution serviceMMI 人机界面Man Machine InterfaceMMIC 单片微波集成电路monolithic microwave integrated circuitMMS 多媒体信息服务Multimedia Messaging ServiceMMSE-BLE最小均方误差块均衡Minimum Mean Square Error Block Linear Equalizer MNC Mobile Network CodeMOM 矩量法Method of MomentMOSFET metal-oxide semiconductor field-effect transistorMP3 Audio Player 3 of MPEG 1 and 2MPEG Moving Picture Experts GroupMS 移动台Mobile StationMSC 移动交换中心MSIN 移动台识别码MSK 最小移频键控MSM Mobile Station ModemMTMRA 多发多收天线MTP 消息传输部分MUD 多用户检测Multiuser DetectionMUX 复分接器Multiplexer/DemultiplexerNAM 号码分配模块NAS 非接入层NBAP 节点B应用协议NCO 数控振荡器Numerically Control Oscillator NFR 陷频滤波测试Notch Filter RejectionNMS 网络管理系统Network management system NNMC 全国网管中心NRI 网络资源标识NTC Negative Temperature CoefficientNZIF Near ZIFODB 运营商闭锁业务ODU 数字微波收发信机Outdoor UnitOEM Original equipment ManufacturerOFDM 正交频分复用Orthogonal Frenquency Division MultiplexingOLED 有机发光显示器Organic Light Emitting DisplayOMC 操作管理中心Operation And Management CenterOMT 操作管理终端Operation And Management TerminalONSRQ 免提开关控制OO-VHDL 面向对象的VHDL Object Oriented VHDLOSA 开放业务接入OSR 过采样比Over Sampling RatioOTA 空中下载技术Over The AirOVSF 正交可变扩频因子Orthogonal Variable Spreading Factor OXCO oven controlled crystal oscillatorPA 功率放大器Power AmplifierPAE power added efficiencyPAN 个人接入网Personal Acess NetworkPAR peak-to-average ratioPAS 个人介入系统Personal Acess SystemPC 功率控制Power ControlPCB 印制电路板Printed Circuit BoardPCCH 寻呼控制信道P-CCPCH 主公共控制物理信道PCDE 峰值码域误差Peak Code Domain ErrorPCH 寻呼信道Paging ChannelPCM 脉冲编码调制pulse-code modulationPCN personal communications networkPCS Personal Communication SystemPCU 程序控制单元Program Control UnitPDA Personal Digital AssistantPDATA 并行数据PDC 个人数字蜂窝电话Personal Digital Cellular PDCP 分组数据汇聚协议Package Data Collect Protocol PDH 准同步数字系列Plesiochronous Digital Hierarchy PDP Packet Data ProtocolPDPCH 分组数据物理信道PDSCH 物理下行链路共享信道PECL positive emitter-coupled logicPGA 可编程功率放大器Programmable Gain Amplifier PhCH 物理信道Physical ChannelPHEMT pseudomorphic high-electron-mobility transistor PHS 个人手持电话系统Personal Handy-phone SystemPI 外围设备连接Peripheral InterconnectPICH 寻呼指示信道PIN 个人识别码PIO 并行输入输出Parallel I/OPLL 索相环Phase-Locked LoopPLMN 公共陆地移动网Public Land Mobile NetworkPMIC 电源管理集成电路Power Management Integrated Circuit PMU 功率管理单元Power Management UnitPNMC 省级网管中心PRACH Physical-Random Access ChannelPRBS 伪随机二进制序列Pseudo-random Binary Pulse Sequence PROM 可编程只读存储器PS Philips SemiconductorPSAM 导频符号辅助调制Pilot Symbol Assisted ModulationPSK phase shift keyingPSTN 公用交换电话网Public Switching Telephone NetworkPVC 永久虚电路PVCO voltage-controlled oscillatorPWDM 极化波复用Polarization Wavelength Division Multiplexing PWM 脉宽调制Pulse Width ModulationQAM quadrature amplitude modulationQASK quadrature amplitude shift keyingQoS 服务质量要求Quality of ServiceQPSK 正交相移键控Quadrature Phase Shift KeyingRAB 无线接入承载Radio Access BearerRACH 随机接入信道Random Access ChannelRAM 随机存储器Random Access MemoryRAN 无线接入网RANAP 无线接入网络应用实体RAT Radio Access TechnologyRBER 残余比特误码率Remainder Bit Error RateRBW 中频分辨率带宽RCCC 并行级联分组码RF 射频Radio FrequencyRFADAT 射频频率合成器数据RFAENB 射频频率合成器启动RFCI RAB子码流组合指示RFDRXM 双路射频收模块Radio Frequency Double Receiver Module RFDTXM 双路射频发模块Radio Frequency Double Transmitter Module RFI 射频接口radio frequency interferenceRFIC 射频集成电路radio frequency integrated circuitRFID 射频标签Radio Frequency IdentificationRFTRXU 射频收发信机模块Radio Frequency Transceiver UnitRISC reduced instruction set computingRLC 无线链路控制RLP 无线链路协议RMS Record Management SystemRMS 均方根值RNC 无线网络控制器RNS 无线网络子系统ROM 只读存储器Read Only MemoryRRC 平方根升余弦Root-Raised CosineRRC 无线资源控制RRM 无线资源管理RRM 无线资源管理Radio Resource ManagementRSC 循环系统卷积码Recursive Systematic ConvolutionalRSCP 接收信号码功率 RSL 接收信号电平 Received signal level RSSI 接收信号强度指示 Received signal strength indication RSU 倒换单元 Redundancy Switch Unit RSVP 资源预留协议 RTK Real Time Kernel RTK-E Real Time Kernel, embedded RTT 无线传输技术 RU Resource Unit RX 接收机 Receiver RXIFN 接收中频信号负 RXIFP 接收中频信号正 RXON 接收开 RXVCO 收信压控振荡器 SA 智能天线 Smart Antenna SABP 服务区广播协议 SACCH 慢速随路控制信道 SAP 服务接入点 SAR 电磁波吸收比值 Specific Absorption Rate SAT 饱和度 SAW 地面声波 Surface Acoustic Wave SBDM "Swift" Baseband Digital Module SC 系统控制器 System Controller S-CCPCH 辅助公共控制物理信道 SCDMA 同步码分多址 Synchronous Code Division Multiplexing Access SCH 同步信道 Synchronization Channel SCIF 系统控制器界面 System Controller Interface SCLK 串行时钟 SCM 信号编码调制 signal code modulation SCTP 简单控制传输协议 SD Sigma Delta 调制 Sigma Delta Modulation SDAT 串行数据 SDCCH 快速随路控制信道 SDH 同步数字系列Synchronous Digital Hierarchy SDM 统计复用 Statistical Division Multiplexing SDR 软件定义无线电 Softwaer Defined Radio SDU 业务数据单元 SEMC 安全性管理中心Security Management Center SF 扩频系数 Spreading Factor SFDR 无杂散动态范围Spurs Free Dynamic Range SFN System Frame Number SGSN 支持 GPRS 的功能实体SGW 信令网关 SiGe silicon-germaniumSIM 用户识别模块 Subscriber Identity Module SIP 系统级封装 SIR 信干比Signal Interference Ratio SLIP 串行线路网际协议 Serial Line Internet Protocol SM 会话管理功能模块 SMCP "Swift" Multi-Chip Package Module SMMI "Swift"人机接口界面 "Swift" Man-Machine Interface Module SMOC 调制解调器 SMR specialized mobile radio SMS Short Message Service (Point-to-Point SMSCB Short Message Service Cell Broadcast SMT surface-mount technology or surface-mount toroidal SNDR 信号与噪声畸变比 Signal to Noise- Distorsion Ratio SNMP 简单网络管理协议 Simple network management protocol. SNR 信噪比 signal-to-noise ratio SoC 系统级芯片 SOC 信号操作控制器 Signal Operation Control SoC 片上系统(系统单芯片)System-on-Chip SOIC small-outline integrated circuit SONET synchronous optical network SPDT single-pole double-throw SPI 串行外围接口 Serial Peripheral Interface SRAM 静态随机存储器 SRB 信令无线承载 SRNC 服务无线网络控制 SRNS 服务无线网络子系统 SS 同步偏移控制符号 Synchronization Shift SS 辅助服务 Supplementary Service SSB single side band SSCF 具体业务协调功能 SSCOP 特定业务面向连接协议 SSPA solid state power amplifiers SSPA 固态功率放大器 Solid State Power Amplifier STM SDH 光同步传输模式 SVC 交换虚电路 SW 开关 SWDC 未调整电压 SW-RF 射频开关SYNSTR 频率合成器启动 TACS 全选址通信系统 Total Access Communications System TACS 全接入移动通信系统 TC 测试用例 Test case TCH Traffic Channel TCP transmission control protocolTDD-LCR Time Division Duplex – Low Chip Rate TDK 东京电气化学工业株式会社 Tokyo Dengikagaku Kogyo K.K TDMA time-division multiple access TD-SCDMA 时分同步码分多址技术 Time Division-Synchronous Code Division Multiple Access TE 终端设备 Terminal Equipment TEMP 温度监测 TETRA trans European trunked radio TF 传输格式 Transport Format TFC 传输格式组合 Transport Format Combination TFCI 传输格式组合指示 Transport Format Combination Indicator TFCS 传输格式组合集合 Transport Format Combination Set TFD 薄膜二极管 Thin Film Diode TFI 传输格式显示 Transport Format Indicator TFS 传输格式集合 Transport Format Set THD 总谐波失真 Total Harmonics Distortion TMEM TD-SCDMA Modem Emulation Module TMU Tandem Mailbox Unit TP 测试点 Test Point TPC 传输功率控制 Transmitter Power Control TrBK 传输块 Transport Block TrCH 传输信道 Transport Channel TSG 技术规范部 Technical Specification Group TSM TD-SCDMA System for Mobile communication TSMB Two-Slot Mother Board TTD Test, Trace and Debug (tool TTI 传输时间间隔 Transmission Time Interval TTL transistor — transistor logic TX Transmitter, Transmission TXC 发信控制 Transmitter Control TXCO temperature-compensated crystal oscillator TXVCO 发信压控振荡器 UART Universal Asynchronous Receiver / Transmitter UCA 均匀圆阵 Uniform Circular Array UE 用户终端 User Equipment UHF 超高频 UltraHigh Frequency ULA 均匀直线阵 Uniform Linear Array UM-SAP 非确认业务接入点 UMTS 公用移动电话系统 UniversalMobile Telecommunications Service UpPTS 上行导频时隙 USB 通用串行总线Universal Serial Bus USCH 上行共享信道 Uplink Shared Channel UTRAN 无线网络子系统 UWB 超宽带 Ultra WidebandVBW 视频分辨率带宽 VCXO 压控晶体振荡器 Voltage Control X-tal [Crystal] Oscillator VDSM 超深亚微米 Very Deep Submicron VHDL 高速集成电路硬件描述语言 VHSIC Hardware Description Language VHE 虚拟归属环境 VHSIC 高速集成电路Very High Speed Integrated Circuit VLR 拜访用户位置寄存器 Visiter Location Register VLR 拜访位置寄存器 VOFDM 正交矢量频分复用 Vector Orthogonal Frequency Division Multiplexing VSAT 小孔径终端 very small aperture terminal (satellite service VSB 残余边带 vestigial side band VSWR 电压驻波比 Voltages Standing Wave Ratio WAD 无线广告业务 Wireless AD WAFI Walkthrough and Fagan Inspection WAP 无线应用协议 Wireless Application Protocol WBMP 无线位图Wireless Bitmap WCDMA 宽带码分多址技术 wideband code-division multiple access WD-CP 看门狗脉冲 WIFI 无线相容性认证 Wireless Fidelity WiMAX 全球微波接入互操作性 Worldwide Interoperability for Microwave Access WLAN 无线局域网wireless local area network WMF 白化匹配滤波 White Matching Filter ZF-BLE 迫零块均衡(算法) Zero Forcing Block Linear Equalizer ZIF 零中频 Zero Intermediate Frequency。

LTTJ资料

2 0.02 0.02 0.2

(Notes 6, 7, 10) (Note 11)

q

1 0.2 5 1 0 5 100 50 250 1.05

q q

V+

V MΩ MΩ

400 5 600

µV/V mV µV/V

1967f

元器件交易网

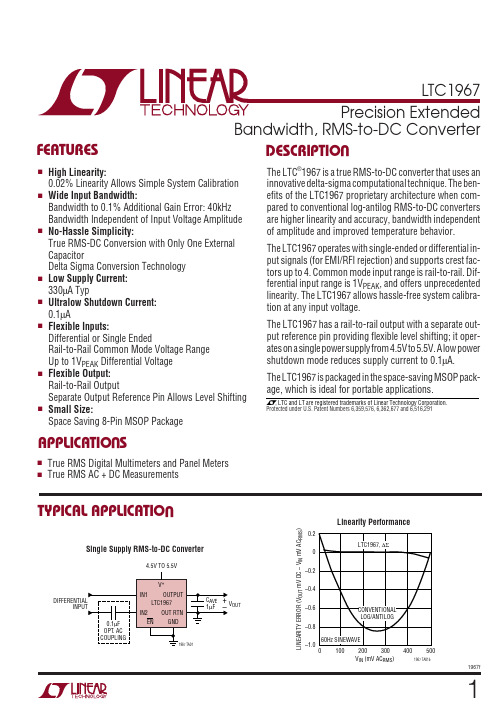

LTC1967

ELECTRICAL CHARACTERISTICS

CONDITIONS 50Hz to 5kHz Input (Notes 6, 7)

q

Additional Error vs Crest Factor (CF) 60Hz Fundamental, 200mVRMS 60Hz Fundamental, 200mVRMS Accuracy = 1% (Note 14) Average, Differential (Note 12) Average, Common Mode (Note 12) (Note 13) (Note 9)

, LTC and LT are registered trademarks of Linear Technology Corporation. Protected under U.S. Patent Numbers 6,359,576, 6,362,677 and 6,516,291

s

s

s

s

s

s

U APPLICATIO S

0.2 LTC1967, ∆Σ 0 –0.2 –0.4 –0.6 –0.8 –1.0 60Hz SINEWAVE 0 100 200 300 VIN (mV ACRMS) 400 500

1967 TA01b

Single Supply RMS-to-DC Converter

88E6122_88E6121-Datasheet-Part 1

Link Street™ 88E6122/88E6121 Datasheet Part 1 of 3: Overview, Pinout, Applications, Mechanical and Electrical Specifications

Doc. No. MV-S103526-01 Rev. -Page 2

CONFIDENTIAL

Document Classification: Restricted Information Not Approved by Document Control - For Review Only

Copyright © 2006 Marvell April 14, 2006, Draft

Final

This document contains specifications on a product that is in final release. Specifications may

Information change without notice. Contact Marvell Field Application Engineers for more information.

Document Status

Advance

This document contains design specifications for initial product development. Specifications may

Information change without notice. Contact Marvell Field Application Engineers for more information.

TSU16AK

FEATURESn Input PortŸRGB analog input portŸFull SOG and composite sync support,including copy protected signalsŸHigh-speed 8-bit triple-ADC with low jitter PLL operates up to 220 MHzn Display Processing EngineŸPatent-pending Hybrid Image Resolution ConverterŸVariable sharpness controlŸInterlaced to progressive conversionŸPatent-pending Dynamic Frame-Rate generator (DFR) – short line storage frame extensiontechnique eliminates short lines in outputframesŸMedia Window Enhancement (MWE)NoteŸPeaking and coring functions for sharpness enhancement and noise reductionŸBrightness and contrast controlŸProgrammable 10-bit gamma correctionŸsRGB supportn Auto-Detection / Auto-Tune SupportŸAuto input signal format (SOG, composite, separated HSYNC, and VSYNC)ŸInput mode detection support analyzes input video signal (H/V polarity, H/V frequency,interlace/field detect) – extensive statusregisters support robust detection of all VESAand IBM modesŸAuto-tuning function including support for phase selection, image position, offset & gainand jitter detectionŸSmart screen-fittingn On-screen display controller (OSD)ŸBuilt-in OSD generator with 291 character font programmable RAMŸInternal OSD rotation degree of 90 and 270ŸSupports 2/4/8 multi-color fontsŸSupports 8/16/256 color paletteŸSupports 1K code attributesŸGradient color functionŸHardware button animation functionŸPattern generator for production testŸSupports OSD MUX and alpha blendingcapabilityn Output Display InterfaceŸSupports 6/8-bit LVDS panel interfaceŸSupports up to SXGA display resolution with up to 135 MHz dot clockŸSpread spectrum output frequency for EMI suppressionŸPWM backlight intensity controln DPMS SupportŸFull green mode DPMS supportŸLow standby power (< 16mA)n External Connection/ComponentŸSupports DDR direct bus (up to 40MHz) and serial bus (up to 400Kbit/sec)Note:The optional MWE function is available with TSU16AWK.BLOCK DIAGRAMMCU XTAL/EXT CLK To PanelAnalog RGBHSYNC/VSYNCGENERAL DESCRIPTIONThe TSU16AK is total solution graphics processing IC for LCD monitors with panel resolutions up to SXGA. It is configured with a high-speed integrated triple-ADC/PLL, a high quality display processing engine, and an integrated output display interface that can support LVDS panel interface format. To further reduce system costs, the TSU16AK also integrates intelligent power management control capability for green-mode requirements and spread-spectrum support for EMI management.The TSU16AK incorporates the world’s first coherent oversampled RGB graphics ADC in a monitor controller system1. The oversampling ADC samples the input RGB signals at a frequency that is much higher than the signal source pixel rate. This can preserve details in the video signal that ordinarily would be lost due to input signal jitter or bandwidth limitations in non-oversampled systems.The TSU16AK also incorporates a new Dynamic Frame Rate (DFR) generator2for the digital output video to the display panel that preserves the advantages of a fixed output clock rate, while eliminating the output end of frame short-line.1,2 Patent PendingPIN DIAGRAM (TSU16AK)L V A 3MV D D P G N D L V A C K P L V A 2M L V A C K M L V A 2P L V A 1P L V A 1M L V A 0P L V A 0M G N D G N D V D D C L V B 3P L V B 3M L V B C K P L V B C K M L V B 2P L V B 2M L V B 1P L V B 1M V D D P G N D L V B 0P G N D N C N C G N D N C N C N C A V D D _A D C N C N C N C R E X T A V D D _P L L G N D B I N 0M B I N 0P G I N 0M G I N 0P S O G I N 0R I N 0M R I N 0P G N DV D D P VDDP PWM1PWM0RDZ/SCL WRZ/SDA G N D A V D D _A D C A V D D _A D C G N DPIN DESCRIPTIONCPU InterfacePin Name Pin Type Function PinHardware reset; active high 32 HWRESET Schmitt Trigger Inputw/ 5V-tolerantCS Input w/ 5V-tolerant 3 Wire Serial Bus Chip Select; active high 69 SDA I/O w/ 5V-tolerant 3 Wire Serial Bus Data; 4mA driving strength 70 SCL Input w/ 5V-tolerant 3 Wire Serial Bus Clock 71 INT Output CPU interrupt; 4mA driving strength 72 AD3 I/O w/ 5V-tolerant DDR direct bus AD3; 4mA driving strength 31 AD2 I/O w/ 5V-tolerant DDR direct bus AD2; 8mA driving strength 78 AD1 I/O w/ 5V-tolerant DDR direct bus AD1; 8mA driving strength 77 AD0 I/O w/ 5V-tolerant DDR direct bus AD0; 4mA driving strength 30 ALE I w/ 5V-tolerant DDR direct bus ALE; active high 69 RDZ I w/ 5V-tolerant DDR direct bus RDZ; active low 71 WRZ I w/ 5V-tolerant DDR direct bus WRZ; active low 706 BUSTYPE Input (not 5V-tolerant) Bus typeŸLow : Serial busŸHigh : DDR Direct busAnalog InterfacePin Name Pin Type Function PinAnalog HSYNC input 37 HSYNC0 Schmitt Trigger Inputw/ 5V-tolerantVSYNC0 Schmitt Trigger InputAnalog VSYNC input 38 w/ 5V-tolerantREFP Internal ADC top de-coupling pin 66 REFM Internal ADC bottom de-coupling pin 67 RIN0P Analog Input Analog red input 63 RIN0M Analog Input Reference ground for analog red input 62 SOGIN0 Analog Input Sync-on-green input 61 GIN0P Analog Input Analog green input 60 GIN0M Analog Input Reference ground for analog green input 59 BIN0P Analog Input Analog blue input 58 BIN0M Analog Input Reference ground for analog blue input 57 REXT External resistor 390 ohm to AVDD_ADC 52LVDS InterfacePin Name Pin Type Function Pin LVA0M Output A-Link Negative LVDS Differential Data Output 113 LVA0P Output A-Link Positive LVDS Differential Data Output 112 LVA1M Output A-Link Negative LVDS Differential Data Output 111 LVA1P Output A-Link Positive LVDS Differential Data Output 110 LVA2M Output A-Link Negative LVDS Differential Data Output 109 LVA2P Output A-Link Positive LVDS Differential Data Output 108 LVA3M Output A-Link Negative LVDS Differential Data Output 103 LVA3P Output A-Link Positive LVDS Differential Data Output 102 LVACKM Output A-Link Negative LVDS Differential Clock Output 107 LVACKP Output A-Link Positive LVDS Differential Clock Output 106 LVB0M Output B-Link Negative LVDS Differential Data Output 1 LVB0P Output B-Link Positive LVDS Differential Data Output 128 LVB1M Output B-Link Negative LVDS Differential Data Output 125 LVB1P Output B-Link Positive LVDS Differential Data Output 124 LVB2M Output B-Link Negative LVDS Differential Data Output 123 LVB2P Output B-Link Positive LVDS Differential Data Output 122 LVB3M Output B-Link Negative LVDS Differential Data Output 119 LVB3P Output B-Link Positive LVDS Differential Data Output 118 LVBCKM Output B-Link Negative LVDS Differential Clock Output 121 LVBCKP Output B-Link Positive LVDS Differential Clock Output 120GPO InterfacePin Name Pin Type Function Pin PWM1 Output PWM1; 4mA driving strength 74 PWM0 Output PWM0; 4mA driving strength 73Misc. InterfacePin Name Pin Type Function Pin BYPASS For External Bypass Capacitor 3 XIN Crystal Oscillator Input Xin 33Xout 34 XOUT Crystal OscillatorOutputPower PinsPin Name Pin Type Function PinAVDD_ADC 3.3V Power ADC Power 45, 51, 55, 65AVDD_PLL 3.3V Power PLL Power 53AVDD_MPLL 3.3V Power MPLL Power 35VDDP 3.3V Power Digital Output Power 11, 21, 84, 94, 104, 114,126VDDC 1.8V Power Digital Core Power 18, 87, 97, 117GND Ground Ground 2, 10, 19, 20, 36, 39, 42,48, 54, 56, 64, 68, 85, 86,95, 96, 105, 115, 116, 127No ConnectsPin Name Pin Type Function PinNC No Connect. Leave These PinsFloating. 4, 5, 7-9, 12-17, 22-29, 40, 41, 43, 44, 46, 47, 49, 50, 75, 76, 79-83, 88-93, 98-101ELECTRICAL SPECIFICATIONS Analog Interface CharacteristicsAbsolute Maximum Ratingsoperation sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.MSTAR SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. NO RESPONSIBILITY IS ASSUMED BY MSTAR SEMICONDUCTOR ARISING OUT OF THE APPLICATION OR USER OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.Electrostatic charges accumulate on both test equipment and human body and can discharge without detection. TSU16AK comes with ESD protection circuitry, however, the device may be permanently damaged when subjected to high energy discharges. The device should be handled with proper ESD precautions to prevent malfunction and performance degradation.REVISION HISTORYDocument Description Date TSU16AK_ds_v01 ŸInitial release Aug 2004 TSU16AK_ds_v02 ŸUpdated Register Table Sep 2004TSU16AK_ds_v03 ŸUpdated MWE related informationŸAdded lead-free information to Ordering GuideŸUpdated Register Table Oct 2004MECHANICAL DIMENSIONSREGISTER DESCRIPTIONGeneral Control RegisterIndex Mnemonic Bits Description00hREGBK 7:0 Default : Access : R/WPORR 7 Power On Reset Ready (read only).0: Not ready.1: Ready.6:4 Reserved.AINC 3 Serial bus address auto increase.0: Enable.1: Disable.BUST 2 BUS type (read only).0: Direct bus.1: Serial bus.REGBK[1:0] 1:0 Register Bank Select.00: Register of digital image processor.01: Register of internal ADC, DVI/HDCP receiver.10: Register of timing controller.11: Register of MWE function.ADC Register (Bank = 01)ADC Register (Bank=01)Index Mnemonic Bits DescriptionDBFC 7:0 Default : 0x00 Access : R/W01h- 7:1 Reserved.DBVB 0 Double Buffer load at Vertical Blanking.0: Disable.1: Enable.02hPLLDIVM 7:0 Default : 0x69 Access : R/WPLLDIV[11:4] 7:0 PLL Divider ratio.When bank 1 register 3Dh[4] = 0ADC PLL will multiply the horizontal line frequency byPLLDIV[11:0] + 3 to generate the ADC sampling clock.When bank 1 register 3Dh[4] = 1ADC PLL will multiply the horizontal line frequency by(PLLDIV[11:0] +3)*2 to generate the ADC sampling clock.03hPLLDIVL 7:0 Default : 0x50 Access : R/WPLLDIV[3:0] 7:4 PLL Divider ratio.Please see the description of PLLDIV[11:4].- 3 Reserved.STAT[2:0] 2:0 Status select. Selects 1/8 internal PLL status values to readfrom register 16h.ADC Register (Bank=01)04hREDGAIN 7:0 Default : 0x80 Access : R/WREDGAIN 7:0 Red channel Gain adjust.05hGRNGAIN 7:0 Default : 0x80 Access : R/WGRNGAIN 7:0 Green channel Gain adjust.06hBLUGAIN 7:0 Default : 0x80 Access : R/WBLUGAIN 7:0 Blue channel Gain adjust.07hREDOFST 7:0 Default : 0x80 Access : R/WREDOFST 7:0 Red channel Offset adjust.08hGRNOFST 7:0 Default : 0x80 Access : R/WGRNOFST 7:0 Green channel Offset adjust.09hBLUOFST 7:0 Default : 0x80 Access : R/WBLUOFST 7:0 Blue channel Offset adjust.0AhCLPACE 7:0 Default: 0x05 Access : R/WCLPACE 7:0 Clamp Placement based on ADC clock.0BhCLDUR 7:0 Default : 0x05 Access : R/WCLDUR 7:0 Clamp Duration based on ADC clock.0ChGCTRL 7:0 Default : 0x82 Access : R/WHSP 7 Input HSYNC Polarity.0: Active low.1: Active high.ECLK 6 External Clock.0: ADC clock from internal ADC PLL.1: ADC clock from external clock.HSLE 5 HS Lock Edge. Determines which edge of HSYNC the ADC PLLwill lock to, assuming HSP is set correctly.0: Leading edge of HSYNC.1: Trailing edge of HSYNC.CLPE 4 Clamp reference Edge.0: Trailing edge of HSYNC.1: Leading edge of HSYNC.CCDIS 3 Disable PLL watchdog timer.0: Always enable clamp.1: Disable clamp during active coast.WDIS 2 Disable watchdog timer.0: Enable PLL watchdog timer. A watchdog timer is used toreset the ADC PLL when the PLL remains much higher thanPLLDIV*HSYNC_FREQ for a predetermined period.See WDTOL (Register 30h).ADC Register (Bank=01)1: Disable PLL watchdog timer (should only be used whenDPL_S = 0).CSTP 1 Coast Polarity.0: Active low.1: Active high.DRBS 0 DVI input Red/Blue swap (DVI features only).0: Normal.1: Swap.BWCOEF 7:0 Default : 0x02 Access : R/W0DhDMODE[1:0] 7:6 Damping coefficient mode control.00: Default value – backward compatibility mode.01: Reserved.10: Automatic DCOEF control (recommended mode).11: Reserved.BWCOEF[5:0] 5:0 PLL loop filter control.0EhFCOEF 7:0 Default : 0x09 Access : R/W7:5 Reserved.FREQCOEF[4:0] 4:0 PLL loop filter control.OFhDCOEF 7:0 Default : 0x05 Access : R/W7:4 Reserved.DAMPCOEF[3:0] 3:0 PLL loop filter control.CLKCTRL1 7:0 Default : 0x08 Access : R/W10h- 7 Reserved.PHASE[6:0] 6:0 Clock Phase adjust (should be always set to PHASECC + 8).11hCLKCTRL2 7:0 Default : 0x00 Access : R/W- 7 Reserved.PHASECC[6:0] 6:0 Clock phase adjust for ADC sampling time point. Phase isadjustable between 0 and 360° in 5.6° steps.12hVCOCTRL 7:0 Default : 0x15 Access : R/WPDGT 7 Phase digitizer frequency compensation disable.DPL_S[2:0] 6:4 VCO range. Sets ADC PLL frequency range.SETCNT[3:0] 3:0 Setting time for ADC PLL phase detector, in ADC clock periods.ADC Register (Bank=01)RT_CTL 7:0 Default : 0x10 Access : R/WSFTF 7 DVI error correction enable (DVI feature only).0: Error correction disable.1: Error correction enable.DEFE 6 DVI R/G/B alignment edge on DE (DVI feature only).0: DE leading edge.1: DE trailing edge.WDF 5 DVI word alignment edge on DE (DVI feature only).0: Disable.1: Enable.13hRT_CTL[4:0] 4:0 Resistor termination control for DVI (DVI feature only).SOG_LVL 7:0 Default : 0x10 Access : R/WRMID 7 Middle clamp of Red Channel.0: Disable.1: Enable (used when YPbPr input).BMID 6 Middle clamp of Blue Channel.0: Disable.1: Enable (used when YPbPr input).SOGFLT 5 SOG Filter (low-pass filter on SOG input).0: Disable.1: Enable.14hSOG_LVL[4:0] 4:0 SOG trigger level.5‘b00000: 10mV;5‘b00001: 20mV;……5‘b11110: 310mV;5‘b11111: 320mV.HS_LVL 7:0 Default: 0x00 Access : R/WADCBW[2:0] 7:5 ADC Bandwidth.- 4 Reserved.- 3 Reserved.15hHL_LVL[2:0] 2:0 HSYNC trigger level.STATUS1 7:0 Default: - Access : RONote: PLL status is read based on STAT[2:0] (Reg_03h).7 When STAT[2:0] = 000:LOCK: PLL Lock status. If 1, PLL is in lock.6 IQ: PLL Lock status. If 1, PLL is in stable lock, and now capableof filtering spurious HSYNC inputs.16h5 SLOW.ADC Register (Bank=01)4 FAST.3:0 Reserved.- 7:0 Default : - Access : -17h- 7:0 Reserved.STATUS5 7:0 Default: - Access : RO18hRCMP[7:0] 7:0 DVI termination resistor status in 2’s complement (DVI featureonly).Positive value represents resistor value on low side, andRT_CTL needs to adjust to higher values for compensation.Negative value represents resistor value on high side, andRT_CTL needs to adjust to lower values for compensation.STATUS4 7:0 Default: Access : RO19hPH_STAT[7:0] 7 DVI phase status indicator in 2’s complement (DVI featureonly).STATUS5 7:0 Default : - Access : RO1AhPH_STAT[15:8] 7 DVI phase status indicator in 2’s complement (DVI featureonly).DVI_PHR 7:0 Default : 0x80 Access : R/WOVPR 7 1BhOVPHR 6:0 Freeze and override DVI red channel PLL phase selection with OVPHR[6:0].DVI_PHG 7:0 Default : 0x80 Access : R/WOVPG 7 1ChOVPHG 6:0 Freeze and override DVI red channel PLL phase selection with OVPHG[6:0].DVI_PHB 7:0 Default : 0x80 Access : R/WOVPB 7 1DhOVPHB 6:0 Freeze and override DVI red channel PLL phase selection with OVPHB[6:0].DVI_ERST 7:0 Default : 0x00 Access : R/W 1EhDRR_ST[7:0] 7:0 DVI bit error status indicator.DVI_ERTH 7:0 Default : 0x00 Access : R/WERR_TH[7:0] / CLPSKIP[7:0] 7:0 DVI bit error tolerance threshold. / Clamp skipping on/select in ADC mode.CLPSKIP[7] 7 Clamp skipping on.1FhCLPSKIP[3:0] 3:0 Clamping skipping select.TESTEN 7:0 Default : 0x00 Access : R/W 20hTESTEN 7 Enable Test Mode.0: Disable.1: Enable.ADC Register (Bank=01)- 6 Reserved.ERRCHSEL[1:0] 5:4 Channel select for DVI error status indicator (DVI feature only).00: Red channel.01: Green channel.10: Blue channel.11: Reserved.ERRD 3 DVI bit error status indicator (ERR_ST) enable (DVI featureonly).0: Normal.1: Read status.RDST 2 Terminator resistance status (RCMP) and DVI phase statusenable (DVI feature only).0: Normal.1: Read status.PHSEL[1:0] 1:0 Channel Select for DVI phase status (DVI feature only).00: Red channel.01: Green channel.10: Blue channel.11: Reserved.21h ~- 7:0 Default : - Access : -2Ch - 7:0 Reserved.TESTMOD 7:0 Default : 0x06 Access : R/W2Dh- 7 Reserved.- 6:5 Reserved.TESTMOD[4:0] 4:0 LVDS/RSDS differential output swing control.5’b01000: 5.0mA for LVDS/ 2.5mA for RSDS5’b00111: 4.6mA for LVDS/ 2.3mA for RSDS5’b00110: 4.2mA for LVDS/ 2.1mA for RSDS2Eh ~- 7:0 Default : - Access : -2Fh - 7:0 Reserved.30hPLLCTRLV 7:0 Default : 0xC6 Access : R/WWDTOL[1:0] 7:6 PLL Watchdog threshold.IQCLR_TH[2:0] 5:3 PLL unstable lock threshold.IQSET_TH[2:0] 2:0 PLL stable lock threshold.31h ~- 7:0 Default : - Access : -3Ch - 7:0 Reserved.DAC_CTRL 7:0 Default : 0x00 Access : R/W3Dh- 7:5 ReservedADC Register (Bank=01)CMPATEN 4 Compatible bit.- 3:0 Reserved.31h ~- 7:0 Default : - Access : -FFh - 7:0 Reserved.Digital Image Processor Register (Bank = 00)Digital Image Processor Register (Bank=00)Index Mnemonic Bits Description01hDBFC 7:0 Default : 0x80 Access : R/W7:3 Reserved.DBL[1:0] 2:1 Double buffer load.00: Keep old register value.01: Load new data (auto reset to 00 when load finish).10: Automatically load data at VSYNC blanking.11: Reserved.DBC 0 Double buffer control.0: Double buffer disable.1: Double buffer enable.02hISELECT 7:0 Default : 0x00 Access : R/WNIS 7 Output lock mode.0: Lock input (input signal exits).1: Free-run (no input signal).STYPE[1:0] 6:5 Input Sync Type.00: Auto detected.01: Input is separated HSYNC and VSYNC.10: Input is Composite sync.11: Input is sync-on-green (SOG).COMP 4 CSYNC/SOG select (only useful when STYPE = 00).0: CSYNC.1: SOG.CSC 3 CSC function.0: Disable (RGB -> RGB).1: Enable (YCbCr -> RGB).IHSU 2 Input Sync Usage.When ISEL=00 or 01:0: Use HSYNC to perform mode detection, HSOUT from ADCto sample pixel.1: Use HSYNC only.When ISEL=10:Digital Image Processor Register (Bank=00)0: Normal.1: Enable DE Ahead/Delay adjust.When ISEL=11:0: Normal.1: Output Black at blanking.ISEL[1:0] 1:0 00: Analog 1.01: Analog 2.10: DVI.11: Video.03h- 7:0 Default : - Access : -- 7:0 Reserved.IPCTRL2 7:0 Default : 0x18 Access : R/W04hDHSR 7 Digital Input Horizontal Sample Range.0: Use DE as sample range, only V position can be adjusted.1: Use SPRHST and SPRHDC as sample range, both H and Vposition can be adjusted.DEON 6 DE Only. HSYNC and VSYNC are ignored.0: Disable.1: Enable.IVSD 5 Input VSYNC Delay select.0: Delay 1/4 input HSYNC (recommended).1: No delay.HSE 4 Input HSYNC reference edge select.0: From HSYNC leading edge, default value.1: From HSYNC tailing edge.VSE 3 Input VSYNC reference edge select.0: From VSYNC leading edge, default value.1: From VSYNC tailing edge.ESLS 2 Early Sample Line Select.0: 8 lines.1: 16 lines.VWRP 1 Input image Vertical wrap.0: Disable.1: Enable.HWRP 0 Input image Horizontal wrap.0: Disable.1: Enable.05hSPRVST-L 7:0 Default : 0x10 Access : R/W, DBSPRVST[7:0] 7:0 Image vertical sample start point, count by input HSYNC.Digital Image Processor Register (Bank=00)06hSPRVST-H 7:0 Default : 0x00 Access : R/W, DB7:3 Reserved.SPRVST[10:8] 2:0 Image vertical sample start point, count by input HSYNC.When Reg. 52, 51, 50 < 90 00 00, SPRHST is multiplied by 2internally.07hSPRHST-L 7:0 Default : 0x01 Access : R/W, DBSPRHST[7:0] 7:0 Image horizontal sample start point, count by input dot clock. 08hSPRHST-H 7:0 Default : 0x00 Access : R/W, DBSPRHSTLSB 7 Back 1 LSB, sample range will move 1 pixel left.- 6 Reserved.- 5 Reserved.- 4 Reserved.SPRGST[11:8] 3:0 Image horizontal sample start point, count by input dot clock. 09hSPRVDC-L 7:0 Default : 0x10 Access : R/W, DBSPRVDC[7:0] 7:0 Image vertical resolution (vertical display enable area count byline).0AhSPRVDC-H 7:0 Default: 0x00 Access : R/W7:3 Reserved.SPRVDC[10:8] 2:0 Image vertical resolution (vertical display enable area count byline).When Reg. 52, 51, 50 < 90 00 00, SPRVST is multiplied by 2internally.SPRHDC-L 7:0 Default : 0x10 Access : R/W0BhSPRHDC[7:0] 7:0 Image horizontal resolution (horizontal display enable areacount by pixel).0ChSPRHDC-L 7:0 Default : 0x00 Access : R/W7:4 Reserved.SPRHDC[11:8] 3:0 Image horizontal resolution (horizontal display enable areacount by pixel).0Dh ~- 7:0 Default : - Access : -0Eh - 7:0 Reserved.0FhLYL 7:0 Default : 0x00 Access : R/W7:5 Reserved.3LVRCEN 4 3 Line Vertical Resolution Conversion Enable.LYL[3:0] 3:0 Lock Y Line.10h DEVST-L 7:0 Default : 0x00 Access : R/WDigital Image Processor Register (Bank=00)DEVST[7:0] 7:0 Output DE Vertical Start.11hDEVST-H 7:0 Default : 0x00 Access : R/W7:3 Reserved.DEVST[10:8] 2:0 See description for DEVST[7:0].12hDEHST-L 7:0 Default : 0x03 Access : R/WDEHST[7:0] 7:0 Output DE Horizontal Start.13hDEHST-H 7:0 Default : 0x00 Access : R/W7:3 Reserved.DEHST[10:8] 2:0 See description for DEHST[7:0].14hDEVEND-L 7:0 Default : 0x06 Access : R/WDEVEND[7:0] 7:0 Output DE Vertical END.15hDEVEND-H 7:0 Default : 0x00 Access : R/W7:3 Reserved.DEVEND[10:8] 2:0 See description for DEVEND[7:0].16hDEHEND-L 7:0 Default : 0x00 Access : R/WDEVEND[7:0] 7:0 Output DE Horizontal END.17hDEHEND-H 7:0 Default : 0x00 Access : R/W7:3 Reserved.DEVEND[10:8] 2:0 See description for DEVEND[7:0].18hOIHST-L 7:0 Default : 0x00 Access : R/WOIHST[7:0] 7:0 Output Image window Horizontal Start.19hOIHST-H 7:0 Default : 0x00 Access : R/W7:3 Reserved.OIHST[10:8] 2:0 See description for OIHST[7:0].1AhOIVEND-L 7:0 Default : 0x06 Access : R/WOIVEND[7:0] 7:0 Output Image window Vertical END.OIVEND-H 7:0 Default : 0x00 Access : R/W 1Bh7:3 Reserved.OIVEND[10:8] 2:0 See description for OIVEND[7:0].1ChOIHEND-L 7:0 Default : 0x00 Access : R/WOIHEND[7:0] 7:0 Output Image window Horizontal END.1DhOIHEND-H 7:0 Default : 0x00 Access : R/W7:3 Reserved.OIHEND[10:8] 2:0 See description for OIHEND[7:0].1Eh VDTOT-L 7:0 Default : 0x03 Access : R/WDigital Image Processor Register (Bank=00)VDTOT[7:0] 7:0 Output Vertical Total.1FhVDTOT-H 7:0 Default : 0x00 Access : R/W7:3 Reserved.VDTOT[10:8] 2:0 See description for VDTOT[7:0].20hVSST-L 7:0 Default : 0x03 Access : R/WVSST[7:0] 7:0 Output VSYNC start (only useful when AOVS=1).21hVSST-H 7:0 Default : 0x00 Access : R/W7:4 Reserved.VSRU 3 VSYNC Register Usage.0: Registers 20h – 23h are used to define output VSYNC.1: Registers 20h and 21h are used to define No signal VSYNC.Registers 22h and 23h are used to define minimum H total.VSST[10:8] 2:0 See description for VSST[7:0].VSEND-L 7:0 Default : 0x06 Access : R/W22hVSEND[7:0] 7:0 Output VSYNC END (only useful when AOVS=1).23hVSEND-H 7:0 Default : 0x00 Access : R/W DB7:3 Reserved.VSEND[10:8] 2:0 See description for VSEND[7:0].24hHDTOT-L 7:0 Default : 0x03 Access : R/W DBHDTOT[7:0] 7:0 Output Horizontal Total.HDTOT-H 7:0 Default : 0x00 Access : R/W25h7:4 Reserved.HDTOT[11:8] 3:0 See description for HDTOT[7:0].26hHSEND 7:0 Default : 0x00 Access : R/WHSEND[7:0] 7:6 Output HSYNC Pulse width.OSCTRL1 7:0 Default : 0x4C Access : R/W27hAOVS 7 Auto Output VSYNC.0: OVSYNC is defined automatically.1: OVSYNC is defined manually (register 0x20 – 0x23).- 6 Reserved.HRSM 5 HSYNC Remove Mode.0: Normal.1: Remove HSYNC when GPOA (Bank 2 register 0x62 – 0x6A) islow.VSGP 4 VSYNC use GPO9.0: Disable.1: Enable (using Bank 2 register 0x59 –0x61 to defineDigital Image Processor Register (Bank=00)OVSYNC).EHTT 3 Even H Total.0: Enable, Output H Total always be even pixels.1: Disable, Output H Total always be odd pixels.- 2 Reserved.AHRT 1 Auto H total and Read start Tuning enable.0: Disable.1: Enable.CTRL 0 0: Disable.1: Enable.28hOSCTRL2 7:0 Default : 0x00 Access : R/W- 7:0 Reserved.29h- 7:0 Default : - Access : -- 7:0 Reserved.BRC 7:0 Default : 0x00 Access : R/W2Ah- 7:1 Reserved.BRC 0 Brightness function, reference to register 2Bh, 2Ch, and 2Eh.0: Off.1: On.2BhBCR 7:0 Default : 0x80 Access : R/WBCR[7:0] 7:0 Brightness Coefficient – Red color.00h: -128.80h: 0, default value.FFh: +127.2ChBCG 7:0 Default : 0x80 Access : R/WBCG[7:0] 7:0 Brightness Coefficient – Green color.00h: -128.80h: 0, default value.FFh: +127.2DhBCB 7:0 Default : 0x80 Access : R/WBCB[7:0] 7:0 Brightness Coefficient – Blue color.00h: -128.80h: 0, default value.FFh: +127.CNTR 7:0 Default : 0x00 Access : R/W2Eh- 7 Reserved.CNREN[6:5] 6:5 Contrast Noise Rounding Enable.11: Enable.Digital Image Processor Register (Bank=00)CCLR 4 Contrast Coefficient LSB – Red color.CCLG 3 Contrast Coefficient LSB – Green color.CCLB 2 Contrast Coefficient LSB – Blue color.CNTT 1 Contrast Type select.0: Use 0 as center point.1: Use 128 as center point.CNTR 0 Contrast function.0: Off.1: On.2FhCCR 7:0 Default : 0x80 Access : R/WCCR[7:0] 7:0 Contrast Coefficient – Red color.00h: 0.0000000.80h: 1.0000000. Default value.FFh: 1.1111111.30hCCG 7:0 Default : 0x80 Access : R/WCCG[7:0] 7:0 Contrast Coefficient – Green color.00h: 0.0000000.80h: 1.0000000. Default value.FFh: 1.1111111.31hCCB 7:0 Default : 0x80 Access : R/WCCB[7:0] 7:0 Contrast Coefficient – Blue color.00h: 0.0000000.80h: 1.0000000. Default value.FFh: 1.1111111.32hFWC 7:0 Default : 0x00 Access : R/W- 7:1 Reserved.FWC 0 Border Color (will be used when output is in free-run mode).0: Off.1: On.33hFCR 7:0 Default : 0x00 Access : R/WFCR[7:0] 7:0 Border Color – Red channel.34hFCG 7:0 Default : 0x00 Access : R/WFCG[7:0] 7:0 Border Color – Green channel.35hFCR 7:0 Default : 0x00 Access : R/WFCB[7:0] 7:0 Border Color – Blue channel.DITHCTRL 7:0 Default : 0x02 Access : R/W36hDITHG[1:0] 7:6 Dither coefficient for G channel.DITHB[1:0] 5:4 Dither coefficient for B channel.Digital Image Processor Register (Bank=00)SROT 3 Spatial coefficient Rotate.0: Disable.1: Enable.TROT 2 Temporal coefficient Rotate.0: Disable.1: Enable.OBN 1 Output Bits Number (used for 8/10-bit gamma).0: 8-bit output.1: 6-bit output (power on default value).DITH 0 Dither function.0: Off.1: On.DITHCOEF 7:0 Default : 0x20 Access : R/W37hTL[1:0] 7:6 Top – Left dither coefficient.TR[1:0] 5:4 Top – Right dither coefficient.BL[1:0] 3:2 Bottom – Left dither coefficient.BR[1:0] 1:0 Bottom – Right dither coefficient.38hTRFN 7:0 Default : 0x00 Access : R/WPSRD 7 Pseudo Random, resets every 4 frames.0: Enable.1: Disable.NDMD 6 Noise Dithering Method.DATP 5 Dither based on Auto Phase threshold.0: Disable.1: Enable.DRT 4 Dither Rotate Type.0: EOR.1: Rotate.DT3 3 Dither Type 2 control.0: Disable dither type 2.1: Enable dither type 2.DT2 2 Dither Type 2.0: Output data bits 1 and 0 according to input pixel value.1: Output data bits 2, 1 and 0 according to input pixel value.DT1 1 Dither Type 1.0: Normal.1: Output data bits 1 and 0 are always 00.TDFNC 0 Tempo-Dither Frame Number Control.0: Tempo-dither every frame.。

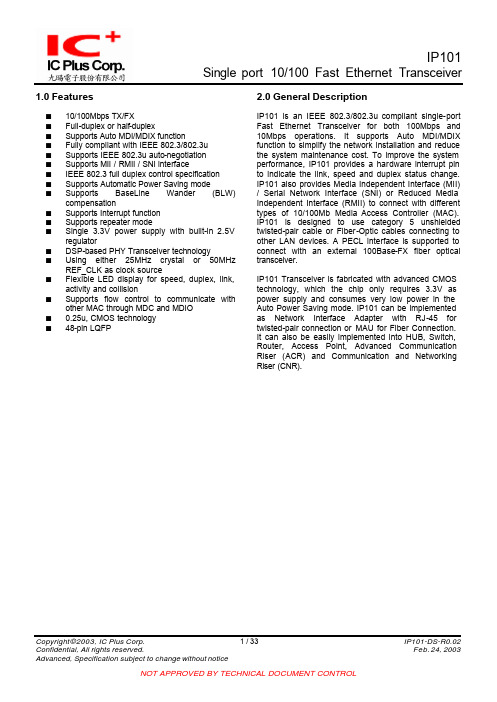

IP101