Speculative Multiprocessor Cache Line Actions Using Instruction and Line History 1 Abstract

计算机术语介绍

DP(Dual Processor,双处理器) DSM(Dedicated Stack Manager,专门堆栈管理) DSMT(Dynamic Simultaneous Multithreading,动态同步多线程) DST(Depleted Substrate Transistor,衰竭型底层晶体管) DTV(Dual Threshold Voltage,双重极限电压) DUV(Deep Ultra-Violet,纵深紫外光) EBGA(Enhanced Ball Grid Array,增强形球状网阵排列) EBL(electron beam lithography,电子束平版印刷) EC(Embedded Controller,嵌入式控制器) EDEC(Early Decode,早期解码) Embedded Chips(嵌入式) EPA(edge pin array,边缘针脚阵列) EPF(Embedded Processor Forum,嵌入式处理器论坛) EPL(electron projection lithography,电子发射平版印刷)

IOPs(Integer Operations Per Second,整数操作/秒) IPC(Instructions Per Clock Cycle,指令/时钟周期) ISA(instruction set architecture,指令集架构) ISD(inbuilt speed-throttling device,内藏速度控制设备) ITC(Instruction Trace Cache,指令追踪缓存) ITRS(International Technology Roadmap for Semiconductors,国 际半导体技术发展蓝图) KNI(Katmai New Instructions,Katmai 新指令集,即 SSE) Latency(潜伏期) LDT(Lightning Data Transport,闪电数据传输总线) LFU(Legacy Function Unit,传统功能单元) LGA(land grid array,接点栅格阵列) LN2(Liquid Nitrogen,液氮) Local Interconnect(局域互连)

专业术语中英文对照表计算机专业

1、CPU3DNow!(3D no waiting,无须等待的3D处理)AAM(AMD Analyst Meeting,AMD分析家会议)ABP(Advanced Branch Prediction,高级分支预测)ACG(Aggressive Clock Gating,主动时钟选择)AIS(Alternate Instruction Set,交替指令集)ALAT(advanced load table,高级载入表)ALU(Arithmetic Logic Unit,算术逻辑单元)Aluminum(铝)AGU(Address Generation Units,地址产成单元)APC(Advanced Power Control,高级能源控制)APIC(Advanced rogrammable Interrupt Controller,高级可编程中断控制器)APS(Alternate Phase Shifting,交替相位跳转)ASB(Advanced System Buffering,高级系统缓冲)ATC(Advanced Transfer Cache,高级转移缓存)ATD(Assembly Technology Development,装配技术发展)BBUL(Bumpless Build-Up Layer,内建非凹凸层)BGA(Ball Grid Array,球状网阵排列)BHT(branch prediction table,分支预测表)Bops(Billion Operations Per Second,10亿操作/秒)BPU(Branch Processing Unit,分支处理单元)BP(Brach Pediction,分支预测)BSP(Boot Strap Processor,启动捆绑处理器)BTAC(Branch Target Address Calculator,分支目标寻址计算器)CBGA (Ceramic Ball Grid Array,陶瓷球状网阵排列)CDIP (Ceramic Dual-In-Line,陶瓷双重直线)Center Processing Unit Utilization,中央处理器占用率CFM(cubic feet per minute,立方英尺/秒)CMT(course-grained multithreading,过程消除多线程)CMOS(Complementary Metal Oxide Semiconductor,互补金属氧化物半导体)CMOV(conditional move instruction,条件移动指令)CISC(Complex Instruction Set Computing,复杂指令集计算机)CLK(Clock Cycle,时钟周期)CMP(on-chip multiprocessor,片内多重处理)CMS(Code Morphing Software,代码变形软件)co-CPU(cooperative CPU,协处理器)COB(Cache on board,板上集成缓存,做在CPU卡上的二级缓存,通常是内核的一半速度))COD(Cache on Die,芯片内核集成缓存)Copper(铜)CPGA(Ceramic Pin Grid Array,陶瓷针型栅格阵列)CPI(cycles per instruction,周期/指令)CPLD(Complex Programmable Logic Device,複雜可程式化邏輯元件)CPU(Center Processing Unit,中央处理器)CRT(Cooperative Redundant Threads,协同多余线程)CSP(Chip Scale Package,芯片比例封装)CXT(Chooper eXTend,增强形K6-2内核,即K6-3)Data Forwarding(数据前送)dB(decibel,分贝)DCLK(Dot Clock,点时钟)DCT(DRAM Controller,DRAM控制器)DDT(Dynamic Deferred Transaction,动态延期处理)Decode(指令解码)DIB(Dual Independent Bus,双重独立总线)DMT(Dynamic Multithreading Architecture,动态多线程结构)DP(Dual Processor,双处理器)DSM(Dedicated Stack Manager,专门堆栈管理)DSMT(Dynamic Simultaneous Multithreading,动态同步多线程)DST(Depleted Substrate Transistor,衰竭型底层晶体管)DTV(Dual Threshold Voltage,双重极限电压)DUV(Deep Ultra-Violet,纵深紫外光)EBGA(Enhanced Ball Grid Array,增强形球状网阵排列)EBL(electron beam lithography,电子束平版印刷)EC(Embedded Controller,嵌入式控制器)EDEC(Early Decode,早期解码)Embedded Chips(嵌入式)EPA(edge pin array,边缘针脚阵列)EPF(Embedded Processor Forum,嵌入式处理器论坛)EPL(electron projection lithography,电子发射平版印刷)EPM(Enhanced Power Management,增强形能源管理)EPIC(explicitly parallel instruction code,并行指令代码)EUV(Extreme Ultra Violet,紫外光)EUV(extreme ultraviolet lithography,极端紫外平版印刷)FADD(Floationg Point Addition,浮点加)FBGA(Fine-Pitch Ball Grid Array,精细倾斜球状网阵排列)FBGA(flipchip BGA,轻型芯片BGA)FC-BGA(Flip-Chip Ball Grid Array,反转芯片球形栅格阵列)FC-LGA(Flip-Chip Land Grid Array,反转接点栅格阵列)FC-PGA(Flip-Chip Pin Grid Array,反转芯片针脚栅格阵列)FDIV(Floationg Point Divide,浮点除)FEMMS:Fast Entry/Exit Multimedia State,快速进入/退出多媒体状态FFT(fast Fourier transform,快速热欧姆转换)FGM(Fine-Grained Multithreading,高级多线程)FID(FID:Frequency identify,频率鉴别号码)FIFO(First Input First Output,先入先出队列)FISC(Fast Instruction Set Computer,快速指令集计算机)flip-chip(芯片反转)FLOPs(Floating Point Operations Per Second,浮点操作/秒)FMT(fine-grained multithreading,纯消除多线程)FMUL(Floationg Point Multiplication,浮点乘)FPRs(floating-point registers,浮点寄存器)FPU(Float Point Unit,浮点运算单元)FSUB(Floationg Point Subtraction,浮点减)GFD(Gold finger Device,金手指超频设备)GHC(Global History Counter,通用历史计数器)GTL(Gunning Transceiver Logic,射电收发逻辑电路)GVPP(Generic Visual Perception Processor,常规视觉处理器)HL-PBGA: 表面黏著,高耐热、轻薄型塑胶球状网阵封装HTT(Hyper-Threading Technology,超级线程技术)Hz(hertz,赫兹,频率单位)IA(Intel Architecture,英特尔架构)IAA(Intel Application Accelerator,英特尔应用程序加速器)ICU(Instruction Control Unit,指令控制单元)ID(identify,鉴别号码)IDF(Intel Developer Forum,英特尔开发者论坛)IEU(Integer Execution Units,整数执行单元)IHS(Integrated Heat Spreader,完整热量扩展)ILP(Instruction Level Parallelism,指令级平行运算)IMM: Intel Mobile Module, 英特尔移动模块Instructions Cache,指令缓存Instruction Coloring(指令分类)IOPs(Integer Operations Per Second,整数操作/秒)IPC(Instructions Per Clock Cycle,指令/时钟周期)ISA(instruction set architecture,指令集架构)ISD(inbuilt speed-throttling device,内藏速度控制设备)ITC(Instruction Trace Cache,指令追踪缓存)ITRS(International Technology Roadmap for Semiconductors,国际半导体技术发展蓝图)KNI(Katmai New Instructions,Katmai新指令集,即SSE)Latency(潜伏期)LDT(Lightning Data Transport,闪电数据传输总线)LFU(Legacy Function Unit,传统功能单元)LGA(land grid array,接点栅格阵列)LN2(Liquid Nitrogen,液氮)Local Interconnect(局域互连)MAC(multiply-accumulate,累积乘法)mBGA (Micro Ball Grid Array,微型球状网阵排列)nm(namometer,十亿分之一米/毫微米)MCA(machine check architecture,机器检查体系)MCU(Micro-Controller Unit,微控制器单元)MCT(Memory Controller,内存控制器)MESI(Modified, Exclusive, Shared, Invalid:修改、排除、共享、废弃)MF(MicroOps Fusion,微指令合并)mm(micron metric,微米)MMX(MultiMedia Extensions,多媒体扩展指令集)MMU(Multimedia Unit,多媒体单元)MMU(Memory Management Unit,内存管理单元)MN(model numbers,型号数字)MFLOPS(Million Floationg Point/Second,每秒百万个浮点操作)MHz(megahertz,兆赫)mil(PCB 或晶片佈局的長度單位,1 mil = 千分之一英寸)MIPS(Million Instruction Per Second,百万条指令/秒)MOESI(Modified, Owned, Exclusive, Shared or Invalid,修改、自有、排除、共享或无效)MOF(Micro Ops Fusion,微操作熔合)Mops(Million Operations Per Second,百万次操作/秒)MP(Multi-Processing,多重处理器架构)MPF(Micro processor Forum,微处理器论坛)MPU(Microprocessor Unit,微处理器)MPS(MultiProcessor Specification,多重处理器规范)MSRs(Model-Specific Registers,特别模块寄存器)MSV(Multiprocessor Specification Version,多处理器规范版本)NAOC(no-account OverClock,无效超频)NI(Non-Intel,非英特尔)NOP(no operation,非操作指令)NRE(Non-Recurring Engineering charge,非重複性工程費用)OBGA(Organic Ball Grid Arral,有机球状网阵排列)OCPL(Off Center Parting Line,远离中心部分线队列)OLGA(Organic Land Grid Array,有机平面网阵包装)OoO(Out of Order,乱序执行)OPC(Optical Proximity Correction,光学临近修正)OPGA(Organic Pin Grid Array,有机塑料针型栅格阵列)OPN(Ordering Part Number,分类零件号码)PAT(Performance Acceleration Technology,性能加速技术)PBGA(Plastic Pin Ball Grid Array,塑胶球状网阵排列)PDIP (Plastic Dual-In-Line,塑料双重直线)PDP(Parallel Data Processing,并行数据处理)PGA(Pin-Grid Array,引脚网格阵列),耗电大PLCC (Plastic Leaded Chip Carriers,塑料行间芯片运载)Post-RISC(加速RISC,或后RISC)PR(Performance Rate,性能比率)PIB(Processor In a Box,盒装处理器)PM(Pseudo-Multithreading,假多线程)PPGA(Plastic Pin Grid Array,塑胶针状网阵封装)PQFP(Plastic Quad Flat Package,塑料方块平面封装)PSN(Processor Serial numbers,处理器序列号)QFP(Quad Flat Package,方块平面封装)QSPS(Quick Start Power State,快速启动能源状态)RAS(Return Address Stack,返回地址堆栈)RAW(Read after Write,写后读)REE(Rapid Execution Engine,快速执行引擎)Register Contention(抢占寄存器)Register Pressure(寄存器不足)Register Renaming(寄存器重命名)Remark(芯片频率重标识)Resource contention(资源冲突)Retirement(指令引退)RISC(Reduced Instruction Set Computing,精简指令集计算机)ROB(Re-Order Buffer,重排序缓冲区)RSE(register stack engine,寄存器堆栈引擎)RTL(Register Transfer Level,暫存器轉換層。

UniversityofWisconsin-Madison(

University of Wisconsin-Madison(UMW)周玉龙1101213442 计算机应用UMW简介美国威斯康辛大学坐落于美国密歇根湖西岸的威斯康辛州首府麦迪逊市,有着风景如画的校园,成立于1848年, 是一所有着超过150年历史的悠久大学。

威斯康辛大学是全美最顶尖的三所公立大学之一,是全美最顶尖的十所研究型大学之一。

在美国,它经常被视为公立的常青藤。

与加利福尼亚大学、德克萨斯大学等美国著名公立大学一样,威斯康辛大学是一个由多所州立大学构成的大学系统,也即“威斯康辛大学系统”(University of Wisconsin System)。

在本科教育方面,它列于伯克利加州大学和密歇根大学之后,排在公立大学的第三位。

除此之外,它还在本科教育质量列于美国大学的第八位。

按美国全国研究会的研究结果,威斯康辛大学有70个科目排在全美前十名。

在上海交通大学的排行中,它名列世界大学的第16名。

威斯康辛大学是美国大学联合会的60个成员之一。

特色专业介绍威斯康辛大学麦迪逊分校设有100多个本科专业,一半以上可以授予硕士、博士学位,其中新闻学、生物化学、植物学、化学工程、化学、土木工程、计算机科学、地球科学、英语、地理学、物理学、经济学、德语、历史学、语言学、数学、工商管理(MBA)、微生物学、分子生物学、机械工程、哲学、西班牙语、心理学、政治学、统计学、社会学、动物学等诸多学科具有相当雄厚的科研和教学实力,大部分在美国大学相应领域排名中居于前10名。

学术特色就学术方面的荣耀而言,威斯康辛大学麦迪逊校区的教职员和校友至今共获颁十七座诺贝尔奖和二十四座普立兹奖;有五十三位教职员是国家科学研究院的成员、有十七位是国家工程研究院的成员、有五位是隶属于国家教育研究院,另外还有九位教职员赢得了国家科学奖章、六位是国家级研究员(Searle Scholars)、还有四位获颁麦克阿瑟研究员基金。

威斯康辛大学麦迪逊校区虽然是以农业及生命科学为特色,但是令人注目,同时也是吸引许多传播科系学子前来留学的最大诱因,则是当前任教于该校新闻及传播研究所、在传播学界有「近代美国传播大师」之称的杰克·麦克劳(Jack McLauld)。

第4章习题答案

(2)SRAM 芯片和 DRAM 芯片各有哪些特点?各自用在哪些场合?

(3)CPU 和主存之间有哪两种通信方式?SDRAM 芯片采用什么方式和 CPU 交换信息?

(4)为什么在 CPU 和主存之间引入 Cache 能提高 CPU 访存效率?

(5)为什么说 Cache 对程序员来说是透明的?

(6)什么是 Cache 映射的关联度?关联度与命中率、命中时间的关系各是什么?

EEPROM (Electrically EPROM) 多模块存储器(Multi-Module Memory) 双口 RAM (Dual Port RAM) 程序访问的局部化

空间局部性(Spatial Locality) 命中时间(Hit Time) 失靶损失(Miss Penalty) Cache 槽或 Cache 行 (Slot / Line) 全相联 Cache(Fully Associative Cache) 多级 Cache(Multilevel Cache) 代码 Cache(指令 Cache) 先进先出 (First-In-First-Out,FIFO) Write Through(写直达、通过式写、直写) Write Back (写回、回写) 物理存储器(Physical Memory) 虚页号(Virtual Page number ) 物理地址(Physical address) 物理页号(Page frame) 重定位(Relocation) 页表基址寄存器(Page table base register) 修改位(Modify bit / Dirty bit) 访问方式位(Access bit) 交换(swapping) / 页面调度(paging) LRU 页(Least Recently Used Page) 分页式虚拟存储器(Paging VM) 段页式虚拟存储器(Paged Segmentation VM)

计算机术语大全(很好的哦)

计算机术语大全1、CPU3DNow!(3D no waiting,无须等待的3D处理)AAM(AMD Analyst Meeting,AMD分析家会议)ABP(Advanced Branch Prediction,高级分支预测)ACG(Aggressive Clock Gating,主动时钟选择)AIS(Alternate Instruction Set,交替指令集)ALAT(advanced load table,高级载入表)ALU(Arithmetic Logic Unit,算术逻辑单元)Aluminum(铝)AGU(Address Generation Units,地址产成单元)APC(Advanced Power Control,高级能源控制)APIC(Advanced rogrammable Interrupt Controller,高级可编程中断控制器)APS(Alternate Phase Shifting,交替相位跳转)ASB(Advanced System Buffering,高级系统缓冲)ATC(Advanced Transfer Cache,高级转移缓存)ATD(Assembly Technology Development,装配技术发展)BBUL(Bumpless Build-Up Layer,内建非凹凸层)BGA(Ball Grid Array,球状网阵排列)BHT(branch prediction table,分支预测表)Bops(Billion Operations Per Second,10亿操作秒)BPU(Branch Processing Unit,分支处理单元)BP(Brach Pediction,分支预测)BSP(Boot Strap Processor,启动捆绑处理器)BTAC(Branch Target Address Calculator,分支目标寻址计算器)CBGA (Ceramic Ball Grid Array,陶瓷球状网阵排列)CDIP (Ceramic Dual-In-Line,陶瓷双重直线)Center Processing Unit Utilization,中央处理器占用率CFM(cubic feet per minute,立方英尺秒)CMT(course-grained multithreading,过程消除多线程)CMOS(Complementary Metal Oxide Semiconductor,互补金属氧化物半导体)CMOV(conditional move instruction,条件移动指令)CISC(Complex Instruction Set Computing,复杂指令集计算机)CLK(Clock Cycle,时钟周期)CMP(on-chip multiprocessor,片内多重处理)CMS(Code Morphing Software,代码变形软件)co-CPU(cooperative CPU,协处理器)COB(Cache on board,板上集成缓存,做在CPU卡上的二级缓存,通常是内核的一半速度))COD(Cache on Die,芯片内核集成缓存)Copper(铜)CPGA(Ceramic Pin Grid Array,陶瓷针型栅格阵列)CPI(cycles per instruction,周期指令)CPLD(Complex Programmable Logic Device,複雜可程式化邏輯元件)CPU(Center Processing Unit,中央处理器)CRT(Cooperative Redundant Threads,协同多余线程)CSP(Chip Scale Package,芯片比例封装)CXT(Chooper eXTend,增强形K6-2内核,即K6-3)Data Forwarding(数据前送)dB(decibel,分贝)DCLK(Dot Clock,点时钟)DCT(DRAM Controller,DRAM控制器)DDT(Dynamic Deferred Transaction,动态延期处理)Decode(指令解码)DIB(Dual Independent Bus,双重独立总线)DMT(Dynamic Multithreading Architecture,动态多线程结构)DP(Dual Processor,双处理器)DSM(Dedicated Stack Manager,专门堆栈管理)DSMT(Dynamic Simultaneous Multithreading,动态同步多线程)DST(Depleted Substrate Transistor,衰竭型底层晶体管)DTV(Dual Threshold Voltage,双重极限电压)DUV(Deep Ultra-Violet,纵深紫外光)EBGA(Enhanced Ball Grid Array,增强形球状网阵排列)EBL(electron beam lithography,电子束平版印刷)EC(Embedded Controller,嵌入式控制器)EDB(Execute Disable Bit,执行禁止位)EDEC(Early Decode,早期解码)Embedded Chips(嵌入式)EM64T(Extended Memory 64 Technology,扩展内存64技术)EPA(edge pin array,边缘针脚阵列)EPF(Embedded Processor Forum,嵌入式处理器论坛)EPL(electron projection lithography,电子发射平版印刷)EPM(Enhanced Power Management,增强形能源管理)EPIC(explicitly parallel instruction code,并行指令代码)EUV(Extreme Ultra Violet,紫外光)EUV(extreme ultraviolet lithography,极端紫外平版印刷)FADD(Floationg Point Addition,浮点加)FBGA(Fine-Pitch Ball Grid Array,精细倾斜球状网阵包装)FBGA(flipchip BGA,轻型芯片BGA)FC-BGA(Flip-Chip Ball Grid Array,翻转芯片球形网阵包装)FC-LGA(Flip-Chip Land Grid Array,翻转接点网阵包装)FC-PGA(Flip-Chip Pin Grid Array,翻转芯片球状网阵包装)FDIV(Floationg Point Divide,浮点除)FEMMS:Fast EntryExit Multimedia State,快速进入退出多媒体状态FFT(fast Fourier transform,快速热欧姆转换)FGM(Fine-Grained Multithreading,高级多线程)FID(FID:Frequency identify,频率鉴别号码)FIFO(First Input First Output,先入先出队列)FISC(Fast Instruction Set Computer,快速指令集计算机)flip-chip(芯片反转)FLOPs(Floating Point Operations Per Second,浮点操作秒)FMT(fine-grained multithreading,纯消除多线程)FMUL(Floationg Point Multiplication,浮点乘)FPRs(floating-point registers,浮点寄存器)FPU(Float Point Unit,浮点运算单元)FSUB(Floationg Point Subtraction,浮点减)GFD(Gold finger Device,金手指超频设备)GHC(Global History Counter,通用历史计数器)GTL(Gunning Transceiver Logic,射电收发逻辑电路)GVPP(Generic Visual Perception Processor,常规视觉处理器)HL-PBGA 表面黏著,高耐热、轻薄型塑胶球状网阵封装HTT(Hyper-Threading Technology,超级线程技术)Hz(hertz,赫兹,频率单位)IA(Intel Architecture,英特尔架构)IAA(Intel Application Accelerator,英特尔应用程序加速器)IATM(Intel Advanced Thermal Manager,英特尔高级热量管理指令集)ICU(Instruction Control Unit,指令控制单元)ID(identify,鉴别号码)IDF(Intel Developer Forum,英特尔开发者论坛)IDMB(Intel Digital Media Boost,英特尔数字媒体推进指令集)IDPC(Intel Dynamic Power Coordination,英特尔动态能源调和指令集)IEU(Integer Execution Units,整数执行单元)IHS(Integrated Heat Spreader,完整热量扩展)ILP(Instruction Level Parallelism,指令级平行运算)IMM Intel Mobile Module, 英特尔移动模块Instructions Cache,指令缓存Instruction Coloring(指令分类)IOPs(Integer Operations Per Second,整数操作秒)IPC(Instructions Per Clock Cycle,指令时钟周期)ISA(instruction set architecture,指令集架构)ISD(inbuilt speed-throttling device,内藏速度控制设备)ITC(Instruction Trace Cache,指令追踪缓存)ITRS(International Technology Roadmap for Semiconductors,国际半导体技术发展蓝图)KNI(Katmai New Instructions,Katmai新指令集,即SSE)Latency(潜伏期)LDT(Lightning Data Transport,闪电数据传输总线)LFU(Legacy Function Unit,传统功能单元)LGA(land grid array,接点栅格阵列)LN2(Liquid Nitrogen,液氮)Local Interconnect(局域互连)MAC(multiply-accumulate,累积乘法)mBGA (Micro Ball Grid Array,微型球状网阵排列)nm(namometer,十亿分之一米毫微米)MCA(Machine Check Architecture,机器检查架构)MCU(Micro-Controller Unit,微控制器单元)MCT(Memory Controller,内存控制器)MESI(Modified, Exclusive, Shared, Invalid:修改、排除、共享、废弃)MF(MicroOps Fusion,微指令合并)mm(micron metric,微米)MMX(MultiMedia Extensions,多媒体扩展指令集)MMU(Multimedia Unit,多媒体单元)MMU(Memory Management Unit,内存管理单元)MN(model numbers,型号数字)MFLOPS(Million Floationg PointSecond,每秒百万个浮点操作)MHz(megahertz,兆赫)mil(PCB 或晶片佈局的長度單位,1 mil = 千分之一英寸)MIMD(Multi Instruction Multiple Data,多指令多数据流)MIPS(Million Instruction Per Second,百万条指令秒)MOESI(Modified, Owned, Exclusive, Shared or Invalid,修改、自有、排除、共享或无效)MOF(Micro Ops Fusion,微操作熔合)Mops(Million Operations Per Second,百万次操作秒)MP(Multi-Processing,多重处理器架构)MPF(Micro processor Forum,微处理器论坛)MPU(Microprocessor Unit,微处理器)MPS(MultiProcessor Specification,多重处理器规范)MSRs(Model-Specific Registers,特别模块寄存器)MSV(Multiprocessor Specification Version,多处理器规范版本)MVP(Mobile Voltage Positioning,移动电压定位)IVNAOC(no-account OverClock,无效超频)NI(Non-Intel,非英特尔)NOP(no operation,非操作指令)NRE(Non-Recurring Engineering charge,非重複性工程費用)OBGA(Organic Ball Grid Arral,有机球状网阵排列)OCPL(Off Center Parting Line,远离中心部分线队列)OLGA(Organic Land Grid Array,有机平面网阵包装)OoO(Out of Order,乱序执行)OPC(Optical Proximity Correction,光学临近修正)OPGA(Organic Pin Grid Array,有机塑料针型栅格阵列)OPN(Ordering Part Number,分类零件号码)PAT(Performance Acceleration Technology,性能加速技术)PBGA(Plastic Pin Ball Grid Array,塑胶球状网阵排列)PDIP (Plastic Dual-In-Line,塑料双重直线)PDP(Parallel Data Processing,并行数据处理)PGA(Pin-Grid Array,引脚网格阵列),耗电大PLCC (Plastic Leaded Chip Carriers,塑料行间芯片运载)Post-RISC(加速RISC,或后RISC)PPE(Power Processor Element,Power处理器元件)PPU(Physics Processing Unit,物理处理单元)PR(Performance Rate,性能比率)PIB(Processor In a Box,盒装处理器)PM(Pseudo-Multithreading,假多线程)PPGA(Plastic Pin Grid Array,塑胶针状网阵封装)PQFP(Plastic Quad Flat Package,塑料方块平面封装)PSN(Processor Serial numbers,处理器序列号)QFP(Quad Flat Package,方块平面封装)QSPS(Quick Start Power State,快速启动能源状态)RAS(Return Address Stack,返回地址堆栈)RAW(Read after Write,写后读)REE(Rapid Execution Engine,快速执行引擎)Register Contention(抢占寄存器)Register Pressure(寄存器不足)Register Renaming(寄存器重命名)Remark(芯片频率重标识)Resource contention(资源冲突)Retirement(指令引退)RISC(Reduced Instruction Set Computing,精简指令集计算机)ROB(Re-Order Buffer,重排序缓冲区)RSE(register stack engine,寄存器堆栈引擎)RTL(Register Transfer Level,暫存器轉換層。

计算机英语词汇

计算机英语词汇计算机英语词汇大全英语单词的产生是汉英两种语言双向交流的产物,一些带有中国特色的名称和概念进入了英语词汇,同时还有一些英语词汇进入了汉语,在文化环境中衍生出新的含义,形成了英语词汇的语义文化特征。

以下是店铺帮大家整理的计算机英语词汇大全,欢迎阅读与收藏。

计算机英语词汇1alu(arithmetic logic unit,算术逻辑单元)agu(address generation units,地址产成单元)bga(ball grid array,球状矩阵排列)bht(branch prediction table,分支预测表)bpu(branch processing unit,分支处理单元)brach pediction(分支预测)cmos: complementary metal oxide semiconductor,互补金属氧化物半导体cisc(complex instruction set computing,复杂指令集计算机)clk(clock cycle,时钟周期)cob(cache on board,板上集成缓存)cod(cache on die,芯片内集成缓存)cpga(ceramic pin grid array,陶瓷针型栅格阵列)cpu(center processing unit,中央处理器)data forwarding(数据前送)decode(指令解码)dib(dual independent bus,双独立总线)ec(embedded controller,嵌入式控制器)embedded chips(嵌入式)epic(explicitly parallel instruction code,并行指令代码)fadd(floationg point addition,浮点加)fcpga(flip chip pin grid array,反转芯片针脚栅格阵列)fdiv(floationg point divide,浮点除)femms:fast entry/exit multimedia state,快速进入/退出多媒体状态fft(fast fourier transform,快速热欧姆转换)fid(fid:frequency identify,频率鉴别号码)fifo(first input first output,先入先出队列)flip-chip(芯片反转)flop(floating point operations per second,浮点操作/秒)fmul(floationg point multiplication,浮点乘)fpu(float point unit,浮点运算单元)fsub(floationg point subtraction,浮点减)gvpp(generic visual perception processor,常规视觉处理器) hl-pbga: 表面黏著,高耐热、轻薄型塑胶球状矩阵封装ia(intel architecture,英特尔架构)icu(instruction control unit,指令控制单元)id:identify,鉴别号码idf(intel developer forum,英特尔开发者论坛)ieu(integer execution units,整数执行单元)imm: intel mobile module,英特尔移动模块instructions cache,指令缓存instruction coloring(指令分类)ipc(instructions per clock cycle,指令/时钟周期)isa(instruction set architecture,指令集架构)kni(katmai new instructions,katmai新指令集,即sse)latency(潜伏期)ldt(lightning data transport,闪电数据传输总线)local interconnect(局域互连)mesi(modified,exclusive,shared,invalid:修改、排除、共享、废弃)mmx(multimedia extensions,多媒体扩展指令集)mmu(multimedia unit,多媒体单元)mflops(million floationg point/second,每秒百万个浮点操作) mhz(million hertz,兆赫兹)mp(multi-processing,多重处理器架构)mps(multiprocessor specification,多重处理器规范)msrs(model-specific registers,特别模块寄存器)naoc(no-account overclock,无效超频)ni:non-intel,非英特尔olga(organic land grid array,基板栅格阵列)ooo(out of order,乱序执行)pga: pin-grid array(引脚网格阵列),耗电大post-riscpr(performance rate,性能比率)psn(processor serial numbers,处理器序列号)pib(processor in a box,盒装处理器)ppga(plastic pin grid array,塑胶针状矩阵封装)pqfp(plastic quad flat package,塑料方块平面封装)raw(read after write,写后读)register contention(抢占寄存器)register pressure(寄存器不足)register renaming(寄存器重命名)remark(芯片频率重标识)resource contention(资源冲突)retirement(指令引退)risc(reduced instruction set computing,精简指令集计算机) sec: single edge connector,单边连接器shallow-trench isolation(浅槽隔离)simd(single instruction multiple data,单指令多数据流)sio2f(fluorided silicon oxide,二氧氟化硅)smi(system management interrupt,系统管理中断)smm(system management mode,系统管理模式)smp(symmetric multi-processing,对称式多重处理架构)soi: silicon-on-insulator,绝缘体硅片sonc(system on a chip,系统集成芯片)spec(system performance evaluation corporation,系统性能评估测试)sqrt(square root calculations,平方根计算)sse(streaming simd extensions,单一指令多数据流扩展)superscalar(超标量体系结构)tcp: tape carrier package(薄膜封装),发热小throughput(吞吐量)tlb(translate look side buffers,翻译旁视缓冲器)uswc(uncacheabled speculative write combination,无缓冲随机联合写操作)valu(vector arithmetic logic unit,向量算术逻辑单元)vliw(very long instruction word,超长指令字)vpu(vector permutate unit,向量排列单元)vpu(vector processing units,向量处理单元,即处理mmx、sse等simd指令的地方)adimm(advanced dual in-line memory modules,高级双重内嵌式内存模块)amr(audio/modem riser;音效/调制解调器主机板附加直立插卡) aha(accelerated hub architecture,加速中心架构)。

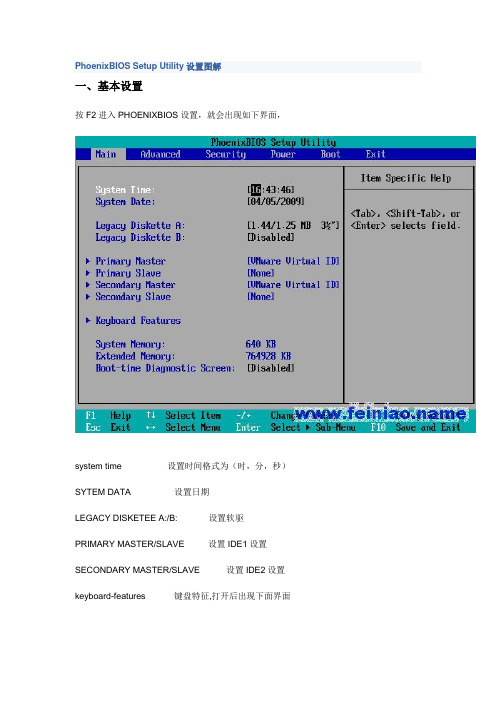

PhoenixBIOS Setup Utility中英文解析

①Main:1.System time 设置时间格式为(时,分,秒)2.SYTEM DATA 设置日期3.LEGACY DISKETEE A:/B: 设置软驱4.PRIMARY MASTER/SLAVE 设置IDE1设置5.SECONDARY MASTER/SLAVE 设置IDE2设置6.keyboard-features 键盘特征【numlock 小键盘灯keyboard auto repeat rate 键盘自动重复时间keyboard auto repeat delay 键盘自动重复延迟时间】7.SYSTEM MENORY 系统内存8.EXTENDED MEMORY 扩展内存6.BOOT-time diagnostic screnn 启动时间诊断屏幕②Advanced(高级设置)1.Multiprocessor Specification 多重处理器规范 1.4 /1.1它专用于多处理器主板,用于确定MPS的版本,以便让PC制造商构建基于英特尔架构的多处理器系统。

与1.1标准相比,1.4增加了扩展型结构表,可用于多重PCI总线,并且对未来的升级十分有利。

另外,v1.4拥有第二条PCI总线,还无须PCI桥连接。

新型的SOS(Server Operating Systems,服务器操作系统)大都支持1.4标准,包括WinNTt 和Linux SMP(Symmetric Multi-Processing,对称式多重处理架构)。

如果可以的话,尽量使用1.4。

Installed o/s 安装O/S模式有IN95和OTHER两个值。

Reset Configuration Data 重设配置数据,有YES和NO两个值。

ache Memory (快取记忆体)此部份提供使用者如何组态特定记忆体区块的方法.【Memory Cache (记忆体快取)设定记忆体的状态.Enabled开启记忆体快取功能.Disabled关闭记忆体快取功能.(预设值)Cache System BIOS area (快取系统BIOS区域)控制系统BIOS区域的快取.Uncached不快取系统BIOS区域.Write Protect忽略写入/储存设定.(预设值)Cache Vedio BIOS area (快取视讯BIOS区域)控制视讯BIOS区域的快取.Uncached不快取视讯BIOS区域.Write Protect忽略写入/储存设定.(预设值)Cache Base 0-512K / 512K-640K (快取传统0-512K / 512K-640K)控制512K / 512K-640K传统记忆体的快取.Uncached不快取视讯BIOS区域.Write Through将写入快取,并同时传送至主记忆体.Write Protect忽略写入/储存设定.Write Back将写入快取,但除非必要,不传送至主记忆体.(预设Cache Extended Memory Area (快取延伸记忆体区域)控制1MB以上的系统记忆体.Uncached不快取视讯BIOS区域.Write Through将写入快取,并同时传送至主记忆体.Write Protect忽略写入/储存设定.Write Back将写入快取,但除非必要,不传送至主记忆体.(预设值)Cache A000-AFFF / B000-BFFF/ C8000-CFFF / CC00-CFFF / D000-DFFF /D400-D7FF/ D800-DBFF / DC00-DFFF / E000-E3FF / E400-F7FFDisabled不快取这个区块.(预设值)USWC CachingUncached Speculative Write Combined.】3.I/O Device Configuration输入输出选项【Serial port A:/B:串行口也就是常说的COM口设置有三个值AUTO自动,ENABLED开启,DISABLED关闭。

PhoenixBIOS Setup Utility设置图解

PhoenixBIOS Setup Utility设置图解一、基本设置按F2进入PHOENIXBIOS设置,就会出现如下界面,system time 设置时间格式为(时,分,秒)SYTEM DATA 设置日期LEGACY DISKETEE A:/B: 设置软驱PRIMARY MASTER/SLAVE 设置IDE1设置SECONDARY MASTER/SLAVE 设置IDE2设置keyboard-features 键盘特征,打开后出现下面界面numlock 小键盘灯keyboard auto repeat rate 键盘自动重复时间keyboard auto repeat delay 键盘自动重复延迟时间SYSTEM MENORY 系统内存EXTENDED MEMORY 扩展内存BOOT-time diagnostic screnn 启动时间诊断屏幕二、高级设置Advanced(高级设置)Multiprocessor Specification 多重处理器规范 1.4 /1.1它专用于多处理器主板,用于确定MPS的版本,以便让PC制造商构建基于英特尔架构的多处理器系统。

与1.1标准相比,1.4增加了扩展型结构表,可用于多重PCI总线,并且对未来的升级十分有利。

另外,v1.4拥有第二条PCI总线,还无须PCI桥连接。

新型的SOS(Server Operating Systems,服务器操作系统)大都支持1.4标准,包括WinNTt和Linux SMP(Symmetric Multi-Processing,对称式多重处理架构)。

如果可以的话,尽量使用1.4。

Installed o/s 安装O/S模式有IN95和OTHER两个值。

Reset Configuration Data 重设配置数据,有YES和NO两个值。

CCache Memory (快取记忆体)此部份提供使用者如何组态特定记忆体区块的方法.Memory Cache (记忆体快取)设定记忆体的状态.Enabled开启记忆体快取功能.Disabled关闭记忆体快取功能.(预设值)Cache System BIOS area (快取系统BIOS区域)控制系统BIOS区域的快取.Uncached不快取系统BIOS区域.Write Protect忽略写入/储存设定.(预设值)Cache Vedio BIOS area (快取视讯BIOS区域)控制视讯BIOS区域的快取.Uncached不快取视讯BIOS区域.Write Protect忽略写入/储存设定.(预设值)Cache Base 0-512K / 512K-640K (快取传统0-512K / 512K-640K) 控制512K / 512K-640K传统记忆体的快取.Uncached不快取视讯BIOS区域.Write Through将写入快取,并同时传送至主记忆体.Write Protect忽略写入/储存设定.Write Back将写入快取,但除非必要,不传送至主记忆体.(预设Cache Extended Memory Area (快取延伸记忆体区域)控制1MB以上的系统记忆体.Uncached不快取视讯BIOS区域.Write Through将写入快取,并同时传送至主记忆体.Write Protect忽略写入/储存设定.Write Back将写入快取,但除非必要,不传送至主记忆体.(预设值) Cache A000-AFFF / B000-BFFF/ C8000-CFFF / CC00-CFFF / D000-DFFF /D400-D7FF/ D800-DBFF / DC00-DFFF / E000-E3FF / E400-F7FFDisabled不快取这个区块.(预设值)USWC CachingUncached Speculative Write Combined.I/O Device Configuration输入输出选项Serial port A:/B:串行口也就是常说的COM口设置有三个值AUTO自动,ENABLED开启,DISABLED关闭。

通信缩写术语

计算机缩写术语完全介绍在使用计算机的过程中,你可能会碰到各种各样的专业术语,特别是那些英文缩写常让我们不知所云,下面收集了各方面的词组,希望对大家有帮助。

一、港台术语与内地术语之对照由于港台的计算机发展相对快一些,许多人都去香港或台湾寻找资料,但是港台使用的电脑专业术语与内地不尽相同,你也许曾被这些东西弄得糊里糊涂的。

---------------------------港台术语内地术语埠接口位元位讯号信号数码数字类比模拟高阶高端低阶低端时脉时钟频宽带宽光碟光盘磁碟磁盘硬碟硬盘程式程序绘图图形数位数字网路网络硬体硬件软体软件介面接口母板主板主机板主板软碟机软驱记忆体内存绘图卡显示卡监视器显示器声效卡音效卡解析度分辨率相容性兼容性数据机调制解调器---------------------------二、英文术语完全介绍在每组术语中,我按照英文字母的排列顺序来分类。

1、CPU3DNow!(3D no waiting,无须等待的3D处理)AAM(AMD Analyst Meeting,AMD分析家会议)ABP(Advanced Branch Prediction,高级分支预测)ACG(Aggressive Clock Gating,主动时钟选择)AIS(Alternate Instruction Set,交替指令集)ALAT(advanced load table,高级载入表)ALU(Arithmetic Logic Unit,算术逻辑单元)Aluminum(铝)AGU(Address Generation Units,地址产成单元)APC(Advanced Power Control,高级能源控制)APIC(Advanced rogrammable Interrupt Controller,高级可编程中断控制器)APS(Alternate Phase Shifting,交替相位跳转)ASB(Advanced System Buffering,高级系统缓冲)ATC(Advanced Transfer Cache,高级转移缓存)ATD(Assembly Technology Development,装配技术发展)BBUL(Bumpless Build-Up Layer,内建非凹凸层)BGA(Ball Grid Array,球状网阵排列)BHT(branch prediction table,分支预测表)Bops(Billion Operations Per Second,10亿操作/秒)BPU(Branch Processing Unit,分支处理单元)BP(Brach Pediction,分支预测)BSP(Boot Strap Processor,启动捆绑处理器)BTAC(Branch Target Address Calculator,分支目标寻址计算器)CBGA (Ceramic Ball Grid Array,陶瓷球状网阵排列)CDIP (Ceramic Dual-In-Line,陶瓷双重直线)Center Processing Unit Utilization,中央处理器占用率CFM(cubic feet per minute,立方英尺/秒)CMT(course-grained multithreading,过程消除多线程)CMOS(Complementary Metal Oxide Semiconductor,互补金属氧化物半导体)CMOV(conditional move instruction,条件移动指令)CISC(Complex Instruction Set Computing,复杂指令集计算机)CLK(Clock Cycle,时钟周期)CMP(on-chip multiprocessor,片内多重处理)CMS(Code Morphing Software,代码变形软件)co-CPU(cooperative CPU,协处理器)COB(Cache on board,板上集成缓存,做在CPU卡上的二级缓存,通常是内核的一半速度))COD(Cache on Die,芯片内核集成缓存)Copper(铜)CPGA(Ceramic Pin Grid Array,陶瓷针型栅格阵列)CPI(cycles per instruction,周期/指令)CPLD(Complex Programmable Logic Device,複雜可程式化邏輯元件)CPU(Center Processing Unit,中央处理器)CRT(Cooperative Redundant Threads,协同多余线程)CSP(Chip Scale Package,芯片比例封装)CXT(Chooper eXTend,增强形K6-2内核,即K6-3)Data Forwarding(数据前送)dB(decibel,分贝)DCLK(Dot Clock,点时钟)DCT(DRAM Controller,DRAM控制器)DDT(Dynamic Deferred Transaction,动态延期处理)Decode(指令解码)DIB(Dual Independent Bus,双重独立总线)DMT(Dynamic Multithreading Architecture,动态多线程结构)DP(Dual Processor,双处理器)DSM(Dedicated Stack Manager,专门堆栈管理)DSMT(Dynamic Simultaneous Multithreading,动态同步多线程)DST(Depleted Substrate Transistor,衰竭型底层晶体管)DTV(Dual Threshold Voltage,双重极限电压)DUV(Deep Ultra-Violet,纵深紫外光)EBGA(Enhanced Ball Grid Array,增强形球状网阵排列)EBL(electron beam lithography,电子束平版印刷)EC(Embedded Controller,嵌入式控制器)EDEC(Early Decode,早期解码)Embedded Chips(嵌入式)EPA(edge pin array,边缘针脚阵列)EPF(Embedded Processor Forum,嵌入式处理器论坛)EPL(electron projection lithography,电子发射平版印刷)EPM(Enhanced Power Management,增强形能源管理)EPIC(explicitly parallel instruction code,并行指令代码)EUV(Extreme Ultra Violet,紫外光)EUV(extreme ultraviolet lithography,极端紫外平版印刷)FADD(Floationg Point Addition,浮点加)FBGA(Fine-Pitch Ball Grid Array,精细倾斜球状网阵排列)FBGA(flipchip BGA,轻型芯片BGA)FC-BGA(Flip-Chip Ball Grid Array,反转芯片球形栅格阵列)FC-PGA(Flip-Chip Pin Grid Array,反转芯片针脚栅格阵列)FDIV(Floationg Point Divide,浮点除)FEMMS:Fast Entry/Exit Multimedia State,快速进入/退出多媒体状态FFT(fast Fourier transform,快速热欧姆转换)FGM(Fine-Grained Multithreading,高级多线程)FID(FID:Frequency identify,频率鉴别号码)FIFO(First Input First Output,先入先出队列)FISC(Fast Instruction Set Computer,快速指令集计算机)flip-chip(芯片反转)FLOPs(Floating Point Operations Per Second,浮点操作/秒)FMT(fine-grained multithreading,纯消除多线程)FMUL(Floationg Point Multiplication,浮点乘)FPRs(floating-point registers,浮点寄存器)FPU(Float Point Unit,浮点运算单元)FSUB(Floationg Point Subtraction,浮点减)GFD(Gold finger Device,金手指超频设备)GHC(Global History Counter,通用历史计数器)GTL(Gunning Transceiver Logic,射电收发逻辑电路)GVPP(Generic Visual Perception Processor,常规视觉处理器)HL-PBGA: 表面黏著,高耐热、轻薄型塑胶球状网阵封装HTT(Hyper-Threading Technology,超级线程技术)Hz(hertz,赫兹,频率单位)IA(Intel Architecture,英特尔架构)IAA(Intel Application Accelerator,英特尔应用程序加速器)ICU(Instruction Control Unit,指令控制单元)ID(identify,鉴别号码)IDF(Intel Developer Forum,英特尔开发者论坛)IEU(Integer Execution Units,整数执行单元)IHS(Integrated Heat Spreader,完整热量扩展)ILP(Instruction Level Parallelism,指令级平行运算)IMM: Intel Mobile Module, 英特尔移动模块Instructions Cache,指令缓存Instruction Coloring(指令分类)IOPs(Integer Operations Per Second,整数操作/秒)IPC(Instructions Per Clock Cycle,指令/时钟周期)ISA(instruction set architecture,指令集架构)ISD(inbuilt speed-throttling device,内藏速度控制设备)ITC(Instruction Trace Cache,指令追踪缓存)ITRS(International Technology Roadmap for Semiconductors,国际半导体技术发展蓝图)KNI(Katmai New Instructions,Katmai新指令集,即SSE)Latency(潜伏期)LDT(Lightning Data Transport,闪电数据传输总线)LFU(Legacy Function Unit,传统功能单元)LGA(land grid array,接点栅格阵列)LN2(Liquid Nitrogen,液氮)Local Interconnect(局域互连)MAC(multiply-accumulate,累积乘法)mBGA (Micro Ball Grid Array,微型球状网阵排列)nm(namometer,十亿分之一米/毫微米)MCA(machine check architecture,机器检查体系)MCU(Micro-Controller Unit,微控制器单元)MCT(Memory Controller,内存控制器)MESI(Modified, Exclusive, Shared, Invalid:修改、排除、共享、废弃)MF(MicroOps Fusion,微指令合并)mm(micron metric,微米)MMX(MultiMedia Extensions,多媒体扩展指令集)MMU(Multimedia Unit,多媒体单元)MMU(Memory Management Unit,内存管理单元)MN(model numbers,型号数字)MFLOPS(Million Floationg Point/Second,每秒百万个浮点操作)MHz(megahertz,兆赫)mil(PCB 或晶片佈局的長度單位,1 mil = 千分之一英寸)MIPS(Million Instruction Per Second,百万条指令/秒)MOESI(Modified, Owned, Exclusive, Shared or Invalid,修改、自有、排除、共享或无效)MOF(Micro Ops Fusion,微操作熔合)Mops(Million Operations Per Second,百万次操作/秒)MP(Multi-Processing,多重处理器架构)MPF(Micro processor Forum,微处理器论坛)MPU(Microprocessor Unit,微处理器)MPS(MultiProcessor Specification,多重处理器规范)MSRs(Model-Specific Registers,特别模块寄存器)MSV(Multiprocessor Specification Version,多处理器规范版本)NAOC(no-account OverClock,无效超频)NI(Non-Intel,非英特尔)NOP(no operation,非操作指令)NRE(Non-Recurring Engineering charge,非重複性工程費用)OBGA(Organic Ball Grid Arral,有机球状网阵排列)OCPL(Off Center Parting Line,远离中心部分线队列)OLGA(Organic Land Grid Array,有机平面网阵包装)OoO(Out of Order,乱序执行)OPC(Optical Proximity Correction,光学临近修正)OPGA(Organic Pin Grid Array,有机塑料针型栅格阵列)OPN(Ordering Part Number,分类零件号码)PAT(Performance Acceleration Technology,性能加速技术)PBGA(Plastic Pin Ball Grid Array,塑胶球状网阵排列)PDIP (Plastic Dual-In-Line,塑料双重直线)PDP(Parallel Data Processing,并行数据处理)PGA(Pin-Grid Array,引脚网格阵列),耗电大PLCC (Plastic Leaded Chip Carriers,塑料行间芯片运载)Post-RISC(加速RISC,或后RISC)PR(Performance Rate,性能比率)PIB(Processor In a Box,盒装处理器)PM(Pseudo-Multithreading,假多线程)PPGA(Plastic Pin Grid Array,塑胶针状网阵封装)PQFP(Plastic Quad Flat Package,塑料方块平面封装)PSN(Processor Serial numbers,处理器序列号)QFP(Quad Flat Package,方块平面封装)QSPS(Quick Start Power State,快速启动能源状态)RAS(Return Address Stack,返回地址堆栈)RAW(Read after Write,写后读)REE(Rapid Execution Engine,快速执行引擎)Register Contention(抢占寄存器)Register Pressure(寄存器不足)Register Renaming(寄存器重命名)Remark(芯片频率重标识)Resource contention(资源冲突)Retirement(指令引退)RISC(Reduced Instruction Set Computing,精简指令集计算机)ROB(Re-Order Buffer,重排序缓冲区)RSE(register stack engine,寄存器堆栈引擎)RTL(Register Transfer Level,暫存器轉換層。

PHOENIXBIOS设置图解教程

按F2进入PHOENIXBIOS设置,就会出现如下界面,system time设置时间格式为(时,分,秒)SYTEM DATA设置日期LEGACY DISKETEE A:/B:设置软驱PRIMARY MASTER/SLAVE设置IDE1设置SECONDARY MASTER/SLAVE设置IDE2设置keyboard-features键盘特征,打开后出现下面界面numlock小键盘灯keyboard auto repeat rate键盘自动重复时间keyboard auto repeat delay键盘自动重复延迟时间SYSTEM MENORY系统内存EXTENDED MEMORY扩展内存BOOT-time diagnostic screnn启动时间诊断屏幕Advanced(高级设置)Multiprocessor Specification多重处理器规范 1.4/1.1它专用于多处理器主板,用于确定MPS的版本,以便让PC制造商构建基于英特尔架构的多处理器系统。

与1.1标准相比,1.4增加了扩展型结构表,可用于多重PCI总线,并且对未来的升级十分有利。

另外,v1.4拥有第二条PCI总线,还无须PCI桥连接。

新型的SOS(Server Operating Systems,服务器操作系统)大都支持1.4标准,包括WinNTt和Linux SMP(Symmetric Multi-Processing,对称式多重处理架构)。

如果可以的话,尽量使用1.4。

Installed o/s安装O/S模式有IN95和OTHER两个值。

Reset Configuration Data重设配置数据,有YES和NO两个值。

CCache Memory (快取记忆体)此部份提供使用者如何组态特定记忆体区块的方法.Memory Cache (记忆体快取)设定记忆体的状态.Enabled开启记忆体快取功能.Disabled关闭记忆体快取功能.(预设值)Cache System BIOS area (快取系统BIOS区域)控制系统BIOS区域的快取.Uncached不快取系统BIOS区域.Write Protect忽略写入/储存设定.(预设值) Cache Vedio BIOS area (快取视讯BIOS区域)控制视讯BIOS区域的快取.Uncached不快取视讯BIOS区域.Write Protect忽略写入/储存设定.(预设值) Cache Base 0-512K / 512K-640K (快取传统0-512K / 512K-640K)控制512K / 512K-640K传统记忆体的快取.Uncached不快取视讯BIOS区域.Write Through将写入快取,并同时传送至主记忆体.Write Protect忽略写入/储存设定.Write Back将写入快取,但除非必要,不传送至主记忆体.(预设Cache Extended Memory Area (快取延伸记忆体区域)控制1MB以上的系统记忆体.Uncached不快取视讯BIOS区域.Write Through将写入快取,并同时传送至主记忆体.Write Protect忽略写入/储存设定.Write Back将写入快取,但除非必要,不传送至主记忆体.(预设值)Cache A000-AFFF / B000-BFFF/ C8000-CFFF / CC00-CFFF /D000-DFFF /D400-D7FF/ D800-DBFF / DC00-DFFF / E000-E3FF / E400-F7FFDisabled不快取这个区块.(预设值)USWC CachingUncached Speculative Write Combined.I/O Device Configuration输入输出选项Serial port A:/B:串行口也就是常说的COM口设置有三个值AUTO自动,ENABLED开启,DISABLED关闭。

计算机英语缩写

计算机英语缩写整理者:quetzal3DNow!(3D no waiting,无须等待的3D处理)AAM(AMD Analyst Meeting,AMD分析家会议)ABP(Advanced Branch Prediction,高级分支预测)ACG(Aggressive Clock Gating,主动时钟选择)AIS(Alternate Instruction Set,交替指令集)ALAT(advanced load table,高级载入表)ALU(Arithmetic Logic Unit,算术逻辑单元)AGU(Address Generation Units,地址产成单元)APC(Advanced Power Control,高级能源控制)APIC(Advanced rogrammable Interrupt Controller,高级可编程中断控制器)APS(Alternate Phase Shifting,交替相位跳转)ASB(Advanced System Buffering,高级系统缓冲)ATC(Advanced Transfer Cache,高级转移缓存)ATD(Assembly Technology Development,装配技术发展)BBUL(Bumpless Build-Up Layer,内建非凹凸层)BGA(Ball Grid Array,球状网阵排列)BHT(branch prediction table,分支预测表)Bops(Billion Operations Per Second,10亿操作/秒)BPU(Branch Processing Unit,分支处理单元)BP(Brach Pediction,分支预测)BSP(Boot Strap Processor,启动捆绑处理器)BTAC(Branch Target Address Calculator,分支目标寻址计算器)CBGA (Ceramic Ball Grid Array,陶瓷球状网阵排列)CDIP (Ceramic Dual-In-Line,陶瓷双重直线)Center Processing Unit Utilization,中央处理器占用率CFM(cubic feet per minute,立方英尺/秒)CMT(course-grained multithreading,过程消除多线程)CMOS(Complementary Metal Oxide Semiconductor,互补金属氧化物半导体)CMOV(conditional move instruction,条件移动指令)CISC(Complex Instruction Set Computing,复杂指令集计算机)CLK(Clock Cycle,时钟周期)CMP(on-chip multiprocessor,片内多重处理)CMS(Code Morphing Software,代码变形软件)co-CPU(cooperative CPU,协处理器)COB(Cache on board,板上集成缓存,做在CPU卡上的二级缓存,通常是内核的一半速度)COD(Cache on Die,芯片内核集成缓存)Copper(铜)CPGA(Ceramic Pin Grid Array,陶瓷针型栅格阵列)CPI(cycles per instruction,周期/指令)CPLD(Complex Programmable Logic Device,複雜可程式化邏輯元件)CPU(Center Processing Unit,中央处理器)CRT(Cooperative Redundant Threads,协同多余线程)CSP(Chip Scale Package,芯片比例封装)CXT(Chooper eXTend,增强形K6-2内核,即K6-3)Data Forwarding(数据前送)dB(decibel,分贝)DCLK(Dot Clock,点时钟)DCT(DRAM Controller,DRAM控制器)DDT(Dynamic Deferred Transaction,动态延期处理)Decode(指令解码)DIB(Dual Independent Bus,双重独立总线)DMT(Dynamic Multithreading Architecture,动态多线程结构)DP(Dual Processor,双处理器)DSM(Dedicated Stack Manager,专门堆栈管理)DSMT(Dynamic Simultaneous Multithreading,动态同步多线程)DST(Depleted Substrate Transistor,衰竭型底层晶体管)DTV(Dual Threshold Voltage,双重极限电压)DUV(Deep Ultra-Violet,纵深紫外光)EBGA(Enhanced Ball Grid Array,增强形球状网阵排列)EBL(electron beam lithography,电子束平版印刷)EC(Embedded Controller,嵌入式控制器)EDEC(Early Decode,早期解码)Embedded Chips(嵌入式)EPA(edge pin array,边缘针脚阵列)EPF(Embedded Processor Forum,嵌入式处理器论坛)EPL(electron projection lithography,电子发射平版印刷)EPM(Enhanced Power Management,增强形能源管理)EPIC(explicitly parallel instruction code,并行指令代码)EUV(Extreme Ultra Violet,紫外光)EUV(extreme ultraviolet lithography,极端紫外平版印刷)FADD(Floationg Point Addition,浮点加)FBGA(Fine-Pitch Ball Grid Array,精细倾斜球状网阵排列)FBGA(flipchip BGA,轻型芯片BGA)FC-BGA(Flip-Chip Ball Grid Array,反转芯片球形栅格阵列)FC-PGA(Flip-Chip Pin Grid Array,反转芯片针脚栅格阵列)FDIV(Floationg Point Divide,浮点除)FEMMS:Fast Entry/Exit Multimedia State,快速进入/退出多媒体状态FFT(fast Fourier transform,快速热欧姆转换)FGM(Fine-Grained Multithreading,高级多线程)FID(FID:Frequency identify,频率鉴别号码)FIFO(First Input First Output,先入先出队列)FISC(Fast Instruction Set Computer,快速指令集计算机)flip-chip(芯片反转)FLOPs(Floating Point Operations Per Second,浮点操作/秒)FMT(fine-grained multithreading,纯消除多线程)FMUL(Floationg Point Multiplication,浮点乘)FPRs(floating-point registers,浮点寄存器)FPU(Float Point Unit,浮点运算单元)FSUB(Floationg Point Subtraction,浮点减)GFD(Gold finger Device,金手指超频设备)GHC(Global History Counter,通用历史计数器)GTL(Gunning Transceiver Logic,射电收发逻辑电路)GVPP(Generic Visual Perception Processor,常规视觉处理器)HL-PBGA: 表面黏著,高耐热、轻薄型塑胶球状网阵封装HTT(Hyper-Threading Technology,超级线程技术)Hz(hertz,赫兹,频率单位)IA(Intel Architecture,英特尔架构)IAA(Intel Application Accelerator,英特尔应用程序加速器)ICU(Instruction Control Unit,指令控制单元)ID(identify,鉴别号码)IDF(Intel Developer Forum,英特尔开发者论坛)IEU(Integer Execution Units,整数执行单元)IHS(Integrated Heat Spreader,完整热量扩展)ILP(Instruction Level Parallelism,指令级平行运算)IMM: Intel Mobile Module, 英特尔移动模块Instructions Cache,指令缓存Instruction Coloring(指令分类)IOPs(Integer Operations Per Second,整数操作/秒)IPC(Instructions Per Clock Cycle,指令/时钟周期)ISA(instruction set architecture,指令集架构)ISD(inbuilt speed-throttling device,内藏速度控制设备)ITC(Instruction Trace Cache,指令追踪缓存)ITRS(International Technology Roadmap forSemiconductors,国际半导体技术发展蓝图)KNI(Katmai New Instructions,Katmai新指令集,即SSE)Latency(潜伏期)LDT(Lightning Data Transport,闪电数据传输总线)LFU(Legacy Function Unit,传统功能单元)LGA(land grid array,接点栅格阵列)LN2(Liquid Nitrogen,液氮)Local Interconnect(局域互连)MAC(multiply-accumulate,累积乘法)mBGA (Micro Ball Grid Array,微型球状网阵排列)nm(namometer,十亿分之一米/毫微米)MCA(machine check architecture,机器检查体系)MCU(Micro-Controller Unit,微控制器单元)MCT(Memory Controller,内存控制器)MESI(Modified, Exclusive, Shared, Invalid:修改、排除、共享、废弃)MF(MicroOps Fusion,微指令合并)mm(micron metric,微米)MMX(MultiMedia Extensions,多媒体扩展指令集)MMU(Multimedia Unit,多媒体单元)MMU(Memory Management Unit,内存管理单元)MN(model numbers,型号数字)MFLOPS(Million Floationg Point/Second,每秒百万个浮点操作)MHz(megahertz,兆赫)mil(PCB 或晶片佈局的長度單位,1 mil = 千分之一英寸)MIPS(Million Instruction Per Second,百万条指令/秒)MOESI(Modified, Owned, Exclusive, Shared or Invalid,修改、自有、排除、共享或无效)MOF(Micro Ops Fusion,微操作熔合)Mops(Million Operations Per Second,百万次操作/秒)MP(Multi-Processing,多重处理器架构)MPF(Micro processor Forum,微处理器论坛)MPU(Microprocessor Unit,微处理器)MPS(MultiProcessor Specification,多重处理器规范)MSRs(Model-Specific Registers,特别模块寄存器)MSV(Multiprocessor Specification Version,多处理器规范版本)NAOC(no-account OverClock,无效超频)NI(Non-Intel,非英特尔)NOP(no operation,非操作指令)NRE(Non-Recurring Engineering charge,非重複性工程費用)OBGA(Organic Ball Grid Arral,有机球状网阵排列)OCPL(Off Center Parting Line,远离中心部分线队列)OLGA(Organic Land Grid Array,有机平面网阵包装)OoO(Out of Order,乱序执行)OPC(Optical Proximity Correction,光学临近修正)OPGA(Organic Pin Grid Array,有机塑料针型栅格阵列)OPN(Ordering Part Number,分类零件号码)PAT(Performance Acceleration Technology,性能加速技术)PBGA(Plastic Pin Ball Grid Array,塑胶球状网阵排列)PDIP (Plastic Dual-In-Line,塑料双重直线)PDP(Parallel Data Processing,并行数据处理)PGA(Pin-Grid Array,引脚网格阵列),耗电大PLCC (Plastic Leaded Chip Carriers,塑料行间芯片运载)Post-RISC(加速RISC,或后RISC)PR(Performance Rate,性能比率)PIB(Processor In a Box,盒装处理器)PM(Pseudo-Multithreading,假多线程)PPGA(Plastic Pin Grid Array,塑胶针状网阵封装)PQFP(Plastic Quad Flat Package,塑料方块平面封装)PSN(Processor Serial numbers,处理器序列号)QFP(Quad Flat Package,方块平面封装)QSPS(Quick Start Power State,快速启动能源状态)RAS(Return Address Stack,返回地址堆栈)RAW(Read after Write,写后读)REE(Rapid Execution Engine,快速执行引擎)Register Contention(抢占寄存器)Register Pressure(寄存器不足)Register Renaming(寄存器重命名)Remark(芯片频率重标识)Resource contention(资源冲突)Retirement(指令引退)RISC(Reduced Instruction Set Computing,精简指令集计算机)ROB(Re-Order Buffer,重排序缓冲区)RSE(register stack engine,寄存器堆栈引擎)RTL(Register Transfer Level,暫存器轉換層。

MPC755资料

To locate any published errata or updates for this document, refer to the website at .

Contents 1. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 2. Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 3. General Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 4. Electrical and Thermal Characteristics . . . . . . . . . . . . 7 5. Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 6. Pinout Listings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 7. Package Description . . . . . . . . . . . . . . . . . . . . . . . . . 31 8. System Design Information . . . . . . . . . . . . . . . . . . . 36 9. Document Revision History . . . . . . . . . . . . . . . . . . . 50 10. Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . 52

(计算机)英文术语完全介绍

(计算机)英文术语完全介绍二、英文术语完全介绍在每组术语中,我按照英文字母的排列顺序来分类。

1、CPU 3DNow!(3D no waiting,无须等待的3D处理) AAM(AMD Analyst Meeting,AMD分析家会议) ABP(Advanced Branch Prediction,高级分支预测)ACG(Aggressive Clock Gating,主动时钟选择) AIS(Alternate Instruction Set,交替指令集) ALAT (advanced load table,高级载入表) ALU(Arithmetic Logic Unit,算术逻辑单元) Aluminum(铝) AGU(Address Generation Units,地址产成单元) APC(Advanced Power Control,高级能源控制) APIC(Advanced rogrammable Interrupt Controller,高级可编程中断控制器) APS(Alternate Phase Shifting,交替相位跳转) ASB(Advanced System Buffering,高级系统缓冲) ATC (Advanced Transfer Cache,高级转移缓存) ATD(Assembly Technology Development,装配技术发展) BBUL(Bumpless Build-Up Layer,内建非凹凸层) BGA(Ball Grid Array,球状网阵排列) BHT(branch prediction table,分支预测表) Bops(Billion Operations Per Second,10亿操作/秒) BPU(Branch Processing Unit,分支处理单元) BP (Brach Pediction,分支预测) BSP(Boot Strap Processor,启动捆绑处理器) BTAC(Branch Target AddressCalculator,分支目标寻址计算器) CBGA (Ceramic Ball Grid Array,陶瓷球状网阵排列) CDIP (Ceramic Dual-In-Line,陶瓷双重直线) Center Processing Unit Utilization,中央处理器占用率 CFM(cubic feet per minute,立方英尺/秒) CMT(course-grained multithreading,过程消除多线程) CMOS(Complementary Metal Oxide Semiconductor,互补金属氧化物半导体) CMOV (conditional move instruction,条件移动指令) CISC (Complex Instruction Set Computing,复杂指令集计算机) CLK(Clock Cycle,时钟周期) CMP(on-chip multiprocessor,片内多重处理) CMS(Code Morphing Software,代码变形软件) co-CPU(cooperative CPU,协处理器) COB(Cache on board,板上集成缓存,做在CPU 卡上的二级缓存,通常是内核的一半速度)) COD(Cache on Die,芯片内核集成缓存) Copper(铜) CPGA(Ceramic Pin Grid Array,陶瓷针型栅格阵列) CPI(cycles per instruction,周期/指令) CPLD(Complex Programmable Logic Device,複雜可程式化邏輯元件) CPU(Center Processing Unit,中央处理器) CRT(Cooperative Redundant Threads,协同多余线程) CSP(Chip Scale Package,芯片比例封装) CXT(Chooper eXTend,增强形K6-2内核,即K6-3) Data Forwarding(数据前送) dB(decibel,分贝) DCLK(Dot Clock,点时钟) DCT(DRAM Controller,DRAM控制器) DDT(Dynamic Deferred Transaction,动态延期处理) Decode(指令解码) DIB(Dual Independent Bus,双重独立总线) DMT(Dynamic Multithreading Architecture,动态多线程结构) DP(Dual Processor,双处理器) DSM(Dedicated Stack Manager,专门堆栈管理) DSMT(Dynamic Simultaneous Multithreading,动态同步多线程) DST(Depleted Substrate Transistor,衰竭型底层晶体管) DTV(Dual Threshold Voltage,双重极限电压) DUV(Deep Ultra-Violet,纵深紫外光) EBGA(Enhanced Ball Grid Array,增强形球状网阵排列) EBL(electron beam lithography,电子束平版印刷) EC(Embedded Controller,嵌入式控制器) EDEC(Early Decode,早期解码) Embedded Chips(嵌入式) EPA(edge pin array,边缘针脚阵列) EPF (Embedded Processor Forum,嵌入式处理器论坛) EPL (electron projection lithography,电子发射平版印刷)EPM(Enhanced Power Management,增强形能源管理) EPIC (explicitly parallel instruction code,并行指令代码)EUV(Extreme Ultra Violet,紫外光) EUV(extreme ultraviolet lithography,极端紫外平版印刷) FADD (Floationg Point Addition,浮点加) FBGA(Fine-PitchBall Grid Array,精细倾斜球状网阵排列) FBGA(flipchip BGA,轻型芯片BGA) FC-BGA(Flip-Chip Ball Grid Array,反转芯片球形栅格阵列) FC-LGA(Flip-Chip Land Grid Array,反转接点栅格阵列) FC-PGA(Flip-Chip Pin Grid Array,反转芯片针脚栅格阵列) FDIV(Floationg Point Divide,浮点除) FEMMS:Fast Entry/Exit Multimedia State,快速进入/退出多媒体状态 FFT(fast Fouriertransform,快速热欧姆转换) FGM(Fine-Grained Multithreading,高级多线程) FID(FID:Frequency identify,频率鉴别号码) FIFO(First Input First Output,先入先出队列) FISC(Fast Instruction Set Computer,快速指令集计算机) flip-chip(芯片反转) FLOPs (Floating Point Operations Per Second,浮点操作/秒)FMT(fine-grained multithreading,纯消除多线程) FMUL (Floationg Point Multiplication,浮点乘) FPRs (floating-point registers,浮点寄存器) FPU(Float Point Unit,浮点运算单元) FSUB(Floationg Point Subtraction,浮点减) GFD(Gold finger Device,金手指超频设备) GHC(Global History Counter,通用历史计数器) GTL(Gunning Transceiver Logic,射电收发逻辑电路) GVPP(Generic Visual Perception Processor,常规视觉处理器) HL-PBGA: 表面黏著,高耐热、轻薄型塑胶球状网阵封装 HTT(Hyper-Threading Technology,超级线程技术) Hz(hertz,赫兹,频率单位) IA(Intel Architecture,英特尔架构) IAA(Intel Application Accelerator,英特尔应用程序加速器) ICU(Instruction Control Unit,指令控制单元) ID(identify,鉴别号码)IDF(Intel Developer Forum,英特尔开发者论坛) IEU (Integer Execution Units,整数执行单元) IHS(Integrated Heat Spreader,完整热量扩展) ILP (Instruction Level Parallelism,指令级平行运算) IMM: Intel Mobile Module, 英特尔移动模块 Instructions Cache,指令缓存 Instruction Coloring(指令分类) IOPs (Integer Operations Per Second,整数操作/秒) IPC (Instructions Per Clock Cycle,指令/时钟周期) ISA (instruction set architecture,指令集架构) ISD (inbuilt speed-throttling device,内藏速度控制设备)ITC(Instruction Trace Cache,指令追踪缓存) ITRS (International Technology Roadmap for Semiconductors,国际半导体技术发展蓝图) KNI(Katmai New Instructions,Katmai新指令集,即SSE) Latency(潜伏期) LDT(Lightning Data Transport,闪电数据传输总线) LFU(Legacy Function Unit,传统功能单元) LGA(land grid array,接点栅格阵列) LN2(Liquid Nitrogen,液氮) Local Interconnect(局域互连) MAC (multiply-accumulate,累积乘法) mBGA (Micro Ball Grid Array,微型球状网阵排列) nm(namometer,十亿分之一米/毫微米) MCA(machine check architecture,机器检查体系) MCU(Micro-Controller Unit,微控制器单元) MCT (Memory Controller,内存控制器) MESI(Modified, Exclusive, Shared, Invalid:修改、排除、共享、废弃)MF(MicroOps Fusion,微指令合并) mm(micron metric,微米) MMX(MultiMedia Extensions,多媒体扩展指令集)MMU(Multimedia Unit,多媒体单元) MMU(Memory Management Unit,内存管理单元) MN(model numbers,型号数字) MFLOPS(Million Floationg Point/Second,每秒百万个浮点操作) MHz(megahertz,兆赫) mil(PCB 或晶片佈局的長度單位,1 mil = 千分之一英寸) MIPS (Million Instruction Per Second,百万条指令/秒) MOESI (Modified, Owned, Exclusive, Shared or Invalid,修改、自有、排除、共享或无效) MOF(Micro Ops Fusion,微操作熔合) Mops(Million Operations Per Second,百万次操作/秒) MP(Multi-Processing,多重处理器架构)MPF(Micro processor Forum,微处理器论坛) MPU (Microprocessor Unit,微处理器) MPS(MultiProcessor Specification,多重处理器规范) MSRs(Model-SpecificRegisters,特别模块寄存器) MSV(MultiprocessorSpecification Version,多处理器规范版本) NAOC (no-account OverClock,无效超频) NI(Non-Intel,非英特尔) NOP(no operation,非操作指令) NRE (Non-Recurring Engineering charge,非重複性工程費用)OBGA(Organic Ball Grid Arral,有机球状网阵排列) OCPL (Off Center Parting Line,远离中心部分线队列) OLGA (Organic Land Grid Array,有机平面网阵包装) OoO(Out of Order,乱序执行) OPC(Optical Proximity Correction,光学临近修正) OPGA(Organic Pin Grid Array,有机塑料针型栅格阵列) OPN(Ordering Part Number,分类零件号码) PAT(Performance Acceleration Technology,性能加速技术) PBGA(Plastic Pin Ball Grid Array,塑胶球状网阵排列) PDIP (Plastic Dual-In-Line,塑料双重直线) PDP(Parallel Data Processing,并行数据处理) PGA (Pin-Grid Array,引脚网格阵列),耗电大 PLCC (Plastic Leaded Chip Carriers,塑料行间芯片运载) Post-RISC(加速RISC,或后RISC) PR(Performance Rate,性能比率)PIB(Processor In a Box,盒装处理器) PM (Pseudo-Multithreading,假多线程) PPGA(Plastic Pin Grid Array,塑胶针状网阵封装) PQFP(Plastic Quad Flat Package,塑料方块平面封装) PSN(Processor Serialnumbers,处理器序列号) QFP(Quad Flat Package,方块平面封装) QSPS(Quick Start Power State,快速启动能源状态) RAS(Return Address Stack,返回地址堆栈) RAW (Read after Write,写后读) REE(Rapid Execution Engine,快速执行引擎) Register Contention(抢占寄存器) Register Pressure(寄存器不足) Register Renaming (寄存器重命名) Remark(芯片频率重标识) Resource contention(资源冲突) Retirement(指令引退) RISC (Reduced Instruction Set Computing,精简指令集计算机) ROB(Re-Order Buffer,重排序缓冲区) RSE(register stack engine,寄存器堆栈引擎) RTL(Register Transfer Level,暫存器轉換層。

硬件英文表

FSUB(Floationg Point Subtraction,浮点减)

GVPP(Generic Visual Perception Processor,常规视觉处理器)

HL-PBGA: 表面黏著,高耐热、轻薄型塑胶球状矩阵封装IA(Intel Architecture,英特尔架构)

BPU(Branch Processing Unit,分支处理单元)

Brach Pediction(分支预测)

CISC(Complex Instruction Set Computing,复杂指令集计算机)

CLK(Clock Cycle,时钟周期)

COB(Cache on board,板上集成缓存)

Reset switch:重启开关

Speaker:喇叭

ห้องสมุดไป่ตู้

Printer:打印机

Scanner:扫描仪

UPS:不断电系统

IDE:集成设备电路 指IDE接口规格Integrated Device Electronics IDE接口装置泛指采用IDE接口的各种设备

SCSI:小型机系统接口 指SCSI接口规格Small Computer System Interface,SCSI接口装置泛指采用SCSI接口的各种设备

Master 主,slave 从(设备主从跳线,常见于IDE硬盘和IDE光驱)

Primary 主要的 secondary 次要的

S.M.A.R.T.:Self-Monitoring, Analysis and Reporting Technology自我监测分析和报告技术。广泛运用于硬盘

1、CPU

芯片相关简写

1、CPU3DNow!(3D no waiting,无须等待的3D处理)AAM(AMD Analyst Meeting,AMD分析家会议)ABP(Advanced Branch Prediction,高级分支预测)ACG(Aggressive Clock Gating,主动时钟选择)AIS(Alternate Instruction Set,交替指令集)ALAT(advanced load table,高级载入表)ALU(Arithmetic Logic Unit,算术逻辑单元)Aluminum(铝)AGU(Address Generation Units,地址产成单元)APC(Advanced Power Control,高级能源控制)APIC(Advanced rogrammable Interrupt Controller,高级可编程中断控制器)APS(Alternate Phase Shifting,交替相位跳转)ASB(Advanced System Buffering,高级系统缓冲)ATC(Advanced Transfer Cache,高级转移缓存)ATD(Assembly Technology Development,装配技术发展)BBUL(Bumpless Build-Up Layer,内建非凹凸层)BGA(Ball Grid Array,球状网阵排列)BHT(branch prediction table,分支预测表)Bops(Billion Operations Per Second,10亿操作/秒)BPU(Branch Processing Unit,分支处理单元)BP(Brach Pediction,分支预测)BSP(Boot Strap Processor,启动捆绑处理器)BTAC(Branch Target Address Calculator,分支目标寻址计算器)CBGA (Ceramic Ball Grid Array,陶瓷球状网阵排列)CDIP (Ceramic Dual-In-Line,陶瓷双重直线)Center Processing Unit Utilization,中央处理器占用率CFM(cubic feet per minute,立方英尺/秒)CMT(course-grained multithreading,过程消除多线程)CMOS(Complementary Metal Oxide Semiconductor,互补金属氧化物半导体)CMOV(conditional move instruction,条件移动指令)CISC(Complex Instruction Set Computing,复杂指令集计算机)CLK(Clock Cycle,时钟周期)CMP(on-chip multiprocessor,片内多重处理)CMS(Code Morphing Software,代码变形软件)co-CPU(cooperative CPU,协处理器)COB(Cache on board,板上集成缓存,做在CPU卡上的二级缓存,通常是内核的一半速度))COD(Cache on Die,芯片内核集成缓存)Copper(铜)CPGA(Ceramic Pin Grid Array,陶瓷针型栅格阵列)CPI(cycles per instruction,周期/指令)CPLD(Complex Programmable Logic Device,复杂可程式化逻辑元件)CPU(Center Processing Unit,中央处理器)CRT(Cooperative Redundant Threads,协同多余线程)CSP(Chip Scale Package,芯片比例封装)CXT(Chooper eXTend,增强形K6-2内核,即K6-3)Data Forwarding(数据前送)dB(decibel,分贝)DCLK(Dot Clock,点时钟)DCT(DRAM Controller,DRAM控制器)DDT(Dynamic Deferred Transaction,动态延期处理)Decode(指令解码)DIB(Dual Independent Bus,双重独立总线)DMT(Dynamic Multithreading Architecture,动态多线程结构)DP(Dual Processor,双处理器)DSM(Dedicated Stack Manager,专门堆栈管理)DSMT(Dynamic Simultaneous Multithreading,动态同步多线程)DST(Depleted Substrate Transistor,衰竭型底层晶体管)DTV(Dual Threshold Voltage,双重极限电压)DUV(Deep Ultra-Violet,纵深紫外光)EBGA(Enhanced Ball Grid Array,增强形球状网阵排列)EBL(electron beam lithography,电子束平版印刷)EC(Embedded Controller,嵌入式控制器)EDEC(Early Decode,早期解码)Embedded Chips(嵌入式)EPA(edge pin array,边缘针脚阵列)EPF(Embedded Processor Forum,嵌入式处理器论坛)EPL(electron projection lithography,电子发射平版印刷)EPM(Enhanced Power Management,增强形能源管理)EPIC(explicitly parallel instruction code,并行指令代码)EUV(Extreme Ultra Violet,紫外光)EUV(extreme ultraviolet lithography,极端紫外平版印刷)FADD(Floationg Point Addition,浮点加)FBGA(Fine-Pitch Ball Grid Array,精细倾斜球状网阵排列)FBGA(flipchip BGA,轻型芯片BGA)FC-BGA(Flip-Chip Ball Grid Array,反转芯片球形栅格阵列)FC-LGA(Flip-Chip Land Grid Array,反转接点栅格阵列)FC-PGA(Flip-Chip Pin Grid Array,反转芯片针脚栅格阵列)FDIV(Floationg Point Divide,浮点除)FEMMS:Fast Entry/Exit Multimedia State,快速进入/退出多媒体状态FFT(fast Fourier transform,快速热欧姆转换)FGM(Fine-Grained Multithreading,高级多线程)FID(FID:Frequency identify,频率鉴别号码)FIFO(First Input First Output,先入先出队列)FISC(Fast Instruction Set Computer,快速指令集计算机)flip-chip(芯片反转)FLOPs(Floating Point Operations Per Second,浮点操作/秒)FMT(fine-grained multithreading,纯消除多线程)FMUL(Floationg Point Multiplication,浮点乘)FPRs(floating-point registers,浮点寄存器)FPU(Float Point Unit,浮点运算单元)FSUB(Floationg Point Subtraction,浮点减)GFD(Gold finger Device,金手指超频设备)GHC(Global History Counter,通用历史计数器)GTL(Gunning Transceiver Logic,射电收发逻辑电路)GVPP(Generic Visual Perception Processor,常规视觉处理器)HL-PBGA: 表面黏著,高耐热、轻薄型塑胶球状网阵封装HTT(Hyper-Threading Technology,超级线程技术)Hz(hertz,赫兹,频率单位)IA(Intel Architecture,英特尔架构)IAA(Intel Application Accelerator,英特尔应用程序加速器)ICU(Instruction Control Unit,指令控制单元)ID(identify,鉴别号码)IDF(Intel Developer Forum,英特尔开发者论坛)IEU(Integer Execution Units,整数执行单元)IHS(Integrated Heat Spreader,完整热量扩展)ILP(Instruction Level Parallelism,指令级平行运算)IMM: Intel Mobile Module, 英特尔移动模块Instructions Cache,指令缓存Instruction Coloring(指令分类)IOPs(Integer Operations Per Second,整数操作/秒)IPC(Instructions Per Clock Cycle,指令/时钟周期)ISA(instruction set architecture,指令集架构)ISD(inbuilt speed-throttling device,内藏速度控制设备)ITC(Instruction Trace Cache,指令追踪缓存)ITRS(International Technology Roadmap for Semiconductors,国际半导体技术发展蓝图)KNI(Katmai New Instructions,Katmai新指令集,即SSE)Latency(潜伏期)LDT(Lightning Data Transport,闪电数据传输总线)LFU(Legacy Function Unit,传统功能单元)LGA(land grid array,接点栅格阵列)LN2(Liquid Nitrogen,液氮)Local Interconnect(局域互连)MAC(multiply-accumulate,累积乘法)mBGA (Micro Ball Grid Array,微型球状网阵排列)nm(namometer,十亿分之一米/毫微米)MCA(machine check architecture,机器检查体系)MCU(Micro-Controller Unit,微控制器单元)MCT(Memory Controller,内存控制器)MESI(Modified, Exclusive, Shared, Invalid:修改、排除、共享、废弃)MF(MicroOps Fusion,微指令合并)mm(micron metric,微米)MMX(MultiMedia Extensions,多媒体扩展指令集)MMU(Multimedia Unit,多媒体单元)MMU(Memory Management Unit,内存管理单元)MN(model numbers,型号数字)MFLOPS(Million Floationg Point/Second,每秒百万个浮点操作)MHz(megahertz,兆赫)mil(PCB 或晶片布局的长度单位,1 mil = 千分之一英寸)MIPS(Million Instruction Per Second,百万条指令/秒)MOESI(Modified, Owned, Exclusive, Shared or Invalid,修改、自有、排除、共享或无效)MOF(Micro Ops Fusion,微操作熔合)Mops(Million Operations Per Second,百万次操作/秒)MP(Multi-Processing,多重处理器架构)MPF(Micro processor Forum,微处理器论坛)MPU(Microprocessor Unit,微处理器)MPS(MultiProcessor Specification,多重处理器规范)MSRs(Model-Specific Registers,特别模块寄存器)MSV(Multiprocessor Specification Version,多处理器规范版本)NAOC(no-account OverClock,无效超频)NI(Non-Intel,非英特尔)NOP(no operation,非操作指令)NRE(Non-Recurring Engineering charge,非重复性工程费用)OBGA(Organic Ball Grid Arral,有机球状网阵排列)OCPL(Off Center Parting Line,远离中心部分线队列)OLGA(Organic Land Grid Array,有机平面网阵包装)OoO(Out of Order,乱序执行)OPC(Optical Proximity Correction,光学临近修正)OPGA(Organic Pin Grid Array,有机塑料针型栅格阵列)OPN(Ordering Part Number,分类零件号码)PAT(Performance Acceleration Technology,性能加速技术)PBGA(Plastic Pin Ball Grid Array,塑胶球状网阵排列)PDIP (Plastic Dual-In-Line,塑料双重直线)PDP(Parallel Data Processing,并行数据处理)PGA(Pin-Grid Array,引脚网格阵列),耗电大PLCC (Plastic Leaded Chip Carriers,塑料行间芯片运载)Post-RISC(加速RISC,或后RISC)PR(Performance Rate,性能比率)PIB(Processor In a Box,盒装处理器)PM(Pseudo-Multithreading,假多线程)PPGA(Plastic Pin Grid Array,塑胶针状网阵封装)PQFP(Plastic Quad Flat Package,塑料方块平面封装)PSN(Processor Serial numbers,处理器序列号)QFP(Quad Flat Package,方块平面封装)QSPS(Quick Start Power State,快速启动能源状态)RAS(Return Address Stack,返回地址堆栈)RAW(Read after Write,写后读)REE(Rapid Execution Engine,快速执行引擎)Register Contention(抢占寄存器)Register Pressure(寄存器不足)Register Renaming(寄存器重命名)Remark(芯片频率重标识)Resource contention(资源冲突)Retirement(指令引退)RISC(Reduced Instruction Set Computing,精简指令集计算机)ROB(Re-Order Buffer,重排序缓冲区)RSE(register stack engine,寄存器堆栈引擎)RTL(Register Transfer Level,暂存器转换层。

PHOENIX BIOS参数设置

PHOENIX BIOS参数设置一、基本设置(Main)近日很多朋友问,怎么设置光驱启动,总是说的不太明白,所以就用图解说下,直观点,BIOS有三种,AWORD、AMI、PHOENIX这里先介绍PHOENIX。

按F2进入PHOENIXBIOS设置,就会出现如下界面,system time 设置时间格式为(时,分,秒)SYTEM DATA 设置日期LEGACY DISKETEE A:/B: 设置软驱PRIMARY MASTER/SLAVE 设置IDE1设置SECONDARY MASTER/SLAVE 设置IDE2设置keyboard-features 键盘特征,打开后出现下面界面numlock 小键盘灯keyboard auto repeat rate 键盘自动重复时间keyboard auto repeat delay 键盘自动重复延迟时间SYSTEM MENORY 系统内存EXTENDED MEMORY 扩展内存BOOT-time diagnostic screnn 启动时间诊断屏幕二、高级设置(Advanced)(一)Multiprocessor Specification 多重处理器规范 1.4 /1.1它专用于多处理器主板,用于确定MPS的版本,以便让PC制造商构建基于英特尔架构的多处理器系统。

与1.1标准相比,1.4增加了扩展型结构表,可用于多重PCI总线,并且对未来的升级十分有利。

另外,v1.4拥有第二条PCI总线,还无须PCI桥连接。

新型的SOS(Server Operating Systems,服务器操作系统)大都支持1.4标准,包括WinNTt和Linux SMP(Symmetric Multi-Processing,对称式多重处理架构)。

如果可以的话,尽量使用1.4。

(二)Installed o/s 安装O/S模式有IN95和OTHER两个值。

(三)Reset Configuration Data 重设配置数据,有YES和NO两个值。

A Scalable Approach to Thread-Level Speculation