编译内核Makefile时 混和的隐含和普通规则。停止

linux makefile编写规则

linux makefile编写规则(原创实用版)目录一、Makefile 简介二、Makefile 的规则1.目标文件2.依赖文件3.命令三、Makefile 中的变量1.通用变量2.局部变量四、Makefile 中的路径1.源文件路径2.目标文件路径3.库文件路径五、Makefile 编写实例六、总结正文一、Makefile 简介Makefile 是一个用于自动化构建和编译软件的脚本文件,通常在Linux 系统中使用。

它可以帮助开发者管理源代码,以及确定哪些文件需要编译,如何编译,以及编译后的文件如何链接。

通过编写 Makefile,开发者可以轻松地构建和维护复杂的软件项目。

Makefile 主要包括三类规则:目标文件、依赖文件和命令。

1.目标文件目标文件是 Makefile 中要生成的文件,可以是对象文件、库文件或执行文件。

在 Makefile 中,目标文件通常以“target”关键字开头,后面跟要生成的文件名。

例如:“target = main.o”。

2.依赖文件依赖文件是 Makefile 中要生成目标文件所需要的其他文件,通常是源代码文件。

在 Makefile 中,依赖文件通常以“prerequisites”关键字开头,后面跟要依赖的文件名。

例如:“prerequisites = a.c b.c”。

3.命令命令是用来生成目标文件的命令,通常是编译器或链接器。

在Makefile 中,命令通常以“command”关键字开头,后面跟要执行的命令。

例如:“command = gcc -o main.o a.c b.c”。

三、Makefile 中的变量Makefile 中的变量可以用于存储常量值,以便在 Makefile 中多次使用。

变量分为通用变量和局部变量。

1.通用变量通用变量是在整个 Makefile 中都可以使用的变量。

通用变量通常在Makefile 的开头定义,使用“define”关键字。

c语言makefile编写规则(一)

c语言makefile编写规则(一)C语言Makefile编写规则1. Makefile介绍Makefile是一种文件,其中包含了一组规则(rules)用于编译和构建项目。

它的作用是告诉系统如何编译代码,生成可执行文件。

2. Makefile规则基本结构Makefile规则由以下几部分组成:目标(Target)目标是一个文件,可以是源代码文件、中间文件或最终生成的可执行文件。

依赖(Dependencies)依赖指的是生成目标所需要的文件或其他目标。

当某个依赖文件发生变化时,目标就需要重新生成。

命令(Commands)命令是指执行编译、链接等操作的具体命令。

当目标需要重新生成时,Makefile会执行相应的命令。

规则示例以下是一个简单的示例,展示了一个C语言源文件的编译过程:target: dependenciescommand其中, - target表示目标文件; - dependencies表示生成目标所需要的文件或其他目标; - command表示具体的编译命令。

例如,假设有一个名为`的C语言源文件,我们想要生成一个名为hello`的可执行文件。

那么对应的Makefile规则可以定义如下:hello:gcc -o hello3. Makefile变量Makefile中还可以定义变量,以提高代码的可读性和重用性。

变量可以存储命令、文件名、路径等信息。

变量定义变量的定义采用变量名 = 值的方式进行,例如:CC = gcc其中,CC是变量名,gcc是变量的值。

变量引用使用变量时,需要在变量名前加$符号进行引用。

例如,使用上述定义的CC变量可以这样写:$(CC) -o hello4. Makefile示例以下是一个完整的Makefile示例,展示了多个目标之间的依赖关系和命令定义:CC = gccall: hellohello:$(CC) -o hello:$(CC) -cclean:rm -f hello在上述示例中,共定义了3个目标:all、hello和。

makefile文件的显示规则

makefile文件的显示规则Makefile文件是用于构建和管理软件项目的工具,它定义了一系列规则,用来指导如何编译、链接和安装软件。

在本文中,我们将详细介绍Makefile文件中的显示规则。

一、目标规则(T arget Rule)目标规则是Makefile中最常见的一种规则,它用来指定如何生成一个目标文件。

一个目标规则由目标、依赖和命令组成。

目标是我们要生成的文件,依赖是生成目标文件所需要的其他文件,而命令则是生成目标文件的具体步骤。

例如,我们可以定义一个目标规则来生成一个名为"hello"的可执行文件:```hello: main.o func.ogcc -o hello main.o func.o```在这个例子中,"hello"是目标文件,"main.o"和"func.o"是依赖文件,而命令"gcc -o hello main.o func.o"则是生成目标文件的具体步骤。

二、伪目标规则(Phony T arget Rule)伪目标规则用来指定一些特殊的目标,它们并不是真正的文件,而是一些需要执行的命令。

伪目标规则的目标名前面通常会加上一个"phony"修饰符,以便与真正的文件区分开来。

例如,我们可以定义一个伪目标规则来清理编译生成的文件:```.PHONY: cleanclean:rm -f hello *.o```在这个例子中,".PHONY"表示这是一个伪目标规则,"clean"是目标名,而命令"rm -f hello *.o"则是清理编译生成的文件的具体步骤。

三、模式规则(Pattern Rule)模式规则是一种更加抽象的规则,它可以匹配多个目标文件。

模式规则使用通配符来表示目标和依赖中的文件名模式,并使用"%"来表示匹配的部分。

makefile的模式规则

Makefile中的模式规则是一种特殊的规则,它允许你使用模式来匹配目标文件,然后根据匹配结果执行相应的命令。

模式规则中的目标文件名包含一个模式字符“%”,该字符可以匹配任何非空字符串。

在模式规则中,目标文件是一个带有模式字符“%”的文件,使用模式来匹配目标文件。

一旦依赖目标中的“%”模式被确定,make 会被要求去匹配当前目录下所有的文件名,一旦找到,make就会执行规则下的命令。

在模式规则中,目标可能会是多个的,如果有模式匹配出多个目标,make就会产生所有的模式目标。

此时,make关心的是依赖的文件名和生成目标的命令这两件事。

以下是一个简单的Makefile模式规则示例:

```makefile

%.o : %.c

$(CC) -c $(CFLAGS) $(CPPFLAGS) $< -o $@

```

这个规则表示将所有的.c文件编译成.o文件。

其中,“$<”表示了所有依赖目标的挨个值,“$@”表示了所有目标的挨个值。

这些自动化变量将在后面的章节中详细讲述。

总的来说,Makefile的模式规则是一种强大的工具,它可以根据文件名模式自动构建目标文件,并执行相应的命令。

makefile编译流程

makefile编译流程Makefile是一种用于自动化编译的工具,它可以根据源代码文件的依赖关系自动编译出目标文件。

Makefile的编写需要遵循一定的规则和语法,下面将介绍Makefile的编译流程。

1. 编写Makefile文件Makefile文件是一个文本文件,其中包含了编译的规则和依赖关系。

在编写Makefile文件时,需要遵循一定的语法规则,如使用TAB键缩进、使用变量和函数等。

2. 执行make命令在Makefile文件所在的目录下执行make命令,make会自动读取Makefile文件,并根据其中的规则和依赖关系进行编译。

如果Makefile文件中没有指定目标,则默认编译第一个目标。

3. 分析依赖关系在执行make命令时,make会先分析Makefile文件中的依赖关系,确定哪些文件需要重新编译。

如果某个源文件被修改了,那么与之相关的目标文件也需要重新编译。

4. 编译源文件在确定需要重新编译的文件后,make会依次编译每个源文件,生成对应的目标文件。

编译过程中,make会根据Makefile文件中的规则和命令进行编译。

5. 链接目标文件在所有的源文件都编译完成后,make会将所有的目标文件链接起来,生成最终的可执行文件。

链接过程中,make会根据Makefile文件中的规则和命令进行链接。

6. 完成编译当所有的源文件都编译完成并链接成功后,make会输出编译成功的信息,并生成最终的可执行文件。

如果编译过程中出现错误,make会输出错误信息并停止编译。

总之,Makefile编译流程是一个自动化的过程,它可以大大提高编译的效率和准确性。

在编写Makefile文件时,需要注意语法规则和依赖关系,以确保编译过程的正确性。

makefile文件语法规则

makefile文件语法规则Makefile文件的基本语法规则包括以下几点:1. 注释:以井号(#)开头的行被视为注释,不会被执行。

2. 规则:每条规则由一个目标文件和一组依赖文件组成,以及一个用于构建目标文件的命令。

规则的格式如下:Css:目标文件:依赖文件命令目标文件和依赖文件之间用冒号(:)分隔,命令部分指定了如何从依赖文件生成目标文件。

3. 变量:Makefile中可以使用变量来存储值,变量的值可以包含文本、空格、数字等。

变量名以美元符号($)开头,例如:Makefile:VAR = value命令= $VAR4. 函数:Makefile支持使用函数来执行更复杂的操作。

函数的语法如下:Scss:函数名(参数)Makefile中内置了一些常用的函数,如字符串操作函数、条件判断函数等。

也可以自定义函数。

5. 通配符:Makefile中可以使用通配符来匹配多个文件,常见的通配符有“*”和“?”。

例如,“*.c”表示匹配所有以“.c”结尾的文件,“a?b”表示匹配“ab”、“axb”、“ayb”等字符串。

6. 回声:在Makefile中,命令前面加上“@”符号可以关闭回声,即不会在执行命令时显示该命令。

例如:Makefile:@echo Hello, world!这条命令执行时不会输出“Hello, world!”的文本。

7. 模式规则:Makefile中的模式规则允许根据一组通配符匹配的文件来定义规则,格式如下:Makefile:模式:目标文件命令1命令2模式匹配的文件将按照指定的命令构建目标文件。

c语言makefile编写规则

c语言makefile编写规则C语言Makefile编写规则什么是MakefileMakefile是一种用于管理和构建软件项目的文件,通常被用于编译和链接C语言程序。

Makefile中包含了一系列的规则和指令,用于告诉编译器如何编译程序中的各个部分,并最终生成可执行文件。

Makefile的基本结构Makefile的基本结构由多个规则组成,每个规则由一个目标(target)和一个或多个依赖(dependencies)组成。

目标指明了要生成的文件或要执行的操作,依赖指明了目标所依赖的文件或操作。

一个简单的Makefile规则的语法如下:target: dependenciescommand其中,target是生成的文件或要执行的操作,dependencies是目标所依赖的文件或操作,command是执行的命令。

每个规则的命令必须以一个tab键开始。

Makefile的应用场景Makefile广泛应用于C语言项目的构建中,它可以自动化执行编译、链接和清理等操作。

通过Makefile,我们可以方便地管理源代码文件、头文件和库文件之间的关系,从而提高项目的可维护性和可扩展性。

Makefile的编写规则1.目标和依赖应该使用合适的命名方式,能够清晰地表达其作用以及所依赖的内容。

避免使用中文、空格和特殊字符,使用下划线和英文字母进行命名。

2.命令行命令应该以tab键开始,而不是空格。

这是Makefile的语法要求,且使用tab键可以提高代码的可读性。

3.注意规则的顺序,确保前置依赖在目标之前。

Makefile会按照规则的声明顺序进行构建,如果前置依赖在目标之后,可能导致构建失败。

4.使用变量来定义重复使用的内容,如编译器选项、源文件列表等。

这样可以提高代码的可维护性,并方便进行后续的修改和维护。

5.使用通配符来表示一类文件,如使用*.c表示所有的C语言源文件,使用$(wildcard pattern)函数来获取符合某种模式的文件列表。

makefile规则

makefile规则makefile规则是指用于描述当make执行Makefile文件时,make 应该采取的动作。

makefile文件由一系列规则组成,并且每条规则都有由一个目标、零个或多个依赖条件和一系列可以对目标文件进行生成、删除和修改的指令构成。

1、静态模式规则:静态模式规则指明了在make执行规则的过程中,make会将特定的依赖关系用静态的模式规则处理。

通常使用固定长度的字符串来定义静态规则,并且字符串中可以包括多个模式,如“%.c”和“%.o”。

2、伪目标规则:伪目标规则可以用来定义一组目标,这些目标只有在其他目标依赖它们时才有可能被make执行。

例如,“clean”是一个伪目标,可以用来定义一组清理工作。

3、自动变量:自动变量是make文件规则中的特殊变量,可以使make更加聪明、更加灵活。

自动变量可以为make命令提供一些临时的信息,使make可以判断出依赖列表中目标的文件是什么,同时也可以为所有的目标提供一种标准的输出路径。

4、变量引用:变量引用是make中的一种重要特性,主要指的是在规则中可以使用一个或多个变量来引用其他变量。

变量引用可以让make在定义变量后不用继续修改makefile文件就能对变量进行操作。

5、函数式语法:函数式语法是make中的一种特殊语法,允许make在一个单独的语句中使用多行表达式。

函数式语法可以用来定义变量,从而减少代码冗余,提高makefile文件的可读性。

6、条件分支语句:条件分支语句是makefile文件中的一种语法,它使得make可以根据某些条件来执行特定的动作。

当make执行makefile文件时,如果if 条件判断成立,则会继续执行if中的语句;如果if条件不成立,则执行else中的语句。

7、包含语句:包含语句是makefile文件中的一种重要语法,它允许make从另一个makefile文件中读取规则并执行它们。

通过此种方式,用户可以将makefile文件划分成多个文件,例如一个文件定义编译目标,另一个文件定义安装规则等,从而使makefile文件更加简洁。

Makefile的隐含规则

Makefile 隱含規則在我們使用Makefile 時,有一些我們會經常使用,而且使用頻率非常高的東西,比如,我們編譯C/C++的來源程式為中間目的檔案(Unix下是[.o]文件,Win dows 下是[.obj]文件)。

本章講述的就是一些在Makefile中的—隱含的II早先約定了的,不需要我們再寫出來的規則。

—隱含規則也就是一種慣例,make會按照這種—慣例心照不喧地來運行,那怕我們的Makefile中沒有書寫這樣的規則。

例如,把[.c]檔編譯成[.o]檔這一規則, 你根本就不用寫出來,make會自動推導出這種規則,並生成我們需要的[.o]文件—隱含規則I會使用一些我們系統變數,我們可以改變這些系統變數的值來定制隱含規則的運行時的參數。

如系統變數一CFLAGS可以控制編譯時的編譯器參數。

我們還可以通過我式規則I的方式寫下自己的隱含規則。

用—尾碼規則來定義隱含規則會有許多的限制。

使用—模式規則I會更回得智慧和清楚,但—尾碼規則可以用來保證我們Makefile 的相容性。

我們瞭解了―隱含規則I,可以讓其為我們更好的服務,也會讓我們知道一些—勺定俗成了的東西,而不至於使得我們在運行Makefile時出現一些我們覺得莫名其妙的東西。

當然,任何事物都是矛盾的,水能載舟,亦可覆舟,所以,有時候—隱含規則I 也會給我們造成不小的麻煩。

只有瞭解了它,我們才能更好地使用它。

、使用隱含規則如果要使用隱含規則生成你需要的目標,你所需要做的就是不要寫出這個目標的規則。

那麼,make 會詴圖去自動推導產生這個目標的規則和命令,如果make 可以自動推導生成這個目標的規則和命令,那麼這個行為就是隱含規則的自動推導。

當然,隱含規則是make事先約定好的一些東西。

例如,我們有下面的一個Makefile :foo : foo.o bar.occ p foo foo.o bar.o $(CFLAGS) $(LDFLAGS)我們可以注意到,這個Makefile中並沒有寫下如何生成foo.o和bar.o這兩目標的規則和命令。

makefile编译规则

makefile编译规则Makefile编译规则一、引言在软件开发过程中,编译是将源代码转化为可执行文件或者库文件的重要步骤。

为了简化编译过程,提高开发效率,我们可以使用Makefile来管理和自动化编译过程。

Makefile是一个文本文件,其中包含一系列的规则,用于描述源文件之间的依赖关系和编译操作。

二、Makefile基本语法1. 目标(T arget)Makefile中的目标是指我们希望生成的文件,可以是可执行文件、库文件或者中间文件等。

目标一般以文件名表示,可以包含路径信息。

2. 依赖(Prerequisites)依赖是指目标生成所依赖的文件或者其他目标。

当依赖文件发生变化时,Make会自动重新编译相关的目标。

3. 规则(Rule)规则是Makefile中最重要的部分,用于描述目标和依赖之间的关系,以及如何生成目标文件。

规则的基本语法如下:```target: prerequisitescommand```其中,target表示目标文件,prerequisites表示依赖文件或者其他目标,command表示生成目标文件的命令。

4. 变量(Variable)Makefile中的变量用于存储和传递数据,可以是字符串、路径、命令等。

变量的定义使用“=”或者“:=”,例如:```CC = gccCFLAGS = -Wall -O2```变量的使用使用“$”符号,例如:```$(CC) $(CFLAGS) -o target source.c```5. 通配符(Wildcard)通配符可以帮助我们查找符合某种模式的文件,常用的通配符包括“*”和“?”。

例如,我们可以使用以下命令查找所有的.c文件:```sources = $(wildcard *.c)```6. 函数(Function)函数是Makefile中的一个重要概念,可以帮助我们处理字符串、路径和文件等。

常用的函数包括:- $(patsubst pattern,replacement,text):将文本中符合模式pattern的部分替换为replacement;- $(shell command):执行shell命令,并返回结果;- $(dir names):返回文件路径部分;- $(notdir names):返回文件名部分;- $(basename names):返回文件名去除后缀部分;- $(suffix names):返回文件后缀部分。

makefile规则

makefile规则

makefile规则是编写makefile文件时必须遵守的规则。

makefile文件是为了帮助程序员自动化编译和构建程序而创建的文件。

makefile文件包含了一系列规则,这些规则指定了程序的依赖关系和编译链接的过程。

这些规则可以分为四个部分:目标、依赖、命令和变量。

目标是makefile文件中最重要的部分,它指定了需要编译的文件或程序。

每个目标都需要指定其依赖关系和相关的命令。

依赖是指目标所依赖的文件或程序。

如果依赖文件发生了改变,那么相应的目标需要重新编译。

命令是执行编译、链接、安装等操作的具体命令。

变量是为了方便编写makefile文件而定义的变量,可以用于指定编译器、编译选项等。

在编写makefile文件时,应该遵守一些规则,以确保makefile 能够正确地工作。

这些规则包括:

1.每个规则必须以一个目标开始。

2.每个目标必须指定其依赖关系。

3.每个目标下必须包含至少一个命令。

4.命令必须以tab键开始。

5.变量必须使用$符号引用。

遵守这些规则可以帮助程序员编写出正确、可读性强的makefile 文件,从而有效地提高程序的编译和构建效率。

- 1 -。

makefile的规则和编写方法

makefile的规则和编写方法Makefile是一种文本文件,它包含了一系列规则和命令,用于描述源代码的编译和构建过程。

Makefile的规则和编写方法对于项目的管理和维护非常重要。

下面是关于Makefile规则和编写方法的一些要点:1. 目标(Targets):每个Makefile中都应该定义一个或多个目标。

目标通常代表项目中的某个文件、可执行程序或者一个任务。

在Makefile中,目标的名称应该在冒号(:)后面给出,并且每个目标都应该独占一行。

2. 依赖(Dependencies):在Makefile中,每个目标通常都会依赖于其他文件或目标。

依赖关系表示了一个文件或目标的生成所依赖的其他文件或目标。

依赖关系可以使用冒号(:)来表示,冒号前是目标名称,冒号后是该目标所依赖的文件或目标。

3. 命令(Commands):在Makefile中,每个目标都需要定义一个或多个命令,用于生成该目标所描述的文件或任务。

每个命令需要以制表符(Tab)开头,紧随其后的是具体的操作指令,如编译命令、链接命令等。

命令之间可以使用换行符进行分隔。

4. 变量(Variables):在Makefile中,可以使用变量来存储常用的数值、目录路径或者编译器选项等信息。

变量可以使用等号(=)或冒号等号(:=)进行赋值。

通过使用变量,可以大大简化Makefile的编写和维护过程。

5. 注释(Comments):注释用于解释Makefile中的规则和命令,以提高代码的可读性。

在Makefile 中,可以使用井号(#)表示注释,井号后的内容会被忽略。

编写一个简单的Makefile示例:```# 定义变量CC = gccCFLAGS = -Wall -O2# 定义目标和依赖关系myprogram: main.o func1.o func2.o$(CC) $(CFLAGS) -o myprogram main.o func1.o func2.o# 生成目标的命令main.o: main.c$(CC) $(CFLAGS) -c main.cfunc1.o: func1.c$(CC) $(CFLAGS) -c func1.cfunc2.o: func2.c$(CC) $(CFLAGS) -c func2.c# 清理目标文件的命令clean:rm -f *.o myprogram```以上是一个简单的Makefile示例。

Makefile的隐含规则

Makefile隱含規則————在我們使用Makefile時,有一些我們會經常使用,而且使用頻率非常高的東西,比如,我們編譯C/C++的來源程式為中間目的檔案(Unix下是[.o]文件,Windows 下是[.obj]文件)。

本章講述的就是一些在Makefile中的―隱含的‖,早先約定了的,不需要我們再寫出來的規則。

―隱含規則‖也就是一種慣例,make會按照這種―慣例‖心照不喧地來運行,那怕我們的Makefile中沒有書寫這樣的規則。

例如,把[.c]檔編譯成[.o]檔這一規則,你根本就不用寫出來,make會自動推導出這種規則,並生成我們需要的[.o]文件。

―隱含規則‖會使用一些我們系統變數,我們可以改變這些系統變數的值來定制隱含規則的運行時的參數。

如系統變數―CFLAGS‖可以控制編譯時的編譯器參數。

我們還可以通過―模式規則‖的方式寫下自己的隱含規則。

用―尾碼規則‖來定義隱含規則會有許多的限制。

使用―模式規則‖會更回得智慧和清楚,但―尾碼規則‖可以用來保證我們Makefile的相容性。

我們瞭解了―隱含規則‖,可以讓其為我們更好的服務,也會讓我們知道一些―約定俗成‖了的東西,而不至於使得我們在運行Makefile時出現一些我們覺得莫名其妙的東西。

當然,任何事物都是矛盾的,水能載舟,亦可覆舟,所以,有時候―隱含規則‖也會給我們造成不小的麻煩。

只有瞭解了它,我們才能更好地使用它。

一、使用隱含規則如果要使用隱含規則生成你需要的目標,你所需要做的就是不要寫出這個目標的規則。

那麼,make會詴圖去自動推導產生這個目標的規則和命令,如果make 可以自動推導生成這個目標的規則和命令,那麼這個行為就是隱含規則的自動推導。

當然,隱含規則是make事先約定好的一些東西。

例如,我們有下面的一個Makefile:foo : foo.o bar.occ –o foo foo.o bar.o $(CFLAGS) $(LDFLAGS)我們可以注意到,這個Makefile中並沒有寫下如何生成foo.o和bar.o這兩目標的規則和命令。

II. C语言本质_22Makefile基础_2 隐含规则和模式规则

第 22 章 Makefile 基础 2. 隐含规则和模式规则上一节的 Makefile 写得中规中矩,比较繁琐,是为了讲清楚基本概念,其实 Makefile 有很多灵活的写法,可以写得更简洁,同时减少出错的可能。

本节我们 来看看这样一个例子还有哪些改进的余地。

一个目标依赖的所有条件不一定非得写在一条规则中,也可以拆开写,例如:main.o: main.h stack.h maze.hmain.o: main.c gcc -c main.c就相当于:main.o: main.c main.h stack.h maze.h gcc -c main.c如果一个目标拆开写多条规则,其中只有一条规则允许有命令列表,其它规则应 该没有命令列表,否则 make 会报警告并且采用最后一条规则的命令列表。

这样我们的例子可以改写成:main: main.o stack.o maze.o gcc main.o stack.o maze.o -o mainmain.o: main.h stack.h maze.h stack.o: stack.h main.h maze.o: maze.h main.hmain.o: main.cgcc -c main.cstack.o: stack.c gcc -c stack.cmaze.o: maze.c gcc -c maze.cclean: -rm main *.o.PHONY: clean这不是比原来更繁琐了吗?现在可以把提出来的三条规则删去,写成:main: main.o stack.o maze.o gcc main.o stack.o maze.o -o mainmain.o: main.h stack.h maze.h stack.o: stack.h main.h maze.o: maze.h main.hclean: -rm main *.o.PHONY: clean这就比原来简单多了。

makefile 隐式规则

makefile 隐式规则Makefile是一种用于自动化构建程序的工具,它可以根据源代码文件的修改情况,自动地编译、链接和生成可执行文件。

Makefile中的隐式规则是指在没有明确指定规则的情况下,Makefile会自动根据文件的后缀名来推断编译规则。

在Makefile中,隐式规则的格式如下:```<目标文件>: <依赖文件><命令>```其中,目标文件是要生成的文件,依赖文件是生成目标文件所需要的文件,命令是生成目标文件的具体操作。

例如,我们要编译一个C语言程序,可以使用以下的隐式规则:```.c.o:gcc -c $< -o $@```这个规则的意思是,将所有的.c文件编译成.o文件,使用gcc编译器进行编译,$<表示依赖文件,$@表示目标文件。

另外,Makefile中还有一些内置的隐式规则,例如:- .c.o:将C语言源文件编译成目标文件- .cpp.o:将C++语言源文件编译成目标文件- .f.o:将Fortran语言源文件编译成目标文件- .y.c:将Yacc源文件生成C语言源文件- .l.c:将Lex源文件生成C语言源文件除了以上的内置规则外,我们还可以自定义隐式规则,例如:```.SUFFIXES: .txt .html.txt.html:pandoc $< -o $@```这个规则的意思是,将所有的.txt文件转换成.html文件,使用pandoc工具进行转换,$<表示依赖文件,$@表示目标文件。

总之,Makefile中的隐式规则可以大大简化编译过程,提高编译效率,是一个非常重要的功能。

在编写Makefile时,我们应该充分利用隐式规则,减少重复的代码,提高代码的可维护性和可读性。

makefile语法规则

makefile语法规则Makefile是一种文本文件,它用来定义一组规则来指明编译软件项目所需要完成的步骤。

它也是构建、编译以及安装一个软件项目必不可少的一部分。

Makefile可以帮助开发者,其中一项重要的原因是它可以在编译软件时降低开发者的工作量,使其能够更快更轻松地解决编译软件的问题。

Makefile语法规则可以分为两类:基本语法规则和特殊语法规则。

基本语法规则涉及Makefile文件中每行需要遵守的语法,而特殊语法规则涉及到Makefile中使用的自定义变量或函数。

下面将详细介绍这两类规则。

1.本语法规则基本语法规则是Makefile文件核心的部分,其定义了文件每一行的正确格式。

下面我们将介绍几条基本语法规则:a)Makefile文件中,每行以冒号开头的一行代表一条规则,并且冒号前面必须是一个有效的标识符,比如变量名或是函数名。

b) Makefile文件中,每行以Tab键开头的一行代表一个操作,这个操作会被执行以完成一个特定的任务c)有以#开头的行都会被忽略,因为它表示一行注释,用来解释Makefile语句的内容d)Makefile文件中,变量与函数的定义必须放在Makefile文件的开头,才能在 Makefile件内部使用它们e)一行末尾需要加上一个分号,这样才能表达出每条规则被终止的意思,以避免 Makefile现错误2.特殊语法规则特殊语法规则涉及到 Makefile件中使用的自定义变量或是函数。

该规则是用来控制 Makefile件中定义的任务如何被执行。

a)量:变量是一种使用字符来代表值的方法,变量使用美元符号($)来表示。

它可以被声明在 Makefile文件的开头,也可以在Makefile件的某一行中使用。

b)数:函数是一种在 Makefile件中独立运行的代码块,它可以接受参数,并且返回一个字符串或者一组字符串。

使用函数有助于提高 Makefile件的整体性和可维护性,并且可以多次使用,以减少重复的工作。

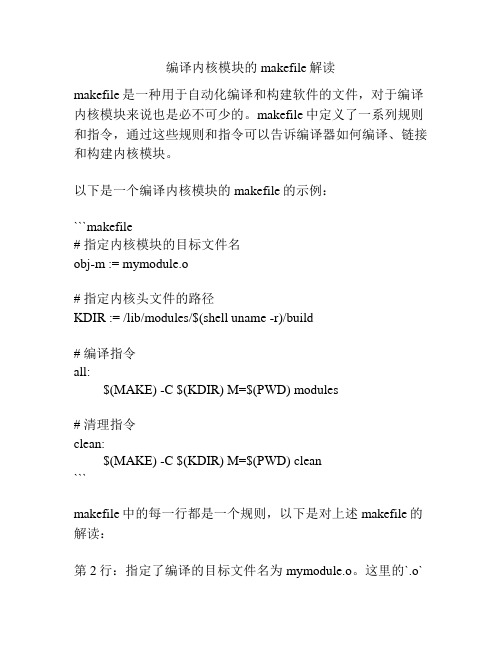

编译内核模块的makefile解读

编译内核模块的makefile解读makefile是一种用于自动化编译和构建软件的文件,对于编译内核模块来说也是必不可少的。

makefile中定义了一系列规则和指令,通过这些规则和指令可以告诉编译器如何编译、链接和构建内核模块。

以下是一个编译内核模块的makefile的示例:```makefile# 指定内核模块的目标文件名obj-m := mymodule.o# 指定内核头文件的路径KDIR := /lib/modules/$(shell uname -r)/build# 编译指令all:$(MAKE) -C $(KDIR) M=$(PWD) modules# 清理指令clean:$(MAKE) -C $(KDIR) M=$(PWD) clean```makefile中的每一行都是一个规则,以下是对上述makefile的解读:第2行:指定了编译的目标文件名为mymodule.o。

这里的`.o`表示编译生成的是一个目标文件。

第5行:指定了内核头文件的路径。

`/lib/modules/$(shell uname -r)/build`是内核源码所在的路径,`uname -r`是一个命令,用于获取当前操作系统的内核版本。

第8行:定义了一个名为`all`的目标,用于编译内核模块。

`$(MAKE)`表示执行`make`命令,`-C`选项用于指定编译的路径,`M=$(PWD)`指定了`KDIR`路径外的文件所在的路径,`modules`表示编译的目标是内核模块。

第11行:定义了一个名为`clean`的目标,用于清理编译生成的文件。

`clean`规则通常包括删除所有生成的文件、临时文件和中间文件等。

通过执行`make`命令,可以编译内核模块并生成目标文件。

执行`make clean`命令可以清理编译生成的文件。

在编译内核模块时,除了makefile之外,还需要注意以下几点:1. 确保系统中已经安装了所需的内核源码和开发工具。

makefile文件的显示规则

makefile文件的显示规则Makefile文件的显示规则Makefile是一种用于自动化编译和构建程序的文件,其中的显示规则定义了程序如何被编译、链接和安装。

下面将详细介绍Makefile 文件中的显示规则。

一、什么是Makefile文件Makefile文件是一种包含了一系列规则的文本文件,用于指导程序的编译和构建过程。

Makefile文件中的规则包括显示规则和隐式规则,其中显示规则指定了如何生成目标文件,而隐式规则则根据文件的扩展名自动推导出如何生成目标文件。

二、显示规则的语法和结构显示规则由目标、依赖和命令组成,其中目标是要生成的文件,依赖是生成目标文件所依赖的文件或规则,命令是生成目标文件的具体操作步骤。

显示规则的语法如下:```目标: 依赖命令```三、示例说明为了更好地理解和应用显示规则,下面以一个简单的C程序为例进行说明。

1. 创建一个名为hello.c的文件,内容如下:```c#include <stdio.h>int main() {printf("Hello, World!\n");return 0;}```2. 创建一个名为Makefile的文件,内容如下:```hello: hello.ogcc -o hello hello.ohello.o: hello.cgcc -c hello.c```在这个示例中,我们定义了两个显示规则。

第一个规则指定了目标文件hello的生成方式,它依赖于hello.o文件,并且执行gcc命令将hello.o文件链接生成可执行文件hello。

第二个规则指定了hello.o文件的生成方式,它依赖于hello.c文件,并且执行gcc命令将hello.c文件编译生成hello.o文件。

四、显示规则的使用注意事项在使用显示规则时,需要注意以下几点:1. 目标文件和依赖文件的命名应当与实际文件名保持一致,以确保规则的正确性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

编译时makefile:Makefile:1503: *** 混和的隐含和普通规则。

停止。

处理

(2012-05-05 16:45:32)

转载▼

1.makefile

#AR=ar

#ARCH=arm

#CC=arm-linux-gcc

obj-m := hello.o

#if we need more than one source code to build the module

#we should use the variable below: example: modules-objs := file1.o file2.o

#KDIR := /lib/modules/$(shell uname -r)/build

KDIR := /UP-Magic/kernel/linux-2.6.24.4

PWD := $(shell pwd)

default:

# $(MAKE) -C $(KDIR) M=$(PWD) modules

$(MAKE) -C $(KDIR) M=$(PWD) modules

clean:

rm -rf *.o *~ core .depend .*.cmd *.ko *.mod.c .tmp_versions *.order *.symvers make时出现;

[root@hpx driverPractise]# make

make -C /UP-Magic/kernel/linux-2.6.24.4 M=/bochuang/driverPractise modules make[1]: 进入目录“/UP-Magic/kernel/linux-2.6.24.4”

Makefile:1503: *** 混和的隐含和普通规则。

停止。

make[1]: 离开目录“/UP-Magic/kernel/linux-2.6.24.4”

make: *** [default] 错误 2

搜索一下,有人解决了,转载过来:

在编译 kernel 时,有机会碰见下面的错误:

Makefile: *** 混合的隐含和普通规则。

停止。

Makefile: *** mixed implicit and normal rules. Stop.

这个原因可能是Make工具对低版本内核的Makefile一些旧的规则兼容不好,我们只需要修改对应的Makefile。

如一:

原始的:

大概在1503行 / %/: prepare scripts FORCE

$(Q)$(MAKE) KBUILD_MODULES=$(if $(CONFIG_MODULES),1)

$(build)=$(build-dir)

修改后:

/: prepare scripts FORCE

$(Q)$(MAKE) KBUILD_MODULES=$(if $(CONFIG_MODULES),1)

$(build)=$(build-dir)

%/: prepare scripts FORCE

$(Q)$(MAKE) KBUILD_MODULES=$(if $(CONFIG_MODULES),1)

$(build)=$(build-dir)

如二:

原始的:

大概在 435行: config %config: scripts_basic outputmakefile FORCE $(Q)mkdir -p include/linux include/config

$(Q)$(MAKE) $(build)=scripts/kconfig $@

修改后:

config: scripts_basic outputmakefile FORCE

$(Q)mkdir -p include/linux include/config

$(Q)$(MAKE) $(build)=scripts/kconfig $@

%config: scripts_basic outputmakefile FORCE

$(Q)mkdir -p include/linux include/config

$(Q)$(MAKE) $(build)=scripts/kconfig $@

解决。