LP4EE1PBABB;中文规格书,Datasheet资料

深圳市中美通用有限公司LiFePO4电池组规格书说明书

Li FePO4 Battery Pack Specification 磷酸铁锂电池组规格书MODEL/型号: IFR26650-12.8V30AHSN: GEB IFR26650 4S8PPrepared By/Date 编制/日期Checked By/Date审核/日期Approved By/Date批准/日期21/09/04 张平21/09/04程建波21/09/04周腾飞Customer Approval 客户批准Signature确认Date日期Company Name:公司名称:Company Stamp:客户印章:--- 保密文件 ---Amendment Records (修正记录)Edition (版本)Description(记述)Prepared by(编制)Approved by(批准)Date(日期)A0 First Edition 2022-11-041.Scope(适用范围)This specification is applied to the reference battery in this Specification that manufactured by General Electronics Technology Co., Ltd.本说明书适用于本书中所提及的深圳市中美通用科技有限公司制造的电池。

2.Adopted Standard(引用标准)National Standard CQC1126-2017 “technical specification for lithium-ion battery pack used in solar street lamps” of CQC.中国质量认证中心CQC1126-2017《太阳能路灯用锂离子电池组技术规范》。

3.Product Specification(产品技术规格)Table 1 (表1)No.(序号) Item(项目)Parameter(参数) Remark(备注)1 Nominal Voltage(标称电压)12.8V单节3.2V2 Rated Capacity(额定容量)Typical(标称容量)31000mAh Standard discharge(0.3C) afterStandard charge(0.2C)(0.2C标准充电后0.3C标准放电)Minimum(最小容量)30000mAh3 Charging Voltage(充电电压) 14.6V4 Charging Mode(充电方式)C.C/C.V.(恒流/恒压方式)Constant Current/Constant Voltage(恒流/恒压)5 Voltage at end ofDischarge(放电终止电压)10V Discharge Cut-off Voltage(放电截止电压)6 Rated Charge Current(额定充电电流)≤6ACharging Current 6A(充电电流6A)7 Maximum ContinuousCharge Current(最大持续充电电流)≤10ANot more then 1 hours(不超过1小时)8 Internal Impedance(内阻)<130mΩ9 Rated Discharge Current(额定放电电流)≤8ADischarging Current 8A(放电电流8A)10 Maximum ContinuousDischarge Current(最大持续放电电流)≤10ANot more then 1 hours(不超过1小时)11 Overcharge Voltage(过充电保护电压)3.65±0.025V /Cell(可调)Single string voltage(单串电压)12 Over Discharge Cut OffVoltage(过放电保护电压)2.5±0.08V /Cell(可调)Single string voltage(单串电压)Continuous the table 1 (续表1)13 Over Current(过流保护)60±5A(瞬间最大过流保护)5ms—30ms14 Short Circuit(短路保护)Detection condition(保护条件)Exterior short circuit(外部电路短路)Release condition(保护解除条件)Cut short circuit(断开短路电路)15 Operating ConsumptionCurrent of PCB(保护板工作消耗电流)≤30μASingle string of cell(单串电池)16 Cell balance Current(均衡电流)50±5mA17 Bleed Start Point(均衡开启电压)3.60±0.025V18 BMS Size(保护板尺寸)56*48*8mm19 Operation TemperatureRange(工作温度范围)Charge(充电): -20~60℃60±25%R.H.Bare Cell(电池储存湿度范围)Discharge(放电): -20~60℃20 Storage TemperatureRange(储存温度范围)Less than 1 year: -20~25℃(小于一年:-20~25℃)60±25%R.H.at the shipment state(出货状态时的湿度范围)less than 3 months: -20~40℃(小于3个月:-20~40℃)Less than 7 day : -20~65℃(小于7天:-20~65℃)21 The battery packDimension(电池组尺寸)Length/长度:220±3MMInitial Dimension(初始尺寸)Width/宽度: 110±3MMHigh/高度:70±3MM22 Cells(电芯)IFR26650 3.2V 4000m A h Li FePO4(磷酸铁锂)23 Connection Type(组合方式)4S8P(4串8并)Cells Without Plastic Bracket(内部不带电芯支架)24 Weight(重量)≤2.9Kg25 Waterproof grade(防水等级)/26Cycle Life(循环寿命)Carry Out 2000 cycle(循环2000次)Higher than 80% of the InitialCapacities of the Cells(剩余电量大于初始容量的80%)3.Performance And Test Conditions (电池性能及测试条件)3.1 Standard Test Conditions(标准测试条件)Test should be conducted with new batteries within one week after shipment from our factory and the cells shall not be cycled more than five times before the test. Unless otherwise specified, test and measurement shall be done under temperature of 23±3℃and relative humidity of 45~85%. If it is judged that the test results are not affected by such conditions, the tests may be conducted at temperature 15~30℃and humidity 25~85%RH.测试必须使用出厂时间不超过一个星期的新电池,且未进行过五次以上的充放电循环。

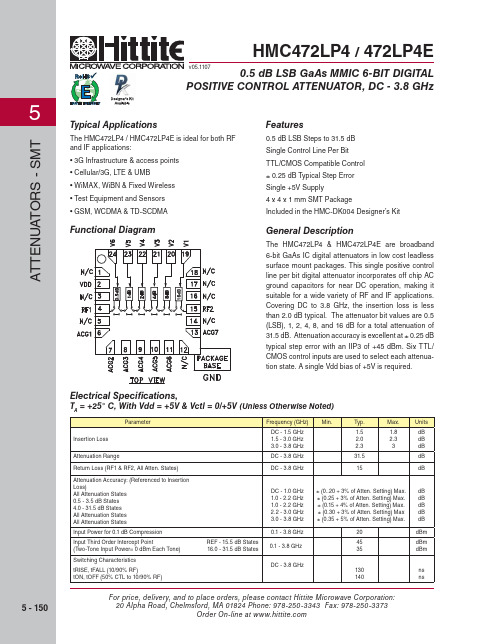

HMC472LP4E中文资料

-2

-2.5

-3 0 0.5 1 1.5 2 2.5 3 3.5 4

FREQUENCY (GHz)

For price, delivery, and to place orders, please contact Hittite Microwave Corporation: 20 Alpha Road, Chelmsford, MA 01824 Phone: 978-250-3343 Fax: 978-250-3373 Order On-line at

Features

The HMC472LP4 / HMC472LP4E is ideal for both RF and IF applications: • 3G Infrastructure & access points • Cellular/3G, LTE & UMB • WiMAX, WiBN & Fixed Wireless • Test Equipment and Sensors • GSM, WCDMA & TD-SCDMA

State Low High Note: Vdd = +5V

Bias Condition 0 to +0.8 Vdc @ -5 uA Typ. + 2.0 to + 5.0 Vdc @ 40 uA Typ.

Truth Table

V1 16 dB

Control Voltage Input

V2 8 dB

5

Relative Phase vs. Frequency

(Only Major States are Shown)

100

80

60

40

31.5 dB

IRGP4086PBF;中文规格书,Datasheet资料

tf

Fall time

td(on)

Turn-On delay time

tr

Rise time

— 65 —

— 30 —

IC = 25A, VCC = 196V

— 33 — ns RG = 10Ω, L=200μH, LS= 200nH

td(off) tf tst

EPULSE

Turn-Off delay time Fall time Shoot Through Blocking Time

2

/

240

VGE = 18V

200

VGE = 15V

VGE = 12V

160

VGE = 10V VGE = 8.0V

120

VGE = 6.0V

ICE (A)

80

40

0

0

4

8

12

16

VCE (V)

Fig 1. Typical Output Characteristics @ 25°C

––– 29 ––– ––– 65 ––– ––– 22 ––– — 36 — — 31 — — 112 —

S VCE = 25V, ICE = 25A nC VCE = 200V, IC = 25A, VGE = 15Ve

IC = 25A, VCC = 196V ns RG = 10Ω, L=200μH, LS= 200nH

Parameter Thermal Resistance Junction-to-Case-(each IGBT) d Case-to-Sink (flat, greased surface) Junction-to-Ambient (typical socket mount) d Weight

IRFZ44NPBF;中文规格书,Datasheet资料

IRFZ44NPbFHEXFET ® Power MOSFET09/21/10ParameterTyp.Max.UnitsR θJC Junction-to-Case––– 1.5R θCS Case-to-Sink, Flat, Greased Surface 0.50–––°C/WR θJAJunction-to-Ambient–––62Thermal Resistance 1TO-220ABAdvanced HEXFET ®to its wide acceptance throughout the industry.l Advanced Process Technology l Ultra Low On-Resistance l Dynamic dv/dt Ratingl 175°C Operating Temperature l Fast Switchingl Fully Avalanche Rated lLead-FreeDescriptionAbsolute Maximum RatingsParameterMax.UnitsI D @ T C = 25°C Continuous Drain Current, V GS @ 10V 49I D @ T C = 100°C Continuous Drain Current, V GS @ 10V 35A I DMPulsed Drain Current 160P D @T C = 25°C Power Dissipation 94W Linear Derating Factor 0.63W/°C V GS Gate-to-Source Voltage ± 20V I AR Avalanche Current25A E AR Repetitive Avalanche Energy 9.4mJ dv/dt Peak Diode Recovery dv/dt 5.0V/ns T J Operating Junction and-55 to + 175T STGStorage Temperature RangeSoldering Temperature, for 10 seconds 300 (1.6mm from case )°CMounting torque, 6-32 or M3 srew10 lbf•in (1.1N•m)PD - 94787BIRFZ44NPbFSource-Drain Ratings and CharacteristicsStarting T J = 25°C, L = 0.48mHR G = 25Ω, I AS = 25A. (See Figure 12)Repetitive rating; pulse width limited by max. junction temperature. (See fig. 11)Notes:I SD ≤ 25A , di/d t ≤ 230A/µs, V DD ≤ V (BR)DSS ,T J ≤ 175°CPulse width ≤ 400µs; duty cycle ≤ 2%.This is a typical value at device destruction and represents operation outside rated limits.This is a calculated value limited to T J = 175°C .Electrical Characteristics @ T J = 25°C (unless otherwise specified)IRFZ44NPbF 3Vs. TemperatureIRFZ44NPbFFig 8. Maximum Safe Operating AreaGate-to-Source VoltageDrain-to-Source VoltageForward Voltage110100V DS , Drain-toSource Voltage (V)0.11101001000I D , D r a i n -t o -S o u r c e C u r r e n t (A )IRFZ44NPbF 5Case TemperatureV V d(on)rd(off)fV DDFig 10a. Switching Time Test CircuitFig 10b. Switching Time WaveformsIRFZ44NPbF6VDSCurrent Sampling ResistorsV GSFig 13b. Gate Charge Test CircuitFig 13a. Basic Gate Charge Waveform Fig 12b. Unclamped Inductive WaveformsI ASVs. Drain CurrentVIRFZ44NPbF 7Peak Diode Recovery dv/dt Test CircuitV DD* Reverse Polarity of D.U.T for P-ChannelV GS*** V GS = 5.0V for Logic Level and 3V Drive Devices Fig 14. For N-channel HEXFET ® power MOSFETs(Dimensions are shown in millimeters (inches)) 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105TAC Fax: (310) 252-7903 Visit us at for sales contact information.09/2010分销商库存信息: IRIRFZ44NPBF。

三菱电机 第4代大型DIPIPM 应用手册

三菱电机株式会社和三菱电机机电(上海)有限公司拥有本手册内所有资料的版权。 任何个人和企业在未得到书面许可的情况下,不得传播、复制、转载、出版和出售涉及本手册的任何内 容。如有违反,我们将保留追究其法律责任的权利。敬请留意。

2009 年 3 月

第 4 代大型 DIPIPM 应用手册

目录

第 1 章 产品概要 ......................................................................................................................................... 1

2.2 保护功能及其工作时序.......................................................................................................................... 9 2.2.1 短路保护......................................................................................................................................... 9 2.2.2 控制电源欠压保护(UV) ..................................................................................................... 12 2.2.............................................................................................. 13

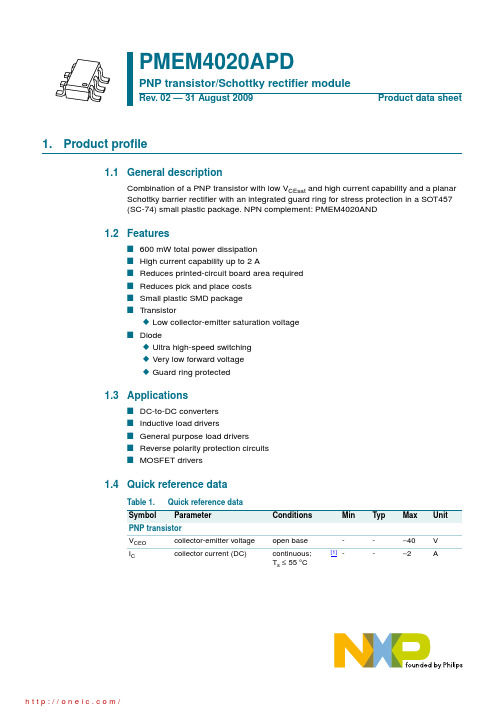

PMEM4020APD,115;中文规格书,Datasheet资料

1.Product profile1.1General descriptionCombination of a PNP transistor with low V CEsat and high current capability and a planar Schottky barrier rectifier with an integrated guard ring for stress protection in a SOT457(SC-74) small plastic package. NPN complement: PMEM4020AND1.2FeaturesI 600 mW total power dissipation I High current capability up to 2 AI Reduces printed-circuit board area required I Reduces pick and place costs I Small plastic SMD package ITransistorN Low collector-emitter saturation voltage I DiodeN Ultra high-speed switching N Very low forward voltage N Guard ring protected1.3ApplicationsI DC-to-DC converters I Inductive load driversI General purpose load driversI Reverse polarity protection circuits IMOSFET drivers1.4Quick reference dataPMEM4020APDPNP transistor/Schottky rectifier moduleRev. 02 — 31 August 2009Product data sheetTable 1.Quick reference data Symbol ParameterConditions Min Typ Max Unit PNP transistorV CEO collector-emitter voltage open base --−40V I Ccollector current (DC)continuous;T s ≤ 55°C[1]--−2A[1]Soldering point of collector or cathode tab.2.Pinning information3.Ordering information4.Marking5.Limiting valuesSchottky barrier rectifierV R continuous reverse voltage --40V I Fcontinuous forward current--1ATable 1.Quick reference data …continued Symbol ParameterConditionsMin Typ Max Unit Table 2.Discrete pinningPin Description Simplified outline Symbol1emitter 2not connected 3cathode 4anode 5base 6collector132456sym04036145Table 3.Ordering informationType numberPackage NameDescriptionVersion PMEM4020APDSC-74plastic surface mounted package; 6 leadsSOT457Table 4.MarkingType number Marking code PMEM4020APDD3Table 5.Limiting valuesIn accordance with the Absolute Maximum Rating System (IEC 60134).Symbol ParameterConditions Min Max Unit PNP transistorV CBO collector-base voltage open emitter -−40V V CEO collector-emitter voltage open base -−40V V EBOemitter-base voltageopen collector-−5V[1]Mounted on a FR4 printed-circuit board, single-sided copper, tin-plated, standard footprint.[2]Device mounted on a printed-circuit board, single-sided copper, tin-plated, 1cm 2 mounting pad for both collector and cathode.[3]Mounted on a ceramic printed-circuit board, single-sided copper, tin-plated, standard footprint.[4]Soldering point of collector or cathode tab.I Ccollector current (DC)continuous [1]-−0.75A continuous [2]-−1A continuous [3]-−1.3A continuous;T s ≤ 55°C[4]-−2A I CM peak collector current -−3A I BM peak base current -−1A P tottotal power dissipationT amb ≤ 25°C [1]-295mW T amb ≤ 25°C [2]-400mW T amb ≤ 25°C [3]-500mW T s ≤ 55°C[4]-1000mW T j junction temperature -150°C Schottky barrier rectifierV R continuous reverse voltage -40V I F continuous forward voltage -1A I FRM repetitive peak forward currentt p ≤ 1 ms;δ≤ 0.5- 3.5A I FSM non-repetitive peak forward currentt = 8 ms; square wave -10A P tottotal power dissipationT amb ≤ 25°C [1]-295mW T amb ≤ 25°C [2]-400mW T amb ≤ 25°C [3]-500mW T s ≤ 55°C[4]-1000mW T j junction temperature [2]-150°C Combined deviceP tot total power dissipation T amb ≤ 25°C[2]-600mW T stg storage temperature −65+150°C T ambambient temperature[2]−65+150°CTable 5.Limiting values …continuedIn accordance with the Absolute Maximum Rating System (IEC 60134).Symbol ParameterConditions Min Max Unit6.Thermal characteristics[1]For Schottky barrier rectifiers thermal run-away has to be considered, as in some applications the reverse power losses P R are a significant part of the total power losses. Nomograms for determining the reverse power losses P R and I F(AV) rating will be available on request.[2]Soldering point of collector or cathode tab.[3]Mounted on a ceramic printed-circuit board, single-sided copper, tin-plated, standard footprint.[4]Device mounted on a printed-circuit board, single-sided copper, tin-plated, 1cm 2 mounting pad for both collector and cathode tab.[5]Mounted on a FR4 printed-circuit board, single-sided copper, tin-plated, standard footprint.Table 6.Thermal characteristics [1]Symbol Parameter Conditions Min Typ Max Unit Single device R th(j-s)thermal resistance from junction to soldering point in free air [2]--95K/W R th(j-a)thermal resistance from junction to ambientin free air[3]--250K/W [4]--315K/W [5]--425K/W Combined device R th(j-a)thermal resistance from junction to ambientin free air[3]--208K/W7.Characteristics[1]Pulse test: t p ≤ 300µs;δ≤ 0.02Table 7.CharacteristicsT amb = 25°C unless otherwise specified Symbol ParameterConditionsMin Typ Max Unit PNP transistorI CBOcollector-base cut-off current V CB =−40 V; I E = 0 A --−100nA V CB =−40 V; I E = 0 A;T j = 150°C--−50µA I CEO collector-emitter cut-off current V CE =−30 V; I B = 0 A --−100nA I EBO emitter-base cut-off current V EB =−5 V; I C = 0 A --−100nAh FEDC current gainV CE =−5 V; I C =−1 mA 300--V CE =−5 V; I C =−100 mA 300--V CE =−5 V; I C =−500 mA 250-900V CE =−5 V; I C =−1 A 160--V CE =−5 V; I C =−2 A[1]50--V CEsatcollector-emitter saturation voltageI C =−100 mA; I B =−1 mA --−120mV I C =−500 mA; I B =−50 mA --−145mV I C =−1 A; I B =−100 mA --−260mV I C =−2 A; I B =−200 mA--−530mV R CEsat equivalent on-resistance I C =−1 A; I B =−100 mA [1]-180280m ΩV BEsat base-emittersaturation voltage I C =−1 A; I B =−100 mA [1]--−1.1V V BEon base-emitter turn-on voltageV CE =−5 V; I C =−1 A [1]--−1.0V f T transition frequency V CE =−10 V; I C =−50 mA;f = 100 MHz150--MHz C ccollector capacitanceV CB =−10 V; I E = i e = 0 A;f = 1 MHz --10pFSchottky barrier rectifier V Fcontinuous forward voltagesee Figure 1I F = 0.1 mA [1]-95130mV I F = 1 mA [1]-155210mV I F = 10 mA [1]-220270mV I F = 100 mA [1]-295350mV I F = 1000 mA[1]-540640mV I Rreverse currentsee Figure 2V R = 10 V [1]-720µA V R = 40 V[1]-30100µA C ddiode capacitanceV R = 1 V; f = 1 MHz;see Figure 3-4348pFSchottky barrier rectifier (1)T amb =150°C (2)T amb =85°C (3)T amb =25°CSchottky barrier rectifier (1)T amb =150°C (2)T amb =85°C (3)T amb =25°CFig 1.Forward current as a function of forward voltage; typical valuesFig 2.Reverse current as a function of reverse voltage; typical valuesSchottky barrier rectifier;T amb = 25°C; f = 1 MHzPNP transistor;V CE =−5 V (1)T amb = 150°C (2)T amb = 25°C (3)T amb =−55°CFig 3.Diode capacitance as a function of reverse voltage; typical valuesFig 4.DC current gain as a function of collector current; typical values0.60.40.2010310210110−1mdb669I F (mA)V F (V)(1)(2)(3)020103040V R (V)mdb670105104103102101I R (µA)(1)(2)(3)05102010008015604020mdb671V R (V)C d (pF)012002004006008001000mhc088−10−1h FE −10−1I C (mA)−102−103−104(1)(2)(3)PNP transistor;V CE =−5 V (1)T amb =−55°C (2)T amb = 25°C (3)T amb = 150°CPNP transistor;I C /I B = 10(1)T amb = 150°C (2)T amb = 25°C (3)T amb =−55°CFig 5.Base-emitter voltage as a function of collector current; typical valuesFig 6.Collector-emitter saturation voltage as a function of collector current; typical valuesPNP transistor;I C /I B = 10(1)T amb = 150°C (2)T amb = 25°C (3)T amb =−55°CPNP transistor;V CE =−10 VFig 7.Equivalent on-resistance as a function of collector current; typical valuesFig 8.Transition frequency as a function of collector current−10−1−10−1mhc089−10−1−1−10V BE (V)I C (mA)−103−102−104(1)(2)(3)−103−102−10−1mhc090−1−10V CEsat (mV)I C (mA)−102−103−104(1)(2)(3)10110−1102mhc091−10−1−1−10R CEsat (Ω)I C (mA)−103−102−104(1)(2)(3)0−100030010020025050150−200−400f T (MHz)I C (mA)−600−800mhc0928.Application informationFig 9.DC-to-DC converterFig 10.Inductive load driver (relays, motors andbuzzers) with free-wheeling diodemgu866V OUTV INCONTROLLERmgu867V CCIN9.Package outlineFig 11.Package outline SOT457 (SC-74)REFERENCESOUTLINE VERSION EUROPEAN PROJECTIONISSUE DATE IECJEDECJEITA SOT457SC-74w BM b pD epin 1indexAA 1L pQdetail XH EE v M AA B yscalecX13245601 2 mmPlastic surface-mounted package (TSOP6); 6 leadsSOT457UNIT A 1b p c D E H E L p Q y w v mm0.10.0130.400.253.12.70.260.101.71.3e 0.953.02.50.20.10.2DIMENSIONS (mm are the original dimensions)0.60.20.330.23A 1.10.905-11-0706-03-1610.Packing informationTable 8.Packing methodsThe indicated -xxx are the last three digits of the 12NC ordering code.[1]Type number Package Description Packing quantity300010000 PMEM4020APD SOT457 4 mm pitch, 8 mm tape and reel; T1-115-1354 mm pitch, 8 mm tape and reel; T2-125-165 [1]For further information and the availability of packing methods, see Section13.分销商库存信息: NXPPMEM4020APD,115。

lapp电缆HFEE 技术文件中文

产品编号

芯数 x 截面积 mm2

HFEE+C 多芯屏蔽电缆

3939001 R+T

2X0.5

3939002 R+T

3G0.5

3939003 R+T

4G0.5

3939004 R+T

5G0.5

3939101 R+T 3939102 R+T 3939103 R+T 3939104 R+T

2X0.75 3G0.75 4G0.75 5G0.75

1) 在订货时,请将编号按相应的颜色色码填充完整。

007=紫色 009=橙色 104=红色

105=白色 106=灰色 114=深蓝色

HFEE 多 芯 电 缆

产品编号

HFEE 多芯电缆

3938001 R+T 3938002 R+T 3938003 R+T 3938004 R+T 3938005 R+T

0.25 0.50 0.75 1.0 1.5 2.5 4.0 6.0 10.0 16.0 25.0 35.0 50.0 70.0 95.0 120.0 150.0 185.0 240.0

导体结构 根数 x 单丝直径

14x0.15 16x0.20 24x0.20 32x0.20 30x0.25 50x0.25 56x0.30 84x0.30 80x0.40 128x0.40 200x0.40 280x0.40 400x0.40 356x0.50 485x0.50 614x0.50 765x0.50 944x0.50 1225x0.50

HFEE 国 产 系 列 低 烟 无 卤 耐 高 温 阻 燃 电 缆

1. 产品系列

DATASHEET (TP4054 线性锂离子电池充电器)

间,并应通过至少一个 1μF 电容器进行旁 路。当 VCC 降至 BAT 引脚电压的 30mV 以 内,TP4054 进入停机模式,从而使 IBAT 降至 2μA 以下。 PROG(引脚 5) :充电电流设定、充电电流 监控和停机引脚。 在该引脚与地之间连接一 个精度为 1%的电阻器 RPROG 可以设定充电 电流。当在恒定电流模式下进行充电时,引 脚的电压被维持在 1V。 PROG 引脚还可用来关断充电器。将设定电 阻器与地断接,内部一个 2.5μA 电流将 PROG 引脚拉至高电平。当该引脚的电压达 到 2.70V 的停机门限电压时, 充电器进入停 机模式,充电停止且输入电源电流降至 45μA。重新将 RPROG 与地相连将使充电器 恢复正常操作状态。

TEL:0755-82863877 13242913995 FAX:0755-82863778 E-MAIL:panxia168@

DATASHEET

(TP4054 线性锂离子电池充电器)

1

TP4054 线性锂离子电池充电器

描述

TP4054 是一款完整的单节锂离子电池采用恒定电流/恒定电压线性充电器。其 SOT 封装与较少的外部元件数目使得 TP4054 成为便携式应用的理想选择。 TP4054 可以适合 USB 电源和适配器电源工作。 由于采用了内部 PMOSFET 架构,加上防倒充电路,所以不需要外部检测电阻器和 隔离二极管。热反馈可对充电电流进行调节,以便在大功率操作或高环境温度条件下对 芯片温度加以限制。 充电电压固定于 4.2V, 而充电电流可通过一个电阻器进行外部设置。 当充电电流在达到最终浮充电压之后降至设定值 1/10 时, TP4054 将自动终止充电循环。 当输入电压(交流适配器或 USB 电源)被拿掉时,TP4054 自动进入一个低电流状 态,将电池漏电流降至 2uA 以下。也可将 TP4054 置于停机模式,以而将供电电流降至 45uA。TP4054 的其他特点包括充电电流监控器、欠压闭锁、自动再充电和一个用于指 示充电结束和输入电压接入的状态引脚。

Datasheet_EE431 高清版

L*)

Ø6 (0.24)

*) 长度请参考订货向导

Ø8

(0.31)

电路连接图

有源变送信号输出

EE431-T3xx

供电 15...35 V DC 24 V AC ±20%

EE431-T6xx

供电 20...35 V DC RL< 500 Ω 11...35 V DC RL< 50 Ω

输出: 0...10 V

-40 ℃…+110 ℃ (-40 °F...+230 °F) -40 ℃…+150 ℃ (-40 °F...+302 °F) 针对PT和NI的浸入式变速器 详见订货向导 典型< 1 mA 1) 双线 接线端子最大2x max. 2.5 mm2 (0 .004 in)2

v2.0 EE431

概述

绝缘电阻

(x)

EE431-

1) 与模拟输出无关

参数设置-模拟输出

量程 2)

单位

-40...60

(002) 公制

(M)

-20...80

(024) 非公制

(N)

0...50

(004)

0...100

(005)

32...212

(075)

-40...140

(083)

2) 可以按照要求提供其他温度输出范围

位置2 - 安装配件

浸入式安装套管 – 螺纹: ½”NPT

长度 黄铜 不锈钢

50 mm (1.97 “) 135 mm (5.31 “) 285 mm (11.22 “)

HA400111 HA400211

HA400112 HA400212

HA400113 HA400213

订货示例

无源电阻信号输出 位置1:

LF411CNNOPB,LF411ACNNOPB,LF411ACHNOPB, 规格书,Datasheet 资料

LF411LF411 Low Offset, Low Drift JFET Input Operational AmplifierLiterature Number: SNOSBH6C 芯天下--/LF411Low Offset,Low Drift JFET Input Operational AmplifierGeneral DescriptionThese devices are low cost,high speed,JFET input opera-tional amplifiers with very low input offset voltage and guar-anteed input offset voltage drift.They require low supply current yet maintain a large gain bandwidth product and fast slew rate.In addition,well matched high voltage JFET input devices provide very low input bias and offset currents.The LF411is pin compatible with the standard LM741allowing designers to immediately upgrade the overall performance of existing designs.These amplifiers may be used in applications such as high speed integrators,fast D/A converters,sample and hold circuits and many other circuits requiring low input offset voltage and drift,low input bias current,high input imped-ance,high slew rate and wide bandwidth.Featuresn Internally trimmed offset voltage:0.5mV(max)n Input offset voltage drift:10µV/˚C(max)n Low input bias current:50pA n Low input noise current:0.01pA/√Hz n Wide gain bandwidth:3MHz(min)n High slew rate:10V/µs(min)n Low supply current: 1.8mA n High input impedance:1012Ωn Low total harmonic distortion:≤0.02%n Low 1/f noise corner:50Hz nFast settling time to 0.01%:2µsTypical Connection 00565501Ordering InformationLF411XYZX indicates electrical grade Y indicates temperature range “M”for military “C”for commercial Z indicates package type “H”or “N”Connection DiagramsMetal Can Package00565505Note:Pin 4connected to case.Top ViewOrder Number LF411ACH or LF411MH/883(Note 11)See NS Package Number H08ADual-In-Line Package00565507Top ViewOrder Number LF411ACN,LF411CN See NS Package Number N08EBI-FET II ™is a trademark of National Semiconductor Corporation.August 2000LF411Low Offset,Low Drift JFET Input Operational Amplifier©2004National Semiconductor Corporation Absolute Maximum Ratings (Note 1)If Military/Aerospace specified devices are required,please contact the National Semiconductor Sales Office/Distributors for availability and specifications.LF411ALF411Supply Voltage±22V ±18V Differential Input Voltage ±38V ±30V Input Voltage Range (Note 2)±19V±15VOutput Short Circuit DurationContinuous ContinuousH PackageN Package Power Dissipation (Notes 3,10)670mW670mW H Package N Package T j max 150˚C 115˚C θj A162˚C/W (Still Air)120˚C/W65˚C/W (400LF/min Air Flow)θj C20˚C/W Operating Temp.Range (Note 4)(Note 4)Storage Temp.Range −65˚C ≤T A ≤150˚C −65˚C ≤T A ≤150˚CLead Temp.(Soldering,10sec.)260˚C 260˚CESD ToleranceRating to be determined.DC Electrical Characteristics(Note 5)SymbolParameterConditions LF411A LF411Units MinTyp Max MinTyp Max V OS Input Offset Voltage R S =10k Ω,T A =25˚C 0.30.50.8 2.0mV ∆V OS /∆T Average TC of Input R S =10k Ω(Note 6)710720µV/˚C Offset Voltage (Note 6)I OSInput Offset CurrentV S =±15V T j =25˚C 2510025100pA (Notes 5,7)T j =70˚C 22nA T j =125˚C 2525nA I BInput Bias CurrentV S =±15V T j =25˚C 5020050200pA (Notes 5,7)T j =70˚C 44nA T j =125˚C5050nA R IN Input Resistance T j =25˚C10121012ΩA VOLLarge Signal Voltage V S =±15V,V O =±10V,5020025200V/mV GainR L =2k,T A =25˚C Over Temperature 2520015200V/mV V O Output Voltage Swing V S =±15V,R L =10k±12±13.5±12±13.5V V CM Input Common-Mode ±16+19.5±11+14.5V Voltage Range −16.5−11.5V CMRR Common-Mode R S ≤10k8010070100dB Rejection Ratio PSRR Supply Voltage (Note 8)8010070100dBRejection Ratio I SSupply Current1.82.81.83.4mAAC Electrical Characteristic(Note 5)SymbolParameterConditionsLF411A LF411Units MinTyp Max Min Typ MaxSR Slew RateV S =±15V,T A =25˚C 1015815V/µs GBW Gain-Bandwidth Product V S =±15V,T A =25˚C 34 2.74MHze n Equivalent Input Noise Voltage T A =25˚C,R S =100Ω,f=1kHz2525i nEquivalent Input Noise CurrentT A =25˚C,f=1kHz0.010.01L F 411 2AC Electrical Characteristic(Note 5)(Continued)Symbol ParameterConditionsLF411A LF411UnitsMinTypMaxMinTypMaxTHDTotal Harmonic DistortionA V =+10,R L =10k,V O =20Vp-p,BW=20Hz−20kHz<0.02<0.02%Note 1:“Absolute Maximum Ratings”indicate limits beyond which damage to the device may occur.Operating Ratings indicate conditions for which the device is functional,but do not guarantee specific performance limits.Note 2:Unless otherwise specified the absolute maximum negative input voltage is equal to the negative power supply voltage.Note 3:For operating at elevated temperature,these devices must be derated based on a thermal resistance of θj A.Note 4:These devices are available in both the commercial temperature range 0˚C ≤T A ≤70˚C and the military temperature range −55˚C ≤T A ≤125˚C.The temperature range is designated by the position just before the package type in the device number.A “C”indicates the commercial temperature range and an “M”indicates the military temperature range.The military temperature range is available in “H”package only.Note 5:Unless otherwise specified,the specifications apply over the full temperature range and for V S =±20V for the LF411A and for V S =±15V for the LF411.V OS ,I B ,and I OS are measured at V CM =0.Note 6:The LF411A is 100%tested to this specification.The LF411is sample tested to insure at least 90%of the units meet this specification.Note 7:The input bias currents are junction leakage currents which approximately double for every 10˚C increase in the junction temperature,T j .Due to limited production test time,the input bias currents measured are correlated to junction temperature.In normal operation the junction temperature rises above the ambient temperature as a result of internal power dissipation,P D .T j =T A +θjA P D where θjA is the thermal resistance from junction to e of a heat sink is recommended if input bias current is to be kept to a minimum.Note 8:Supply voltage rejection ratio is measured for both supply magnitudes increasing or decreasing simultaneously in accordance with common practice,from ±15V to ±5V for the LF411and from ±20V to ±5V for the LF411A.Note 9:RETS 411X for LF411MH and LF411MJ military specifications.Note 10:Max.Power Dissipation is defined by the package characteristics.Operating the part near the Max.Power Dissipation may cause the part to operate outside guaranteed limits.Typical Performance CharacteristicsInput Bias CurrentInput Bias Current0056551100565512LF4113Typical Performance Characteristics(Continued)Supply CurrentPositive Common-Mode Input Voltage Limit0056551300565514Negative Common-Mode Input Voltage LimitPositive Current Limit0056551500565516Negative Current Limit Output Voltage Swing0056551700565518L F 411 4Typical Performance Characteristics(Continued)Output Voltage SwingGain Bandwidth0056551900565520Bode Plot Slew Rate0056552100565522Distortion vs FrequencyUndistorted Output Voltage Swing0056552300565524LF4115Typical Performance Characteristics(Continued)Open Loop FrequencyResponseCommon-Mode RejectionRatio0056552500565526Power Supply Rejection Ratio Equivalent Input NoiseVoltage0056552700565528Open Loop Voltage Gain Output Impedance0056552900565530L F 411 6Typical Performance Characteristics(Continued)Inverter Settling Time00565531Pulse Response RL=2kΩ,C L10pFSmall Signal Inverting00565539Small Signal Non-Inverting00565540Large Signal Inverting00565541Large Signal Non-Inverting00565542LF4117Pulse Response R L =2k Ω,C L 10pF(Continued)Current Limit (R L =100Ω)00565543Application HintsThe LF411series of internally trimmed JFET input op amps (BI-FET II ™)provide very low input offset voltage and guaranteed input offset voltage drift.These JFETs have large reverse breakdown voltages from gate to source and drain eliminating the need for clamps across the inputs.Therefore,large differential input voltages can easily be accommodated without a large increase in input current.The maximum differential input voltage is independent of the supply voltages.However,neither of the input voltages should be allowed to exceed the negative supply as this will cause large currents to flow which can result in a destroyed unit.Exceeding the negative common-mode limit on either input will force the output to a high state,potentially causing a reversal of phase to the output.Exceeding the negative common-mode limit on both inputs will force the amplifier output to a high state.In neither case does a latch occur since raising the input back within the common-mode range again puts the input stage and thus the amplifier in a normal operating mode.Exceeding the positive common-mode limit on a single input will not change the phase of the output;however,if both inputs exceed the limit,the output of the amplifier may be forced to a high state.The amplifier will operate with a common-mode input voltage equal to the positive supply;however,the gain bandwidth and slew rate may be decreased in this condition.When the negative common-mode voltage swings to within 3V of the negative supply,an increase in input offset voltage may occur.The LF411is biased by a zener reference which allows normal circuit operation on ±4.5V power supplies.Supply voltages less than these may result in lower gain bandwidth and slew rate.The LF411will drive a 2k Ωload resistance to ±10V over the full temperature range.If the amplifier is forced to drive heavier load currents,however,an increase in input offset voltage may occur on the negative voltage swing and finally reach an active current limit on both positive and negative swings.Precautions should be taken to ensure that the power supply for the integrated circuit never becomes reversed in polarity or that the unit is not inadvertently installed backwards in a socket as an unlimited current surge through the resulting forward diode within the IC could cause fusing of the internal conductors and result in a destroyed unit.As with most amplifiers,care should be taken with lead dress,component placement and supply decoupling in order to ensure stability.For example,resistors from the output to an input should be placed with the body close to the input to minimize “pick-up”and maximize the frequency of the feed-back pole by minimizing the capacitance from the input to ground.A feedback pole is created when the feedback around any amplifier is resistive.The parallel resistance and capacitance from the input of the device (usually the inverting input)to AC ground set the frequency of the pole.In many instances the frequency of this pole is much greater than the expected 3dB frequency of the closed loop gain and consequently there is negligible effect on stability margin.However,if the feedback pole is less than approximately 6times the ex-pected 3dB frequency,a lead capacitor should be placed from the output to the input of the op amp.The value of the added capacitor should be such that the RC time constant of this capacitor and the resistance it parallels is greater than or equal to the original feedback pole time constant.L F 411 8LF411 Typical ApplicationsHigh Speed Current Booster Array00565509PNP=2N2905NPN=2N2219unless notedTO-5heat sinks for Q6-Q79Typical Applications(Continued)10-Bit Linear DAC with No V OS Adjust00565532where A N =1if the A N digital input is highA N =0if the A N digital input is lowSingle Supply Analog Switch with Buffered Output00565533L F 411 10Simplified Schematic00565506Note 11:Available per JM38510/11904Detailed Schematic00565534LF41111Physical Dimensionsinches (millimeters)unless otherwise notedMetal Can Package (H)Order Number LF411MH/883or LF411ACHNS Package Number H08AMolded Dual-In-Line Package (N)Order Number LF411ACN or LF411CNNS Package Number N08EL F 411 12NotesLIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices orsystems which,(a)are intended for surgical implant into the body,or(b)support or sustain life,and whose failure to perform when properly used in accordance with instructions for use provided in the labeling,can be reasonably expected to result in a significant injury to the user.2.A critical component is any component of a lifesupport device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.BANNED SUBSTANCE COMPLIANCENational Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification(CSP-9-111C2)and the Banned Substances and Materials of Interest Specification (CSP-9-111S2)and contain no‘‘Banned Substances’’as defined in CSP-9-111S2.National Semiconductor Americas CustomerSupport CenterEmail:new.feedback@ Tel:1-800-272-9959National SemiconductorEurope Customer Support CenterFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)6995086208English Tel:+44(0)8702402171Français Tel:+33(0)141918790National SemiconductorAsia Pacific CustomerSupport CenterEmail:ap.support@National SemiconductorJapan Customer Support CenterFax:81-3-5639-7507Email:jpn.feedback@Tel:81-3-5639-7560 LF411 Low Offset, Low Drift JFET Input Operational AmplifierNational does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAudio /audio Communications and Telecom /communicationsAmplifiers Computers and Peripherals /computersData Converters Consumer Electronics /consumer-appsDLP®Products Energy and Lighting /energyDSP Industrial /industrialClocks and Timers /clocks Medical /medicalInterface Security /securityLogic Space,Avionics and Defense /space-avionics-defense Power Mgmt Transportation and Automotive /automotiveMicrocontrollers Video and Imaging /videoRFID OMAP Mobile Processors /omapWireless Connectivity /wirelessconnectivityTI E2E Community Home Page Mailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2011,Texas Instruments Incorporated。

D5V0L1B2LP4-7B,D5V0L1B2LP4-7B,D5V0L1B2LP4-7B, 规格书,Datasheet 资料

LOW CAPACITANCE BIDIRECTIONAL TVS DIODEFeatures• Provides ESD Protection per IEC 61000-4-2 Standard: Air – ±30kV, Contact – ±30kV• Ultra Low Profile (0.4mm), Ideal for Thin Portable Electronics • 1 Channel of ESD Protection • Low Channel Input Capacitance• Typically Used in Cellular Handsets, Portable Electronics, Communication Systems, Computers and Peripherals • Lead Free/RoHS Compliant (Note 1) • “Green” Device (Note 2)Mechanical Data• Case: X2-DFN1006-2• Case Material: Molded Plastic, “Green” Molding Compound. UL Flammability Classification Rating 94V-0 • Moisture Sensitivity: Level 1 per J-STD-020• Terminals: NiPdAu over Copper leadframe. Solderable per MIL-STD-202, Method 208•Weight: 0.001 grams (approximate)Ordering Information (Note 3)D 5V0 L X B X XXX- XX5V0: 5.0 Volts Voltage Capacitance # of Channels Polarity # of Pins Package PackingX: Extremely Low (<0.5pF)F: Ultra Low (0.5 ~ 1.0pF)P: Very Low (1.1 ~ 10pF)L: Low (10.1 ~ 20pF)M: Medium (>20pF)1: 1 Channel 2: 2 Channels 4: 4 Channels 6: 6 ChannelsB: Bidirectional (Symmetrical)U: Unidirectional A: Bidirectional (Asymmetrical)2: 2 Pins 3: 3 Pins 5: 5 Pins 6: 6 Pins 8: 8 Pins 10: 10 PinsLP3: X3-DFN0603-2LP: X1-DFN1006-2LP4: X2-DFN1006-2WS: SOD323T: SOD523/SOT523SO: SOT23/SOT25W: SOD123/SOT323TS: TSOT25/TSOT26S: SOT353/SOT363V:SOT553/SOT5637: 7” reel (3K/reel)7B: 7” reel (10Kreel)13: 13” reelPart Number CasePackagingD5V0L1B2LP4-7BX2-DFN1006-210,000/Tape & ReelNotes:1. EU Directive 2002/95/EC (RoHS) & 2011/65/EU (RoHS 2) compliant. No purposely added lead. Halogen and Antimony free.2. Diodes Inc.’s “Green” policy can be found on our website at .3. For packaging details, go to our website at .Marking InformationDevice SchematicBottom View Z = Product Type Marking Code Line Denotes Pin 1X2-DFN1006-2ZMaximum Ratings @T A = 25°C unless otherwise specifiedCharacteristic Symbol Value Unit ConditionsPeak Pulse Power Dissipation P PP 84 W 8/20μs, Per Fig. 1 Peak Pulse Current I PP 6 A 8/20μs, Per Fig. 1 ESD Protection – Contact Discharge V ESD_Contact ±30 kV IEC 61000-4-2 Standard ESD Protection – Air Discharge V ESD_Air±30 kV IEC 61000-4-2 StandardThermal CharacteristicsCharacteristic Symbol Value Unit Package Power Dissipation (Note 4) P D 250 mW Thermal Resistance, Junction to Ambient (Note 4) R θJA500 °C/W Operating and Storage Temperature Range T J , T STG -65 to +150 °CElectrical Characteristics @T A = 25°C unless otherwise specifiedCharacteristicSymbol Min Typ Max Unit Test Conditions Reverse Standoff VoltageV RWM - - 5 V - Channel Leakage Current (Note 5) I RM - 10 100 nA V RWM= 5VClamping Voltage, Positive Transients V CL --- - 7.0 9.0 10.5 11.5 9.0 11.0 12.0 14.0 VI PP = 1A, t p = 8/20μS I PP = 3.5A, t p = 8/20μS I PP = 5A, t p = 8/20μS I PP = 6A, t p = 8/20μSBreakdown Voltage V BR 6 7 8 V I R= 1mADifferential ResistanceR DIF - 0.2 - Ω I R = 1A, t p = 8/20μSChannel Input CapacitanceC T - 15 20 pF V R = 0V, f = 1MHzNotes:4. Device mounted on FR-4 PCB pad layout (2oz copper) as shown on Diodes, Inc. suggested pad layout AP02001, which can be found on our website at.5. Short duration pulse test used to minimize self-heating effect.t, TIME (s)Fig. 1 Pulse WaveformμI , P E A K P U L S E C U R R E N T (%I )P p p P V , REVERSE VOLTAGE (V)Fig. 2Typical Total Capacitance vs. Reverse VoltageR C , T O T A L C A P A C I T A N C E (p F )TP E A K P U L S E D E R A T I N G % O F P E A K P O W E R O R C U R R E N TT , AMBIENT TEMPERATURE (°C)Fig. 3 Pulse Derating CurveAFig. 4 Typical Reverse CharacteristicsV , REVERSE VOLTAGE (V)R I , L E A K A G E C U R R E N T (n A )RPackage Outline DimensionsSuggested Pad LayoutX2-DFN1006-2 Dim Min Max Typ A 0.34 0.4 0.37 A1 0 0.05 0.03 b 0.45 0.55 0.50 D 0.95 1.075 1.00 E 0.55 0.675 0.60 E ⎯ ⎯ 0.40 L 0.20 0.30 0.25 R 0.05 0.15 0.10 All Dimensions in mmDimensions Value (in mm)Z 1.1 G 0.3 X 0.7 Y 0.4 C 0.7ZXCG YIMPORTANT NOTICEDIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDING TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.LIFE SUPPORTDiodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:A. Life support devices or systems are devices or systems which:1. are intended to implant into the body, or2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in thelabeling can be reasonably expected to result in significant injury to the user.B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.Copyright © 2012, Diodes Incorporated。

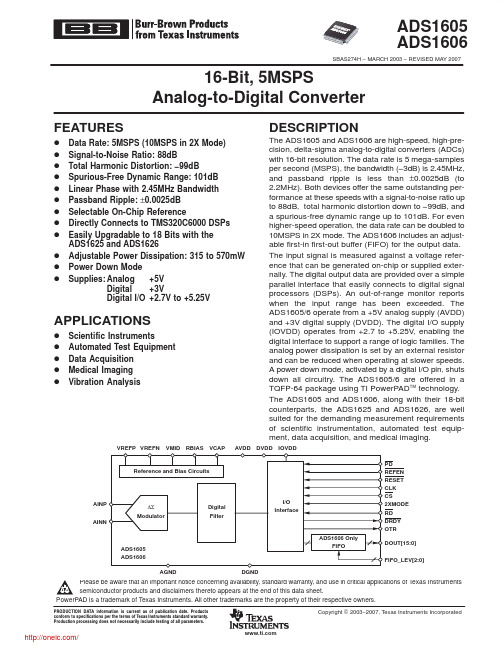

ADS1605IPAPT;ADS1606IPAPT;ADS1605IPAPR;ADS1605IPAPRG4;ADS1605IPAPTG4;中文规格书,Datasheet资料

APPLICATIONS

D D D D D

Scientific Instruments Automated Test Equipment Data Acquisition Medical Imaging Vibration Analysis

PRODUCT PACKAGE−LEAD PACKAGE DESIGNATOR PAP PAP SPECIFIED TEMPERATURE RANGE −40°C to +85°C −40°C to +85°C PACKAGE MARKING ADS1605I ADS1606I ORDERING NUMBER ADS1605IPAPT ADS1605IPAPR ADS1606IPAPT ADS1606IPAPR TRANSPORT MEDIA, QUANTITY Tape and Reel, 250 Tape and Reel, 1000 Tape and Reel, 250 Tape and Reel, 1000

ADS1605 ADS1606

HTQFP−64 HTQFP−64

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this data sheet, or see the TI web site at .

ADS1605 ADS1606

SBAS274H − MARCH 2003 − REVISED MAY 2007

LT6604IUFF-15#PBF,LT6604CUFF-15#PBF,LT6604CUFF-15#TRPBF,LT6604IUFF-15#TRPBF, 规格书,Datasheet 资料

T YPICAL APPLICATIOND ESCRIPTION Differential Amplifi er and15MHz Lowpass FilterThe LT ®6604-15 consists of two matched, fully differential amplifi ers, each with a 4th order, 15MHz lowpass fi lter. The fi xed frequency lowpass fi lter approximates a Chebyshev response. By integrating a fi lter and a differential ampli-fi er, distortion and noise are made exceptionally low. At unity gain, the measured in band signal-to-noise ratio is an impressive 76dB. At higher gains, the input referred noise decreases, allowing the part to process smaller input differential signals without signifi cantly degrading the signal-to-noise ratio.Gain and phase are highly matched between the two chan-nels. Gain for each channel is independently programmed using two external resistors. The LT6604-15 enables level shifting by providing an adjustable output common mode voltage, making it ideal for directly interfacing to ADCs.The LT6604-15 is fully specifi ed for 3V operation. The differential design enables outstanding performance at a 2V P-P signal level for a single 3V supply. See the back page of this datasheet for a complete list of related single and dual differential amplifi ers with integrated 2.5MHz to 20MHz lowpass fi lters.Channel to Channel Gain MatchingF EATURESA PPLICATIONS nDual Differential Amplifi er with 15MHz Lowpass Filters 4th Order Filters Approximates Chebyshev Response Guaranteed Phase and Gain Matching Resistor-Programmable Differential Gain n 76dB Signal-to-Noise (3V Supply, 2V P-P Output)n Low Distortion, 2V P-P , 800Ω Load, V S = 3V 1MHz: 86dBc 2nd, 90dBc 3rd 10MHz: 63dBc 2nd, 69dBc 3rd n Specifi ed for Operation with 3V , 5V and ±5V Supplies n Fully Differential Inputs and Outputsn Adjustable Output Common Mode Voltage n Small 4mm × 7mm × 0.75mm QFN PackagenDual Differential ADC Driver Plus Filter n Single-Ended to Differential Converter n Matched, Dual, Differential Filter Stagen Common Mode T ranslation of Differential Signals nHigh Speed ADC Antialiasing and DAC Smoothing in Wireless Infrastructure or Networking Applications n High Speed Test and Measurement Equipment n Medical ImagingL , L T , L TC and L TM are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.+––0.2512160.15660415 TA01b841014620–0.2–0.1–0.150.05–0.050.10.200.25GAIN MATCH (dB)LT6604-15P IN CONFIGURATIONA BSOLUTE MAXIMUM RATINGS Total Supply Voltage .................................................11V Operating Temperature Range (Note 6)....–40°C to 85°C Specifi ed Temperature Range (Note 7) ....–40°C to 85°C Junction Temperature ...........................................150°C Storage Temperature Range ...................–65°C to 150°C Input Current+IN, –IN, V OCM , V MID (Note 8) .........................±10mA Lead Temperature (Soldering, 10 sec) ..................300°CPARAMETERCONDITIONSMIN TYP MAX UNITS Filter Gain Either Channel, V S = 3VV IN = 2V P-P , f IN = DC to 260kHzV IN = 2V P-P , f IN =1.5MHz (Gain Relative to 260kHz)V IN = 2V P-P , f IN = 7.5MHz (Gain Relative to 260kHz)V IN = 2V P-P , f IN = 12MHz (Gain Relative to 260kHz)V IN = 2V P-P , f IN = 15MHz (Gain Relative to 260kHz)V IN = 2V P-P , f IN = 45MHz (Gain Relative to 260kHz)V IN = 2V P-P , f IN = 75MHz (Gain Relative to 260kHz)l l l l l l–0.5–0.1–0.3–0.3–0.70.1000.20–29–460.50.10.41.01.0–25dB dB dB dB dB dB dBORDER INFORMATIONLEAD FREE FINISH TAPE AND REEL PART MARKING*PACKAGE DESCRIPTIONSPECIFIED TEMPERATURE RANGE L T6604CUFF-15#PBF L T6604CUFF-15#TRPBF 6041534-Lead (4mm × 7mm) Plastic QFN 0°C to 70°C L T6604IUFF-15#PBFL T6604IUFF-15#TRPBF6041534-Lead (4mm × 7mm) Plastic QFN–40°C to 85°CConsult L TC Marketing for parts specifi ed with wider operating temperature ranges. *The temperature grade is identifi ed by a label on the shipping container.Consult L TC Marketing for information on non-standard lead based fi nish parts.For more information on lead free part marking, go to: http://www.linear .com/leadfree/ For more information on tape and reel specifi cations, go to: http://www.linear .com/tapeandreel/E LECTRICAL CHARACTERISTICS The l denotes specifi cations that apply over the full operating temperaturerange, otherwise specifi cations are at T A = 25°C. Unless otherwise specifi ed V S = 5V (V + = 5V , V –= 0V), R IN = 536Ω, and R LOAD = 1k.31 V –32 V –33 N C34 V M I D AV +B 17N C 16N C 15V O C M B 1430 NC 29 –OUTA 28 NC 27 +OUTA 26 NC 25 V +A 24 V –23 NC 22 NC 21 –OUTB 20 NC 19 +OUTB 18 NCNC 1+INA 2NC 3–INA 4NC 5V OCMA 6V – 7V MIDB 8NC 9+INB 10NC 11–INB 12NC 13TOP VIEW UFF PACKAGE34-LEAD (4mm × 7mm) PLASTIC QFN35T JMAX = 150°C, θJA = 34°C/W , θJC = 2.7°C/WEXPOSED PAD (PIN 35) IS V –, MUST BE SOLDERED TO PCB(Note 1)LT6604-15 E LECTRICAL CHARACTERISTICSThel denotes specifi cations that apply over the full operating temperature range, otherwise specifi cations are at T A = 25°C. Unless otherwise specifi ed V S = 5V (V+ = 5V, V– = 0V), R IN = 536Ω, and R LOAD = 1k.PARAMETER CONDITIONS MIN TYP MAX UNITSMatching of Filter Gain, V S = 3V V IN = 2V P-P, f IN = DC to 260kHzV IN = 2V P-P, f IN = 1.5MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 7.5MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 12MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 15MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 45MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 75MHz (Gain Relative to 260kHz)llllll0.050.010.020.030.060.130.150.50.10.30.40.61.52.8dBdBdBdBdBdBdBMatching of Filter Phase, V S = 3V V IN = 2V P-P, f IN = 1.5MHzV IN = 2V P-P, f IN = 7.5MHzV IN = 2V P-P, f IN = 12MHz lll0.60.80.9134degdegdegFilter Gain Either Channel, V S = 5V V IN = 2V P-P, f IN = DC to 260kHzV IN = 2V P-P, f IN =1.5MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 7.5MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 12MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 15MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 45MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 75MHz (Gain Relative to 260kHz)llllll–0.5–0.1–0.4–0.4–0.80.1–29–460.50.10.30.90.9–25dBdBdBdBdBdBdBMatching of Filter Gain, V S = 5V V IN = 2V P-P, f IN = DC to 260kHzV IN = 2V P-P, f IN =1.5MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 7.5MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 12MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 15MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 45MHz (Gain Relative to 260kHz)V IN = 2V P-P, f IN = 75MHz (Gain Relative to 260kHz)llllll0.050.010.020.030.060.130.150.50.10.30.40.61.52.8dBdBdBdBdBdBdBMatching of Filter Phase, V S = 5V V IN = 2V P-P, f IN = 1.5MHzV IN = 2V P-P, f IN = 7.5MHzV IN = 2V P-P, f IN = 12MHz lll0.60.80.9134degdegdegFilter Gain Either Channel, V S = ±5V V IN = 2V P-P, f IN = DC to 260kHz–0.6–0.10.4dBFilter Gain, R IN = 133ΩV IN = 0.5V P-P, f IN = DC to 260kHz V S = 3VV S = 5VV S = ±5V 11.511.511.412.012.011.912.512.512.4dBdBdBFilter Gain Temperature Coeffi cient (Note 2)f IN = 250kHz, V IN = 2V P-P780ppm/°C Noise Noise BW = 10kHz to 15MHz, R IN = 536Ω109μV RMSDistortion (Note 4)1MHz, 2V P-P, R L = 800Ω, V S = 3V 2nd Harmonic3rd Harmonic 8690dBcdBc10MHz, 2V P-P, R L = 800Ω, V S = 3V 2nd Harmonic3rd Harmonic 6369dBcdBcChannel Separation (Note 9)1MHz, 2V P-P, R L = 800Ω–117dB10MHz, 2V P-P, R L = 800Ω–102dBDifferential Output Swing Measured Between +OUT and –OUT, V OCM shorted to V MIDV S = 5VV S = 3V ll3.803.754.754.50V P-P_DIFFV P-P_DIFFInput Bias Current Average of IN+ and IN–l–90–35μAInput Referred Differential Offset R IN = 536Ω V S = 3VV S = 5VV S = ±5V lll51010253035mVmVmVR IN = 133Ω V S = 3VV S = 5VV S = ±5V lll555151720mVmVmVLT6604-15PARAMETER CONDITIONSMIN TYP MAX UNITS Differential Offset Drift10μV/°CInput Common Mode Voltage (Note 3)Differential Input = 500mV P-P, R IN = 133ΩV S = 3V V S = 5V V S = ±5Vl l l00–2.51.531V V VOutput Common Mode Voltage (Note 5)Differential Output = 2V P-P, V MID = Open, Common Mode Voltage at V OCM V S = 3V V S = 5V V S = ±5V l l l 11.5–1 1.532V V V Output Common Mode Offset (with Respect to V OCM )V S = 3V V S = 5V V S = ±5V l l l –35–40–5555–10404035mV mV mV Common Mode Rejection Ratio 64dB Voltage at V MID V S = 3V V S = 5Vl 2.45 2.501.5 2.56V V V MID Input Resistance l 4.3 5.77.7kΩV OCM Bias CurrentV OCM = V MID = V S /2 V S = 3VV S = 5V l l –10–10–2–2μA μAPower Supply Current (per Channel)V S = 3V, V S = 5V V S = 3V V S = 5V V S = ±5Vl l l 35343839444548mA mA mA mA Power Supply Voltagel311VE LECTRICAL CHARACTERISTICS The l denotes specifi cations that apply over the full operating temperaturerange, otherwise specifi cations are at T A = 25°C. Unless otherwise specified V S = 5V (V + = 5V , V –= 0V), R IN = 536Ω, and R LOAD = 1k.Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.Note 2: This is the temperature coeffi cient of the internal feedback resistors assuming a temperature independent external resistor (R IN ).Note 3: The input common mode voltage is the average of the voltagesapplied to the external resistors (R IN ). Specification guaranteed for R IN ≥ 100Ω.Note 4: Distortion is measured differentially using a differential stimulus. The input common mode voltage, the voltage at V OCM , and the voltage at V MID are equal to one half of the total power supply voltage.Note 5: Output common mode voltage is the average of the +OUT and –OUT voltages. The output common mode voltage is equal to V OCM .Note 6: The L T6604C-15 is guaranteed functional over the operating temperature range –40°C to 85°C.Note 7: The L T6604C-15 is guaranteed to meet 0°C to 70°C specifi cations and is designed, characterized and expected to meet the extendedtemperature limits, but is not tested at –40°C and 85°C. The L T6604I-15 is guaranteed to meet specifi ed performance from –40°C to 85°C.Note 8: Input pins (+IN, –IN, V OCM and V MID ) are protected by steering diodes to either supply. If the inputs should exceed either supply voltage, the input current should be limited to less than 10mA. In addition, the inputs +IN, –IN are protected by a pair of back-to-back diodes. If the differential input voltage exceeds 1.4V , the input current should be limited to less than 10mA.Note 9: Channel separation (the inverse of crosstalk) is measured by driving a signal into one input, while terminating the other input. Channel separation is the ratio of the resulting output signal at the driven channel to the output at the channel that is not driven.LT6604-15T YPICAL PERFORMANCE CHARACTERISTICS Output ImpedanceCommon Mode Rejection RatioPower Supply Rejection RatioDistortion vs FrequencyDistortion vs Signal LevelAmplitude ResponsePassband Gain and PhasePassband Gain and DelayFREQUENCY (MHz)0.1–20G A I N (d B )–10010110100660415 G01–30–40–50–60FREQUENCY (MHz)G A I N (d B )PHASE (DEG)–3–1120660415 G02–5–7–4–20–6–8–945135225–45–135090180–90–180–2255101525FREQUENCY (MHz)G A I N (d B )DELAY (ns)6101420660415 G042–248120–4–630405*********4515505101525FREQUENCY (MHz)1O U T P U T I M P E D A N C E (Ω)100.110100660415 G050.11100FREQUENCY (MHz)0.1C M R R (d B )607080110100660415 G065040306575554535FREQUENCY (MHz)0.150P S R R (d B )607080110100660415 G07403020100FREQUENCY (MHz)0.1–100–110D I S T O R T I O N (d B c )–60–50110100660415 G08–70–80–90INPUT LEVEL (V P-P )–60–50–404660415 G09–70–801235–90–100–110D I S T O R T I O N (d B c )Passband Gain and DelayFREQUENCY (MHz)G A I N (d B )DELAY (ns)–3–1120660415 G03–5–7–4–20–6–8–9304050201025354515505101525LT6604-15TYPICAL PERFORMANCE CHARACTERISTICSDistortion vs Output Common Mode LevelSingle Channel Supply Current vs Total Supply VoltageT ransient Response,Channel Separation vs Frequency (Note 9)Distortion vs Signal LevelDistortion vs Input Common Mode LevelDistortion vs Input Common Mode LevelINPUT LEVEL (V P-P )–60–50–404660415 G10–70–801235–90–100–110D I S T O R T I O N (d B c )INPUT COMMON MODE VOTLAGE RELATIVE TO V MID (V)–3–110–100D I S T O R T I O N C O M P O N E N T (d B c )–90–80–70–60–50–40–2–1012660415 G113INPUT COMMON MODE VOTLAGE RELATIVE TO V MID (V)–3–100D I S T O R T I O N C O M P O NE N T (d B c )–90–80–70–60–50–40–2–1012660415 G123(V OCM – V MID ) VOLTAGE (V)D I S T O R T I O N C O M P O NE N T (d B c )–70–60–500.51 1.5660415 G13–80–90–1.5–1–0.502 2.5–100–110–402V P-P 1MHz INPUT GAIN = 1,R L = 800Ω AT EACH OUTPUTT A = 25°CTOTAL SUPPLY VOLTAGE (V)20S U P P L Y C U R R E N T (m A )3040502535452468660415 G141012OUT –200mV/DIV IN +500mV/DIVIN –100ns/DIVDIFFERENTIAL GAIN = 1SINGLE-ENDED INPUT DIFFERENTAL OUTPUT660415 G15OUT +200mV/DIVFREQUENCY (MHz)0.1–50–60C H A N N E L S E P A R A T I O N (d B )–40110100660415 G16–70–80–100–90–120–130–110LT6604-15 P IN FUNCTIONS+INA and –INA (Pins 2, 4): Channel A Input Pins. Signals can be applied to either or both input pins through identi-cal external resistors, R IN. The DC gain from differential inputs to the differential outputs is 536Ω/R IN.V OCMA (Pin 6): DC Common Mode Reference Voltage for the 2nd Filter Stage in Channel A. Its value programs the common mode voltage of the differential output of the fi lter. Pin 6 is a high impedance input, which can be driven from an external voltage reference, or Pin 6 can be tied to Pin 34 on the PC board. Pin 6 should be bypassed with a 0.01μF ceramic capacitor unless it is connected to a ground plane.V– (Pins 7, 24, 31, 32, 35): Negative Power Supply Pin (can be ground).V MIDB (Pin 8): The V MIDB pin is internally biased at mid-supply, see Block Diagram. For single supply operation the V MIDB pin should be bypassed with a quality 0.01μF ceramic capacitor to ground. For dual supply operation, Pin 8 can be bypassed or connected to a high quality DC ground. A ground plane should be used. A poor ground will increase noise and distortion. Pin 8 sets the output common mode voltage of the 1st Filter Stage in channel B. It has a 5.5kΩ impedance, and it can be overridden with an external low impedance voltage source.+INB and –INB (Pins 10, 12): Channel B Input Pins. Signals can be applied to either or both input pins through identi-cal external resistors, R IN. The DC gain from differential inputs to the differential outputs is 536Ω/R IN.V OCMB (Pin 14):Is the DC Common Mode Reference Voltage for the 2nd Filter Stage in Channel B. Its value programs the common mode voltage of the differential output of the fi lter. Pin 14 is a high impedance input, which can be driven from an external voltage reference, or Pin 14 can be tied to Pin 8 on the PC board. Pin 14 should be bypassed with a 0.01μF ceramic capacitor unless it is connected to a ground plane.V+A and V+B (Pins 25, 17): Positive Power Supply Pins for Channels A and B. For a single 3.3V or 5V supply (Pins 7, 24, 31, 32 and 35 grounded) a quality 0.1μF ceramic bypass capacitor is required from the positive supply pin (Pins 25, 17) to the negative supply pin (Pins 7, 24, 31, 32 and 35). The bypass should be as close as possible to the IC. For dual supply applications, bypass the negative supply pins to ground and Pins 25 and 17 to ground with a quality 0.1μF ceramic capacitor.+OUTB and –OUTB (Pins 19, 21): Output Pins. Pins 19 and 21 are the fi lter differential outputs for channel B. With a typical short-circuit current limit greater than ±40mA each pin can drive a 100Ω and/or 50pF load to AC ground.+OUTA and –OUTA (Pins 27, 29): Output Pins. Pins 27 and 29 are the fi lter differential outputs for channel A. With a typical short-circuit current limit greater than ±40mA each pin can drive a 100Ω and/or 50pF load to AC ground.V MIDA (Pin 34): The V MIDA pin is internally biased at mid-supply, see Block Diagram. For single supply operation the V MIDA pin should be bypassed with a quality 0.01μF ceramic capacitor to ground. For dual supply operation, Pin 34 can be bypassed or connected to a high quality DC ground. A ground plane should be used. A poor ground will increase noise and distortion. Pin 34 sets the output common mode voltage of the 1st stage fi lter stage in chan-nel A. It has a 5.5kΩ impedance, and it can be overridden with an external low impedance voltage source. Exposed Pad (Pin 35): V–. The Exposed Pad must be soldered to the PCB.LT6604-15BLOCK DIAGRAMV IN –V IN +V IN +V IN –OCMBNCNCV BNC+OUTA–OUTANCNCV +ANCV –NCNC+OUTBNC–OUTBV –V –V NCLT6604-15APPLICATIONS INFORMATIONInterfacing to the L T6604-15Note: The LT6604-15 contains two identical fi lters. The following applications information only refers to one fi lter. The two fi lters are independent except that they share thesame negative supply voltage V –. The two filters can be used simultaneously by replicating the example circuits. The referenced pin numbers correspond to the A channel fi lterThe LT6604-15 channel requires two equal external re-sistors, R IN , to set the differential gain to 536Ω/R IN . The inputs to the fi lter are the voltages V IN + and V IN – presented to these external components, Figure 1. The difference between V IN + and V IN – is the differential input voltage. The average of V IN + and V IN – is the common mode input voltage. Similarly, the voltages V OUT + and V OUT – appearing at Pins 27 and 29 of the LT6604-15 are the fi lter outputs. The dif-ference between V OUT + and V OUT – is the differential output voltage. The average of V OUT + and V OUT – is the commonmode output voltage. Figure 1 illustrates the LT6604-15 operating with a single 3.3V supply and unity passband gain; the input signal is DC coupled. The common mode input voltage is 0.5V, and the differential input voltage is 2V P-P . The common mode output voltage is 1.65V, and the differential output voltage is 2V P-P for frequencies below 15MHz. The common mode output voltage is determined by the voltage at V OCM . Since V OCM is shorted to V MID , the output common mode is the mid-supply voltage. In addition, the common mode input voltage can be equal to the mid-supply voltage of V MID .Figure 2 shows how to AC couple signals into the LT6604-15. In this instance, the input is a single-ended signal. AC cou-pling allows the processing of single-ended or differential signals with arbitrary common mode levels. The 0.1μF coupling capacitor and the 536Ω gain setting resistor form a high pass fi lter, attenuating signals below 3kHz. Larger values of coupling capacitors will proportionally reduce this highpass 3dB frequency.V INV INOUT +OUT –t321t3210V OUT+OUT –3221t100–1Figure 1Figure 2LT6604-15APPLICATIONS INFORMATIONIn Figure 3 the LT6604-15 is providing 12dB of gain. The gain resistor has an optional 62pF in parallel to improve the passband fl atness near 15MHz. The common mode output voltage is set to 2V.Use Figure 4 to determine the interface between the LT6604-15 and a current output DAC. The gain, or “tran-simpedance,” is defi ned as A = V OUT /I IN . To compute the transimpedance, use the following equation:A =536•R1(R1+R2)(Ω)By setting R1 + R2 = 536Ω, the gain equation reduces to A = R1 (Ω).The voltage at the pins of the DAC is determined by R1, R2, the voltage on V MID and the DAC output current. Consider Figure 4 with R1 = 49.9Ω and R2 = 487Ω. Thevoltage at V MID , for V S = 3.3V, is 1.65V. The voltage at the DAC pins is given by: V DAC =V MID •R1R1+R2+536+I IN •R1•R2R1+R2=77mV +I IN •45.3ΩI IN is I IN + or I IN –. The transimpedance in this example is 49.8Ω.Evaluating the L T6604-15The low impedance levels and high frequency operation of the LT6604-15 require some attention to the matching networks between the LT6604-15 and other devices. The previous examples assume an ideal (0Ω) source impedance and a large (1k) load resistance. Among practical examplesV INV INOUT +OUT–t32103210OUT+OUT–660415 F04=V OUT + – V OUT –I IN + – I IN –536 • R1R1 + R2Figure 3Figure 4Figure 511660415fbA PPLICATIONS INFORMATION where impedance must be considered is the evaluation of the LT6604-15 with a network analyzer.Figure 5 is a laboratory setup that can be used to char-acterize the LT6604-15 using single-ended instruments with 50Ω source impedance and 50Ω input impedance. For a unity gain confi guration the LT6604-15 requires an 536Ω source resistance yet the network analyzer output is calibrated for a 50Ω load resistance. The 1:1 transformer, 52.3Ω and 523Ω resistors satisfy the two constraints above. The transformer converts the single-ended source into a differential stimulus. Similarly, the output of the LT6604-15 will have lower distortion with larger load resistance yet the analyzer input is typically 50Ω. The 4:1 turns (16:1 impedance) transformer and the two 402Ω resistors of Figure 5, present the output of the LT6604-15 with a 1600Ω differential load, or the equiva-lent of 800Ω to ground at each output. The impedance seen by the network analyzer input is still 50Ω, reducing refl ections in the cabling between the transformer and analyzer input.Differential and Common Mode Voltage Ranges The differential amplifi ers inside the LT6604-15 contain circuitry to limit the maximum peak-to-peak differential voltage through the fi lter. This limiting function prevents excessive power dissipation in the internal circuitry and provides output short-circuit protection. The limiting function begins to take effect at output signal levelsabove 2V P-P and it becomes noticeable above 3.5V P-P . This is illustrated in Figure 6; the LT6604-15 channel was confi gured with unity passband gain and the input of the fi lter was driven with a 1MHz signal. Because this voltage limiting takes place well before the output stage of the fi lter reaches the supply rails, the input/output behavior of the IC shown in Figure 6 is relatively independent of the power supply voltage.The two amplifi ers inside the LT6604-15 channel have independent control of their output common mode voltage (see the Block Diagram section). The following guidelines will optimize the performance of the fi lter. V MID can be allowed to float, but it must be bypassed to an AC ground with a 0.01μF capacitor or some instability may be observed. V MID can be driven from a low impedance source, provided it remains at least 1.5V above V – and at least 1.5V below V +. An internal resistor divider sets the voltage of V MID . While the internal 11k resistors are well matched, their absolute value can vary by ±20%. This should be taken into consideration when connecting an external resistor network to alter the voltage of V MID . V OCM can be shorted to V MID for simplicity. If a different common mode output voltage is required, connect V OCM to a voltage source or resistor network. For 3V and 3.3V supplies the voltage at V OCM must be less than or equal to the mid supply level. For example, voltage (V OCM ) ≤ 1.65V on a single 3.3V supply. For power supply voltages higher than 3.3V the voltage at V OCM can be set above mid supply. The voltage on V OCM should not be more than 1V below the voltage on V MID . The voltage on V OCM should not be more than 2V above the voltage on V MID . V OCM is a high impedance input.The LT6604-15 was designed to process a variety of input signals including signals centered on the mid-supply volt-age and signals that swing between ground and a positive voltage in a single supply system (Figure 1). The range of allowable input common mode voltage (the average of V IN + and V IN – in Figure 1) is determined by the power supply level and gain setting (see Distortion vs Input Common Mode Level in the Typical Performance Characteristics).1MHz INPUT LEVEL (V P-P )200–20–40–60–80–10035660415 F0612467O U T P U T L E V E L (d B V )Figure 6. Output Level vs Input Level, Differential 1MHz Input, Gain = 1芯天下--/Common Mode DC CurrentsIn applications like Figure 1 and Figure 3 where the LT6604-15 not only provides lowpass fi ltering but also level shifts the common mode voltage of the input signal, DC currents will be generated through the DC path between input and output terminals. Minimize these currents to decrease power dissipation and distortion. Consider the application in Figure 3. V MID sets the output common mode voltage of the 1st differential amplifi er inside the LT6604-15 channel (see the Block Diagram section) at 2.5V. Since the input common mode voltage is near 0V, there will be approxi-mately a total of 2.5V drop across the series combination of the internal 536Ω feedback resistor and the external 133Ω input resistor. The resulting 3.7mA common mode DC current in each input path, must be absorbed by the sources V IN+ and V IN–. V OCM sets the common mode output voltage of the 2nd differential amplifi er inside the LT6604-15 channel, and therefore sets the common mode output voltage of the fi lter. Since, in the example of Figure 3, V OCM differs from V MID by 0.5V, an additional 2.5mA (1.25mA per side) of DC current will fl ow in the resistors coupling the 1st differential amplifi er output stage to the fi lter output. Thus, a total of 9.9mA per channel is used to translate the common mode voltages.A simple modifi cation to Figure 3 will reduce the DC com-mon mode currents by 40%. If V MID is shorted to V OCM the common mode output voltage of both op amp stages will be 2V and the resulting DC current will be 6mA per channel. Of course, by AC coupling the inputs of Figure 3, the common mode DC current can be reduced to 2.5mA per channel.NoiseThe noise performance of the LT6604-15 channel can be evaluated with the circuit of Figure 6. Given the low noise output of the LT6604-15 and the 6dB attenuation of the transformer coupling network, it will be necessary to measure the noise fl oor of the spectrum analyzer and subtract the instrument noise from the fi lter noise mea-surement.Example: With the IC removed and the 25Ω resistors grounded, Figure 6, measure the total integrated noise (e S) of the spectrum analyzer from 10kHz to 15MHz. With the IC inserted, the signal source (V IN) disconnected, and the input resistors grounded, measure the total integrated noise out of the fi lter (e O). With the signal source connected, set the frequency to 1 MHz and adjust the amplitude until V IN measures 100mV P-P. Measure the output amplitude, V OUT, and compute the passband gain A = V OUT/V IN. Now compute the input referred integrated noise (e IN) as:e INTable 1 lists the typical input referred integrated noise for various values of R IN.Table 1. Noise PerformancePASSBANDGAINR ININPUT REFERREDINTEGRATED NOISE10kHz TO 15MHzINPUT REFERREDINTEGRATED NOISE10kHz TO 30MHz 4133Ω36μV RMS51μV RMS2267Ω62μV RMS92μV RMS1536Ω109μV RMS169μV RMSAPPLICATIONS INFORMATION芯天下--/12660415fb。

LPE-4841-100MB中文资料

PACKAGE CODE

INDUCTANCE VALUE

See the end of this data book for conversion tables

102

For technical questions, contact Magnetics@

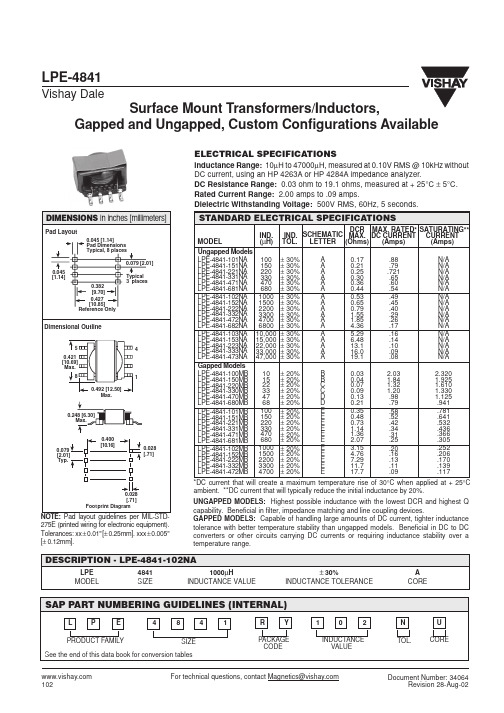

Inductance Range: 10µH to 47000µH, measured at 0.10V RMS @ 10kHz without DC current, using an HP 4263A or HP 4284A impedance analyzer. DC Resistance Range: 0.03 ohm to 19.1 ohms, measured at + 25°C ± 5°C. Rated Current Range: 2.00 amps to .09 amps. Dielectric Withstanding Voltage: 500V RMS, 60Hz, 5 seconds.

NOTE: Pad layout guidelines per MIL-STD275E (printed wiring for electronic equipment). Tolerances: xx ± 0.01" [± 0.25mm]. xxx ± 0.005" [± 0.12mm].

DESCRIPTION - LPE-4841-102NA

元器件交易网

LPE-4841

Vishay Dale

Surface Mount Transformers/Inductors, Gapped and Ungapped, Custom Configurations Available

2P4M中文资料(nec)中文数据手册「EasyDatasheet - 矽搜」

DRM,

Tj = 125°C

−

Tj = 25°C

−

Tj = 125°C

−

dV D/dt Tj = 125°C, V DM = 2/3 V DRM

10

−

VTM ITM = 4 A

−

IGT VDM = 6 V, R L = 100 Ω,

−

栅极触发电压

Note

VGT VDM = 6 V, R L = 100 Ω,

1985, 2006

The revised points can be easily searched by copying an "现场:修订部分可以通过在 PDF文件中复制一个 “R”,并在 “查找内容 ”指定它可以很容易地搜索 .

芯片中文手册,看全文,戳

2P4M,2P6M

最大额定值

Note

IH VDM = 24 V, I TM = 4 A

−

1

3

mA 参照图9

电路改判关断时间

tq

Tj = 125°C, I TM = 500毫安,

−

30

−

μs

−

diR / DT = 15 A /μs, V R ≥ 25 V,

VDM = 2/3 V DRM ,DV D / dt的= 10V μ/ s

特性

符号

非重复性峰值反向电压 非重复性峰值断态电压 重复峰值反向电压 重复峰值断态电压

Note Note Note Note

VRSM VDSM VRRM VDRM

通态电流

IT (AV)

有效的通态电流 浪涌不重复通态电流 熔断电流

IT (RMS)

IT S M

∫

i2

IPC PFE回馈说明书

目录序言------------------------------------------------------------------2 开箱检查注意事项------------------------------------------------3 第一章安全信息------------------------------------------------41.1 安全定义-----------------------------------------------41.2 安装和配线注意事项--------------------------------41.3 使用注意事项-----------------------------------------51.4 其它-----------------------------------------------------5 第二章产品型号与规格---------------------------------------62.1 产品技术规格-----------------------------------------62.2 IPC PFE系列回馈装置的外形尺寸---------------7 第三章产品安装指南------------------------------------------93.1 主回路接线--------------------------------------------93.1.1 主回路端子排列------------------------------93.1.2 主回路接线方法------------------------------93.1.3 变频器的直流母线端子的辩认-----------113.1.4 与电梯控制柜连接时的接线--------------133.2 产品安装------------------------------------------------14 第四章IPC PFE系列回馈装置性能及参数---------------154.1 IPC PFE系列回馈装置的特点--------------------154.2 IPC PFE型号说明-----------------------------------164.3 IPC PFE 220V系列回馈装置型号与规格-------174.4 IPC PFE 220V系列回馈装置的外部接线规格-174.5 IPC PFE 380V系列回馈装置型号与规格-------184.6 IPC PFE 380V系列回馈装置的外部接线规格-18 第五章常见故障的排除--------------------------------------19 第六章质量保证-----------------------------------------------20序言感谢您购买和使用加能公司生产的IPC PFE系列电梯专用能量回馈装置。

LiFePO4 Battery

鋰鐵電池特性

高效率輸出:標準放電為2 5C、連續高電流放電可達10C, 高效率輸出:標準放電為2~5C、連續高電流放電可達10C,瞬間 10C 脈衝放電(10sec)可達20C 20C。 脈衝放電(10sec)可達20C。 極好的使用壽命, 500次迴圈 其放電容量仍大於95% 次迴圈, 95%。 極好的使用壽命,經500次迴圈,其放電容量仍大於95%。 安全性高,即使電池內部或外部受到傷害,電池不燃燒、不爆炸。 安全性高,即使電池內部或外部受到傷害,電池不燃燒、不爆炸。 耐熱程度佳,且可承受3~5C 甚至更高的充放電速度。 3~5C、 耐熱程度佳,且可承受3~5C、甚至更高的充放電速度。 高溫時性能良好:工作環境外部溫度65℃ 65℃時 高溫時性能良好:工作環境外部溫度65℃時,內部溫度將高達 95℃,電池放電結束時溫度可達160℃ 但電池的結構安全、 160℃, 95℃,電池放電結束時溫度可達160℃,但電池的結構安全、完 好。 過放電到零伏也無損壞。 過放電到零伏也無損壞。 可快速充電。 可快速充電。 鋰鐵電池原料沒有使用稀有金屬,可以大幅降低成本。 鋰鐵電池原料沒有使用稀有金屬,可以大幅降低成本。 對環境無污染。 對環境無污染。

LFP Battery Process

磷酸鋰鐵 (Cathode material)

分子式LiFePO4,又稱磷酸鐵鋰、鋰鐵磷,簡 稱LFP(三維橄欖石結構)

LFP Power Process

磷酸鋰鐵材料的合成可分為濕式法與乾式法兩 種,技術重點在配方與燒成控制。 一般生產工廠都配備攪拌機、氣氛燒成爐、研 磨機與篩分機等裝置。

2004年 2004年 3.2V 120-160 255 115 2000 2000 5~6