MTC24中文资料

c-24中文说明书

AVID C|24Guide 中文说明书一、简介1、C|24功能控件功能• 24个声道条,每个声道条都有以下控件: • 触敏机动推子 • 多功能旋转编码器和开关• 自动化模式选择器• 专用EQ和Dynamics开关• 专用Insert和Send开关• 专用Input和RecEnable开关• 声道Solo和Mute开关• 声道选择开关• 双排多功能显示器• 全局自动化模式和启动开关• 走带和导航控件• 编辑和功能控件• ProTools窗口和全局控制开关模拟音频功能• 16麦克风/线路/DI前置放大器具有以下功能:• 无级变速输入增益控件• 有开关控制的高通滤波器• 削波指示器• 幻象电源(8个声道分2组,每组都有)• 8x2辅助混音器具有以下功能:• 8 个输入装置都配有独立的增益控件• 立体声混音输出配有主音量控件• C|24 监控器分区输出装置有开关控制• 6声道监控器分区具有以下功能:2 个 (主要的和辅助的)环绕声输出音源2 个外部立体声输入音源配有选择器开关和电平控件的主要监控器输出装置 (5.1、LCRS 或立体声)和辅助监控输出装置(立体声)提示输出的2个声道 配有电平控件和提示监控功能的耳机输出装置 配有内置或外部音源和电平控件的对讲电话 配有外部输入和电平控件的对听机二、启动和关闭 Pro Tools 系统 基于 D-Command 的系统必须按照特定顺序启动和关闭。

按照此顺序打开系统电源:1、 首先打开外置硬盘。

等待 10 至 15 秒,让它们达到所需的转速。

2 、打开 C|243、 如果计划使用 MIDI 设备工作,打开 MIDI 接口和其他MIDI 装置。

4 、打开全部 Pro Tools 音频接口。

5、 打开计算机。

6 、打开监听音箱放大器或有源音箱。

按照此顺序关闭系统:1、 关闭监听音箱放大器或有源音箱。

2 、关闭全部 Pro Tools 音频接口。

3 、关闭计算机。

24C04中文资料

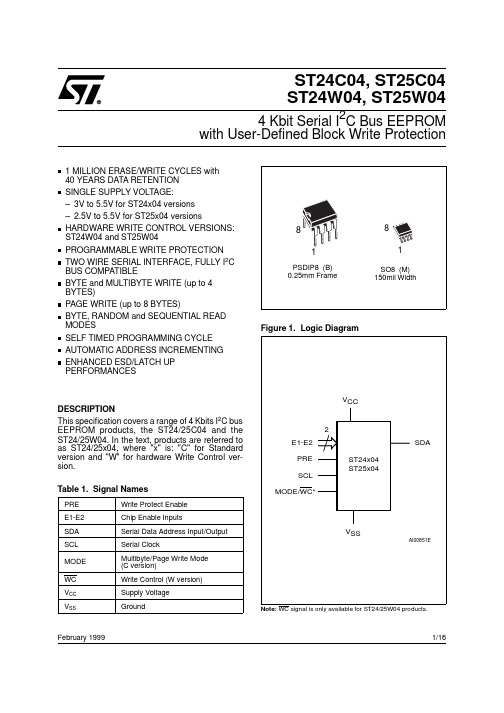

ST24C04, ST25C04 ST24W04, ST25W044 Kbit Serial I 2C Bus EEPROMwith User-Defined Block Write ProtectionFebruary 19991/16AI00851E2E1-E2SDAV CCST24x04ST25x04MODE/WC*SCLV SSPRE Figure 1. Logic Diagram1 MILLION ERASE/WRITE CYCLES with 40 YEARS DATA RETENTION SINGLE SUPPLY VOLTAGE:–3V to 5.5V for ST24x04 versions –2.5V to 5.5V for ST25x04 versionsHARDWARE WRITE CONTROL VERSIONS:ST24W04 and ST25W04PROGRAMMABLE WRITE PROTECTION TWO WIRE SERIAL INTERFACE, FULLY I 2C BUS COMPATIBLEBYTE and MULTIBYTE WRITE (up to 4BYTES)PAGE WRITE (up to 8 BYTES)BYTE, RANDOM and SEQUENTIAL READ MODESSELF TIMED PROGRAMMING CYCLE AUTOMATIC ADDRESS INCREMENTING ENHANCED ESD/LATCH UP PERFORMANCESDESCRIPTIONThis specification covers a range of 4 Kbits I 2C bus EEPROM products, the ST24/25C04 and the ST24/25W04. In the text, products are referred to as ST24/25x04, where "x" is: "C" for Standard version and "W" for hardware Write Control ver-sion.PRE Write Protect Enable E1-E2Chip Enable InputsSDA Serial Data Address Input/Output SCL Serial ClockMODE Multibyte/Page Write Mode (C version)WC Write Control (W version)V CC Supply Voltage V SSGroundTable 1. Signal Names81SO8 (M)150mil Width81PSDIP8 (B)0.25mm FrameNote: WC signal is only available for ST24/25W04 products.The ST24/25x04 are 4 Kbit electrically erasable programmable memories (EEPROM), organized as 2 blocks of 256 x8 bits. They are manufactured in STMicroelectronics’s Hi-Endurance Advanced CMOS technology which guarantees an endur-ance of one million erase/write cycles with a data retention of 40 years.Both Plastic Dual-in-Line and Plastic Small Outline packages are available.The memories are compatible with the I 2C stand-ard, two wire serial interface which uses a bi-direc-tional data bus and serial clock. The memoriescarry a built-in 4 bit, unique device identification code (1010) corresponding to the I 2C bus defini-tion. This is used together with 2 chip enable inputs (E2, E1) so that up to 4 x 4K devices may be attached to the I 2C bus and selected individually.The memories behave as a slave device in the I 2C protocol with all memory operations synchronized by the serial clock. Read and write operations are initiated by a START condition generated by the bus master. The START condition is followed by a stream of 7 bits (identification code 1010), plus one read/write bit and terminated by an acknowledge bit.SDAV SSSCL MODE/WC E1PRE V CCE2AI00852EST24x04ST25x0412348765Figure 2A. DIP Pin Connections 1AI01107E2348765SDAV SSSCL MODE/WC E1PRE V CCE2ST24x04ST25x04Figure 2B. SO Pin ConnectionsDESCRIPTION (cont’d)Symbol ParameterValue Unit T A Ambient Operating Temperature –40 to 125 °C T STG Storage Temperature –65 to 150°C T LEAD Lead Temperature, Soldering (SO8 package)(PSDIP8 package)40 sec 10 sec215260°C V IO Input or Output Voltages –0.6 to 6.5 V V CC Supply Voltage–0.3 to 6.5V V ESDElectrostatic Discharge Voltage (Human Body model) (2)4000V Electrostatic Discharge Voltage (Machine model) (3)500VNotes:1.Except for the rating "Operating Temperature Range", stresses above those listed in the Table "Absolute Maximum Ratings"may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to Absolute MaximumRating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents.-STD-883C, 3015.7 (100pF, 1500 Ω).3.EIAJ IC-121 (Condition C) (200pF, 0 Ω).Table 2. Absolute Maximum Ratings (1)2/16ST24/25C04, ST24/25W04ModeRW bit MODE Bytes Initial SequenceCurrent Address Read ’1’X 1START, Device Select, RW = ’1’Random Address Read ’0’X1START, Device Select, RW = ’0’, Address,’1’reSTART, Device Select, RW = ’1’Sequential Read ’1’X 1 to 512Similar to Current or Random Mode Byte Write ’0’X 1START, Device Select, RW = ’0’Multibyte Write (2)’0’V IH 4START, Device Select, RW = ’0’Page Write’0’V IL8START, Device Select, RW = ’0’Notes:1.X = V IH or V IL2.Multibyte Write not available in ST24/25W04 versions.Table 4. Operating Modes (1)Device CodeChip EnableBlock Select RW Bitb7b6b5b4b3b2b1b0Device Select11E2E1A8RWNote: The MSB b7 is sent first.Table 3. Device Select CodeWhen writing data to the memory it responds to the 8 bits received by asserting an acknowledge bit during the 9th bit time. When data is read by the bus master, it acknowledges the receipt of the data bytes in the same way. Data transfers are termi-nated with a STOP condition.Power On Reset: V CC lock out write protect. In order to prevent data corruption and inadvertent write operations during power up, a Power On Reset (POR) circuit is implemented. Until the V CC voltage has reached the POR threshold value, the internal reset is active, all operations are disabled and the device will not respond to any command.In the same way, when V CC drops down from the operating voltage to below the POR threshold value, all operations are disabled and the device will not respond to any command. A stable V CC must be applied before applying any logic signal.SIGNAL DESCRIPTIONSSerial Clock (SCL). The SCL input pin is used to synchronize all data in and out of the memory. A resistor can be connected from the SCL line to V CC to act as a pull up (see Figure 3).Serial Data (SDA). The SDA pin is bi-directional and is used to transfer data in or out of the memory.It is an open drain output that may be wire-OR’edwith other open drain or open collector signals on the bus. A resistor must be connected from the SDA bus line to V CC to act as pull up (see Figure 3).Chip Enable (E1 - E2). These chip enable inputs are used to set the 2 least significant bits (b2, b3)of the 7 bit device select code. These inputs may be driven dynamically or tied to V CC or V SS to establish the device select code.Protect Enable (PRE). The PRE input pin, in ad-dition to the status of the Block Address Pointer bit (b2, location 1FFh as in Figure 7), sets the PRE write protection active.Mode (MODE). The MODE input is available on pin 7 (see also WC feature) and may be driven dynami-cally. It must be at V IL or V IH for the Byte Write mode, V IH for Multibyte Write mode or V IL for Page Write mode. When unconnected, the MODE input is internally read as V IH (Multibyte Write mode). Write Control (WC). An hardware Write Control feature (WC) is offered only for ST24W04 and ST25W04 versions on pin 7. This feature is usefull to protect the contents of the memory from any erroneous erase/write cycle. The Write Control sig-nal is used to enable (WC = V IH ) or disable (WC =V IL ) the internal write protection. When uncon-nected, the WC input is internally read as V IL and the memory area is not write protected.3/16ST24/25C04, ST24/25W04AI01100V CCC BUSSDA R LMASTERR LSCLC BUS10020030040048121620C BUS (pF)R L m a x (k Ω)V CC = 5VFigure 3. Maximum R L Value versus Bus Capacitance (C BUS ) for an I 2C BusThe devices with this Write Control feature no longer support the Multibyte Write mode of opera-tion, however all other write modes are fully sup-ported.Refer to the AN404 Application Note for more de-tailed information about Write Control feature.DEVICE OPERATION I 2C Bus BackgroundThe ST24/25x04 support the I 2C protocol. This protocol defines any device that sends data onto the bus as a transmitter and any device that reads the data as a receiver. The device that controls the data transfer is known as the master and the other as the slave. The master will always initiate a data transfer and will provide the serial clock for syn-chronisation. The ST24/25x04 are always slave devices in all communications.Start Condition. START is identified by a high to low transition of the SDA line while the clock SCL is stable in the high state. A START condition must precede any command for data transfer. Except during a programming cycle, the ST24/25x04 con-tinuously monitor the SDA and SCL signals for a START condition and will not respond unless one is given.Stop Condition. STOP is identified by a low to high transition of the SDA line while the clock SCL is stable in the high state. A STOP condition termi-nates communication between the ST24/25x04and the bus master. A STOP condition at the end of a Read command, after and only after a No Acknowledge, forces the standby state. A STOP condition at the end of a Write command triggers the internal EEPROM write cycle.Acknowledge Bit (ACK). An acknowledge signal is used to indicate a successfull data transfer. The bus transmitter, either master or slave, will release the SDA bus after sending 8 bits of data. During the 9th clock pulse period the receiver pulls the SDA bus low to acknowledge the receipt of the 8 bits of data.Data Input. During data input the ST24/25x04sample the SDA bus signal on the rising edge of the clock SCL. Note that for correct device opera-tion the SDA signal must be stable during the clock low to high transition and the data must change ONLY when the SCL line is low.Memory Addressing. To start communication be-tween the bus master and the slave ST24/25x04,the master must initiate a START condition. Follow-ing this, the master sends onto the SDA bus line 8bits (MSB first) corresponding to the device select code (7 bits) and a READ or WRITE bit.SIGNAL DESCRIPTIONS (cont’d)4/16ST24/25C04, ST24/25W04Symbol ParameterTest ConditionMinMax Unit C IN Input Capacitance (SDA)8pF C IN Input Capacitance (other pins)6pF Z WCL WC Input Impedance (ST24/25W04)V IN ≤ 0.3 V CC 520k ΩZ WCH WC Input Impedance (ST24/25W04)V IN ≥ 0.7 V CC500k Ωt LPLow-pass filter input time constant (SDA and SCL)100nsNote: 1. Sampled only, not 100% tested.Table 5. Input Parameters (1) (T A = 25 °C, f = 100 kHz )Symbol ParameterTest Condition MinMax Unit I LI Input Leakage Current 0V ≤ V IN ≤ V CC ±2µA I LO Output Leakage Current 0V ≤ V OUT ≤ V CC SDA in Hi-Z ±2µA I CCSupply Current (ST24 series)V CC = 5V, f C = 100kHz (Rise/Fall time < 10ns)2mA Supply Current (ST25 series)V CC = 2.5V, f C = 100kHz 1mA I CC1Supply Current (Standby)(ST24 series)V IN = V SS or V CC ,V CC = 5V 100µA V IN = V SS or V CC , V CC = 5V, f C = 100kHz 300µA I CC2Supply Current (Standby) (ST25 series)V IN = V SS or V CC , V CC = 2.5V 5µA V IN = V SS or V CC , V CC = 2.5V, f C = 100kHz50µA V IL Input Low Voltage (SCL, SDA)–0.30.3 V CC V V IH Input High Voltage (SCL, SDA)0.7 V CC V CC + 1V V IL Input Low Voltage(E1-E2, PRE, MODE, WC)–0.30.5V V IH Input High Voltage(E1-E2, PRE, MODE, WC)V CC – 0.5V CC + 1V V OLOutput Low Voltage (ST24 series)I OL = 3mA, V CC = 5V 0.4V Output Low Voltage (ST25 series)I OL = 2.1mA, V CC = 2.5V0.4VTable 6. DC Characteristics(T A = 0 to 70°C, –20 to 85°C or –40 to 85°C; V CC = 3V to 5.5V or 2.5V to 5.5V)5/16ST24/25C04, ST24/25W04The 4 most significant bits of the device select codeare the device type identifier, corresponding to the I 2C bus definition. For these memories the 4 bits are fixed as 1010b. The following 2 bits identify the specific memory on the bus. They are matched to the chip enable signals E2, E1. Thus up to 4 x 4K memories can be connected on the same bus giving a memory capacity total of 16 Kbits. After a START condition any memory on the bus will iden-tify the device code and compare the following 2bits to its chip enable inputs E2, E1.The 7th bit sent is the block number (one block =256 bytes). The 8th bit sent is the read or write bit (RW), this bit is set to ’1’ for read and ’0’ for write operations. If a match is found, the corresponding memory will acknowledge the identification on the SDA bus during the 9th bit time.Input Rise and Fall Times ≤ 50nsInput Pulse Voltages0.2V CC to 0.8V CCInput and Output Timing Ref. Voltages 0.3V CC to 0.7V CCAC MEASUREMENT CONDITIONSAI008250.8V CC0.2V CC0.7V CC 0.3V CCFigure 4. AC Testing Input Output WaveformsDEVICE OPERATION (cont’d)Symbol Alt ParameterMinMax Unit t CH1CH2t R Clock Rise Time 1µs t CL1CL2t F Clock Fall Time 300ns t DH1DH2t R Input Rise Time 1µs t DL1DL1t F Input Fall Time300ns t CHDX (1)t SU:STA Clock High to Input Transition 4.7µs t CHCL t HIGH Clock Pulse Width High4µs t DLCL t HD:STA Input Low to Clock Low (START)4µs t CLDX t HD:DAT Clock Low to Input Transition 0µs t CLCH t LOW Clock Pulse Width Low4.7µs t DXCX t SU:DAT Input Transition to Clock Transition 250ns t CHDH t SU:STO Clock High to Input High (STOP) 4.7µs t DHDL t BUF Input High to Input Low (Bus Free) 4.7µs t CLQV (2)t AA Clock Low to Next Data Out Valid 0.3 3.5µs t CLQX t DH Data Out Hold Time 300ns f C f SCL Clock Frequency 100kHz t W (3)t WRWrite Time10msNotes:1.For a reSTART condition, or following a write cycle.2.The minimum value delays the falling/rising edge of SDA away from SCL = 1 in order to avoid unwanted START and/or STOP conditions.3.In the Multibyte Write mode only, if accessed bytes are on two consecutive 8 bytes rows (6 address MSB are not constant) themaximum programming time is doubled to 20ms.Table 7. AC Characteristics(T A = 0 to 70°C, –20 to 85°C or –40 to 85°C; V CC = 3V to 5.5V or 2.5V to 5.5V)6/16ST24/25C04, ST24/25W04SCL SDA INSCL SDA OUTSCL SDA INtCHCLtDLCLtCHDXSTARTCONDITIONtCLCHtDXCXtCLDXSDAINPUTSDACHANGEtCHDHtDHDLSTOP &BUS FREEDATA VALIDtCLQV tCLQXDATA OUTPUTtCHDHSTOPCONDITIONtCHDXSTARTCONDITIONWRITE CYCLEtWAI00795BFigure 5. AC WaveformsWrite OperationsThe Multibyte Write mode (only available on the ST24/25C04 versions) is selected when the MODE pin is at V IH and the Page Write mode when MODE pin is at V IL. The MODE pin may be driven dynami-cally with CMOS input levels.Following a START condition the master sends a device select code with the RW bit reset to ’0’. The memory acknowledges this and waits for a byte address. The byte address of 8 bits provides ac-cess to one block of 256 bytes of the memory. After receipt of the byte address the device again re-sponds with an acknowledge.For the ST24/25W04 versions, any write command with WC = 1 will not modify the memory content. Byte Write. In the Byte Write mode the master sends one data byte, which is acknowledged by the memory. The master then terminates the transfer by generating a STOP condition. The Write mode is independant of the state of the MODE pin which could be left floating if only this mode was to be used. However it is not a recommended operating mode, as this pin has to be connected to either V IH or V IL, to minimize the stand-by current.7/16ST24/25C04, ST24/25W04SCL SDASCL SDASDASTARTCONDITIONSDAINPUTSDACHANGEAI00792STOPCONDITION 123789MSB ACKSTARTCONDITIONSCL123789MSB ACKSTOPCONDITION Figure 6. I2C Bus ProtocolMultibyte Write. For the Multibyte Write mode, the MODE pin must be at V IH. The Multibyte Write mode can be started from any address in the memory. The master sends from one up to 4 bytes of data, which are each acknowledged by the mem-ory. The transfer is terminated by the master gen-erating a STOP condition. The duration of the write cycle is t W = 10ms maximum except when bytes are accessed on 2 rows (that is have different values for the 6 most significant address bits A7-A2), the programming time is then doubled to a maximum of 20ms. Writing more than 4 bytes in the Multibyte Write mode may modify data bytes in an adjacent row (one row is 8 bytes long). However, the Multibyte Write can properly write up to 8 consecutive bytes as soon as the first address of these 8 bytes is the first address of the row, the 7 following bytes being written in the 7 following bytes of this same row.Page Write. For the Page Write mode, the MODE pin must be at V IL. The Page Write mode allows up to 8 bytes to be written in a single write cycle, provided that they are all located in the same ’row’in the memory: that is the 5 most significant mem-8/16ST24/25C04, ST24/25W04ory address bits (A7-A3) are the same inside one block. The master sends from one up to 8 bytes of data, which are each acknowledged by the mem-ory. After each byte is transfered, the internal byte address counter (3 least significant bits only) is incremented. The transfer is terminated by the master generating a STOP condition. Care must be taken to avoid address counter ’roll-over’ which could result in data being overwritten. Note that, for any write mode, the generation by the master of the STOP condition starts the internal memory pro-gram cycle. All inputs are disabled until the comple-tion of this cycle and the memory will not respond to any request.Minimizing System Delays by Polling On ACK.During the internal write cycle, the memory discon-nects itself from the bus in order to copy the data from the internal latches to the memory cells. The maximum value of the write time (t W ) is given in the AC Characteristics table, since the typical time is shorter, the time seen by the system may be re-duced by an ACK polling sequence issued by the master.WRITE Cycle in ProgressAI01099BNext Operation is Addressing the MemorySTART Condition DEVICE SELECT with RW = 0ACK ReturnedYESNOYESNOReSTARTSTOPProceedWRITE OperationProceedRandom Address READ OperationSend Byte AddressFirst byte of instruction with RW = 0 already decoded by ST24xxxFigure 8. Write Cycle Polling using ACKAI00855B1FFhb7b3b2XX100hBlock 1Block 0Protect Flag Enable = 0Disable = 18 byte boundary address Protect Location Figure 7. Memory Protection9/16ST24/25C04, ST24/25W04The sequence is as follows:–Initial condition: a Write is in progress (see Figure 8).–Step 1: the Master issues a START condition followed by a Device Select byte (1st byte of the new instruction).–Step 2: if the memory is busy with the internal write cycle, no ACK will be returned and the master goes back to Step 1. If the memory has terminated the internal write cycle, it will re-spond with an ACK, indicating that the memory is ready to receive the second part of the next instruction (the first byte of this instruction was already sent during Step 1).Write Protection. Data in the upper block of 256bytes of the memory may be write protected. The memory is write protected between a boundary address and the top of memory (address 1FFh)when the PRE input pin is taken high and when the Protect Flag (bit b2 in location 1FFh) is set to ’0’.The boundary address is user defined by writing it in the Block Address Pointer. The Block Address Pointer is an 8 bit EEPROM register located at the address 1FFh. It is composed by 5 MSBs Address Pointer, which defines the bottom boundary ad-dress, and 3 LSBs which must be programmed atDEVICE OPERATION (cont’d)’0’. This Address Pointer can therefore address a boundary in steps of 8 bytes.The sequence to use the Write Protected feature is:–write the data to be protected into the top of the memory, up to, but not including, location 1FFh;–set the protection by writing the correct bottom boundary address in the Address Pointer (5MSBs of location 1FFh) with bit b2 (Protect flag)set to ’0’. Note that for a correct fonctionality of the memory, all the 3 LSBs of the Block Address Pointer must also be programmed at ’0’.The area will now be protected when the PRE input pin is taken High. While the PRE input pin is read at ’0’ by the memory, the location 1FFh can be used as a normal EEPROM byte.Caution: Special attention must be used when using the protect mode together with the Multibyte Write mode (MODE input pin High). If the Multibyte Write starts at the location right below the first byte of the Write Protected area, then the instruction will write over the first 3 bytes of the Write Protected area. The area protected is therefore smaller than the content defined in the location 1FFh, by 3 bytes.This does not apply to the Page Write mode as the address counter ’roll-over’ and thus cannot go above the 8 bytes lower boundary of the protected area.S T O PS T A R TBYTE WRITEDEV SELBYTE ADDR DATA INS T A R TMULTIBYTE ANDPAGE WRITEDEV SEL BYTE ADDR DATA IN 1DATA IN 2AI00793S T O PDATA IN NACKACKACKR/W ACKACKACKR/WACKACKFigure 9. Write Modes Sequence (ST24/25C04)10/16ST24/25C04, ST24/25W04S T O PS T A R TBYTE WRITEDEV SELBYTE ADDR DATA INWCS T A R TPAGE WRITEDEV SELBYTE ADDR DATA IN 1WCDATA IN 2AI01101BPAGE WRITE (cont'd)WC (cont'd)S T O PDATA IN NACKACKACKR/WACKACKACKR/WACKACKFigure 10. Write Modes Sequence with Write Control = 1 (ST24/25W04)Read OperationsRead operations are independent of the state of the MODE pin. On delivery, the memory content is set at all "1’s" (or FFh).Current Address Read. The memory has an inter-nal byte address counter. Each time a byte is read,this counter is incremented. For the Current Ad-dress Read mode, following a START condition,the master sends a memory address with the RW bit set to ’1’. The memory acknowledges this and outputs the byte addressed by the internal byte address counter. This counter is then incremented.The master does NOT acknowledge the byte out-put, but terminates the transfer with a STOP con-dition.Random Address Read. A dummy write is per-formed to load the address into the address counter, see Figure 11. This is followed by another START condition from the master and the byte address is repeated with the RW bit set to ’1’. The memory acknowledges this and outputs the byte addressed. The master have to NOT acknowledge the byte output, but terminates the transfer with a STOP condition.Sequential Read. This mode can be initiated with either a Current Address Read or a Random Ad-dress Read. However, in this case the master DOES acknowledge the data byte output and the memory continues to output the next byte in se-quence. To terminate the stream of bytes, the master must NOT acknowledge the last byte out-11/16put, but MUST generate a STOP condition. The output data is from consecutive byte addresses,with the internal byte address counter automat-ically incremented after each byte output. After a count of the last memory address, the addresscounter will ’roll- over’ and the memory will continue to output data.Acknowledge in Read Mode. In all read modes the ST24/25x04 wait for an acknowledge during the 9th bit time. If the master does not pull the SDA line low during this time, the ST24/25x04 terminate the data transfer and switches to a standby state.S T A R TDEV SEL *BYTE ADDRS T A R TDEV SELDATA OUT 1AI00794CDATA OUT NS T O PS T A R TCURRENT ADDRESS READDEV SELDATA OUTRANDOM ADDRESS READS T O PS T A R TDEV SEL *DATA OUTSEQUENTIAL CURRENT READS T O P DATA OUT NS T A R TDEV SEL *BYTE ADDR SEQUENTIAL RANDOM READS T A R TDEV SEL *DATA OUT 1S T O PACKR/WNO ACKACKR/WACKACK R/WACKACK ACK NO ACKR/WNO ACKACKACKR/WACK ACKR/WACK NO ACKFigure 11. Read Modes SequenceNote:*The 7 Most Significant bits of DEV SEL bytes of a Random Read (1st byte and 3rd byte) must be identical.DEVICE OPERATION (cont’d)12/16ORDERING INFORMATION SCHEMENotes: 3 * Temperature range on special request only.Parts are shipped with the memory content set at all "1’s" (FFh).For a list of available options (Operating Voltage, Range, Package, etc...) or for further information on any aspect of this device, please contact the STMicroelectronics Sales Office nearest to you.Operating Voltage ST24C04 3V to 5.5V ST24W04 3V to 5.5V ST25C04 2.5V to 5.5V ST25W04 2.5V to 5.5VRangeStandardHardware Write Control StandardHardware Write ControlPackage B PSDIP80.25mm Frame MSO8 150mil WidthTemperature Range 10 to 70 °C 5–20 to 85 °C 6–40 to 85 °C 3 *–40 to 125 °COption TRTape & Reel PackingExample: ST24C04 M 1 TR13/16PSDIP-aA2A1A Le1DE1EN1CeA eBB1BSymbmm inches TypMin Max TypMin Max A 3.90 5.900.1540.232A10.49–0.019–A2 3.30 5.300.1300.209B 0.360.560.0140.022B1 1.15 1.650.0450.065C 0.200.360.0080.014D 9.209.900.3620.390E 7.62––0.300––E1 6.00 6.700.2360.264e1 2.54––0.100––eA 7.80–0.307–eB –10.00–0.394L 3.00 3.800.1180.150N88Drawing is not to scalePSDIP8 - 8 pin Plastic Skinny DIP , 0.25mm lead frame14/16SO-aENCPBe ADCLA1α1Hh x 45˚Symbmm inches TypMin Max TypMin Max A 1.35 1.750.0530.069A10.100.250.0040.010B 0.330.510.0130.020C 0.190.250.0070.010D 4.80 5.000.1890.197E 3.80 4.000.1500.157e 1.27––0.050––H 5.80 6.200.2280.244h 0.250.500.0100.020L 0.400.900.0160.035α0°8°0°8°N 88CP0.100.004Drawing is not to scaleSO8 - 8 lead Plastic Small Outline, 150 mils body width15/16Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.The ST logo is a registered trademark of STMicroelectronics© 1999 STMicroelectronics - All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia - Brazil - Canada - China - France - Germany - Italy - Japan - Korea - Malaysia - Malta - Mexico - Morocco - The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.16/16。

LMV324DTBR2G资料

9 IN C−

IN B− 6

8 OUT C OUT B 7

TSSOP−14

−A+

+D−

−+ +−

B

C

14 OUT D 13 IN D− 12 IN D+ 11 V− 10 IN C+ 9 IN C− 8 OUT C

(Top View)

2

元器件交易网

GAIN (dB) CMRR (dB)

50

40

30

20

10

Over −40°C to +85°C 0 Same Gain $1.8 dB (Typ)

−10

10k

100k

1M

10M

FREQUENCY (Hz)

Figure 1. Open Loop Frequency Response (RL = 2 kW, TA = 255C, VS = 5 V)

SC−70

Continuous 150

280

°C °C/W

Micro8

238

TSOP−5

333

UDFN8 (1.2 mm x 1.8 mm x 0.5 mm)

350

SOIC−8

212

SOIC−14

156

TSSOP−14

190

Tstg

Storage Temperature

Mounting Temperature (Infrared or Convection −20 sec)

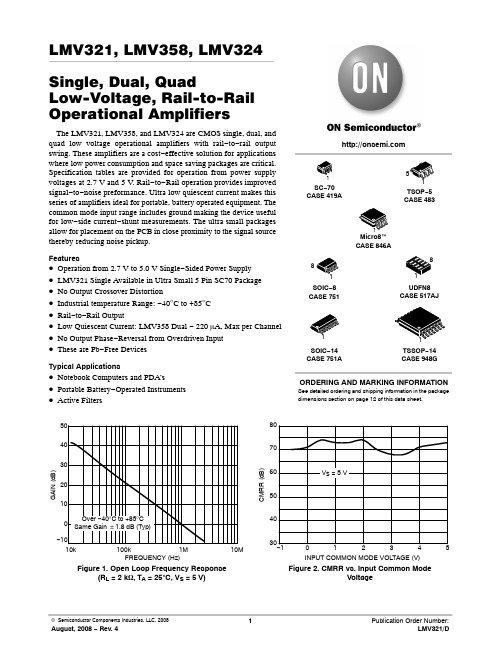

LMV321, LMV358, LMV324

MAXIMUM RATINGS

Symbol

Rating

Value

Unit

74ACT00MTC中文资料

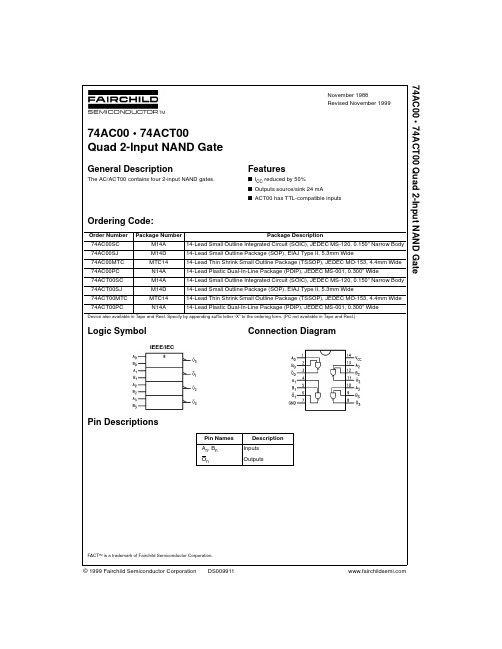

Device also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering form. (PC not available in Tape and Reel.)

TC24 用户手册说明书

User manualTable of ContentsGenerally (3)FCC notes (3)Section 15.19 (3)Section 15.21 Statement (3)Section 15.105 (a) Statement (3)IC notes (3)RSS-GEN – User Manual Statements (English/French) (3)RF exposure statement (3)2 / 3GenerallyThe module is not sold separately and is exclusively used for systems of HBC-radiomatic. The module is only used in professional industrial radio applications.For integration in host device integration instructions define requirements for installation, safety instructions written in host manual and labeling requirements.Changes or modifications made to this module not expressly approved by the party responsible for compliance may void the authorization to operate this equipment.FCC notesSection 15.19This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) this device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.Section 15.21 StatementChanges or modifications to the unit not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.Section 15.105 (a) StatementThis equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference in which case the user will be required to correct the interference at his own expense.IC notesRSS-GEN – User Manual Statements (English/French)Licence exemptThis device complies with Industry Canada’s licence-exempt RSSs. Operation is subject to the following two conditions:1. This device may not cause interference; and2. This device must accept any interference, including interference that may cause undesiredoperation of the device.Le présent appareil est conforme aux CNR d’Industrie Canada applicables aux appareils radio exempts de licence. L’exploitation est autorisée aux deux conditions suivantes:1. l’appareil ne doit pas produire de brouillage;2. l’utilisateur de l’appareil doit accepte r tout brouillage radioélectrique subi, même si le brouillageest susceptible d’en compromettre le fonctionnement.RF exposure statementThis RF module will be integrated with internal and external antennas in different host devices. For each final host device the RF exposure conditions to comply with FCC / ISED requirements will be individually defined and the user instructions of the host device will have appropriate installation or usage instructions. In general, the final host device will be used in such a manner that the potential for human contact including by-standers during normal operation is minimized.3 / 3。

NM24C03中文资料

Connection Diagrams

Dual-in-Line Package (N), SO Package (M8) and TSSOP Package (MT8)

A0 A1 A2 VSS 1 2 NM24C02 3 4 6 5 SCL SDA

元器件交易网

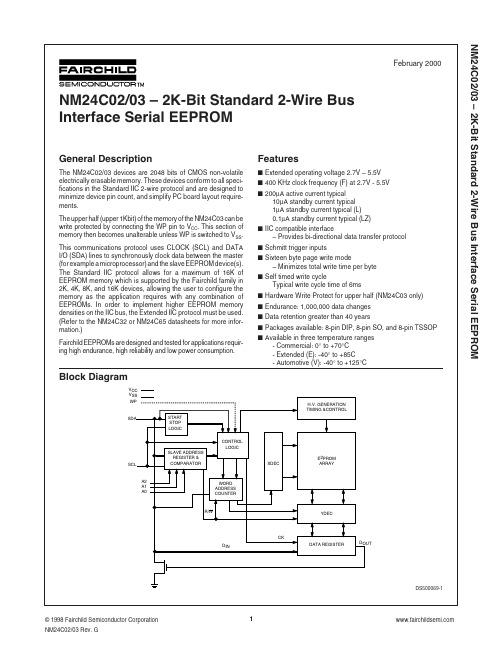

NM24C02/03 – 2K-Bit Standard 2-Wire Bus Interface Serial EEPROM

February 2000

NM24C02/03 – 2K-Bit Standard 2-Wire Bus Interface Serial EEPROM

DC Electrical Characteristics (2.7V to 5.5V)

Symbol Parameter Test Conditions Min

ICCA ISB Active Power Supply Current Standby Current fSCL = 400 KHz fSCL = 100 KHz VIN = GND or VCC VCC = 2.7V - 5.5V VCC = 2.7V - 5.5V (L) VCC = 2.7V - 4.5V (LZ)

Features

I Extended operating voltage 2.7V – 5.5V I 400 KHz clock frequency (F) at 2.7V - 5.5V I 200µA active current typical 10µA standby current typical 1µA standby current typical (L) 0.1µA standby current typical (LZ) I IIC compatible interface – Provides bi-directional data transfer protocol I Schmitt trigger inputs I Sixteen byte page write mode – Minimizes total write time per byte I Self timed write cycle Typical write cycle time of 6ms I Hardware Write Protect for upper half (NM24C03 only) I Endurance: 1,000,000 data changes I Data retention greater than 40 years I Packages available: 8-pin DIP, 8-pin SO, and 8-pin TSSOP I Available in three temperature ranges - Commercial: 0° to +70°C - Extended (E): -40° to +85C - Automotive (V): -40° to +125°C

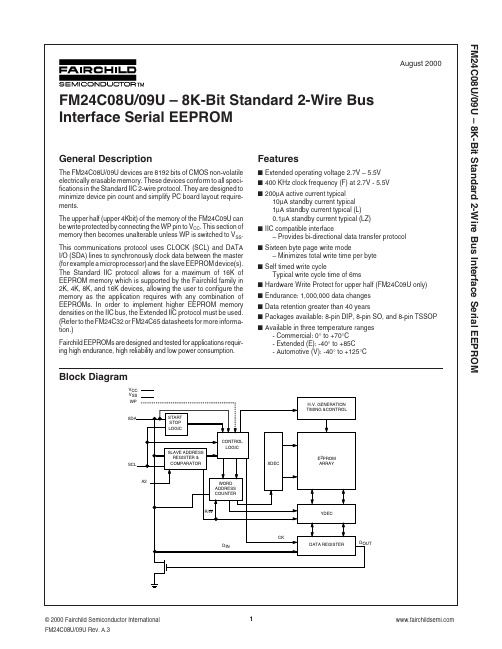

FM24C08中文资料

2

FM24C08U/09U Rev. A.3

元器件交易网

FM24C08U/09U – 8K-Bit Standard 2-Wire Bus Interface Serial EEPROM

Ordering Information FM 24 C XX U F LZ E XXX

NOTE: Pins designated as "NC" are typically unbonded pins. However some of them are bonded for special testing purposes. Hence if a signal is applied to these pins, care should be taken that the voltage applied on these pins does not exceed the VCC applied to the device. This will ensure proper operation.

DC Electrical Characteristics (2.7V to 5.5V)

Symbol Parameter Test Conditions Min

ICCA ISB (Note 3) ILI ILO VIL VIH VOL Active Power Supply Current Standby Current fSCL = 400 KHz ("F" version) fSCL = 100 KHz VIN = GND or VCC VCC = 2.7V - 5.5V VCC = 2.7V - 5.5V (L) VCC = 2.7V - 4.5V (LZ)

atc中文手册

A T24C256中文资料2009-11-15 09:43特性与1MHz I2C 总线兼容1.8 到6.0 伏工作电压范围低功耗CMOS 技术写保护功能当WP 为高电平时进入写保护状态64 字节页写缓冲器自定时擦写周期100,000 编程/擦写周期可保存数据100 年8 脚DIP SOIC 封装温度范围商业级工业级和汽车级概述CAT24WC256 是一个256K 位串行CMOS E2PROM 内部含有32768 个字节每字节为8 位CATALYST 公司的先进CMOS 技术实质上减少了器件的功耗CAT24WC256 有一个64 字节页写缓冲器该器件通过I2C 总线接口进行操作管脚描述管脚名称功能A0 A1 地址输入SDA 串行数据/地址SCL 串行时钟WP 写保护Vcc +1.8V 6.0V 电源Vss 地NC 未连接极限参数工作温度工业级-55 +125商业级0 +75贮存温度-65 +150各管脚承受电压-2.0V Vcc+2.0VVcc 管脚承受电压-2.0V +7.0V封装功率损耗Ta=25 1.0W焊接温度(10 秒) 300口输出短路电流100mA功能描述CAT24WC256 支持I2C 总线数据传送协议I2C 总线协议规定任何将数据传送到总线的器件作为发送器任何从总线接收数据的器件为接收器数据传送是由产生串行时钟和所有起始停止信号的主器件控制的CAT24WC256 是作为从器件被操作的主器件和从器件都可以作为发送器或接收器但由主器件控制传送数据发送或接收的模式管脚描述SCL 串行时钟CAT24WC256 串行时钟输入管脚用于产生器件所有数据发送或接收的时钟这是一个输入管脚SDA 串行数据/地址双向串行数据/地址管脚用于器件所有数据的发送或接收SDA 是一个开漏输出管脚可与其它开漏输出或集电极开路输出进行线或wire-ORWP 写保护当WP 脚连接到Vcc 所有内存变成写保护只能读当WP 引脚连接到Vss 或悬空允许器件进行读/写操作A0 A1 器件地址输入这些管脚为硬连线或者不连接对于单总线系统最多可寻址4 个CAT24WC256 器件参阅器件寻址当这些引脚没有连接时其默认值为0I2C 总线协议I2C 总线协议定义如下1 只有在总线空闲时才允许启动数据传送2 在数据传送过程中当时钟线为高电平时数据线必须保持稳定状态不允许有跳变时钟线为高电平时数据线的任何电平变化将被看作总线的起始或停止信号起始信号时钟线保持高电平期间数据线电平从高到低的跳变作为I2C 总线的起始信号停止信号时钟线保持高电平期间数据线电平从低到高的跳变作为I2C 总线的停止信号器件寻址主器件通过发送一个起始信号启动发送过程然后发送它所要寻址的从器件的地址8 位从器件地址的高5 位固定为10100 见图5 接下来的2 位A1 A0 为器件的地址位最多可以连接4 个器件到同一总线上这些位必须与硬连线输入脚A1 A0 相对应从器件地址的最低位作为读写控制位1表示对从器件进行读操作0 表示对从器件进行写操作在主器件发送起始信号和从器件地址字节后CAT24WC256 监视总线并当其地址与发送的从地址相符时响应一个应答信号通过SDA 线CAT24WC256 再根据读写控制位R/W 的状态进行读或写操作应答信号I2C 总线数据传送时每成功地传送一个字节数据后接收器都必须产生一个应答信号应答的器件在第9 个时钟周期时将SDA 线拉低表示其已收到一个8 位数据CAT24WC256 在接收到起始信号和从器件地址之后响应一个应答信号如果器件已选择了写操作则在每接收一个8 位字节之后响应一个应答信号当CAT24WC256 工作于读模式时在发送一个8 位数据后释放SDA 线并监视一个应答信号一旦接收到应答信号CAT24WC256 继续发送数据如主器件没有发送应答信号器件停止传送数据并等待一个停止信号写操作字节写在字节写模式下主器件发送起始信号和从器件地址信息R/W 位置0 给从器件在从器件送回应答信号后主器件发送两个8 位地址字写入CAT24WC256 的地址指针主器件在收到从器件的应答信号后再发送数据到被寻址的存储单元CAT24WC256 再次应答并在主器件产生停止信号后开始内部数据的擦写在内部擦写过程中CAT24WC256 不再应答主器件的任何请求页写在页写模式下单个写周期内CAT24WC256 最多可以写入64 个字节数据页写操作的启动和字节写一样不同在于传送了一字节数据后主器件允许继续发送63 个字节每发送一个字节后CAT24WC256 将响应一个应答位且内部低6 位地址加1 高位地址保持不变如果主器件在发送停止信号之前发送大于64 个字节地址计数器将自动翻转先前写入的数据被覆盖当所有64 字节接收完毕主器件发送停止信号内部编程周期开始此时所有接收到的数据在单个写周期内写入CAT24WC256应答查询可以利用内部写周期时禁止数据输入这一特性一旦主器件发送停止位指示主器件操作结束时CAT24WC256 启动内部写周期应答查询立即启动包括发送一个起始信号和进行写操作的从器件地址如果CAT24WC256 正在进行内部写操作将不会发送应答信号如果CAT24WC256 已经完成了内部写操作将发送一个应答信号主器件可以继续对CAT24WC256 进行下一次读写操作写保护写保护操作特性可使用户避免由于不当操作而造成对存储区域内部数据的改写当WP 管脚接高时整个寄存器区全部被保护起来而变为只可读取CAT24WC256 可以接收从器件地址和字节地址但是装置在接收到第一个数据字节后不发送应答信号从而避免寄存器区域被编程改写读操作CAT24WC256 读操作的初始化方式和写操作时一样仅把R/W 位置为1 有三种不同的读操作方式立即/当前地址读选择/随机读和连续读立即/当前地址读的地址计数器内容为最后操作字节的地址加1 也就是说如果上次读/写的操作地址为N 则立即读的地址从地址N+1 开始如果N=E 此处E=32767 则计数器将翻转到0 且继续输出数据CAT24WC256接收到从器件地址信号后R/W 位置1 它首先发送一个应答信号然后发送一个8 位字节数据主器件不需发送一个应答信号但要产生一个停止信号选择/随机读选择/随机读操作允许主器件对寄存器的任意字节进行读操作主器件首先通过发送起始信号从器件地址和它想读取的字节数据的地址执行一个伪写操作在CAT24WC256 应答之后主器件重新发送起始信号和从器件地址此时R/W 位置1 CAT24WC256 响应并发送应答信号然后输出所要求的一个8 位字节数据主器件不发送应答信号但产生一个停止信号连续读连续读操作可通过立即读或选择性读操作启动在CAT24WC256 发送完一个8 位字节数据后主器件产生一个应答信号来响应告知CAT24WC256 主器件要求更多的数据对应每个主机产生的应答信号CAT24WC256 将发送一个8 位数据字节当主器件不发送应答信号而发送停止位时结束此操作从CAT24WC256 输出的数据按顺序由N 到N+1 输出读操作时地址计数器在CAT24WC256 整个地址内增加这样整个寄存器区域在可在一个读操作内全部读出当读取的字节超过E 此处E=32767计数器将翻转到零并继续输出数据字节。

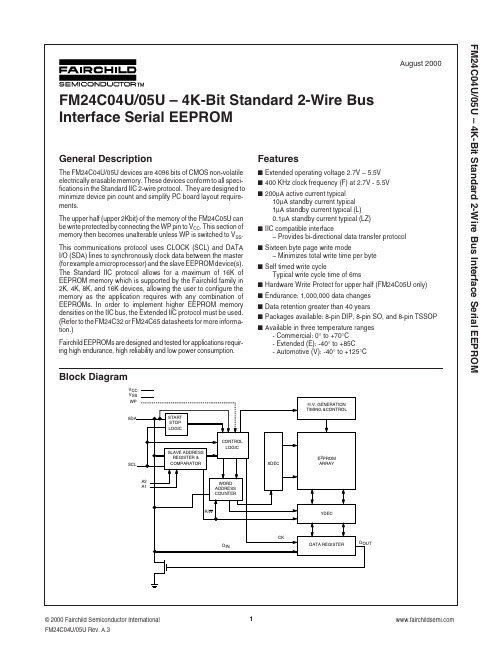

FM24C02中文资料

元器件交易网

FM24C04U/05U – 4K-Bit Standard 2-Wire Bus Interface Serial EEPROM

Ordering Information FM 24 C XX U F LZ E XXX

Operating Conditions

Ambient Operating Temperature FM24C04U/05U FM24C04UE/05UE FM24C04UV/05UV Positive Power Supply FM24C04U/05U FM24C04UL/05UL FM24C04ULZ/05ULZ 0°C to +70°C -40°C to +85°C -40°C to +125°C 4.5V to 5.5V 2.7V to 5.5V 2.7V to 5.5V

FM24C04U/05U – 4K-Bit Standard 2-Wire Bus Interface Serial EEPROM

Product Specifications Absolute Maximum Ratings

Ambient Storage Temperature All Input or Output Voltages with Respect to Ground Lead Temperature (Soldering, 10 seconds) ESD Rating –65°C to +150°C –0.3V to 6.5V +300°C 2000V min.

元器件交易网

FM24C04U/05U – 4K-Bit Standard 2-Wire Bus Interface Serial EEPROM

MTC产品说明书

在一支 MTC 型插入式多测点流量传感器上,配置 4 ~ 12 对高、低端感 压孔(视管径大小而不同)。在检测管中流量信号被平均后输出,其输出则代表 了多个测点的平均流速或流量。当管道内插入多支 MTC 流量传感器时,构成 矩阵分布的面测量方法,就可以准确测量流速分布不均匀的管道截面流量。

在流量测量过程中,流体的各相关参数经变送器转换为相对应的直流电流 信号(4-20 mA.DC),直接传送到DCS系统,运算并显示出管道的瞬时流量值。 或将变送器输出的直流电流信号传输到DZL-2智能流量信号转换仪运算显示出 管道的瞬时流量,并传送到DCS系统显示出瞬时流量。

MTC型 插入式多测点流量测量装置

产品说明书

量制陕字00000212号

西安中航流量技术研究所

1

MTC 型插入式多测点流量测量装置产品说明书

概述

在电力、冶金、石油、化工等诸多行业中有许多输送流体的工艺管道,准 确测量其流体的流量是操控设备自动、安全运行,实现节能降耗、提高生产效 率、保证产品质量的重要环节之一。很多大中型企业,尤其是电厂,设备庞大 且大管道繁多。管道布局受空间限制,大管道的交汇、分支、弯曲、变径等部 位,不能按最佳流态设计。由于阻力件形式繁杂,流量调节阀特性不佳、直管 段过短、流体温度混合不均、流速太低、管道振动、流体夹带大量粉尘及粒状 杂质等诸多因素的制约,造成管道流态复杂、流场紊乱。使得当前各类传统的 经典流量测量装置无法准确测量,不能满足自动测控要求。发明解决低速、管 道流场复杂多变、夹带粉粒杂质的流量测量的先进技术产品,并投放市场,是 我们的重要使命。

24lc256系列中文

I2C™ 串行 EEPROM 系列数据手册

特征:

• 容量从 128 位到 512 千位 • 24AAXX 器件单电源供电,工作电压低至 1.8V • 低功耗 CMOS 技术: - 1 mA 典型工作电流 - 1 µA 典型待机电流 (工业级温度) • 2 线串行接口总线,兼容 I2C™ • 施密特触发器输入以抑制噪声 •输出斜率控制以消除接地反弹 • 兼容 100 kHz (1.8V)和 400 kHz (≥ 2.5V)两 种传输速率 • 24FCXX 器件工作频率为 1 MHz • 自定时擦/写周期 (包括自动擦除) • 页写入缓冲器 • 大部分器件具有硬件写保护功能 • 具有工厂编程 (QTP)功能 • 静电保护电压 > 4,000V • 擦写次数可达 1,000,000 次 • 数据保存超过 200 年 • 8 引脚 PDIP、SOIC、 TSSOP 和 MSOP 封装 • 5 引脚 SOT-23 封装 (大部分容量为 1 到 16 千位的 器件) • 提供 8 引脚 2x3mm 和 5x6mm DFN 封装 • 扩展工作温度范围: - 工业级 (I) : -40°C 到 +85°C - 汽车级 (E) :-40°C 到 +125°C

2005 Microchip Technology Inc.

DS21930A_CN 第 3 页

24AAXX/24LCXX/24FCXX

2.0 电气特性

绝对最大额定值 (†)

VCC .............................................................................................................................................................................6.5V 相对于 Vss 的所有输入和输出 ............................................................................................................ -0.6V 到 VCC +1.0V 存储温度 ................................................................................................................................................. -65°C 到 +150°C 环境温度 (使用电源时) ........................................................................................................................ -40°C 到 +125°C 所有引脚静电保护 ....................................................................................................................................................................≥ 4 kV

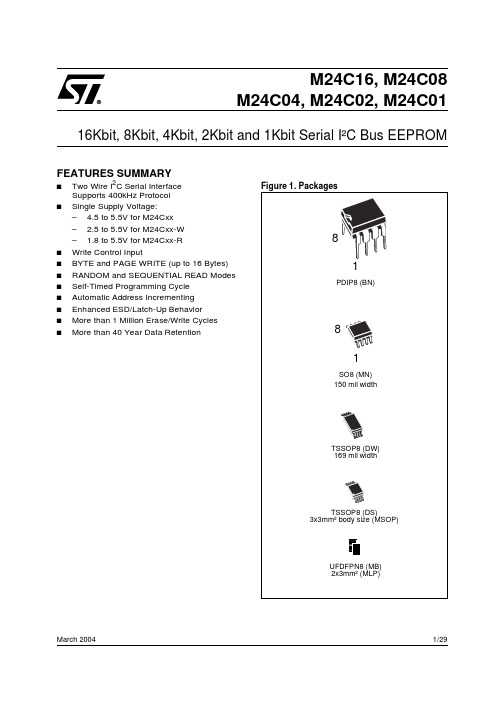

M24C04-RMB6T中文资料

1/29March 2004M24C16, M24C08M24C04, M24C02, M24C0116Kbit, 8Kbit, 4Kbit, 2Kbit and 1Kbit Serial I²C Bus EEPROMFEATURES SUMMARY■Two Wire I 2C Serial Interface Supports 400kHz Protocol ■Single Supply Voltage:– 4.5 to 5.5V for M24Cxx – 2.5 to 5.5V for M24Cxx-W – 1.8 to 5.5V for M24Cxx-R ■Write Control Input■BYTE and PAGE WRITE (up to 16 Bytes)■RANDOM and SEQUENTIAL READ Modes ■Self-Timed Programming Cycle ■Automatic Address Incrementing ■Enhanced ESD/Latch-Up Behavior ■More than 1 Million Erase/Write Cycles ■More than 40 Year Data RetentionM24C16, M24C08, M24C04, M24C02, M24C01TABLE OF CONTENTSFEATURES SUMMARY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 Figure 1.Packages. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1SUMMARY DESCRIPTION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4Figure 2.Logic Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4 Table 1.Signal Names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4 Power On Reset: VCC Lock-Out Write Protect. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4 Figure 3.DIP, SO, TSSOP and MLP Connections (Top View). . . . . . . . . . . . . . . . . . . . . . . . . . . . .4SIGNAL DESCRIPTION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5Serial Clock (SCL). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5 Serial Data (SDA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5 Chip Enable (E0, E1, E2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5 Write Control (WC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5 Figure 4.Maximum RL Value versus Bus Capacitance (CBUS) for an I2C Bus . . . . . . . . . . . . . . .5 Figure 5.I2C Bus Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6 Table 2.Device Select Code. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6DEVICE OPERATION. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7Start Condition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 Stop Condition. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 Acknowledge Bit (ACK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 Data Input. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 Memory Addressing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 Table 3.Operating Modes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7 Figure 6.Write Mode Sequences with WC=1 (data write inhibited). . . . . . . . . . . . . . . . . . . . . . . . .8 Write Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 Byte Write. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 Page Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8 Figure 7.Write Mode Sequences with WC=0 (data write enabled) . . . . . . . . . . . . . . . . . . . . . . . . .9 Figure 8.Write Cycle Polling Flowchart using ACK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10 Minimizing System Delays by Polling On ACK. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10 Figure 9.Read Mode Sequences. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11 Read Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11 Random Address Read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11 Current Address Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11 Sequential Read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12 Acknowledge in Read Mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12INITIAL DELIVERY STATE. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12MAXIMUM RATING. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13 Table 4.Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .132/29M24C16, M24C08, M24C04, M24C02, M24C01DC and AC PARAMETERS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14Table 5.Operating Conditions (M24Cxx) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14 Table 6.Operating Conditions (M24Cxx-W) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14 Table 7.Operating Conditions (M24Cxx-R). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14 Table 8.AC Measurement Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15 Figure 10.AC Measurement I/O Waveform. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15 Table 9.Input Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15 Table 10.DC Characteristics (M24Cxx, Device Grade 6). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15 Table 11.DC Characteristics (M24Cxx, Device Grade 3). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16 Table 12.DC Characteristics (M24Cxx-W, Device Grade 6). . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16 Table 13.DC Characteristics (M24Cxx-W, Device Grade 3). . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17 Table 14.DC Characteristics (M24Cxx-R) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17 Table 15.AC Characteristics (M24Cxx, Device Grade 6). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18 Table 16.AC Characteristics (M24Cxx, Device Grade 3; M24Cxx-W, Device Grade 6 or 3). . . . .18 Table 17.AC Characteristics (M24Cxx-R). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19 Figure 11.AC Waveforms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20PACKAGE MECHANICAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21Figure 12.PDIP8 – 8 pin Plastic DIP, 0.25mm lead frame, Package Outline . . . . . . . . . . . . . . . . .21 Table 18.PDIP8 – 8 pin Plastic DIP, 0.25mm lead frame, Package Mechanical Data. . . . . . . . . .21 Figure 13.SO8 narrow – 8 lead Plastic Small Outline, 150 mils body width, Package Outline . . . .22 Table 19.SO8 narrow – 8 lead Plastic Small Outline, 150 mils body width, Package Mechanical Data 22Figure 14.UFDFPN8 (MLP8) 8-lead Ultra thin Fine pitch Dual Flat Package No lead 2x3mm², Outline 23Table 20.UFDFPN8 (MLP8) 8-lead Ultra thin Fine pitch Dual Flat Package No lead 2x3mm², Data.23Figure 15.TSSOP8 – 8 lead Thin Shrink Small Outline, Package Outline . . . . . . . . . . . . . . . . . . .24 Table 21.TSSOP8 – 8 lead Thin Shrink Small Outline, Package Mechanical Data. . . . . . . . . . . .24 Figure 16.TSSOP8 3x3mm² – 8 lead Thin Shrink Small Outline, 3x3mm² body size, Package Outline 25Table 22.TSSOP8 3x3mm² – 8 lead Thin Shrink Small Outline, 3x3mm² body size, Mechanical Data 25PART NUMBERING . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26Table 23.Ordering Information Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26 Table 24.How to Identify Current and New Products by the Process Identification Letter. . . . . . .27REVISION HISTORY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28 Table 25.Document Revision History. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .283/29M24C16, M24C08, M24C04, M24C02, M24C014/29SUMMARY DESCRIPTIONThese I 2C-compatible electrically erasable pro-grammable memory (EEPROM) devices are orga-nized as 2048/1024/512/256/128x 8 (M24C16,M24C08, M24C04, M24C02, M24C01).I C uses a two wire serial interface, comprising a bi-directional data line and a clock line. The devic-es carry a built-in 4-bit Device Type Identifier code (1010) in accordance with the I 2C bus definition.The device behaves as a slave in the I 2C protocol,with all memory operations synchronized by the serial clock. Read and Write operations are initiat-ed by a Start condition, generated by the bus mas-ter. The Start condition is followed by a Device Table 2.),terminated by an acknowledge bit.When writing data to the memory, the device in-serts an acknowledge bit during the 9th bit time,following the bus master’s 8-bit transmission.When data is read by the bus master, the bus master acknowledges the receipt of the data byte in the same way. Data transfers are terminated by a Stop condition after an Ack for Write, and after a NoAck for Read.Table 1. Signal NamesPower On Reset: V CC Lock-Out Write Protect In order to prevent data corruption and inadvertent Write operations during Power-up, a Power On Reset (POR) circuit is included. At Power-up, the internal reset is held active until V CC has reached the POR threshold value, and all operations are disabled – the device will not respond to any com-mand. In the same way, when V CC drops from the operating voltage, below the POR threshold value,all operations are disabled and the device will not respond to any command.A stable and valid V CC (as defined in Table 6. and Table 7.) must be applied before applying any log-ic signal.Note: 1.NC = Not Connected2.See PACKAGE MECHANICAL section for package dimensions, and how to identify pin-1.E0, E1, E2Chip Enable SDA Serial Data SCL Serial Clock WC Write Control V CC Supply Voltage V SSGroundM24C16, M24C08, M24C04, M24C02, M24C01 SIGNAL DESCRIPTIONSerial Clock (SCL).This input signal is used to strobe all data in and out of the device. In applica-tions where this signal is used by slave devices to synchronize the bus to a slower clock, the bus master must have an open drain output, and a pull-up resistor can be connected from Serial Clock (SCL) to V CC. (Figure 4. indicates how the value of the pull-up resistor can be calculated). In most applications, though, this method of synchro-nization is not employed, and so the pull-up resis-tor is not necessary, provided that the bus master has a push-pull (rather than open drain) output. Serial Data (SDA).This bi-directional signal is used to transfer data in or out of the device. It is an open drain output that may be wire-OR’ed with other open drain or open collector signals on the bus. A pull up resistor must be connected from Se-rial Data (SDA) to V CC. (Figure 4. indicates how the value of the pull-up resistor can be calculated). Chip Enable (E0, E1, E2).These input signals are used to set the value that is to be looked for on the three least significant bits (b3, b2, b1) of the 7-bit Device Select Code. These inputs must be tied to V CC or V SS, to establish the Device Select Code.Write Control (WC).This input signal is useful for protecting the entire contents of the memory from inadvertent write operations. Write opera-tions are disabled to the entire memory array when Write Control (WC) is driven High. When uncon-nected, the signal is internally read as V IL, and Write operations are allowed.When Write Control (WC) is driven High, Device Select and Address bytes are acknowledged, Data bytes are not acknowledged.25/29M24C16, M24C08, M24C04, M24C02, M24C012Table 2. Device Select CodeDevice Type Identifier1Chip Enable2,3RW b7b6b5b4b3b2b1b0 M24C01Select Code1010E2E1E0RW M24C02Select Code1010E2E1E0RW M24C04Select Code1010E2E1A8RW M24C08Select Code1010E2A9A8RW M24C16Select Code1010A10A9A8RW Note: 1.The most significant bit, b7, is sent first.2.E0, E1 and E2 are compared against the respective external pins on the memory device.3.A10, A9 and A8 represent most significant bits of the address.6/297/29M24C16, M24C08, M24C04, M24C02, M24C01DEVICE OPERATIONThe device supports the I 2C protocol. This is sum-marized in Figure 5.. Any device that sends data on to the bus is defined to be a transmitter, and any device that reads the data to be a receiver.The device that controls the data transfer is known as the bus master, and the other as the slave de-vice. A data transfer can only be initiated by the bus master, which will also provide the serial clock for synchronization. The M24Cxx device is always a slave in all communication.Start ConditionStart is identified by a falling edge of Serial Data (SDA) while Serial Clock (SCL) is stable in the High state. A Start condition must precede any data transfer command. The device continuously monitors (except during a Write cycle) Serial Data (SDA) and Serial Clock (SCL) for a Start condition,and will not respond unless one is given.Stop ConditionStop is identified by a rising edge of Serial Data (SDA) while Serial Clock (SCL) is stable and driv-en High. A Stop condition terminates communica-tion between the device and the bus master. A Read command that is followed by NoAck can be followed by a Stop condition to force the device into the Stand-by mode. A Stop condition at the end of a Write command triggers the internal EE-PROM Write cycle.Acknowledge Bit (ACK)The acknowledge bit is used to indicate a success-ful byte transfer. The bus transmitter, whether it be bus master or slave device, releases Serial Data (SDA) after sending eight bits of data. During the 9th clock pulse period, the receiver pulls Serial Data (SDA) Low to acknowledge the receipt of the eight data bits.Data InputDuring data input, the device samples Serial Data (SDA) on the rising edge of Serial Clock (SCL).For correct device operation, Serial Data (SDA)must be stable during the rising edge of Serial Clock (SCL), and the Serial Data (SDA) signal must change only when Serial Clock (SCL) is driv-en Low.Memory AddressingTo start communication between the bus master and the slave device, the bus master must initiate a Start condition. Following this, the bus master sends the Device Select Code, shown in Table 2.(on Serial Data (SDA), most significant bit first).The Device Select Code consists of a 4-bit Device Type Identifier, and a 3-bit Chip Enable “Address”(E2, E1, E0). To address the memory array, the 4-bit Device Type Identifier is 1010b.Each device is given a unique 3-bit code on the Chip Enable (E0, E1, E2) inputs. When the Device Select Code is received, the device only responds if the Chip Enable Address is the same as the val-ue on the Chip Enable (E0, E1, E2) inputs. How-ever, those devices with larger memory capacities (the M24C16, M24C08 and M24C04) need more address bits. E0 is not available for use on devices that need to use address line A8; E1 is not avail-able for devices that need to use address line A9,and E2 is not available for devices that need to use address line A10 (see Figure 3. and Table 2. for details). Using the E0, E1 and E2 inputs, up to eight M24C02 (or M24C01), four M24C04, two M24C08 or one M24C16 devices can be connect-ed to one I 2C bus. In each case, and in the hybrid cases, this gives a total memory capacity of 16Kbits, 2KBytes (except where M24C01 devic-es are used).The 8th set to 1 for Read and 0 for Write operations.If a match occurs on the Device Select code, the corresponding device gives an acknowledgment on Serial Data (SDA) during the 9th bit time. If the device does not match the Device Select code, it deselects itself from the bus, and goes into Stand-by mode.Table 3. Operating ModesNote: 1.X = V IH or V IL .ModeRW bit WC 1Bytes Initial SequenceCurrent Address Read 1X 1START, Device Select, RW = 1Random Address Read 0X 1START, Device Select, RW = 0, Address 1X reSTART, Device Select, RW = 1Sequential Read 1X ≥ 1Similar to Current or Random Address Read Byte Write 0V IL 1START, Device Select, RW = 0Page WriteV IL≤ 16START, Device Select, RW = 0M24C16, M24C08, M24C04, M24C02, M24C018/29Following a Start condition the bus master sends a Device Select Code with the RW bit reset to 0.The device acknowledges this, as shown in Figure 7., and waits for an address byte. The device re-sponds to the address byte with an acknowledge bit, and then waits for the data byte.When the bus master generates a Stop condition immediately after the Ack bit (in the “10th bit” time slot), either at the end of a Byte Write or a Page Write, the internal memory Write cycle is triggered.A Stop condition at any other time slot does not trigger the internal Write cycle.During the internal Write cycle, Serial Data (SDA)and Serial Clock (SCL) are ignored, and the de-vice does not respond to any requests.Byte WriteAfter the Device Select code and the address byte,the bus master sends one data byte. If the ad-dressed location is Write-protected, by Write Con-trol (WC) being driven High (during the period frombyte), the device replies to the data byte with NoAck, as shown in Figure 6., and the location is not modified. If, instead, the addressed location is not Write-protected, the device replies with Ack.The bus master terminates the transfer by gener-ating a Stop condition, as shown in Figure 7..Page WriteThe Page Write mode allows up to 16 bytes to be written in a single Write cycle, provided that they are all located in the same page in the memory:that is, the most significant memory address bits are the same. If more bytes are sent than will fit up to the end of the page, a condition known as ‘roll-over’ occurs. This should be avoided, as data starts to become overwritten in an implementation dependent way.The bus master sends from 1 to 16 bytes of data,each of which is acknowledged by the device if Write Control (WC) is Low. If the addressed loca-ing driven High (during the period from the StartM24C16, M24C08, M24C04, M24C02, M24C01condition until the end of the address byte), the de-vice replies to the data bytes with NoAck, as shown in Figure 6., and the locations are not mod-ified. After each byte is transferred, the internal byte address counter (the 4 least significant ad-dress bits only) is incremented. The transfer is ter-minated by the bus master generating a Stop condition.9/29M24C16, M24C08, M24C04, M24C02, M24C0110/29During the internal Write cycle, the device discon-nects itself from the bus, and writes a copy of the data from its internal latches to the memory cells.The maximum Write time (t w ) is shown in Table 15. to Table 17., but the typical time is shorter. To make use of this, a polling sequence can be used by the bus master.The sequence, as shown in Figure 8., is:–Step 1: the bus master issues a Start condition followed by a Device Select Code (the first byte of the new instruction).–Step 2: if the device is busy with the internal Write cycle, no Ack will be returned and the bus master goes back to Step 1. If the device has terminated the internal Write cycle, it responds with an Ack, indicating that the device is ready to receive the second part of the instruction (the first byte of this instruction having been sent during Step 1).Read OperationsRead operations are performed independently of the state of the Write Control (WC) signal.The device has an internal address counter which is incremented each time a byte is read. Random Address ReadA dummy Write is first performed to load the ad-dress into this address counter (as shown in Fig-ure 9.) but without sending a Stop condition. Then, the bus master sends another Start condition, and repeats the Device Select Code, with the RW bit set to 1. The device acknowledges this, and out-puts the contents of the addressed byte. The bus master must not acknowledge the byte, and termi-nates the transfer with a Stop condition.Current Address ReadFor the Current Address Read operation, following a Start condition, the bus master only sends a De-vice Select Code with the RW bit set to 1. The de-vice acknowledges this, and outputs the byte addressed by the internal address counter. The counter is then incremented. The bus master ter-minates the transfer with a Stop condition, as shown in Figure 9., without acknowledging the byte.11/29Sequential ReadThis operation can be used after a Current Ad-dress Read or a Random Address Read. The bus master does acknowledge the data byte output, and sends additional clock pulses so that the de-vice continues to output the next byte in sequence. To terminate the stream of bytes, the bus master must not acknowledge the last byte, and must generate a Stop condition, as shown in Figure 9.. The output data comes from consecutive address-es, with the internal address counter automatically incremented after each byte output. After the last memory address, the address counter ‘rolls-over’, and the device continues to output data from memory address 00h.Acknowledge in Read ModeFor all Read commands, the device waits, after each byte read, for an acknowledgment during the 9th bit time. If the bus master does not drive Serial Data (SDA) Low during this time, the device termi-nates the data transfer and switches to its Stand-by mode.INITIAL DELIVERY STATEThe device is delivered with the memory array erased: all bits are set to 1 (each byte contains FFh).12/2913/29MAXIMUM RATINGStressing the device above the rating listed in the Absolute Maximum Ratings" table may cause per-manent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not im-plied. Exposure to Absolute Maximum Rating con-ditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality docu-ments.Table 4. Absolute Maximum RatingsNote: pliant with JEDEC Std J-STD-020B (for small body, Sn-Pb or Pb assembly), the ST ECOPACK ® 7191395 specification, andthe European directive on Restrictions on Hazardous Substances (RoHS) 2002/95/EU 2.JEDEC Std JESD22-A114A (C1=100pF, R1=1500 Ω, R2=500 Ω)Symbol ParameterMin.Max.Unit T STG Storage Temperature–65150°C T LEAD Lead Temperature during Soldering See note 1°C V IO Input or Output range –0.50 6.5V V CC Supply Voltage–0.50 6.5V V ESDElectrostatic Discharge Voltage (Human Body model) 2–40004000V14/29DC AND AC PARAMETERSThis section summarizes the operating and mea-surement conditions, and the DC and AC charac-teristics of the device. The parameters in the DC and AC Characteristic tables that follow are de-rived from tests performed under the Measure-ment Conditions summarized in the relevant tables. Designers should check that the operating conditions in their circuit match the measurement conditions when relying on the quoted parame-ters.Table 5. Operating Conditions (M24Cxx)Note: 1.This range is Not for New Design, and will soon be replaced by the M24Cxx-W range.Table 6. Operating Conditions (M24Cxx-W)Table 7. Operating Conditions (M24Cxx-R)Symbol ParameterMin.Max.Unit V CC Supply Voltage4.55.5V T AAmbient Operating Temperature (Device Grade 6)–4085°C Ambient Operating Temperature (Device Grade 3)–40125°CSymbol ParameterMin.Max.Unit V CC Supply Voltage2.5 5.5V T AAmbient Operating Temperature (Device Grade 6)–4085°C Ambient Operating Temperature (Device Grade 3)–40125°CSymbol ParameterMin.Max.Unit V CC Supply Voltage1.8 5.5V T AAmbient Operating Temperature–4085°C15/29Table 8. AC Measurement ConditionsTable 9. Input ParametersNote: 1.T A = 25°C, f = 400kHz2.Sampled only, not 100% tested.Table 10. DC Characteristics (M24Cxx, Device Grade 6)Note: 1.This range is Not for New Design, and will soon be replaced by the M24Cxx-Wxx6 range.Symbol ParameterMin.Max.Unit C LLoad Capacitance 100pF Input Rise and Fall Times 50ns Input Levels0.2V CC to 0.8V CC V Input and Output Timing Reference Levels0.3V CC to 0.7V CCVSymbol Parameter 1,2Test ConditionMin .Max .Unit C IN Input Capacitance (SDA)8pF C IN Input Capacitance (other pins)6pF Z WCL WC Input Impedance V IN < 0.5V 570k ΩZ WCH WC Input Impedance V IN > 0.7V CC 500k Ωt NSPulse width ignored(Input Filter on SCL and SDA)Single glitch100nsSymbol ParameterTest Condition(in addition to those in Table 5.)Min.Max.Unit I LI Input Leakage Current (SCL, SDA)V IN = V SS or V CC± 2µA I LO Output Leakage Current V OUT = V SS or V CC, SDA in Hi-Z ± 2µA I CC Supply CurrentV CC =5V , f c =400kHz (rise/fall time < 30ns)2mA I CC1Stand-by Supply Current V IN = V SS or V CC , V CC = 5V1µA V ILInput Low Voltage(E2, E1, E0, SCL, SDA)–0.450.3V CC V Input Low Voltage (WC)–0.450.5V V IH Input High Voltage(E2, E1, E0, SCL, SDA, WC)0.7V CC V CC +1V V OLOutput Low VoltageI OL = 3mA, V CC = 5V 0.4V16/29Table 11. DC Characteristics (M24Cxx, Device Grade 3)Note: 1.This range is Not for New Design, and will soon be replaced by the M24Cxx-Wxx3 range.Table 12. DC Characteristics (M24Cxx-W, Device Grade 6)Symbol ParameterTest Condition(in addition to those in Table 5.)Min.Max.Unit I LI Input Leakage Current (SCL, SDA)V IN = V SS or V CC± 2µA I LO Output Leakage Current V OUT = V SS or V CC, SDA in Hi-Z ± 2µA I CC Supply CurrentV CC =5V , f c =400kHz (rise/fall time < 30ns)3mA I CC1Stand-by Supply Current V IN = V SS or V CC , V CC = 5V5µA V ILInput Low Voltage(E2, E1, E0, SCL, SDA)–0.450.3V CC V Input Low Voltage (WC)–0.450.5V V IH Input High Voltage(E2, E1, E0, SCL, SDA, WC)0.7V CC V CC +1V V OLOutput Low VoltageI OL = 3mA, V CC = 5V 0.4VSymbol ParameterTest Condition(in addition to those in Table 6.)Min.Max.Unit I LI Input Leakage Current (SCL, SDA)V IN = V SS or V CC± 2µA I LO Output Leakage Current V OUT = V SS or V CC, SDA in Hi-Z ± 2µA I CC Supply CurrentV CC =2.5V, f c =400kHz (rise/fall time < 30ns)1mA I CC1Stand-by Supply Current V IN = V SS or V CC , V CC = 2.5V0.5µA V ILInput Low Voltage(E2, E1, E0, SCL, SDA)–0.450.3V CC V Input Low Voltage (WC)–0.450.5V V IH Input High Voltage(E2, E1, E0, SCL, SDA, WC)0.7V CC V CC +1V V OLOutput Low VoltageI OL = 2.1mA, V CC = 2.5V 0.4V。

MTC 25 CC和MTC 25C操作说明书