MC14557_IcpdfCom

IE-MiniMc 用户手册说明书

Advantech B+B SmartWorx - Americas707 Dayton RoadOttawa, IL 61350 USAPhone (815) 433-5100Fax (815) 433-5105Advantech B+B SmartWorx - European HeadquartersWestlink Commercial ParkOranmore, Co. Galway, IrelandPhone +353 91-792444Fax +353 91-792445B+B SMARTWORX TECHNICAL SUPPORTUSA/Canada: 1 (800) 346-3119 (Ottawa IL USA location)(Monday - Friday, 7:00 a.m. to 7:00 p.m. CST) Europe: +353 91 792444 (Ireland location)(Monday - Friday, 8 a.m. to 5:00 p.m. GMT) Email: ************************Web: CONTENTSB+B SMARTWORX TECHNICAL SUPPORT (i)List of Figures (ii)List of Tables (iii)FCC RADIO FREQUENCY INTERFERENCE STATEMENT (iii)WARRANTY (iv)ABOUT THE IE-MINIMC (1)HARDWARE INSTALLATION -both product lines (2)hardware mounting options (2)powering options (3)LEDS (4)DC terminal block wiring instructions (5)Cascading DC Power (5)SPECIFICATIONS (6)CERTIFICATIONS/APPROVALS (7)ELECTROSTATIC DISCHARGE PRECAUTIONS (8)FIBER OPTIC CLEANING GUIDELINES (9)CERTIFICATIONS (10)LIST OF FIGURESFigure 1. Wall Mount Bracket (2)Figure 2. DIN Rail Mounting (3)LIST OF TABLESTable 1. LEDS (4)Table 2. Specifications (6)Table 3. Certifications (7)FCC RADIO FREQUENCY INTERFERENCE STATEMENTThis equipment has been tested and found to comply with the limits for a Class B computing device, pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference in which the user will be required to correct the interference at his own expense.Any changes or modifications not expressly approved by the manufacturer could void the user’s authority to operate the equipment. The use of non-shielded I/O cables may not guarantee compliance with FCC RFI limits. This digital apparatus does not exceed the Class B limits for radio noise emission from digital apparatus set out in the Radio Interference Regulation of the Canadian Department of Communications. Le présent appareil numérique n’émet pas de bruits radioélectriquesdépassant les limites applicables aux appareils numériques de classe B prescrites dans le Règlement sur le brouillage radioélectrique publié par le ministère des Communications du Canada.WARRANTYEffective for products of B+B SmartWorx shipped on or after May 1, 2013, B+B SmartWorx warrants that each such product shall be free from defects in material and workmanship for its lifetime. This limited lifetime warranty is applicable solely to the original user and is not transferable.This warranty is expressly conditioned upon proper storage, installation, connection, operation and maintenance of products in accordance with their written specifications. Pursuant to the warranty, within the warranty period, B+B SmartWorx, at its option will:1. Replace the product with a functional equivalent;2. Repair the product; or3. Provide a partial refund of purchase price based on a depreciated value.Products of other manufacturers sold by B+B SmartWorx are not subject to any warranty or indemnity offered by B+B SmartWorx, but may be subject to the warranties of the other manufacturers.Notwithstanding the foregoing, under no circumstances shall B+B SmartWorx have any warranty obligations or any other liability for: (i) any defects resulting from wear and tear, accident, improper use by the buyer or use by any third party except in accordance with the written instructions or advice of the B+B SmartWorx or the manufacturer of the products, including without limitation surge and overvoltage conditions that exceed specified ratings, (ii) any products which have been adjusted, modified or repaired by any party other than B+B SmartWorx or (iii) any descriptions, illustrations, figures as to performance, drawings and particulars of weights and dimensions contained in the B+B SmartWorx’ catalogs, price lists, marketing materials or elsewhere since they are merely intended to represent a general idea of the products and do not form part of this price quote and do not constitute a warranty of any kind, whether express or implied, as to any of the B+B SmartWorx’ products.THE REPAIR OR REPLACEMENT OF THE DEFECTIVE ITEMS IN ACCORDANCE WITH THE EXPRESS WARRANTY SET FORTH ABOVE IS B+B SMARTWORX’ SOLE OBLIGATION UNDER THIS WARRANTY. THE WARRANTY CONTAINED IN THIS SECTION SHALL EXTEND TO THE ORIGINAL USER ONLY, IS IN LIEU OF ANY AND ALL OTHER WARRANTIES, EXPRESS OR IMPLIED, AND ALL SUCH WARRANTIES AND INDEMNITIES ARE EXPRESSLY DISCLAIMED, INCLUDING WITHOUT LIMITATION (I) THE IMPLIED WARRANTIES OF FITNESS FOR A PARTICULAR PURPOSE AND OF MERCHANTABILITY AND (II) ANY WARRANTY THAT THE PRODUCTS ARE DO NOT INFRINGE OR VIOLATE THE INTELLECTUAL PROPERTY RIGHTS OF ANY THIRD PARTY. IN NO EVENT SHALL B+B SMARTWORX BE LIABLE FOR LOSS OF BUSINESS, LOSS OF USE OR OF DATA INTERRUPTION OF BUSINESS, LOST PROFITS OR GOODWILL OR OTHER SPECIAL, INCIDENTAL, EXEMPLARY OR CONSEQUENTIAL DAMAGES. B&B ELECTRONIC SHALL DISREGARD AND NOT BE BOUND BY ANY REPRESENTATIONS, WARRANTIES OR INDEMNITIES MADE BY ANY OTHER PERSON, INCLUDING WITHOUT LIMITATION EMPLOYEES, DISTRIBUTORS, RESELLERS OR DEALERS OF B+B SMARTWORX WHICH ARE INCONSISTENT WITH THE WARRANTY, SET FORTH ABOVE.ABOUT THE IE-MINIMCThe IE-MiniMc Industrial Ethernet media converter features 10/100 switching copper-to-fiber conversion. Miniature in size, it offers plug-and-play operation, and supports an extended voltage range as well as extended operating temperature.. The media converter can function as a PD device, and is compliant to the IEEE 802.3af Power Over Ethernet (PoE) standard. Available in a variety of Single Mode and Multi Mode fiber types, it supports an MTU of 1916 bytes. Several mounting options and powering options are available and detailed in the following sections of the manual.HARDWARE INSTALLATION -BOTH PRODUCT LINES The IE-MiniMc installs virtually anywhere as a standalone device in locations with extremely limited space. Installation options include:·Velcro strips·DIN rail mounting with DIN Rail clips· A wall mount bracket· A PowerTray/18 for high density applicationsHARDWARE MOUNTING OPTIONSThe IE-MiniMc can be mounted on a DIN rail or using wall mount brackets (shown below).Figure 1. Wall Mount BracketDIN rail clips (part number 806-39105) and wall mount brackets (part number 895-39229) are available for purchase through an B&B Electronics Distributor. The DIN Rail clips include screws, to allow the installation onto a DIN Rail. Install the screws into DIN Rail clips, which should be mounted parallel or perpendicular to the DIN Rail. Snap the converter onto the clips. To remove the converter from the DIN Rail, use a flat-head screwdriver into the slot to gently pry the converter from the rail.Figure 2. DIN Rail MountingPOWERING OPTIONSThe IE-MiniMc includes multiple powering options:· A country-specific, high-reliability AC power adapter (included)·The IEEE 802.3af Power over Ethernet standard; draws power from power sourcing equipment (NON-Telco version only)·The 4-terminal DC power block·IE-PowerTray/18 for Rack MountingPower Over EthernetPower Over Ethernet technology allows the IE-MiniMc to be a Powered Draw device (PD) and draw power when connected to Power Sourcing Equipment (PSE). Power Sourcing Equipment distributes an electrical current across existing copper data cabling.LEDSEach IE-MiniMc includes two LEDs, located on the RJ-45 connector.LED functions are as follows:FXLNK/ACT Glows green when a link is established on the fiber port; blinks green when activity is detected on the fiber port.TXLNK/ACT Glows amber when a link is established on the copper port; blinks amber when activity is detected on the copper port.Table 1. LEDSDC TERMINAL BLOCK WIRING INSTRUCTIONSThe IE-MiniMc can also be powered with the DC terminal block. From a power source, connect to any one positive and any one negative terminal on the IE-MiniMcFigure 3. DC Terminal BlockNOTEWhen using stranded wire, the leads must be tinned and equivalent to a 16 AWG solid conductor. The DC terminal block is protected against mis-wiring. If the unit is mis-wired, positive power lead to the negative terminal and negative power lead to the positive terminal, it will not function. When powering a unit with voltages near the upper limit of the device’s specification (for example: 50 volts) take precautions to limit the voltage at the units terminal block. When turning on high voltage DC circuits, initial voltages may exceed the maximum allowed duration of the unit’s transient protection devices.Cascading DC PowerWhen installing multiple IE-MiniMc units on a DIN rail, the end user can connect to one DC input source, and then cascade from one DC block to the next, until reaching the maximum current available.SPECIFICATIONSConnectorsCopper RJ-45Fiber ST, SCEnvironmental -- Intended for indoor and outdoor use.Operating Temperature -40°F to +185°F (-40°C to +85°C) DC configuration +14°F to +122°F (-10°C to +50°C) with AC wall adapterStorage Temperature-40°F to +185°F (-40°C to +85°C)Operating Humidity 5 to 95% (non-condensing); 0 to 10,000 ft. altitude LED Indicators One Green LEDCopper RJ-45 port LNK/ACT Color = GREENBlink = GREEN when data is passing Off = NO COLORFiber Port LNK/ACT Color = AMBERBlink = AMBER when data is passing Off = NO COLORPower InputDC Terminal Block 7 to 50 VDC, 1-0.1ADC jack 5 to 24 VDCPoE When IE-MiniMc uses PoE technology to be a PD,the maximum supply voltage is 50VTable 2. SpecificationsCERTIFICATIONS/APPROVALSCertificationsFCC FCC Part 15 Class BCEEN55022 CISPR 22 Class BEN61000-3-2 Generic Standards for Residential, Commercial, & Light IndustrialEN61000-4-2 ESD (15kV air & 4kV contact)EN61000-4-3 RFIEN61000-4-4 EFTEN61000-4-5 SurgeEN61000-4-6 CIEN61000-4-8 Power Frequency MagneticVoltage Dips & InterruptionsEN61000-4-11Regulatory ApprovalsROHS and WEEE CompliantTable 3. CertificationsELECTROSTATIC DISCHARGE PRECAUTIONS Electrostatic discharge (ESD) can cause damage to any product, add-in modules or stand-alone units, containing electronic components. Always observe the following precautions when installing or handling these kinds of products:Do not remove unit from its protective packaging until ready to install. Wear an ESD wrist grounding strap before handling any module or component. If the wrist strap is not available, maintain grounded contact with the system unit throughout any procedure requiring ESD protection. Hold the units by the edges; do not touch the electronic components or gold connectors.After removal, always place the boards on a grounded, static-free surface, ESD pad or in a proper ESD bag. Do not slide the modules orstand-alone units over any surface. WARNING! Integrated circuits and fiber optic components are extremely susceptible to electrostatic dischargedamage. Do not handle these components directly unless you are a qualified service technician and use tools andtechniques that conform to accepted industry practices.FIBER OPTIC CLEANING GUIDELINESFiber optic transmitters and receivers are extremely susceptible to contamination by particles of dirt or dust, which can obstruct the optic path and cause performance degradation. Good system performance requires clean optics and connector ferrules.Use fiber patch cords (or connectors, if you terminate your own fiber) only from a reputable supplier; low-quality components can cause many hard-to-diagnose problems in an installation.Dust caps are installed at B+B SmartWorx to ensure factory-clean optical devices. These protective caps should not be removed until the moment of connecting the fiber cable to the device. Should it be necessary to disconnect the fiber device, reinstall the protective dust caps.Store spare caps in a dust-free environment such as a sealed plastic bag or box so that when reinstalled they do not introduce any contamination to the optics.If you suspect that the optics have been contaminated, alternate between blasting with clean, dry, compressed air and flushing with methanol to remove particles of dirt.CERTIFICATIONSCE: The products described herein comply with the Council Directive on Electromagnetic Compatibility (2004/108/EC). For further details, contact B+B SmartWorx.European Directive 2002/96/EC (WEEE) requires that any equipment that bears this symbol on product or packaging must not be disposed of with unsorted municipal waste. This symbol indicates that the equipment should be disposed of separately from regular household waste. It is the consumer’s responsibility to dispose of this and all equipment so marked through designated collection facilities appointed by government or local authorities. Following these steps through proper disposal and recycling will help prevent potential negative consequences to the environment and human health. For more detailed information about proper disposal, please contact local authorities, waste disposal services, or the point of purchase for this equipment.____________________________________________________© 2017 B+B SmartWorx. All rights reserved. The information in this document is subject to change without notice. B+B SmartWorx assumes no responsibility for any errors that may appear in this document. IE-MiniMc is a trademark of B+BSmartWorx. Other brands or product names may be trademarks and are the property of their respective companies.Document #: 55-80722-00-A8_1017。

MC14550中文资料

自适应差值脉冲编码(ADPCM)芯片MC14550一、典型参数1、单一供电方式:~2、低功耗:5V时,150mW 功耗下降3V时,65mW 功耗下降3、低噪声:有差分模拟电路。

4、u律/A律压扩PCM编译码/滤波器电路5、三种速率选择(32、24、16kbit/s)、四种算法ADPCM CODEC完全满足G721、723、726和G714的PCM性能。

6、通用可编程双音频发生器。

7、可编程,发送增益调整,接收增益调整与侧音增益调整。

8、可直接与话简接口的低噪声,高增益的三端输入运算放大器电路。

9、可直接与与扬声器接口,推挽300Ω负载阻抗。

10、可提供振铃接口的推挽300Ω的驱动电路。

11、可提供降功耗方式,3V电源输入数字信号处理电路5V电源输入模拟信号处理电路12、在接收端具有噪声突发检测算法13、有串行控制口和监控内存,可实现微计算机控制二、引脚图三、逻辑图四、管脚功能简介第1引脚(TG-Transmit Gain):发送增量控制。

由第2引脚(TI-)和第3引脚(TI+)输入的音频模拟信号经输入运放后从该端输出。

该端实质上是发送滤波器的输入端。

这是设定运算放大器发送增益的输出和输入到发送带通滤波器。

此运算放大器能驱动2K Ω负载到V AG引脚。

当TI_和TI+连到V DD时,TG运算放大器掉电,TG引脚变成高阻抗,输入到发送放大器。

此引脚上的所有信号以V AG引脚为基准。

当器件是在模拟掉电方式下时,此引脚是高阻抗。

此运算放大器由V DD引脚加电。

第2引脚(TI_Transmit Analog Inverting Input):模拟运算放大器反相输入端。

音频模拟信号通过该端进入模拟运放。

这是发送增益设定运算放大器的反相输入。

增益设定电阻通常从此引脚连到TG和从此引脚到模拟信号源。

TI+和TI_引脚的工模范围从1.0V到-2V。

连接此引脚和TI+(引脚3)到V DD 将置此放大器的输出(TG)于高阻抗状态,这样,允许TG引脚作为发送滤波器的高阻抗输入。

XHS151114SW47P42-01 A2

SPECIFICATIONMICRO SPEAKERCUSTOMER:Haosheng P/N:XHS151114SW47P42-01CUSTOMER P/N:DATE: 2015-9-19APPROVER CHECKER DESIGNERCUSTOMER APPROVERSIGNATURE DATEJIASHAN HAOSHENG ELECTRONIC CO.,LTD.Add:HaoSheng Technology Building,NO.328,Huimin,Jiashan,Zhejiang,P.R.China 314112TEL:86-573-84645930 84646197Fax:86-573-84646190E-mail: services@.TEL:86-573-84645930 、84646197FAX:86-573-84646190TYPE NO.XHS151114SW47P42-01 Issue:A/2E-mail: services@.EnvironmentalHF RoHS√REACHRequirementRevisionNo Date Page Description Signupdate Lzm 12015.9.18 6/15SPECupdate Lzm2/15SPEC2 2015.9.19Table of ContentsNo.Item Page1Product Outline 2/152Electroacoustic Characteristics 2/153General Reliability 3/154 Mechanical Layout and Dimensions 4,5,6,7/15Setup 8/155 MeasuringFrequency 9/156 ResonanceResponse 10/157 Frequency8 Total Harmonic Distortion 11/159 ApplicationNote 12,13,14/1510 Package 15/15TEL:86-573-84645930 、84646197FAX:86-573-84646190E-mail: services@.TYPE NO.XHS151114SW47P42-01 Issue:A/2 1. Product Outline1-1. Scope This specification is a typical speaker unit for telephone handset1-2. Dimensions As shown in figure 11-3. Net Weight Approx 1.3 grams1-4. Operating TemperatureRange-30°C to +70°C without loss of function1-5. Storage TemperatureRange-40°C to +85°C (Note: Return to ambient room temperature before using) 2. Electroacoustic Characteristics2-1. Test Setup Measuring instrument as shown in Figure 72-2. Impedance DC:7.2 ± 15% ohmAC:8 ± 15% ohm ( at 2.5 KHz,1V input )2-3.Sound Pressure Level 89.5±3dB SPL /0.7W/10cm at 3kHz in 1cc boxSpeaker shall be mounted in a baffle with minimum dimensions of 80cm x 100cm. See Figure 8.2-4.Frequency Response See Figure 11, Table 1Test at 2.36V/10 cm with the speaker mounted in 1cc measure box in a baffle.2-5. Resonance Frequency 800±15% Hz in 1cc Box. See Figure 102-6. Input Power (Rated. /Max.) Rated Power: 0.7W (in 1cc box) Maximum Power: 1.0W (in 1cc box)2-7.Rub and Buzz The input power shall be set at 0.7W. Using an audio oscillator, sweep from300 to 5000 Hz with the speaker mounted in 1cc measure box and in a baffle.There shall be no buzzes, rattles, nor spurious noises.2-8.THD See Figure12 , Table 2Test at0.7W/10 cm with the speaker mounted in 1cc measure box in a baffle.2-9.Polarity When a DC source’s “+” polarity is attached to speaker’s “+” polarity,“-“ polarity is attached speaker’s “-“ polarity ,the membrane will move forward .(Figure 4)4.6 Date Code(Figure 6)TEL:86-573-84645930 、84646197FAX:86-573-84646190TYPE NO.XHS151114SW47P42-01 Issue:A/2 E-mail: services@.5. Measuring Setup(Figure 7)(Figure 8)TEL:86-573-84645930 、84646197FAX:86-573-84646190TYPE NO. XHS151114SW47P42-01 Issue:A/2 E-mail: services@.6. Resonance Frequency(Figure 9)(Figure 10)TEL:86-573-84645930 、84646197FAX:86-573-84646190TYPE NO.XHS151114SW47P42-01 Issue:A/2 E-mail: services@.7. Frequency Response(Figure 11)Table 1:Tolerance Limits Data for FRFrequency(Hz) Upper Limits(dB)Frequency(Hz) Lower Limits(dB)30078 3006778098 85088120098 100090250092.5 225086.5450094 4500867000101 80008810000110TEL:86-573-84645930 、84646197FAX:86-573-84646190TYPE NO.XHS151114SW47P42-01 Issue:A/2 E-mail: services@.8. Total Harmonic Distortion(Figure 12)Table 2: Limits Data for THDFrequency(Hz) Limits300 40400 35500 25700 101000 102000 58000 5TEL:86-573-84645930 、84646197FAX:86-573-84646190TYPE NO.XHS151114SW47P42-01 Issue:A/2E-mail: services@.9. Application Note1.Air tight is needed between front cover of speaker and housing, otherwise cause audioperformance's losing, such as higher THD, lower sensitivity;2.Tiny air leakage in back of speaker is permitted to keep balance of air pressure;3.For this speaker, the standard power is 0.7W in 1cc back cavity, when the back cavity is less ormore than the standard volume of back cavity, the handling power also will be changed. See below figure about the relationship between power handling and back volume, here the power is excursion limited power; the thermal power should be evaluated, especially in small back cavity, such as 0.5cc. And the recommend minumum back volume is 0.5cc.4.If the power higher than 0.7W input the speaker in standard back cavity, there is the risk ofdamaging speaker. In case of the back volume larger than 1cc, i.e. 1.5cc, the power handing of the speaker is pretty low. To maintain the rated power as 0.7W, we suggest adding thicker mesh with more acoustic resistance on the cover to reduce the vibration amplitude, or using electric filter to attenuate the maximum vibration amplitude.(Figure 13)TEL:86-573-84645930 、84646197FAX:86-573-84646190TYPE NO.XHS151114SW47P42-01 Issue:A/2E-mail: services@.5.Resonance frequency VS sealed back volumeT he resonance frequency of the speaker box will vary with different sealed back volume.(Figure 14)6. T/S parametersThiele-Small Parameters: The following Thiele-Small Parameters are guidelines from a speaker exhibiting good audio performance.Fs 431.4 HzRe 7.17 ohmsSd 1.08 cm^2Bl 0.642 T.mVas 2.8 ccCms 1.696 mm/NMms 80 mgQms 2.619Qes 3.779Qt 1.547TEL:86-573-84645930 、84646197FAX:86-573-84646190TYPE NO.XHS151114SW47P42-01 Issue:A/2 E-mail: services@.7.Peak to peak excursionXp-p in different power input(Figure 15)。

ICDPPCNEXUS MPC55xx MPC56xx In-Circuit Debugger

ICDPPCNEXUSMPC55xx / MPC56xx In-Circuit DebuggerQuick Start GuideCopyright 2009, P&E Microcomputer Systems, Inc. All rights reserved.Visit us on the web at Document Version HistoryVersion Date Notes1.0 21 Sep 2009 Initial versionCONTENTS1 Introduction (4)1.1 P&E Compatible Hardware (4)2 Getting Started (5)2.1 Connecting to your Target (5)2.2 Reset Script (6)2.3 Loading Data and Debug Information (7)2.4 CPU and Memory Windows (8)3 Debugging (10)3.1 GOTIL command (10)3.1 Stepping through C instructions (11)3.3 Setting and Reaching Breakpoints (12)3.4 Using Code Window Popup Debug Evaluation Hints (13)3.5 Using the Variables Window (15)3.6 Modifying a Variable (16)3.7 Using the Register Interpreter (17)3.8 Adding Register Field Descriptions to the Variables Window (20)1 IntroductionThis document is a step-by-step guide to using the P&E ICDPPCNEXUS in-circuit debugger software, which is compatible with Freescale MPC55xx / MPC56xx processors. This guide covers the most commonly used features of the debugger: loading binary & debug information, accessing CPU registers & memory, stepping code, setting breakpoints, and monitoring variables.1.1 P&E Compatible HardwareThe following lists the P&E hardware compatible with the ICDPPCNEXUS debugger software.P&E Part Number Interface to host PCCABPPCNEXUS Parallel (LPT) portUSB-ML-PPCNEXUS USB 2.0 (Backwards compatible with USB 1.1 ports) Cyclone MAX Serial (RS232) portUSB 1.1 (Upwards compatible with USB 2.0 ports)Ethernet2 Getting Started2.1 Connecting to your TargetUpon starting the debugger, the connection assistant dialog appears:•Use the “Interface” and “Port” drop-down menus to choose the P&E hardware interface connected between the PC and your target board.•The “Target CPU” setting can safely be left at the “Autodetect” setting for most users. If you experience problems connecting, you can try specifying the exact Freescale device that you are connecting to.• A BDM_SPEED parameter between 2 to 4 can typically be used.Processors running at slower clock speeds will require higher values.Click the Connect button, and ICDPPCNEXUS will attempt to contact the processor. Using the default debugger settings, ICDPPCNEXUS will establish communications and reset the processor.After establishing communications, the main debugger screen will appear, and a debugger reset script macro should automatically execute and complete.2.2 Reset ScriptThis section explains the initialization that the debugger, using a reset script macro file, performs on the processor. The user can view and modify all of the macro file's initialization tasks.The processor Boot Assist Module (BAM) would normally initialize the memory of the processor. However, when running the target application from the debugger, the BAM functionality is disabled. To account for this, the debugger must run a script file on reset. The script initializes the memory of the processor similar to the way in which the BAM would initialize the processor.If ICDPPCNEXUS is launched from the Freescale CodeWarrior IDE, the correct reset script file is automatically selected.If ICDPPCNEXUS is launched stand-alone, the reset script file may need to be configured. Several reset script macros are included with the ICDPPCNEXUS debugger and have a .mac extension. For detailed information, you can view each macro file using a simple text editor such as Notepad. The macro contents will contain useful comments, such as which devices are supported by that particular macro.To configure the debugger reset script macro, select the debugger Configuration menu, Automated Script Options dialog, shown here:2.3 Loading Data and Debug InformationIf ICDPPCNEXUS is launched from the Freescale CodeWarrior IDE, your code will automatically be downloaded to the processor.•RAM projects are loaded into the processor’s internal SRAM.•FLASH projects will invoke the CPROGPPCNEXUS Flash programming software to burn the code into the processor’s internal FLASH.The debug information is also automatically loaded from CodeWarrior, which will allow you to debug using your high level source code and variables.If ICDPPCNEXUS is launched stand-alone, you will need to manually download the code and debug information. Launch the Load Dialog by clicking on the High Level Load button on the debugger tool bar:This dialog allows you to specify the binary/debug file and whether to load into RAM or FLASH. Once you are satisfied with your settings, press the “Process Load Command” button to begin the download process. This step will also load the debug information.2.4 CPU and Memory WindowsThe CPU Window displays all CPU core registers, including the Program Counter (PC) and all general purpose registers.•To modify CPU register contents, double-click the register value. You will be prompted for a new value.The Memory Window displays data at any given memory address. It can be used to view RAM contents, FLASH contents, and values of peripheral registers.•To change the memory address, right-click inside the Memory Window and select “Set Base Address”. You will be prompted for a new address to begin displaying data.•To change the contents in memory, double-click the value in memory that you would like to change. You will be prompted for a new value.3 DebuggingThis section outlines the different debugging capabilities available in the ICDPPCNEXUS debugger once the debug information has been loaded.3.1 GOTIL commandAt this point, your source window will show the assembly language startup code generated by the compiler:If you do not need to debug this section and would like to run the processor until the beginning of your “main” function, you can use the “GOTIL” command.•Type “GOTIL main” in the Status window to tell the debugger to run code until it reaches the “main” function of your code.The “GOTIL” command works with any function in your code.3.1 Stepping through C instructionsStep through the initialization code, or any source code, using the high-level language source step command. Use this feature by typing “HSTEP” in the Status window or by clicking the high-level step button on the debugger tool bar:Each time the HSTEP command executes, the debugger will rapidly single step assembly instructions until it encounters the next source instruction, at which point target execution will cease. When the debugger reaches the next source instruction, all visible windows will be updated with data from the board. After reaching the main function, step through several C language instructions. Notice that some instructions will take longer to step through than others because each C instruction may consist of a greater or fewer number of underlying assembly instructions.3.3 Setting and Reaching BreakpointsIn the source code window, there will be a small red dot and a small blue arrow next to each source instruction that has underlying object code. If a large blue arrow appears on a source line, this indicates that the program counter (PC) currently points to this instruction. If a large red stop sign appears on the source line, this indicates that a breakpoint exists on this line.•Set a breakpoint at an instruction by double-clicking the tiny red dot.•To remove a breakpoint, double-click the large red stop sign.Execution will begin in real-time when you issue the HGO command or click the high-level language GO button on the debugger tool bar:If the debugger encounters a breakpoint, execution will stop on this source line. If it does not encounter a breakpoint, target execution will continue until you press a key or use the stop button on the debugger tool bar:•By double clicking the small blue arrow, you will be issuing a GOTIL command to the address of this source line.A GOTIL command will set a single breakpoint at the desired address, and the processor will begin executing code in real-time from the current program counter (PC). When the debugger encounters the GOTIL address, execution stops. If the debugger does not encounter this location, execution continues until you press akey or use the stop button on the debugger tool bar. Note that all user breakpoints are ignored when the GOTIL command is used.You may also double-click the red and blue symbols in the disassembly window. The disassembly window may display an additional symbol, a small, blue "S" enclosed in a box. This indicates that that a source code instruction begins on this disassembly instruction.3.4 Using Code Window Popup Debug Evaluation HintsWhen debugging source code, it is convenient to view the contents of a variable while viewing your source code. The in-circuit debugger has a feature, debug hints, which displays the value of a variable while the mouse cursor is held over the variable name. The hint may be displayed in any of three locations, as shown below.The three locations for the debug hints are the code window title bar, the status window caption bar, and a popup hint that appears over the variable in source code. You can configure the hints to display in any combination.•Set the locations of debug hints in the configuration menu of the debuggerThe information in the popup hint box is similar to the information displayed in the variables window.The information includes the variable name (i), value ($1), and type (signed long).3.5 Using the Variables WindowThe variables window displays the current value of application variables. The following window shows a display of variables from the example application.Variables that are pointer or reference types are displayed in red. Normal variables are displayed in black.•Add a variable by typing the VAR command, by right clicking the variables window and choosing “Add a variable”, or by hitting the "Add Variable"button in the variables window.When adding a variable using the pop-up menu, the debugger displays the following screen.In the variable field, type the address or name of the variable. Typically, set the type of the variable to “Default”, which means that the variable will be displayed as it is defined in the debugging information. When adding a variable, you may specify the numeric display base of the variable.3.6 Modifying a Variable•To modify the current value of a variable, right-click the variable name in the variables window and select “Modify Variable” to display a dialog.Check the “Modify value” checkbox, and type the variable’s new value. After you click the OK button, the debugger updates the variable value on the target, and the debugger refreshes the variable window to display the new value. Note that the debugger will not edit certain user-defined types, such as enumerated types.•You may also modify a variable’s display properties, such as the type or numeric display base using this dialog.3.7 Using the Register InterpreterThe register interpreter provides a descriptive display of bit fields within the processor’s peripheral registers. The register interpreter allows you easily to change the value of these registers. You may quickly check the current state of a peripheral and examine the configuration of the target device.When you use the register interpreter within the debugger, it reads the current value of the peripheral register, decodes it, and displays it.To launch the register interpreter in the debugger, either use the “R” command or click the view/edit register button on the tool bar:A window will appear that allows you to select a peripheral block to examine.Double clicking the module of choice will launch the register selection window.Double clicking a specific register will launch the edit/display window for that register.The window lists the keystrokes and mouse actions, allowing you to modify the values of each of the fields. After right clicking on a specific field, the register interpreter will display all options for that field.When you quit the register view/edit window by hitting the ESC key, you will be given the opportunity to write the new value into the register, as shown in the following window.3.8 Adding Register Field Descriptions to the Variables WindowAdd register bit fields to the variables window by using the “_TR” command in the debugger or by clicking the "Add Register" button in the variables window. After selecting the register field, the field appears in the debugger variables window, and the debugger will continually update its value.。

用MC145572进行ISDN BRIU接口设计

2 用 MC1 7  ̄5 2设 计 B I R U接 口

本 人 在 设 计 ID B I 接 口 中 使 用 了 S N R U

瑚 2÷ l 2 8I l 3_

无 戴 电 鱼 雷 拭 术

2 7

维普资讯

R U接 口设 计 15 7 S NB I

左 军 瑞

( 电子 第 5 4研 究 所

捕要

关键 词

石 家 庄  ̄ oo ) o 2

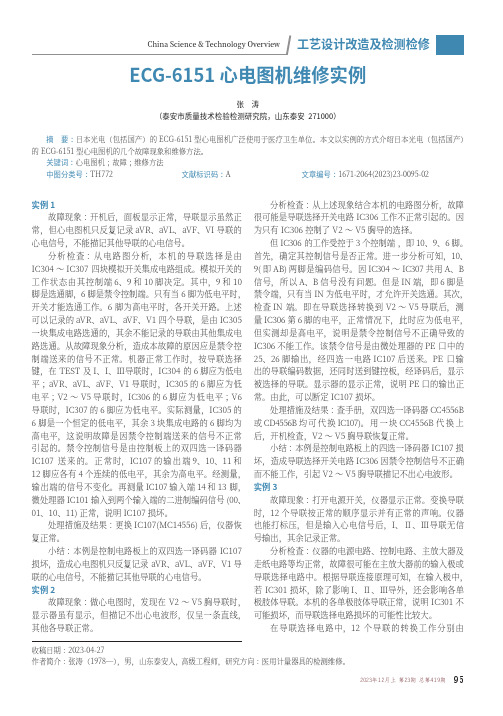

主要介 绍采 用摩托 罗拉, 司的 u接 口收发器芯片 M 1 7 ^ 、 C@52实现 ID l S NB H U接 口的设计 方案 , 并结合

U接 口就 是指 在 U参 考 点 上 的 ID S N物 理 接人 点 , 于 和 N 1 一类 网络终端 ) 问。它通 过 一 位 T( 之

对 双绞线 , 供 l bCs 提  ̄ki 速率 的全双 工 数 字信 号 传 输 , 中 包括 两个  ̄k i 其 bCs的 B 话 音 ) 道 和 一 个 ( 通

口, 双工 操 作 , 过 S P 将 控 制 和 状 态信 息 传 出 全 通 C,

或 传人 M 157 。S P与 M c 6 C 4 52 C P 8 o的 s I串行 外 部 P( 接 口) 全 兼 容 , 此 可 以使 用 MP S 的 S I 完 因 C ̄ P 对 MC4 52进 行 控 制 。 这 时 M C  ̄ 是 主 控 者 , 157 P8 而

基本 的一 种用 户接 口方式 , R ( 本 速 率 接 口) 也 B I基 , 应用得越 来越 广泛 。 所示 , 中 E : 图 T 交 换 终 端 ( 换 机 ) 交 ,

: 线 路终 端 , T : N 1 网络终 端 1 仅 O I ( S 第 一 层 ) N : 络 , 网

GE Fanuc RX3i PACSystem IC695CMM004 四通道串行通信模块说明书

Rx3i PacSystem919-535-3180*******************GE Fanuc IC695CMM004/automation/ge-fanuc/rx3i-pacsystem/IC695CMM004RX3i serial communications module. Four isolated RS-232/485 port.IC695C IC695CM IC695CMMPACSystems™ RX3iIC695CMM002 and IC695CMM004 GFK-2461B Serial Communications Modules August 2007communications capabilities of the RX3i system.in the main PACSystems RX3i backplane.module can only be configured for DNP3 Master or Slave.Additional module features include:▪Port-to-port isolation and port-to-backplane isolation▪▪Hardware handshake: RTS/CTS for RS-232▪57.6K, 115.2K▪▪indicators▪▪Flash memory for future upgradesThese modules must be located in an RX3i Universal Backplane.RX3i Serial Communications can be hot-inserted and removedfollowing the instructions in the PACSystems RX3i System Manual,GFK-2314.2 RX3i Serial Communications Modules GFK-2461BRelease InformationThis release is an upgrade of previous version 1.10.Release HistoryRelease UpgradeKitCommentsIC695CMM002-AA IC695CMM004-AA N/A InitialReleaseIC695CMM002-AB IC695CMM004-AB 44A753277-G0244A753278-G02Supports CCM Slave ProtocolIC695CMM002-AC IC695CMM004-AC 44A753277-G0344A753278-G03Supports DNP3 Master and DNP3 Slave ProtocolNew for this ReleaseThis release of the RX3i Serial Module adds support for Distributed Network Protocol 3.0 Master and Slave to the other protocols: MODBUS Master/Slave, CCM, and Serial I/O. This module does not operate with COMMREQs but rather uses preconfigured mappings of the I/O reference memory.MODBUS Master and MODBUS Slave Protocols now support the configuration of 1 stop bit, for compatibility with some GE Fanuc Automation MODBUS Slaves.CompatibilityProgrammer: Proficy® Machine Edition Logic Developer 5.6 with Service Pack 2 SIM 10RX3i CPU: PACSystems RX3i CPU Version 5.00 or later is required to be able to use the timesynchronization feature on a DNP3 Master port.Problems Resolved for This ReleaseWhen parity is set to none in the port configuration for the Modbus Master or Modbus Slave protocols, the stop bits were forced to 2. This restriction has now been removed and the stop bits can be set to 1 or 2.RX3i Serial Communications Modules 3GFK-2461BRestrictions and Open Issues in this Release1. When multiple group objects (i.e. %I and %AI memory) are read in a single request, the DNP3 port willignore all but the first object. Operations of multiple group objects should be split into multiple successiveexchanges (i.e. exchange 1 - %I, exchange 2 - %AI).2. The DNP3 slave port has problems using the link layer to validate frame receipt. The DNP3 organizationencourages users not to do this.3. These modules do not support GE Fanuc special MODBUS commands for use with a Daniels FlowComputer.4. PLC Reference Address and Reference Length Parameters do not support bit length/start. Bit and Non-Byte Length operations must begin on a byte boundary.5. When a port is configured for CCM Slave protocol, and:▪ a new configuration is stored to the PLC using Machine Edition, or▪the system is power-cycled, or▪the module is hot-inserted,if the first query received from the CCM Master is a Read Scratchpad request, the module will reject thatrequest. All subsequent Read Scratchpad requests will be successful unless one of the above conditionsoccurs again.Operating NotesThe maximum resolution for the MODBUS drop delay is 420us, so the minimum time for a drop delay is 420us.Installation in Hazardous Locations•EQUIPMENT LABELED WITH REFERENCE TO CLASS I, GROUPS A, B, C & D, DIV. 2 HAZARDOUSLOCATIONS IS SUITABLE FOR USE IN CLASS I, DIVISION 2, GROUPS A, B, C, D OR NON-HAZARDOUSLOCATIONS ONLY•WARNING - EXPLOSION HAZARD - SUBSTITUTION OF COMPONENTS MAY IMPAIR SUITABILITY FOR CLASSI, DIVISION 2;•WARNING - EXPLOSION HAZARD - WHEN IN HAZARDOUS LOCATIONS, TURN OFF POWER BEFOREREPLACING OR WIRING MODULES; AND•WARNING - EXPLOSION HAZARD - DO NOT CONNECT OR DISCONNECT EQUIPMENT UNLESS POWER HASBEEN SWITCHED OFF OR THE AREA IS KNOWN TO BE NONHAZARDOUS.4 RX3i Serial Communications ModulesGFK-2461BSpecifications: IC695CMM002 and IC695CMM004Refer to the PACSystems RX3i System Manual , GFK-2314, for product standards and general specifications.Number of Serial PortsIC695CMM002: two independent serial ports IC695CMM004: four independent serial portsConnectors RJ-45 Number of Serial Communications Modules per CPU Six in the main CPU backplaneIC695CMM002 ********************************************Backplane power requirementsIC695CMM004********************************************LEDs Module OK, Port Fault, Port Status (2 or 4)Port TypeRS-232 or RS-485/22. 4-wire (full duplex) or 2-wire (half-duplex) operation for RS-485/422Flow Control for R-232 Selectable: Hardware (CTS/RTS) or noneBaud rates 1200, 2400, 4800, 9600, 19.2K, 38.4K, 57.6K, 115.2k Parity Even, odd, noneData bits 7, 8 Stop bits1, 2Operating Temperature 0°C to + 60°CInput Impedance Zin > 96 kOhm for RS-485/422 3 kOhm < Zin < 7 kOhm for RS-232 Max Overvoltage +/- 25VChannel-Channel Crosstalk –55dB minimumIsolationPort to Backplane and to frame ground: 250 VAC continuous; 1500 VAC for 1 minute, 2550VDC for one second. Port to port: 500VDC continuous, 710VDC for one minute.In order to meet emission and immunity requirements for the EMC directive (CE mark), shielded cable must be used with this module.RX3i Serial Communications Modules 5GFK-2461BLEDsSerial PortsEach port is a standard RJ-45 female connector with the following pin assignments. For MODBUS applications,note that these pin assignments are different than the standard MODBUS pin assignments. If the port isconfigured for MODBUS master or slave operation, custom cables are needed.6 RX3i Serial Communications Modules GFK-2461BIf the Serial Communications module is communicating with a Series 90-30 CPU363 or external PACSystemsRX3i CPU, the connections are:RX3i Serial Module CPU363/RX3iRD('B')T+ ToT- ToRD('A')SD('B')R+ ToSD('A')R- ToTerminationBy default, each port is set for no termination. Termination is needed if the module is the first or last device on an RS-485 network, even if there is only one other device on the network. Termination can be provided using either an external resistor as shown below or the port’s built-in 120-Ohm termination. If line termination other than 120 Ohms is required, an appropriate external resistor must be supplied.User-Supplied Termination for RS-485Termination using the built-in 120-Ohm resistor can be provided by either setting the appropriate RS-4851. Remove the module’s faceplate by pressing in on the side tabs and pulling the faceplate away from themodule.2. With the module oriented as shown, move either the upper or lower jumper:。

CS5532-BSZR;CS5534-BSZR;CDB5532U;中文规格书,Datasheet资料

Copyright © Cirrus Logic, Inc. 2008CS5532/34-BS24-bit ∆Σ ADCs with Ultra-low-noise PGIAFeaturesChopper-stabilized PGIA (ProgrammableGain Instrumentation Amplifier, 1x to 64x)– 6 nV/√Hz @ 0.1 Hz (No 1/f noise) at 64x –1200pA Input Current with Gains >1 Delta-sigma Analog-to-digital Converter –Linearity Error: 0.0007% FS–Noise-free Resolution: Up to 23 bits Two- or Four-channel Differential MUX Scalable Input Span via Calibration –±5 mV to differential ±2.5VScalable V REF Input: Up to Analog Supply Simple Three-wire Serial Interface –SPI™ and Microwire™ Compatible –Schmitt Trigger on Serial Clock (SCLK) R/W Calibration Registers Per Channel Selectable Word Rates: 6.25 to 3,840 Sps Selectable 50 or 60 Hz RejectionPower Supply Configurations–VA+ = +5 V; VA- = 0 V; VD+ = +3 V to +5 V–VA+ = +2.5 V; VA- = -2.5 V; VD+ = +3 V to +5 V –VA+ = +3 V; VA- = -3 V; VD+ = +3 VGeneral DescriptionThe CS5532/34 are highly integrated ∆Σ Analog-to-Digi-tal Converters (ADCs) which use charge-balance techniques to achieve 24-bit performance. The ADCs are optimized for measuring low-level unipolar or bipolar signals in weigh scale, process control, scientific, and medical applications.To accommodate these applications, the ADCs come as either two-channel (CS5532) or four-channel (CS5534)devices and include a very low-noise, chopper-stabilized instrumentation amplifier (6 nV/√Hz @ 0.1 Hz) with se-lectable gains of 1×, 2×, 4×, 8×, 16×, 32×, and 64×.These ADCs also include a fourth-order ∆Σ modulator followed by a digital filter which provides twenty selectable output word rates of 6.25, 7.5, 12.5, 15, 25, 30, 50, 60, 100,120, 200, 240, 400, 480, 800, 960, 1600, 1920, 3200, and 3840 Sps (MCLK =4.9152MHz).To ease communication between the ADCs and a micro-controller, the converters include a simple three-wire se-rial interface which is SPI™ and Microwire™ compatible with a Schmitt-trigger input on the serial clock (SCLK).High dynamic range, programmable output rates, and flexible power supply options makes these ADCs ideal solutions for weigh scale and process control applications.ORDERING INFORMATIONSee page 47VA+C1C2VREF+VREF-VD+DIFFERENTIAL 4TH ORDER ∆ΣMODULATORPGIA 1,2,4,8,16PROGRAMMABLE SINC FIR FILTERMUX(CS5534SHOWN)AIN1+AIN1-AIN2+AIN2-AIN3+AIN3-AIN4+AIN4-SERIAL INTERFACELATCHCLOCK GENERATORCALIBRATION SRAM/CONTROLLOGICDGNDCSSDI SDO SCLKOSC2OSC1A1A0/GUARD VA-32,64OCT ‘08TABLE OF CONTENTS1.CHARACTERISTICS AND SPECIFICATIONS (4)ANALOG CHARACTERISTICS (4)TYPICAL RMS NOISE (NV) (7)TYPICAL NOISE-FREE RESOLUTION(BITS) (7)5 V DIGITAL CHARACTERISTICS (8)3 V DIGITAL CHARACTERISTICS (8)DYNAMIC CHARACTERISTICS (9)ABSOLUTE MAXIMUM RATINGS (9)SWITCHING CHARACTERISTICS (10)2.GENERAL DESCRIPTION (12)2.1.Analog Input (12)2.1.1. Analog Input Span (13)2.1.2. Multiplexed Settling Limitations (13)2.1.3. Voltage Noise Density Performance (13)2.1.4. No Offset DAC (14)2.2.Overview of ADC Register Structure and Operating Modes (14)2.2.1. System Initialization (15)2.2.2. Serial Port Interface (22)2.2.3. Reading/Writing On-Chip Registers (23)2.3.Configuration Register (23)2.3.1. Power Consumption (23)2.3.2. System Reset Sequence (23)2.3.3. Input Short (24)2.3.4. Guard Signal (24)2.3.5. Voltage Reference Select (24)2.3.6. Output Latch Pins (24)2.3.7. Offset and Gain Select (25)2.3.8. Filter Rate Select (25)2.4.Setting up the CSRs for a Measurement (27)2.5.Calibration (30)2.5.1. Calibration Registers (30)2.5.2. Performing Calibrations (31)2.5.3. Self Calibration (31)2.5.4. System Calibration (32)2.5.5. Calibration Tips (32)2.5.6. Limitations in Calibration Range (33)2.6.Performing Conversions (33)2.6.1. Single Conversion Mode (33)2.6.2. Continuous Conversion Mode (34)2.6.3. Examples of Using CSRs to Perform Conversions and Calibrations (35)ing Multiple ADCs Synchronously (36)2.8.Conversion Output Coding (36)2.9.Digital Filter (38)2.10.Clock Generator (39)2.11.Power Supply Arrangements (39)2.12.Getting Started (43)2.13.PCB Layout (43)3.PIN DESCRIPTIONS (44)4.SPECIFICATION DEFINITIONS (46)5.ORDERING INFORMATION (47)6.ENVIRONMENTAL, MANUFACTURING, & HANDLING INFORMATION (47)7.PACKAGE DRAWINGS (48)LIST OF FIGURESFigure 1. SDI Write Timing (Not to Scale) (11)Figure 2. SDO Read Timing (Not to Scale) (11)Figure 3. Multiplexer Configuration (12)Figure 4. Input models for AIN+ and AIN- pins (13)Figure 5. Measured Voltage Noise Density (13)Figure 6. CS5532/34 Register Diagram (14)Figure 7. Command and Data Word Timing (22)Figure 8. Guard Signal Shielding Scheme (24)Figure 9. Input Reference Model when VRS = 1 (25)Figure 10. Input Reference Model when VRS = 0 (25)Figure 11. Self Calibration of Offset (32)Figure 12. Self Calibration of Gain (32)Figure 13. System Calibration of Offset (32)Figure 14. System Calibration of Gain (32)Figure 15. Synchronizing Multiple ADCs (36)Figure 16. Digital Filter Response (WR = 60 Sps) (38)Figure 18. 120 Sps Filter Phase Plot to 120 Hz (38)Figure 17. 120 Sps Filter Magnitude Plot to 120 Hz (38)Figure 19. Z-Transforms of Digital Filters (38)Figure 20. On-chip Oscillator Model (39)Figure 21. CS5532 Configured with a Single +5 V Supply (40)Figure 22. CS5532 Configured with ±2.5 V Analog Supplies (41)Figure 23. CS5532 Configured with ±3 V Analog Supplies (41)Figure 24. CS5532 Configured for Thermocouple Measurement (42)Figure 25. Bridge with Series Resistors (42)LIST OF TABLESTable 1. Conversion Timing – Single Mode (34)Table 2. Conversion Timing – Continuous Mode (35)Table 3. Command Byte Pointer (35)Table 4. Output Coding for 24-bit CS5532 and CS5534 (37)1. CHARACTERISTICS AND SPECIFICATIONSANALOG CHARACTERISTICS(VA+, VD+ = 5 V ±5%; VREF+ = 5 V; VA-, VREF-, DGND = 0 V; MCLK = 4.9152 MHz; OWR (Output Word Rate) = 60 Sps; Bipolar Mode; Gain = 32)(See Notes 1 and 2.)Notes: 1.Applies after system calibration at any temperature within -40 °C ~ +85 °C.2.Specifications guaranteed by design, characterization, and/or test. LSB is 24 bits.3. This specification applies to the device only and does not include any effects by external parasiticthermocouples. The PGIA contributes 5 nV of offset drift, and the modulator contributes 640/G nV of offset drift, where G is the amplifier gain setting.4.Drift over specified temperature range after calibration at power-up at 25 °C.ParameterMin Typ Max Unit Accuracy Linearity Error -±0.0007±0.0015%FS No Missing Codes 24--Bits Bipolar Offset -±16±32LSB 24Unipolar Offset-±32±64LSB 24Offset Drift(Notes 3 and 4)-640/G +5-nV/°C Bipolar Full-scale Error -±8±31ppm Unipolar Full-scale Error -±16±62ppm Full-scale Drift(Note 4)-2-ppm/°CANALOG CHARACTERISTICS (Continued)(See Notes 1 and 2.)Notes: 5.The voltage on the analog inputs is amplified by the PGIA, and becomes V CM ± Gain*(AIN+ - AIN-)/2 atthe differential outputs of the amplifier. In addition to the input common mode + signal requirements for the analog input pins, the differential outputs of the amplifier must remain between (VA- + 0.1 V) and (VA+ - 0.1 V) to avoid saturation of the output stage.6.See the section of the data sheet which discusses input models.7.Input current on AIN+ or AIN- (with Gain =1), or VREF+ or VREF- may increase to 250nA if operatedwithin 50mV of VA+ or VA-. This is due to the rough charge buffer being saturated under these conditions.ParameterMin TypMaxUnitAnalog InputCommon Mode + Signal on AIN+ or AIN-Bipolar/Unipolar ModeGain = 1 Gain = 2, 4, 8, 16, 32, 64(Note 5)VA-VA- + 0.7--VA+VA+ - 1.7V V CVF Current on AIN+ or AIN-Gain = 1 (Note 6, 7)Gain = 2, 4, 8, 16, 32, 64--501200--nA pA Input Current Noise Gain = 1 Gain = 2, 4, 8, 16, 32, 64--2001--pA/√Hz pA/√Hz Input Leakage for Mux when Off (at 25 °C)-10-pA Off-channel Mux Isolation -120-dB Open Circuit Detect Current 100300-nA Common Mode Rejection dc, Gain = 1dc, Gain = 6450, 60 Hz ---90130120---dB dB dB Input Capacitance -60-pF Guard Drive Output -20-µA Voltage Reference Input Range (VREF+) - (VREF-)1 2.5(VA+)-(VA-)V CVF Current (Note 6, 7)-50-nA Common Mode Rejection dc 50, 60 Hz --120120--dB dB Input Capacitance 11-22pF System Calibration Specifications Full-scale Calibration Range Bipolar/Unipolar Mode 3-110%FS Offset Calibration Range Bipolar Mode -100-100%FS Offset Calibration Range Unipolar Mode -90-90%FSANALOG CHARACTERISTICS (Continued)(See Notes 1 and 2.)8.All outputs unloaded. All input CMOS levels.9.Power is specified when the instrumentation amplifier (Gain ≥ 2) is on. Analog supply current is reducedby approximately 1/2 when the instrumentation amplifier is off (Gain = 1).10.Tested with 100 mV change on VA+ or VA-.ParameterMinTypMaxUnitPower SuppliesDC Power Supply Currents (Normal Mode)I A+, I A-I D+- - 130.5151mA mA Power ConsumptionNormal Mode (Notes 8 and 9)Standby Sleep---70450080--mW mW µW Power Supply Rejection (Note 10)dc Positive Supplies dc Negative Supply--115115--dB dBTYPICAL RMS NOISE (nV)(See notes 11, 12, 13 and 14)Notes:11.The -B devices provide the best noise specifications.12.Wideband noise aliased into the baseband. Referred to the input. Typical values shown for 25 °C.13.For Peak-to-Peak Noise multiply by 6.6 for all ranges and output rates.14.Word rates and -3dB points with FRS = 0. When FRS = 1, word rates and -3dB points scale by 5/6.TYPICAL NOISE-FREE RESOLUTION(BITS)(See Notes 15 and 16)15.Noise-free resolution listed is for bipolar operation, and is calculated as LOG((Input Span)/(6.6xRMSNoise))/LOG(2) rounded to the nearest bit. For unipolar operation, the input span is 1/2 as large, so one bit is lost. The input span is calculated in the analog input span section of the data sheet. The noise-free resolution table is computed with a value of 1.0 in the gain register. Values other than 1.0 will scale the noise, and change the noise-free resolution accordingly.16.“Noise-free resolution” is not the same as “effective resolution”. Effective resolution is based on theRMS noise value, while noise-free resolution is based on a peak-to-peak noise value specified as 6.6 times the RMS noise value. Effective resolution is calculated as LOG((Input Span)/(RMS Noise))/LOG(2).Specifications are subject to change without notice.Output Word Rate (Sps)-3 dB Filter Frequency (Hz)Instrumentation Amplifier Gain x64x32x16x8x4x2x17.5 1.948.59101526509915 3.88121315213770139307.751718213052991966015.524252942731402771203134364259103198392240628013626051410202050409048012211319436973014502900581096023015927452310302060411082301,920390260470912181036207230145003,84078013602690538010800215004300086000Output Word Rate (Sps)-3 dB Filter Frequency (Hz)Instrumentation Amplifier Gainx64x32x16x8x4x2x17.5 1.942021222323232315 3.8820212222222222307.75192021222222226015.5192021212121211203118192021212121240621717181818181848012217171717171717960230161617171717171,920390161616161616163,840780131313131313135 V DIGITAL CHARACTERISTICS(VA+, VD+ = 5 V ±5%; VA-, DGND = 0 V; See Notes 2 and 17.)3 V DIGITAL CHARACTERISTICS(T A = 25 °C; VA+ = 5V ±5%; VD+ = 3.0V±10%; VA-, DGND = 0V; See Notes 2 and 17.)17.All measurements performed under static conditions.ParameterSymbol Min Typ Max Unit High-level Input Voltage All Pins Except SCLKSCLK V IH 0.6 VD+(VD+) - 0.45--VD+VD+V Low-level Input Voltage All Pins Except SCLKSCLK V IL 0.00.0-0.80.6V High-level Output Voltage A0 and A1, I out = -1.0 mASDO, I out = -5.0 mA V OH (VA+) - 1.0(VD+) - 1.0--V Low-level Output Voltage A0 and A1, I out = 1.0 mASDO, I out = 5.0 mAV OL --(VA-) + 0.40.4V Input Leakage Current I in -±1±10µA SDO Tri-State Leakage Current I OZ --±10µA Digital Output Pin CapacitanceC out-9-pFParameterSymbol Min Typ Max Unit High-level Input Voltage All Pins Except SCLKSCLK V IH 0.6 VD+(VD+) - 0.45-VD+VD+V Low-level Input Voltage All Pins Except SCLKSCLK V IL 0.00.0-0.80.6V High-level Output Voltage A0 and A1, I out = -1.0 mASDO, I out = -5.0 mA V OH (VA+) - 1.0(VD+) - 1.0--V Low-level Output Voltage A0 and A1, I out = 1.0 mASDO, I out = 5.0 mAV OL --(VA-) + 0.40.4V Input Leakage Current I in -±1±10µA SDO Tri-State Leakage Current I OZ --±10µA Digital Output Pin CapacitanceC out-9-pFDYNAMIC CHARACTERISTICS18.The ADCs use a Sinc 5 filter for the 3200 Sps and 3840 Sps output word rate (OWR) and a Sinc 5 filterfollowed by a Sinc 3 filter for the other OWRs. OWR sinc5 refers to the 3200 Sps (FRS = 1) or 3840 Sps (FRS = 0) word rate associated with the Sinc 5 filter.19.The single conversion mode only outputs fully settled conversions. See Table 1 for more details aboutsingle conversion mode timing. OWR SC is used here to designate the different conversion time associated with single conversions.20.The continuous conversion mode outputs every conversion. This means that the filter’s settling timewith a full scale step input in the continuous conversion mode is dictated by the OWR.ABSOLUTE MAXIMUM RATINGS(DGND = 0 V; See Note 21.)Notes:21.All voltages with respect to ground.22.VA+ and VA- must satisfy {(VA+) - (VA-)} ≤ +6.6 V.23.VD+ and VA- must satisfy {(VD+) - (VA-)} ≤ +7.5 V.24.Applies to all pins including continuous overvoltage conditions at the analog input (AIN) pins.25.Transient current of up to 100 mA will not cause SCR latch-up. Maximum input current for a power supply pin is ±50 mA.26.Total power dissipation, including all input currents and output currents.WARNING:Operation at or beyond these limits may result in permanent damage to the device.Normal operation is not guaranteed at these extremes.ParameterSymbol Ratio Unit Modulator Sampling Ratef s MCLK/16Sps Filter Settling Time to 1/2 LSB (Full Scale Step Input)Single Conversion mode (Notes 18, 19, and 20)Continuous Conversion mode, OWR < 3200 Sps Continuous Conversion mode, OWR ≥ 3200 Spst s t s t s1/OWR SC5/OWR sinc5 + 3/OWR5/OWRs s sParameterSymbol Min Typ Max Unit DC Power Supplies(Notes 22 and 23)Positive Digital Positive Analog Negative Analog VD+VA+VA--0.3-0.3+0.3---+6.0+6.0-3.75V V V Input Current, Any Pin Except Supplies (Notes 24 and 25)I IN --±10mA Output Current I OUT--±25mA Power Dissipation (Note 26)PDN --500mW Analog Input Voltage VREF pins AIN PinsV INR V INA (VA-) -0.3(VA-) -0.3--(VA+) + 0.3(VA+) + 0.3V V Digital Input VoltageV IND -0.3-(VD+) + 0.3V Ambient Operating Temperature T A -40-85°C Storage Temperature T stg-65-150°CSWITCHING CHARACTERISTICS(VA+ = 2.5 V or 5 V ±5%; VA- = -2.5V±5% or 0 V; VD+ = 3.0 V ±10% or 5 V ±5%;DGND = 0 V; Levels: Logic 0 = 0 V, Logic 1 = VD+; C L = 50 pF; See Figures 1 and 2.)Notes:27.Device parameters are specified with a 4.9152 MHz clock.28.Specified using 10% and 90% points on waveform of interest. Output loaded with 50pF.29.Oscillator start-up time varies with crystal parameters. This specification does not apply when using anexternal clock source.ParameterSymbol Min Typ MaxUnitMaster Clock Frequency (Note 27)External Clock or Crystal OscillatorMCLK1 4.91525MHz Master Clock Duty Cycle 40-60%Rise Times(Note 28)Any Digital Input Except SCLKSCLKAny Digital Output t rise-----50 1.0100-µs µs ns Fall Times(Note 28)Any Digital Input Except SCLKSCLKAny Digital Output t fall-----50 1.0100-µs µs ns Start-upOscillator Start-up Time XTAL = 4.9152 MHz(Note 29)t ost-20-ms Serial Port Timing Serial Clock Frequency SCLK 0-2MHz Serial Clock Pulse Width High Pulse Width Lowt 1t 2250250----ns nsSDI Write TimingCS Enable to Valid Latch Clock t 350--ns Data Set-up Time prior to SCLK rising t 450--ns Data Hold Time After SCLK Rising t 5100--ns SCLK Falling Prior to CS Disable t 6100--nsSDO Read Timing CS to Data Validt 7--150ns SCLK Falling to New Data Bit t 8--150ns CS Rising to SDO Hi-Zt 9--150ns分销商库存信息:CIRRUS-LOGICCS5532-BSZR CS5534-BSZR CDB5532U。

MC33171DR2G,MC33174DR2G,MC33174DR2G,MC33174DR2G,MC33172DG,MC33171PG, 规格书,Datasheet 资料

MC33171, 2, 4,NCV33172, 4Single Supply 3.0 V to 44 V, Low Power Operational AmplifiersQuality bipolar fabrication with innovative design concepts are employed for the MC33171/72/74, NCV33172/74 series ofmonolithic operational amplifiers. These devices operate at 180 m A per amplifier and offer 1.8 MHz of gain bandwidth product and 2.1 V/m s slew rate without the use of JFET device technology. Although this series can be operated from split supplies, it is particularly suited for single supply operation, since the common mode input voltage includes ground potential (V EE). With a Darlington input stage, these devices exhibit high input resistance, low input offset voltage and high gain. The all NPN output stage, characterized by no deadband crossover distortion and large output voltage swing, provides high capacitance drive capability, excellent phase and gain margins, low open loop high frequency output impedance and symmetrical source/sink AC frequency response.The MC33171/72/74, NCV33172/74 are specified over the industrial/automotive temperature ranges. The complete series of single, dual and quad operational amplifiers are available in plastic as well as the surface mount packages.Features•Low Supply Current: 180 m A (Per Amplifier)•Wide Supply Operating Range: 3.0 V to 44 V or ±1.5 V to ±22 V •Wide Input Common Mode Range, Including Ground (V EE)•Wide Bandwidth: 1.8 MHz•High Slew Rate: 2.1 V/m s•Low Input Offset V oltage: 2.0 mV•Large Output V oltage Swing: −14.2 V to +14.2 V(with ±15 V Supplies)•Large Capacitance Drive Capability: 0 pF to 500 pF•Low Total Harmonic Distortion: 0.03%•Excellent Phase Margin: 60°•Excellent Gain Margin: 15 dB•Output Short Circuit Protection•ESD Diodes Provide Input Protection for Dual and Quad •NCV Prefix for Automotive and Other Applications Requiring Site and Control Changes•These Devices are Pb−Free and are RoHS CompliantPDIP−8P SUFFIXCASE 626SO−8D, VD SUFFIXCASE 751PDIP−14P, VP SUFFIXCASE 646114SO−14D, VD SUFFIXCASE 751A1See detailed ordering and shipping information in the package dimensions section on page 9 of this data sheet.ORDERING INFORMATIONTSSOP−14DTB SUFFIXCASE 948GSee general marking information in the device marking section on page 10 of this data sheet.DEVICE MARKING INFORMATIONSINGLE(Single, Top View)(Top View)Offset Null 12348765Noninv. InputV EENC V CC Output Offset NullInv. Input V EEInputs 1Inputs 2Output 2Output 1 V CC +-QUADInputs 1V Inputs 2Output 4Inputs 4V EEInputs 3Output 3(Top View)PIN CONNECTIONSDUAL-Offset Null (MC33171)Figure 1. Representative Schematic Diagram(Each Amplifier)MAXIMUM RATINGSRating Symbol Value Unit Supply Voltage V CC/V EE±22VInput Differential Voltage Range V IDR(Note 1)VInput Voltage Range V IR(Note 1)V Output Short Circuit Duration (Note 2)t SC Indefinite sec Operating Ambient Temperature Range T A(Note 3)°C Operating Junction Temperature T J+150°C Storage Temperature Range T stg−65 to +150°C Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.DC ELECTRICAL CHARACTERISTICS (V CC = +15 V, V EE = −15 V, R L connected to ground, T A = +25°C, unless otherwise noted.)Characteristics Symbol Min Typ Max UnitInput Offset Voltage (V CM = 0 V)V CC = +15 V, V EE = −15 V, T A = +25°CV CC = +5.0 V, V EE = 0 V, T A = +25°CV CC = +15 V, V EE = −15 V, T A = T low to T high(Note 3)V IO−−−2.02.5−4.55.06.5mVAverage Temperature Coefficient of Offset Voltage D V IO/D T−10−m V/°CInput Bias Current (V CM = 0 V) T A = +25°CT A = T low to T high(Note 3)I IB−−20−100200nAInput Offset Current (V CM = 0 V) T A = +25°CT A = T low to T high(Note 3)I IO−−5.0−2040nALarge Signal Voltage Gain (V O = ±10 V, R L = 10 k) T A = +25°CT A = T low to T high(Note 3)A VOL5025500−−−V/mVOutput Voltage SwingV CC = +5.0 V, V EE = 0 V, R L = 10 k, T A = +25°CV CC = +15 V, V EE = −15 V, R L = 10 k, T A = +25°CV CC = +15 V, V EE = −15 V, R L = 10 k, T A = T low to T high (Note 3)V OH3.513.613.34.314.2−−−−VV CC = +5.0 V, V EE = 0 V, R L = 10 k, T A = +25°CV CC = +15 V, V EE = −15 V, R L = 10 k, T A = +25°CV CC = +15 V, V EE = −15 V, R L = 10 k, T A = T low to T high(Note 3)V OL−−−0.05−14.2−0.15−13.6−13.3Output Short Circuit (T A = +25°C)Input Overdrive = 1.0 V, Output to GroundSourceSink I SC3.0155.027−−mAInput Common Mode Voltage Range T A = +25°CT A = T low to T high(Note 3)V ICRV EE to (V CC−1.8)V EE to (V CC−2.2)VCommon Mode Rejection Ratio (R S≤ 10 k), T A = +25°C CMRR8090−dB Power Supply Rejection Ratio (R S = 100 W), T A = +25°C PSRR80100−dBPower Supply Current (Per Amplifier)V CC = +5.0 V, V EE = 0 V, T A = +25°CV CC = +15 V, V EE = −15 V, T A = +25°CV CC = +15 V, V EE = −15 V, T A = T low to T high(Note 3)I D−−−180220−250250300m A1.Either or both input voltages must not exceed the magnitude of V CC or V EE.2.Power dissipation must be considered to ensure maximum junction temperature (T J) is not exceeded.3.MC3317x T low = −40°C T high = +85°CMC3317xV, NCV3317x T low = −40°C T high = +125°CAC ELECTRICAL CHARACTERISTICS (V= +15 V, V = −15 V, R connected to ground, T = +25°C, unless otherwise noted.)Figure 2. Input Common Mode Voltage Rangeversus Temperature Figure 3. Split Supply Output Saturationversus Load CurrentV , I N P U T C O M M O N M O D E V O L T A G E R A N G E (V )I C RT A , AMBIENT TEMPERATURE (°C)V , O U T P U T S A T U R A T I O N V O L T A G E (V )s a t I L , LOAD CURRENT (±mA)0.1001.0Figure 4. Open Loop Voltage Gain andPhase versus Frequency Figure 5. Phase Margin and Percent Overshoot versus Load CapacitanceFigure 6. Normalized Gain Bandwidth Productand Slew Rate versus Temperature Figure 7. Small and Large SignalTransient ResponseFigure 8. Output Impedance and Frequency Figure 9. Supply Current versus Supply Voltage5.0 m s/DIV50 m V /D I V10 V /D I V 5.0 m s/DIVf, FREQUENCY (Hz), E X C E S S P A H S E (D E G R E E S )φ, O P E N L O O P V O L T A G E G A I N (d B )V O L m , P H A S E M A R G I N (D E G R E E S )φC L , LOAD CAPACITANCE (pF)%, P E R C E N T O V E R S H O O T T A , AMBIENT TEMPERATURE (°C)G B W A N D S R (N O R M A L I Z E D )f, FREQUENCY (Hz)z , O U T P U T I M P E D A N C E ( )Ωo V CC /V EE , SUPPLY VOLTAGE (±V)D I , I , P O WE R S U P P L Y C U R R E N T (m A )C CA 3020100706050403020100806040200 2002.0 k20 k200 k 2.0 M5.010152025V CC /V EE = ±15 V V CM = 0 V V O = 0 VD I O = ±0.5 mA T A = 25°CAPPLICATIONS INFORMATION − CIRCUIT DESCRIPTION/PERFORMANCE FEATURESAlthough the bandwidth, slew rate, and settling time of the MC33171/72/74 amplifier family is similar to low power op amp products utilizing JFET input devices, these amplifiers offer additional advantages as a result of the PNP transistor differential inputs and an all NPN transistor output stage. Because the input common mode voltage range of this input stage includes the V EE potential, single supply operation is feasible to as low as 3.0 V with the common mode input voltage at ground potential.The input stage also allows differential input voltages up to ±44 V, provided the maximum input voltage range is not exceeded. Specifically, the input voltages must range between V CC and V EE supply voltages as shown by the maximum rating table. In practice, although not recommended, the input voltages can exceed the V CC voltage by approximately 3.0 V and decrease below the V EE voltage by 0.3 V without causing product damage, although output phase reversal may occur. It is also possible to source up to 5.0 mA of current from V EE through either inputs’clamping diode without damage or latching, but phase reversal may again occur. If at least one input is within the common mode input voltage range and the other input is within the maximum input voltage range, no phase reversal will occur. If both inputs exceed the upper common mode input voltage limit, the output will be forced to its lowest voltage state.Since the input capacitance associated with the small geometry input device is substantially lower (0.8 pF) than that of a typical JFET (3.0 pF), the frequency response for a given input source resistance is greatly enhanced. This becomes evident in D−to−A current to voltage conversion applications where the feedback resistance can form a pole with the input capacitance of the op amp. This input pole creates a 2nd Order system with the single pole op amp and is therefore detrimental to its settling time. In this context, lower input capacitance is desirable especially for higher values of feedback resistances (lower current DACs). This input pole can be compensated for by creating a feedback zero with a capacitance across the feedback resistance, if necessary, to reduce overshoot. For 10 k W of feedback resistance, the MC33171/72/74 family can typically settle to within 1/2 LSB of 8 bits in 4.2 m s, and within 1/2 LSB of 12 bits in 4.8 m s for a 10V step. In a standard inverting unity gain fast settling configuration, the symmetrical slew rate is typically ±2.1V/m s. In the classic noninverting unity gain configuration the typical output positive slew rate is also 2.1V/m s, and the corresponding negative slew rate will usually exceed the positive slew rate as a function of the fall time of the input waveform.The all NPN output stage, shown in its basic form on the equivalent circuit schematic, offers unique advantages over the more conventional NPN/PNP transistor Class AB output stage. A 10 k W load resistance can typically swing within 0.8V of the positive rail (V CC) and negative rail (V EE), providing a 28.4 Vpp swing from ±15 V supplies. This large output swing becomes most noticeable at lower supply voltages.The positive swing is limited by the saturation voltage of the current source transistor Q7, the V BE of the NPN pull−up transistor Q17, and the voltage drop associated with the short circuit resistance, R5. For sink currents less than 0.4mA, the negative swing is limited by the saturation voltage of the pull−down transistor Q15, and the voltage drop across R4 and R5. For small valued sink currents, the above voltage drops are negligible, allowing the negative swing voltage to approach within millivolts of V EE. For sink currents (> 0.4 mA), diode D3 clamps the voltage across R4. Thus the negative swing is limited by the saturation voltage of Q15, plus the forward diode drop of D3 (≈V EE +1.0 V). Therefore an unprecedented peak−to−peak output voltage swing is possible for a given supply voltage as indicated by the output swing specifications.If the load resistance is referenced to V CC instead of ground for single supply applications, the maximum possible output swing can be achieved for a given supply voltage. For light load currents, the load resistance will pull the output to V CC during the positive swing and the output will pull the load resistance near ground during the negative swing. The load resistance value should be much less than that of the feedback resistance to maximize pull−up capability.Because the PNP output emitter−follower transistor has been eliminated, the MC33171/72/74 family offers a 15 mA minimum current sink capability, typically to an output voltage of (V EE +1.8 V). In single supply applications the output can directly source or sink base current from a common emitter NPN transistor for current switching applications.In addition, the all NPN transistor output stage is inherently faster than PNP types, contributing to the bipolar amplifier’s improved gain bandwidth product. The associated high frequency low output impedance (200W typ @ 1.0MHz) allows capacitive drive capability from 0 pF to 400 pF without oscillation in the noninverting unity gain configuration. The 60° phase margin and 15 dB gain margin, as well as the general gain and phase characteristics, are virtually independent of the source/sink output swing conditions. This allows easier system phase compensation, since output swing will not be a phase consideration. The AC characteristics of the MC33171/72/74 family also allow excellent active filter capability, especially for low voltage single supply applications.Although the single supply specification is defined at 5.0 V, these amplifiers are functional to at least 3.0V @ 25°C. However slight changes in parametrics such as bandwidth, slew rate, and DC gain may occur.If power to this integrated circuit is applied in reverse polarity, or if the IC is installed backwards in a socket, large unlimited current surges will occur through the device that may result in device destruction.As usual with most high frequency amplifiers, proper lead dress, component placement and PC board layout should be exercised for optimum frequency performance. For example, long unshielded input or output leads may result in unwanted input/output coupling. In order to preserve the relatively low input capacitance associated with these amplifiers, resistors connected to the inputs should be immediately adjacent to the input pin to minimize additional stray input capacitance. This not only minimizes the input pole for optimum frequency response, but also minimizes extraneous “pick up” at this node. Supply decoupling with adequate capacitance immediately adjacent to the supply pin is also important, particularly over temperature, since many types of decoupling capacitors exhibit great impedance changes over temperature.The output of any one amplifier is current limited and thus protected from a direct short to ground. However, under such conditions, it is important not to allow the device to exceed the maximum junction temperature rating. Typically for ±15 V supplies, any one output can be shorted continuously to ground without exceeding the maximum temperature rating.Figure 10. AC Coupled Noninverting Amplifierwith Single +5.0 V Supply Figure 11. AC Coupled Inverting Amplifierwith Single +5.0 V SupplyFigure 12. DC Coupled Inverting Amplifier Maximum Output Swing with Single+5.0 V SupplyFigure 13. Offset Nulling CircuitFigure 14. Active High −Q Notch Filter Figure 15. Active Bandpass FilterV BW ( -3.0 dB) = 20 kHzBW ( -3.0 dB) = 200 kHzV Offset Nulling range is approximately ±80 mV with a 10 k potentiometer, MC33171 only.V inOV inV OCC= 30 kHz O = 1.02 H OR3 =Q p f o C R1 R34Q 2R1 -R3Q o f o GBW < 0.1Given f o = center frequency A o = Gain at center frequency Choose Value f o , Q, A o , CFor less than 10% error for operational amplifier, where f o and GBW are expressed in Hz.ORDERING INFORMATIONOp AmpFunction DeviceOperatingTemperature Range Package Shipping†Single MC33171DGT A = −40° to +85°CSO−8(Pb−Free)98 Units/Rail MC33171DR2G SO−8(Pb−Free)2500 / Tape & Reel MC33171PG PDIP(Pb−Free)50 Units/RailDual MC33172DGT A = −40° to +85°CSO−8(Pb−Free)98 Units/Rail MC33172DR2G SO−8(Pb−Free)2500 / Tape & Reel MC33172PG PDIP(Pb−Free)50 Units/Rail MC33172VDGT A = −40° to +125°CSO−8(Pb−Free)98 Units/Rail MC33172VDR2G SO−8(Pb−Free)2500 / Tape & ReelNCV33172DR2G*SO−8(Pb−Free)2500 / Tape & ReelQuad MC33174DGT A = −40° to +85°CSO−14(Pb−Free)55 Units/Rail MC33174DR2G SO−14(Pb−Free)2500 / Tape & Reel MC33174DTBG TSSOP−14(Pb−Free)96 Units/Rail MC33174DTBR2G TSSOP−14(Pb−Free)2500 / Tape & Reel MC33174PG PDIP(Pb−Free)25 Units/Rail MC33174VDGT A = −40° to +125°CSO−14(Pb−Free)55 Units/Rail MC33174VDR2G SO−14(Pb−Free)2500 / Tape & Reel MC33174VPG PDIP(Pb−Free)25 Units/Rail NCV33174DTBR2G*TSSOP−14(Pb−Free)2500 / Tape & Reel†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.*NCV prefix for automotive and other applications requiring site and change controls.MARKING DIAGRAMSPDIP −8P SUFFIX CASE 62618x = 1 or 2A = Assembly Location WL, L = Wafer Lot YY , Y = YearWW, W = Work WeekG or G = Pb −Free PackageSO −8D SUFFIX CASE 751SO −8MC33172VD NCV33172D CASE 751PDIP −14P SUFFIX CASE 646114MC33174P AWLYYWWG PDIP −14VP SUFFIX CASE 646SO −14D SUFFIX CASE 751ASO −14VD SUFFIX CASE 751ATSSOP −14DTB SUFFIXCASE 948G MC3317xPAWL YYWWG 114114MC33174ALYW G G MC33174VP AWLYYWWG(Note: Microdot may be in either location)8 LEAD PDIP CASE 626−05 ISSUE MNOTE 5TOP VIEWEND VIEWEND VIEWNOTE 3DIM MIN NOM MAXINCHESA−−−−−−−−0.210A10.015−−−−−−−−b0.0140.0180.022C0.0080.0100.014D0.3550.3650.400D10.005−−−−−−−−e0.100 BSCE0.3000.3100.325L0.1150.1300.150−−−−−−−− 5.330.38−−−−−−−−0.350.460.560.200.250.369.029.2710.020.13−−−−−−−−2.54 BSC7.627.878.262.923.30 3.81MIN NOM MAXMILLIMETERSNOTES:1.DIMENSIONING AND TOLERANCING PER ASMEY14.5M, 1994.2.CONTROLLING DIMENSION: INCHES.3.DIMENSION E IS MEASURED WITH THE LEADS RE-STRAINED PARALLEL AT WIDTH E2.4.DIMENSION E1 DOES NOT INCLUDE MOLD FLASH.5.ROUNDED CORNERS OPTIONAL.E10.2400.2500.280 6.10 6.357.11E2E3−−−−−−−−0.430−−−−−−−−10.920.300 BSC7.62 BSCSOIC −8 NB CASE 751−07ISSUE AKNOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.4.MAXIMUM MOLD PROTRUSION 0.15 (0.006)PER SIDE.5.DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBARPROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.6.751−01 THRU 751−06 ARE OBSOLETE. NEW STANDARD IS 751−07.DIM AMIN MAX MINMAX INCHES4.805.000.1890.197MILLIMETERS B 3.80 4.000.1500.157C 1.35 1.750.0530.069D 0.330.510.0130.020G 1.27 BSC 0.050 BSC H 0.100.250.0040.010J 0.190.250.0070.010K 0.40 1.270.0160.050M 0 8 0 8 N 0.250.500.0100.020S5.806.200.2280.244MYM0.25 (0.010)YM0.25 (0.010)Z SXS____0.6ǒmm inchesǓSCALE 6:1*For additional information on our Pb −Free strategy and solderingdetails, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*PDIP−14 CASE 646−06 ISSUE PDIM MIN MAX MIN MAXMILLIMETERSINCHESA0.7150.77018.1619.56B0.2400.260 6.10 6.60C0.1450.185 3.69 4.69D0.0150.0210.380.53F0.0400.070 1.02 1.78G0.100 BSC 2.54 BSCH0.0520.095 1.32 2.41J0.0080.0150.200.38K0.1150.135 2.92 3.43LM−−−10 −−−10N0.0150.0390.38 1.01__NOTES:1.DIMENSIONING AND TOLERANCING PER ANSIY14.5M, 1982.2.CONTROLLING DIMENSION: INCH.3.DIMENSION L TO CENTER OF LEADS WHENFORMED PARALLEL.4.DIMENSION B DOES NOT INCLUDE MOLD FLASH.5.ROUNDED CORNERS OPTIONAL.KM0.13 (0.005)0.2900.3107.377.87SOIC −14CASE 751A −03ISSUE JNOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.4.MAXIMUM MOLD PROTRUSION 0.15 (0.006)PER SIDE.5.DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127(0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.SBM0.25 (0.010)AST SEATING PLANEDIM MIN MAX MIN MAX INCHESMILLIMETERS A 8.558.750.3370.344B 3.80 4.000.1500.157C 1.35 1.750.0540.068D 0.350.490.0140.019F 0.40 1.250.0160.049G 1.27 BSC 0.050 BSC J 0.190.250.0080.009K 0.100.250.0040.009M 0 7 0 7 P 5.80 6.200.2280.244R0.250.500.0100.019____DIMENSIONS: MILLIMETERSSOLDERING FOOTPRINT*For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.TSSOP −14CASE 948G −01ISSUE BDIM MIN MAX MIN MAX INCHES MILLIMETERS A 4.90 5.100.1930.200B 4.30 4.500.1690.177C −−− 1.20−−−0.047D 0.050.150.0020.006F 0.500.750.0200.030G 0.65 BSC 0.026 BSC H 0.500.600.0200.024J 0.090.200.0040.008J10.090.160.0040.006K 0.190.300.0070.012K10.190.250.0070.010L 6.40 BSC 0.252 BSC M0 8 0 8 NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSION A DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.4.DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.5.DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08(0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.6.TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY .7.DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE −W −.____14X REF 14X0.360.65PITCH*For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

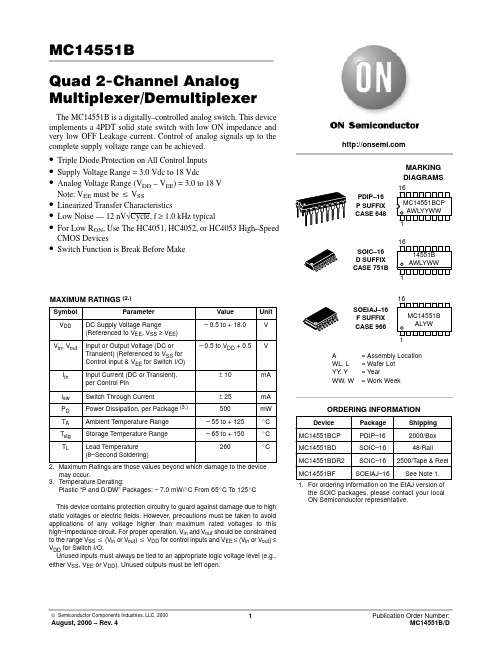

MC14551BCP中文资料