ABSTRACT Automated Synthesis for Asynchronous FPGAs

C#中abstract的用法详解

C#中abstract的⽤法详解abstract可以⽤来修饰类,⽅法,属性,索引器和时间,这⾥不包括字段. 使⽤abstrac修饰的类,该类只能作为其他类的基类,不能实例化,⽽且abstract修饰的成员在派⽣类中必须全部实现,不允许部分实现,否则编译异常. 如:using System;namespace ConsoleApplication8{class Program{static void Main(string[] args){BClass b = new BClass();b.m1();}}abstract class AClass{public abstract void m1();public abstract void m2();}class BClass : AClass{public override void m1(){throw new NotImplementedException();}//public override void m2()//{// throw new NotImplementedException();//}}}Abstract classes have the following features:抽象类拥有如下特征:1,抽象类不能被实例化, 但可以有实例构造函数, 类是否可以实例化取决于是否拥有实例化的权限 (对于抽象类的权限是abstract, 禁⽌实例化),即使不提供构造函数, 编译器也会提供默认构造函数;2,抽象类可以包含抽象⽅法和访问器;3,抽象类不能使⽤sealed修饰, sealed意为不能被继承;4,所有继承⾃抽象类的⾮抽象类必须实现所有的抽象成员,包括⽅法,属性,索引器,事件;abstract修饰的⽅法有如下特征:1,抽象⽅法即是虚拟⽅法(隐含);2,抽象⽅法只能在抽象类中声明;3,因为抽象⽅法只是声明, 不提供实现, 所以⽅法只以分号结束,没有⽅法体,即没有花括号部分;如public abstract void MyMethod();4,override修饰的覆盖⽅法提供实现,且只能作为⾮抽象类的成员;5,在抽象⽅法的声明上不能使⽤virtual或者是static修饰.即不能是静态的,⼜因为abstract已经是虚拟的,⽆需再⽤virtual强调.抽象属性尽管在⾏为上与抽象⽅法相似,但仍有有如下不同:1,不能在静态属性上应⽤abstract修饰符;2,抽象属性在⾮抽象的派⽣类中覆盖重写,使⽤override修饰符;抽象类与接⼝:1,抽象类必须提供所有接⼝成员的实现;2,继承接⼝的抽象类可以将接⼝的成员映射位抽象⽅法.如:interface I{void M();}abstract class C: I{public abstract void M();}抽象类实例:// abstract_keyword.cs// 抽象类using System;abstract class BaseClass // 抽象类{protected int _x = 100; //抽象类可以定义字段,但不可以是抽象字段,也没有这⼀说法.protected int _y = 150;public BaseClass(int i) //可以定义实例构造函数,仅供派⽣的⾮抽象类调⽤; 这⾥显式提供构造函数,编译器将不再提供默认构造函数. {fielda = i;}public BaseClass(){}private int fielda;public static int fieldsa = 0;public abstract void AbstractMethod(); // 抽象⽅法public abstract int X { get; } //抽象属性public abstract int Y { get; }public abstract string IdxString { get; set; } //抽象属性public abstract char this[int i] { get; } //抽象索引器}class DerivedClass : BaseClass{private string idxstring;private int fieldb;//如果基类中没有定义⽆参构造函数,但存在有参数的构造函数,//那么这⾥派⽣类得构造函数必须调⽤基类的有参数构造函数,否则编译出错public DerivedClass(int p): base(p) //这⾥的:base(p)可省略,因为基类定义了默认的⽆参构造函数{fieldb = p;}public override string IdxString //覆盖重新属性{get{return idxstring;}set{idxstring = value;}}public override char this[int i] //覆盖重写索引器{get { return IdxString[i]; }}public override void AbstractMethod(){_x++;_y++;}public override int X // 覆盖重写属性{get{return _x + 10;}}public override int Y // 覆盖重写属性{get{return _y + 10;}}static void Main(){DerivedClass o = new DerivedClass(1);o.AbstractMethod();Console.WriteLine("x = {0}, y = {1}", o.X, o.Y);}}以上所述是⼩编给⼤家介绍的C#中abstract的⽤法详解,希望对⼤家有所帮助,如果⼤家有任何疑问请给我留⾔,⼩编会及时回复⼤家的。

2020年在nature catalysis上发表重要成果

2020年在nature catalysis上发表重要成果

2020年,在《Nature Catalysis》杂志上发表了一项重要成果,该成果由某科研团队经过多年努力终于成功研发出一种新型的催化剂,能够有效地将废弃塑料转化为高附加值的产品。

这项成果的研发背景是,随着人类对塑料的依赖程度不断加深,废弃塑料的污染问题日益严重,给生态环境带来了巨大的压力。

因此,科研团队一直在寻找一种能够有效处理废弃塑料的方法。

该科研团队通过多年的研究,成功研发出这种新型催化剂。

该催化剂能够在常温常压下将废弃塑料中的聚乙烯和聚丙烯等塑料成分转化为燃料和化学品等高附加值的产品。

这种转化过程不仅能够有效处理废弃塑料,而且能够产生经济效益,具有很高的应用价值。

该成果的发表引起了广泛关注。

在《Nature Catalysis》杂志上,该论文被选为封面文章,并得到了编辑部的特别推荐。

该论文的发表不仅证明了该科研团队在催化剂研究方面的实力,也标志着人类在解决废弃塑料污染问题方面取得了重要进展。

未来,该科研团队将继续优化这种新型催化剂的制备工艺和应用范围,希望能够为解决全球废弃塑料污染问题做出更大的贡献。

同时,他们也希望通过与产业界的合作,将这种技术应用于实际生产中,为人类创造更加美好的生态环境和可持续发展未来。

Simulation and Synthesis Techniques for Asynchronous FIFO Design with Asynchronous Pointer Compariso

Simulation and Synthesis Techniques for Asynchronous FIFO Design with Asynchronous Pointer ComparisonsClifford E. Cummings Peter AlfkeSunburst Design, Inc. Xilinx, Inc.SNUG-2002San Jose, CAVoted Best Paper1st Place ABSTRACTAn interesting technique for doing FIFO design is to perform asynchronous comparisons between the FIFO write and read pointers that are generated in clock domains that are asynchronous to each other. The asynchronous FIFO pointer comparison technique uses fewer synchronization flip-flops to build the FIFO. The asynchronous FIFO comparison method requires additional techniques to correctly synthesize and analyze the design, which are detailed in this paper.To increase the speed of the FIFO, this design uses combined binary/Gray counters that take advantage of the builtin binary ripple carry logic.The fully coded, synthesized and analyzed RTL Verilog model (FIFO Style #2) is included.This FIFO design paper builds on information already presented in another FIFO design paper where the FIFO pointers are synchronized into the opposite clock domain before running "FIFO full" or "FIFO empty" tests. The reader may benefit from first reviewing the FIFO Style #1 method before proceeding to this FIFO Style #2 method.Post-SNUG Editorial Comment (by Cliff Cummings)Although this paper was voted “Best Paper - 1st Place” by SNUG attendees, this paper builds off of a second FIFO paper listed as reference [1]. The first FIFO paper laid the foundation for some of the content of this paper; therefore, it is highly recommended that readers download and read the FIFO1 paper[1] to acquire background information already assumed to be known by the reader of this paper.1.0 IntroductionAn asynchronous FIFO refers to a FIFO design where data values are written sequentially into a FIFO buffer using one clock domain, and the data values are sequentially read from the same FIFO buffer using another clock domain, where the two clock domains are asynchronous to each other.One common technique for designing an asynchronous FIFO is to use Gray[4] code pointers that are synchronized into the opposite clock domain before generating synchronous FIFO full or empty status signals[1]. An interesting and different approach to FIFO full and empty generation is to do an asynchronous comparison of the pointers and then asynchronously set the full or empty status bits[6].This paper discusses the FIFO design style with asynchronous pointer comparison and asynchronous full and empty generation. Important details relating to this style of asynchronous FIFO design are included. The FIFO style implemented in this paper uses efficient Gray code counters, whose implementation is described in the next section.2.0 Gray code counter - style #2One Gray code counter style uses a single set of flip-flops as the Gray code register with accompanying Gray-to binary conversion, binary increment, and binary-to-Gray conversion[1].A second Gray code counter style, the one described in this paper, uses two sets of registers, one a binary counter and a second to capture a binary-to-Gray converted value. The intent of this Gray code counter style #2 is to utilize the binary carry structure, simplify the Gray-to-binary conversion; reduce combinational logic, and increase the upper frequency limit of the Gray code counter.The binary counter conditionally increments the binary value, which is passed to both the inputs of the binary counter as the next-binary-count value, and is also passed to the simple binary-to-Gray conversion logic, consisting of one 2-input XOR gate per bit position. The converted binary value is the next Gray-count value and drives the Gray code register inputs.Figure 1 shows the block diagram for an n-bit Gray code counter (style #2).This implementation requires twice the number of flip-flops, but reduces the combinatorial logic and can operate at a higher frequency. In FPGA designs, availability of extra flip-flops is rarely a problem since FPGAs typically contain far more flip-flops than any design will ever use. In FPGA designs, reducing the amount of combinational logic frequently translates into significant improvements in speed.The ptr output of the block diagram in Figure 1 is an n-bit Gray code pointer.Note: since the MSB of a binary sequence is equal to the MSB of a Gray code sequence, this design can be further simplified by using the binary MSB-flip-flop as the Gray codeMSB-flip-flop. The Verilog code in this paper did not implement this additional optimization. This would save one flip-flop per pointer.3.0 Full & empty detectionAs with any FIFO design, correct implementation of full and empty is the most difficult part of the design.There are two problems with the generation of full and empty:First, both full and empty are indicated by the fact that the read and write pointers are identical. Therefore,something else has to distinguish between full and empty. One known solution to this problem appends an extra bit to both pointers and then compares the extra bit for equality (for FIFO empty) or inequality (for FIFO full), along with equality of the other read and write pointer bits[1].Another solution, the one described in this paper, divides the address space into four quadrants and decodes the two MSBs of the two counters to determine whether the FIFO was going full or going empty at the time the two pointers became equal.If the write pointer is one quadrant behind the read pointer, this indicates a "possibly going full" situation as shown in Figure 2. When this condition occurs, the direction latch of Figure 4 is set.Figure 3 - FIFO is going empty because the rptr trails the wptr by one quadrantIf the write pointer is one quadrant ahead of the read pointer, this indicates a "possibly going empty" situation as shown in Figure 3. When this condition occurs, the direction latch of Figure 4 is cleared.When the FIFO is reset the direction latch is also cleared to indicate that the FIFO “is going empty” (actually, it is empty when both pointers are reset). Setting and resetting the direction latch is not timing-critical, and the direction latch eliminates the ambiguity of the address identity decoder.The Xilinx FPGA logic to implement the decoding of the two wptr MSBs and the two rptr MSBs is easily implemented as two 4-input look-up tables.The second, and more difficult, problem stems from the asynchronous nature of the write and read clocks. Comparing two counters that are clocked asynchronously can lead to unreliable decoding spikes when either or both counters change multiple bits more or less simultaneously. The solution described in this paper uses a Gray count sequence, where only one bit changes from any count to the next. Any decoder or comparator will then switch only from one valid output to the next one, with no danger of spurious decoding glitches.4.0 FIFO style #2For the purposes of this paper, FIFO style #1 refers to a FIFO implementation style that synchronizes pointers from one clock domain to another before generating full and empty flags [1].The FIFO style described in this paper (FIFO style #2) does asynchronous comparison between Gray code pointers to generate an asynchronous control signal to set and reset the full and empty flip-flops.The block diagram for FIFO style #2 is shown in Figure 5.To facilitate static timing analysis of the style #2 FIFO design, the design has been partitioned into the following five Verilog modules with the following functionality and clock domains:•fifo2.v - (see Example 1 in section 5.1) - this is the top-level wrapper-module that includes all clock domains. The top module is only used as a wrapper to instantiate all of the other FIFO modules used in the design. If this FIFO is used as part of a larger ASIC or FPGA design, thistop-level wrapper would probably be discarded to permit grouping of the other FIFO modules into their respective clock domains for improved synthesis and static timing analysis.fifomem.v - (see Example 2 in section 5.2) - this is the FIFO memory buffer that is accessed by both the write and read clock domains. This buffer is most likely an instantiated, synchronous dual-port RAM. Other memory styles can be adapted to function as the FIFO buffer.•async_cmp.v - (see Example 3 in section 5.3) - this is an asynchronous pointer-comparison module that is used to generate signals th at control assertion of the asynchronous “full” and “empty” status bits. This module only contains combinational comparison logic. No sequential logic is included in this module.•rptr_empty.v - (see Example 4 in section 5.4) - this module is mostly synchronous to the read-clock domain and contains the FIFO read pointer and empty-flag logic. Assertion of the aempty_n signal (an input to this module) is synchronous to the rclk-domain, sinceaempty_n can only be asserted when the rptr incremented, but de-assertion of the aempty_n signal happens when the wptr increments, which is asynchronous to rclk.•wptr_full.v - (see Example 5 in section 5.5) - this module is mostly synchronous to the write-clock domain and contains the FIFO write pointer and full-flag logic. Assertion of theafull_n signal (an input to this module) is synchronous to the wclk-domain, since afull_n can only be asserted when the wptr incremented (and wrst_n), but de-assertion of theafull_n signal happens when the rptr increments, which is asynchronous to wclk.5.0 RTL code for FIFO style #2The Verilog RTL code for the FIFO style #2 model is listed in this section.5.1 fifo2.v - FIFO top-level moduleThe fifo2 top-level module is a parameterized module with all sub-blocks instantiated following safe coding practices using named port connections.module fifo2 (rdata, wfull, rempty, wdata,winc, wclk, wrst_n, rinc, rclk, rrst_n);parameter DSIZE = 8;parameter ASIZE = 4;output [DSIZE-1:0] rdata;output wfull;output rempty;input [DSIZE-1:0] wdata;input winc, wclk, wrst_n;input rinc, rclk, rrst_n;wire [ASIZE-1:0] wptr, rptr;wire [ASIZE-1:0] waddr, raddr;async_cmp #(ASIZE) async_cmp(.aempty_n(aempty_n), .afull_n(afull_n),.wptr(wptr), .rptr(rptr), .wrst_n(wrst_n));fifomem #(DSIZE, ASIZE) fifomem(.rdata(rdata), .wdata(wdata),.waddr(wptr), .raddr(rptr),.wclken(winc), .wclk(wclk));rptr_empty #(ASIZE) rptr_empty(.rempty(rempty), .rptr(rptr),.aempty_n(aempty_n), .rinc(rinc),.rclk(rclk), .rrst_n(rrst_n));wptr_full #(ASIZE) wptr_full(.wfull(wfull), .wptr(wptr),.afull_n(afull_n), .winc(winc),.wclk(wclk), .wrst_n(wrst_n));endmoduleExample 1 - Top-level Verilog code for the FIFO style #2 design5.2 fifomem.v - FIFO memory bufferThe FIFO memory buffer could be an instantiated ASIC or FPGA dual-port, synchronous memory device. The memory buffer could also be synthesized to ASIC or FPGA registers using the RTL code in this module.If a vendor RAM is instantiated, it is highly recommended that the instantiation be done using named port connections.module fifomem (rdata, wdata, waddr, raddr, wclken, wclk);parameter DATASIZE = 8; // Memory data word widthparameter ADDRSIZE = 4; // Number of memory address bitsparameter DEPTH = 1<<ADDRSIZE; // DEPTH = 2**ADDRSIZEoutput [DATASIZE-1:0] rdata;input [DATASIZE-1:0] wdata;input [ADDRSIZE-1:0] waddr, raddr;input wclken, wclk;`ifdef VENDORRAM// instantiation of a vendor's dual-port RAMVENDOR_RAM MEM (.dout(rdata), .din(wdata),.waddr(waddr), .raddr(raddr),.wclken(wclken), .clk(wclk));`elsereg [DATASIZE-1:0] MEM [0:DEPTH-1];assign rdata = MEM[raddr];always @(posedge wclk)if (wclken) MEM[waddr] <= wdata;`endifendmoduleExample 2 - Verilog RTL code for the FIFO buffer memory array5.3 async_cmp.v - Asynchronous the full/empty comparison logicThe logic used to determine the full or empty status on the FIFO is the most distinctive difference between FIFO style #1 and FIFO style #2.Async_cmp is an asynchronous comparison module, used to compare the read and write pointers to detect full and empty conditions.module async_cmp (aempty_n, afull_n, wptr, rptr, wrst_n);parameter ADDRSIZE = 4;parameter N = ADDRSIZE-1;output aempty_n, afull_n;input [N:0] wptr, rptr;input wrst_n;reg direction;wire high = 1'b1;wire dirset_n = ~( (wptr[N]^rptr[N-1]) & ~(wptr[N-1]^rptr[N]));wire dirclr_n = ~((~(wptr[N]^rptr[N-1]) & (wptr[N-1]^rptr[N])) |~wrst_n);always @(posedge high or negedge dirset_n or negedge dirclr_n)if (!dirclr_n) direction <= 1'b0;else if (!dirset_n) direction <= 1'b1;else direction <= high;//always @(negedge dirset_n or negedge dirclr_n)//if (!dirclr_n) direction <= 1'b0;//else direction <= 1'b1;assign aempty_n = ~((wptr == rptr) && !direction);assign afull_n = ~((wptr == rptr) && direction);endmoduleExample 3 - Verilog RTL code for the asynchronous comparator moduleThree of the last seven lines of the Verilog code of Example 3 have been commented out in this model. In theory, a synthesis tool should be capable of inferring an RS-flip-flop from the comment-removed code, but the LSI_10K library that is included with the default installation of the Synopsys tools did not infer a correct RS-flip-flop with this code when tested, so the always block immediately preceding the commented code was added to infer an RSflip-flop.5.3.1 Asynchronous generation of full and emptyIn the async_cmp code of Example 3, and shown in Figure 6, aempty_n and afull_n are the asynchronously decoded signals. The aempty_n signal is asserted on the rising edge of an rclk, but is de-asserted on the rising edge of a wclk. Similarly, the afull_n signal is asserted on a wclk and removed on an rclk.The empty signal will be used to stop the next read operation, and the leading edge of aempty_n is properly synchronous with the read clock, but the trailing edge needs to be synchronized to the read clock. This is done in a two-stage synchronizer that generates rempty.The wfull signal is generated in the symmetrically equivalent way.5.3.2 Resetting the FIFOThe first FIFO event of interest takes place on a FIFO-reset operation. When the FIFO is reset, four important things happen within the async_cmp module and accompanying full and empty synchronizers of the wptr_full and rptr_empty modules (the connections between the async_cmp, wptr_full and rptr_empty modules are shown in Figure 7):1. The reset signal directly clears the wfull flag. The rempty flag is not cleared by a reset.2. The reset signal clears both FIFO pointers, so the pointer comparator asserts that the pointers are equal.3. The reset clears the direction bit.4. With the pointers equal and the direction bit cleared, the aempty_n bit is asserted, which presets the rempty flag.5.3.3 FIFO-writes & FIFO fullThe second FIFO operational event of interest takes place when a FIFO-write operation takes place and the wptr is incremented. At this point, the FIFO pointers are no longer equal so the aempty_n signal is de-asserted, releasing the preset control of the rempty flip-flops. After two rising edges on rclk, the FIFO will de-assert the rempty signal. Because the de-assertion of aempty_n happens on a rising wclk and because the rempty signal is clocked by the rclk, the two-flip-flop synchronizer as shown in Figure 8 is required to remove metastability that could be generated by the first rempty flip-flop.The second FIFO operational event of interest takes place when the wptr increments into the next Gray code quadrant beyond the rptr (see section 3.0 for a discussion of Gray code quadrants). The direction bit is cleared (but it was already clear).The third FIFO operational event of interest occurs when the wptr is within one quadrant of catching up to the rptr as described in section 3.0. When this happens, the dirset_n bit of Figure 6 is asserted low, which sets the direction bit high. This means that the direction bit is set long before the FIFO is full and is not timingcritical to assertion of the afull_n signal. The fourth FIFO operational event of interest is when the wptr catches up to the rptr (and the direction bit is set). When this happens, the afull_n signal presets the wfull flip-flops. The afull_n signal is asserted on a FIFO-write operation and is synchronous to the rising edge of the wclk; therefore, asserting full is synchronous to the wclk. See section 5.3.6 for a discussion of the critical timing path associated with assertion of the wfull signal.The fifth FIFO operational event of interest is when a FIFO-read operation takes place and the rptr is incremented. At this point, the FIFO pointers are no longer equal so the afull_n signal is de-asserted, releasing the preset control of the wfull flip-flops. After two rising edges on wclk, the FIFO will de-assert the wfull signal. Because the de-assertion of afull_n happens on a rising rclk and because the wfull signal is clocked by the wclk, the two-flip-flop synchronizer, shown in Figure 8, is required to remove metastability that could be generated by the first wfull flip-flop capturing the inverted and asynchronously generated afull_n data input.During operation, wfull is generated synchronous to the write clock, in a similar way that rempty is generated synchronous to the read clock. The afull_n signal is asserted as a result of a write clock, and the leading (falling) edge is thus naturally synchronous to the write clock. The trailing (rising) edge is, however caused by the read clock, and must, therefore be synchronized to thewrite clock. The same timing issues related to the setting of the full flag also apply to the setting of the empty flag.5.3.4 FIFO-reads & FIFO emptyThe sixth FIFO operational event of interest takes place when the rptr increments into the next Gray code quadrant beyond the wptr. The direction bit is again set (but it was already set). The seventh FIFO operational event of interest occurs when the rptr is within one quadrant of catching up to the wptr. When this happens, the dirrst bit of Figure 6 is asserted high , which clears the direction bit. This means that the direction bit is cleared long before the FIFO is empty and is not timing critical to assertion of the aempty_n signal.The eighth FIFO operational event of interest is when the rptr catches up to the wptr (and the direction bit is zero). When this happens, the aempty_n signal presets the remptyflip-flops. The aempty_n signal is asserted on a FIFO-read operation and is synchronous to the rising edge of the rclk; therefore, asserting empty is synchronous to the rclk. See section 5.3.6 for a discussion of the critical timing path associated with assertion of the rempty signal. Finally, when a FIFO-write operation takes place and the wptr is incremented. At this point, the FIFO pointers are no longer equal so the aempty_n signal is de-asserted, releasing the preset control of the rempty flip-flops. After two rising edges on rclk, the FIFO will de-assert the rempty signal. Because the de-assertion of aempty_n happens on a rising wclk and because the rempty signal is clocked by the rclk, the two-flip-flop synchronizer as shown in Figure 8 is required to remove metastability that could be generated by the first rempty flip-flop.5.3.5 Alternate method to preset the full & empty flagsAnother method for setting the rempty or wfull flags is to use a self-timed differentiating circuit as shown in Figure 9. In this figure, the flip-flops are shown with high-true presets, similar to what is found on Xilinx FPGAs.(equivalent circuitry could also be designed using low-true presets). When the aempty signal goes high, the rempty output flip-flop is preset and assuming that the signal between the flip-flops was low, this signal combined with aempty-high will drive the output of the and gate high and set the first flip-flop. When the first flip-flop is set,the and gate will quit driving the preset signal to the first flip-flop. This is a self-timed preset signal that releases preset immediately after preset occurs, well before the aempty signal goes low.5.3.6 Full and empty critical timing pathsUsing the asynchronous comparison technique described in this paper, there are critical timing paths associated with the generation of both the rempty and wfull signals.The rempty critical timing path, shown in Figure 10, consists of (1) the rclk-to-q incrementing of the rptr, (2) comparison logic of the rptr to the wptr, (3) combining the comparator output with the direction latch output to generate the aempty_n signal, (4) presetting the rempty signal,(5) any logic that is driven by the rempty signal, and (6) resultant signals meeting the setup time of any down-stream flip-flops clocked within the rclk domain. This critical timing path has a symmetrically equivalent critical timing path for the generation of the wfull signal, also shown in Figure 10.5.3.7 Asynchronous concerns, questions and answersWhile writing this paper, the authors asked and answered numerous questions to address concerns over the highly asynchronous nature of the generation and removal of the full and empty bits for the FIFO style described in this paper. This section captures a number of the questions, concerns and answers that lead both authors to believe this coding style does indeed work. Generation of the aempty_n control signal is straightforward. Whenever the read pointer (rptr) equals the write pointer (wptr), and the direction latch is clear, the FIFO is empty. The empty flag is used only in the read clock domain and since the read pointer, incremented by a read clock,causes the empty flag to be set, assertion of the empty flag is always synchronous in the read clock domain. As long as the empty flag meets the critical empty-assertion timing path described in section 5.3.6, there is no synchronization problems associated with asserting the empty flag.The de-assertion of aempty_n is caused by the write clock incrementing the write pointer, and is thus unrelated to the read clock. The de-assertion of aempty_n must, therefore, be synchronized in a dual-flip-flop synchronizer, clocked by the read clock. The first flip-flop is subject to metastability but the second flip-flop is included to wait for the metastability to subside, just like any other multi-clock synchronizer[2].Since aempty_n is started by one clock and terminated by the other, it has an undefined duration,and might even be a runt pulse. A runt pulse is a Low-High-Low signal transition where the transition to High may or may not pass through the logic-“1” threshold level of the logic family being used.If the aempty_n control signal is a runt pulse, there are four possible scenarios that should be addressed:(1) the runt signal is not recognized by the rempty flip-flops and empty is not asserted. This is not a problem.(2) The runt pulse might preset the first synchronizer flip-flop, but not the second flip-flop. This is highly unlikely, but would result in an unnecessary, but properly synchronized rempty output, that will show up on the output of the second flip-flop one read clock later. This is not a problem.(3) The runt pulse might preset the second synchronizer flip-flop, but not the first flip-flop. This is highly unlikely,but would result in an unnecessary, but properly synchronized rempty output (as long as the empty critical timing is met), that will be set on the output of the second flip-flop until the next read clock, when it will be cleared by the zero from the first flip-flop. This is not a problem.(4) The most likely case is that the runt pulse sets both flip-flops, thus creating a properly synchronized rempty output that is two read-clock periods long. The longer duration is caused by the two-flip-flop synchronizer ( to avoid metastable problems as described below). This is not a problem.The runt pulse cannot have any effect on the synchronizer data-input, since an aempty_n runt pulse can only occur immediately after a read clock edge, thus long before the next read clock edge (as long as critical timing is met).The aempty_n signal might also stay high longer and go low at any moment, even perhaps coincident with the next read clock edge. If it goes low well before the set-up time of the first synchronize flip-flop, the result is like scenario (4) above. If it goes low well after the set-up time, the synchronizer will stretch rempty by one more read clock period.If aempty_n goes low within the metstability-catching set-up time window, the first synchronizer flip-flop output will be indeterminate for a few nanoseconds, but will then be either high or low. In either case, the output of the second synchronizer flip-flop will create the appropriate synchronized rempty output.The next question is, what happens if the write clock de-asserts the aempty_n signal coincident with the rising rclk on the dual synchronizer? The first flip-flop could go metastable, which is why there is a second flip-flop in the dual synchronizer.But the removal of the setting signal on the second flip-flop will violate the recovery time of the second flip-flop.Will this cause the second flip-flop to go metastable? The authors do not believe this can happen because the preset to the flip-flop forced the output high and the input to the same flip-flop is already high, which we believe is not subject to a recovery time instability on the flip-flop.Challenge: if anyone can prove that a flip-flop that is set high, and is also driven by ahigh-data-input signal, can go metastable if the preset signal is removed coincident with the rising edge of the clock to the same flip-flop, the authors would like to be made aware of any such claim. The authors believe that recovery time parameters are with respect to removing a preset when the data input value is zero. The authors could not find any published reference to discount the possibility of metastability on the output of the second flip-flop but we believe that metastabilityin this case is not possible.Last question. Can a runt-preset pulse, where the trailing edge of the runt pulse is caused by the wclk, preset the second synchronizer flip-flop in close proximity to a rising rclk, violate the preset recovery time and cause metastability on the output of the second flip-flop? The answer is no as long as the aempty_n critical timing path is met. Assuming that critical timing is met, the aempty_n signal going low should occur shortly after a rising rclk and well before the rising edge of the second flip-flop, so runt pulses can only occur well before the rising edge of an rclk.Again, symmetrically equivalent scenarios and arguments can be made about the generation of the wfull flag.5.4 rptr_empty.v - Read pointer & empty generation logicThis module encloses all of the FIFO logic that is generated within the read clock domain (except synchronizers).The read pointer is an n-bit Gray code counter. The FIFO rempty output is asserted when the aempty_n signal goes low and the rempty output is de-asserted on the second rising rclk edge after aempty_n goes high (a rare metastable state could cause the rempty output to be de-asserted on the third rising rclk edge). This module is completely synchronous to the rclk for simplified static timing analysis, except for the aempty_n input, which is de-asserted asynchronously to the rclk.module rptr_empty (rempty, rptr, aempty_n, rinc, rclk, rrst_n); parameter ADDRSIZE = 4;output rempty;output [ADDRSIZE-1:0] rptr;input aempty_n;input rinc, rclk, rrst_n;reg [ADDRSIZE-1:0] rptr, rbin;reg rempty, rempty2;wire [ADDRSIZE-1:0] rgnext, rbnext;//---------------------------------------------------------------// GRAYSTYLE2 pointer//--------------------------------------------------------------- always @(posedge rclk or negedge rrst_n)if (!rrst_n) beginrbin <= 0;rptr <= 0;endelse beginrbin <= rbnext;rptr <= rgnext;end//---------------------------------------------------------------// increment the binary count if not empty//--------------------------------------------------------------- assign rbnext = !rempty ? rbin + rinc : rbin;assign rgnext = (rbnext>>1) ^ rbnext; // binary-to-gray conversion。

abstract方法

abstract方法Abstract方法。

在面向对象的编程中,抽象方法是一种非常重要的概念。

它是一种在抽象类或者接口中声明但不实现的方法,需要由子类去实现具体的逻辑。

本文将对抽象方法进行详细的介绍,包括其定义、特点、使用方法以及示例等内容。

首先,抽象方法是指在抽象类或者接口中声明但不实现的方法。

它只有方法的声明,没有方法体。

抽象方法的存在是为了让子类去实现具体的逻辑,从而达到代码的灵活性和可扩展性。

在Java中,使用关键字“abstract”来声明抽象方法,而在C#中,则使用关键字“abstract”来修饰方法。

其次,抽象方法的特点是必须在抽象类或者接口中声明,而且不能包含方法体。

另外,包含抽象方法的类必须被声明为抽象类,而包含抽象方法的接口则必须被实现。

在使用抽象方法时,需要注意的是子类必须实现父类中的所有抽象方法,否则子类也必须声明为抽象类。

使用抽象方法的好处在于可以定义一套规范,让子类去实现具体的逻辑。

这样一来,可以在不同的子类中实现不同的逻辑,从而提高代码的复用性和可维护性。

此外,抽象方法还可以降低代码的耦合度,使得程序更加灵活和易于扩展。

下面通过一个简单的示例来说明抽象方法的使用方法。

假设有一个图形类Shape,其中包含一个抽象方法calculateArea()用于计算图形的面积。

然后有两个子类Circle和Rectangle分别继承Shape类,并实现calculateArea()方法来计算圆形和矩形的面积。

这样一来,就可以通过多态的方式来调用不同子类的calculateArea()方法,而不需要关心具体是哪个子类。

总之,抽象方法是面向对象编程中非常重要的概念,它可以提高代码的灵活性和可扩展性,降低代码的耦合度,使得程序更加易于维护和扩展。

通过本文的介绍,相信读者对抽象方法有了更深入的理解,可以在实际的项目中更加灵活地运用抽象方法来设计和实现代码。

计算机专业术语中英文对照

计算机专业术语中英⽂对照计算机专业术语对照Aabstraction layer,抽象层access,获取,存取acoustic coupler,声⾳耦合器Active Directory,活动⽬录Acyclic Dependencies Principle,⾮循环依赖原则(ADP)acyclic digraph,有向⽆环图Adaptive Code,⾃适应代码Add Parameter,添加参数ADSL,Asymmetrical Dingital Subscriber Loop,⾮对称数字⽤户环线affinity,绑定affinity group,地缘组agent,代理agent-based interface,代理⼈界⾯Agile,敏捷⽅法论agile practice,敏捷实践agile peocess,敏捷流程agility,敏捷性AI,Artificial Intelligence,⼈⼯智能air waves,⽆线电波algorithm,算法analog,模拟的animation,动画annotation,注解,注释answering machine,电话应答机antenna,天线anti-pattern,反模式APM,异步编程模型(Asynchronous Programming Model)Apocalyptic defect,灾难缺陷application,应⽤,应⽤程序,应⽤软件application life cycle,应⽤程序⽣命周期application pool,应⽤程序池Application Programming Interface,应⽤程序编程接⼝(API)architecture,体系机构,结构architecture decay,架构腐坏Architecture Style,架构风格ARPA,Advanced Research Projects Agency,(美国国防部)⾼级研究计划署ARPAnet,ARPA⽹Arrange-Act-Assert,准备-执⾏-断⾔(AAA)artifact,构建物4ASF,Apache Software Foundation 的简写Aspect-Oriented Programming,⾯向切⾯编程(AOP)aspect ratio,屏幕⾼宽⽐assembly,程序集Asynchronous Programming Model,异步编程模型(APM)ATM,asynchronous transfer mode,异步传输模式atomic opreation,原⼦操作atomic transaction,原⼦事务atomicity,原⼦性attribute,特性augmented reality,增强实现authentication,⾝份验证authorization,授权automated unit testing,⾃动化单元测试automation,⾃动化autonomous,独⽴性availability,可⽤性availability set,可⽤性集AZs,可⽤性区域(Availability Zones,亚马逊 AWS 中数据中⼼的叫法)4BBackend as a Service,后端即服务(BaaS)backpane,底板backward compatibility,向后兼容性bandwidth,带宽bar code,条形码Base Class Library,基类库(BCL)baseline,准线baud,波特BCL,基类库(Base Class Library)bear,熊behavior,⾏为behavior preserving program transformations,⾏为保留式程序转换1 Behavioral error,⾏为错误BFF,为前端服务的后端(Backends For Frontends)4Big Ball of Mud,⼤泥球(BBM)big data,⼤数据Big Design Up Front,⼤优先设计(BDUF)binary,⼆进制的binochlar,双⽬并⽤的bit,⽐特Bit-field,位域bitnik,⽐特族blob,BLOBblock,阻断block blob,块 BLOBBlockchain as a Service,区块链即服务(BaaS)bottleneck,瓶颈bounded context,边界上下⽂、界限上下⽂4box,装箱bps,bits per second,⽐特/秒breakpoint,断点broadcast,(⽆线电或电视)⼴播Broken Hierarchy,⽀离破碎的层次结构2Broken Modularization,拆散的模块化2brownfield project,⾏进中项⽬Browser Object Model,浏览器对象模型(BOM)browser-server,浏览器-服务器bug,缺陷built-in,内置的,内建的;嵌⼊的;内置bulkhead,舱壁4business intelligence,商业智能business layer,业务层business logic layer,业务逻辑层busy (status),忙(状态);繁忙(状态)byte,字节Ccable,电缆Cache/Caching,缓存call stack,调⽤堆栈callout box,标注框camelCase,camel ⼤⼩写canary releasing,⾦丝雀发布4carbon copy,复写本,副本;抄送(CC)carriage return,回车Cascading Style Sheets,层叠样式表(CSS)catastrophic failover,灾难性故障转移4CD,持续交付(Continuous Delivery)4CDC,消费者驱动的契约(Customer-Driven Contract)4CDN,内容分发⽹络(Content Delivery Network)cell,单元cellular telephone,移动电话Central Processing Unit,中央处理器(CPU)certificate,(数字)证书Certificate Authority,证书认证机构Change Bidirectional Association to Unidirectional,将双向关联改为单向关联1Change Point,修改点:需要往代码中引⼊修改的点Change Reference to Value,将引⽤对象改为值对象1Change Unidirectional Association to Bidirectional,将单向关联改为双向关联1Change Value to Reference,将值对象改为引⽤对象1channel,信道,频道character,字符Characterization test,特征测试:描述软件某部分的当前⾏为的测试,当你修改代码时能够⽤来保持⾏为check in,签⼊check out,签出chip,芯⽚choreography,协同CI,持续集成(Continuous Integration)4cipher,密码claim,声明class definition,类定义CLI,公共语⾔基础结构(Common Language Infrastructure)client-server,客户端-服务器clone,克隆,复制cloud computing,云计算cloud service,云服务CLR,公共语⾔运⾏时(Common Language Runtime)CLS,公共语⾔规范(Common Language Specification)cluster,集群clustered index,聚集索引CMS,内容管理系统(Content Management System)co-occurring smells,同时出现的坏味2coaxial cable,同轴电缆COBIT,信息和相关技术的控制⽬标,Control Objectives for Information and Related Technology4 CoC,更改开销(Cost of Change)code smell,代码味道Collapse Hierarchy,折叠继承关系1comcurrency,并发command,命令command prompt,命令⾏提⽰Command/Query Responsibility Segregation,命令/查询职责分离(CQRS)Command/Query Separation,命令/查询分离(CQS)commingled bits,混合的⽐特communication,通信community,社区committed,已提交(的)Common Intermediate Language,公共中间语⾔Common Language Infrastructure,公共语⾔基础结构(CLI)Common Language Runtime,公共语⾔运⾏时(CLR)Common Language Specification,公共语⾔规范(CLS)Common Type System,公共类型系统(CTS)common name,通⽤名称compatibility,兼容性Competing Consumer pattern,消费者竞争模式4Component Object Model,组件对象模型(COM)composite formatting,复合格式化Composite Pattern,复合模式concurrency conflicts,并发冲突concurrency mode,并发模式conditional compilation,条件编译conditional compilation statement,条件编译语句configuration,配置,设置connection string,连接字符串Consolidate Conditional Expression,合并条件表达式1Consolidate Duplicate Conditional Fragments,合并重复的条件⽚段1consistenct,⼀致性constructor,构造函数container,容器Container As A Service,容器即服务(CaaS)4content,内容context,上下⽂contextual keyword,上下⽂关键字continuous integration,持续集成contribute,贡献Contributor License Agreement,贡献者许可协议convention,约定covariance,协变contravariance,逆变convert,转换Convert Procedural Design to Objects,将过程化设计转化为对象设计1cookie,Cookiecore,内核;.NET Core 的简写(能且仅能与 .NET Framework 的简写nfx同时出现,作如nfx/core,单独使⽤时应为全称.NET Core)corruption,损毁Cosmetic issue,外观上问题Cost of Change,更改开销(CoC)COTS,现成的商业软件(Commercial Off-The Shelf)4counterpoint,对位4Coupling count,耦合数:当⼀个⽅法被调⽤时传给它以及从它传出来的值的数⽬。

Synthesis(怎样写Synthesis)

整理人: 报告人:

Definition

Definition of synthesis essay

A synthesis is a combination, usually a shortened version, of several texts. A synthesis is not a summary. A synthesis is an opportunity to create new knowledge out of already existing knowledge.

sources.

Difference between summary and synthesis

Shows what the original authours wrote.

Not only reflects your knowledge about what the original authors wrote, but also creates something new out of two or more pieces of writing.

one unified entity.

Presents a cursory overview.

Forcuses on both main ideas and details.

Demonstrates an understanding of the overall

meaning.

Achieves new insight.

Addresses one set of information(eg.article,chapte r,document) at a time Each

c++ abstract修饰类用法

C++中abstract修饰类的用法1. 概述在C++中,我们经常会听到关于abstract类的概念。

那么,abstract 类到底是什么?它又有什么作用呢?2. 什么是abstract类在C++中,我们可以使用关键字“abstract”来修饰一个类,使其成为一个“abstract类”。

一个abstract类是一种不能被实例化的类,即不能创建它的对象。

abstract类通常用于定义接口和抽象的行为,它的目的是为了让其他类继承并实现它的纯虚函数。

3. abstract类的定义要定义一个abstract类,我们可以在类中声明纯虚函数。

纯虚函数是指在类中声明但没有实现的虚函数。

通过在函数声明后面加上“= 0”来将一个虚函数声明为纯虚函数。

例如:```C++class AbstractClass {public:virtual void pureVirtualFunction() = 0;};```4. abstract类的作用abstract类的作用主要有以下几点:- 定义接口:abstract类定义了一组接口,表示了一种抽象的行为。

其他类可以继承并实现这些接口。

这样一来,我们就可以通过基类指针来调用派生类的函数。

- 特定行为的约束:abstract类可以约束其派生类必须实现某些特定的行为。

这样一来,我们就可以确保派生类都具有相同的接口,从而提高代码的一致性和可维护性。

- 防止实例化:abstract类的对象不能被创建,这可以防止程序员错误地使用该类,从而避免一些潜在的错误。

5. 如何使用abstract类在C++中,我们可以通过继承abstract类并实现其中定义的纯虚函数来使用abstract类。

例如:```C++class ConcreteClass : public AbstractClass {public:void pureVirtualFunction() override {// 实现纯虚函数的具体逻辑}};```在上面的例子中,ConcreteClass继承了AbstractClass,并实现了其中定义的纯虚函数pureVirtualFunction。

Abstract图形界面的使用

These options control the grid analysis function that calculates the best metal1 and metal2 routing grid pitches and offsets for your standard cells. 默认关闭该功能。

当开关关闭时,整条Net都定义

为Pin,并且每一次改变走向都

增加编号。例如:en1、en2等

A

当开关打开,在boundary的边

缘位置创建Pin,默认情况以

label所在层的最窄宽度为边长

的正方形。

B

第42页/共59页

Adjust Step

Boundary pin max distance to boundary

第16页/共59页

第17页/共59页

第18页/共59页

5、给Layout增加prBoundary

这一层用于规划IP的大小,属于标识层。 今后可以在Layout设计时就加入这层。需 要注意Stream out GDS文件时要在map文件 中添加对这层的说明,否则会丢失。

第19页/共59页

边缘黄色线条就是prBoundary这层 使用时需要到LSW的Edit中开启这一 层的显示。

Abstract界面

第8页/共59页

菜单说明

Verify step Abstract step Extract step Pins step Logial import Layout import Open library

第9页/共59页

菜单说明

第10页/共59页

数据准备及建库流程

• Tech.lef • GDS • Schematic Library • PDK library

基于人工智能算法的自动化化学合成研究

基于人工智能算法的自动化化学合成研究在过去的几年中,人工智能技术迅猛发展,从语音识别到自动驾驶,已经在许多领域取得了显著的进展。

在化学合成领域,人工智能技术同样发挥着越来越重要的作用,尤其是在自动化化学合成方面的研究。

本文将重点讨论基于人工智能算法的自动化化学合成研究的相关问题。

一、人工智能算法在化学合成领域的应用化学合成是一项复杂的过程,需要研究人员的极大努力和经验。

为了通过更有效的方式设计和优化化学合成过程,研究人员已经开始使用人工智能算法,并取得了显著的进展。

这些算法可以通过模拟和研究化学反应进行数据分析和预测,以便更好地理解化学反应的机制以及控制其变量以实现更可靠的化学合成。

人工智能算法中最常用的是机器学习算法,这些算法可以利用大量的已知数据进行训练,以预测新数据的行为。

基于机器学习算法的化学合成研究,大大降低了合成的时间和成本,并提高了化学合成的效率。

例如,使用机器学习算法可以创建模型,有效预测无机化合物的热稳定性和电导率,有助于设计新的材料或优化新的方案。

除了机器学习算法外,基于人工智能的合成研究中还应用了其他算法,包括基于规则和基于知识的方法。

基于规则的算法适用于有限的、已知的化学反应,需要根据规则在数据中进行查找和匹配。

基于知识的算法则可以判断新的反应是否可行,获得经验和实验知识,有助于发现新的化合物和新的反应路径。

二、基于人工智能算法的自动化化学合成研究随着人工智能算法在化学领域的应用越来越广泛,自动化化学合成的研究也逐渐兴起。

自动化化学合成可以利用人工智能技术,通过自动化设计合成方案、测试化合物、控制变量和自动记录实验数据等方法,有效地降低人为干预和操作的错误的风险,并提高了合成效率和准确度。

例如,自动化化学合成可以通过高通量实验室设备等来实现自动合成,减轻实验者的压力,同时加快反应过程,并减少实验的时间和成本。

此外,自动化化学合成还可以利用人工智能算法,在数百个准备好的合成化合物中进行筛选优化方案,并充分发挥化学家的专业技能,以获得更快、更准确、更经济的合成合物的成果。

the automatic creation of literature abstracts解析

the automatic creation of literature abstracts解析1. 引言1.1 概述在当今信息爆炸的时代,人们需要快速而准确地获取所需信息,并从中获取有用的知识。

然而,随着大量文献的出现,阅读和分析所有这些内容变得十分耗时费力。

为了解决这个问题,自动创建文献摘要成为一个备受关注的研究领域。

本篇文章将探讨自动创建文献摘要的重要性、方法与技术以及目前的研究进展。

1.2 文章结构本文共分为五个部分,每个部分都围绕着自动创建文献摘要展开讨论。

首先,在引言部分概述了自动创建文献摘要的背景和意义。

接下来,在第二部分中,我们将详细介绍文献摘要的定义、作用以及传统方法存在的局限性。

第三部分将介绍实现自动创建文献摘要所使用的技术和方法,包括文本分析和自然语言处理技术、机器学习和深度学习方法以及相关数据集和评估指标。

第四部分将回顾目前已有的研究进展并分析面临的挑战以及未来的发展方向。

最后,第五部分将总结本文的主要观点和工作内容,并对自动创建文献摘要领域的未来发展进行展望。

1.3 目的本文旨在介绍自动创建文献摘要的重要性及其在不同领域中的应用。

通过探讨已有方法和技术,我们将揭示传统方法存在的局限性,并引入新兴的机器学习和深度学习方法。

此外,我们还将审视当前研究进展并识别面临的挑战,为自动创建文献摘要领域未来发展提供新思路和方向。

通过阅读本文,读者将能够全面了解自动创建文献摘要相关概念、技术和研究进展,并理解该领域未来可能取得的突破与应用前景。

2. 自动创建文献摘要的重要性2.1 文献摘要的定义和作用文献摘要是对一篇文章、论文或研究报告的简洁概述。

它的主要目的是向读者传达原文中最重要的信息,使读者能够快速了解全文的核心内容,确定是否需要深入阅读整篇文献。

2.2 传统方法的局限性传统上,人工撰写文献摘要是一个耗时且费力的过程。

需要有资深领域专家阅读并理解完整的文章,然后提取关键信息进行总结。

肖文精 光催化不对称minsci反应

肖文精光催化不对称minsci反应肖文精是光催化不对称minsci反应的开创者之一,他的研究成果在有机合成领域引起了广泛的关注和重视。

本文将以肖文精光催化不对称minsci 反应为主题,一步一步解析其原理、应用和进展。

一、光催化不对称minsci反应的原理光催化不对称minsci反应是一种利用光催化剂的酏木机制来实现的有机合成反应。

光催化剂能够通过吸收光照射而激发电子,形成激发态的中间体。

在光激发状态下,光催化剂能够参与化学反应,催化反应物之间的转化。

不对称minsci反应是以不对称催化剂为前驱体,催化反应的进行,并在反应过程中引入手性元件,使得反应产物具有手性。

光催化不对称minsci反应有以下三个重要步骤:1. 光激发:光催化剂在光照射下吸收光,电子被激发至激发态。

2. 电子转移:激发态的光催化剂与反应底物之间进行电子转移,生成激发态的反应底物。

3. 反应进行:激发态的反应底物参与反应,通过不对称催化剂的催化作用,生成手性产物。

二、光催化不对称minsci反应的应用光催化不对称minsci反应在有机合成中具有重要的应用价值,可以实现对手性产物的高效合成。

其应用领域主要包括以下几个方面:1. 天然产物合成:光催化不对称minsci反应可以实现对复杂天然产物的有效合成。

通过选择不同的催化剂和反应底物,可以实现对天然产物特定手性中心的选择性合成。

2. 药物合成:光催化不对称minsci反应在药物合成中有广泛的应用。

通过该反应可以合成手性药物的药效亚型,提高药物的立体选择性和生物活性。

3. 化学功能材料合成:光催化不对称minsci反应在化学功能材料的合成中有重要作用。

通过该反应可以合成具有特定手性的功能材料,拓展其应用范围。

三、光催化不对称minsci反应的进展光催化不对称minsci反应是一个快速发展的研究领域,近年来取得了一系列重要进展。

1. 发展新型催化剂:研究人员不断寻找新型的光催化剂,以提高反应的效率和选择性。

不对称自由基反应英文

不对称自由基反应英文Asymmetric Radical Reactions: An Insight into Their Mechanism and Applications.Introduction.Asymmetric radical reactions have emerged as a powerful tool in organic synthesis, enabling the synthesis of chiral compounds with high enantiomeric purity. These reactions differ significantly from their symmetric counterparts, as they involve the generation and utilization of chiral radicals. These chiral radicals can undergo a range of reactions, including substitution, addition, and cyclization, leading to the formation of enantiomerically enriched products.Mechanism of Asymmetric Radical Reactions.The mechanism of asymmetric radical reactions typically involves three key steps: radical generation, chiralitytransfer, and radical termination.Radical Generation.The first step involves the generation of a radical species. This can be achieved through various methods, such as photolysis, thermal decomposition, or redox reactions. The generated radical can be chiral or achiral, depending on the starting materials and the conditions used.Chirality Transfer.The second step involves the transfer of chirality from a chiral auxiliary or catalyst to the radical species. This chirality transfer can occur through covalent or non-covalent interactions between the catalyst/auxiliary and the radical. The nature of these interactions determines the stereoselectivity of the reaction.Radical Termination.The final step involves the termination of the radicalspecies, leading to the formation of the desired product. This termination can occur through various mechanisms, such as coupling with another radical species, hydrogen atom abstraction, or disproportionation.Applications of Asymmetric Radical Reactions.Asymmetric radical reactions have found widespread applications in various fields of organic synthesis, including the synthesis of natural products, pharmaceuticals, and functional materials.Synthesis of Natural Products.Natural products often possess complex chiral structures, making their synthesis challenging. Asymmetric radical reactions have proven to be effective tools for the synthesis of such chiral natural products. For example, the use of chiral radicals generated from appropriate precursors has enabled the enantioselective synthesis of alkaloids, terpenes, and amino acids.Pharmaceutical Applications.The enantiomers of chiral drugs often differ significantly in their biological activities, making it crucial to control their enantiomeric purity. Asymmetric radical reactions can be used to synthesize enantiomerically enriched chiral drugs with high selectivity. This approach has been successfully applied to the synthesis of various drugs, including anti-inflammatory agents, anticancer agents, and antiviral agents.Functional Materials.Chiral materials possess unique physical and chemical properties that make them useful in various applications, such as displays, sensors, and catalysts. Asymmetricradical reactions can be used to synthesize chiral building blocks for the preparation of such materials. For instance, chiral polymers can be synthesized by utilizing asymmetric radical polymerization reactions, leading to the formation of materials with controlled chirality and tailored properties.Conclusion.Asymmetric radical reactions have emerged as powerful tools for the synthesis of enantiomerically enriched chiral compounds. Their unique mechanism, involving chirality transfer from a chiral catalyst/auxiliary to the radical species, enables high selectivity and enantiopurity in the product. The widespread applications of asymmetric radical reactions in organic synthesis, particularly in the synthesis of natural products, pharmaceuticals, and functional materials, highlight their importance in modern chemistry.Future Perspectives.Despite the significant progress made in the field of asymmetric radical reactions, there are still numerous challenges and opportunities for further exploration.Improving Selectivity and Efficiency.One of the key challenges in asymmetric radical reactions is achieving high selectivity and efficiency. While significant progress has been made in this area, there is still room for improvement. Future research could focus on developing new chiral catalysts/auxiliaries that can promote asymmetric radical reactions with higher selectivity and efficiency.Expanding the Scope of Reactions.Currently, the scope of asymmetric radical reactions is limited by the availability of suitable precursors and the reactivity of the generated radicals. Future research could aim to expand the scope of these reactions by developing new methods for generating radicals with desired functionalities and reactivities.Applications in Sustainable Chemistry.In the context of sustainable chemistry, asymmetric radical reactions offer an attractive alternative to traditional synthetic methods. By utilizing renewableresources and mild reaction conditions, asymmetric radical reactions could contribute to the development of more sustainable synthetic routes for the preparation of chiral compounds.Integration with Other Techniques.The integration of asymmetric radical reactions with other techniques, such as photocatalysis, electrochemistry, and microfluidics, could lead to the development of new and innovative synthetic methods. By combining the advantages of these techniques, it may be possible to achieve even higher selectivity, efficiency, and scalability in asymmetric radical reactions.In conclusion, asymmetric radical reactions have emerged as powerful tools for the synthesis of enantiomerically enriched chiral compounds. While significant progress has been made in this area, there are still numerous opportunities for further exploration and development. Future research in this field could lead tothe discovery of new and innovative synthetic methods with improved selectivity, efficiency, and sustainability.。

abstractautoproxycreator的原理

abstractautoproxycreator的原理AbstractAutoProxyCreator是一个用于创建自动代理对象的工具类,它能够根据对象的属性和方法自动生成相应的代理代码,以提高代码的复用性和可维护性。

本文将详细介绍AbstractAutoProxyCreator的原理、使用方法和注意事项。

一、背景在软件开发中,代理模式是一种常用的设计模式之一,它通过创建一个代理对象来代理原始对象的行为,从而实现代码的重用和扩展。

AbstractAutoProxyCreator正是基于这种设计模式,通过自动生成代理代码的方式来简化开发过程。

二、原理1. 代理对象与原始对象的关联:AbstractAutoProxyCreator通过将代理对象与原始对象建立关联,从而实现对原始对象行为的代理。

2. 代理对象的自动生成:AbstractAutoProxyCreator根据对象的属性和方法,自动生成相应的代理代码,包括getter、setter、构造函数、析构函数以及自定义的方法等。

3. 代理行为的动态加载:当代理对象被实例化时,AbstractAutoProxyCreator根据对象的属性值动态加载相应的行为代码,从而实现代理对象的行为。

(1)定义代理对象和原始对象的类名、属性、方法等信息;(2)根据这些信息生成代理对象的框架代码;(3)根据对象的属性和方法,动态生成相应的getter、setter、构造函数、析构函数以及自定义方法的代理代码;(4)将生成的代理代码保存到文件中,供后续使用;(5)在需要使用代理对象的地方,实例化代理对象,并传入相应的属性值;(6)根据属性值动态加载相应的行为代码,实现代理对象的行为。

三、使用方法在使用AbstractAutoProxyCreator之前,需要先进行以下准备工作:(2)根据项目的需求,定义好代理对象和原始对象的类名、属性、方法等信息;(3)将需要生成的代理代码保存到指定的文件中,以便后续使用。

abstract 编程 -回复

abstract 编程-回复关于编程,我将以中括号内的主题为核心,进行一步一步的回答。

[编程]是一种通过编写和执行一系列指令来实现特定任务的过程。

随着科技的不断发展,编程已经成为现代社会中不可或缺的一部分。

它广泛应用于各个领域,例如软件开发、网站设计、数据分析等,对于个人和企业而言,都具有重要的意义。

首先,我们需要了解编程的基本概念和原则。

编程语言是人与计算机之间交流的桥梁,它们分为高级编程语言和低级编程语言。

高级编程语言更接近自然语言,比如Python、Java等,而低级编程语言更接近计算机的语言,如汇编语言。

每种编程语言都有其特点和应用范围,根据不同需求选择适合的编程语言非常重要。

接下来,我们需要了解编程的基本步骤。

首先,明确任务和目标。

在编程过程中,我们需要清楚地知道要实现的任务和目标,这有助于我们选择合适的编程语言和开发工具。

其次,进行程序设计。

在程序设计阶段,我们需要设计和规划程序的逻辑结构,确定所需的功能和算法。

然后,编写代码。

编写代码是将程序设计转化为计算机语言的过程,我们需要使用相应的编程语言和编译器来进行编码工作。

最后,进行测试和调试。

在编程过程中,我们需要进行多次测试和调试,以确保程序的正确性和稳定性。

除了基本的编程步骤,我们还需要了解一些编程的核心概念。

控制流是编程过程中的一个重要概念,它用于控制程序的执行顺序。

常见的控制流结构包括顺序结构、条件结构和循环结构。

顺序结构是按照代码的先后顺序执行,而条件结构和循环结构可以根据特定条件来控制程序的执行。

另外,变量和数据类型也是编程过程中的重要概念。

变量用于存储和表示数据,而数据类型用于定义变量的性质和操作。

常见的数据类型包括整数、浮点数、字符串等。

当我们了解了编程的基本概念和步骤之后,就可以开始编写实际的程序了。

在这个过程中,我们需要运用各种编程技巧和方法来解决问题。

例如,模块化编程可以将程序分解成多个功能相对独立的模块,方便开发和维护。

AI小说家人工智能如何创作出令人惊叹的小说

AI小说家人工智能如何创作出令人惊叹的小说AI小说家:人工智能如何创作出令人惊叹的小说近年来,人工智能(Artificial Intelligence,AI)的技术快速发展,渗透到我们生活的各个领域。

其中,AI小说家以其独特的创作方式和令人惊叹的成果引起了广泛关注。

本文将探讨AI小说家的工作原理、创作过程以及其产生的深远影响。

一、AI小说家的技术原理AI小说家依赖于深度学习技术和自然语言处理算法。

首先,它通过大量的训练数据,运用人工神经网络构建了一个复杂的模型。

这个模型可以分析和理解文本的语义、句法结构以及情感色彩。

然后,AI小说家根据训练数据中的模式和规律,生成新的文本内容。

二、AI小说家的创作过程1. 数据训练:AI小说家需要大量的已有小说作品作为训练数据,以便学习其中的文本结构、情节安排和语言表达方式。

2. 文本生成:在训练完成后,AI小说家可以根据输入的关键词或主题,生成新的文章段落或完整的故事情节。

AI小说家通过模拟人类写作,使用合适的语法和表达方式,创作出令人惊叹的小说。

三、AI小说家的优势和挑战1. 创作效率:相较于人类作家,AI小说家具有极高的创作效率。

它可以根据输入的要求,在短时间内快速生成大量的文字内容。

2. 创作多样性:AI小说家可以同时参考大量的文本作品,跨越不同的文学流派和风格,创作出独特多样的小说内容。

然而,AI小说家也面临着一些挑战。

首先,它缺乏情感和创造力,无法像人类作家一样体验和表达情绪。

其次,由于模型的局限性,AI小说家生成的文本可能存在逻辑不清、信息缺失等问题。

因此,尽管AI小说家具备一定的创作能力,但在文学艺术上仍然难以与人类作家媲美。

四、AI小说家的影响和前景1. 探索新领域:AI小说家的出现推动了文学创作方法的创新。

它能够自动生成大量新颖的故事情节和创意,并激发人们在文学领域的思考和探索。

2. 扩大受众:AI小说家可以根据读者的喜好和需求,定制个性化的小说。

基于人工智能的自动化文献摘要生成算法研究

基于人工智能的自动化文献摘要生成算法研究自动化文献摘要生成算法是基于人工智能技术和自然语言处理技术的一种新型应用。

在信息爆炸的时代,人们需要快速获取大量信息,这正是自动化文献摘要技术被广泛运用的原因之一。

本文将探讨基于人工智能的自动化文献摘要生成算法的研究,包括算法原理、应用场景和未来发展趋势。

一、算法原理自动化文献摘要生成算法的核心是利用自然语言处理技术和机器学习算法,对文献中的主要内容进行抽取和概括,生成简洁、准确的摘要。

具体而言,该算法需要利用文献的关键词,结合上下文语义,识别文献的主要议题,将之转化为简洁、准确的语言文字,并进行语法优化和内容完整性的检查,保证最终生成的摘要不失准确性和易读性。

在算法的实现过程中,需要利用自然语言处理先对文献进行语义分析和文本挖掘,识别文本中的实体、事件和关系,并进行意图分析和情感分析,提取出文本中的重要意义。

同时,将文本转化为数学模型,利用机器学习算法进行模型训练,将人工智能技术与自动文献摘要生成技术进行结合。

二、应用场景自动化文献摘要生成技术用于文献或资料的内容概括、整理和传播。

在很多领域都有着广泛的应用场景。

首先,研究人员需要通过查阅大量文献来寻找研究资料,在这个过程中往往需要快速查阅文献核心内容,以便更好地确定研究方向和方法。

自动化文献摘要生成技术可以快速生成文献摘要,给学者节约宝贵时间。

其次,新闻、出版、广告、知识管理等领域都需要快速了解大量信息,对信息的快速处理和概括有着重大需求。

自动化文献摘要生成技术可以将大量文献信息概括成简洁、准确的语言文字,提高工作效率,降低工作难度。

此外,在自媒体时代,自动化文献摘要生成技术对于新闻资讯的整合和快速传播也具有重要意义。

通过利用自动化文献摘要生成技术,可以快速归纳、整合新闻事件,撰写对应的新闻报道,以更快的速度传播信息。

三、未来发展趋势自动化文献摘要生成技术是基于人工智能技术和自然语言处理技术的,因此,随着人工智能技术的不断发展,该技术也将逐步得到完善和应用。

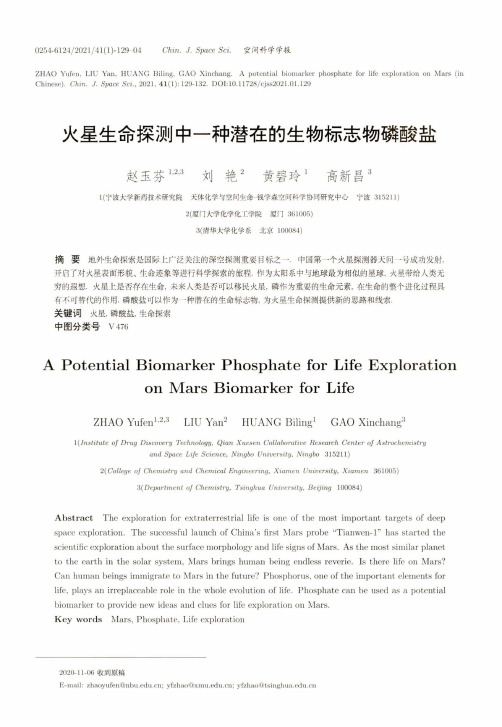

火星生命探测中一种潜在的生物标志物磷酸盐

0254-6124/2021/41(1)-129-04 Chin. J. Space Sci.空间科学学报ZHAO Yufen. LIU Yan, HUANG Biling, GAO Xinchang. A potential biomarker phosphate for life exploration on Mars (in Chinese). Chin. J. Space Sci, 2021, 41(1): 129-132. D01:10.11728/cjss2021.01.129火星生命探测中一种潜在的生物标志物磷酸盐赵玉芬1>2’3刘艳2黄碧玲1高新昌31(宁波大学新药技术研究院天体化学与空间生命#学森空间科学协同研究中心宁波315211)门大学化学化工学院ffl门361005)3(清华大学化学系北京100084)f商要地外生命探索是国际上广泛关注的深空探测重要目标之一.中国第一个火星探测器天问-号成功发射,开启了对火星表面形貌、生命迹象等进行科学探索的旅程.作为太阳系中与地球最为相似的星球.火星带给人类无 穷的遐想.火星上是否存在生命,未来人类是否可以移民火星,磷作为重要的生命元素,在生命的整个进化过程具t不可替代的作用.磷酸盐可以作为-种潜在的生命标志物,为火星生命探测提供新的思路和线索.关键词火星,磷酸盐,生命探索中图分类号V476A P oten tial Biom arker P h osp h ate for Life E xplorationon M ars Biom arker for LifeZHAO Yufen1’2,3LIU Yan2HUANG Biling1GAO Xinchang3\[Instit,ute of Drug Discovery Technology, Qian Xuesen Collaborative Research Center of Astrochemistryand Space Life Science, Ningbo University, Ningbo315211)2(College of Chemistry and Chemical Engineering, Xiamen University, Xiamen361005)^(Department of Chemistry, Tsinghua University, Beijing100084)Abstract T h e e x p l o r a t i o n f o r e x t r a t e r r e s t r i a l life is o n e o f t h e m o s t i m p o r t a n t t a r g e t s o f d e e ps p a c e e x p l o r a t i o n.T h e s u c c e s s f u l l a u n c h o f C h i n a’s first M a r s p r o b e“T i a n w e n-1”h a s s t a r t e d t h e s c i e n t i f i c e x p l o r a t i o n a b o u t t h e s u r f a c e m o r p h o l o g y a n d life s i g n s o f M a r s.A s t h e m o s t s i m i l a r p l a n e t t o t h e e a r t h i n t h e s o l a r s y s t e m,M a r s b r i n g s h u m a n b e i n g e n d l e s s r e v e r i e.I s t h e r e life o n M a r s?C a n h u m a n b e i n g s i m m i g r a t e t o M a r s i n t h e f u t u r e?P h o s p h o r u s,o n e o f t h e i m p o r t a n t e l e m e n t s f o rlife, p l a y s a n i r r e p l a c e a b l e r o l e i n t h e w h o l e e v o l u t i o n o f life. P h o s p h a t e c a n b e u s e d a s a p o t e n t i a lb i o m a r k e r t o p r o v i d e n e w i d e a s a n dc l u e s f o r life e x p l o r a t i o n o n M a r s.Key words M a r s,P h o s p h a t e,L i f e e x p l o r a t i o n2020-11-06收到原稿E-mail: *****************.cn;**************.cn;*******************.cnDNARNABaseOHBaseOH OH〇引言2020年7月23日12时41分,在中国文昌航天 发射场,长征五号遥四运载火箭将中国第一个火星探 测器天问一号成功发射.随着天问一号直刺苍穹,中 国开启了对火星表面形貌、物质成分、生命迹象等进 行科学探索的旅程.1火星上是否存在生命2019年度诺贝尔物理学奖授予了吉姆■皮布尔 斯(Jam es P eeb les )、米歇尔.麦耶(M ichel M a y o r)和 迪迪埃.奎洛兹(D idier Q u e lo z )三位科学家,以表彰 他们在宇宙物理学和太阳系外行星领域做出的贡献. 迄今在银河系中已发现了 4000多颗系外行星,这些 系外行星的发现改变了地球在宇宙中的地位.这些 行星中有类似地球的岩石行星,地球在宇宙中是否独 一无二,其他行星中是否也存在生命尚未可知.火星上是否有生命存在对于人类未来在火星建 立基地,进行火星移民有着非常重要的意义.据中国 古籍中记载,火星被古人称为“荧惑”,意为不详之星, 而西方则认为火星是罗马战神,通常被称为红色星 球.火星是离太阳第四近的行星,是太阳系四颗类地 行星之一.科学家们发现在太阳系中火星是与地球 最为相似的星球.首先,火星所处轨道接近太阳系的 宜居地带,尽管现在的火星是一个干燥、寒冷、贫瘠 的星球,却可能在以前或者现在正孕育着生命;其次, 火星的地表环境砾石遍布,北部是平原而南部是布 满陨石坑的高地,其地表环境特征与地球极为相似; 第三,目前发现火星上存在少量水,并在火星盖尔陨 石坑内发现富含矿物盐的沉积物;第四,火星大气层130中存在甲烷,构成甲烷的碳、氢元素是地球生命出现 的基础.因此,火星上具备了与生命存在相关的基本 条件.但是,科学家们尚未发现火星上生命存在的标 记物,无法确认火星上是否有生命存在.2磷是遗传物质不可替代的基本元素生命由核酸、蛋白质等物质组成.遗传信息的传 递遵循遗传学中心法则,即遗传物质贮存于脱氧核糖 核酸(D NA ), D NA进行自我复制.将遗传信息传递给子代D N A ,子代D NA 经转录过程将遗传信息传递给核糖核酸(R N A ), R NA在核糖体中经翻译过程形成生命活动的主要承担者——蛋白质,从而将遗传 信息传递给了蛋白质.磷酸二酯键是构成DN A 和R N A的基本骨架(见图1),磷在核酸中的含量为9%. D N A作为遗传物质,要求其有足够的稳定性,遗传信息才能长期保存并代代传递.而磷在保证D N A稳定性方面起到了关键性作用.1987年W e s t h e i m e r W研究提出:DN A的半衰期为1〇5年;当由硫替代磷酸二酯键中的磷时,其 半衰期为2.7h ;当由硅或砷替代磷时其半衰期则仅 为1〜2 m i n ;而由矾替代磷时极其不稳定,几乎立即 水解.另外,磷酸二酯键及其负电荷性质保护了D N A不被水解,并且使其保留于细胞内而不会穿过磷脂细胞膜.由此可见,遗传物质DN A中的磷是不可替代的.因此,磷元素的存在也应是行星生命探索的必要 条件之一.地球上最古老的蛋白是37亿年前产生的AT P结合蛋白其次是磷转移蛋白.二者在地球上出现氧气之前便已存在.在地球早期海洋中,金属F e , Mn,Chin . J . Space Sci .空间科学学报 2021,41(1)〇|o LV O—=p -—o -io .i-〇l p —〇二〇〇图1D N A 与R N A 结构片段F ig. 1D N A a n d R N A s tru c tu r a l fra g m e ntsC o, Ni含量较高.这些金属可以催化偏三磷酸钠与腺苷反应,将腺苷转化为A T P l '而A T P可以诱导A T P 结合蛋白的产生.生物体的生命活动都必须 有AT P的参与.人体每天可以产生并消耗的AT P量与自身体重相当ATP结合盒转运体(A T P-b i n d i n gc a s s e t t e t r a n s p o r t e r , A B C转运体)是一类A T P结合蛋白,其利用AT P水解释放的能量执行转运细胞内外物质的功能.保证细胞营养物质的充 足与代谢产物的清除.A B C转运体若发生功能障碍,将V 某些疾病的发生密切相关,如阿尔兹海默症、谷固醇血症等【5】.由此可见,磷元素是生命体必不可少的基本元 素.是不可替代的生命元素.在原始生命的形成过程 中具有重要作用.3地球上的磷矿生物沉集中国主要磷矿形成于距今6.5亿至5.5亿年的震 旦纪晚期及寒武纪成矿年代,当时中国长江流域的四 川、陕西、贵州、云南、湖北等省还是一片汪洋大海. 古称扬子古海.气候温和、阳光充足.繁殖有大量的 藻类.扬子古海的磷矿源于海洋中的生物遗骸.经 过1亿年,蓝绿藻在海洋中沉积了超过105亿吨的 胶磷矿(平均每年沉积约100吨),占中国磷资源总量 的75%.因此.磷酸盐可能是生物的遗骸,应该是很 好的生命标志物.4火星上_的探测基丁-磷元素对生命的重要意义.1957年度的诺 贝尔化学奖获得者L o r d (A l e x a n d e r R ) To d d教授于1981年在日本大阪召开的一次国际会议上做了 一个主旨为:“哪里有生命,哪里就有憐”的精彩报 告,并提出••我猜想,如果宇宙的其他地方有生命存 在的话,那么极有可能是发生在具有充足磷元素的星球上”161.因此.磷酸盐是生命探索的一种潜在标志 物.对地外生命的探索.也需探究地外星球上是否有 憐的存在.2〇13 年 A^u r e G e o s c i e n c e发表了 A d c o c k 等丨的研究成果.他们认为.通过勇气号火星探测车的a 粒子X 射线光谱法测到火星表面有磷.火星上的磷赵玉芬等:火星生命探测中一种潜在的生物标志物磷醆盐不同于地球.地球上的磷矿石主要存在形式是氟磷 灰石C a 5(P 04)3F ,而氣离子对生物体是有毒性的.因 此,炼磷矿过程中需将氟离子去除,不含氟离子的磷 肥才可用尹促进农作物的生长.而火星磷矿石的主 要存在形式是氯磷灰石C a 5(P 04)3C I ,氯离子是与生 命体共存的.是生物体可以利用的基本元素.通过对 矿石的溶解速率与溶解度分别进行比较分析,发现氯 磷灰石释放磷的速率远快于氟磷灰石.火星上水-岩 相互作用时.磷酸盐的释放速率是地球上的45倍.早 期火星上潮湿环境中的磷酸盐浓度可能是早期地球 上的2倍这些都表明火星上的磷酸盐可利用性 高于地球.5火星上的磷是否来自生物氧存在三种稳定同位素:160. 170, 180.三者在 地球圈的含量分别为99.759%, 0.037%和0.204%.磷 酸根P〇i 广中的氧原子16〇对非生物过程的同位素交换有很强的抵抗力,即在没有生物或酶参与下.p〇r与其他物质发生氧同位素交换很慢.实验证据表明,羟基磷灰石来自骨骼和牙齿的磷酸根,其180 含量高,说明同位素可以快速交换.而非生物的磷矿 石和花岗石18〇含量低[8,91.生物几乎参与了磷循环的每个过程.酶是细胞活 性的指示物.酶催化的磷酸盐与水分子之间的氧同位 素交换表明生命的存在.L i a n g 等11U 1和B l a k e等I 11)提出,P 18〇疒的<518〇p 值可能提供了存在地外生命的重要生物特征.如果将火星上的磷矿石带回地球, 那么磷酸根P 18〇〗_的<518O p 值可以作为火星生命 探索的标志物.<518〇p 的定义I 11]为Q x 1_.(1)\ "VSMOWf18〇式中,"R sample 为样品中的比值,尺VSMOW 为维也纳标准平均海水(V i e n n a S t a n d a r d Me a nO c e a n18〇W a t e r, VS M O W)中元石的比值.因此,若能知道宇宙样品中磷酸盐中氧同位素f 8〇P 原始值,将样品的测量值W 该原始值进行 比较,即可获知该样品中的磷是否曾被生物利用,便 可探测生命是否存在.1316火星上的磷可否被生物利用火星上的磷水溶性很好,但是火星上的盐为高氯酸盐,地球上的生物不能直接利用,必须将高氯酸盐 还原分解为氯离子才能实现生物利用.例如,可以利 用耐辐射的特殊微生物将其还原分解为氯离子,并进 一步利用多种功能微生物将火星上的磷、氮及钾解 离出来.氮及钾对地球上的植物仍是必须的.可以设 想将多种极端生物,如地衣、水熊虫、嗜冷菌、嗜压 菌等有机结合成一个小型生态圈,实现对火星土壤及 磷资源的有效利用.虽然上面的描述仅仅是设想,但 是理论上是可行的,值得潜心尝试研究,以期为今后 的“火星移民”提供重要的理论支撑及实验验证.7展望由于火星与地球相似并具备一些适宜的条件,其可能是一个潜在的可居住环境.人类若考虑对外星 球进行移民,火星将是人类的首选星球.但是,火星 对人类来说充满了未知,火星过去是否有生命存在. 磷是否来自火星生物遗骸,地球上的生命能否利用火 星上的磷及其他原位资源来生存,这些重要课题亟待 人类去研究探索,并激发人类为之不懈努力.天问一 号的成功发射,必将为中国的火星探测乃至深空探测 的研究带来前所未有的惊喜和收获.参考文献[1] WESTHEIMER F H. Why nature chose phosphates [J].Science, 1987, 235:1173-1178132[2] KIM K M, QIN T, JIANG Y Y, et al. Protein domainstructure uncovers the origin of aerobic metabolism and the rise of planetary oxygen [J ].2012,20:67-76[3] CHENG C, FAN C, WAN R, et al. Phosphorylation of adenosine with trimetaphosphate under simulated pre- biotic conditions [J]. Orig. Life Evol. Biosph., 2002, 32:219-224[4] TORNROTH-HORSEFIELD S, NEUTZE R. Opening and closing the metabolite gate [J]. Proc. Natl. Acad. Sci., 2008, 105:19565-19566[5] TARLING E J, DE AGUIAR VALLIM T Q, EDWARDS P A. Role of ABC transporters in lipid transport and human disease [J]. Trends Endocrinol. Metab.^ 2013, 24:342-350[6] TODD L. Where There's Life, There's Phosphorus [M ]. Tokyo: Japan Sciencs Society Press, 1981:275-279[7] ADCOCK C T, HAUSRATH E M, FORSTER P M. Readily available phosphate from minerals in early aqueous environments on Mars[J]. Nat. Geosci., 2013. 6:824- 827[8] SCHWARTZ A W. Phosphorus in prebiotic chemistry [J].Philos. Trans. R. Soc. Lond. B. Biol. Sci., 2006, 361: 1743-1749[9] LECUYER C, GRANDJEAN P, SHEPPARD S M F. Oxygen isotope exchange between dissolved phosphate and water at temperatures ( 135°C: inorganic versus biological fractionations [J]. Geochim. Cosmochim. Ac., 1999, 63:855-862[10] LIANG Y, BLAKE R E. Oxygen isotope fractionation between apatite and aqueous-phase phosphate: 20~45°C [J]. Chem. Geol, 2007, 238: 121-133[11] BLAKE R E, ALT J C, MARTINI A M. Oxygen isotoperatios of PO 4: an inorganic indicator of enzymatic activity and P metabolism and a new biomarker in the search for life[J]. Proc. Natl. Acad. Sci., 2001. 98:2148-2153Chin . J . Space Sci .空间科学学报 2021, 41(1)。

斯威特柱后衍生系统原理

斯威特柱后衍生系统原理解析1. 背景介绍斯威特柱后衍生系统(Swivel Posterior Derivation System)是一种用于语言模型的后处理技术。

在自然语言处理中,语言模型是指能够预测下一个词或者短语的模型。

斯威特柱后衍生系统通过对已生成的文本进行修正和改进,提高了生成文本的质量和流畅度。

2. 基本原理斯威特柱后衍生系统基于以下两个基本原理来进行文本修正和改进:2.1 后验概率调整在生成文本时,语言模型会根据上下文预测下一个词或短语。

然而,由于训练数据的限制以及模型复杂度等因素,语言模型可能会产生一些不合理或不流畅的词组。

斯威特柱后衍生系统通过计算每个词组出现的条件概率,并与一个经验阈值进行比较,来判断该词组是否需要调整。

如果该词组出现的条件概率低于经验阈值,则认为需要对其进行调整。

具体地,在判断一个词组是否需要调整时,斯威特柱后衍生系统会考虑以下几个因素: - 词组的上下文信息:词组出现的上下文信息对该词组的合理性有很大影响。

如果一个词组在给定的上下文中不够合理,那么可能需要进行调整。

- 词组的频率信息:如果一个词组在训练数据中出现的频率较低,那么它可能是一种不常见或者不合理的表达方式,需要进行调整。

- 词组的语法信息:如果一个词组违反了语法规则,那么它可能需要进行调整。

基于以上因素,斯威特柱后衍生系统可以计算出一个后验概率,用于判断是否需要对该词组进行调整。

如果后验概率低于经验阈值,则认为该词组需要调整。

2.2 调整算法当判断出一个词组需要调整时,斯威特柱后衍生系统会使用一种基于统计和规则的算法来对其进行修正。

具体地,在修正过程中,系统会考虑以下几个因素: - 上下文信息:通过分析上下文中其他相关的词汇和短语,系统可以更好地判断该词组应该如何调整。

- 语法规则:根据语法规则,系统可以调整词组的顺序、形态和结构,使其更符合语言的规范。

- 语义信息:通过分析词组的语义信息,系统可以对其进行合理的替换或修改。

ai药化设计

ai药化设计AI药化设计是指利用人工智能技术来进行药物化学设计和优化的过程。

药物化学设计是一种通过改造和优化化学分子结构,以获得具有理想药效和选择性的药物的方法。

AI药化设计能够加速药物发现的过程,提高药物研发的效率和成功率。

通过AI药化设计,科学家可以利用机器学习和深度学习算法来预测药物分子的性质和活性,指导研究人员在设计和合成新药分子时作出最优化的选择。

AI药化设计可以快速筛选药物候选物,减少实验室试错带来的时间和成本开销,并提高研发过程中的智能化和自动化程度。

AI药化设计的方法主要包括药物分子的筛选、设计和生成。

首先,通过分析已知有效药物的结构特征,建立药物化学和生物学的相关数据库。

然后,利用机器学习算法学习和预测药物分子的性质和活性,筛选出潜在的药物候选物。

接下来,利用深度学习模型生成新的药物分子结构,并通过模拟和预测对其进行评估。

最后,通过合成化学的方法合成并测试这些新的药物候选物,验证其理论预测结果。

AI药化设计在现代药物研发中发挥着重要作用。

它可以加速药物发现的节奏,提高药物研发的效率。

借助AI药化设计,科学家可以更好地理解药物在生物体内的作用机制,针对疾病发展的特点设计出更具针对性和选择性的药物分子。

与传统的试错方法相比,AI药化设计具有更高的准确性和可预测性,有助于减少研究人员的主观判断和经验依赖。

总之,AI药化设计是一种利用人工智能技术来进行药物化学设计和优化的方法。

它可以加速药物研发过程,提高研发效率和成功率。

随着人工智能和机器学习技术的不断发展,相信AI药化设计将在未来的药物研发中发挥越来越重要的作用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。