集成电路IC测试简介ppt课件

集成电路IC测试简介

FT设备示例FT equipment

• Tester测试机

• Load Board/Socket/Handler

➢其测试系统称为ATE,由电子电路和机械硬 件组成,是由同一个主控制器指挥下的电 源、计量仪器、信号发生器、模式(pattern )生成器和其他硬件项目的集合体,用于 模仿被测器件将会在应用中体验到的操作

成测示意图FT schematic

diagram

Contact chuck

Contact blade

测试相关术语 Test technicalities

• CP - Circuit probing(晶圆测试、中测) • FT - Final test (成品测试) • ATE - Automatic Test Equipment(自动测试

设备) • DUT - Device Under Test(被测器件) • DIB - Device Interface Board / Load board(

集成电路测试简 介

Brief instruction of IC Test

目录catalog

IC制造工艺流程简介 IC测试定义与术语 中测简介 成测简介

IC制造工艺流程 ( I ) IC MFG process flow

Product

Design

Design House

Front End

Dut socket

TESTER

Test Head

Load board

Han

• Handler 必须与 tester意相图连接(docking)及接上interface才能进 行测试, 动作过程为handler的手臂将 DUT 放入socket,此时 contact chuck下压, 使 DUT的脚正确与 socket 接触后, 送出 start 讯号, 透过 interface tester, 测试完后, tester 送回 binning 及EOT 讯号; handler 做分类动作。客户产品的尺寸 及脚数不同, handler 提供不同的模具 (kits) 供使用。

IC测试简介

IC测试简介1.什么是IC?IC即集成电路(integrated circuit)是一种微型电子器件或部件。

采用一定的工艺,把一个电路中所需的晶体管、二极管、电阻、电容和电感等元件及布线互连一起,制作在一小块或几小块半导体晶片或介质基片上,然后封装在一个管壳内,成为具有所需电路功能的微型结构。

2.什么是IC 测试?IC测试就是用相关的电子仪器(如万用表、示波器、直流电源,ATE等)将IC所具备的电路功能、电气性能参数测试出来。

测试的项目一般有:直流参数(电压、电流)、交流参数(频率)、功能测试等。

3.为什么要进行IC测试?IC测试是为了检测IC在设计和制造过程中,由于设计不完善、制造工艺偏差、晶圆质量环境污染等因素,造成IC功能失效、性能降低等缺陷。

通过分析测试数据,找出失效原因,并改进设计及工艺,以提高良率及产品质量,是IC产业中至关重要的.4. IC测试分类及区别?IC测试分为晶圆测试(或叫CP:Chip Probing)和成品测试(或叫FT:Final Test).CP与FT的区别CP在整个制程中算是半成品测试,目的有2个,1个是监控前道工艺良率,是对整片Water的每个DIE来测试可以直接的知道Wafer的良率.另1个是降低后道成本(避免封装过多的坏芯片,其能够测试的项比FT要少些。

最简单的一个例子,碰到大电流测试CP肯定是不测的(探针容许的电流有限),这项只能在封装后的FT测。

FT是对package进行测试检查封装厂制造的工艺水平。

一般来说,如果测试时间很长,cp和ft又都能测,像trimming项,加在PROBE能显著降低时间成本.但是有些PAD会封装到IC内部,FT无法测到,只能通过cp测试,例如功率管的gate端漏电流测试。

CP与FT的测试项目很多是完全一样的;不同的是卡的SPEC不同而已;因为封装都会导致参数飘移,所以cp SPEC 收的要比FT更紧以确保最终成品的良率.5.如何进行IC 测试?在wafer加工完成后,送至中测车间用探针卡(probecard)、探针台(probe)、测试机(ATE:Automatic Test Equipment )对wafer中的每颗裸芯片进行电气参数的测试,并按照一定的规范进行筛选,分出好坏裸片的过程。

集成电路测试PPT课件

7

故障的等效和从属

故障等效

s-a-1

A

B

&

C

s-a-0

Z

故障从属

s-a-0

A

B

&

C

s-a-1

Z

12.11.2020

故障类型与测试码

测试码 ABC Z 11 1 0

01 1 1 10 1 1 11 0 1

故障

A/0, B/0, C/0, Z/1 A/1,Z/0 B/1,Z/0 C/1,Z/0

8

基本概念2:测试向量和测试图形

故障:集成电路不能正常工作。 故障模型:物理缺陷的逻辑等效。

12.11.2020

5

故障举例

物理缺陷

逻辑等效

12.11.2020

6

逻辑门故障模型

固定值逻辑:所有缺陷都表现为逻辑门 层次上线网的逻辑值被固定为0或者1。 表示:s-a-1, s-a-0。

桥接 逻辑门故障模型的局限性

12.11.2020

f

(X)

•

d dxi

g(X)

g(X)

•

d dxi

f

(X)

d dxi

f (X)• d dxi

g(X)

d dxi

f

(X)

g(X)

f

(X)

•

d dxi

g(X)

g(X)

•

d dxi

f

(X)

d dxi

f (X)• d dxi

g(X)

12.11.2020

22

差分法

如果g(X)与xi无关,则可以简化为:

esets

Tester_Stro 2

2

集成电路IC测试简介课件-新版.ppt

Test Head

CP示意图

PIB Probe Card

Wafer Probe Chuck Prober

Interface

当 probe card 的探针正确接触wafer 內一颗 die的每个 bond pads 后, 送出Start 讯号透过 Interface 给 tester 开始测试, tester 完成测试送回分类讯号( End of test) 给Prober, 量产时必须 tester 与 prober 做连接(docking) 才能测试。

Board Insertion& Assembly

Board Test

Finish Goods

Program

精选

Circuit Probing

Final Test Drop Ship

IC 测试定义Definition of IC Test

IC测试的定义 IC测试是通过测量IC的输出响应,将其与预期的输出相比较,以评估IC器件电性能的过

集成电路测试简介

Brief instruction of IC Test

精选

目录catalog

IC制造工艺流程简介 IC测试定义与术语 中测简介 成测简介

精选

IC制造工艺流程 ( I ) IC MFG process flow

Product

Design

Design House

Front End

精选

CP设备示例CP equipment

Probe探针台

Probe Card针卡

精选

成测 Final Test

晶圆被切割成独立的电路单元,且每个单元都被封装出来后,需要经历此测试以验 证封装过程的正确性并保证器件仍然能达到它的设计指标,也称为“Final Test”、 Package Test、FT测试、成品测试等。

集成电路介绍PPT课件

11.TQFP 扁平簿片方形封装 12.TSOP 微型簿片式封装 13.CBGA 陶瓷焊球阵列封装 14.CPGA 陶瓷针栅阵列封装 15.CQFP 陶瓷四边引线扁平 16.CERDIP 陶瓷熔封双列 17.PBGA 塑料焊球阵列封装 18.SSOP 窄间距小外型塑封 19.WLCSP 晶圆片级芯片规 模封装 20.FCOB 板上倒装片

也较大;

• (4)外部引脚容易在芯片的插拔过程当中损坏,不 太适用于高可靠性场合;

• (5)DIP封装还有一个致命的缺陷,那就是它只适 用于引脚数目小于100 的中小规模集成电路。

5.1 直插式

17

. 2019/11/4

衡量一个芯片封装技术先进与否的重要 指标是芯片面积与封装面积之比R,这个比 值越接近l越好。

2019/11/4

集成电路简要介绍

一、集成电路定义

2

. 2019/11/4

二、集成电路特点

三、集成电路发展

四、集成电路分类

五、集成电路封装技术

一、集成电路定义

3

. 2019/11/4

• 集成电路(Integrated Circuit,简称IC)是20世纪 60年代初期发展起来的一种新型半导体器件。把 构成具有一定功能的电路所需的半导体、电阻、 电容等元件及它们之间的连接导线全部集成在一 小块硅片上,然后焊接封装在一个管壳内的电子 器件。

以采用40根I/O引脚塑料双列直插式封 装(PDIP)的CPU为例,其芯片面积/封装面积 R=(3×3)/(15.24×50)=1:86,离l相差 很远。这种封装尺寸远比芯片大,说明封装 效率很低,占去了很多有效安装面积。

5.2 表面贴装式

1SOP封装

5.2 表面贴装式

集成电路IC测试简介课件.ppt

中测 Circuit Probing

当晶圆制造过程完成,Wafer上每个die都必须经过测试。测试一片晶圆称为“Circuit probe”(即常说的CP,芯片测试)、“Wafer probe”或者“Die sort”。

在这个过程中,每个Die都被测试以确保它能基本满足器件的特征或设计规格 (Specification),通常包括电压、电流、时序和功能的验证。

。。

成测示意图FT schematic diagram

Contact chuck

TESTER

Contact blade Dut socket

Test Head

ቤተ መጻሕፍቲ ባይዱ

Load board

Handler

Interface

FT示意图

Handler 必须与 tester 相连接(docking)及接上interface才能进行测试, 动作过程 为handler的手臂将 DUT 放入socket,此时 contact chuck下压, 使 DUT的脚正确 与 socket 接触后, 送出start 讯号, 透过 interface tester, 测试完后, tester 送回 binning 及EOT 讯号; handler 做分类动作。客户产品的尺寸及脚数不同, handler 提供不同的模具 (kits) 供使用。

程。它是验证产品性能、监控生产状况、分析产品实效的重要手段。 为何要进行IC测试? IC的制造工艺永远无法达到100%的良率,为验证IC功能的正常与完整性,在其上系统前,

需先进行测试,剔除不良品以降低成本的损失。

。。

测试相关术语 Test technicalities

CP - Circuit probing(晶圆测试、中测) FT - Final test (成品测试) ATE - Automatic Test Equipment(自动测试设备) DUT - Device Under Test(被测器件) DIB - Device Interface Board / Load board(负载板,用于成测) Die - An individual site on a wafer (指晶圆上的芯片) PIB - Probe Interface Board (用于中测) BIN - Sorting the DUTs dependant upon test results (指给所测芯片分类) Handler - 自动分选机,用于成测中自动分类已测芯片的机器 Prober - 探针台,中测中用于晶圆测试的机器

集成电路可测性原理与设计PPT课件

– 测试只保留了低15位数据, 因此并不排除更高位有 错误数据无法被发现的可能。虽然这种可能性比较 小。

2020/12/18

9

2.产品测试

• 产品测试与样品测试不同, 目的在于如何让 机器用统一固定的算法来解决大量电路的 快速测试问题和为“故障定位”提供可能。

2020/12/18

19

“或非”门测试因子的计算

Y = X1X2 CC1(Y) = CC0(X1) + CC0(X2) + 1 CC0(Y) = min[ CC1(X1), CC1(X2) ] + 1 CO(X1) = CC0(X2) + CO(Y) + 1 CO(X2) = CC0(X1) + CO(Y) + 1 SC0(Y) = min[ SC1(X1), SC1(X2) ] SC1(Y) = SC0(X1) + SC0(X2) SO(X1) = SC0(X2) + SO(Y) SO(X2) = SC0(X1) + SO(Y)

1. 样品测试

– 人工进行 – 测试时间充裕 – 测试方法自由

2. 产品测试

– 机器测试 – 测试时间折进产品成本(有时比制造成本还高) – 测试代码编写

2020/12/18

4

1.样品的测试

• 大规模IC, 其输入/输出管脚众多。

• 理论上, 只有“穷尽”了输入信号的所有组 合, 并验证了输出信号相应无误后, 才能断 定此电路是合格产品。

2020/12/18

ቤተ መጻሕፍቲ ባይዱ

25

复杂电路的可测性设计(DFT)

• 对于组合电路

集成电路测试概述PPT课件

寿命缺陷——电介质崩溃、电迁移 等。

封装缺陷——触点退化、密封泄露 等。

第6页/共48页

集成电路的不正常状态

• 缺陷(defect) • 故障(fault) • 失效(failure)

集成电路的缺陷导致它的功能发 生变化

第7页/共48页

➢ 成品检测进行随机抽 样,对样品做入厂测 试。

第36页/共48页

按测试目的分类

•

验证测试(特性测试)

•

生产测试

•

验收测试(成品检测)

•

使用测试

系统RMS(Reliability ,Maintainability,Serviceability) 技术的需要。使用测试是在器件使用期间进行的测 试,包括对器件进行各类可靠性试验后的评价测试, 系统使用过程出现故障进行故障芯片检测和定位所 进行的测试等

测试框架结构

➢ 在生产阶段,管芯制 成后和封装后都要进 行电性能和参数测试, 包括性能鉴定、可靠 性试验和失效分析等 测试。 ➢ 作用: 对产品 进行挑 选和分 级;剔 除失效 的芯片;

第44页/共48页

测试框架结构

测试的费用往往会随器件级、板级、 系统级和现场故障寻迹维修测试, 按每级10倍的递增量而逐级递增,

故障检测和故障诊断的首要问题

• 测试图形的生成 • 测试生成过程要能迅速准确地得到测试码,并且能判断测试码的有效性,还要保证测试码尽量简单,必须

讨论测试码与测试图形的各种生成方法和集成电路的各类故障模型。

第19页/共48页

第20页/共48页

• 集成电路测试的基本原理 • 集成电路故障与测试 • 集成电路测试过程 • 集成电路测试分类 • 集成电路测试的意义与作用 • 半导体技术的发展对测试的影响

集成电路的认识与检测PPT课件

集成电路直接代换时,集成电路的功能、性能指标、封装形式、引脚用途、引脚序号和间隔等几 方面均相同。其中应该注意逻辑极性相同,即输出输入电平极性、电压、电流幅度必须相同。代换时 若输出不同极性AFT电压或者输出不同极性的同步脉冲的集成电路都不能直接代换,即使是同一公司 或厂家的产品,都应注意区分。性能指标是指集成电路的主要电参数、最大耗散功率、最高工作电压、 频率范围及各信号输入、输出阻抗等参数要与原集成电路相近。

集成电路的认识与检测

精选ppt课件2021

1

什么是集成电路

集成电路是将一个单元电路或者是多个单元电路的主要元器件或者全部的元器件 集成在一个单晶硅片上,并封装在特制的外壳中,具备一定功能的电路,其在结构上 已经组成了一个整体。

精选ppt课件2021

2

集成电路的分类

1、按功能结构分类

集成电路按其功能、结构的不同,可以分为模拟集成电路、数字集成电路和数/ 模混合集成电路三大类。

安装集成电路时,要注意方向不要搞错,否则,通电时集成电路很可能被烧毁。而且要注意,有 的单列直插式功放集成电路,虽型号、功能、特性相同,但引脚排列顺序的方向是有所不同的。

不同型号的集成电路,若型号前缀字母相同、数字不同集成电路的代换,只要相互间的引脚功能 完全相同,其内部电路和电参数稍有差异,也可相互直接代换;若型号前缀字母不同、数字相同的集 成电路,一般情况下,前缀字母是表示生产厂家及电路的类别,前缀字母后面的数字相同,大多数可 以直接代换。但也有少数,虽数字相同,但功能却完全不同,这样的不能代换。

模拟集成电路又称线性电路,用来产生、放大和处理各种模拟信号,其输入信号 和输出信号成比例关系。目前,在家电维修中或一般性电子制作中,所遇到的主要是 模拟信号。而数字集成电路用来产生、放大和处理各种数字信号。

IC基本知识PPT课件

1,模拟集成电路(电源IC,运放,A/D等) 2,数字集成电路(如MCU,DSP等)

(二)导电类型分类:

1,双极型集成电路(bipolar工艺复杂,功耗大) 2,单极型集成电路(COMS电路简单,功耗小)

(三)通用和专用IC

.

2

IC的制造流程

1,晶圆处理工序(Wafer Fabrication) 2,晶圆针测工序(Wafer Probe) 3,构装工序(Packaging) 4,测试工序(Initial Test and Final Test)等

.

4

IC的制造过程

1,晶圆处理制程:在晶圆上制作电路和电子组件(如晶体 管,电容体,逻辑电路等)

2,晶圆针测制程:晶粒(Die)经过针测(Probe)仪器测试 其电气特性

3,IC构装制程:利用塑料或陶瓷包装晶粒与配线以成集成电 路

4,测试制程:可分为初步测试和最终测试,划分不同的IC等 级,保证产品质量;

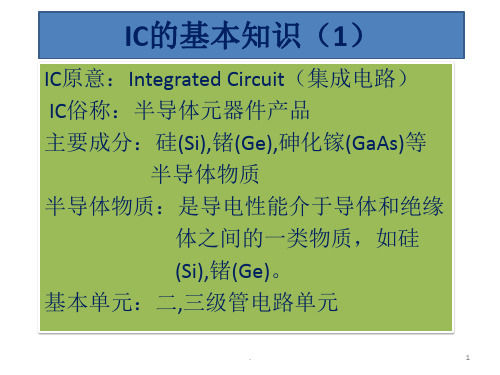

IC的基本知识(1)

IC原意:Integrated Circuit(集成电路) IC俗称:半导体元器件产品 主要成分:硅(Si),锗(Ge),砷化镓(GaAs)等

半导体物质 半导体物质:是导电性能介于导体和绝缘

体之间的一类物质,如硅 (Si),锗(Ge)。 基本单元:二,三级管电路单元

.

1

IC的分类

.

5

IC的设计方法

1,正向设计和反向设计 2,自顶向下(Top-down)和自底向上设计

(Bottom-up)

.

6

正向设计和反向设计

.

7

自顶向下和自底向上设计

.

8

IC的设计流程

1,设计输入:电路图和硬件描述语言

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

IC的制造工艺永远无法达到100%的良率,为验证IC功能的正常与完整性,在其上系统前, 需先进行测试,剔除不良品以降低成本的损失。

5

测试相关术语 Test technicalities

CP - Circuit probing(晶圆测试、中测) FT - Final test (成品测试) ATE - Automatic Test Equipment(自动测试设备) DUT - Device Under Test(被测器件) DIB - Device Interface Board / Load board(负载板,用于成测) Die - An individual site on a wafer (指晶圆上的芯片) PIB - Probe Interface Board (用于中测) BIN - Sorting the DUTs dependant upon test results (指给所测芯片分类) Handler - 自动分选机,用于成测中自动分类已测芯片的机器 Prober - 探针台,中测中用于晶圆测试的机器

Wafer Fab

Back End

Board Assembly

Probing

Assembly

Test

Board Assembly

IC Design Test

Materials Wafer

Program Fab

Bank

Wafer

Fab

Wafer Sort

Die Bank

Assembly Final Test Drop Ship

集成电路测试简介

1

Brief instruction of IC Test

2

目录catalog

IC制造工艺流程简介 IC测试定义与术语 中测简介 成测简介

3

IC制造工艺流程 ( I ) IC MFG process flow

Product

Design

Design House

Front End

6

中测 Circuit Probing

➢ 当晶圆制造过程完成,Wafer上每个die都必须经过测试。测试一片晶圆称为“Circuit probe”(即常说的CP,芯片测试)、“Wafer probe”或者“Die sort”。

➢ 在这个过程中,每个Die都被测试以确保它能基本满足器件的特征或设计规格 (Specification),通常包括电压、电流、时序和功能的验证。

ห้องสมุดไป่ตู้

10

成测示意图FT schematic diagram

Contact chuck

TESTER

Contact blade Dut socket

Test Head

Load board

Handler

Interface

FT示意图

Handler 必须与 tester 相连接(docking)及接上interface才能进行测试, 动作过程 为handler的手臂将 DUT 放入socket,此时 contact chuck下压, 使 DUT的脚正确 与 socket 接触后, 送出start 讯号, 透过 interface tester, 测试完后, tester 送回 binning 及EOT 讯号; handler 做分类动作。客户产品的尺寸及脚数不同, handler 提供不同的模具 (kits) 供使用。

8

CP设备示例CP equipment

Probe探针台

Probe Card针卡

9

成测 Final Test

晶圆被切割成独立的电路单元,且每个单元都被封装出来后,需要经历此测试以验 证封装过程的正确性并保证器件仍然能达到它的设计指标,也称为“Final Test”、 Package Test、FT测试、成品测试等。

Board Insertion& Assembly

Board Test

Finish Goods

Program

Circuit Probing

Final Test Drop Ship

4

IC 测试定义Definition of IC Test

IC测试的定义

IC测试是通过测量IC的输出响应,将其与预期的输出相比较,以评估IC器件电性能的过 程。它是验证产品性能、监控生产状况、分析产品实效的重要手段。

➢ 如果某个Die不符合规格,那么它会被测试过程判为失效(Fail),通常会用墨点(Ink)将 其标示出来(也可以通过Mapping图来区分)。

晶圆顶端平缺口,用 以确保生产测试方向 一致

Bin mapping

坏的Die被墨点标 示出来

7

中测示意图CP schematic diagram

Tester

11

FT设备示例FT equipment

Tester测试机

Load Board/Socket/Handler

Test Head

CP示意图

PIB Probe Card

Wafer Probe Chuck Prober

Interface

当 probe card 的探针正确接触wafer 內一颗 die的每个 bond pads 后, 送出Start 讯号透过 Interface 给 tester 开始测试, tester 完成测试送回分类讯号( End of test) 给Prober, 量产时必须 tester 与 prober 做连接(docking) 才能测试。

➢ 其测试系统称为ATE,由电子电路和机械硬件组成,是由同一个主控制器指挥下的 电源、计量仪器、信号发生器、模式(pattern)生成器和其他硬件项目的集合体, 用于模仿被测器件将会在应用中体验到的操作条件,以发现不合格的产品。

➢ 测试系统硬件由运行一组指令(测试程序)的计算机控制,在测试时提供合适的电 压、电流、时序和功能状态给DUT并监测DUT的响应,对比每次测试的结果和预先 设定的界限,做出pass或fail的判断。