DS90C385A

液晶显示器易损芯片故障列表

FPD87326 LG PHILIPS IC

GVS690H9 液晶 IC

HX8912TA 液晶 IC

LPD91821 三星液晶屏专用

LRE031212A LTM170EU-L21 的屏主芯片

LRU4312X1A 三星多款17 寸屏主芯片,损坏率高

LXD91810

LXD91811 三星14,15 寸屏主芯片,白屏、花屏、灰色竖条、无显示,可代替91812,91810

LXD91812

LXD91814

LXD91820

MST8116B CMV 和BENQ 等、液晶主芯片,此IC 损坏率高,出现故障:花屏、白屏、连接信号线无显示等

TSU16AK 图像信号处理芯片

单片机

NT68F63 三星,冠捷等液晶MCU

NT68F633 PHILIPS

WT61P4 三星液晶MCU

W78E65 冠捷常用,可代替M6759,SM5964

液晶显示器易损芯片故障列表

AAT1101A M150XN05 屏电源管理芯片,损坏后表现为白屏‘开机图像暗淡等

AAT1164 M170EG01 新款屏通病,主要用在明基FP71G+液晶显示器上面。用一段时间会白屏、关机在开用一段时间又出现白 .本芯片为液晶屏高压产生及管理芯片、明基液晶显示器常坏、故障为:白屏。

MST8131A MST8131A MST8111B MST8111A

此四个型号通用,联想\宏基\BENQ 等液晶显示器主芯片,此IC 损坏率高,出现故障:花 、白屏、连接信号线无显示等

NT68521 4 合1 电视板芯片

RTD2023 LVDS 图像信号处理芯片,M170EP01-2.0 版一体屏和多个厂家驱动板使用。

液晶电视的原理与维修

液晶电视的原理与维修液晶:又称LCD,是利用液状晶体在电压的作用下发光成像的原理。

组成屏幕的液状晶体有三种:红、绿、蓝,叫做三基色,它们按照一定的顺序排列,通过电压来刺激这些液状晶体,就可以呈现出不同的颜色,不同比例的搭配可以呈现出千变万化的色彩。

因此,精确到“点”的液晶电视比“逐行扫描”的普通电视又高出了一个层次。

高清晰、高亮度、宽视角、影像逼真、画质细腻而富立体感是液晶电视带给观者的第一印象;而轻薄、省电、无闪烁、无辐射亦是液晶电视傲视传统CRT彩电之处;同时,液晶电视的接口也极为丰富,可接驳电脑、DVD等音视频设备,现在一些厂家还将读取Flash卡的功能整合进了液晶电视,这也让液晶电视具备了更多的数码味道。

使用的是和笔记本电脑及台式电脑平板显示器相同的显示技术。

其生动的画面是由一个造价不菲的特殊玻璃嵌板以及上面的晶体管生成的。

不过这种电视价格昂贵,特别是超过40英寸的大尺寸液晶电视。

一些液晶电视在从侧面观看时,画面也不是十分清楚。

目前国内市场上的液晶电视主要以15-32吋为主,也有42吋的超大液晶电视销售。

1.显示器整机无电这是一个应该说是非常简单的故障,一般的液晶显示器分机内电源和机外电源两种,机外的常见一些。

不论那种电源,它的结构比crt显示器的电源简单多了,易损的一般是一些小元件,象保险管、输入电感、开关管、稳压二极管等。

比较少见的故障是由主板cpu引起的电源不启动,这部分其实原理也比较简单,就是通过键控板到cpu,再通过cpu输出一个控制信号驱动电源变换集成电路工作。

2.显示屏亮一下就不亮了,但是电源指示灯常亮这种问题一般是高压异常造成的,是保护电路动作了,在这种情况下,一般液晶屏上是有显示的,看的方法是“斜”。

检修的要点是对比修理法。

因为,现在的液晶显示器的高压板的设计一般都是对称的设计,而两边都坏的可能基本上没有。

一般老机容易出问题的是升压变压器和灯管,新机的保护电路和工艺问题比较的多。

思科德技术.Samsung S5PV210开发板说明

三星 S5PV210 技术方案提供商

可以实现 2000DMIPS(每秒 2 亿指令集)的高性能运算能力 采用 45nm 低功率制程,CPU 典型功耗 11mW

GPU 图形芯片

内建高性能 PowerVRSGX5403D 图形引擎和 2D 图形引擎 多边形生成率为 2800 万多边形/秒,像素填充率可达 2.5 亿/秒, 支持 DX9、SM3.0、OpenGL2.0 等 PC 级别显示技术 2D 图形加速,最大支持 8000*8000 分辨率图片。 JPEG 硬件编解码,最大支持 65536*65536 分辨率图片 IVA3 硬件加速器,支持全高清、多标准的视频编码,流畅播录 1080p 视频文件

PCB 规格

6 层板

2/3

三星 S5PV210 技术方案提供商

沉金工艺

软件资源

Kernel 2.6.35 源码 Android 2.3.5 源码 bootloader 源码 按键驱动 RTC 驱动 看门狗驱动 I2C 驱动 USB TP 驱动 9.7 LCD 驱动 USB HUB 驱动 HDMI 驱动 GC2015 Camera 驱动 WM8960 音频播放、录音驱动 NC024 WIFI、蓝牙驱动 PWM 背光驱动 外置 TF 卡驱动 内置 INAND 驱动 串口驱动 ADC 电池电量检测驱动 USB 转以太网芯片 DM9620 驱动 SPI 接口驱动 MMA8452 重力芯片感应驱动 2D、3D 显示驱动 JPEG 硬件编解码驱动 MFC 视频处理驱动 视频硬件编解码驱动 耳机插入检测驱动 电池充电检测驱动 背光控制驱动

硬件资源

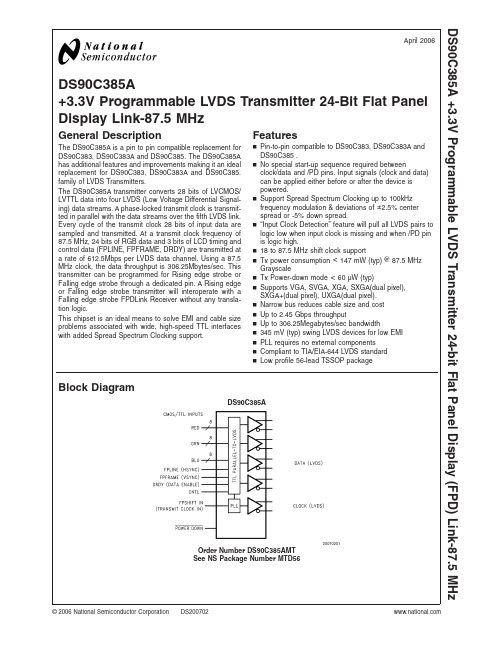

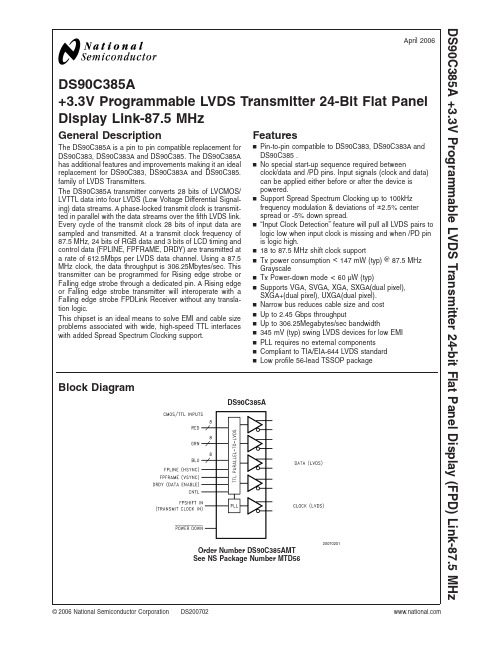

CPU:S5PV210 内存:DDR2 512MB 内置存储:INANAD 4G 显示接口:LVDS(DS90C385A) 背光控制芯片:MP3302 复位芯片:STM6603,有延时复位功能 外置 TF 卡接口 单独可充电 RTC 锂电池 WIFI/BT 芯片: NC024 音频芯片:WM8960,3.5 标准耳机接口 内置 MIC 左右声道喇叭各一 摄像头:GC2015 200 万像素 USB-HUB 芯片:USB2514B(4 路 USB-HOST 接口) TP 接口:支持 USB 和 I2C 方式 G-Sensor:MMA8452 电池接口 电池充电控制芯片:HB6298B 系统按键:power、音量+、音量-、home、锁屏幕旋转键 HDMI 接口:A 型 调试串口 电源开关 OTA 接口:MicroUSB

飞利浦液晶电视常见故障及排查

飞利浦液晶电视维修常见故障及排查1、显示器整机无电1电源故障:这是一个应该说是非常简单的故障,一般的液晶显示器分机内电源和机外电源两种,机外的常见一些.不论那种电源,它的结构比crt显示器的电源简单多了,易损的一般是一些小元件,象保险管、整流桥.300V滤波电容、电源开关管、电源管理IC,整流输出二极管,滤波电容等.电源板常用ic:6841203d06,这些常用的pmw芯片在我这样的专业液晶配件店里都能买到.2驱动板故障:驱动板烧保险或者是稳压芯片出现故障,有部分机器是把开关电源内置,输出两组电源,其中一组是5V,供信号处理用,另外一组是12V提供高压板点背光用,如果开关电源部分电路出现了故障会有可能导致两组电源均没输出.先查12V电压正常否,跟着查5V电压正常否,因为A/D驱动板的MCU芯片的工作电压是5V,所以查找开不了机的故障时,先用万用表测量5V电压,如果没有5V电压或者5V 电压变得很低,那么一种可能是电源电路输入级出现了问题,也就是说12V 转换到5V的电源部分出了问题,这种故障很常见,检查5端稳压块常见型号8050SD-LM2596-AIC15-01等.另一种可能就是5V的负载加重了,把5V 电压拉得很低,换一种说法就是说,后级的信号处理电路出了问题,有部分电路损坏,引起负载加重,把5V电压拉得很低,逐一排查后级出现问题的元件,替换掉出现故障的元件后,5V能恢复正常,故障一般就此解决,也经常遇到5V电压恢复正常后还不能正常开机的,这种情况也有多种原因,一方面是MCU的程序被冲掉可能会导致不开机,还有就是MCU本身损坏,比如说MCU的I/O口损坏,使MCU扫描不了按键,遇到这种由MCU引起的故障,找硬件的问题是没有用的,就算你换了MCU也解决不了问题,因为MCU是需要编程和写码的,在没办法找到原厂的AD驱动板替换的情况下,我们只能用通用A/D驱动板代换如:151D或161B等.2、显示屏亮一下就不亮了,但是电源指示灯绿灯常亮这种问题一般是高压异常造成的,是保护电路动作了,在这种情况下,一般液晶屏上是有显示的,看的方法是"斜视".,飞利浦液晶电视维修;3、显示屏黑屏,无背光.电源灯绿灯常亮斜视液晶屏有显示图像,多属于高压板供电电路问题.重点检查12V供电保险丝F和3V或5V的开关电压是否正常.若是因为MCU问题造成没有输出开关控制电压,可以直接提取3端稳压块的AIC10843.3V代替.修理高压板的思路电源保险丝----开关控制管----电源管理IC----推挽发大管----电源开关管----DA转换电路储能电感,整流管---LC升压电路升压变压器,升压电容------耦合电容----灯管.4、屏幕亮线,亮带或者是暗线这种问题,一般是液晶屏的故障.亮线故障一般是连接液晶屏本体的排线出了问题或者某行和列的驱动IC损坏.暗线一般是屏的本体有漏电,或者TAB柔性板连线开路.以上两种问题基本上就是给机器判了死刑了,没有维修价值的,因为一块屏的价格太高了.广州有专门更换码片的,收费极高,返修率也高.5、花屏或者是白屏这种问题一般是屏的驱动电压出了问题,先换驱动板和驱屏线试验,若不行检查屏背板供电电路,维修思路:驱动板5V转3.3V的稳压块AIC1084是否有供电输出.---屏体驱动板保险丝F-3.3V-----DC-DC 转换电路----负压形成IC-7V----行,列驱动IC.AAT1101AM150XN05屏电源管理芯片,损坏后表现为白屏'开机图像暗淡等AAT1164M170EG01新款屏通病,主要用在明基FP71G+液晶显示器上面.用一段时间会白屏、关机在开用一段时间又出现白屏.本芯片为液晶屏高压产生及管理芯片、明基液晶显示器常坏、故障为:白屏.AAT1343LG、PHILIPS屏用,开机白屏、花屏、竖条等AD8567友达屏用,白屏AU30707友达屏用,白屏、花屏、图像淡AU30803友达屏用,白屏、花屏、图像淡AUO-003M170EG01屏,主供电短路、开机白屏或画屏、开机彩色失真、彩色竖条等DS90C385MTDFPD87326LGPHILIPS 屏ICGVS690H9HX8912TALPD91821三星液晶屏专用LRE031212ALTM170EU-L21的屏上主芯片LRU4312X1ALXD91810LXD91811LXD91814LXD91820MST8116BCMVBENQ等、液晶显示器主芯片,此IC损坏率高,出现故障:花屏、白屏、连接信号线无显示等MST8131AMST8131AMST8111BMST8111A通用,联想宏基BENQ等、液晶显示器主芯片,此IC损坏率高,出现故障:花屏、白屏、连接信号线无显示等NT68521RTD2023SE7889-LF三星液晶显示器驱动板主芯片,此IC损坏率高,出现故障:花屏SN0209033PZPLG.Philips液晶屏专用LM170E01TFP7425PTL2272MLTSU16AK6、偏色故障一般可以进入工厂调整模式进行调整.如没有此模式,维修思路:更换屏线和转接板-----重写驱动程序-----驱动板坏不常见-----屏背板的控制IC坏不常见--------拔掉屏线观察背光颜色背光扁色为灯管老化-------换灯管.7、字符虚或拖尾8、LCD屏幕内部有污点维修思路:擦拭或更换换保护膜-----拆开屏体清洗外层偏光片和有机玻璃用棉球,纯净水处理---风筒吹干9、LCD屏漏光或光线不均维修思路:重新安装灯管-----调整导光板10、LCD屏亮点一个或二个大的亮点,可以尝试轻轻用指尖压亮点,可消失,说明多为此象素的开关管和电极虚连.小的黑点和灰点有可能是内部导光板或偏光片有灰尘造成.可清洗处理.以上方法在试验时要先征取客户同意,才可操作,否则后果自付,一切责任与我老康无关.11、LCD屏亮度低检查高压板ADJ亮度调节电路----------换灯管--------换高压板--------调整或更换导光板12、错误提示"超出频率范围"检查信号线--------重写MCU驱动程序-------更换EPROM------重写EPROM程序-----换驱动板13、通电后不按开关按键即白屏出现背光,按键后图像可正常显示高压板接口的开关信号和ADJ信号反接造成,部分属于驱动板MCU的开关信号输出不正常,可以重写MCU程序修复.-------换MCU对于灯管老化的屏更换时要搞清灯管的尺寸,因为尽管屏幕尺寸一样,但是灯管长度与粗细略有差异,在找不到相同尺寸灯管的时候,如果能用短灯则好,如果不能使用,稍长的的灯管用手术刀小心切除屏框,并用热缩管做好绝缘.液晶常见故障与维修要领下面就是一台液晶显示器的结构和所有的配件1、PANEL液晶屏2、A/D驱动板;3、液晶驱屏线4、高压板又称升压板、高压条、INVERTER5、高压板线材6、电源适配器外置,一般都用直流3A/12V,也有部分的显示器的开关电源部分内置在机内的,直接输入AC220V以下是根据我们日常的维修总结的一些维修思路:检修的方法可用单灯高压板接一个灯管试验,,批发零售液晶电视挂架底座电视挂架挂架;因为,现在的液晶显示器的高压板的设计一般都是对称的设计,而两边都坏的可能基本上没有.一般老机容易出问题的是某一路的电源管,升压管,升压变压器和灯管短路或空载,而造成的电源管理IC负载均衡保护.看到高压板接口有这么多条线,很多初学者认为更换很复杂,其实很简单,只需要4个信号接到高压板即可:1,电源.2,地.3,开关控制ON/OFF.4,ADI亮度调节.首先确定电源线正极和负极,有保险丝的一般来说是正极,负极多是接在电容的负极上.然后确定电压,确定电压的最好办法是看电容的标记了,假如6V左右那么就是3.3V的,假如电容上标12V左右,那么输入电压肯定是5V,假如是24V左右或以上,那么就是12V,以次类推,把电容上所标的伏数除以二,最接近几伏就是几伏了.有的人说按这样接了,还是不亮,或者只是闪一下就灭了,是的有很多高压板多是这样的,那怎么办呢找出控制脚,看看那只脚是接到一个小三极管上的,一般是直接引接到三极管上的,最多中间有个小电容,应该很容易辨认的,控制脚一般是3.3V和5V,也有个别是接地的,所以我们在不知道的情况下,先接地试一下,不行再接3.3V再接5V,假如输入电压和控制电压多是3.3V的情况是,可以直接合并.多余的脚怎么办呀让他空着好了,不用理它.。

lvds液晶屏幕接口详解

1.LVDS输出接口概述液晶显示器驱动板输出的数字信号中,除了包括RGB数据信号外,还包括行同步、场同步、像素时钟等信号,其中像素时钟信号的最高频率可超过28MHz。

采用TTL接口,数据传输速率不高,传输距离较短,且抗电磁干扰(EMI)能力也比较差,会对RGB数据造成一定的影响;另外,TTL多路数据信号采用排线的方式来传送,整个排线数量达几十路,不但连接不便,而且不适合超薄化的趋势。

采用LVDS输出接口传输数据,可以使这些问题迎刃而解,实现数据的高速率、低噪声、远距离、高准确度的传输。

那么,什么是LVDS输出接口呢?LVDS,即Low Voltage Differential Signaling,是一种低压差分信号技术接口。

它是美国NS公司(美国国家半导体公司)为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研制的一种数字视频信号传输方式。

LVDS输出接口利用非常低的电压摆幅(约350mV)在两条PCB走线或一对平衡电缆上通过差分进行数据的传输,即低压差分信号传输。

采用LVDS输出接口,可以使得信号在差分PCB线或平衡电缆上以几百Mbit/s的速率传输,由于采用低压和低电流驱动方式,因此,实现了低噪声和低功耗。

目前,LVDS输出接口在17in及以上液晶显示器中得到了广泛的应用。

2.LVDS接口电路的组成在液晶显示器中,LVDS接口电路包括两部分,即驱动板侧的LVDS输出接口电路(LVDS发送器)和液晶面板侧的LVDS输入接口电路(LVDS接收器)。

LVDS发送器将驱动板主控芯片输出的17L电平并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过驱动板与液晶面板之间的柔性电缆(排线)将信号传送到液晶面板侧的LVDS接收器,LVDS接收器再将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。

图1所示为LVDS接口电路的组成示意图。

图1 LVDS接口电路的组成示意图在数据传输过程中,还必须有时钟信号的参与,LVDS接口无论传输数据还是传输时钟,都采用差分信号对的形式进行传输。

DS90C385AMTX中文资料

µA

31

45

mA

37

50

mA

48

60

mA

55

65

mA

2

DS90C385A

元器件交易网

Electrical Characteristics (Continued)

Over recommended operating supply and temperature ranges unless otherwise specified.

Duration

Continuous

Junction Temperature

+150˚C

Storage Temperature

−65˚C to +150˚C

Lead Temperature

(Soldering, 4 sec)

+260˚C

Maximum Package Power Dissipation Capacity @ 25˚C

f = 25 MHz f = 40 MHz f = 65 MHz f = 87.5 MHz

Min Typ Max Units

2.0

VCC

V

0

0.8

V

−0.79 −1.5

V

+1.8 +10

µA

−10

0

µA

250 345 450

mV

35

mV

1.13 1.25 1.38

V

35

mV

−3.5 −5

mA

±1 ±10

Block Diagram

DS90C385A

Order Number DS90C385AMT See NS Package Number MTD56

LVDS驱动芯片

?在液晶显示器中,LVDS接口电路包括两部分,即驱动板侧的LVDS输出接口电路(LVDS发送器)和液晶面板侧的LVDS输入接口电路(LVDS接收器)。LVDS发送器将驱动板主控芯片输出的17L电平并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过驱动板与液晶面板之间的柔性电缆(排线)将信号传送到液晶面板侧的LVDS接收器,LVDS接收器再将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。图1所示为LVDS接口电路的组成示意图。

3.LVDS输出接口电路类型

与TTL输出接口相同,LVDS输出接口也分为以下四种类型:

(l)单路6位LVDS输出接口

这种接口电路中,采用单路方式传输,每个基色信号采用6位数据,共18位RGB数据,因此,也称18位或18bitLVDS接口。此,也称18位或18bitLVDS接口。

(2)双路6位LVDS输出接口

应该注意的是,液晶面板的输入信号中都必须要有DE信号,但有的液晶面板只使用单一的DE信号而不使用行场同步信号。因此,应用于不同的液晶面板时,有的LVDS发送芯片可能只需输入DE信号,而有的需要同时输入DE和行场同步信号。

②输入时钟信号:即像素时钟信号,也称为数据移位时钟(在LVDS发送芯片中,将输入的并行RGB数据转换成串行数据时要使用移位寄存器)。像素时钟信号是传输数据和对数据信号进行读取的基准。

在供8bit液晶面板使用的五通道LVDS发送芯片中,共有二十四个RGB信号输入引脚,分别是红基色数据R0~W(8bit红基色数据,R0为最低有效位,R7为最高有效位)八个,绿基色数据G0~G7八个,蓝基色数据B0~B7八个;一个有效显示数据使能信号DE(数据有效信号)输入引脚;一个行同步信号HS输入引脚;一个场同步信号VS输入引脚;一个各用输入引脚。也就是说,在五通道LVDS发送芯片中,共有二十八个数据信号输入引脚。

lvds液晶屏幕接口详解

1.LVDS输出交心概括之阳早格格创做液晶隐现器启动板输出的数字旗号中,除了包罗RGB数据旗号中,还包罗止共步、场共步、像素时钟等旗号,其中像素时钟旗号的最下频次可超出28MHz.采与TTL交心,数据传输速率没有下,传输距离较短,且抗电磁搞扰(EMI)本领也比较好,会对付RGB数据制成一定的做用;其余,TTL多路数据旗号采与排线的办法去传递,所有排线数量达几十路,没有单连交便当,而且没有符合超薄化的趋势.采与LVDS输出交心传输数据,不妨使那些问题迎刃而解,真止数据的下速率、矮噪声、近距离、下准确度的传输.那么,什么是LVDS输出交心呢?LVDS,即Low V oltage Differential Signaling,是一种矮压好分旗号技能交心.它是好国NS公司(好国国家半导体公司)为克服以TTL电仄办法传输宽戴下码率数据时功耗大、EMI电磁搞扰大等缺面而研制的一种数字视频旗号传输办法.LVDS输出交心利用非常矮的电压晃幅(约350mV)正在二条PCB走线大概一对付仄稳电缆上通过好分举止数据的传输,即矮压好分旗号传输.采与LVDS输出交心,不妨使得旗号正在好分PCB线大概仄稳电缆上以几百Mbit/s的速率传输,由于采与矮压战矮电流启动办法,果此,真止了矮噪声战矮功耗.暂时,LVDS输出交心正在17in及以上液晶隐现器中得到了广大的应用.2.LVDS交心电路的组成正在液晶隐现器中,LVDS交心电路包罗二部分,即启动板侧的LVDS输出交心电路(LVDS收支器)战液晶里板侧的LVDS 输进交心电路(LVDS交支器).LVDS收支器将启动板主控芯片输出的17L电仄并止RGB数据旗号战统制旗号变换成矮电压串止LVDS旗号,而后通过启动板与液晶里板之间的柔性电缆(排线)将旗号传递到液晶里板侧的LVDS交支器,LVDS交支器再将串止旗号变换为TTL电仄的并止旗号,支往液晶屏时序统制与止列启动电路.图1所示为LVDS交心电路的组成示企图.图1 LVDS交心电路的组成示企图正在数据传输历程中,还必须奇尔钟旗号的介进,LVDS 交心无论传输数据仍旧传输时钟,皆采与好分旗号对付的形式举止传输.所谓旗号对付,是指LVDS交心电路中,每一个数据传输通道大概时钟传输通道的输出皆为二个旗号(正输出端战背输出端).需要证明的是,分歧的液晶隐现器,其启动板上的LVDS 收支器没有尽相共,有些LVDS收支器为一片大概二片独力的芯片(如DS90C383),有些则集成正在主控芯片中(如主控芯片gm5221内里便集成了LVDS收支器).3.LVDS输出交心电路典型与TTL输出交心相共,LVDS输出交心也分为以下四种典型:(l)单路6位LVDS输出交心那种交心电路中,采与单路办法传输,每个基色(即RGB三色中的其中所有一种颜色)旗号采与6位数据(XOUT0+、TXOUT0-,TXOUT1+、TXOUT1-,TXOUT2+、TXOUT2-),共18位RGB(6bit X 3(RGB3色))数据,果此,也称18位大概18bit LVDS交心.此,也称18位大概18bit LVDS 交心.(2)单路6位LVDS输出交心那种交心电路中,采与单路办法传输,每个基色旗号采与6位数据,其中奇路数据为18位,奇路数据为18位,共36位RGB数据,果此,也称36位大概36bit LVDS交心.(3)单路8位1TL输出交心那种交心电路中,采与单路办法传输,每个基色旗号采与8位数据(XOUT0+、TXOUT0-,TXOUT1+、TXOUT1-,TXOUT2+、TXOUT2-,TXOUT3+,TXOUT3),共24位RGB 数据(8bit X 3),果此,也称24位大概24bit LVDS交心.(4)单路8位1TL输出位交心那种交心电路中,采与单路办法传输,每个基色旗号采与8位数据,其中奇路数据为24位,奇路数据为24位,共48位RGB数据,果此,也称48位大概48bit LVDS交心4.典型LVDS收支芯片介绍典型的LVDS收支芯片分为四通道、五通道战十通道几种,底下简要举止介绍.(1)四通道LVDS收支芯片图2 所示为四通道LVDS收支芯片(DS90C365)内里框图.包罗了三个数据旗号(其中包罗RGB、数据使能DE、止共步旗号HS、场共步旗号VS)通道战一个时钟旗号收支通道.图2 4通道LVDS收支芯片内里框图4通道LVDS收支芯片主要用于启动6bit液晶里板.使用四通道LVDS收支芯片不妨形成单路6bit LVDS交自电路战奇/奇单路6bit LVDS交心电路.(2)五通道LVDS收支芯片图3 所示为五通道LVDS收支芯片(DS90C385)内里框图.包罗了四个数据旗号(其中包罗RGB、数据使能DE、止共步旗号IIS、场共步旗号vs)通道战一个时钟旗号收支通道.图3 5通道LVDS收支芯片内里框图五通道LVDS收支芯片主要用于启动8bit液晶里板.使用五通道LVDS收支芯片主要用去形成单路8bit LVDS交心电路战奇/奇单路8bit LVDS交心电路.(3)十通道LVDS收支芯片图4所示为十通道LVDS收支芯片(DS90C387)内里框图.包罗了八个数据旗号(其中包罗RGB、数据使能DE、止共步旗号HS、场共步旗号VS)通道战二个时钟旗号收支通道.图4 十通道LV DS收支芯片内里框图十通道LVDS收支芯片主要用于启动8bit液晶里板.使用十通道LYDS收支芯片主要用去形成奇/奇单路8bit LVDS位交心电路.正在十通道LVDS收支芯片中,树坐了二个时钟脉冲输出通道,那样搞的手段是不妨越收机动的符合分歧典型的LVDS 交支芯片.当LVDS交支电路共样使用一片十通道LVDS交支芯片时,只需使用一个通道的时钟旗号即可;当LVDS交支电路使用二片五通道LVDS交支芯片时,十通道LYDS收支芯片需要为每个LVDS交支芯片提供单独的时钟旗号.5.LVDS收支芯片的输进与输出旗号(1)LVDS收支芯片的输进旗号LVDS收支芯片的输进旗号去自决控芯片,输进旗号包罗RGB数据旗号、时钟旗号战统制旗号三大类.①数据旗号:为了证明的便当,将RGB旗号以及数据选通DE战止场共步旗号皆算做数据旗号.正在供6bit液晶里板使用的四通道LVDS收支芯片中,公有十八个RGB旗号输进引足,分别是R0~R5白基色数据(6bit 白基色数据,R0为最矮灵验位,R5为最下灵验位)六个,G0~G5绿基色数据六个,B0~B5蓝基色数据六个;一个隐现数据使能旗号DE(数据灵验旗号)输进引足;一个止共步旗号HS输进引足;一个场共步旗号VS输进引足.也便是道,正在四通道LYDS收支芯片中,公有二十一个数据旗号输进引足.正在供8bit液晶里板使用的五通道LVDS收支芯片中,公有二十四个RGB旗号输进引足,分别是白基色数据R0~W(8bit白基色数据,R0为最矮灵验位,R7为最下灵验位)八个,绿基色数据G0~G7八个,蓝基色数据B0~B7八个;一个灵验隐现数据使能旗号DE(数据灵验旗号)输进引足;一个止共步旗号HS输进引足;一个场共步旗号VS输进引足;一个各用输进引足.也便是道,正在五通道LVDS收支芯片中,公有二十八个数据旗号输进引足.该当注意的是,液晶里板的输进旗号中皆必须要有DE旗号,然而有的液晶里板只使用简单的DE旗号而没有使用止场共步旗号.果此,应用于分歧的液晶里板时,有的LVDS收支芯片大概只需输进DE旗号,而有的需要共时输进DE战止场共步旗号.②输进时钟旗号:即像素时钟旗号,也称为数据移位时钟(正在LVDS收支芯片中,将输进的并止RGB数据变换成串止数据时要使用移位寄存器).像素时钟旗号是传输数据战对付数据旗号举止读与的基准.③待机统制旗号(POWER DOWN):当此旗号灵验时(普遍为矮电通常),将关关LVDS收支芯片中时钟PLL锁相环电路的供电,停止IC的输出.④数据与样面采用旗号:用去采用使用时钟脉冲的降下沿仍旧下落沿读与所输进的RGB数据.有的LVDS收支芯片大概本去没有树坐待机统制旗号战数据与样面采用旗号,然而也有的除了上述二个统制旗号还树坐有其余一些统制旗号.(2)LVDS收支芯片的输出旗号LVDS收支芯片将以并止办法输进的TTL电仄RGB数据旗号变换成串止的LVDS旗号后,曲交支往液晶里板侧的LVDS 交支芯片.LVDS收支芯片的输出是矮晃幅好分对付旗号,普遍包罗一个通道的时钟旗号战几个通道的串止数据旗号.由于LVDS收支芯片是以好分旗号的形式举止输出,果此,输出旗号为二条线,一条线输出正旗号,另一条线输出背旗号.①时钟旗号输出:LVDS收支芯片输出的时钟旗号频次与输进时钟旗号(像素时钟旗号)频次相共.时钟旗号的输出常表示为:TXCLK+战TXCLK-,时钟旗号占用LVDS收支芯片的一个通道.②LVDS串止数据旗号输出:对付于四通道LVDS收支芯片,串止数据占用三个通道,其数据输出旗号常表示为TXOUT0+、TXOUT0-,TXOUT1+、TXOUT1-,TXOUT2+、TXOUT2-.对付于五通道LVDS收支芯片,串止数据占用四个通道,其数据输出旗号常表示为TXOUT0+、TXOUT0-,TXOUT1+、TXOUTI-,TXOUT2+、TXOUT2-,TXOUT3+、TXOUT3-.对付于十通道LVDS收支芯片,串止数据占用八个通道,其数据输出旗号常表示为TXOUT0+、TXOUT0-,TXOUT1+、TXOUT1-,TXOUT2+、TXOUT2-,TXOUT3+、TXOUT3-,TXOUT4+、TXOUT4-,TXOUT5+、TXOUT5-,TXOUT6+、TXOUT6-,TXOUT7+、TXOLT7-.如果只瞅电路图,是没有克没有及从LVDS收支芯片的输出旗号TXOUT-、TXOUT0+中瞅出其内里到底包罗哪些旗号数据,以及那些数据是何如排列的(大概者道那些数据的圆法是何如的).究竟上,分歧厂家死产的LVDS收支芯片,其输出数据排列办法大概是分歧的.果此,液晶隐现器启动板上的LVDS收支芯片的输出数据圆法必须与液晶里板LVDS交支芯片央供的数据圆法相共,可则,启动板与液晶里板没有匹配.那也是调换液晶里板时必须思量的一个问题.博家面拔LVDS收支芯片正在一个时钟脉冲周期内,每个数据通道皆输出7bit的串止数据旗号,而没有是罕睹的8bit数据,如图5所示图5LVDS交心电路正在一个时钟脉冲周期内传输7bit数据(3)LVDS收支芯片输出旗号的圆法LVDS收支芯片输出旗号的圆法,即LVDS收支芯片输进的RGB数据,以及止共步旗号HS、场共步旗号VS、灵验隐现数据使能旗号DE正在各个输出通道中数据位的排列程序.由于几个大的LYDS芯片死产厂家制定了分歧的尺度,果此,存留着几种分歧的LVDS收支芯片数据输出圆法,正在调换液晶隐现器启动板大概调换液晶里板时,必须弄浑LVDS交心液晶里板所央供的LVDS旗号圆法,使液晶隐现器启动板侧LVDS 收支芯片的输出数据圆法与液晶里板LVDS交支芯片所央供的数据圆法相共.①单路6bit LVDS收支芯片数据输出圆法:单路6bit LVDS收支电路使用四通道LVDS收支芯片,输出旗号圆法如图6所示.图6 单路6bit LVDS收支芯片数据输出圆法图6中NA的意义是已使用.此例为统制旗号仅使用DE的模式,已使用止共步旗号HS战场共步旗号VS.关于DE、IIS、VS旗号的使用问题,将正在第9章举止介绍.当统制旗号为DE+止场共步旗号模式时,图中的二个NA调换为场共步旗号VS战止共步旗号HS.②单路6bit LVDS收支芯片数据输出圆法:单路6bit LVDS 收支电路使用二片四通道LVDS收支芯片,输出旗号圆法如图7所示.图7 单路6bit LVDS收支芯片数据输出圆法从图7中不妨瞅出,单路6bit LVDS收支芯片数据输出圆法与单路6bit LVDS收支芯片数据输出圆法是相共的,只没有过一路传递奇数像素RGB数据,另工路传递奇数像素RGB数据.OR0、OR1、…中的“O”代表奇数像素,ER0、ER1、…中的“E”代表奇数像素.③单路8bit LVDS收支芯片数据输出圆法:单路8bit LVDS收支电路使用五通道LVDS收支芯片,输出旗号圆法有多种,底下只介绍其中的二种.图8所示是其中的一种输出旗号圆法.图9所示是爆收那种数据旗号圆法的电路交法.图8 单路8bit LVDS收支芯片数据输出圆法之一图9 所示数据输出圆法的电路交法图10 所示为单路8bit LVDS收支芯片的另一种数据输出圆法.图10 单路8bit LVDS收支芯片数据输出圆法之二图11 所示圆法中的统制旗号仅使用DE模式,当统制旗号为DE+止场共步旗号模式时,第二数据通道TXOUT2中的二个NA应调换为场共步旗号VS战止共步旗号HS(通过对付启动板编程可改写).从以上二种输出圆法中不妨瞅出,数据旗号的排列程序没有共很大,没有过,要念让其排列普遍,真足不妨通过对付启动板编程去完毕.图11 单路8bit LVDS收支芯片数据输出圆法之一④单路8bit LVDS收支芯片数据输出圆法:单路8bit LVDS收支电路使用二片五通道LVDS收支芯片大概一片十通道LVDS收支芯片,单路8bit LVDS收支芯片数据输出圆法也有多种形式,图11所示是其中的一种.上头咱们了解了屏的型号战交心了,然而是咱们还没有了解那个是几位的屏战几的供电,为了让大家沉快搞会那一步,咱们拿一个单6位LVDS的屏去剖析一下,此款屏的型号为:LP141X3(20针插交心)屏交心定义正在液晶屏那内里出现了二组数据每组中皆有一对付时钟旗号,那个屏咱们便能瞅出那是一个30针单8位屏,屏的供电为5V.罕睹的LVDS交心定义20PIN单6定义:1:电源2:电源3:天4:天5:R0 6:R0+ 7:天8:R1 9:R1+ 10:天11:R2 12:R2+ 13:天14:CLK 15:CL K+ 16空17空18空19空20空每组旗号线之间电阻为(数字表100欧安排)指针表20-100欧安排(4组相共阻值)20PIN单6定义:1:电源2:电源3:天4:天5:R0 6:R0+ 7:R1 8:R1+ 9:R2 10:R2+ 11:CLK 12:CLK+ 1 3:RO1 14:RO1+ 15:RO2 16:RO2+ 17:RO3 18:RO 3+ 19:C L K120:C L K1+每组旗号线之间电阻为(数字表100欧安排)指针表20-100欧安排(8组相共阻值)20PIN单8定义:1:电源2:电源3:天4:天5:R0 6:R0+ 7:天8:R1 9:R1+ 10:天11:R2 12:R2+ 13:天14:C L K15:C L K+16:R317:R3+ 每组旗号线之间电阻为(数字表100欧安排)指针表20-100欧安排(5组相共阻值)30PIN单8定义:1:电源2:电源3:电源4:空5:空6:空7:天8:R0 9:R0+ 10:R1 11:R1+ 12:R2 13:R2+ 14:天15:CLK 16:CLK + 17:天18:R3 19:R3+ 20:RB0 21:RB0+ 22:RB1 2 3:RB1+ 24:天25:RB2 26:RB2+ 27:CLK2 28:C L K2+29:R B330:R B3+ 每组旗号线之间电阻为(数字表100欧安排)指针表20-100欧安排(10组相共阻值)普遍14PIN、20PIN、30PIN 为LVDS交心,15寸(含15寸)以下多为3.3V供电17(含17)以上多为5V供电.那不过罕睹屏是那样程序,而没有是所有的皆是那样.罕睹TTL的屏交心定义列:那是一个罕睹的41扣TTL的屏交心去瞅瞅与LVDS 的屏有什么辨别(屏型号为M12153DS 41扣单六位TTL屏)知识面:TTL交心的屏线明隐比LVDS的屏线多罕睹31扣41扣30+50 60扣70扣80扣TTL的屏也有单组数据战单组数据之分以此类推便不妨了罕睹TTL屏线D6T(单6位TTL):31扣针,41扣针.对付应屏的尺寸主要为条记原液晶屏(8寸,10寸,11寸,12寸),另有部分台式机屏15寸为41扣针交心.S6T(单6位TTL):30+45针硬排线,60扣针,70扣针,80扣针.主要为台式机的14寸,15寸液晶屏.S8T(单8位TTL):有,很少睹80扣针(14寸,15寸)。

风速传感器介绍

厦华LC29K6型液晶电视数字板 及视频处理板主要IC介绍

"程国强

1. 数字板的主要集成电路介绍

如图 4 所示。主要作用是:把主解码芯片 U12 输出的

(1)DVI 接口及 A/D 转换处理电路 U15(TFP403P), 1024×768/60 Hz 的 TFT 信号转换为 LCD 液晶屏能显

图 4 风速传感器 AFS- 0001 的外观形貌( 二) 2. 使用锗热敏电阻器的风速传感器 使用锗热敏电阻器的风速传感器是一种可以同时 测量风速和风温的风速传感器。使用锗热敏电阻器进 行风速和风温的测量,可以测量 0.05~10 m/s 的风 速,以及 0~+50℃的风温。 通常,风速传感器的输出电压与风速的关系不是 直线性的,所以需要有线性化电路。为此而生产了专用 的信号变换器。 在图 5~图 8 中给出了使用锗热敏电阻器的风速 传感器的外观形貌。

图 11 QB 型的球状风速器件

图 9 SL 系列( 上) 与 NL 系列( 下) 风速传感器

4. 可以测量表面风速的风速传感器探头 这种传感器探头可以测量无法安装传统探头处 的表面风速。可以绕轴 360°进行无指向性测量,测量 范围是 0.01~30 m/s 的风速与 0~+50℃的风温。由 于是在提供测试物体的表面用双面黏胶带粘贴上以 后使用的,因此粘贴夹具和提供测试的物体表面都不 需要进行加工。 另外,市场上还出售有一种最多能够连接 960 个 这种风速传感器通道,可以同时进行多点测量风速与 风温的单元。 在图 10~图 12 中给出了表面风速传感器探头的 外观形貌。

这种风速传感器组件使用的风速探头是薄膜铂电

阻。温度补偿电路位于传感器的内部,所以可以得到与

实战维修,液晶屏维修方法,逻辑板维修经验几十列

实战维修,液晶屏维修⽅法,逻辑板维修经验⼏⼗列HSD190MGW1-AXX屏拖影严重与开机花屏横竖线的维修⽅法近⽇接到⼀个优派VA1903MB液晶屏,有时⼀次能正常图像的,但⼀关屏再开机⼜是线了。

经⽹上查找次料,很多⼈的HSD190MGW1屏都是拖尾严重的通病。

经本⼈的总结经验如下屏前左下⾓有6个检测点,主要是测量由上到下数的5、6点的检测点,第5点正常值是21.8V,第6点的正常值是负10.1V .第5点电压不正常就会引起屏拖尾严重。

第6点电压不正常就会引起开机花屏横竖线或有1/3横竖线的问题。

这两个电压在屏上都可以找到,VGL =-10.1V VGH-M=21.8V我是找根很⼩的漆包线⼀头去漆,不要太长哦!找⼀快⿊⾊的软胶能压缩的那种,在DVD机上⽤来顶住机盖或主板的那种,只要能压缩的不导电的就可以了,不⽤调什么导电胶了,切成⾼度要⾼⼀点因为要借助屏的⾦属架的压⼒把漆包线和检测点接通。

放的时候你找点双⾯粘胶粘到软胶的⼀⾯上,放好漆包的和检测点的位置,然后把有粘胶的⼀⾯粘下去就好了。

再⽤屏的⾦属架压住装上缧丝就OK了。

这块屏可能很多⼈都遇到过,图像反应巨慢!且⾊彩失真,论坛⾥也有前辈谈论过解决办法就是飞线VGH-M电压到屏,看似简单,难就难在玻璃屏上如何固定飞线,今⽇刚好花了50块钱回收⼀台19宽屏冠捷就是这失败⽽放弃了!⼿⾥有导电银漆,本店以修本为主,修液晶为辅的业务,于是发挥了导电银漆的威⼒,终极解决这类故障!1.HSD190MGW1-A00 REV:1屏,通电试机先是⽩屏然后慢慢⾊彩出现。

最后到⼀定程度就是⾊彩失真拆开盖位于屏的左下⾓有六个测试点,从上往下我量的电压为1.53V 0.78V 3.25V -9.9V -0.55V -9.93V。

对照⽹上别⼈所测的电压,参考了下有⼏处不对,不知道他的是不是对的,我也不管这么多了,以从上往下第处。

刷,OK。

此前曾经修好过⼀个过样的屏。

只是故障现象有所不同。

lvds液晶屏幕接口详解

1.LVDS输出接口概述液晶显示器驱动板输出的数字信号中,除了包括RGB数据信号外,还包括行同步、场同步、像素时钟等信号,其中像素时钟信号的最高频率可超过28MHz。

采用TTL接口,数据传输速率不高,传输距离较短,且抗电磁干扰(EMI)能力也比较差,会对RGB数据造成一定的影响;另外,TTL 多路数据信号采用排线的方式来传送,整个排线数量达几十路,不但连接不便,而且不适合超薄化的趋势。

采用LVDS输出接口传输数据,可以使这些问题迎刃而解,实现数据的高速率、低噪声、远距离、高准确度的传输。

那么,什么是LVDS输出接口呢?LVDS,即Low Voltage Differential Signaling,是一种低压差分信号技术接口。

它是美国NS公司(美国国家半导体公司)为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研制的一种数字视频信号传输方式。

LVDS输出接口利用非常低的电压摆幅(约350mV)在两条PCB走线或一对平衡电缆上通过差分进行数据的传输,即低压差分信号传输。

采用LVDS输出接口,可以使得信号在差分PCB线或平衡电缆上以几百Mbit/s的速率传输,由于采用低压和低电流驱动方式,因此,实现了低噪声和低功耗。

目前,LVDS输出接口在17in及以上液晶显示器中得到了广泛的应用。

2.LVDS接口电路的组成在液晶显示器中,LVDS接口电路包括两部分,即驱动板侧的LVDS输出接口电路(LVDS发送器)和液晶面板侧的LVDS输入接口电路(LVDS接收器)。

LVDS发送器将驱动板主控芯片输出的17L电平并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过驱动板与液晶面板之间的柔性电缆(排线)将信号传送到液晶面板侧的LVDS接收器,LVDS接收器再将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。

图1所示为LVDS接口电路的组成示意图。

图1 LVDS接口电路的组成示意图在数据传输过程中,还必须有时钟信号的参与,LVDS接口无论传输数据还是传输时钟,都采用差分信号对的形式进行传输。

ds90c385A-386开发板

FPD-Link Evaluation Kit User’s Manual NSID FLINK3V8BT-85Rev 3.0Table of ContentsINTRODUCTION (3)CONTENTS OF EVALUATION KIT (4)APPLICATIONS (4)FEATURES AND EXPLANATIONS.................................................................................. T RANSMITTER (7)R ECEIVER (12)HOW TO HOOK UP THE DEMO BOARDS (OVERVIEW) (6)TRANSMITTER BOARD (7)S ELECTABLE J UMPER S ETTINGS FOR THE T X B OARD (8)LVDS M APPING BY IDC C ONNECTOR (9)T X O PTIONAL:P ARALLEL T ERMINATION FOR T X IN (10)BOM(B ILL OF M ATERIALS) (11)RECEIVER BOARD (12)S ELECTABLE J UMPER S ETTINGS FOR THE R X B OARD (13)LVDS M APPING BY IDC C ONNECTOR (14)R X O PTIONAL:S ERIES T ERMINATION FOR R X O UT (15)BOM(B ILL OF M ATERIALS) (16)TYPICAL CONNECTION / TEST EQUIPMENT (17)T YPICAL W AVESHAPES (19)TROUBLESHOOTING (21)ADDITIONAL INFORMATION (22)A PPLICATION N OTES (22)APPENDIX (23)T RANSMITTER AND R ECEIVER S CHEMATICS (24)Introduction:National Semiconductor - Interface Products Group FPD-Link evaluation kit contains a Transmitter (Tx) board, a Receiver (Rx) board along with interfacing cables. This kit will demonstrate the DS90C385A/DS90CF386 chipsets interfacing from test equipment or a graphics controller using Low Voltage Differential Signaling (LVDS) to a receiver board.The Transmitter board accepts LVTTL/LVCMOS RGB signals from the graphics controller along with the clock signal. The LVDS Transmitter converts the LVTTL/LVCMOS parallel lines into four serialized LVDS data pairs plus a LVDS clock. The serial data streams toggle at 3.5 times the clock rate.The Receiver board accepts the LVDS serialized data streams plus clock and converts the data back into parallel LVTTL/LVCMOS RGB signals and clock for the panel timing controller.The user needs to provide the proper RGB inputs and clock to the Transmitter and also provide a proper interface from the Receiver output to the panel timing controller or test equipment. A cable conversion board or harness scramble may be necessary depending on type of cable/connector interface used. A power down feature is also provided that reduces current draw when the link is not required.Contents of the Evaluation Kit:1) One Transmitter board with the DS90C385AMTD - 28 bit Transmitter2) One Receiver board with the DS90CF386MTD - 28 bit Receiver3) One 20-pin IDC Flat Ribbon Cable4) One 60-pin IDC Flat Ribbon Cable5) Evaluation Kit Documentation (this manual)6) DS90C385A/DS90CF386 Datasheet7) LVDS Owner’s Manual (2nd Edition)FPD-Link Typical Application:DS90C385A DS90CF386FPD-Link ApplicationTypical FPD-Link Application (24-bit Color)The diagrams above illustrate the use of the Chipset (Tx/Rx) in a Host to LCD Panel Interface.Chipsets support up to 18-bit or 24-bit AM-TFT LCD Panels for any VGA (640X480), SVGA (800X600), XGA (1024X768), and Single/Dual Pixel SXGA (1280X1024) resolutions.Because of the non-periodic nature of STN-DD SHFCLK, the Chipset may not work with all D-STN panels. The PLL CLK input of the Transmitter requires a free running periodic SHFCLK. Most Graphics Controller can provide a separate pin with a free running clock. In this case the STN-DD SHFCLK can be sent as Data while the free running clock can be used as SHFCLK for the PLL ref CLK. For example, C&T's 65550's WEC (Pin 102) can be programmed to provide a free running clock using the BMP (Bios Modification Program). Please refer to STN Application using (AN-1056) for more information on STN support.Refer to the proper datasheet information on Chipsets (Tx/Rx) provided on each board for more detailed information.How to set up the Evaluation Kit:The PCB routing for the Tx input pins (TxIN) have been laid out to accept incoming data from a 60-pin IDC connector. The TxOUT/RxIN interface uses a 20-pin IDC connector through a IDC ribbon cable. Please follow these steps to set up the evaluation kit for bench testing and performance measurements:1) Connect one end of the 20-pin IDC cable to the transmitter board and the otherend to the receiver board. Longer lengths can be used.Note: Previous HSL Tx/Rx 8 Bit boards have different IDC pinouts and must be scrambled in the IDC cable in order to be compatible with this demo kit.2) Jumpers have been configured at the factory, they should not require anychanges for operation of the chipset. See text on Jumper settings for more details.3) From the Graphics card, connect a flat (ribbon) cable to the transmitter board andconnect the another flat cable from the receiver board to the panel (Note: Refer to AN-1127 for suggested mapping schemes). Note that pin 1 on the connector should be connected to pin 1 of the cable. A scramble cable may be required.4) Power for the Tx and Rx boards must be supplied externally through TP1 (Vcc).Grounds for both boards are connected through TP2 (GND) (see section below).Power Connection:The Transmitter and Receiver boards must be powered by supplying power externally through TP1 (Vcc) and TP2 (GND) on EACH board. The maximum voltage that should ever be applied to the FPD-Link Transmitter (385A) or Receiver (386) Vcc terminal is +4V MAXIMUM.FPD-Link Transmitter Board Description:J1 (60 position) accepts 28 bit LVTTL/LVCMOS data along with the clock.The FPD-Link Transmitter board is powered externally. For the transmitter to be operational, the Power Down pin must be set HIGH with a jumper. Rising or falling edge reference clock is selected by JP1 tied to Vcc (rising) or GND (falling).The 20-pin IDC connector (J2) provides the interface for LVDS signals for the Receiver board.Note: Previous HSL Tx/Rx 8 Bit boards have different IDC pinouts and must be scrambled in the IDC cable in order to be compatible with this demo kit.Vcc and Gnd MUST be applied externally here1 2 TXIN0 GNDTXIN1 GNDTXIN2 GNDTXIN3 GNDTXIN4 GNDTXIN5 GNDTXIN6 GNDTXIN7 GNDTXIN8 GNDTXIN9 GND TXIN10 GND TXIN11 GND TXIN12 GND TXIN13 GND TXIN14 GND TXIN15 GND TXIN16 GND TXIN17 GND TXIN18 GND TXIN19 GND TXIN20 GND TXIN21 GND TXIN22 GND TXIN23 GND TXIN24 GND TXIN25 GND TXIN26 GND TXIN27 GND TXCLKIN GND GND59 60J1/PDTxOUT LVDS signals 20-pin IDC connector60-pin IDC Connector R_FB 1 2 GND OUT0- OUT0+ GNDGNDOUT1- OUT1+ GNDGNDOUT2- OUT2+ GNDGNDCLK- CLK+ GNDGNDOUT3- OUT3+ GND19 20J2Note: Previous HSL Tx/Rx 8 Bit boards have different IDC pinouts and must be scrambled in the IDC cable in order to be compatible with this demo kit.Jumper Settings for the Tx BoardJumper Purpose SettingsR_FB R ising or F alling = FallingDataStrobe Vcc GND Vcc GND(JP1)Default setting is JP1 set LOW (to GND), falling edge strobe./PD P ower D own OFF (JP2) Vcc GND Vcc GND(ON: Tx is operational; OFF: Tx powers down) Default setting is JP2 set HIGH (to Vcc), operational mode.Tx LVDS Mapping by IDC ConnectorThe following two figures illustrate how the Tx inputs are mapped to the IDC connector (J1) (Note – labels are also printed on the demo boards). The 20-pin IDC (J2) connector pinout is also shown.60-pin IDC Connector(Transmitter Board)TXOUT3TXOUT2TXOUT1TXOUT0TxOUT LVDS signals 20-pin IDC connectorParallel LVTTL/LVCMOS Data Inputs Mapped to LVDS Outputs2Pin 12019GND OUT0- OUT0+ GND GND OUT1- OUT1+ GND GND OUT2- OUT2+ GND GND CLK- CLK+ GND GND OUT3- OUT3+GNDJ2Tx Board Options: 50 Ohm Termination for TxINOn the Tx demo board, the 29 inputs have an option for 50 Ohm terminations. There are 0402 pads for this purpose. One side is connected to the signal line and the other side is tied to ground. These pads are unpopulated from the factory but are provided if the user needs to install a 50 Ohm termination. R1 TO R28 are associated with the Tx data input lines. R29 is associated with CLKIN. Some test equipment may require a 50 Ohm load.Mapping of Transmitter Inputs for the Optional Termination Resistors is shown below:Tx Pin Names Tx PinNumberTerminationResistorTxIN0 51R1TxIN1 52 R2 TxIN2 54 R3 TxIN3 55 R4 TxIN4 56 R5 TxIN5 2 R6 TxIN6 3 R7 TxIN7 4 R8 TxIN8 6 R9 TxIN9 7 R10 TxIN10 8 R11 TxIN11 10 R12 TxIN12 11 R13 TxIN13 12 R14 TxIN14 14 R15 TxIN15 15 R16 TxIN16 16 R17 TxIN17 18 R18 TxIN18 19 R19 TxIN19 20 R20 TxIN20 22 R21 TxIN21 23 R22 TxIN22 24 R23 TxIN23 25 R24 TxIN24 27 R25 TxIN25 28 R26 TxIN26 30 R27 TxIN27 50 R28 TxCLKIN 31 R29BOM (Bill of Materials) Transmitter PCB:HSL Demo Board Schematic REV3HSL8TXR3 Revision: 3 FPD-LinkItem Qty Reference Part Pkg SizeC1 10 µF CASE D1 12 4C2,C6,C10,C14 0.1 µF 1206 (3216)C3,C7,C11,C15 22 µF 7343 (D)3 4C4,C8,C12 0.001 µF 0805 (2012)4 3C5,C9,C13 0.01 µF 0805 (2012)5 3spacing JP2,JP1 3_PIN_HEADER 0.1"6 2J1 IDC30X2 IDC607 1J2 IDC10X2 IDC208 1R1,R2,R3,R4,R5,R6,R7,R8,Optional 04029 29page)previous(SeeR9,R10,R11,R12,R13,R14,R15,R16,R17,R18,R19,R20,R21,R22,R23,R24,R25,R26,R27,R28,R29Ohm 040210 8 R30,R31,R32,R33,R34,R35,0R36,R3711 2 TP1,TP2 N/A TP_.2"X.2"TSSOP 12 1 U1 DS90C385AMTD 56-pinRx FPD-Link Receiver Board:J1 (60 position) provides access to the 28 bit LVTTL/LVCMOS and clock outputs. The FPD-Link Receiver board is powered from the pads show below. For the receiver to be operational, the Power Down pin must be set HIGH with the jumper. The 20-pin IDC connector (J2) provides the interface for LVDS signals for the Receiver board.Note: Previous HSL Tx/Rx 8 Bit boards have different IDC pinouts and must be scrambled in the IDC cable in order to be compatible with this demo kit.Vcc and Gnd MUST beapplied externally here RxIN LVDS signals20-pin IDC connector/PD 60 59RXOUT27 GNDRXOUT26 GNDRXOUT25 GNDRXOUT24 GNDRXOUT23 GNDRXOUT22 GNDRXOUT21 GNDRXOUT20 GNDRXOUT19 GNDRXOUT18 GNDRXOUT17 GNDRXOUT16 GNDRXOUT15 GNDRXOUT14 GNDRXOUT13 GNDRXOUT12 GNDRXOUT11 GNDRXOUT10 GNDRXOUT9 GNDRXOUT8 GNDRXOUT7 GNDRXOUT6 GNDRXOUT5 GNDRXOUT4 GNDRXOUT3 GNDRXOUT2 GNDRXOUT1 GNDRXOUT0 GND RXCLKOUT GNDGND GND 2 1J160-pin IDC Connector1 2IN0-IN0+ GNDGND IN1-IN1+ GNDGND IN2-IN2+ GNDGND CLK-CLK+ GNDGND IN3-IN3+ GND19 20J2Note: Previous HSL Tx/Rx 8 Bit boards have different IDC pinouts and must be scrambled in the IDC cable in order to be compatible with this demo kit.Selectable Jumper Settings for the Rx BoardJumper Purpose Settings/PD P ower D own = ON(JP1) Vcc GND Vcc GND(ON: Rx is operational; OFF: Rx powers down) Default setting is JP1 set HIGH (to Vcc), operational mode.LVDS Mapping by IDC ConnectorThe following two figures illustrate how the Rx outputs are mapped to the IDCconnector (J1) (Note – labels are also printed on the demo boards). The 20-pin IDC connector (J2) pinout is also shown.RXIN3 RXIN2 RXIN1 RXIN0RXCLKIN60-pin IDC ConnectorRxIN LVDS signals 20-pin IDC connector(Receiver Board)LVDS Data Inputs Mapped to LVTTL/LVCMOS Outputs2Pin 12019GND IN0- IN0+ GND GND IN1- IN1+ GND GND IN2- IN2+ GND GND CLK- CLK+ GND GND IN3- IN3+GNDJ2Rx Optional: Series Termination for RxOutOn the Rx demo board, there are 29 outputs that have an 0402 pad in series (which are shorted out). These pads are unpopulated from the factory but are provided if the user needs to install a 450 Ohm series resistors. This is required if directly connecting to 50 Ohm inputs on a scope. To use this option the user must cut the signal line between the pads before installing the 450 Ohm series resistors. R1 to R28 are associated with the DATA output lines. R29 is associated with CLKOUT. The total load presented to the receiver output is 500 Ohms (450 + 50). The waveform on the scope is 1/10 of the signal due to the resulting voltage divider (50 / (450 + 50)).Optional Series Termination Resistor mapping is shown below:Rx Pin Names Rx PinNumber Series TerminationResistorRxOUT0 27 R28 RxOUT1 29 R27 RxOUT2 30 R26 RxOUT3 32 R25 RxOUT4 33 R24 RxOUT5 34 R23 RxOUT6 35 R22 RxOUT7 37 R21 RxOUT8 38 R20 RxOUT9 39 R19 RxOUT10 41 R18 RxOUT11 42 R17 RxOUT12 43 R16 RxOUT13 45 R15 RxOUT14 46 R14 RxOUT15 47 R13 RxOUT16 49 R12 RxOUT17 50 R11 RxOUT18 51 R10 RxOUT19 53 R9 RxOUT20 54 R8 RxOUT21 55 R7 RxOUT22 1 R6 RxOUT23 2 R5 RxOUT24 3 R4 RxOUT25 5 R3 RxOUT26 6 R2 RxOUT27 7 R1 RxCLKOUT 26 R29BOM (Bill of Materials) Receiver PCB:HSL Demo Board Schematic REV3HSL8RXR3 Revision: 3 FPD-LinkItem Qty Reference Part Pkg SizeC1 10 µF CASE D1 12 4C2,C6,C10,C14 0.1 µF 1206 (3216)C3,C7,C11,C15 22 µF 7343 (D)3 4C4,C8,C12 0.001 µF 0805 (2012)4 3C5,C9,C13 0.01 µF 0805 (2012)5 3spacing6 1JP1 3_PIN_HEADER 0.1"J1 IDC30X2 IDC607 1J2 IDC10X2 IDC208 1R1,R2,R3,R4,R5,R6,R7,R8,Optional 04029 29page)previous(SeeR9,R10,R11,R12,R13,R14,R15,R16,R17,R18,R19,R20,R21,R22,R23,R24,R25,R26,R27,R28,R29Ohm 040210 6 R35,R36,R37,R38,R39,R400Ohm 040211 5 R30,R31,R32,R33,R34 10012 2 TP1,TP2 N/A TP_.2"X.2"TSSOP 13 1 U1 DS90CF386MTD 56-pinTypical Connection / Test EquipmentThe following is a list of typical test equipment that may be used to generate signals for the TX inputs:1) Graphics card or GUI controller with digital RGB (LVTTL) output.2) TEK HFS9009 - This pattern generator along with 9DG2 Cards may be used togenerate input signals and also the clock signal.3) TEK DG2020 - This generator may also be used to generate data and clocksignals.4) TEK MB100 BERT - This bit error rate tester may be used for both signal sourceand receiver.5) Any other signal / pattern generator that generates the correct input levels asspecified in the datasheet.The following is a list of typically test equipment that may be used to monitor the output signals from the RX:1) LCD Display Panel which supports digital RGB (LVTTL) inputs.2) TEK MB100 BERT - Receiver.3) Any SCOPE with 50 Ohm inputs or high impedance probes.LVDS signals may be easily measured with high impedance / high bandwidth differential probes such as the TEK P6247 or P6248 differential probes.The picture below shows a typical test set up using a Graphics Card and LCD Panel.GraphicsCardAGP/PCI/ISA BusTypical FPD-Link Setup / PC Panel ApplicationThe picture below shows a typical test set up using a generator and scope.Typical Connection / Test Equipment SetupTypical WaveshapesLVDSThe plot above shows both the LVDS Data channel with PRBS data and also the LVDS Clock over laid. Note that the clock pattern is 4 bit times HIGH and 3 bit times LOW. The differential signal should be typically +/-300mV. These waveforms were acquired using the TEK P6248 Probes. Clock rate is 85MHz.RxOUTThe plot above shows both the recovered PRBS data and also the regenerated Clock overlaid. Note that the clock transitions slightly before the data transition and strobes the data on the falling edge of the clock. The data and clock signals are low drive 3V CMOS outputs. The plot above is at 85MHz.TroubleshootingIf the demo boards are not performing properly, use the following as a guide forquick solutions to potential problems.QUICK CHECKS:1. Check that Power and Ground are connected to both Tx AND Rx boards.2. Check the supply voltage (typical3.3V) and also current draw with both Tx andRx boards (should be about 200mA with clock and one data bit at 66MHz).3. Verify input clock and input data signals meet requirements (VIL, VIH, tset,thold), Also verify that data is strobed on the selected rising/falling (R_FB pin)edge of the clock.4. Check that the Jumpers are set correctly.5. Check that the cable is properly connected.TROUBLESHOOTING CHARTProblem… Solution…There is only the output clock.There is no output data.Make sure the data is applied to the correct input pin.Make sure data is valid at the input.No output data and clock. Make sure Power is on. Input data and clock areactive and connected correctly.Make sure that the cable is secured to both demoboards.Power, ground, input data and input clock are connected correctly, but no outputs. Check the Power Down pins of both boards and make sure that the devices are enabled (/PD=Vcc) for operation.The devices are pulling more than 1A of current. Check for shorts in the cables connecting the TX and RX boards.After powering up the demo boards, the power supply reads less than 3V when it is set to 3.3V. Use a larger power supply that will provide enough current for the demo boards, a 500mA power supply is recommended.Additional InformationFor more information on FPD-Link Transmitters/Receivers, refer to the National’s LVDS website at:/appinfo/fpdApplication Notes•AN-1032 An Introduction to FPD-Link•AN-1056 STN Application using FPD-Link•AN-1059 High Speed Transmission with LVDS Devices• AN-1084 Parallel Application of Link Chips•AN-1085 FPD-Link PCB and Interconnect Design-In Guidelines•AN-1127 LVDS Display Interface (LDI) TFT Data Mapping for Interoperability with FPD-Link•AN-1163 TFT Data Mapping for Dual Pixel LDI Application - Alternate A - Color MapAppendixTx PCB SchematicTransmitter Board: HSL Demo Board Schematic Document Number: HSL8TXR3Rev: 3.0Rx PCB SchematicReceiver Board: HSL Demo Board Schematic Document Number: HSL8RXR3Rev: 3.0IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAudio /audio Automotive and Transportation /automotiveAmplifiers Communications and Telecom /communicationsData Converters Computers and Peripherals /computersDLP®Products Consumer Electronics /consumer-appsDSP Energy and Lighting /energyClocks and Timers /clocks Industrial /industrialInterface Medical /medicalLogic Security /securityPower Mgmt Space,Avionics and Defense /space-avionics-defense Microcontrollers Video and Imaging /videoRFID OMAP Mobile Processors /omapWireless Connectivity /wirelessconnectivityTI E2E Community Home Page Mailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2012,Texas Instruments Incorporated。

ESMARC工控主板如何连接显示屏

当使用ESMARC主板RGB显示接口连接LVDS显示屏时,需要专用芯片将RGB数字信号转化为LVDS差分信号,同时必须根据LVDS显示屏使用的数据映射关系,正确的设计转换电路。

TI的DS90C385A是常用的24-bit RGB转LVDS接口芯片,其数字输入端可直接与ESMARC RGB接口相连。

DS90C385A支持最高87.5MHz的数据时钟,即最大可支持1280×800 @50Hz左右的显示分辨率。

DS90C385A的数字输入与LVDS输出对应关系如下图所示(详细说明请参考DS90C385A数据手册):图1 DS90C385A的数字输入与LVDS输出对应关系下图是利用DS90C385A实现JEIDA标准的RGB转LVDS转接电路:图2 并行RGB转LVDS(JEIDA标准)下图是利用DS90C385A实现SPWG标准的RGB转LVDS转接电:图3 并行RGB转LVDS(SPWG标准)ESM928x系列连接LVDS显示屏,需要根据显示屏的LVDS-RGB数据映射关系选择对应的转换电路。

ESM335x-LVDS的显示接口就是使用的图2所示的转换电路,采用JEIDA标准,如果用户的LCD 为SPWG格式,就需要选择ESM335x RGB显示接口,然后在应用底板上参考图3的设计将RGB转为LVDS信号。

ESM680x系列主板的LVDS显示接口可支持JEIDA/SPWG软件切换,方便与LVDS显示屏的直接连接。

3、HDMI显示HDMI是标准的显示接口,用户可直接参考ESMARC评估底上的相关电路。

4、LVDS + HDMI双屏显示ESM680x系列(Linux)工控主板可支持LVDS和HDMI同时显示,相关说明请参考:《ESM6802双屏显示(LVDS+HDMI)设置》。

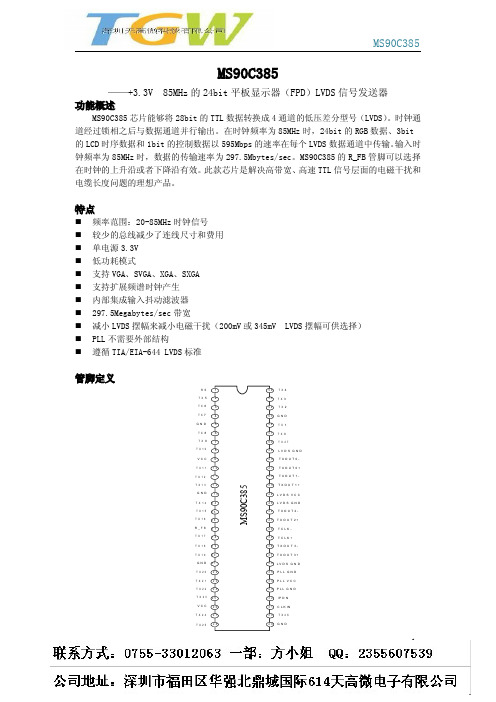

DS90C385

Block Diagram

DS90C385A

Order Number DS90C385AMT See NS Package Number MTD56

20070201

© 2006 National Semiconductor Corporation DS200702

DS90C385A

n Narrow bus reduces cable size and cost n Up to 2.45 Gbps throughput n Up to 306.25Megabytes/sec bandwidth n 345 mV (typ) swing LVDS devices for low EMI n PLL requires no external components n Compliant to TIA/EIA-644 LVDS standard n Low profile 56-lead TSSOP package

f = 25 MHz f = 40 MHz f = 65 MHz f = 87.5 MHz

Min Typ Max Units

2.0

VCC

V

0

0.8

V

−0.79 −1.5

V

+1.8 +10

µA

−10

0

µA

250 345 450

mV

35

mV

1.13 1.25 1.38

V

35

mV

−3.5 −5

mA

±1 ±10

This chipset is an ideal means to solve EMI and cable size problems associated with wide, high-speed TTL interfaces with added Spread Spectrum Clocking support.

天高微 MS90C385 LVDS接收发送芯片

图 8.上升、下降时间与高电平、低电平保持时间

图 9.输入时钟与输出时钟间延迟

- 6 -

MS90C385

封装图

- 7 -

结构框图

M S 9 0 C3 8 5

C M O S /T T L IN PU TS R ED

GRN

8

TTL PARALLEL -TO- LVDS

8

L VDS DAT A (140 T O 5 9 5 M bit /s On Each LVDS Channel )

BLU H SYN C VSYN C DE CNTL

直流特性

符号 VOD △VOD VOC △VOC IOZ /PDN=0V 共模电压(RS=VCC) 共模电压(RS=GND) 参数 差分输出电压(RS=VCC) 差分输出电压(RS=GND) RL=100Ω 条件 Min 250 100 1.125 Typ 345 200 1.25 1.20 35 ±10 mV uA Max 450 300 35 1.375 mV V Units mV

图 3.TTL 输入

图 4.LVDS 输出 Vdiff=(TXOUT+)-(TXOUT-)

图 5.锁相环设置时间

图 6.发送器状态

- 5 -

MS90C385

Vdiff=(TXOUT+)-(TXOUT-) , ……(TCLK+)-(TCLK-) 图 7.并行 TTL 输入数据与 LVDS 输出数据匹配关系

电学特性

符号 VIH VIL IIN IPD

开关特性

符号 TTCIT TTCP TTCH TTCL TTS TTH TLVT TTCD TTDP1 TTDP0 TTDP6 TTDP5 TTDP4 TTDP3 TTDP2 TTDP1 TTDP0 TTDP6 TTDP5 TTDP4 TTDP3 TTDP2 TTDP1 TTDP0 TTDP6 TTDP5 TTDP4 TTDP3 TTDP2 TTDP1 参数 时钟信号过渡时间 时钟周期 时钟高电平持续时间 时钟低电平持续时间 TTL 数据建立时间 TTL 数据保持时间 LVDS 信号转换时间 时钟输入与差分时钟信号延迟 输出数据位 0 输出数据位 1 输出数据位 2 输出数据位 3 输出数据位 4 输出数据位 5 输出数据位 6 输出数据位 0 输出数据位 1 输出数据位 2 输出数据位 3 输出数据位 4 输出数据位 5 输出数据位 6 输出数据位 0 输出数据位 1 输出数据位 2 输出数据位 3 输出数据位 4 输出数据位 5 输出数据位 6 输出数据位 0 20MHz -0.2 35MHz -0.2 50MHz -0.2 85MHz -0.2 11.76 0.35T 0.35T 2.5 0 0.6 2T/7+2. 3 0 1.68 3.36 5.04 6.72 8.40 10.08 0 2.86 5.71 8.57 11.42 14.28 17.14 0 4.08 8.16 12.24 16.33 20.41 24.49 0 +0.2 +0.2 +0.2 +0.2 T 0.5T 0.5T Min Typ Max 5.0 50 0.65T 0.65T Units ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns ns

lvds液晶屏幕接口详解完整版

l v d s液晶屏幕接口详解标准化管理处编码[BBX968T-XBB8968-NNJ668-MM9N]1.LVDS输出接口概述液晶显示器驱动板输出的数字信号中,除了包括RGB数据信号外,还包括行同步、场同步、像素时钟等信号,其中像素时钟信号的最高频率可超过28MHz。

采用TTL接口,数据传输速率不高,传输距离较短,且抗电磁干扰(EMI)能力也比较差,会对RGB 数据造成一定的影响;另外,TTL多路数据信号采用排线的方式来传送,整个排线数量达几十路,不但连接不便,而且不适合超薄化的趋势。

采用LVDS输出接口传输数据,可以使这些问题迎刃而解,实现数据的高速率、低噪声、远距离、高准确度的传输。

那么,什么是LVDS输出接口呢LVDS,即Low Voltage Differential Signaling,是一种低压差分信号技术接口。

它是美国NS公司(美国国家半导体公司)为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研制的一种数字视频信号传输方式。

LVDS输出接口利用非常低的电压摆幅(约350mV)在两条PCB走线或一对平衡电缆上通过差分进行数据的传输,即低压差分信号传输。

采用LVDS输出接口,可以使得信号在差分PCB线或平衡电缆上以几百Mbit/s的速率传输,由于采用低压和低电流驱动方式,因此,实现了低噪声和低功耗。

目前,LVDS输出接口在17in及以上液晶显示器中得到了广泛的应用。

2.LVDS接口电路的组成在液晶显示器中,LVDS接口电路包括两部分,即驱动板侧的LVDS输出接口电路(LVDS发送器)和液晶面板侧的LVDS输入接口电路(LVDS接收器)。

LVDS发送器将驱动板主控芯片输出的17L电平并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过驱动板与液晶面板之间的柔性电缆(排线)将信号传送到液晶面板侧的LVDS接收器,LVDS接收器再将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。

什么是等离子电视

什么是等离子电视————————————————————————————————作者:————————————————————————————————日期:什么是等离子电视,工作原理是什么?等离子(简称PDP全称是Plasma Display Panel)是一种继承了CRT电视发光优势的平板显示技术。

它是在两张超薄的玻璃板之间注入混合气体,并施加电压利用荧光粉发光成像的设备。

与CRT显像管显示器相比,具有分辨率高,屏幕大,超薄的特点,有同时继承了CRT色彩丰富、鲜艳。

对比度强烈、显影速度迅速的特点。

等离子电视工作原理:等离子电视的工作原理是一种利用气体放电的显示技术,其工作原理与日光灯很相似。

它采用了等离子管作为发光元件,屏幕上每一个等离子管对应一个像素,屏幕以玻璃作为基板,基板间隔一定距离,四周经气密性封接形成一个个放电空间。

放电空间内充入氖、氙等混合惰性气体作为工作媒质。

在两块玻璃基板的内侧面上涂有金属氧化物导电薄膜作激励电极。

当向电极上加入电压,放电空间内的混合气体便发生等离子体放电现象。

气体等离子体放电产生紫外线,紫外线激发荧光屏,荧光屏发射出可见光,显现出图像。

等离子是一种自发光显示技术,不需要背景光源,因此没有LCD显示器的视角和亮度均匀性问题,而且实现了较高的色彩显示能力和对比度,同时,等离子技术也避免了LCD技术中的响应时间问题。

因此从目前的技术水平看,等离子显示技术在动态视频显示领域的优势更加明显,更加适合作为家庭影院和大屏幕显示终端使用。

真正的了解什么等离子电视机,那就不能不提等离子电视机的缺点。

等离子电视机和液晶电视机比较,其主要缺点包括能源利用效率低,间接导致能耗大、发热大和亮度低;分辨率提高困难、重量较重和尺寸线较短。

这些方面的劣势成为阻碍等离子电视产品普及的主要原因。

等离子电视还有另一问题,那就是烧屏,又称残影、残像。

什么是“烧屏”:等离子显示原理决定如果屏幕上长时间保持一幅静止图像,则屏幕上会留下该图像的“鬼影”。

数字电视接收机总体框

5.2 A/D变换电路

• SDA:串行数据I/O。 • SCL:串行时钟。 • A0:串行地址输入1。 • RED:红通道数据输出。 • GREEN:绿通道数据输出。 • BLUE :蓝通道数据输出。 • 数据输出时钟(DATACK):此引脚通常为输出数据和HSOUT的外部

逻辑提供主时钟输出信号,它由内部时钟产生,并于内部取样时钟 同步。当采样时间随PHASE调整器改变时,输出时序也切换, DATACK和HSOUT输出也改变。所以时序关系着信号的稳定。

• 3)分量输入端口 • 分量(Component)接口如图5-4所示,它的标记为Y/Pb/Pr,用红、

绿、蓝三种颜色来标注每条线缆和接口。绿色线缆(Y),传输亮度 信号。蓝色和红色线缆(Pb和Pr)传输的是色差信号。分量端口的 效果要好于S端子,

上一页 下一页 返回

5.1数字电视接收机总体框图

因此很多高清播放设备上都采用该接口。如果使用优质的线材和接 口,即使采用10米长的线缆,也能传输优质的画面。 • 4)VGA接口 • VGA又称D-Sub接口,如图5-5所示。VGA接口共有15针,分成3排, 每排5个孔,是显卡上应用最为广泛的接口类型,绝大多数显卡都带 有此种接口。它传输红、绿、蓝模拟信号以及同步信号(行和场信 号)。使用VGA连接设备,线缆长度最好不要超过10米,而且要注 意接头是否安装牢固,否则可能引起图像中出现虚影。 • 5)DVI接口(数字视觉接口)

上一页 下一页 返回

5.2 A/D变换电路

• 5.2.3 引脚功能

• AD9883共有80个引脚,其主要引脚的功能如下: • 行同步输出(HSOUT):HSYNC的经过相位调整的副本。其极性和

幅度可通过串行总线寄存器控制。行同步取决于串行数据的不断调 整。 • 场同步输出(VSOUT):视频VSYNC的经过相位调整的副本。其输 出极性由串行总线寄存器位控制。它在所有模式图像传输的过程中 有效。 • 绿同步限制输出(SOGOUT):由绿通道提取复合同步信号,从限 制比较器输出,或输出未处理的行同步信号HSYNC。

液晶显示器的显示原理及亮度概念

液晶显示器的显示原理及亮度概念LCD显示器在近年逐渐加快了替代CRT显示器的步伐,你打算购买一台LCD吗?你了解LCD吗?液晶显示器和传统的CRT显示器,在其发光的技术原理上有什么不同?传统的CRT显示器主要是依*显象管内的电子枪发射的电子束射击显示屏内侧的荧光粉来发光,在显示器内部人造磁场的有意干扰下,电子束会发生一定角度的偏转,扫描目标单元格的荧光粉而显示不同的色彩。

而TFT-LCD却是采用背光(backlight)原理,使用灯管作为背光光源,通过辅助光学模组和液晶层对光线的控制莉来达到较为理想的显示效果。

液晶是一种规则性排列的有机化合物,它是一种介于固体和液体之间的物质,目前一般采用的是分子排列最适合用于制造液晶显示器的nematic细柱型液晶。

液晶本身并不能构发光,它主要是通过因为电压的更改产生电场而使液晶分子排列产生变化来显示图像。

液晶面板主要是由两块无钠玻璃夹着一个由偏光板、液晶层和彩色虑光片构成的夹层所组成。

偏光板、彩色滤光片决定了有多少光可以通过以及生成何种颜色的光线。

液晶被灌在两个制作精良的平面之间构成液晶层,这两个平面上列有许多沟槽,单独平面上的沟槽都是平行的,但是这两个平行的平面上的沟槽却是互相垂直的。

简单的说就是后面的平面上的沟槽是纵向排列的话,那么前面的平面就是横向排列的。

位于两个平面间液晶分子的排列会形成一个Z轴向90度的逐渐扭曲状态。

背光光源即灯管发出的光线通过液晶显示屏背面的背光板和反光膜,产生均匀的背光光线,这些光线通过后层会被液晶进行Z轴向的扭曲,从而能够通过前层平面。

如果给液晶层加电压将会产生一个电场,液晶分子就会重新排列,光线无法扭转从而不能通过前层平面,以此来阻断光线。

液晶显示器的缺点在于亮度、画面均匀度、可视角度和反应时间上与CRT显示器有比较明显的差距。

其中反应时间和可视角度均取决于液晶面板的质量,画面均匀度和辅助光学模块有很大关系。

而液晶显示器的亮度主要取决于背光光源。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DS90C385A+3.3V Programmable LVDS Transmitter 24-Bit Flat Panel Display Link-87.5MHzGeneral DescriptionThe DS90C385A is a pin to pin compatible replacement for DS90C383,DS90C383A and DS90C385.The DS90C385A has additional features and improvements making it an ideal replacement for DS90C383,DS90C383A and DS90C385.family of LVDS Transmitters.The DS90C385A transmitter converts 28bits of LVCMOS/LVTTL data into four LVDS (Low Voltage Differential Signal-ing)data streams.A phase-locked transmit clock is transmit-ted in parallel with the data streams over the fifth LVDS link.Every cycle of the transmit clock 28bits of input data are sampled and transmitted.At a transmit clock frequency of 87.5MHz,24bits of RGB data and 3bits of LCD timing and control data (FPLINE,FPFRAME,DRDY)are transmitted at a rate of 612.5Mbps per LVDS data ing a 87.5MHz clock,the data throughput is 306.25Mbytes/sec.This transmitter can be programmed for Rising edge strobe or Falling edge strobe through a dedicated pin.A Rising edge or Falling edge strobe transmitter will interoperate with a Falling edge strobe FPDLink Receiver without any transla-tion logic.This chipset is an ideal means to solve EMI and cable size problems associated with wide,high-speed TTL interfaces with added Spread Spectrum Clocking support.Featuresn Pin-to-pin compatible to DS90C383,DS90C383A and DS90C385.n No special start-up sequence required betweenclock/data and /PD pins.Input signals (clock and data)can be applied either before or after the device is powered.n Support Spread Spectrum Clocking up to 100kHz frequency modulation &deviations of ±2.5%center spread or -5%down spread.n “Input Clock Detection”feature will pull all LVDS pairs to logic low when input clock is missing and when /PD pin is logic high.n 18to 87.5MHz shift clock supportn Tx power consumption <147mW (typ)@87.5MHz Grayscalen Tx Power-down mode <60µW (typ)n Supports VGA,SVGA,XGA,SXGA(dual pixel),SXGA+(dual pixel),UXGA(dual pixel).n Narrow bus reduces cable size and cost n Up to 2.45Gbps throughputn Up to 306.25Megabytes/sec bandwidthn 345mV (typ)swing LVDS devices for low EMI n PLL requires no external components n Compliant to TIA/EIA-644LVDS standard n Low profile 56-lead TSSOP packageBlock DiagramDS90C385A20070201Order Number DS90C385AMT See NS Package Number MTD56PRELIMINARYOctober 2005DS90C385A +3.3V Programmable LVDS Transmitter 24-bit Flat Panel Display (FPD)Link-87.5MHz©2005National Semiconductor Corporation Absolute Maximum Ratings (Note 1)If Military/Aerospace specified devices are required,please contact the National Semiconductor Sales Office/Distributors for availability and specifications.Supply Voltage (V CC )−0.3V to +4VCMOS/TTL Input Voltage −0.5V to (V CC +0.3V)LVDS Driver Output Voltage −0.3V to (V CC +0.3V)LVDS Output Short Circuit DurationContinuousJunction Temperature +150˚CStorage Temperature −65˚C to +150˚CLead Temperature (Soldering,4sec)+260˚CMaximum Package Power Dissipation Capacity @25˚CMTD56(TSSOP)Package:DS90C385AMT1.63W Package Derating:DS90C385AMT 12.5mW/˚C above +25˚CESD Rating(HBM,1.5k Ω,100pF)7kV (EIAJ,0Ω,200pF)500VLatch Up Tolerance @25˚C±100mARecommended Operating ConditionsMinNom Max Units Supply Voltage (V CC )3.0 3.33.6VOperating Free Air Temperature (T A )−10+25+70˚CSupply Noise Voltage (V CC )200mV PPTxCLKIN frequency1887.5MHzElectrical CharacteristicsOver recommended operating supply and temperature ranges unless otherwise specified.Symbol ParameterConditionsMin TypMax Units LVCMOS/LVTTL DC SPECIFICATIONSV IH High Level Input Voltage 2.0V CC V V IL Low Level Input Voltage 00.8V V CL Input Clamp Voltage I CL =−18mA−0.79−1.5V I INInput CurrentV IN =0.4V,2.5V or V CC +1.8+10µA V IN =GND−100µALVDS DC SPECIFICATIONS V OD Differential Output Voltage R L =100Ω250345450mV ∆V OD Change in V OD between complimentary output states 35mV V OS Offset Voltage (Note 4) 1.131.251.38V ∆V OS Change in V OS between complimentary output states 35mV I OS Output Short Circuit Current V OUT =0V,R L =100Ω−3.5−5mA I OZOutput TRI-STATE ®CurrentPower Down =0V,V OUT =0V or V CC ±1±10µATRANSMITTER SUPPLY CURRENT ICCTWTransmitter Supply Current Worst CaseR L =100Ω,C L =5pF,Worst Case Pattern (Figures 1,3)”Typ ”values are given for V CC =3.6V and T A =+25˚C,”Max ”values are given for V CC =3.6V and T A =−10˚Cf =25MHz 3145mA f =40MHz 3750mA f =65MHz 4860mA f =87.5MHz5565mAD S 90C 385A 2Electrical Characteristics(Continued)Over recommended operating supply and temperature ranges unless otherwise specified.Symbol Parameter Conditions Min Typ Max Units TRANSMITTER SUPPLY CURRENTICCTG Transmitter Supply Current16Grayscale R L=100Ω,C L=5pF,16Grayscale Pattern(Figures2,3)”Typ”values are given forV CC=3.6V and T A=+25˚C,”Max”valuesare given for V CC=3.6V and T A=−10˚Cf=25MHz2940mAf=40MHz3345mAf=65MHz3950mAf=87.5MHz4455mAICCTZ Transmitter Supply CurrentPower Down Power Down=LowDriver Outputs in TRI-STATE underPower Down Mode17150µANote1:“Absolute Maximum Ratings”are those values beyond which the safety of the device cannot be guaranteed.They are not meant to imply that the device should be operated at these limits.The tables of“Electrical Characteristics”specify conditions for device operation.Note2:Typical values are given for V CC=3.3V and T A=+25C unless specified otherwise.Note3:Current into device pins is defined as positive.Current out of device pins is defined as negative.Voltages are referenced to ground unless otherwise specified(except V OD and∆V OD).Note4:V OS previously referred as V CM.Recommended Transmitter Input CharacteristicsOver recommended operating supply and temperature ranges unless otherwise specifiedSymbol Parameter Min Typ Max UnitsTCIT TxCLK IN Transition Time(Figure5) 1.0 6.0nsTCIP TxCLK IN Period(Figure6)11.42T55.55nsTCIH TxCLK IN High Time(Figure6)0.35T0.5T0.65T nsTCIL TxCLK IN Low Time(Figure6)0.35T0.5T0.65T nsTXIT TxIN,and PWR DOWN pin Transition Time 1.5 6.0nsTXPD Minimum pulse width for PWR DOWN pin signal.1us Transmitter Switching CharacteristicsOver recommended operating supply and temperature ranges unless otherwise specifiedSymbol Parameter Min Typ Max UnitsLLHT LVDS Low-to-High Transition Time(Figure4)0.75 1.4nsLHLT LVDS High-to-Low Transition Time(Figure4)0.75 1.4nsTPPos0Transmitter Output Pulse Position(Figure12)(Note5)f=25MHz−0.450+0.45nsTPPos1Transmitter Output Pulse Position 5.26 5.71 6.16nsTPPos2Transmitter Output Pulse Position10.9811.4311.88nsTPPos3Transmitter Output Pulse Position16.6917.1417.59nsTPPos4Transmitter Output Pulse Position22.4122.8623.31nsTPPos5Transmitter Output Pulse Position28.1228.5729.02nsTPPos6Transmitter Output Pulse Position33.8434.2934.74nsDS90C385A3Transmitter Switching Characteristics(Continued)Over recommended operating supply and temperature ranges unless otherwise specifiedSymbol ParameterMinTyp Max Units TPPos0Transmitter Output Pulse Position (Figure 12)(Note 5)f =40MHz−0.250+0.25ns TPPos1Transmitter Output Pulse Position 3.32 3.57 3.82ns TPPos2Transmitter Output Pulse Position 6.897.147.39ns TPPos3Transmitter Output Pulse Position 10.4610.7110.96ns TPPos4Transmitter Output Pulse Position 14.0414.2914.54ns TPPos5Transmitter Output Pulse Position 17.6117.8618.11ns TPPos6Transmitter Output Pulse Position21.1821.4321.68ns TPPos0Transmitter Output Pulse Position (Figure 12)(Note 5)f =65MHz−0.200+0.20ns TPPos1Transmitter Output Pulse Position 2.00 2.20 2.40ns TPPos2Transmitter Output Pulse Position for Bit 2 4.20 4.40 4.60ns TPPos3Transmitter Output Pulse Position for Bit 3 6.39 6.59 6.79ns TPPos4Transmitter Output Pulse Position 8.598.798.99ns TPPos5Transmitter Output Pulse Position 10.7910.9911.19ns TPPos6Transmitter Output Pulse Position12.9913.1913.39ns TPPos0Transmitter Output Pulse Position (Figure 12)(Note 5)f =87.5MHz−0.200+0.20ns TPPos1Transmitter Output Pulse Position 1.48 1.68 1.88ns TPPos2Transmitter Output Pulse Position 3.16 3.36 3.56ns TPPos3Transmitter Output Pulse Position 4.84 5.04 5.24ns TPPos4Transmitter Output Pulse Position 6.52 6.72 6.92ns TPPos5Transmitter Output Pulse Position 8.208.408.60ns TPPos6Transmitter Output Pulse Position 9.8810.0810.28ns TSTC Required TxIN Setup to TxCLK IN (Figure 6)at 85MHz2.5ns THTC Required TxIN Hold to TxCLK IN (Figure 6)at 87.5MHz0.5ns TCCDTxCLK IN to TxCLK OUT Delay.Measure from TxCLK IN edge to immediately crossing point of differential TxCLK OUT by following the positive TxCLK OUT.50%duty cycle input clock is assumed.(Figure 7)T A =−10˚,and 87.5MHz for "Min ",T A =70˚,and 25MHz for "Max ",V CC =3.6V,R_FB pin =VCC 3.0867.211nsMeasure from TxCLK IN edge to immediately crossing point of differential TxCLK OUT by following the positive TxCLK OUT.50%duty cycle input clock is assumed.(Figure 8)T A =−10˚,and 87.5MHz for "Min ",T A =70˚,and 25MHz for "Max ",V CC =3.6V,R_FB pin =GND2.868 6.062nsD S 90C 385A 4Transmitter Switching Characteristics(Continued)Over recommended operating supply and temperature ranges unless otherwise specifiedSymbol Parameter Min Typ Max UnitsSSCG Spread Spectrum Clock support;Modulation frequency with a linear profile.(Note6)f=25MHz100kHz±2.5%/−5% f=40MHz100kHz±2.5%/−5% f=65MHz100kHz±2.5%/−5% f=87.5MHz100kHz±2.5%/−5%TPLLS Transmitter Phase Lock Loop Set(Figure9)10msTPDD Transmitter Power Down Delay(Figure11)100ns Note5:The Minimum and Maximum Limits are based on statistical analysis of the device performance over process,voltage,and temperature ranges.This parameter is functionality tested only on Automatic Test Equipment(ATE).Note6:Care must be taken to ensure TSTC and THTC are met so input data are sampling correctly.This SSCG parameter only shows the performance of tracking Spread Spectrum Clock applied to TxCLK IN pin,and reflects the result on TxCLKOUT+and TxCLKOUT−pins.DS90C385A5AC Timing DiagramsNote 7:The worst case test pattern produces a maximum toggling of digital circuits,LVDS I/O and LVCMOS/LVTTL I/O.Note 8:The 16grayscale test pattern tests device power consumption for a “typical”LCD display pattern.The test pattern approximates signal switching needed to produce groups of 16vertical stripes across the display.Note 9:Figures 1,2show a falling edge data strobe (TxCLK IN/RxCLK OUT).Note 10:Recommended pin to signal mapping.Customer may choose to define differently.20070204FIGURE 1.“Worst Case”Test Pattern (Note 7)20070205FIGURE 2.“16Grayscale”Test Pattern -DS90C385A (Notes 8,9,10)D S 90C 385A 6AC Timing Diagrams(Continued)20070230FIGURE 3.DS90C385A (Transmitter)LVDS Output Load.5pF is showed as board loading20070206FIGURE 4.DS90C385A (Transmitter)LVDS Transition Times20070208FIGURE 5.DS90C385A (Transmitter)Input Clock Transition Time20070210FIGURE 6.DS90C385A (Transmitter)Setup/Hold and High/Low Times with R_FB pin =GND (Falling Edge Strobe)20070212FIGURE 7.DS90C385A (Transmitter)Clock In to Clock Out Delay with R_FB pin =VCCDS90C385A7AC Timing Diagrams(Continued)20070235FIGURE 8.DS90C385A (Transmitter)Clock In to Clock Out Delay with R_FB pin =GND20070214FIGURE 9.DS90C385A (Transmitter)Phase Lock Loop Set Time20070217FIGURE 10.28Parallel TTL Data Inputs Mapped to LVDS Outputs -DS90C385AD S 90C 385A 8AC Timing Diagrams(Continued)20070218FIGURE 11.Transmitter Power Down Delay20070226FIGURE 12.Transmitter LVDS Output Pulse Position Measurement -DS90C385ADS90C385A9DS90C385A MTD56(TSSOP)Package Pin Descriptions —FPD Link TransmitterPin Name I/O No.DescriptionTxIN I 28LVTTL level input.This includes:8Red,8Green,8Blue,and 4control lines —FPLINE,FPFRAME and DRDY (also referred to as HSYNC,VSYNC,Data Enable).TxOUT+O 4Positive LVDS differentiaI data output.TxOUT−O 4Negative LVDS differential data output.TxCLKIN I 1LVTTL Ievel clock input.Pin name TxCLK IN.R_FB I 1LVTTL Ievel programmable strobe select (See Table 1).TxCLK OUT+O 1Positive LVDS differential clock output.TxCLK OUT−O 1Negative LVDS differential clock output.PWR DOWN I 1LVTTL level input.When asserted (low input)TRI-STATE the outputs,ensuring low current at power down.V CC I 3Power supply pins for LVTTL inputs.GND I 5Ground pins for LVTTL inputs.PLL V CC I 1Power supply pin for PLL.PLL GND I 2Ground pins for PLL.LVDS V CC I 1Power supply pin for LVDS outputs.LVDS GNDI3Ground pins for LVDS outputs.D S 90C 385A 10Applications InformationThe DS90C385A is backward compatible with the DS90C385,DS90C383A,DS90C383in TSSOP56-lead package,and it is a pin-for-pin replacements.This device DS90C385A also features reduced variation of the TCCD parameter which is important for dual pixel appli-cations.(See AN-1084)This device may also be used as a replacement for the DS90CF583(5V,65MHz)and DS90CF581(5V,40MHz) FPD-Link Transmitters with certain considerations/ modifications:1.Change5V power supply to 3.3V.Provide this 3.3Vsupply to the V CC,LVDS V CC and PLL V CC of the transmitter.2.The DS90C385A transmitter input and control inputsaccept3.3V LVTTL/LVCMOS levels.They are not5V tolerant.3.To implement a falling edge device for the DS90C385A,the R_FB pin may be tied to ground OR left unconnected (an internal pull-down resistor biases this pin low).Bias-ing this pin to Vcc implements a rising edge device. TRANSMITTER INPUT PINSThe TxIN and control input pins are compatible with LVC-MOS and LVTTL levels.These pins are not5V tolerant. TRANSMITTER INPUT CLOCK/DATA SEQUENCING Unlike the DS90C385,DS90C(F)383A/363A,the DS90C385A does not require any special requirement for sequencing of the input clock/data and PD(PowerDown) signal.The DS90C385A offers a more robust input sequenc-ing feature where the input clock/data can be inserted after the release of the PD signal.In the case where the clock/ data is stopped and reapplied,such as changing video mode within Graphics Controller,it is not necessary to cycle the PD signal.However,there are in certain cases where the PD may need to be asserted during these mode changes.In cases where the source(Graphics Source)may be supply-ing an unstable clock or spurious noisy clock output to the LVDS transmitter,the LVDS Transmitter may attempt to lock onto this unstable clock signal but is unable to do so due the instability or quality of the clock source.The PD signal in these cases should then be asserted once a stable clock is applied to the LVDS transmitter.Asserting the PWR DOWN pin will effectively place the device in reset and disable the PLL,enabling the LVDS Transmitter into a power saving standby mode.However,it is still generally a good practice to assert the PWR DOWN pin or reset the LVDS transmitter whenever the clock/data is stopped and reapplied but it is not mandatory for the DS90C385A.SPREAD SPECTRUM CLOCK SUPPORTThe DS90C385A can support Spread Spectrum Clocking signal type inputs.The DS90C385A outputs will accurately track Spread Spectrum Clock/Data inputs with modulation frequencies of up to100kHz(max.)with either center spread of±2.5%or down spread-5%deviations.POWER SOURCES SEQUENCEIn typical applications,it is recommended to have V CC,LVDS V CC and PLL V CC from the same power source with three separate de-coupling bypass capacitor groups.There is no requirement on which VCC entering the device first.Pin Diagram for TSSOP PackagesDS90C385AMT20070223DS90C385A11Typical Application20070203Truth TableTABLE 1.Programmable Transmitter (DS90C385A)Pin Condition Strobe Status R_FB R_FB =V CCRising edge strobe R_FBR_FB =GND or NCFalling edge strobeD S 90C 385A 12Physical Dimensionsinches (millimeters)unless otherwise noted56-Lead Molded Thin Shrink Small Outline Package,JEDECDimensions in millimeters only Order Number DS90C385AMT NS Package Number MTD56National does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.For the most current product information visit us at .LIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or systems which,(a)are intended for surgical implant into the body,or (b)support or sustain life,and whose failure to perform when properly used in accordance with instructions for use provided in the labeling,can be reasonably expected to result in a significant injury to the user.2.A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.BANNED SUBSTANCE COMPLIANCENational Semiconductor manufactures products and uses packing materials that meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2)and the Banned Substances and Materials of Interest Specification (CSP-9-111S2)and contain no ‘‘Banned Substances’’as defined in CSP-9-111S2.Leadfree products are RoHS compliant.National Semiconductor Americas Customer Support CenterEmail:new.feedback@ Tel:1-800-272-9959National SemiconductorEurope Customer Support CenterFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)6995086208English Tel:+44(0)8702402171Français Tel:+33(0)141918790National Semiconductor Asia Pacific Customer Support CenterEmail:ap.support@National SemiconductorJapan Customer Support Center Fax:81-3-5639-7507Email:jpn.feedback@ Tel:81-3-5639-7560DS90C385A +3.3V Programmable LVDS Transmitter 24-bit Flat Panel Display (FPD)Link-87.5MHz。