GC4732中文资料

GC4722中文资料

DESCRIPTIONThe GC4700series diodes are specially processed PIN diodes designed for use in passive or active limiters at frequencies through Ku band.Twelve categories of devices are offered for flexibility in design of low (lower Vb,fastest turn-on time),me-dium and high (highest Vb,slowest turn-on time)power limiters.LIMITER DIODESAPPLICATIONSA diode limiter is a power-sensitive variable attenuatorthat uses the non-linear properties of the diode to pro-vide an impedance mismatch when sufficient amounts of RF power are incident on the device.The output power is reduced to a level that will not overdrive a re-ceiver,burn out a mixer,etc.For varying input power levels in excess of the diode’s threshold level,the limiter’s output power tends to remain constant.A passive limiter is one in which the limiter diodes are “turned on”by the RF signal itself.An active limiter is one in which the limiter diodes are “turned on”primarily by an external bias current typically supplied by a Schottky de-tector diode which senses the incident signal.Since limiter diodes are not designed to dissipate large amounts of power,the limiter must reflect or divert the excess incident power back to the source or to another load (i.e.via a circulator,hybrid coupler,etc.).Limiter diodes may be used in wave guides,coax,mi-crostrip,stripline or other media.Single or cascaded devices may be used,depending on power levels.1)Pulse length 1microsecond.2)As measure in style 30package.BASIC TWO-DIODE LIMITERSEMICONDUCTOR OPERATION75T echnology Drive Lowell,MA 01851 T el:978-442-5600 Fax:978-937-374883Control DevicesLIMITER DIODESRATINGSMaximum Leakage Current:0.5µA at 80%of minimum rated breakdown Operating Temperature:55°C to +150°CTYPICAL PERFORMANCENotes:1.Available in standard case styles 30,35,42AND 45.When ordering specify the desired case style by adding its number as a suffix to the basicpart number.Some other case styles are available on request.P O W E R O U T (m w )+1.0+10+100+100010,000+10+20+30+40+50PEAK POWER INPUT (dBm)+1+2+3+4+5+6+7+8+924681012141618L E A K A G E P O W E R A B O V E 1.0G H z (d B )FREQUENCY (GHz)GC4701, 4741GC4721SEMICONDUCTOR OPERATION75T echnology Drive Lowell,MA 01851 T el:978-442-5600 Fax:978-937-374884Control Devices。

元件型号1N4742A(rectron)中文数据手册「EasyDatasheet」

芯片中文手册,看全文,戳

额 定 值 和 特 性 曲 线 ( 1N4728A-1N4758A)

1.0

C/W) 250

0.8

200

0.6

150

0.4

100

,总功耗(W)

0.2

50

Pd

0

0

,QTJHAERM0AL RESISTANCE JUNCTION TO AMBIENT (

40

80 120 160 200 R 0 5 10 15 20 25 30

100

5mA

10mA

20mA

差分齐1纳0 阻0 10 20 30 40 50 60

0

10

100

VZ, ZENER VOLTAGE(V)

VZ, ZENER VOLTAGE(V)

Figure3结电容VS齐纳电压

Figure4典型齐纳阻抗与齐纳电压

1000

MINIMUM

500

MAXIMUM

ZZk@IZk

(W)

MAX

400 400 400 400 500 550 600 700 700 700 700 700 700 700 700 700 700 700 700 750 750 750 750 1000 1000 1000 1000 1500 1500 1500 2000

IR@VR

(mA)

RECTRON

VZT@IZT

(伏)

标称

3.3 3.6 3.9 4.3 4.7 5.1 5.6 6.2 6.8 7.5 8.2 9.1 10 11 12 13 15 16 18 20 22 24 27 30 33 36 39 43 47 51 56

IZT

按GB150与JB4732编制设备强度计算书

55.15

mm

δd = δ + C2 =

58.15

mm

名义厚度:

δ'n = δd + C1 =

58.45

mm

取

δn =

80

mm

有效厚度:

δe = δn - C1 - C2

76.7

mm

1.结构设计时应保证锥段的母线长度≥559.1mm.(本锥体的母线长度约为2252mm)

2.与锥壳大端连接处的圆筒加强段长度应≥316.3mm,此段圆筒厚度应≥37.88mm。(不包义厚度:

取

有效厚度:

最小厚度: 检验结论:

C = C1 + C2 = δ'nh = δh + C =

δnh =

1.60 10.80

12

δeh = δnh - C1 C2 =

10.4

δmin=

6

满足最小厚度要求

应力校核

mm mm mm

mm

mm 合格

说明: 1、当Ri/ri≤

无数值 mm 51.40

δ/Ri<0.002 mm

不符合

名义厚度:

δ'n = δd + C1 =

51.70

mm

取

δn =

60

mm

有效厚度:

δe = δn - C1 - C2 =

58

mm

设计

计 算内压 力

计 算外压 力 设计温度 锥壳大端内直径

锥壳小端内直径 锥体切线高度 锥体半顶角 锥壳大端折边半径 (至内壁) 锥壳小端折边半径 (至外壁) 锥壳材料

(适用标准:JB4732-2005)

容器代号: 容器名称: 所属图号: 设 计: 校 对: 审 核: 批 准: 日 期:

EETHC1C473LJ中文资料(panasonic)中文数据手册「EasyDatasheet - 矽搜」

½ 33000

35

长短

(mm)

25 30 25 35 40 30 45 35 25 50 40 30 25 45 35 30 40 35 45 40 50 45 50 25 30 25 35 40 30 45 35 25 50 40 30 25 45 35 30 40 35 45 40 50 45 50

200

33000

22 25

45

EETHC1A333HJ

40

EETHC1A333JJ

3.40

0.65

3.40

0.65

200 200

10

25

45

EETHC1A393JJ

3.70

0.71

200

39000

30

30

EETHC1A393KJ

3.70

0.71

200

35

25

EETHC1A393LJ

3.70

0.71

200

200 200

22

45

EETHC1C223HJ

3.80

0.55

200

22000

25

35

EETHC1C223JJ

3.80

0.55

200

30

25

EETHC1C223KJ

3.80

0.55

200

22

50

EETHC1C273HJ

4.20

0.55

200

16

27000

25 30

40

EETHC1C273JJ

30

EETHC1C273KJ

产品规格

最小包装台数

涟

tan δ

当前

IN4732A中文资料

For BZXyy series: Voltage rating 5.0 Third Line: Device name - For 1Nxx series: 7th to 8th characters of the device name.

4.085

4.3

4.515

4.465

4.7

4.935

4.845

5.1

5.355

5.32

5.6

5.88

5.89

6.2

6.51

6.46

6.8

7.14

7.125

7.5

7.875

7.79

8.2

8.61

8.645

9.1

9.555

9.5

10

10.5

10.45

11

11.55

11.4

12

12.6

12.35

13

13.65

1N4753A 1N4754A 1N4755A 1N4756A 1N4757A

1N4758A 1N4759A 1N4760A 1N4761A 1N4762A

1N4763A 1N4764A

Line 1

LOGO LOGO LOGO LOGO LOGO

LOGO LOGO LOGO LOGO LOGO

LOGO LOGO LOGO LOGO LOGO

1N4733A 1N4734A 1N4735A 1N4736A 1N4737A

华芯飞JZ4732 JZ4740 JZ47XX系统烧录工具下载[多线程版--带驱动]

![华芯飞JZ4732 JZ4740 JZ47XX系统烧录工具下载[多线程版--带驱动]](https://img.taocdn.com/s3/m/a6818566caaedd3383c4d30e.png)

华芯飞JZ4732/JZ4740/JZ47XX系统烧录工具下载[多线程版--带驱动]Post By:2008-4-24 18:17: 19华芯飞JZ47XX方案烧录/刷机/升级说明:=======================================请认真回贴,您的回复是发贴人的动力,否则将有可能无法下载相关附件,发垃圾贴,灌水严重者封ID 或IP方法一(推荐):具体步骤如下:1、使用USB数据线,将播放器与电脑连接。

2、将ABC.HXF升级文档复制到播放器的根目录下(文件名不能更改)。

3、从电脑USB端口安全移除播放器。

4、按OK键不松手,同时按(开机键),播放器将自动进行升级状态,显示如图1:以下内容只有回复后才可以浏览此主题相关图片如下:1.jpg升级完成后进入主界面。

注意:升级时请务必保证播放器有足够的电量,以免电量不足导至升级失败。

如果本机现有的软件与升级软件版本相同时,升级时将出现以下界面(图2),此主题相关图片如下:2.jpg.jpg播放器将直接进入主界面。

方法二:具体步骤如下:1、按住“下一曲”键(如图3);此主题相关图片如下:3.jpg2、将USB线插入播放器的USB插口,另一端连接电脑,电脑屏幕将出现“发现新硬件”提示(如图4);并弹出“安装新硬件向导”,按电脑提示(图5-8)将播放的驱动程序安装好;3、将播放器的驱动程序安装好后,点击“此主题相关图片如下:drv.jpg”,弹出系统烧录工具(如图9),此主题相关图片如下:4.jpg此主题相关图片如下:5.jpg此主题相关图片如下:6.jpg此主题相关图片如下:78.jpg“浏览”选择光碟内的“usb_drv”文件夹此主题相关图片如下:9.jpg4、系统配置在光碟中选择“ABC_5060.dl”文件,系统文件在光碟中选择“ABC.HXF”文件,然后点击“烧录系统”,进行烧录(如图10);此主题相关图片如下:10.jpg5、烧录成功(如图11),此主题相关图片如下:11.jpg烧录成功后,弹出USB,重新开机,即可正常使用。

LM4732资料

LM4732Stereo 50W Audio Power Amplifier with MuteGeneral DescriptionThe LM4732is a stereo audio amplifier capable of typically delivering 50W per channel of continuous average output power into a 4Ωor 8Ωload with less than 10%THD+N from 20Hz -20kHz.The LM4732has short circuit protection and a thermal shut down feature that is activated when the die temperature exceeds 150˚C.The LM4732also has an under voltage lock out feature for click and pop free power on and off.Each amplifier of the LM4732has an independent smooth transition fade-in/out mute.The LM4732has a wide operating supply range from +/-10V -+/-40V allowing for lower cost unregulated power supplies to be used.The LM4732amplifiers can easily be configured for bridge or parallel operation for 100W mono solutions.Key Specificationsj Output Power/Channel at 10%THD+N,1kHz into 4Ωor 8Ω50W (typ)j THD+N at 2x 1W into 8Ω,1kHz 0.01%(typ)j Mute Attenuation 110dB (typ)j PSRR 89dB (typ)j Slew Rate19V/µs (typ)Featuresn Low external component count n Quiet fade-in/out mute mode n Wide supply range:20V -80VApplicationsn Audio amplifier for component stereo n Audio amplifier for compact stereon Audio amplifier for self-powered speakers n Audioamplifierforhigh-end and HD TVsTypical Application20072422FIGURE 1.Typical Audio Amplifier Application CircuitJuly 2003LM4732Stereo 50W Audio Power Amplifier with Mute©2003National Semiconductor Corporation Connection DiagramsPlastic Package (Note 13)200724D7Top ViewOrder Number LM4732TA See NS Package Number TA27ATO-220Top Marking200724D6Top ViewU -Wafer Fab Code Z -Assemble Plant CodeXY -Date CodeTT -Die Run Traceability L4732TA -LM4732TAL M 4732 2Absolute Maximum Ratings(Notes1, 2)If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.Supply Voltage|V+|+|V-|80V Common Mode Input Voltage(V+or V-)and|V+|+|V-|≤80V Differential Input Voltage(Note12)60V Output Current Internally Limited Power Dissipation(Note3)125W ESD Susceptability(Note4) 3.0kV ESD Susceptability(Note5)200V Junction Temperature(T JMAX)(Note9)150˚CSoldering InformationTA Package(10seconds)260˚C Storage Temperature-40˚C to+150˚C Thermal ResistanceθJA30˚C/W θJC0.8˚C/W Operating Ratings(Notes1,2) Temperature RangeT MIN≤T A≤T MAX−20˚C≤T A≤+85˚C Supply Voltage|V+|+|V-|20V≤V TOTAL≤80VElectrical Characteristics(Notes1,2)The following specifications apply for V+=+29V,V-=−29V,I MUTE=-1mA/Channel and R L=8Ωunless otherwise specified. Limits apply for T A=25˚C.Symbol Parameter Conditions LM4732Units(Limits)Typical Limit(Note6)(Notes7,8)|V+|+|V-|Power Supply Voltage(Note10)V PIN7−V-≥9V182080V(min)V(max)A M Mute Attenuation I MUTE=0mA110dBP O Output Power(RMS)THD+N=10%(max),f=1kHz|V+|=|V-|=22V,R L=4Ω|V+|=|V-|=29V,R L=8Ω50504545W(min)W(min) THD+N=1%(max),f=1kHz|V+|=|V-|=22V,R L=4Ω|V+|=|V-|=29V,R L=8Ω4242WWTHD+N Total Harmonic Distortion+NoiseP O=1W,f=1kHzA V=26dB|V+|=|V-|=22V,R L=4Ω|V+|=|V-|=29V,R L=8Ω0.020.01%%X talk Channel Separation(Note11)P O=10W,f=1kHz70dB P O=10W,f=10kHz72dBSR Slew Rate V IN=2.0V P-P,t RISE=2ns19V/µsI DD Total Quiescent Power V CM=0V,105170mA(max)Supply Current V O=0V,I O=0AV OS Input Offset Voltage V CM=0V,I O=0mA110mV(max) I B Input Bias Current V CM=0V,I O=0mA0.2µAPSRR Power Supply Rejection Ratio V EE=-29V+V RIPPLE=1V RMSf RIPPLE=120Hz sine wave,V CC=29V DC62dB V CC=29V+V RIPPLE=1V RMSf RIPPLE=120Hz sine wave,V EE=-29V DC89dBA VOL Open Loop Voltage Gain R L=2kΩ,∆V O=40V115dBe IN Input Noise IHF-A-Weighting Filter,R IN=600Ω(Input Referred)2.0µVNote1:All voltages are measured with respect to the ground pins,unless otherwise specified.Note2:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.Operating Ratings indicate conditions for which the device is functional,but do not guarantee specific performance limits.Electrical Characteristics state DC and AC electrical specifications under particular test conditions which guarantee specific performance limits.This assumes that the device is within the Operating Ratings.Specifications are not guaranteed for parameters where no limit is given;however,the typical value is a good indication of device performance.LM47323Electrical Characteristics (Notes 1,2)(Continued)Note 3:The maximum power dissipation must be de-rated at elevated temperatures and is dictated by T JMAX ,θJC ,and the ambient temperature T A .The maximum allowable power dissipation is P DMAX =(T JMAX -T A )/θJC or the number given in the Absolute Maximum Ratings,whichever is lower.For the LM4732,T JMAX =150˚C and the typical θJC is 0.8˚C/W.Refer to the Thermal Considerations section for more information.Note 4:Human body model,100pF discharged through a 1.5k Ωresistor.Note 5:Machine Model:a 220pF -240pF discharged through all pins.Note 6:Typical specifications are measured at 25˚C and represent the parametric norm.Note 7:Tested limits are guaranteed to National’s AOQL (Average Outgoing Quality Level).Note 8:Datasheet min/max specification limits are guaranteed by design,test,or statistical analysis.Note 9:The maximum operating junction temperature is 150˚C.However,the instantaneous Safe Operating Area temperature is 250˚C.Note 10:V -must have at least -9V at its pin with reference to GND in order for the under-voltage protection circuitry to be disabled.In addition,the voltage differential between V +and V -must be greater than 14V.Note 11:Cross talk performance was measured using the demo board shown in the datasheet.PCB layout will affect cross talk.It is recommended that input and output traces be separated by as much distance as possible.Return ground traces from outputs should be independent back to a single ground point and use as wide of traces as possible.Note 12:The Differential Input Voltage Absolute Maximum Rating is based on supply voltages V +=40V and V -=-40V.Note 13:The TA27A is a non-isolated package.The package’s metal back,and any heat sink to which it is mounted are connected to the V -potential when using only thermal compound.If a mica washer is used in addition to thermal compound,θCS (case to sink)is increased,but the heat sink will be electrically isolated from V -.Note 14:CCIR/ARM:A Practical Noise Measurement Method;by Ray Dolby,David Robinson and Kenneth Gundry,AES Preprint No.1353(F-3).L M 4732 4LM4732 Bridged Amplifier Application Circuit20072414FIGURE2.Bridged Amplifier Application Circuit5Parallel Amplifier Application Circuit20072413FIGURE 3.Parallel Amplifier Application CircuitL M 4732 6Single Supply Application CircuitNote:*Optional components dependent upon specific design requirements.Auxiliary Amplifier Application Circuit20072406FIGURE 4.Single Supply Amplifier Application Circuit200724D5FIGURE 5.Special Audio Amplifier Application CircuitLM47327External Components Description(Figures 1-5)Components Functional Description1R BPrevents current from entering the amplifier’s non-inverting input.This current may pass through to the load during system power down,because of the amplifier’s low input impedance when the undervoltage circuitry is off.This phenomenon occurs when the V +and V -supply voltages are below 1.5V.2R i Inverting input resistance.Along with R f ,sets AC gain.3R fFeedback resistance.Along with R i ,sets AC gain.4R f2(Note 15)Feedback resistance.Works with Cf and Rf creating a lowpass filter that lowers AC gain at high frequencies.The -3dB point of the pole occurs when:(R f -R i )/2=R f //[1/(2πf c C f )+R f2]for the Non-Inverting configuration shown in Figure 5.5C f(Note 15)Compensation capacitor.Works with R f and R f2to reduce AC gain at higher frequencies.6C C(Note 15)Compensation capacitor.Reduces the gain at higher frequencies to avoid quasi-saturation oscillations of the output transistor.Also suppresses external electromagnetic switching noise created from fluorescent lamps.7C i(Note 15)Feedback capacitor which ensures unity gain at DC.Along with R i also creates a highpass filter at f c =1/(2πR i C i ).8C SProvides power supply filtering and bypassing.Refer to the Supply Bypassing application section for proper placement and selection of bypass capacitors.9R V(Note 15)Acts as a volume control by setting the input voltage level.10R IN(Note 15)Sets the amplifier’s input terminals DC bias point when C IN is present in the circuit.Also works with C IN to create a highpass filter at f C =1/(2πR IN C IN ).If the value of R IN is too large,oscillations may be observed on the outputs when the inputs are floating.Recommended values are 10k Ωto 47k Ω.Refer to Figure 5.11C IN(Note 15)Input capacitor.Prevents the input signal’s DC offsets from being passed onto the amplifier’s inputs.12R SN(Note 15)Works with C SN to stabilize the output stage by creating a pole that reduces high frequency instabilities.13C SN(Note 15)Works with R SN to stabilize the output stage by creating a pole that reduces high frequency instabilities.The pole is set at f C =1/(2πR SN C SN ).Refer to Figure 5.14L (Note 15)Provides high impedance at high frequencies so that R may decouple a highly capacitive load and reduce the Q of the series resonant circuit.Also provides a low impedance at low frequencies to short out R and pass audio signals to the load.Refer to Figure 5.15R (Note 15)16R A Provides DC voltage biasing for the transistor Q1in single supply operation.17C AProvides bias filtering for single supply operation.18R INP(Note 15)Limits the voltage difference between the amplifier’s inputs for single supply operation.Refer to the Clicks and Pops application section for a more detailed explanation of the function of R INP .19R BI Provides input bias current for single supply operation.Refer to the Clicks and Pops application section for a more detailed explanation of the function of R BI .20R E Establishes a fixed DC current for the transistor Q1in single supply operation.This resistor stabilizes the half-supply point along with C A .21R MMute resistance set up to allow 0.5mA to be drawn from each MUTE pin to turn the muting function off.→R M is calculated using:R M ≤(|V EE |−2.6V)/l where l ≥0.5mA.Refer to the Mute Attenuation vs Mute Current curves in the Typical Performance Characteristics section.22C M Mute capacitance set up to create a large time constant for turn-on and turn-off muting.23S 1Mute switch.When open or switched to GND,the amplifier will be in mute mode.24R OUTReduces current flow between outputs that are caused by Gain or DC offset differences between the amplifiers.Note 15:Optional components dependent upon specific design requirements.L M 4732 8Optional External Component InteractionThe optional external components have specific desired functions.Their values are chosen to reduce the bandwidth and eliminate unwanted high frequency oscillation.They may,however,cause certain undesirable effects when they interact.Interaction may occur when the components pro-duce reactions that are nearly equal to one another.One example is the coupling capacitor,C C,and the compensa-tion capacitor,C f.These two components are low imped-ances at certain frequencies.They may couple signals from the input to the output.Please take careful note of basic amplifier component functionality when selecting the value of these components and their placement on a printed circuit board(PCB).The optional external components shown in Figure4and Figure5,and described above,are applicable in both single and split supply voltage configurations.Typical Performance CharacteristicsSupply Current vs Supply VoltagePSRR vs Frequency±29V,VRIPPLE=1V RMSR L=8Ω,80kHz BW200724E5200724E4THD+N vs Frequency ±22V,POUT=1W/Channel R L=4Ω,80kHz BWTHD+N vs Frequency±29V,POUT=1W/ChannelR L=8Ω,80kHz BW200724D8200724E6LM4732 9Typical Performance Characteristics(Continued)THD+N vs Output Power/Channel±22V,R L =4Ω,80kHz BWTHD+N vs Output Power/Channel±29V,R L =8Ω,80kHz BW200724F0200724F1Output Power/Channel vs Supply Voltagef =1kHz,R L =4Ω,80kHz BW Output Power/Channel vs Supply Voltagef =1kHz,R L =8Ω,80kHz BW200724E2200724E3Total Power Dissipation vs Output Power/Channel1%THD (max),R L =4Ω,80kHz BW Total Power Dissipation vs Output Power/Channel1%THD (max),R L =8Ω,80kHz BW200724F3200724D9L M 4732 10Typical Performance Characteristics(Continued)Crosstalk vs Frequency ±22V,P OUT =10W R L =4Ω,80kHz BWCrosstalk vs Frequency ±29V,P OUT =10W R L =8Ω,80kHz BW200724C5200724A5Mute Attenuation vs Mute Pin Current P OUT =10W/ChannelCommon Mode Rejection Ratio200724C6200724C9THD+N vs Frequency ±22V,P OUT =1W &50WBridge Mode (Note 16),R L =8Ω,80kHz BW THD+N vs Frequency ±29V,P OUT =1W &50WParallel Mode (Note 17),R L =4Ω,80kHz BW200724E8200724E9LM473211Typical Performance Characteristics(Continued)THD+N vs Output Power±22V,Bridge Mode (Note 16)R L =8Ω,80kHz BWTHD+N vs Output Power±29V,Parallel Mode (Note 17)R L =4Ω,80kHz BW200724F2200724E7Output Power vsSupply Voltage,Bridge Mode (Note 16)f =1kHz,R L =8Ω,80kHz BW Output Power vsSupply Voltage,Parallel Mode (Note 17)f =1kHz,R L =4Ω,80kHz BW200724E0200724E1Note 16:Bridge mode graphs were taken using the demo board and inverting the signal to the channel B input.Note 17:Parallel mode graphs were taken using the demo board and connecting each output through a 0.1Ω/3W resistor to the load.L M 4732 12Application InformationMUTE MODEThe muting function allows the user to mute the amplifier. This can be accomplished as shown in the Typical Applica-tion Circuit.The resistor R M is chosen with reference to the negative supply voltage and is used in conjunction with a switch.The switch,when opened or switched to GND,cuts off the current flow from the MUTE pins to−V EE,thus placing the LM4732into mute mode.Refer to the Mute Attenuation vs Mute Current curves in the Typical Performance Char-acteristics section for values of attenuation per current out of each MUTE pin.The resistance R M is calculated by the following equation:R M≤(|−V EE|−2.6V)/I MUTEWhere I MUTE≥0.5mA for each MUTE pin.The MUTE pins can be tied together so that only one resistor is required for the mute function.The mute resistor value must be chosen so that a minimum of1mA is pulled through the resistor R M.This ensures that each amplifier is fully operational.Taking into account supply line fluctuations,it is a good idea to pull out1mA per MUTE pin or2mA total if both pins are tied together.A turn-on MUTE or soft start circuit may also be used during power up.A simple circuit like the one shown below may be used.200724A3The RC combination of C M and R M1may cause the voltage at point A to change more slowly than the-V EE supply voltage.Until the voltage at point A is low enough to have 0.5mA of current per MUTE pin flow through R M2,the IC will be in mute mode.The series combination of R M1and R M2 needs to satisfy the mute equation above for all operating voltages or mute mode may be activated during normal operation.For a longer turn-on mute time,a larger time constant,τ=RC=R M1C M(sec),is needed.For the values show above and with the MUTE pins tied together,the LM4732will enter play mode when the voltage at point A is -17.6V.The voltage at point A is found with Equation(1) below.V A(t)=(V f-V O)e-t/τ(Volts)(1) where:t=time(sec)τ=RC(sec)V o=Voltage on C at t=0(Volts)V f=Final voltage,-V EE in this circuit(Volts)UNDER-VOLTAGE PROTECTIONUpon system power-up,the under-voltage protection cir-cuitry allows the power supplies and their corresponding capacitors to come up close to their full values before turning on the LM4732.Since the supplies have essentially settled to their final value,no DC output spikes occur.At power down,the outputs of the LM4732are forced to ground before the power supply voltages fully decay preventing transients on the output.OVER-VOLTAGE PROTECTIONThe LM4732contains over-voltage protection circuitry thatlimits the output current while also providing voltage clamp-ing.The clamp does not,however,use internal clampingdiodes.The clamping effect is quite the same because theoutput transistors are designed to work alternately by sinkinglarge current spikes.THERMAL PROTECTIONThe LM4732has a sophisticated thermal protection schemeto prevent long-term thermal stress of the device.When thetemperature on the die exceeds150˚C,the LM4732shutsdown.It starts operating again when the die temperaturedrops to about145˚C,but if the temperature again begins torise,shutdown will occur again above150˚C.Therefore,thedevice is allowed to heat up to a relatively high temperatureif the fault condition is temporary,but a sustained fault willcause the device to cycle in a Schmitt Trigger fashion be-tween the thermal shutdown temperature limits of150˚C and145˚C.This greatly reduces the stress imposed on the IC bythermal cycling,which in turn improves its reliability undersustained fault conditions.Since the die temperature is directly dependent upon theheat sink used,the heat sink should be chosen so thatthermal shutdown is not activated during normal operation.Using the best heat sink possible within the cost and spaceconstraints of the system will improve the long-term reliabilityof any power semiconductor device,as discussed in theDetermining the Correct Heat Sink section.DETERMlNlNG MAXIMUM POWER DISSIPATIONPower dissipation within the integrated circuit package is avery important parameter requiring a thorough understand-ing if optimum power output is to be obtained.An incorrectmaximum power dissipation calculation may result in inad-equate heat sinking causing thermal shutdown and thuslimiting the output power.Equation(2)shows the theoretical maximum power dissipa-tion point of each amplifier in a single-ended configurationwhere V CC is the total supply voltage.P DMAX=(V CC)2/2π2R L(2) Thus by knowing the total supply voltage and rated outputload,the maximum power dissipation point can be calcu-lated.The package dissipation is twice the number whichresults from Equation(2)since there are two amplifiers ineach LM4732.Refer to the graphs of Power Dissipationversus Output Power in the Typical Performance Charac-teristics section which show the actual full range of powerdissipation not just the maximum theoretical point that re-sults from Equation(2).DETERMINING THE CORRECT HEAT SINKThe choice of a heat sink for a high-power audio amplifier ismade entirely to keep the die temperature at a level suchthat the thermal protection circuitry is not activated undernormal circumstances.The thermal resistance from the die to the outside air,θJA(junction to ambient),is a combination of three thermal re-sistances,θJC(junction to case),θCS(case to sink),andθSA(sink to ambient).The thermal resistance,θJC(junction tocase),of the LM4732T is0.8˚C/ing Thermalloy Ther-macote thermal compound,the thermal resistance,θCS(case to sink),is about0.2˚C/W.Since convection heat flow(power dissipation)is analogous to current flow,thermalLM473213Application Information(Continued)resistance is analogous to electrical resistance,and tem-perature drops are analogous to voltage drops,the power dissipation out of the LM4732is equal to the following:P DMAX =(T JMAX −T AMB )/θJA (3)where T JMAX =150˚C,T AMB is the system ambient tempera-ture and θJA =θJC +θCS +θSA .20072452Once the maximum package power dissipation has been calculated using Equation (2),the maximum thermal resis-tance,θSA ,(heat sink to ambient)in ˚C/W for a heat sink can be calculated.This calculation is made using Equation (4)which is derived by solving for θSA in Equation (3).θSA =[(T JMAX −T AMB )−P DMAX (θJC +θCS )]/P DMAX (4)Again it must be noted that the value of θSA is dependent upon the system designer’s amplifier requirements.If the ambient temperature that the audio amplifier is to be working under is higher than 25˚C,then the thermal resistance for the heat sink,given all other things are equal,will need to be smaller.SUPPLY BYPASSINGThe LM4732has excellent power supply rejection and does not require a regulated supply.However,to improve system performance as well as eliminate possible oscillations,the LM4732should have its supply leads bypassed with low-inductance capacitors having short leads that are located close to the package terminals.Inadequate power supply bypassing will manifest itself by a low frequency oscillation known as “motorboating”or by high frequency instabilities.These instabilities can be eliminated through multiple by-passing utilizing a large tantalum or electrolytic capacitor (10µF or larger)which is used to absorb low frequency variations and a small ceramic capacitor (0.1µF)to prevent any high frequency feedback through the power supply lines.If adequate bypassing is not provided,the current in the supply leads which is a rectified component of the load current may be fed back into internal circuitry.This signal causes distortion at high frequencies requiring that the sup-plies be bypassed at the package terminals with an electro-lytic capacitor of 470µF or more.BRIDGED AMPLIFIER APPLICATIONThe LM4732has two operational amplifiers internally,allow-ing for a few different amplifier configurations.One of these configurations is referred to as “bridged mode”and involves driving the load differentially through the LM4732’s outputs.This configuration is shown in Figure 2.Bridged mode op-eration is different from the classical single-ended amplifier configuration where one side of its load is connected to ground.A bridge amplifier design has a distinct advantage over the single-ended configuration,as it provides differential drive to the load,thus doubling output swing for a specified supplyvoltage.Theoretically,four times the output power is pos-sible as compared to a single-ended amplifier under thesame conditions.This increase in attainable output power assumes that the amplifier is not current limited or clipped.A direct consequence of the increased power delivered to the load by a bridge amplifier is an increase in internal power dissipation.For each operational amplifier in a bridge con-figuration,the internal power dissipation will increase by a factor of two over the single ended dissipation.Thus,for an audio power amplifier such as the LM4732,which has two operational amplifiers in one package,the package dissipa-tion will increase by a factor of four.To calculate the LM4732’s maximum power dissipation point for a bridged load,multiply Equation (2)by a factor of four.This value of P DMAX can be used to calculate the correct size heat sink for a bridged amplifier application.Since the inter-nal dissipation for a given power supply and load is in-creased by using bridged-mode,the heatsink’s θSA will have to decrease accordingly as shown by Equation (4).Refer to the section,Determining the Correct Heat Sink,for a more detailed discussion of proper heat sinking for a given appli-cation.PARALLEL AMPLIFIER APPLICATIONParallel configuration is normally used when higher output current is needed for driving lower impedance loads (i.e.4Ωor lower)to obtain higher output power levels.As shown in Figure 3,the parallel amplifier configuration consist of de-signing the amplifiers in the IC to have identical gain,con-necting the inputs in parallel and then connecting the outputs in parallel through a small external output resistor.Any num-ber of amplifiers can be connected in parallel to obtain the needed output current or to divide the power dissipation across multiple IC packages.Ideally,each amplifier shares the output current equally.Due to slight differences in gain the current sharing will not be equal among all channels.If current is not shared equally among all channels then the power dissipation will also not be equal among all channels.It is recommended that 0.1%tolerance resistors be used to set the gain (R i and R f )for a minimal amount of difference in current sharing.When operating two or more amplifiers in parallel mode the impedance seen by each amplifier is equal to the total load impedance multiplied by the number of amplifiers driving the load in parallel as shown by Equation (5)below:R L(parallel)=R L(total)*Number of amplifiers(5)Once the impedance seen by each amplifier in the parallel configuration is known then Equation (2)can be used with this calculated impedance to find the amount of power dis-sipation for each amplifier.Total power dissipation (P DMAX )within an IC package is found by adding up the power dissipation for each amplifier in the IC ing the calculated P DMAX the correct heat sink size can be deter-mined.Refer to the section,Determining the Correct Heat Sink ,for more information and detailed discussion of proper heat sinking.SINGLE-SUPPLY AMPLIFIER APPLICATIONThe typical application of the LM4732is a split supply am-plifier.But as shown in Figure 4,the LM4732can also be used in a single power supply configuration.This involves using some external components to create a half-supply bias which is used as the reference for the inputs and outputs.Thus,the signal will swing around half-supply much like it swings around ground in a split-supply application.AlongL M 473214Application Information(Continued)with proper circuit biasing,a few other considerations must be accounted for to take advantage of all of the LM4732 functions,like the mute function.CLICKS AND POPSIn the typical application of the LM4732as a split-supply audio power amplifier,the IC exhibits excellent“click”and “pop”performance when utilizing the mute mode.In addition, the device employs Under-Voltage Protection,which elimi-nates unwanted power-up and power-down transients.The basis for these functions are a stable and constant half-supply potential.In a split-supply application,ground is the stable half-supply potential.But in a single-supply applica-tion,the half-supply needs to charge up at the same rate as the supply rail,V CC.This makes the task of attaining a clickless and popless turn-on more challenging.Any uneven charging of the amplifier inputs will result in output clicks and pops due to the differential input topology of the LM4732. To achieve a transient free power-up and power-down,the voltage seen at the input terminals should be ideally the same.Such a signal will be common-mode in nature,and will be rejected by the LM4732.In Figure4,the resistor R INP serves to keep the inputs at the same potential by limiting the voltage difference possible between the two nodes.This should significantly reduce any type of turn-on pop,due to an uneven charging of the amplifier inputs.This charging is based on a specific application loading and thus,the system designer may need to adjust these values for optimal perfor-mance.As shown in Figure4,the resistors labeled R BI help bias up the LM4732off the half-supply node at the emitter of the 2N3904.But due to the input and output coupling capacitors in the circuit,along with the negative feedback,there are two different values of R BI,namely10kΩand200kΩ.These resistors bring up the inputs at the same rate resulting in a popless turn-on.Adjusting these resistors values slightly may reduce pops resulting from power supplies that ramp extremely quick or exhibit overshoot during system turn-on. PROPER SELECTION OF EXTERNAL COMPONENTS Proper selection of external components is required to meet the design targets of an application.The choice of external component values that will affect gain and low frequency response are discussed below.The gain of each amplifier is set by resistors R f and R i for the non-inverting configuration shown in Figure1.The gain is found by Equation(6)below:A V=1+R f/R i(V/V)(6) For best noise performance,lower values of resistors are used.A value of1kΩis commonly used for R i and then setting the value of R f for the desired gain.For the LM4732 the gain should be set no lower than10V/V and no higher than50V/V.Gain settings below10V/V may experience instability and using the LM4732for gains higher than50V/V will see an increase in noise and THD.The combination of R i with C i(see Figure1)creates a high pass filter.The low frequency response is determined by these two components.The-3dB point can be found from Equation(7)shown below:f i=1/(2πR i C i)(Hz)(7) If an input coupling capacitor is used to block DC from the inputs as shown in Figure5,there will be another high pass filter created with the combination of C IN and R IN.Whenusing a input coupling capacitor R IN is needed to set the DCbias point on the amplifier’s input terminal.The resulting-3dB frequency response due to the combination of C IN andR IN can be found from Equation(8)shown below:f IN=1/(2πR IN C IN)(Hz)(8)With large values of R IN oscillations may be observed on theoutputs when the inputs are left floating.Decreasing thevalue of R IN or not letting the inputs float will remove theoscillations.If the value of R IN is decreased then the value ofC IN will need to increase in order to maintain the same-3dBfrequency response.HIGH PERFORMANCE CONSIDERATIONSUsing low cost electrolytic capacitors in the signal path suchas C IN and C i(see Figures1-5)will result in very goodperformance.However,electrolytic capacitors are less linearthan other premium capacitors.Higher THD+N performancemay be obtained by using high quality polypropylene capaci-tors in the signal path.A more cost effective solution may bethe use of smaller value premium capacitors in parallel withthe larger electrolytic capacitors.This will maintain signalquality in the upper audio band where any degradation ismost noticeable while also coupling in the signals in thelower audio band for good bass response.Distortion is introduced as the audio signal approaches thelower-3dB point,determined as discussed in the sectionabove.By using larger values of capacitors such that the-3dB point is well outside of the audio band will reduce thisdistortion and improve THD+N performance.Increasing the value of the large supply bypass capacitorswill improve burst power output.The larger the supply by-pass capacitors the higher the output pulse current withoutsupply droop increasing the peak output power.This will alsoincrease the headroom of the amplifier and reduce THD.SIGNAL-TO-NOISE RATIOIn the measurement of the signal-to-noise ratio,misinterpre-tations of the numbers actually measured are common.Oneamplifier may sound much quieter than another,but due toimproper testing techniques,they appear equal in measure-ments.This is often the case when comparing integratedcircuit designs to discrete amplifier designs.Discrete transis-tor amps often“run out of gain”at high frequencies andtherefore have small bandwidths to noise as indicated below.20072499Integrated circuits have additional open loop gain allowingadditional feedback loop gain in order to lower harmonicdistortion and improve frequency response.It is this addi-tional bandwidth that can lead to erroneous signal-to-noisemeasurements if not considered during the measurementprocess.In the typical example above,the difference inbandwidth appears small on a log scale but the factor of10inbandwidth,(200kHz to2MHz)can result in a10dB theoreti-cal difference in the signal-to-noise ratio(white noise isproportional to the square root of the bandwidth in a system).LM473215。

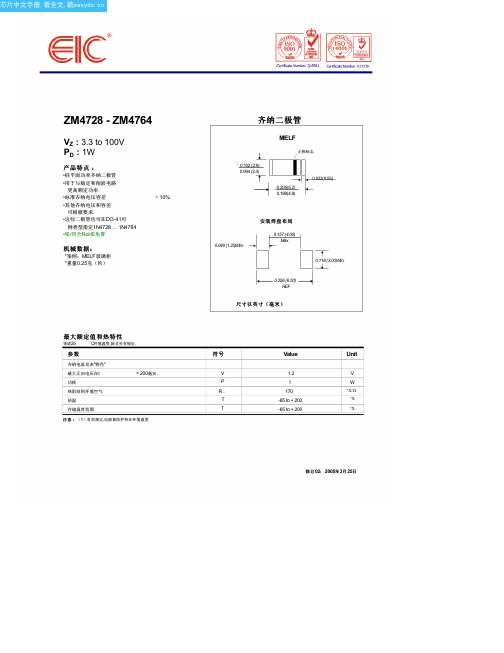

ZM4732中文资料(EIC discrete)中文数据手册「EasyDatasheet - 矽搜」

6.0

ZM4739

9.1

28.0

5.0

700

0.5

10

7.0

ZM4740

10

25.0

7.0

700

0.25

10

7.6

ZM4741

11

23.0

8.0

700

0.25

5.0

8.4

ZM4742

12

21.0

9.0

700

0.25

5.0

9.1

ZM4743

13

19.0

10

700

0.25

5.0

9.9

ZM4744

15

17.0

(µA)

(V)

ZM4728

3.3

76.0

10

400

1.0

100

1.0

ZM4729

3.6

69.0

10

400

1.0

100

1.0

ZM4730

3.9

64.0

9.0

400

1.0

50

1.0

ZM4731

4.3

58.0

9.0

400

1.0

10

1.0

ZM4732

4.7

53.0

8.0

500

1.0

10

1.0

ZM4733

5.1

49.0

7.0

550

1.0

10

1.0

ZM4734

5.6

45.0

5.0

600

1.0

10

2.0

ZM4735

6.2

41.0

MAX4732中文资料

General DescriptionThe MAX4731/MAX4732/MAX4733 low-voltage, dual,single-pole/single-throw (SPST) analog switches oper-ate from a single +2V to +11V supply and handle Rail-to-Rail ®analog signals. These switches exhibit low leakage current (0.1nA) and consume less than 0.5nW (typ) of quiescent power, making them ideal for battery-powered applications.When powered from a +3V supply, these switches fea-ture 50Ω(max) on-resistance (R ON ) with 3.5Ω(max)matching between channels, and 9Ω(max) flatness over the specified signal range.The MAX4731 has two normally open (NO) switches,the MAX4732 has two normally closed (NC) switches,and the MAX4733 has one NO and one NC switch. The MAX4731/MAX4732/MAX4733 are available in a 9-bump chip-scale package (UCSP™) and an 8-pin µMAX package. The tiny UCSP occupies a 1.52mm ✕1.52mm area and significantly reduces the required PC board area.ApplicationsBattery-Powered Systems Audio/Video-Signal RoutingLow-Voltage Data-Acquisition Systems Cell PhonesCommunications Circuits PDAsFeatureso 1.52mm ✕1.52mm UCSP Package o Guaranteed On-Resistance (R ON )25Ω(max) at +5V 50Ω(max) at +3Vo On-Resistance Matching3Ω(max) at +5V 3.5Ω(max) at +3Vo Guaranteed <0.1nA Leakage Current at T A = +25°Co Single-Supply Operation from +2.0V to +11V o TTL/CMOS-Logic Compatible o -108dB Crosstalk (1MHz)o -72dB Off-Isolation (1MHz)o Low Power Consumption: 0.5nW (typ)o Rail-to-Rail Signal HandlingMAX4731/MAX4732/MAX473350ΩDual SPST Analog Switches in UCSP________________________________________________________________Maxim Integrated Products 1Ordering Information19-2645; Rev 0; 10/02For pricing, delivery, and ordering information,please contact Maxim/Dallas Direct!at 1-888-629-4642, or visit Maxim’s website at .Pin Configurations/Functional Diagrams/Truth TablesNote:Requires special solder temperature profile described in the Absolute Maximum Ratings section.**UCSP reliability is integrally linked to the user’s assemblymethods, circuit board material, and environment. See the UCSP Reliability section of this data sheet for more information.UCSP is a trademark of Maxim Integrated Products, Inc.Rail-to-Rail is a registered trademark of Nippon Motorola, Ltd.*Future product—contact factory for availability.M A X 4731/M A X 4732/M A X 473350ΩDual SPST Analog Switches in UCSP 2_______________________________________________________________________________________ABSOLUTE MAXIMUM RATINGSELECTRICAL CHARACTERISTICS —Single +3V Supply(V+ = +3V ±10%, V IH = +2.0V, V IL = +0.8V, T A = T MIN to T MAX , unless otherwise noted. Typical values are at V+ = +3V, T A = +25°C.)Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.(All Voltages Referenced to GND)V+...........................................................................-0.3V to +12V IN_, COM_, NO_, NC_ (Note 1)....................-0.3V to (V+ + 0.3V)Continuous Current (any pin)...........................................±10mA Peak Current (any pin, pulsed at 1ms, 10% duty cycle)...±20mA Continuous Power Dissipation (T A = +70°C)8-Pin µMAX (derate 4.5mW/°C above +70°C).............362mW 9-Bump UCSP (derate 4.7mW/°C above +70°C).........379mWOperating Temperature Range ...........................-40°C to +85°C Storage Temperature Range.............................-65°C to +150°C Maximum Junction Temperature.....................................+150°C Lead Temperature (soldering, 10s).................................+300°C Bump Temperature (soldering, Note 2)Infrared (15s)...............................................................+220°C Vapor Phase (60s).......................................................+215°CNote 1:Signals on IN_, NO_, NC_, or COM_ exceeding V+ or GND are clamped by internal diodes. Limit forward-diode current tomaximum current rating.Note 2:This device is constructed using a unique set of packaging techniques that impose a limit on the thermal profile the devicecan be exposed to during board level solder attach and rework. This limit permits only the use of the solder profiles recom-mended in the industry-standard specification, JEDEC 020A, paragraph 7.6, Table 3 for IR/VPR and Convection reflow. Pre-heating is required. Hand or wave soldering is not allowed.MAX4731/MAX4732/MAX473350ΩDual SPST Analog Switches in UCSP_______________________________________________________________________________________3ELECTRICAL CHARACTERISTICS —Single +3V Supply (continued)(V+ = +3V ±10%, V IH = +2.0V, V IL = +0.8V, T A = T MIN to T MAX , unless otherwise noted. Typical values are at V+ = +3V, T A = +25°C.)(Notes 3, 4)M A X 4731/M A X 4732/M A X 473350ΩDual SPST Analog Switches in UCSPELECTRICAL CHARACTERISTICS —Single +5V Supply(V+ = +5V ±10%, V IH = +2.0V, V IL = +0.8V, T A = T MIN to T MAX , unless otherwise noted. Typical values are at V+ = +5V, T A = +25°C.)MAX4731/MAX4732/MAX473350ΩDual SPST Analog Switches in UCSP_______________________________________________________________________________________5Note 3:The algebraic convention, where the most negative value is a minimum and the most positive value a maximum, is used in this data sheet.Note 4:UCSP parts are 100% tested at +25°C only, and guaranteed by design over temperature. µMAX parts are 100% tested at+85°C and +25°C and guaranteed by design over temperature.Note 5:∆R ON = R ON(MAX)- R ON(MIN).Note 6:UCSP on-resistance matching between channels and on-resistance flatness guaranteed by design.Note 7:Flatness is defined as the difference between the maximum and minimum value of on-resistance as measured over thespecified analog signal range.Note 8:Guaranteed by design.Note 9:Off-Isolation = 20 log 10(V NO_/V COM_), V NO_= output, V COM_= input to off switch.Note 10:Between any two switches.ELECTRICAL CHARACTERISTICS —Single +5V Supply(V+ = +5V ±10%, V IH = +2.0V, V IL = +0.8V, T A = T MIN to T MAX , unless otherwise noted. Typical values are at V+ = +5V, T A = +25°C.)(Notes 3, 4)M A X 4731/M A X 4732/M A X 473350ΩDual SPST Analog Switches in UCSP 6_______________________________________________________________________________________Typical Operating Characteristics(T A = +25°C, unless otherwise noted.)ON-RESISTANCE vs. V COMV COM (V)R O N (Ω)864210203040500010ON-RESISTANCE vs. V COM (V+ = +2.5V)V COM (V)R O N (Ω)2.01.51.00.51015202530502.5ON-RESISTANCE vs. V COM (V+ = +3.0V)V COM (V)R O N (Ω)2.01.51.00.51015202530050 3.02.5ON-RESISTANCE vs. V COM(V+ = +5.0V)V COM (V)R O N (Ω)432148121620005ON/OFF-LEAKAGE CURRENTvs. TEMPERATURETEMPERATURE (°C)O N /O F F -L E A K A G E C U R R E N T (p A )604020-2011010010000-4080CHARGE INJECTION vs. V COMV COM (V)C H A R G E I N J E C T I O N (p C )432151015202530354045005SUPPLY CURRENT vs. TEMPERATURETEMPERATURE (°C)S U P P L Y C U R R E N T (n A )8060-20020400.51.01.52.02.53.03.54.00-40LOGIC THRESHOLD VOLTAGE vs. SUPPLY VOLTAGEV+ (V)L O G I C T H R E S H O L D V O L T A G E (V )108640.51.01.52.02.53.002TURN-ON/OFF TIME vs. SUPPLY VOLTAGEV+ (V)t O N /O F F (n s )864204060801001200210Applications InformationOperating Considerations forHigh-Voltage SupplyThe MAX4731/MAX4732/MAX4733 operate to +11V with some precautions. The absolute maximum rating for V+ is +12V (referenced to G ND). When operating near this region, bypass V+ with a minimum 0.1µF capacitor to ground as close to the IC as possible.Logic LevelsThe MAX4731/MAX4732/MAX4733 are TTL compatible when powered from a single +5V supply. When pow-ered from other supply voltages, the logic inputs shouldIN1 and IN2 should be driven low to 0V and high to 11V. With a +3.3V supply, IN1 and IN2 should be dri-ven low to 0V and high to 3.3V. Driving IN1 and IN2 rail-to-rail minimizes power consumption.Analog Signal LevelsAnalog signals that range over the entire supply volt-age (G ND to V+) pass with very little change in R ON (see Typical Operating Characteristics ). The bidirec-tional switches allow NO_, NC_, and COM_ connec-tions to be used as either inputs or outputs.MAX4731/MAX4732/MAX473350ΩDual SPST Analog Switches in UCSP_______________________________________________________________________________________7Pin DescriptionTypical Operating Characteristics (continued)(T A = +25°C, unless otherwise noted.)TURN-ON/OFF TIME vs. TEMPERATURETEMPERATURE (°C)t O N /O F F (n s )6040-202010203040506070800-4080FREQUENCY RESPONSEFREQUENCY (Hz)L O S S (d B )100M10M1M100k-100-80-60-40-200-12010k1GTOTAL HARMONIC DISTORTIONvs. FREQUENCYFREQUENCY (Hz)T H D (%)10k1k 1000.0010.010.110.000110100kM A X 4731/M A X 4732/M A X 4733Power-Supply Sequencing andOvervoltage ProtectionCAUTION: Do not exceed the absolute maximum ratings. Stresses beyond the listed ratings can cause permanent damage to the devices.Proper power-supply sequencing is recommended for all CMOS devices. Always apply V+ before applying analog signals, especially if the analog signal is not current limited. If this sequencing is not possible, and if the analog inputs are not current limited to <20mA, add a small-signal diode, D1, as shown in Figure 1. If the analog signal can dip below G ND, add D2. Adding protection diodes reduces the analog signal range to a diode drop (about 0.7V) below V+ (for D1), and to a diode drop above ground (for D2). Leakage is unaffect-ed by adding the diodes. On-resistance increases slightly at low supply voltages. Maximum supply volt-age (V+) must not exceed +11V.Adding protection diodes causes the logic thresholds to be shifted relative to the power-supply rails. The most significant shift occurs when using low supply voltages (+5V or less). With a +5V supply, TTL compatibility is not guaranteed when protection diodes are added.Driving IN1 and IN2 all the way to the supply rails (i.e.,to a diode drop higher than the V+ pin, or to a diode drop lower than the GND pin) is always acceptable.Protection diodes D1 and D2 also protect against some overvoltage situations. Using the circuit in Figure 1, no damage results if the supply voltage is below the absolute maximum rating (+12V) and if a fault voltage up to the absolute maximum rating (V+ + 0.3V) is applied to an analog signal terminal.UCSP Package ConsiderationFor general UCSP package information and PC layout considerations, please refer to the Maxim Application Note, “Wafer-Level Chip-Scale Packages.”UCSP ReliabilityThe chip-scale package (UCSP) represents a unique package that greatly reduces board space compared to other packages. UCSP reliability is integrally linked to the user ’s assembly methods, circuit board material,and usage environment. The user should closely review these areas when considering a UCSP. Performance through Operation Life Test and Moisture Resistance is equal to conventional package technology as the wafer-fabrication process primarily determines it.However, this form factor may not perform equally to a packaged product through traditional mechanical relia-bility tests.Mechanical stress performance is a greater considera-tion for a UCSP. UCSP solder joint contact integrity must be considered since the package is attached through direct solder contact to the user ’s PC board.Testing done to characterize the UCSP reliability perfor-mance shows that it is capable of performing reliably through environmental stresses. Results of environmen-tal stress test and additional usage data and recom-mendations are detailed in the UCSP application note,which can be found on Maxim ’s website at .50ΩDual SPST Analog Switches in UCSP 8_______________________________________________________________________________________Figure 1. Overvoltage Protection Using External Blocking DiodesTest Circuits/Timing DiagramsMAX4731/MAX4732/MAX473350ΩDual SPST Analog Switches in UCSP_______________________________________________________________________________________9Test Circuits/Timing Diagrams (continued)M A X 4731/M A X 4732/M A X 473350ΩDual SPST Analog Switches in UCSP 10______________________________________________________________________________________Figure 5. Off-Isolation/On-Channel BandwidthPin Configurations/Functional Diagrams/Truth Tables (continued)Chip InformationTRANSITOR COUNT: 68PROCESS: CMOSTest Circuits/Timing Diagrams (continued)MAX4731/MAX4732/MAX473350ΩDual SPST Analog Switches in UCSP______________________________________________________________________________________11Package Information(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information,go to /packages .)M A X 4731/M A X 4732/M A X 473350ΩDual SPST Analog Switches in UCSP Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.12____________________Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600©2002 Maxim Integrated ProductsPrinted USAis a registered trademark of Maxim Integrated Products.Package Information (continued)(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information,go to /packages .)。

承受内压的回转壳JB4732

• 半球形封头计算厚度

注意1 半球形封头的计算厚度可以按照7.4设 计计算。

0.5 pcRi KSm 0.25 pc

注意2

7-4

封头与圆筒的连接,当厚度不一样 时,过渡连接形式采用附录H。

南京工业大学

JB4732-1995

• 碟形封头计算厚度

当

Ri

0.002 且

pc

KSm

0.08时,按图7 — 1确定。

7-1

7-2

e为自然对数的底,e=2.71828……..

南京工业大学

JB4732-1995

• 内压与经向薄膜力F同时作用

当F为正值,且超过0.25pcDi时

0.5pcDi 2F δ 2KSm pc

7-3

当F为负值时,应按8.6校核圆筒的轴向稳定

南京工业大学

JB4732-1995

强度理论及其相应的强度条件

JB4732-1995

• 球壳: 对于球壳的主应力为:

1 2

PD 4t

利用上述的推导方式:

南京工业大学

JB4732-1995

• 内压与经向薄膜应力F同时作用: 3 -F 还是按照第三强度理论,可以推导出壁厚:

南京工业大学

JB4732-1995

锥壳

南京工业大学

JB4732-1995

第一强度理论——最大主应力理论

I 当

PD 1 适用于脆性材料 2t

第二强度理论——最大变形理论(未用) 第三强度理论——最大剪应力理论

III 当 1 - 3

PD 0 适用于塑性材料 2t

第四强度理论——能量理论(适用塑性材料)

IV 当

JB4730.2射线检测__在实际工作中的应用讲解

(2)、公称厚度、透照厚度与标准中相关规 定的对应关系(表5)

(3)、增感屏材料及前后增感屏厚度

射线检测一般应使用金属增感屏或不用增感屏。 增感屏的选用应符合下表的规定。

• ②(纵缝)双壁透照:同上。 • ③椭圆形封头拼接缝透照(纵缝单壁内透照):

三次周向曝光 N=L’eff /250+2L”eff/250

L’eff=2(0.42Di+0.47T) L”eff=0.19 Di+1.1T+H

说明:N—透照片数;T—母材厚度;H—直边高度

f1min=0.57Di , f1max=0.9Di f2min=0.17Di f2min=0.31Di +0.79T ,

3 对小径管圆形缺陷评定区按10mm×10mm

• 透照方式的选择:

1 、应根据工件特点和技术条件的要求选择适宜

的透照方式。在可以实施的情况下应选用单壁透照 方式,在单壁透照不能实施时才允许采用双壁透照 方式。 2 、在源在内单壁透照和源在外单壁透照之间选择时 ,尽可能多采用源在内单壁透照方式

3 、典型透照方式的b值如表3。

3.13缺陷评定区;在质量分级评定时,为评价缺陷 数量和密集程度而设置的一定尺寸区域。可以是 正方形或长方形。缺陷评定区应选在缺陷最严重 的部位。

1 理解;缺陷系指条形缺陷和圆形缺陷。

评定区尺寸选取只与母材的公称厚度有关,与技 术级别无关。

2 应用;按不同性质的缺陷和母材的公称厚度择 评定区,测量时评定区应与焊缝平行, (5.1.5.1)在圆形缺陷评定区内存在条形缺陷时 要综合评级

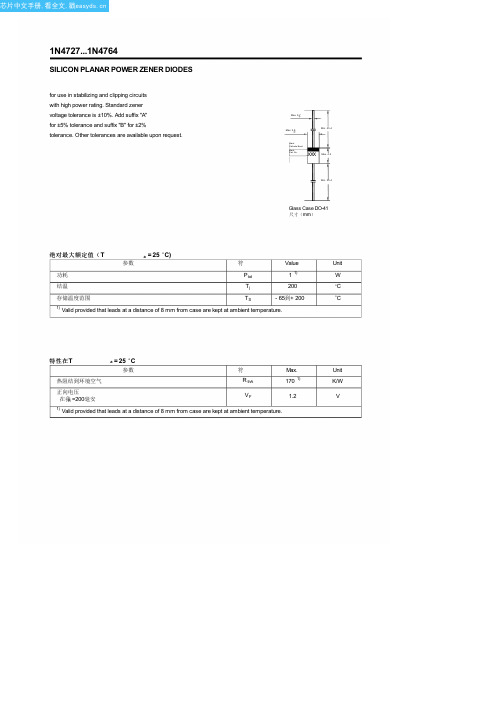

元件型号1N4732(Daya Electric)中文数据手册「EasyDatasheet」

Max. 0.7

Max. 2.8

Min. 25.4

B lac k Cathode Band

B lac k Part No.

XXX

Max. 4.2

Min. 25.4

Glass Case DO-41 尺寸(mm)

绝对最大额定值(T

a = 25 O C)

参数

符

Value

Unit

功耗

P tot

1 1)

W

结温

22

750

0.25

5

15.2

225

1N4748

22

11.5

23

750

0.25

5

16.7

205

1N4749

24

10.5

25

750

0.25

5

18.2

190

1N4750

27

9.5

35

750

0.25

5

20.6

170

1N4751

30

8.5

40

1000

0.25

5

22.8

150

1N4752

33

7.5

45

1000

0.25

700

1

10

3

730

1N4736

6.8

37

3.5

700

1

10

4

660

1N4737

7.5

34

4

700

0.5

10

5

605

1N4738

8.2

31

4.5

700

0.5

10

6

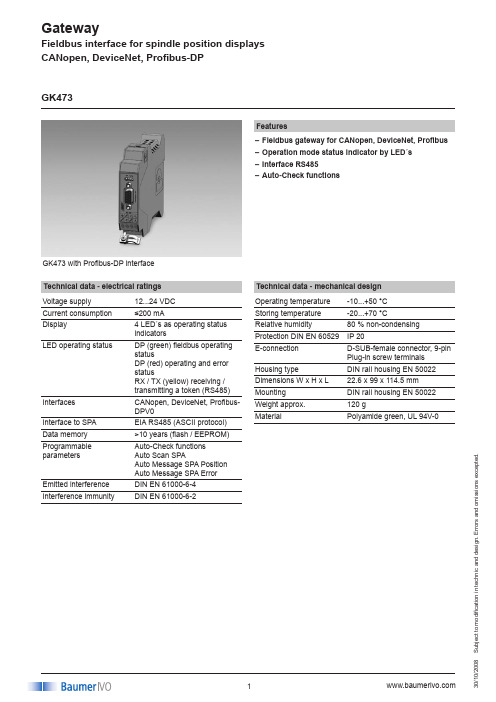

GK473.0073PD2中文资料

S u b j e c t t o m o d i fi c a t i o n i n t e c h n i c a n d d e s i g n . E r r o r s a n d o m i s s i o n s e x c e p t e d .008GK473 with Profibus-DP interface FeaturesFieldbus gateway for CANopen, DeviceNet, Profibus –Operation mode status indicator by LED´s –Interface RS485 –Auto-Check functions–Technical data - electrical ratings Voltage supply 12...24 VDC Current consumption ≤200 mADisplay4 LED´s as operating status indicatorsLED operating statusDP (green) fieldbus operating statusDP (red) operating and error statusRX / TX (yellow) receiving / transmitting a token (RS485)Interfaces CANopen, DeviceNet, Profibus-DPV0Interface to SPA EIA RS485 (ASCII protocol)Data memory >10 years (flash / EEPROM)Programmable parametersAuto-Check functions Auto Scan SPAAuto Message SPA Position Auto Message SPA Error Emitted interference DIN EN 61000-6-4Interference immunityDIN EN 61000-6-2GK473Technical data - mechanical design Operating temperature -10...+50 °C Storing temperature -20...+70 °CRelative humidity 80 % non-condensing Protection DIN EN 60529IP 20E-connection D-SUB-female connector, 9-pin Plug-in screw terminals Housing type DIN rail housing EN 50022Dimensions W x H x L 22.6 x 99 x 114.5 mm Mounting DIN rail housing EN 50022Weight approx.120 gMaterialPolyamide green, UL 94V-0S u b j e c t t o m o d i fi c a t i o n i n t e c h n i c a n d d e s i g n . E r r o r s a n d o m i s s i o n s e x c e p t e d .008GK473Part number GK473.007PDFirmware2Without data carrier3Including data carrier(describing file GSD/EDS/Profibus function modules and manual)Fieldbus connection D With connector D-SUBFieldbus interface 3Profibus-DP 5CANopen 8DeviceNetInterface to SPA7RS485Auto Scan SPAIf this function is activated, during operation the gateway will proceed a continous AutoScan of all SPAs connected checking whether they are “in position”. This information can be collected by special command for fieldbus readin upon request. AutoScan spares the fieldbus master of cyclic scanning every SPA himself.Auto Message SPA PositionIf this function is activated, in the following events thegateway will automatically provide a message without prior request by the fieldbus master: After all SPAs having previ-ously been “in position” this is no longer valid for at least one SPA. The message will also be given if previously at least one SPA was not “in position” and now all SPAs are “in position” again.Auto Message SPA ErrorIf this function is activated, in the following events thegateway will automatically provide a message without prior request by the fieldbus master. After all SPAs having been previously in status “no error” (“in position” or “not in posi-tion”) now at least one SPA is in “error” status. After previ-ously at least one SPA having been in “error” status, now all SPAs are again “in position” or “not in position”.Auto-Check functionsGK473 gateway (interface converter) enables networking of approx. 32 spindle position displays (SPA) of the Baumer IVO multicon system (for example N 140, N 141, N 150 and a fieldbus-capable control (PLC). The gateway is converting the SPA’s RS485 interface into a fieldbus interface and vice-versa. Four LEDs serve as status indicators. The gateway is capable of Auto-Check functions what means a relief to the control.One bus segment allows operation of several gateways for connecting more SPAs. The gateway provides a small hous-ing for DIN rail mounting, Node-ID and bus termination can be parameterized.DescriptionS u b j e c t t o m o d i fi c a t i o n i n t e c h n i c a n d d e s i g n . E r r o r s a n d o m i s s i o n s e x c e p t e d .008GK473RS485The serial interface is conform to EIA RS485. Max. 32 multicon spindle positioning displays can be networked in any combination to RS485 bus.CANopenThe CANopen interface is in line with CAN-Bus standard ISO / DIS 11898 CAN 2.0B. Optional data transmission rates are 10 k, 20 k, 50 k, 100 k, 125 k, 250 k and 500 kBaud. The baudrate is DIP-switch settable, the user address is set by two turnable switches. The supported CANopen- communication profile is DS 301. Since there is no CANopen application profile available for this kind of gateway it is manufacturer-specific. CANopen connection is by integrated 9-pin D-SUB-connector (female). Any CAN bus loops required can be effected in the connector itself (not included in the delivery).DeviceNetDeviceNet is based on CAN Bus (Layer 2), in line with CAN-Bus standards ISO / DIS 11898 CAN 2.0B. Optionaltransmission rates of 125 kBit/s, 250 kBit/s and 500 kBit/s. The baudrate is set by DIP switch. The user address (MAC ID, 0..63) is set by help of two rotary switches. Since there Is no existing standard DeviceNet profile for this kind ofgateway it is manufacturer-specific. DeviceNet connection is by integrated 9-pin D-SUB connector (female). Any CAN bus loops required can be realized in the connector itself (not included in the delivery).ProfibusThe Profibus-DP interface is in line with Profibus standard DP-V0 (cyclic communication) according to DIN EN 50170. Optional data transmission rates are 9600, 19200, 93,75 k, 187,5 k, 500 k, 1.5 M, 3 M, 6 M and 12 MBaud. The baud rate applied is automatically recognised. Since there is no standard gateway profile available it is manufacturer-specific. Profibus-DP connection is by integrated 9-pin D-SUB connector (female). Any Profibus loops required can be realized in the connector itself (not included in the delivery).Terminal significanceConnection RS485 (plug in screw terminal)Connector Assignment Pin 1 Shield Pin 2 GND (signal)Pin 3 Data line+Pin 4 Data line-Pin 5 GND B Pin 6 UB Pin 7 GND B Pin 8UBConnection CANopen (D-SUB)Connector Assignment Pin 1 Shield / groundPin 2 CAN-Bus signal (dominant low)Pin 3 –Pin 4 –Pin 5 –Pin 6 –Pin 7 CAN-Bus signal (dominant high)Pin 8 –Pin 9–Connection DeviceNet (D-SUB)Connector Assignment Pin 1 –Pin 2 CAN-Bus signal (dominant low)Pin 3 –Pin 4 –Pin 5 –Pin 6 –Pin 7 CAN-Bus signal (dominant high)Pin 8 DRAIN Pin 9–Connection Profibus (D-SUB)Connector Assignment Pin 1 Shield / ground Pin 2 –Pin 3 Profibus B (+)Pin 4 –Pin 5 –Pin 6 –Pin 7 –Pin 8 Profibus A (-)Pin 9–Terminal assignmentS u b j e c t t o m o d i fi c a t i o n i n t e c h n i c a n d d e s i g n . E r r o r s a n d o m i s s i o n s e x c e p t e d .008GK473DimensionsProfibus function moduleFunction modules are capable of taking over basic functions in the communication between PLC and Profibus gateway what means a considerable relief to the S7 operator.Step7® provides convenient implementation of the Baumer IVO multicon project. The function modules written into AWL sub-software (FC’s) are availabe as pure text files and additionally as complete Step7® example project. This allows convenient individual modifications. The functions comprise reading and writing of current and target values into the spindle position displays (SPA), profile administrati -on and storage in the PLC, automatic address designation for the SPAs connected as well as bit parameter administra-tion. Other integrated functions enable optimized evaluation of automatic gateway scanning functions. The function modules are intended for a Siemens® S7 300DP® and available in AWL, however it can be taken for granted that by slight modifications they can be easily implemented into other AWL-capable PLCs by Siemens.Function modules。

ZS4732A中文资料(PACELEADER INDUSTRIAL)中文数据手册「EasyDatasheet - 矽搜」

0C

+125

0C

1

芯片中文手册,看全文,戳

ZS4728A直通ZS4755A

表面贴装齐纳类型

电气特性

型号

ZS4728A ZS4729A ZS4730A ZS4731A ZS4732A ZS4733A ZS4734A ZS4735A ZS4736A ZS4737A ZS4738A ZS4739A ZS4740A ZS4741A ZS4742A ZS4743A ZS4744A ZS4745A ZS4746A ZS4747A ZS4748A ZS4749A ZS4750A ZS4751A ZS4752A ZS4753A ZS4754A ZS4755A 齐纳电压注5%容差

VR

A

Volts

150

1

100

1

100

1

50

1

10

1

10

1

10

2

10

3

10

4

10

5

10

6

10

7

10

7.6

5

8.4

5

9.1

5

9.9

5

Байду номын сангаас

11.4

5

12.2

5

13.7

5

15.2

5

16.7

5

18.2

5

20.6

5

22.8

5

25.1

5

27.4

5

29.7

5

32.7

浪涌电流

Isurge mA 1380 1260 1190 1070 970 890 810 730 660 605 550 500 454 414 380 344 304 285 250 225 205 190 170 150 135 125 115 105

JB4732-1995

-40

09MnNiD

调质

≤300

-70

④第1号修改单表6-2

07MnCrMoVR钢板:“钢板标准”一栏中列入“GB19189”,“注”一栏中取消“1)”。

07MnNiCrMoVDR钢板:钢号改为“07MnNiCrMoVDR”,“钢板标准”一栏中列入“GB19189”,“注”一栏中取消“1)”

⑤第1号修改单附录F

①第2章引用标准

增加GB19189《压力容器用调质高强度钢板》。

②表6-6

取消16MnMoD钢锻件一栏。

③表6-7

改用新表6-7。

新表6-7

钢号

热处理状态

公称厚度,mm

最低冲击试验温度,℃

16MnD

调质

≤300

-40

20MnMoD

调质

≤300

-40

>300~700

-30

08MnNiCrMoVD

调质

≤300

jb47321995钢制压力容器分析设计标准第2号修改单本修改单经中华人民共和国国家发展和改革委员会于2005年7月26日批准以2005年第46号公告公布自200《钢制压力容器-分析设计标准》

第2号修改单

本修改单经中华人民共和国国家发展和改革委员会于2005年7月26日批准,以2005年第46号公告公布,自2005年10月1日起实施。

JB4732钢制压力容器分析设计应力分类过程简介

应力强度限制 :

(1)一次总体薄膜应力强度S1

限制条件:S1≤KSm

K----载荷组合系数, K=1.0~1.25

(2)一次局部薄膜应力强度SⅡ

限制条件:SⅡ ≤1.5KSm

(3)一次薄膜(总体或局部)加一次弯曲应力强度SⅢ

限制条件:S Ⅲ ≤1.5KSm

(4)一次加二次应力强度SⅣ 限制条件:S Ⅳ ≤3Sm

在结构不连续区产生的薄膜应力

(二)二次应力 Q

——相邻部件的约束或结构的自身约束所引起 的正应力或切应力 基本特征:自限性

① 总体结构不连续处的弯曲应力 ② 总体热应力

(三)峰值应力 F

——由局部结构不连续和局部热应力的影响而叠 加到一次加二次应力之上的应力增量

应力强度计算 :

应力强度: 该点最大主应力与最小主应力之差 五类基本的应力强度:

校核线 0-0 :

校核线0-0通过筒体最大应力处,方向沿壁厚方向,远 离结构不连续处。

圆筒壳体薄膜应力理论解: Pm=PR/S =146.7MPa 与有限元结果相对误差为2.7% 球壳薄膜应力理论解: Pm=PR/2S =122.1MPa 与有限元结果相对误差为0.2%

路径 0-0 MEMBRANE 150.6 Pm=SⅡ ≤KSm MEM+BEND 157.8 Pm+Pb+Q=SⅣ ≤3Sm TOTAL 157.9 PL+Pb +Q+F=SⅤ ≤Sa

[7]陈小辉.基于有限元法压力容器分析设计方法的评议. 硕士论文,2010.

(5)峰值应力强度SⅤ 限制条件:S Ⅴ ≤Sa

Sa----由疲劳设计曲线得到的应力幅

二、应力分类法具体操作

应力分类的原则与实施:

4732标准释义

4732标准释义

4732标准全称为JB4732-1995《钢制压力容器—分析设计标准》,是中华人民共和国原机械工业部发布的行业标准。

该标准规定了钢制压力容器的设计、制造、检验、验收、操作、维修和报废等方面的内容,以确保其安全可靠运行。

JB4732标准与GB/T 150一起作为压力容器的设计标准并同时实施,但两者在某些方面存在差异。

例如,JB4732允许采用较高的设计应力强度,这意味着在相同设计条件下,容器的厚度可以减薄,重量可以减轻。

然而,由于设计计算工作量大、选材、制造、检验及验收等方面的要求较严,综合经济效益不一定高,一般推荐用于重量大、结构复杂、操作参数较高和超出GB/T150适用范围的压力容器设计。

jb4732 失效准则

jb4732 失效准则

jb4732失效准则是指用于判断某一产品或设备是否失效的标准和方法。

这些标准和方法通常基于科学和工程原理,考虑到产品的设计、使用环境和维护历史。

失效准则的制定旨在提高产品的安全性、可靠性和性能,并在必要时采取措施预防或修复可能的失效。

常见的jb4732失效准则包括:

1.寿命期失效准则:根据产品使用的寿命期来判断其是否失效。

这种准则对于一些易磨损或易老化的产品有很好的适用性。

2.功能失效准则:根据产品是否能够正常实现其设计功能来判断其是否失效。

这种准则适用于大多数产品,特别是那些功能复杂、由多个部件组成的产品。

3.安全失效准则:根据产品是否存在安全隐患来判断其是否失效。

这种准则适用于那些可能导致人员伤害或财产损失的产品。

4.可靠性失效准则:根据产品在使用中是否频繁发生故障来判断其是否失效。

这种准则适用于需要高度可靠性的产品,如航空、医疗等领域。

总之,jb4732失效准则是对产品失效的一种预判和判断方法,能够帮助生产厂家和使用者更好地掌握产品的质量和使用情况,从而采取必要的维修或更换措施,保证产品的正常使用和安全性。

- 1 -。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

83

元器件交易网

Control Devices

LIMITER DIODES

TYPICAL LIMITER PERFORMANCE RATINGS: TA = 25°C

MODEL NUMBER

GC4701 GC4702 GC4711 GC4712 GC4713 GC4721 GC4722 GC4723 GC4731 GC4732 GC4741 GC4742

DC BLOCK

INPUT

DC

RETURN

λ

4

DC BLOCK

COARSE (HIGH POWER) LIMITER DIODE

CLEAN UP

(FAST)

OUTPUT

LIMITER

DIODE

BASIC TWO-DIODE LIMITER

APPLICATIONS

A diode limiter is a power-sensitive variable attenuator that uses the non-linear properties of the diode to provide an impedance mismatch when sufficient amounts of RF power are incident on the device. The output power is reduced to a level that will not overdrive a receiver, burn out a mixer, etc. For varying input power levels in excess of the diode’s threshold level, the limiter’s output power tends to remain constant.

A passive limiter is one in which the limiter diodes are “turned on” by the RF signal itself. An active limiter is one in which the limiter diodes are “turned on” primarily by an external bias current typically supplied by a Schottky detector diode which senses the incident signal.

45

0.50

0.30

GC4713

45

0.70

0.50

GC4721

120

0.20

0.15

GC4722

120

0.60

0.30

GC4723

120

0.80

0.50

GC4731

15

0.12

0.10

GC4732

15

0.20

0.15

GC4741

30

0.12

0.10

GC4742

30

0.20

0.15

1) Pulse length 1 microsecond. 2) As measure in style 30 package.

FREQUENCY (GHz)

SEMICONDUCTOR OPERATION

75 Technology Drive Lowell, MA 01851 Tel: 978-442-5600 Fax: 978-937-3748

84

元器件交易网

Control Devices

LIMITER DIODES

DESCRIPTION

The GC4700 series diodes are specially processed PIN diodes designed for use in passive or active limiters at frequencies through Ku band.

POWER OUT (mw) LEAKAGE POWER ABOVE 1.0GHz (dB)

TYPICAL PERFORMANCE

10,000

+1000

+100 THRESHOLD

+10

GC4721 0dB 10dB 20dB 30dB

GC4701, 4741

+1.0

+10 +20 +30 +40 +50 +60 PEAK POWER INPUT (dBm)

MAXIMUM PEAK PIN

@1.µS (dBm)

+50 +53 +53 +56 +59 +60 +63 +66 +47 +50 +47 +50

TYPICAL

LEAKAGE

Pout (dBm)

+22 +24 +27 +29 +31 +39 +41 +44 +19 +22 +24 +27

TYPICAL THRESHOLD

TYPICAL RS

@10 mA (Ohms)

1.5 1.2 1.5 1.2 1.0 1.5 1.0 0.5 2.0 1.5 2.0 1.5

TYPICAL TL

(nS)

5 10 10 15 20 50 50 100 5 5 7 7

TYPICAL

θP1

(°C/W)

20 12 15 10 6 1.2 0.5 0.3 30 20 20 15

CHIP ELECTRICAL PARAMETERS: TA = 25°C

MODEL NUMBER

VB MIN (VOLTS)

IR = 10µA

CJO TYP (pF)

CJ6 MAX (pF)

GC4701

20

0.20

0.15

GC4702

20

0.50

0.30

GC4711

45

0.20

0.15

GC4712

Limiter diodes may be used in wave guides, coax, microstrip, stripline or other media. Single or cascaded devices may be used, depending on power levels.

Notes: 1. Available in standard case styles 30, 35, 42 AND 45. When ordering specify the desired case style by adding its number as a suffix to the

basic part number. Some other case styles are available on request.

MAXIMUM 2

THERMAL RESISTANCE

(°C/W)

100 80 80 60 40 40 20 15 120 80 100 70

SEMICONDUCTOR OPERATION

75 Technology Drive Lowell, MA 01851 Tel: 978-442-5600 Fax: 978-937-3748

Twelve categories of devices are offered for flexibility in design of low (lower Vb, fastest turn-on time), medium and high (highest Vb, slowest turn-on time) power limiters.

RATINGS

Maximum Leakage Current:

Operating Temperature:

0.5µA at 80% of minimum rated breakdown

55°C to +150°C

+9 +8

+7

+6 GC4721

+5

+4

+3

+2

+1

GC4701, 4741

0

2

4

6

8

10 12 14 16 18

(dBm)

+10 +10 +15 +15 +15 +20 +20 +20 +7 +7 +12 +12

TYPICAL INSERTION LOSS

(dB)

0.1 0.2 0.1 0.2 0.2 0.1 0.2 0.2 0.1 0.1 0.1 0.1

MAXIMUM

CW

POWER

(Watts)

2 3 3 4 5 5 10 15 2 3 3 4