MIPS指令系统和MIPS体系结构

mips指令集指的是什么

mips指令集指的是什么MIPS是高效精简指令集计算机(RISC)体系结构中最优雅的一种;即使连MIPS的竞争对手也这样认为,这可以从MIPS对于后来研制的新型体系结构比如DEC的Alpha和HP的Precision产生的强烈影响看出来。

虽然自身的优雅设计并不能保证在充满竞争的市场上长盛不衰,但是MIPS微处理器却经常能在处理器的每个技术发展阶段保持速度最快的同时保持设计的简洁。

MIPS与MIPS指令集指令集是存储在CPU内部,对CPU运算进行指导和优化的硬程序。

拥有这些指令集,CPU就可以更高效地运行。

MIPS指令集属于精简指令集,MIPS 的所有指令都是32位,指令格式简单,而X86的指令长度不是固定的。

简单的指令和格式易于译码和流水线操作,但是代码密度不高,导致二进制文件大。

低端的CPU物理面积只有1.5平方毫米(在SOC系统里面肉眼很难找到)。

而高端的R10000处理器,第一次投放市场时可能是世界上最快的CPU,它的物理面积几乎有1平方英寸,发热近30瓦特。

虽然MIPS看起来没什么优势,但是足够的销售量使其能健康发展:1997年面市的44M的MIPS CPU,绝大多数使用于嵌入式应用领域。

MIPS(Million InstrucTIons Per Second):单字长定点指令平均执行速度Million InstrucTIons Per Second的缩写,每秒处理的百万级的机器语言指令数。

这是衡量CPU速度的一个指标。

像是一个Intel80386 电脑可以每秒处理3百万到5百万机器语言指令,即我们可以说80386是3到5MIPS的CPU。

MIPS只是衡量CPU性能的指标。

MIPS是世界上很流行的一种RISC处理器。

MIPS的意思无内部互锁流水级的微处理器(Microprocessor without interlocked piped stages),其机制是尽量利用软件办法避免流水线中的数据相关问题。

mips指令集(24条指令)的字段和功能描述

MIPS指令集(24条指令)的字段和功能描述指令集概述M I PS(M ic ro pr oc es s or wi th ou tI nt erl o ck ed Pi pe li ne dSt a ge s)指令集是一种精简指令集(R IS C)体系结构,广泛应用于计算机体系结构的教学和实践中。

本文将介绍M IP S指令集中的24条常用指令,并对它们的字段和功能进行详细描述。

加载和存储指令1.l w指令字段描述:-指令格式:lw$r t,o f fs et($rs)-r s(源寄存器):指定存储单元的基址寄存器-r t(目标寄存器):指定目标寄存器,用于存储从存储单元中加载的数据-o ff se t:用于指定存储单元的偏移量,计算出实际地址功能描述:l w指令用于从存储单元中加载数据到目标寄存器。

它通过基址寄存器和偏移量计算出实际地址,并将存储单元中的数据加载到目标寄存器中。

2.s w指令字段描述:-指令格式:sw$r t,o f fs et($rs)-r s(源寄存器):指定存储单元的基址寄存器-r t(目标寄存器):指定源寄存器,用于存储到存储单元中的数据-o ff se t:用于指定存储单元的偏移量,计算出实际地址功能描述:s w指令用于将源寄存器中的数据存储到指定的存储单元中。

它通过基址寄存器和偏移量计算出实际地址,并将源寄存器中的数据存储到该地址对应的存储单元中。

算术和逻辑指令3.a d d指令字段描述:-指令格式:ad d$rd,$rs,$rt-r s(源寄存器1):参与运算的第一个源寄存器-r t(源寄存器2):参与运算的第二个源寄存器-r d(目标寄存器):用于存储运算结果功能描述:a d d指令用于将两个源寄存器中的数据相加,并将结果存储到目标寄存器中。

4.s u b指令字段描述:-指令格式:su b$rd,$rs,$rt-r s(源寄存器1):参与运算的第一个源寄存器-r t(源寄存器2):参与运算的第二个源寄存器-r d(目标寄存器):用于存储运算结果功能描述:s u b指令用于将源寄存器2中的数据从源寄存器1中的数据减去,并将结果存储到目标寄存器中。

计算机组成原理 MIPS

k

c j

字对齐方式下的存储器访问

速度较高 接口较简单

CPU

寄存器 Byte3

Byte2

Byte1

Byte0

2020/11/20

Byte3 Byte2 Byte1 Byte0 存储器

字不对齐方式下的存储器访问

节省空间 访存速度慢 接口复杂

CPU

寄存器 Byte3 Byte2 Byte1 Byte0

操作码 地址码 1 地址码 2 地址码 3

例1 设某台计算机有100条指令, (1) 采用固定长度操作码编码,试设计其操作码的编码。 (2) 假如这100条指令中有10条指令的使用概率达到90%,其余 90条指令的使用概率为10%。试采用不等长编码设计操作码。

解:

(1) 采用固定长度操作码编码时,需要7位操作码。 取其中的100个代码作为指令操作码,可以用 0000000到1100011之间的代码代表100条指令,即

2020/11/20

访存次数问题

– Char c; – Short int i,j; – int k;

int i Int k

Char c Short j Int k

字对齐方式下的数据存储

2020/11/20

空间浪费问题

– Char c; – Short int i,j; – int k;

零地址指令

操作码

地址码

1111 1100 0000 0000~1111 1100 0000

指令的格式

R1

ADD load

2020/11/20

三、指令长度

固定长度

– 取指快、译码简单。 – 单字长、双字长、多字长

可变长度

– 可提高编码效率 四、指令助记符

MIPS

作者点评:MIPS技术公司则是一家设计制造高性能、高档次及嵌入式32位和64位处理器的厂商。在通用方面,MIPS R系列微处理器用于构建SGI的高性能工作站、服务器和超级计算机系统。在嵌入式方面,MIPS K系列微处理器是目前仅次于ARM的用得最多的处理器之一(1999年以前MIPS是世界上用得最多的处理器),其应用领域覆盖游戏机、路由器、激光打印机、掌上电脑等各个方面。

MIPS的系统结构及设计理念比较先进,其指令系统经过通用处理器指令体系MIPS I、MIPS II、MIPS III、MIPS IV到MIPS V,嵌入式指令体系MIPS16、MIPS32到MIPS64的发展已经十分成熟。在设计理念上MIPS强调软硬件协同提高性能,同时简化硬件设计。

中国龙芯2和前代产品采用的都是64位MIPS指令架构,它与大家平常所知道的X86指令架构互不兼容,MIPS指令架构由MIPS公司所创,属于RISC体系。过去,MIPS架构的产品多见于工作站领域,索尼PS2游戏机所用的“Emotion Engine”也采用MIPS指令,这些MIPS处理器的性能都非常强劲,而龙芯2也属于这个阵营,在软件方面与上述产品完全兼容。

MIPS公司设计RISC处理器始于二十世纪八十年代初,1986年推出R2000处理器,1988年推R3000处理器,1991年推出第一款64位商用微处器R4000。之后又陆续推出R8000(于1994年)、R10000(于1996年)和R12000(于1997年)等型号。

MIPS 指令系统和汇编语言

其中 A1 为目的操作数地址,A2 为源操作数地址。 指令的含义:(A1)OP(A2)→A1。 (3)一地址指令 一地址指令顾名思义只有一个显地址,它的指令格式为: OP A1

一地址指令只有一个地址, 那么另一个操作数来自何方呢?指令中虽未明显给出,但按事 先约定,这个隐含的操作数就放在一个专门的寄存器中。因为这个寄存器在连续性运算时,保 存着多条指令连续操作的累计结果,故称为累加寄存器(AC) 。 指令的含义:(AC)OP(A1)→AC (4)零地址指令 零地址指令格式中只有操作码字段,没有地址码字段,其格式为: OP 零地址的运算类指令仅用在堆栈计算机中的。 堆栈计算机没有一般计算机中必备的通用寄 存器,因此堆栈就成为提供操作数和保存运算结果的唯一场所。通常,参加运算的两个操作数 隐含地从堆栈顶部(栈顶和次栈顶单元)弹出,送到运算器中进行运算,运算的结果再隐含地 压入堆栈中。对于同一个问题,用三地址指令编写的程序最短,但指令长度(程序存储量)最 长;而用二、一、零地址指令来编写程序,程序的长度一个比一个长,但指令的长度一个比一 个短。

作码结构等,是一个很复杂的问题,它与计算机系统结构、数据表示方法、指令功能设计等都 密切相关。

指令的基本格式

一条指令就是机器语言的一个语句, 它是一组有意义的二进制代码, 指令的基本格式如下: 操作码字段 地址码字段

其中操作码指明了指令的操作性质及功能,地址码则给出了操作数的地址。 指令的长度是指一条指令中所包含的二进制代码的位数, 指令长度与机器字长没有固定的 关系,它可以等于机器字长,也可以大于或小于机器字长。通常,把指令长度等于机器字长的 指令称为单字长指令; 指令长度等于半个机器字长的指令称为半字长指令;指令长度等于两个 机器字长的指令称为双字长指令。 在一个指令系统中,若所有指令的长度都是相等的,称为定长指令字结构。定长结构指令 系统控制简单,但不够灵活。若各种指令的长度随指令功能而异,就称为变长指令字结构。现 代计算机广泛采用变长指令字结构,变长结构指令系统灵活,但指令的控制较复杂。 计算机执行一条指令所需要的全部信息都必须包含在指令中。 对于一般的双操作数运算类 指令来说,除去操作码之外,地址码字段中应包含以下信息: 第一操作数地址。 第二操作数地址。 操作结果存放地址。 这些信息可以在指令中明显的给出,称为显地址;也可以依照某种事先的约定,用隐含的 方式给出,称为隐地址。所以,从地址结构的角度可以分为三地址指令、二地址指令、一地址 指令和零地址指令。 (1)三地址指令 三地址指令格式为: OP A1 A2 A3

实验三MIPS指令系统和MIPS体系结构

实验3 MIPS指令系统和MIPS体系结构一.实验目的(1)了解和熟悉指令级模拟器(2)熟悉掌握MIPSsim模拟器的操作和使用方法(3)熟悉MIPS指令系统及其特点,加深对MIPS指令操作语义的理解(4)熟悉MIPS体系结构二. 实验内容和步骤首先要阅读MIPSsim模拟器的使用方法,然后了解MIPSsim的指令系统。

(1)、启动MIPSsim。

(2)、选择“配置”->“流水方式”选项,使模拟器工作在非流水方式。

(3)、参照使用说明,熟悉MIPSsim模拟器的操作和使用方法。

(4)、选择“文件”->“载入程序”选项,加载样例程序 alltest.asm,然后查看“代码”窗口,查看程序所在的位置。

(5)、查看“寄存器”窗口PC寄存器的值:[PC]=0X00000000 。

(6)、执行load和store指令,步骤如下:1)单步执行一条指令(F7)。

2)下一条指令地址为OX00000004 ,是一条有(有,无)符号载入 (字节,半字,字)指令。

3)单步执行一条指令(F7)。

4)查看R1的值,[R1]= 0xFFFFFFFFFFFFFF80 。

5)下一条指令地址为 OX000000008 ,是一条有 (有,无)符号载入(字节,半字,字)指令。

6)单步执行1条指令。

7)查看R1的值,[R1]=0x0。

8)下一条指令地址为 0x0000000c ,是一条无(有,无)符号载入(字节,半字,字)指令。

9)单步执行1条指令。

10)查看R1的值,[R1]=0x0 。

11)单步执行1条指令。

12)下一条指令地址为0x00000014 ,是一条保存字节(字节,半字,字)指令。

13)单步执行一条指令。

14)查看内存BUFFER处字的值,值为0x00000080。

(7)、执行算术运算类指令。

步骤如下:1)双击“寄存器”窗口中的R1,将其值修改为2。

2)双击“寄存器”窗口中的R2,将其值修改为3。

3)单步执行一条指令。

MISP体系结构

MIPS 的基地址空间

MIPS 的基地址空间

kuseg:0x0000 0000到0x7FFF FFFF(2G大小)。这是用 户模式下可用的程序地址,要经过MMU(TLB)转换地址。 kseg0:0x8000 0000到0x9FFF FFFF(512MB)。其对应的 物理地址是0x0000 0000到0x1FFF FFFF。访问不需要通 过地址转换。无MMU时存放大多数的程序和数据,有 MMU时操作系统内核会存放于此。

MIPS 的寄存器

MIPS 的寄存器

用于保存异常处理函数的地址。 发生异常(中断)时, 这两个寄存器的值不会恢复。

用来存放子程序调用的返回地址。

MIPS 的寄存器

在MIPS 32/64位 CPU上,增加了浮点运算协处理器,同 时也增加了32个浮点寄存器,一般在汇编代码中成为$f0$f31。 在MIPS CPU中采用专用的整数乘除法部件。一般乘法要 用4-12个时钟周期,而除法要用20-80个,所以乘除部件 一般互锁,如果运算结束前就读取结果,会导致CPU等待 运算结束。而且,除运算时从来不检查除数是否为0。

MIPS 体系结构

Contents

1. MIPS 简介 2. MIPS 体系结构 3. MIPS 处理器控制 4. MIPS Cache 机制 5. MIPS 异常,中断和启动 6. MIPS 内存管理 & TLB

Contents

1. MIPS 简介 2. MIPS 体系结构 3. MIPS 处理器控制 4. MIPS Cache 机制 5. MIPS 异常,中断和启动 6. MIPS 内存管理 & TLB

执行后,t2的值为0xFFFF FFFE(-2),t3的值为 0x0000 00FE(254)。

04MIPS指令系统(1)_447408859

微机原理(计算机原理)第4讲MIPS指令系统(1)1MIPS体系结构概述数据处理指令数据传送指令分支与跳转指令MIPS指令格式第4讲MIPS指令系统(1)MIPS诞生于1980年代,是最早的RISC处理器之一,也是目前销量最好的RISC处理器之一,从游戏机到路由器,再到SGI的超级计算机,都可以看到MIPS CPU 的应用MIPS起源于Stanford大学John Hennessy教授的研究成果。

Hennessy于1984年在硅谷创立了MIPS公司()John L. Hennessy出版了两本著名的教科书:Computer Organization and Design : TheHardware/Software Interface(计算机组成与设计:硬件/软件接口)Computer Architecture : A QuantitativeApproach(计算机体系结构:量化方法)MIPS=Microprocessor without InterlockedPipeline Stages,无互锁流水级的微处理器MIPS的另一个含义是每秒百万条指令——Millions of instructions per secondMIPS体系结构的发展MIPS体系结构经历了以下几代MIPS I——该指令集用于最初的32位处理器,至今仍然很流行,R2000、R3000都是MIPS I的实现MIPS II——MIPS I的升级,最初为R6000定义,失败MIPS III——应用于R4000的64位指令集MIPS IV——MIPS III的升级,应用于R5000和R1000032个通用寄存器可供编程使用:$0~$31,其中$0无论写入什么永远返回0$31被子程序调用指令(“跳转与链接指令”)用来保存返回地址除此以外,所有寄存器都可以在任何指令中以相同方式使用——真正通用通用寄存器的习惯用法和命名寄存器编号助记符用法0zero永远为01at用做汇编器的临时变量2-3v0, v1用于过程调用时返回结果4-7a0-a3用于过程调用时传递参数8-15t0-t7临时寄存器。

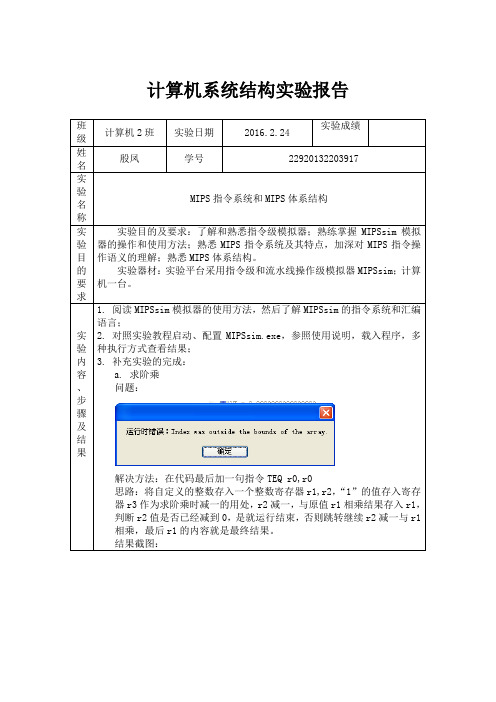

计算机系统结构实验一MIPS指令系统和MIPS体系结构

计算机系统结构实验报告班级计算机2班实验日期2016.2.24实验成绩姓名殷凤学号22920132203917实验名称MIPS指令系统和MIPS体系结构实验目的要求实验目的及要求:了解和熟悉指令级模拟器;熟练掌握MIPSsim模拟器的操作和使用方法;熟悉MIPS指令系统及其特点,加深对MIPS指令操作语义的理解;熟悉MIPS体系结构。

实验器材:实验平台采用指令级和流水线操作级模拟器MIPSsim;计算机一台。

实验内容、步骤及结果1. 阅读MIPSsim模拟器的使用方法,然后了解MIPSsim的指令系统和汇编语言;2. 对照实验教程启动、配置MIPSsim.exe,参照使用说明,载入程序,多种执行方式查看结果;3. 补充实验的完成:a.求阶乘问题:解决方法:在代码最后加一句指令TEQ r0,r0思路:将自定义的整数存入一个整数寄存器r1,r2,“1”的值存入寄存器r3作为求阶乘时减一的用处,r2减一,与原值r1相乘结果存入r1,判断r2值是否已经减到0,是就运行结束,否则跳转继续r2减一与r1相乘,最后r1的内容就是最终结果。

结果截图:b.ALU运算求(X-Y)*2-(X+Y)/8问题:无思路:题目要求不可以使用乘除指令,则利用逻辑左移(SLL)一位实现乘2,利用逻辑右移(SRL)3实现除以8。

r1 r2中存放自定义的x y,r3中存放x-y的值,r4存放x+y的值,最后结果放在r5中。

结果截图:c.求补码问题:解决方法:把高32位和低32位之间base的差值4个字节事先存进寄存器r6问题:解决方法:改成LABLE1问题:如果是正数的话结果总是错误的解决方法:刚开始忘记判断正负了,如果是正数就直接存回存储器原来的位置,判断正负通过高32位(存在r2中)和十六进制数0x00…0080000000(寄存器r9)进行AND,如果结果等于0(与$r0比较),就为正数,否则就是负数。

思路:r1中放取字指令LW的base值,根据内存中的数据来决定,存储器中高32位数据取出来放进r2,低32位数据放进r3。

MIPS微处理器原理-MIPS汇编语言

操作数:寄存器、存储器、常数

因常数的值可以立即访问,故又称为立即数(immediate)。

加立即数指令 ( addi ):

# $s0=a, $s1=b

addi $s0, $s1, 4 # a=b+4 addi $s1, $s0,-2 # b=a-2

没有NOT,可用下面代替 A NOR $0 = NOT A

Source Values $s1 0000 0000 0000 0000 0000 0000 1111 1111

andi rt、rs、imm

Assembly Code

imm 0000 0000 0000 0000 1111 1010 0011 0100

用途 常数0 汇编器临时变量 函数返回值 函数参数 临时变量 保存变量

名称 $t8 ~ $t9 $k0 ~$k1 $gp $sp $fp $ra

编号 24~25 26~27 28 29 30 31

用途

临时变量

操作系统临时变量

全局指针

栈指针

帧指针

保存变量

8

MIPS Register Set

Name $0 $at $v0-$v1 $a0-$a3 $t0-$t7 $s0-$s7 $t8-$t9 $k0-$k1 $gp $sp $fp $ra

4个准则: ① 简单设计有助于规整化; ② 加快常见功能; ③ 越小的设计越快; ④ 好的设计需要好的折中方法。

4

R I S C 指令集的特点

Reduced Instruction Set Computer Complex Instruction Set Computer

• 精简了指令系统,流水线以及常用指令均可用硬件执行;

MIPS构架

MIPS体系结构首先是一种RISC架构1 MIPS32架构中有32个通用寄存器,其中$0(无论你怎么设置,这个寄存器中保存的数据都是0)和$31(保存函数调用jal的返回地址)有着特殊的用途,其它的寄存器可作为通用寄存器用于任何一条指令中。

虽然硬件没有强制性的指定寄存器使用规则,在实际使用中,这些寄存器的用法都遵循一系列约定。

这些约定与硬件确实无关,但如果你想使用别人的代码,编译器和操作系统,你最好是遵循这些约定。

寄存器编号助记符用法0 zero永远返回值为0 1 at用做汇编器的暂时变量2-3 v0,v1子函数调用返回结果4-7 a0-a3子函数调用的参数8-15 t0-t7 24-25 t8-t9暂时变量,子函数使用时不需要保存与恢复16-25s0-s7子函数寄存器变量。

子函数必须保存和恢复使用过的变量在函数返回之前,从而调用函数知道这些寄存器的值没有变化。

26,27 k0,k1通常被中断或异常处理程序使用作为保存一些系统参数28 gp全局指针。

一些运行系统维护这个指针来更方便的存取“static”和“extern"变量。

29 sp堆栈指针30 s8/fp第9个寄存器变量。

子函数可以用来做桢指针31 ra 子函数的返回地2 MIPS32中如果有FPA(浮点协处理器),将会有32个浮点寄存器,按汇编语言的约定为$f0~$f31,MIPS32中只能实用偶数号的浮点寄存器,奇数号的用途是:在做双精度的浮点运算时,存放该奇数号之前的偶数号浮点寄存器的剩余无法放下的32位。

比如在做双精度的浮点运算时,$1存放$0的剩余的部分,所以在MIPS32中可以通过加载偶数号的浮点寄存器而把64位的双精度数据加载到两个浮点寄存器中,每个寄存器存放32位。

比如:l.d $02,24(t1)被扩充为两个连续的寄存器加载:lwc1 $f0,24(t1)lwc1 $f1,28(t1)3 MIPS架构中没有X86中的PC(程序计数)寄存器,它的程序计数器不是一个寄存器。

CPU架构讲解X86、ARM、RISC、MIPS

CPU架构讲解X86、ARM、RISC、MIPS一、当前CPU的主流架构:1.X86架构采用CISC指令集(复杂指令集计算机),程序的各条指令是按顺序串行执行的,每条指令中的各个操作也是按顺序串行执行的。

2.ARM架构是一个32位的精简指令集(RISC)架构。

3.RISC-V架构是基于精简指令集计算(RISC)原理建立的开放指令集架构。

4.MIPS架构是一种采取精简指令集(RISC)的处理器架构,可支持高级语言的优化执行。

CPU架构是CPU厂商给属于同一系列的CPU产品定的一个规范,是区分不同类型CPU的重要标示。

二、目前市面上的CPU分类主要分有两大阵营:1.intel、AMD为首的复杂指令集CPU;2.IBM、ARM为首的精简指令集CPU。

两个不同品牌的CPU,其产品的架构也不相同,例如,Intel、AMD的CPU是X86架构的,而IBM的CPU是PowerPC架构,ARM是ARM架构。

三、四大主流CPU架构详解(X86、ARM、RISC、MIPS)1.X86架构X86是微处理器执行的计算机语言指令集,指一个Intel通用计算机系列的标准编号缩写,也标识一套通用的计算机指令集合。

1978年6月8日,Intel 发布了新款16位微处理器8086,也同时开创了一个新时代:X86架构诞生了。

X86指令集是Intel为其第一块16位CPU(i8086)专门开发的,IBM 1981年推出的世界第一台PC机中的CPU–i8088(i8086简化版)使用的也是X86指令。

采用CISC(Complex Instruction Set Computer,复杂指令集计算机)架构。

与采用RISC不同的是,在CISC处理器中,程序的各条指令是按顺序串行执行的,每条指令中的各个操作也是按顺序串行执行的。

顺序执行的优点是控制简单,但计算机各部分的利用率不高,执行速度慢。

随着CPU技术的不断发展,Intel陆续研制出更新型的i80386、i80486直到今天的Pentium 4系列,但为了保证电脑能继续运行以往开发的各类应用程序以保护和继承丰富的软件资源,所以Intel所生产的所有CPU仍然继续使用X86指令集。

MIPS指令集及汇编

和R12000(1997年)等型号。 z 随后,MIPS公司把重点放在嵌入式系统。

{ 1999年发布MIPS32和MIPS64架构标准,集成了所有原 来MIPS指令集,并且增加了许多更强大的功能。陆续开发 了高性能、低功耗的32位处理器内核(core)MIPS324Kc 与高性能64位处理器内核MIPS64 5Kc。

{ 应用广泛的32位MIPS CPU包括R2000,R3000 其ISA都是MIPS I,另一个广泛使用的、含有许多 重要改进的64位MIPS CPU R4000及其后续产 品,其ISA版本为MIPS III

一、 MIPS简介

{ 1984年,MIPS计算机公司成立。1992年,SGI收购了 MIPS计算机公司。1998年,MIPS脱离SGI,成为MIPS 技术公司。

龙芯2E笔记本电脑运行 OpenOffice打开Word文档

ቤተ መጻሕፍቲ ባይዱ

二、MIPS体系结构

{ 指令集体系结构类型:寄存器——寄存器型

(1)寄存器的特点 (2)整数乘法单元和寄存器 (3)寻址方式 (4)存储器和寄存器中的数据类型 (5)流水线冒险

二、 MIPS体系结构——(1)寄存器

{ MIPS 包含32个通用寄存器

{ 2000年,MIPS公司发布了针对MIPS32 4Kc的版本以及 64位MIPS 64 20Kc处理器内核。

一、 MIPS简介

{ 基于龙芯2E处理器的千元的PC、1999元的笔记本电脑、 意法半导体3000万元购买龙芯2E 5年的生产和销售权, 国产操作系统内核在龙芯2E上测试成功。

MIPS教程

MIPS教程MIPS指令系统及MIPS汇编(基于MARS)汇编语⾔是使⽤符号格式表⽰指令,可直接⾯向机器内存以及寄存器的程序设计语⾔。

本部分主要学习内容包括:1、以MIPS指令系统为例,学习并掌握MIPS指令集及汇编语⾔,能够使⽤MIPS汇编语⾔编写顺序、分⽀、循环等具有特定功能的结构化程序,掌握函数调⽤及栈操作等汇编程序设计⽅法。

该部分内容请参考《数字设计和计算机体系结构》第6章2、熟练使⽤MARS⼯具软件,具备MARS调试汇编代码的能⼒,能使⽤MARS模拟CPU执⾏汇编指令,通过观察相应寄存器、存储等部件的变化情况,查看程序是否符合期望;能够使⽤MIPS汇编语⾔编写并⽣成MIPS CPU可执⾏的⼆进制机器指令,便于对后续实验中所设计的CPU进⾏功能测试。

具体请参考《MARS使⽤教程》MIPS体系结构的寄存器MIPS体系结构定义了32个寄存器通⽤寄存器标志由$符号开头,寄存器表⽰有两种⽅式直接使⽤该寄存器对应的编号,例如:从$0到$31使⽤对应的寄存器名称,例如:$t0,$t1,……, $sp等每个寄存器都有其特定的作⽤,有相应的规范,可参考《数字设计和计算机体系结构》第6章表6-1MIPS汇编语句MIPS汇编中⼀般有3类语句,通常是⼀个语句⼀⾏(1)可执⾏指令(instruction),是处理器⽣成在运⾏时执⾏的机器码,告诉处理器该做什么,⼀条可执⾏指令对应⼀条机器指令(2)伪指令(Extended (pseudo) instruction)和宏,简化编程⼈员的⼯作,由编译器编译成⼀条或多条可执⾏指令,常见的伪指令如move,la,li等(相应的伪指令在Mars中的Help中有解释)(3)汇编器指令(伪操作)(Directives),不会被编译器编译成可执⾏指令(或机器指令),会被翻译成预处理指令,⽤于指⽰编译器⼯作,⽤来定义段、分配内存变量等;汇编器指令不是指令集的⼀部分MIPS汇编语⾔指令格式: [ 标签:] 操作符 [ 操作数 ] [ #注释 ]标签:(可选),标记内存地址,必须跟冒号。

计算机系统结构实验报告-MIPS 指令系统和MIPS 体系结构

计算机系统结构实验报告实验名称:MIPS 指令系统和MIPS 体系结构专业年级:0xxxxxxx姓名:xxxxxx计算机系统结构实验报告班级xxxxxxxxxxx 实验日期xxxxxxxxxx 实验成绩姓名xxxxxxxx 学号230xxxxxxxxxx4实验名称Cache性能分析实验目的、要求及器材实验目的:1、加深对Cache的基本概念、基本组织结构以及基本工作原理的理解。

2、掌握Cache容量、相联度、块大小对Cache性能的影响3、掌握降低Cache不命中率的各种方法以及这些方法对提高Cache性能的好处。

4、理解LRU与随机法的基本思想以及它们对Cache性能的影响实验平台:采用Cache模拟器MyCache。

实验内容、步骤及结果首先要掌握 MaCache模拟器的使用方法。

1、Cache容量对不命中率的影响选择地址流文件,选择不同的Cache容量,执行模拟器,记录各种情况的不命中率。

表:地址流文件名: eg.din结论:Cache容量越大,不命中率越低.但增加到一定程度时命中率不变。

2、相联度对不命中率的影响表:64KB相联度 1 2 4 8 16 32 不命中率(%)0.89 0.53 0.47 0.45 0.44 0.44地址流文件: all.din图:64KB表:256KB相联度 1 2 4 8 16 32 不命中率(%)0.49 0.38 0.36 0.36 0.35 0.35地址流文件: all.din图:256KB结论:相联路数越多,则不命中率越低,同时,有个极限值,且该极限值随Cache容量大小的增加而减小。

3 Cache块大小对不命中率的影响块大小Cache容量2 8 32 128 51216 18.61 10.12 3.81 1.95 1.4232 14.22 7.59 2.84 1.26 0.8764 12.62 6.47 2.36 0.92 0.60128 12.98 6.35 2.31 0.76 0.47256 16.04 7.29 2.15 0.72 0.40地址流文件:ccl.din结论:不命中率随分块大小的增大先减小后增大,即存在一个最优的分块大小,且该最优分块随Cache容量的增大而增大。

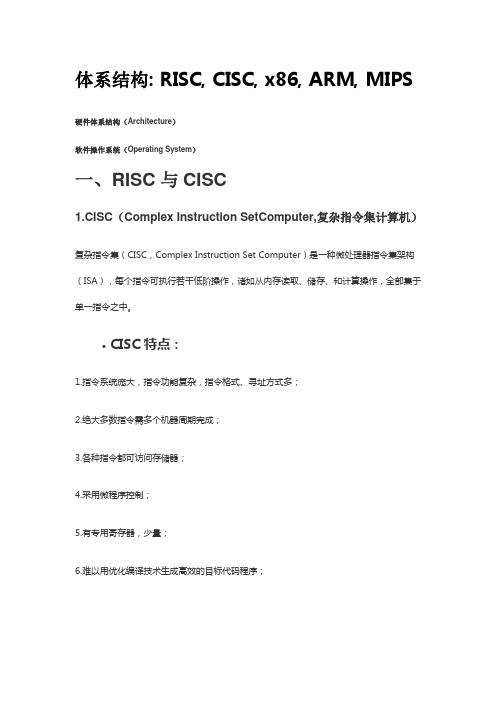

体系结构 RISC, CISC, x86, ARM, MIPS

体系结构: RISC, CISC, x86, ARM, MIPS硬件体系结构(Architecture)软件操作系统(Operating System)一、RISC与CISC1.CISC(Complex Instruction SetComputer,复杂指令集计算机)复杂指令集(CISC,Complex Instruction Set Computer)是一种微处理器指令集架构(ISA),每个指令可执行若干低阶操作,诸如从内存读取、储存、和计算操作,全部集于单一指令之中。

CISC特点:1.指令系统庞大,指令功能复杂,指令格式、寻址方式多;2.绝大多数指令需多个机器周期完成;3.各种指令都可访问存储器;4.采用微程序控制;5.有专用寄存器,少量;6.难以用优化编译技术生成高效的目标代码程序;在CISC指令集的各种指令中,大约有20%的指令会被反复使用,占整个程序代码的80%。

而余下的80%的指令却不经常使用,在程序设计中只占20%。

2.RISC(reduced instruction setcomputer,精简指令集计算机)精简指令集这种设计思路对指令数目和寻址方式都做了精简,使其实现更容易,指令并行执行程度更好,编译器的效率更高。

它能够以更快的速度执行操作。

这种设计思路最早的产生缘自于有人发现,尽管传统处理器设计了许多特性让代码编写更加便捷,但这些复杂特性需要几个指令周期才能实现,并且常常不被运行程序所采用。

此外,处理器和主内存之间运行速度的差别也变得越来越大。

在这些因素促使下,出现了一系列新技术,使处理器的指令得以流水执行,同时降低处理器访问内存的次数。

实际上在后来的发展中,RISC与CISC在竞争的过程中相互学习,现在的RISC指令集也达到数百条,运行周期也不再固定。

虽然如此,RISC设计的根本原则——针对流水线化的处理器优化—0—没有改变,而且还在遵循这种原则的基础上发展出RISC的一个并行化变种VLIW(包括Intel EPIC),就是将简短而长度统一的精简指令组合出超长指令,每次执行一条超长指令,等于并行执行多条短指令。

MIPS汇编指令学习

MIPS汇编指令学习MIPS汇编语⾔基础 MIPS的系统结构及设计理念⽐较先进,其指令系统经过通⽤处理器指令体系MIPS I、MIPS II、MIPS III、MIPS IV、MIPS V,以及嵌⼊式指令体系MIPS16、MIPS32到MIPS64的发展。

MIPS32的架构是⼀种基于固定长度的定期编码指令集,并采⽤导⼊/存储(load/store)数据模型。

经改进,这种架构可⽀持⾼级语⾔的优化执⾏。

在路由器中,经常使⽤的⼀种MIPS架构就是MIPS32。

MIPS寄存器 RISC的⼀个显著特点就是⼤量使⽤寄存器。

因为寄存器的存取可以在⼀个时钟周期内完成,同时简化了寻找⽅式,所以,MIPS32的指令中除了加载/存储指令以外,都使⽤寄存器或者⽴即数作为操作数,以便让编译器通过保持对寄存器内数据的频繁存取进⼀步优化代码的⽣成性能。

MIPS32寄存器分为两类:通⽤寄存器(GPR)和特殊寄存器。

1、通⽤寄存器(GPR) 在MIPS体系结构中有32个通⽤寄存器,在汇编程序中可以⽤编号$0~$31表⽰,也可以⽤寄存器的名字表⽰,如$sp、$t1、$ta等,如图,堆栈是从内存的⾼地址⽅向向低地址⽅向增长的。

编号寄存器名称寄存器描述0 zero第0号寄存器,其值始终为01$at保留寄存器2~3$v0~v1values, 保存表达式或函数返回结果4-7$a0~a3aruments, 作为函数的前4个参数8~15$t0~$t7temporaries,供汇编程序使⽤的临时寄存器16~23$s0~$s7saved values,⼦函数使⽤时需要先保存原寄存器的值24~25$t8~t9temporaries, 供汇编程序的临时寄存器,补充$t0~t726~27$k0~$k1保留,中断处理函数使⽤28$gp global pointer,全局指针29$sp stack pointer, 堆栈指针,指向堆栈的栈顶30$fp frame pointer, 保存栈指针31$ra return address, 返回地址$0:即$zero,该寄存器总是返回0,为0这个有⽤常数提供了⼀个简洁的编码形式。

指令集的峰值mips

指令集的峰值mipsMIPS(Microprocessor without Interlocked Pipelined Stages)是一种常用的指令集架构,其峰值性能非常出色。

MIPS指令集广泛应用于各种计算机系统和嵌入式设备中,具有高效、可靠和灵活的特点。

MIPS架构的峰值性能主要体现在以下几个方面。

MIPS指令集的精简性使得其执行效率非常高。

MIPS指令集只包含了约60条指令,相比其他复杂的指令集,MIPS指令集更加简洁明了。

这不仅降低了硬件实现的复杂度,还提高了指令的执行速度。

MIPS架构采用了流水线技术,使得指令的执行可以并行进行。

在MIPS架构中,指令被分为多个阶段,每个阶段都可以同时执行不同指令的不同部分。

这种流水线的设计可以大大提高指令的执行效率,使得多条指令可以同时执行,进而实现更高的峰值性能。

MIPS指令集还采用了延迟槽技术,通过在分支指令之后插入无关指令来隐藏分支延迟。

这样可以充分利用CPU的计算资源,提高指令的执行效率。

同时,MIPS指令集还提供了丰富的分支和跳转指令,使得程序可以更加灵活地控制流程,进一步提高了峰值性能。

MIPS架构还支持多种优化技术,如乱序执行、超标量执行和动态调度等。

这些技术可以根据程序的特点和需求进行灵活配置,进一步提高指令的执行效率和系统的峰值性能。

总体来说,MIPS指令集的峰值性能在当今计算机系统中占据重要地位。

其精简的指令集、高效的流水线设计、延迟槽技术和优化技术的支持,使得MIPS架构在高性能计算、嵌入式系统和网络设备等领域都有广泛的应用。

无论是在超级计算机上进行科学计算,还是在智能手机上运行复杂的应用程序,MIPS指令集都可以提供卓越的性能和能力。

而且,MIPS架构的开放性和可扩展性也使得其在学术界和工业界都备受青睐。

MIPS指令集以其高效、可靠和灵活的特点,在计算机系统和嵌入式设备中发挥了重要作用。

其优秀的峰值性能得益于精简的指令集、流水线设计、延迟槽技术和优化技术的支持。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一 MIPS指令系统和MIPS体系结构

实验目的:

(1)了解和熟悉指令级模拟器

(2)熟练掌握MIPSsim模拟器的操作和使用方法

(3)熟悉MIPS指令系统及其特点,加深对MIPS指令操作语义的理解

(4)熟悉MIPS体系结构

实验平台:

实验平台采用指令级和流水线操作级模拟器MIPSsim。

实验内容和步骤:

首先要阅读MIPSsim模拟器的使用方法,然后了解MIPSsim的指令系统和汇编语言。

(1)启动MIPSsim(用鼠标双击MIPSsim.exe)。

(2)选择“配置”->“流水方式”选项,使模拟器工作在非流水方式。

(3)参照使用说明,熟悉MIPSsim模拟器的操作和使用方法。

可以先载入一个样例程序(在本模拟器所在的文件夹下的“样例程序”文件夹中),然后分别以单步执行一条指令、执行多条指令、连续执行、设置断点等的方式运行程序,观察程序的执行情况,观察CPU中寄存器和存储器的内容的变化。

(4)选择“文件”->“载入程序”选项,加载样例程序 alltest.asm,然后查看“代码”

窗口,查看程序所在的位置(起始地址为0x00000100)。

(5)查看“寄存器”窗口PC寄存器的值:[PC]=0X00000000。

(6)执行load和store指令,步骤如下:

1)单步执行一条指令(F7)。

2)下一条指令地址为=0X00000004 ,是一条有(有,无)符号载

入字节(字节,半字,字)指令。

3)单步执行一条指令(F5)。

4)查看R1的值,[R1]=0XFFFFFFFFFFFFFF80。

5)下一条指令地址为0X00000008 ,是一条有(有,无)符号

载入字(字节,半字,字)指令。

6)单步执行1条指令。

7)查看R1的值,[R1]=0X0000000000000080。

8)下一条指令地址为0x0000000c,是一条无(有,无)符号载入字节(字

节,半字,字)指令。

9)单步执行1条指令。

10)查看R1的值,[R1]= 0X0000000000000080 。

11)单步执行1条指令。

12)下一条指令地址为0X00000014,是一条保存字(字节,半字,字)

指令。

13)单步执行一条指令(F5)。

14)查看内存BUFFER处字的值,值为0X00000080 。

(7)执行算术运算类指令。

步骤如下:

1)双击“寄存器”窗口中的R1,将其值修改为2。

2)双击“寄存器”窗口中的R2,将其值修改为3。

3)单步执行一条指令。

4)下一条指令地址为0x00000020,是一条加法指令。

5)单步执行一条指令。

6)查看R3的值,[R3]= 0x0000000000000005 。

下一条指令地址为0x00000024,是一条乘法指令。

7)单步执行一条指令。

8)查看LO、HI的值,[LO]=0x0000000000000006,[HI]=0x0000000000000000。

(8)执行逻辑运算类指令。

步骤如下:

1)双击“寄存器”窗口中的R1,将其值修改为0XFFFF0000。

2)双击“寄存器”窗口中的R2,将其值修改为0XFF00FF00。

3)单步执行一条指令。

4)下一条指令地址为0x00000030 ,是一条逻辑与运算指令,第二个操作数寻址方式

是寄存器直接寻址(寄存器直接寻址,立即数寻址)。

5)单步执行一条指令。

6)查看R3的值,[R3]= 0x00000000FF000000。

7)下一条指令地址为0x00000034,是一条逻辑与指令,第二个操作数寻址方式是

立即数寻址(寄存器直接寻址,立即数寻址)。

8)单步执行一条指令。

9)查看R3的值,[R3]= 0x0000000000000000。

(9)执行控制转移类指令。

步骤如下:

1)双击“寄存器”窗口中R1,将其值修改为2。

2)双击“寄存器”窗口中R2,将其值修改为2。

3)单步执行一条指令。

4)下一条指令地址为0x00000040__________,是一条BEQ指令,其测试条件是__相等________,目标地址为0x0000004C__________。

5) 单步执行1条指令。

6) 查看PC的值,[PC]=0x0000004c__________,表明分支_成功_________(成功,失败)。

7) 一条指令是一条BGEZ指令,其测试条件是大于或等于零________,目标地址为0x00000058__________。

8) 单步执行1条指令。

9) 查看PC的值,[PC]=0x00000058_________,表明分支___成功_______(成功,失败)。

10) 下一条指令是一条BGEZAL指令,其测试条件是___小于或等于零转移_______,目标地址为0x00000064__________。

11) 单步执行1条指令。

12) 查看PC的值,[PC]=0x00000064_________,表明分支___成功_______(成功,失败);查看R31的值,[R31]=0x000000000000005C_______________。

13) 单步执行1条指令。

14)查看R1的值,[R1]=0x0000000000000074_______________。

15)下一条指令地址为0x00000068________,是一条JALR指令,保存目标地址的寄存器为R1_____,保存返回地址的目标寄存器为R3___。

16)单步执行1条指令。

17)查看PC和R3的值,[PC]=0x00000074____,[R3]=0x000000000000006C________。