VHDL语言第四章VHDL语言构造体描述方式

合集下载

VHDL语言的基本结构

1 实体说明 1)实体语句结构 ENTITY 实体名 IS [GENERIC(类属表);] [PORT(端口表);] END ENTITY 实体名 2)类属参数说明 GENERIC([常数名:数据类型[:设定值] {;常数名:数据类型[:设定值]};

4

一、VHDL语言设计的基本单元及其构成

3)端口说明 PORT(端口名{,端口名}:方向 数据类型; 是对设计实体与外部接口 的描述,即对元件引脚、 ┇ 数据类型和I/O方向的描述 端口名{,端口名}:方向 数据类型); 1端口名

设计实体

进程 或其它并行结构 结构体 n (ARCHITECTURE 进程 或其它并行结构

配置(CONFIGURATION)

VHDL程序设计实体的一般结构

2

VHDL语言的基本结构

主要内容

一、 VHDL语言设计的基本单元及其构成 二、 VHDL语言构造体的子结构描述 三、 包集合、库及配置

3

一、VHDL语言设计的基本单元及其构成

VHDL语言

15

二、VHDL语言构造体的子结构描述

【例】4位二进制加法计数器构造体逻辑描述。

SIGNAL cnt4:INTEGER RANGE O TO 15; ... PROCESS(clk,clear,Stop) BEGIN IF clear='0' THEN cnt4<=0; ELSIF clk'EVENT AND clk='1' THEN IF stop='0' THEN cnt4<=cnt4+1; END IF; END IF; END PROCESS; --注意cnt4的数据类型

存盘文件 为 bpac.vhd

4

一、VHDL语言设计的基本单元及其构成

3)端口说明 PORT(端口名{,端口名}:方向 数据类型; 是对设计实体与外部接口 的描述,即对元件引脚、 ┇ 数据类型和I/O方向的描述 端口名{,端口名}:方向 数据类型); 1端口名

设计实体

进程 或其它并行结构 结构体 n (ARCHITECTURE 进程 或其它并行结构

配置(CONFIGURATION)

VHDL程序设计实体的一般结构

2

VHDL语言的基本结构

主要内容

一、 VHDL语言设计的基本单元及其构成 二、 VHDL语言构造体的子结构描述 三、 包集合、库及配置

3

一、VHDL语言设计的基本单元及其构成

VHDL语言

15

二、VHDL语言构造体的子结构描述

【例】4位二进制加法计数器构造体逻辑描述。

SIGNAL cnt4:INTEGER RANGE O TO 15; ... PROCESS(clk,clear,Stop) BEGIN IF clear='0' THEN cnt4<=0; ELSIF clk'EVENT AND clk='1' THEN IF stop='0' THEN cnt4<=cnt4+1; END IF; END IF; END PROCESS; --注意cnt4的数据类型

存盘文件 为 bpac.vhd

VHDL的构造体architecture

每个构造体必须属于一个实体; 每个构造体必须有一个名称: 通常可以根据描述方式起名:

str rtl beh 构造体分为两部分: is – bigin: 说明语句; bigin – end: 并行语句;

2

构造体的说明语句ห้องสมุดไป่ตู้

type declarations;

类型说明

signal declarations; 信号说明

17

常用预定义类型

预定义类型在相关的包集合中定义

std.standard:

bit(位)、boolean(布尔)

integer(整数)、real(实数)

ieee.std_logic_1164:

std_logic(标准逻辑量);

ieee.std_logic_arith:

signed、unsigned;

20

常用预定义类型

boolean:(falth,true) 逻辑量,用于关系判断; 可进行逻辑运算; 不能表达为多位数组;

21

常用预定义类型 integer:(-231-1 -- +231-1) 算术量,用于算术运算; 其子集合有natural和positive; 考虑到电路综合效率,对于整数类型,可 以在说明时对数据范围进行限制;

18

常用预定义类型 bit、bit_vector:2值逻辑 数据范围(0,1),用于逻辑运算 说明方式: signal x:bit;--x为1位逻辑信号; signal y:bit_vector(3 downto 0); --y为4位逻辑信号,最高位为y(3), 在最左边;

19

常用预定义类型

bit、bit_vector:常数表达形式 一位逻辑量采用单引号: '1' '0' 多位逻辑量采用双引号: " 1001" 可以采用其他进制的缩写形式: b" 1001" o" 7777" x"ffff"

str rtl beh 构造体分为两部分: is – bigin: 说明语句; bigin – end: 并行语句;

2

构造体的说明语句ห้องสมุดไป่ตู้

type declarations;

类型说明

signal declarations; 信号说明

17

常用预定义类型

预定义类型在相关的包集合中定义

std.standard:

bit(位)、boolean(布尔)

integer(整数)、real(实数)

ieee.std_logic_1164:

std_logic(标准逻辑量);

ieee.std_logic_arith:

signed、unsigned;

20

常用预定义类型

boolean:(falth,true) 逻辑量,用于关系判断; 可进行逻辑运算; 不能表达为多位数组;

21

常用预定义类型 integer:(-231-1 -- +231-1) 算术量,用于算术运算; 其子集合有natural和positive; 考虑到电路综合效率,对于整数类型,可 以在说明时对数据范围进行限制;

18

常用预定义类型 bit、bit_vector:2值逻辑 数据范围(0,1),用于逻辑运算 说明方式: signal x:bit;--x为1位逻辑信号; signal y:bit_vector(3 downto 0); --y为4位逻辑信号,最高位为y(3), 在最左边;

19

常用预定义类型

bit、bit_vector:常数表达形式 一位逻辑量采用单引号: '1' '0' 多位逻辑量采用双引号: " 1001" 可以采用其他进制的缩写形式: b" 1001" o" 7777" x"ffff"

第4章_VHDL设计初步1

4.2.2 D触发器VHDL描述的语言现象说明

4. 上升沿检测表式和信号属性函数EVENT

关键词EVENT是信号属性,VHDL通过以下表式来测定 某信号的跳变边沿: <信号名>'EVENT

4.2.2 D触发器VHDL描述的语言现象说明

5. 不完整条件语句与时序电路

【例4-11】 ENTITY COMP_BAD IS PORT( a1 : IN BIT; b1 : IN BIT; q1 : OUT BIT ); END ; ARCHITECTURE one OF COMP_BAD IS BEGIN PROCESS (a1,b1) BEGIN IF a1 > b1 THEN q1 <= '1' ; ELSIF a1 < b1 THEN q1 <= '0' ;-- 未提及当a1=b1时,q1作何操作 END IF; END PROCESS ; END ;

第4章

本章内容

4.1 多路选择器VHDL描述(简单组合电 路) 4.2 寄存器描述及其VHDL语言现象(简 单时序电路) 4.3 1为二进制全加器的VHDL设计(实例) 4.4 VHDL文本输入设计方法(工具使用, 通过上机操作掌握)

本章重点掌握内容

1、实体及端口的定义。 2、结构体和信号的定义。 3、基本逻辑操作符和信号赋值操作符。 4、IF-THEN-ELSE(顺序)、WHEN-ELSE (并行)语句。 5、进程语句。 6、信号的上升沿表示方法。 7、元件例化方法。

是什么是VHDL?

Very high speed integrated Hardware Description Language (VHDL)

是IEEE、工业标准硬件描述语言 用语言的方式而非图形等方式描述硬件电路

第4章VHDL语言基础

BEGIN 结构体描述部分;

END 结构体名;

4.1.3 结构体部分

结构体组成

结

构 体

说

明 结

构

体 结 构 体

功 能 描 述

常数说明 数据类型说明

信号说明 例化元件说明 子程序说明

块语句 进程语句 信号赋值语句 子程序调用语句 元件例化语句

结构体描述风格

行为描述 描述该设计单元的功能,主要使用函数、过程和进程语 句,以算法形式描述数据的变换和传送

例4-4

Library ieee; Use ieee.std_logic_1164.all; Use ieee.std_logic_unsigned.all; Use ieee.std_logic_arith.all;

行为描述

Entity eqcomp4 is Port (a,b: in std_logic_vector (3 downto 0); equals: out std_logic);

4.1.2 实体部分

实体(ENTITY)

实体是一个设计实体的表层设计单元,其功能是 对这个设计实体与外部电路进行接口描述。它规定了 设计单元的输入/输出接口信号或引脚,是设计实体 经封装后对外的一个通信界面。类似于原理图中的一 个部件符号。

4.1.2 实体部分

实体格式

ENTITY 实体名 IS

书写格式: GENERIC([常数名:数据类型[:设定值]

{;常数名:数据类型[:=设定值 ]}); 例4-1

GENERIC (cntwidth : integer:=4);

4.1.2 实体部分

PORT端口

用于定义模块所有的输入/输出信号,相当于定义一个 模块符号

END 结构体名;

4.1.3 结构体部分

结构体组成

结

构 体

说

明 结

构

体 结 构 体

功 能 描 述

常数说明 数据类型说明

信号说明 例化元件说明 子程序说明

块语句 进程语句 信号赋值语句 子程序调用语句 元件例化语句

结构体描述风格

行为描述 描述该设计单元的功能,主要使用函数、过程和进程语 句,以算法形式描述数据的变换和传送

例4-4

Library ieee; Use ieee.std_logic_1164.all; Use ieee.std_logic_unsigned.all; Use ieee.std_logic_arith.all;

行为描述

Entity eqcomp4 is Port (a,b: in std_logic_vector (3 downto 0); equals: out std_logic);

4.1.2 实体部分

实体(ENTITY)

实体是一个设计实体的表层设计单元,其功能是 对这个设计实体与外部电路进行接口描述。它规定了 设计单元的输入/输出接口信号或引脚,是设计实体 经封装后对外的一个通信界面。类似于原理图中的一 个部件符号。

4.1.2 实体部分

实体格式

ENTITY 实体名 IS

书写格式: GENERIC([常数名:数据类型[:设定值]

{;常数名:数据类型[:=设定值 ]}); 例4-1

GENERIC (cntwidth : integer:=4);

4.1.2 实体部分

PORT端口

用于定义模块所有的输入/输出信号,相当于定义一个 模块符号

4.1VHDL语言顺序描述语句

VHDL顺序语句

例:

注意变 量I初 始化和 在循环 中的加1 处理

8位奇偶校验电路 architecture abc of example is begin

PROCESS(a) variable tmp:std_logic;

begin tmp:=‘0’; i:=0; WHILE (i<8) LOOP tmp:=tmp XOR a(i); i:=i+1; END LOOP; Y<=tmp;

格式: 标号:FOR 循环变量 IN 循环次数范围 LOOP 顺序处理语句; …… END LOOP;

注意: 循环变量只是一个临时变量,由LOOP语句自动定

义,不需预先定义; LOOP语句范围内不要再使用其它与该循环变量同

名的标识符。 循环次数完成后程序自动退出循环。

VHDL顺序语句

例:

能否定 义为信

VHDL顺序语句

3、CASE语句

格式:

Case 表达式 Is WHEN 选择值 =>顺序处理语句;

…… WHEN 选择值 =>顺序处理语句; WHEN OTHERS =>顺序处理语句; End case;

注意: CASE语句至少包含一个条件句; CASE语句中条件表达式的值必须列举穷尽,但不

能重复; 无法穷举,用OTHERS表达。

注意:IF 语句隐含有优先级的关系,可用来设计具有优 先权的电路 。

VHDL顺序语句

例:

不需穷 尽所有

情况

四选一数据选择器 architecture abc of example is signal sel:std_logic_vector(1 downto 0); begin

sel<=b &a; process(sel) begin

VHDL的描述风格

BEGIN

u1: half_adder PORT MAP (x, y, b, a);

u2: half_adder PORT MAP (c_in, b, sum, c);

u3: or_gate PORT MAP (c, a, c_out);

END structural;

由上例可见,对于一个复杂的电子系统,可以将其分解为若 干个子系统,每个子系统再分解成模块,形成多层次设计。 这样,可以使更多的设计者同时进行合作。在多层次设计中, 每个层次都可以作为一个元件,再构成一个模块或系统,可 以先分别仿真每个元件,然后再整体调试。所以说结构化描 述不仅是一种设计方法,而且是一种设计思想,是大型电子 系统高层次设计的重要手段。

1 10

1

0

1 11

1

1

END IF;

-- (0 TO 3)

sum <= sum_vector (n) AFTER 2*tpd; - - sum_vector初值为“0101”

c_out <= carry_vector (n) AFTER 3*tpd; - - carry_vector初值为“0011”

GENERIC(tpd:TIME:=10 ns); PORT(in1, in2: IN STD_LOGIC;

out1: OUT STD_LOGIC); END or_gate;

ARCHITECTURE rtl OF or_gate IS

BEGIN

out1 <= in1 OR in2 AFTER tpd;

下面结合一个全加器来说明这四种描述风格,全加器的端口 示意图如图所示,其输入输出关系如表所示。

全加器的输入输出关系

全加器框图

3.3 VHDL语言结构体的描述方法

当a和b的 宽度发生 变化时, 需要修改 设计,当 宽度过大 时,设计 非常繁琐

Architecture dataflow2 of eqcomp4 is begin equal <= not(a(0) xor b(0))and not(a(1) xor b(1))and not(a(2) xor b(2))and not(a(3) xor b(3)); end dataflow2;

程序包

程序包的格式: 包集合标题 PACKAGE 包集合名 IS [说明语句] END 包集合名; 定义子程序

包集合体

PACKAGE BODY 包集合名 IS [说明语句] 实现子程序 END 包集合名;

Hale Waihona Puke 函数(Function)Function 函数名 (参数表) Return 数据类型 函数首 在程序包标题 中定义 Function 函数名 (参数表) Return 数据类型 IS 说明部分 Begin 顺序语句 函数体 END Function 函数名; 在程序包体中 定义

函数应用实例

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE WORK.hanshu.ALL ; ENTITY axamp IS PORT(dat1,dat2 : IN STD_LOGIC_VECTOR(3 DOWNTO 0); dat3,dat4 : IN STD_LOGIC_VECTOR(3 DOWNTO 0); out1,out2 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ); END; ARCHITECTURE bhv OF axamp IS BEGIN out1 <= max(dat1,dat2); --用在赋值语句中的并行函数调用语句 PROCESS(dat3,dat4) BEGIN out2 <= max(dat3,dat4); --顺序函数调用语句 END PROCESS; END;

Architecture dataflow2 of eqcomp4 is begin equal <= not(a(0) xor b(0))and not(a(1) xor b(1))and not(a(2) xor b(2))and not(a(3) xor b(3)); end dataflow2;

程序包

程序包的格式: 包集合标题 PACKAGE 包集合名 IS [说明语句] END 包集合名; 定义子程序

包集合体

PACKAGE BODY 包集合名 IS [说明语句] 实现子程序 END 包集合名;

Hale Waihona Puke 函数(Function)Function 函数名 (参数表) Return 数据类型 函数首 在程序包标题 中定义 Function 函数名 (参数表) Return 数据类型 IS 说明部分 Begin 顺序语句 函数体 END Function 函数名; 在程序包体中 定义

函数应用实例

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE WORK.hanshu.ALL ; ENTITY axamp IS PORT(dat1,dat2 : IN STD_LOGIC_VECTOR(3 DOWNTO 0); dat3,dat4 : IN STD_LOGIC_VECTOR(3 DOWNTO 0); out1,out2 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ); END; ARCHITECTURE bhv OF axamp IS BEGIN out1 <= max(dat1,dat2); --用在赋值语句中的并行函数调用语句 PROCESS(dat3,dat4) BEGIN out2 <= max(dat3,dat4); --顺序函数调用语句 END PROCESS; END;

第4章 VHDL语言基础

设计实体

结构体1

结构体2

结构体3

。 。 。

结构体n

FPGA-CPLD原理及应用

结构体的语法

第4章 VHDL语言基础

architecture 结构体名称 of 实体名称 is [说明语句] ;

begin [(功能描述)语句];

end [architecture] 结构体名称;

注:同一实体的结构体不能同名。定义语句中的常 数、信号不能与实体中的端口同名。

equal: out std_logic ); end eqcomp4;

A[3..0] B[3..0]

equal

FPGA-CPLD原理及应用

端口声明

第4章 VHDL语言基础

确定输入、输出端口的数目和类型。

Port (端口名称{,端口名称}:端口模式

… 端口名称{,端口名称}:端口模式 );

数据类型; 数据类型

FPGA-CPLD原理及应用

VHDL组成

第4章 VHDL语言基础

库 包 实体

结构体

eqcomp4.vhd

--eqcomp4 is a four bit equality comparator

Library IEEE; use IEEE.std_logic_1164.all;

entity eqcomp4 is port(a, b:in std_logic_vector(3 downto 0);

FPGA-CPLD原理及应用

第4章 VHDL语言基础

计数器等效描述(out与buffer的区别)

FPGA-CPLD原理及应用

3、数据类型

第4章 VHDL语言基础

指端口上流动的数据表达格式,为预先定好的数据类型,如: bit、bit_vector、integer、std_logic、std_logic_vector 等。 例: entity m81 is port (a: in std_logic_vector(7 downto 0); sel: in std_logic_vector(2 downto 0); b:out bit ); end entity m81;

4.VHDL程序结构和常用描述方法

VHDL构造体常用描述方法 3

• 结构描述

– 把复杂的电子实体按其不同的硬件电路功能 划分为若干部分,然后对各部件具体描述。 – 全加器的一种逻辑结构图:

x y 半 加 器 a

b

Cin

半 加 器

c

或门

Cout Sum

结构描述

• 主要组成部分:元件、例元、生成语句

• 元件:用以描述某个实体的同一构造的同类 型部件(半加器)

• Architecture behave_aa OF aa Is Signal s1:bit; Signal s2,s3:std_logic_vector(0 to 3); ... Begin ... End data;

常数说明

结 构 体 说 明 结 构 体 结 构 体 功 能 描 述 数据类型说明 信号说明 例化元件说明 子程序说明 块语句 进程语句 信号赋值语句 子程序调用语句

类属常用于定义: 实体端口的大小、

设计实体的物理特性、 总线宽度、 元件例化的数量等。 例 1: entity mck is generic(width: integer:=16); port(add_bus:out std_logic_vector (width-1 downto 0)); …

例2:2输入与门的实体描述(P.213)

例:结构体中错误的信号声明

VHDL的程序结构

库、程序包 实体(Entity) 结构体

(Architecture)

进程 或其它并行结构

配置(Configuration)

VHDL的程序结构

四、配置

结构体1 结构体2 设计实体

• 一个设计实体的多种实现方式

Behave_.. Rtl_...

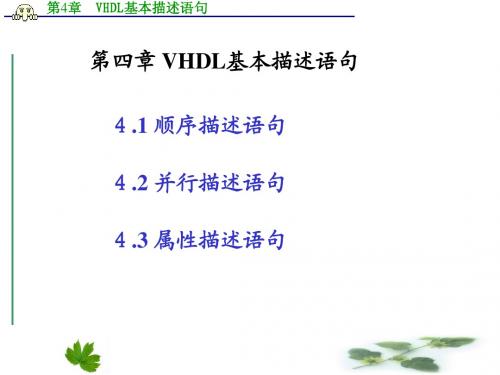

第四章 VHDL基本描述语句

temp1 : = ( cvolt + 1.8 ) * ccurrent ;

temp2 : = c + 78 ;

temp3 : = c / 5 ; temp4 : = d ; temp5 : = temp4 ( 2 ) ; END PROCESS cfuzhi ; -- 此时c必须是5的倍数

END behavioral ;

第 4章

VHDL基本描述语句

4.1.3 赋值语句

变量赋值语句格式:

变量赋值目标 := 赋值源 ;

表示把右边的变量表达式的值代入到目的变量。

第 4章

VHDL基本描述语句

cfuzhi : PROCESS(c,d)

BEGIN temp0 : = cvolt ; 值 -- 变量直接赋值 -- 变量表达式赋

4.4.1 WAIT 语句

进程的运行要么处于执行状态,要么处于挂起状态,进程 的执行是由敏感信号列表来触发的,所以此时进程的同步点 由敏感信号列表来控制,这是一种隐式同步,同步点 在”END PROCESS[进程名]”这一行上。 当进程没有敏感信号表时,进程的状态就由WAIT来控制,

这是一显式同步,同步点在“WAIT 语句”这一行上。

SIGNAL temp1, temp2, temp3 : STD_LOGIC ; BEGIN cwait3 : PROCESS BEGIN temp1 <= data0 AND sel ; temp2 <= data1 AND ( NOT sel ) ; temp3 <= temp1 OR temp2 ;

第 4章

VHDL基本描述语句

2. WAIT FOR语句说明

WAIT FOR时间表达式为超时语句,在此语句中定义了一 个时间段,从执行到当前的WAIT语句开始,在此时间段 内,进程处于挂起状态,当超过这一时间段后,进程自动 恢复执行。(此语句不可综合) cwait2 : PROCESS BEGIN y <= ( a AND b ) OR ( m XOR t ) ; z <= c NAND d ;

vhdl结构化描述

VHDL的基本结构由实体(ENTITY)和结构体(ARCHITECTURE)两部分构成。

其中,结构化描述主要使用AND、OR等逻辑运算符来描述元件之间的连接关系,具体步骤包括:

1.原件说明,用于说明原件的调用,并描述该元件的接口。

2.原件例化,指定原件的安放位置,并确定与其他元件放置的连线关系。

3.原件配置,指定原件所用的设计实体。

另外,结构化描述程序的主要步骤包括:

1.绘制框图。

2.原件说明。

3.信号说明。

4.元件例化。

5.添加必要的框架。

以上步骤和内容仅供参考,如需了解更多关于VHDL结构化描述的信息,建议查阅专业书籍或咨询专业技术人员。

EDA教程之第四章VHDL语言的主要描述语句

Y <= tmp;

END Process P1;

LOOP语句

循环变量(i)在信号说明、变量说明中不能出现,信号、 变量不能代入到循环变量中。

局部变量(tmp)仅能在进程中出现。 全局变量、信号可以将局部变量的值带ential statement

BEGIN

Indata <= S3 & S2 & S1 & S0;

P1:PROCESS (Indata, G1,G2)

IF( G1='0' AND G2='0') THEN

CASE indata IS

WHEN "0000"=> y <="01 11 11 11 11 11 11 11";

WHEN "0001"=> y <="10 11 11 11 11 11 11 11";

功能wait语句使系统暂时挂起(等同于end process),此时,信号值开始更新。条件满足后, 系统将继续运行。

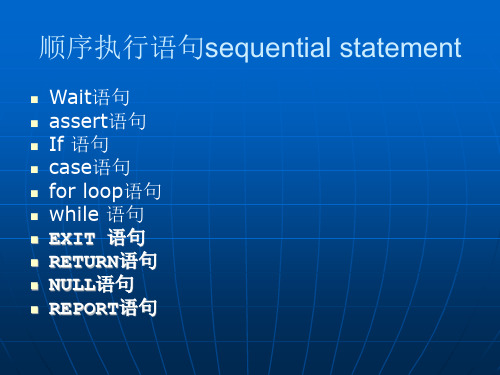

顺序执行语句sequential statement

顺序执行语句sequential statement

顺序执行语句sequential statement

顺序执行语句sequential statement

并行处理语句concurrent statement

并行处理语句concurrent statement

并行处理语句concurrent statement

顺序执行语句和并行处理语句总结

1、顺序执行语句wait、assert、if -else 、 case、for-loop、while语句只能用在 process、function 和procedure 中; 2、并行处理语句(条件信号带入和选择信 号带入)只能用在architecture、block中;

VHDL语言结构体的描述方式

① 元件说明:描述局部接口。 ② 元件例化:相对于其他元件放置元件。 ③ 元件配置:指定元件所有的设计实体。

结构描述用于层次化设计,高层次的设计模块 调用低层次的设计模块,或直接用门电路来构成一 个复杂的逻辑电路。

7

第7页/共12页

VHDL语言结构体的描述方式

【例3.3】将例3.1中的数据选择器采用结构描述。

c: OUT STD_LOGIC );

END COMPONENT;

COMPONENT or2

PORT (a, b: IN STD_LOGIC;

c: OUT STD_LOGIC );

END COMPONENT;

U1

1 ns

s

U3

& ab

d0

U2

&

U4 ≥1

y

d1

aa

8

第8页/共12页

VHDL语言结构体的描述方式

【例3.1】试用行为描述完成二选一数据选择器的设计。

设数据输入为d0和d1、选择输入为s,输出为y。

程序清单:

ENTITY mux21 IS

PORT ( d1, d0: IN STD_LOGIC;

s:

IN STD_LOGIC;

y:

OUT STD_LOGIC );

END mux21;

ARCHITECTURE behavior OF mux21 IS

● 行为描述只需描述清楚输入与输出的行为, 而与它们的结构无关;

● 描述程序大多采用算术运算、关系运算、惯 性延时、传输延时等语句;

● 结构体中的过程语句属于典型的行为描述。

3

第3页/共12页

VHDL语言结构体的描述方式

3.2 结构体的数据流描述

结构描述用于层次化设计,高层次的设计模块 调用低层次的设计模块,或直接用门电路来构成一 个复杂的逻辑电路。

7

第7页/共12页

VHDL语言结构体的描述方式

【例3.3】将例3.1中的数据选择器采用结构描述。

c: OUT STD_LOGIC );

END COMPONENT;

COMPONENT or2

PORT (a, b: IN STD_LOGIC;

c: OUT STD_LOGIC );

END COMPONENT;

U1

1 ns

s

U3

& ab

d0

U2

&

U4 ≥1

y

d1

aa

8

第8页/共12页

VHDL语言结构体的描述方式

【例3.1】试用行为描述完成二选一数据选择器的设计。

设数据输入为d0和d1、选择输入为s,输出为y。

程序清单:

ENTITY mux21 IS

PORT ( d1, d0: IN STD_LOGIC;

s:

IN STD_LOGIC;

y:

OUT STD_LOGIC );

END mux21;

ARCHITECTURE behavior OF mux21 IS

● 行为描述只需描述清楚输入与输出的行为, 而与它们的结构无关;

● 描述程序大多采用算术运算、关系运算、惯 性延时、传输延时等语句;

● 结构体中的过程语句属于典型的行为描述。

3

第3页/共12页

VHDL语言结构体的描述方式

3.2 结构体的数据流描述

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

传输延时常用于描述总线延时、连接线的延时及 ASIC芯片中的路径延时。

具有传输延时的代入语句如下所示:

b<=TRANSPORT a AFTER 20ns; 语句中“TRANSPORT”是专门用于说明传输延时的前 置词。

举例

下面左图的门电路的惯性延时用传输延时来替代,那么就可 以得到如下面右图的波形结果。从下面右图波形可以看到,同样 门电路,当有10ns的脉冲波形输入时,经20ns传输延时以后,在 输出端就产生10ns的脉冲波形。也就是说,输出端的信号除延时 规定时间外,将完全复现输入端的输入波形,而不管输入波形的 形状和宽窄如何。

c<=a AND b AFTER 5ns; END and2_behav;

举例2

用行为描述方式描述四选一电路。

6个输入端口和一个输出端口。a和 b是选择信号输入端口

条件信号代 入语句

选择信号代入语句 根据选择型号 sel 当 前 值 , 将指定代入值 代入给输出量

根据a和b具体状态,将0-4值代入 信号量sel

BEGIN

信号a由两个驱动源b和d驱动。

a<=b AFTER 5 ns; a的值将取决于两个驱动器的

a<=d AFTER 5 ns; 输出b和d。那么信号a到底应

END sample;

该取何值?这一点在标准的数

据类型中没有定义。

为了解决多个驱动器同时驱动一个信号的信号行为 描述,在包集合STD_LOGIC_1164中专门定义了一 种描述判决函数的数据类型,称判决函数子类型。

4.1.3 多驱动器描述语句

在VHDL语言中,创建一个驱动器可以由一条信号代入语 句来实现。当有多个信号并行输出时,在构造体内部必须利用 代入语句,对每个信号创建一个驱动器。这样在构造体内部就 会有多个代入语句。

在设计逻辑电路时,有时会碰到多个驱动器的输出将连接 到同一条信号线上,如下例:

ARCHITECTURE sample OF sample IS

4.1.2 延时语句

VHDL中存在两种延时类型:惯性延时和传输延时。 这两种延时常用于VHDL语言的行为描述方式。

1、惯性延时

惯性延时是缺省的,即在语句中如果不作特别声明, 产生的延时一定是惯性延时。这是因为大多数器件在行 为仿真时都会呈现这种惯性延时。

在惯性模型中,系统或器件输出信号要发生变化必 须有一段时间的延时,这段延时时间常称为系统或器件 的惯性或称惯性延时。

惯性延时有一个重要的特点,即当一个系统或器件, 它的输入信号变化周期小于系统或器件的惯性(或惯性 延时)时,其输出将保持不变。

举例

如上图所示,有一个门电路,惯性延时时间为20ns,当输入 端a输入一个10ns的脉冲信号时,输出端b仍维持低电平而不发生 变化。这是因为输入信号的变化周期比惯性延时时间20ns短。

代入语句是VHDL语言中进行行为描述的最基本的语句。 例如: a<=b; 该语句的功能是a得到b的值。当该语句有效时,现行信号b的 值将代入到信号a。只要b的值有一个新的变化,那么该语句将 被执行。所以,b是该代入语句的一个敏感量。

最普遍的格式为:信号量<=敏感信号量表达式; 例如:z<=a NOR (b AND c);

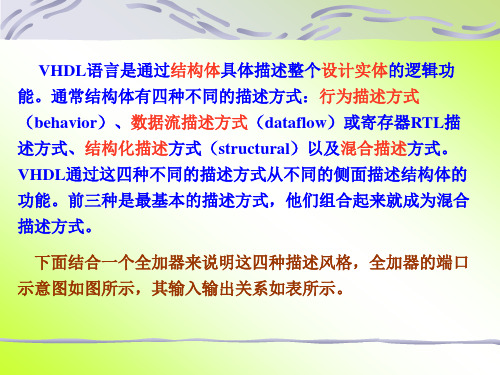

第四章

VHDL语言构造体描述方 式

对硬件系统进行描述,可以采用3种不同风格的 描述方式,即行为描述方式、寄存器传输(或数据流 Data Flow)描述方式和结构化的描述方式。这3种描 述方式从不同的角度对硬件系统进行行为和功能的描 述。在当前情况下,采用后两种描述方式的VHDL语 言程序可以进行逻辑综合,而采用行为描述的VHDL 语言程序,大部分只用于系统仿真,少数的也可以进 行逻辑综合。本章针对这3种不同风格的描述方式作 一介绍。

补充:什么是仿真?什么是逻辑综合?

仿真:一个计算系统通过使用允许它运行为 另一个系统而写的程序的软件和硬件,而对 后者进行的模拟。简单说来就是对一个程序 或模型进行“模拟”的过程.

逻辑综合:设计自动化工具将高层次的系统 描述转化为具体的硬件.这与计算机软件程 序编译成机器代码类似.

4.1.1 代入语句

几乎所有器件都存在惯性延时,因此,硬件电路的设计人员为 了逼真地仿真硬件电路的实际工作情况,在代入语句中总要加上惯 性延时时间的说明。例如:

b<=a AFTER 10ns; 惯性延时说明只在行为仿真时有意义,逻辑综合时将被忽略, 或者在逻辑综合前必须去掉延时说明。

Hale Waihona Puke 2、传输延时VHDL语言中,传输延时不是缺省的,必须在语句 中明确说明。

所谓判决函数就是在多个驱动器同时驱动一个信号 时,定义输出哪一个值的函数。

当系统要确定多驱动器输出的状态时,可调用判决 函数。

4.1.4 GENERIC语句

类属说明: 确定实体或组件中定义的局部常数。模块化设计时多用于不同

层次模块之间信息的 传递。可从外部改变内部电路结构和规模。 类属说明必须放在端口说明之前。

GENERIC ( 常数名称:类型 [:= 缺省值] {常数名称:类型 [:= 缺省值]} );

使用GENERIC语句易于使器件模块化和通用化。

• 类属映射语句可用于设计从外部端口改变元件内部 参数或结构,在元件例化中使用特别方便。其语句 格式是: GENERIC MAP(类属表);

类属映射语句常配合端口映射语句使用。

4.1 构造体的行为描述方式

行为描述方式是对系统数学模型的描述,其抽象程度比 寄存器传输描述方式和结构化描述方式的更高。

在行为描述方式的程序中大量采用算术运算、关系运算、 惯性延时、传输延时等难于进行逻辑综合和不能进行逻 辑综合的VHDL语句。 一般来说,采用行为描述方式的VHDL语言程序主要用于 系统数学模型的仿真或者系统工作原理的仿真。

具有延时时间的代入语句:a<=b AFTER 5ns; 该语句表示,当b发生新的变化5ns以后才被代入到信号a 。

举例1

用具有延时时间的代入语句来描述二输入的 与门。

ENTITY and2 IS PORT (a,b: IN BIT; c: OUT BIT);

END and2; ARCHITECTURE and2_behav OF and2 IS BEGIN

具有传输延时的代入语句如下所示:

b<=TRANSPORT a AFTER 20ns; 语句中“TRANSPORT”是专门用于说明传输延时的前 置词。

举例

下面左图的门电路的惯性延时用传输延时来替代,那么就可 以得到如下面右图的波形结果。从下面右图波形可以看到,同样 门电路,当有10ns的脉冲波形输入时,经20ns传输延时以后,在 输出端就产生10ns的脉冲波形。也就是说,输出端的信号除延时 规定时间外,将完全复现输入端的输入波形,而不管输入波形的 形状和宽窄如何。

c<=a AND b AFTER 5ns; END and2_behav;

举例2

用行为描述方式描述四选一电路。

6个输入端口和一个输出端口。a和 b是选择信号输入端口

条件信号代 入语句

选择信号代入语句 根据选择型号 sel 当 前 值 , 将指定代入值 代入给输出量

根据a和b具体状态,将0-4值代入 信号量sel

BEGIN

信号a由两个驱动源b和d驱动。

a<=b AFTER 5 ns; a的值将取决于两个驱动器的

a<=d AFTER 5 ns; 输出b和d。那么信号a到底应

END sample;

该取何值?这一点在标准的数

据类型中没有定义。

为了解决多个驱动器同时驱动一个信号的信号行为 描述,在包集合STD_LOGIC_1164中专门定义了一 种描述判决函数的数据类型,称判决函数子类型。

4.1.3 多驱动器描述语句

在VHDL语言中,创建一个驱动器可以由一条信号代入语 句来实现。当有多个信号并行输出时,在构造体内部必须利用 代入语句,对每个信号创建一个驱动器。这样在构造体内部就 会有多个代入语句。

在设计逻辑电路时,有时会碰到多个驱动器的输出将连接 到同一条信号线上,如下例:

ARCHITECTURE sample OF sample IS

4.1.2 延时语句

VHDL中存在两种延时类型:惯性延时和传输延时。 这两种延时常用于VHDL语言的行为描述方式。

1、惯性延时

惯性延时是缺省的,即在语句中如果不作特别声明, 产生的延时一定是惯性延时。这是因为大多数器件在行 为仿真时都会呈现这种惯性延时。

在惯性模型中,系统或器件输出信号要发生变化必 须有一段时间的延时,这段延时时间常称为系统或器件 的惯性或称惯性延时。

惯性延时有一个重要的特点,即当一个系统或器件, 它的输入信号变化周期小于系统或器件的惯性(或惯性 延时)时,其输出将保持不变。

举例

如上图所示,有一个门电路,惯性延时时间为20ns,当输入 端a输入一个10ns的脉冲信号时,输出端b仍维持低电平而不发生 变化。这是因为输入信号的变化周期比惯性延时时间20ns短。

代入语句是VHDL语言中进行行为描述的最基本的语句。 例如: a<=b; 该语句的功能是a得到b的值。当该语句有效时,现行信号b的 值将代入到信号a。只要b的值有一个新的变化,那么该语句将 被执行。所以,b是该代入语句的一个敏感量。

最普遍的格式为:信号量<=敏感信号量表达式; 例如:z<=a NOR (b AND c);

第四章

VHDL语言构造体描述方 式

对硬件系统进行描述,可以采用3种不同风格的 描述方式,即行为描述方式、寄存器传输(或数据流 Data Flow)描述方式和结构化的描述方式。这3种描 述方式从不同的角度对硬件系统进行行为和功能的描 述。在当前情况下,采用后两种描述方式的VHDL语 言程序可以进行逻辑综合,而采用行为描述的VHDL 语言程序,大部分只用于系统仿真,少数的也可以进 行逻辑综合。本章针对这3种不同风格的描述方式作 一介绍。

补充:什么是仿真?什么是逻辑综合?

仿真:一个计算系统通过使用允许它运行为 另一个系统而写的程序的软件和硬件,而对 后者进行的模拟。简单说来就是对一个程序 或模型进行“模拟”的过程.

逻辑综合:设计自动化工具将高层次的系统 描述转化为具体的硬件.这与计算机软件程 序编译成机器代码类似.

4.1.1 代入语句

几乎所有器件都存在惯性延时,因此,硬件电路的设计人员为 了逼真地仿真硬件电路的实际工作情况,在代入语句中总要加上惯 性延时时间的说明。例如:

b<=a AFTER 10ns; 惯性延时说明只在行为仿真时有意义,逻辑综合时将被忽略, 或者在逻辑综合前必须去掉延时说明。

Hale Waihona Puke 2、传输延时VHDL语言中,传输延时不是缺省的,必须在语句 中明确说明。

所谓判决函数就是在多个驱动器同时驱动一个信号 时,定义输出哪一个值的函数。

当系统要确定多驱动器输出的状态时,可调用判决 函数。

4.1.4 GENERIC语句

类属说明: 确定实体或组件中定义的局部常数。模块化设计时多用于不同

层次模块之间信息的 传递。可从外部改变内部电路结构和规模。 类属说明必须放在端口说明之前。

GENERIC ( 常数名称:类型 [:= 缺省值] {常数名称:类型 [:= 缺省值]} );

使用GENERIC语句易于使器件模块化和通用化。

• 类属映射语句可用于设计从外部端口改变元件内部 参数或结构,在元件例化中使用特别方便。其语句 格式是: GENERIC MAP(类属表);

类属映射语句常配合端口映射语句使用。

4.1 构造体的行为描述方式

行为描述方式是对系统数学模型的描述,其抽象程度比 寄存器传输描述方式和结构化描述方式的更高。

在行为描述方式的程序中大量采用算术运算、关系运算、 惯性延时、传输延时等难于进行逻辑综合和不能进行逻 辑综合的VHDL语句。 一般来说,采用行为描述方式的VHDL语言程序主要用于 系统数学模型的仿真或者系统工作原理的仿真。

具有延时时间的代入语句:a<=b AFTER 5ns; 该语句表示,当b发生新的变化5ns以后才被代入到信号a 。

举例1

用具有延时时间的代入语句来描述二输入的 与门。

ENTITY and2 IS PORT (a,b: IN BIT; c: OUT BIT);

END and2; ARCHITECTURE and2_behav OF and2 IS BEGIN