EDA第9章 DSP Builder设计初步

DSP Builder系统设计工具

DSP Builder系统设计工具DSP Builder是Altera推出的一个数字信号处理(DSP)开发工具,它在Quartus Ⅱ FPGA设计环境中集成了MathWorks的Matlab和Simulink DSP开发软件。

Altera的DSP系统体系解决方案是一项具有开创性的解决方案,它将FPGA的应用领域从多通道高性能信号处理扩展到很广泛的基于主流DSP的应用,是Altera第一款基于C代码的可编程逻辑设计流程。

在Altera基于C代码的DSP设计流程中,设计者编写在Nios Ⅱ嵌入处理器上运行的C代码。

为了优化DSP算法的实现,设计者可以使用由Matlab和Simulink工具开发的专用DSP指令。

这些专用指令通过Altera的DSP Builder和SOPC Builder工具集成到可重配置的DSP设计中。

对DSP设计者而言,与以往FPGA厂商所需的传统的基于硬件描述语言(HDL)的设计相比,这种流程会更快、更容易。

除了全新的具有软件和硬件开发优势的设计流程之外,Altera DSP系统体系解决方案还引入了先进的S tratix和Stratix Ⅱ系列FPGA开发平台。

Stratix器件是Altera第一款提供嵌入式DSP块的FPGA,其中包括能够有效完成高性能DSP功能的乘法累加器(MAC)结构。

Stratix Ⅱ FPGA能够提供比Stratix器件高四倍的DSP带宽,更适合于超高性能DSP应用。

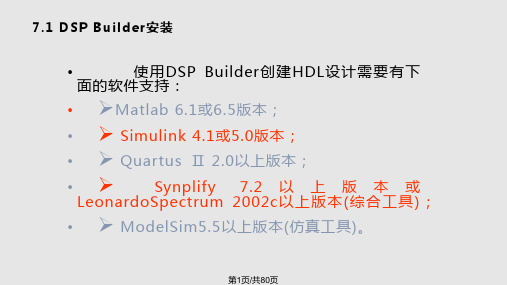

6.1 DSP Builder安装6.1.1 软件要求使用DSP Builder创建HDL设计需要有下面的软件支持:? Matlab 6.1或6.5版本;? Simulink4.1或5.0版本;? Quartus Ⅱ 2.0以上版本;? Synplify 7.2以上版本或LeonardoSpectrum 2002c以上版本(综合工具);? ModelSim5.5以上版本(仿真工具)。

6.1.2 DSP Builder软件的安装在安装DSP Builder之前,首先安装Matlab和Simulink软件以及Quartus Ⅱ软件。

DSP Builder的功能和流程

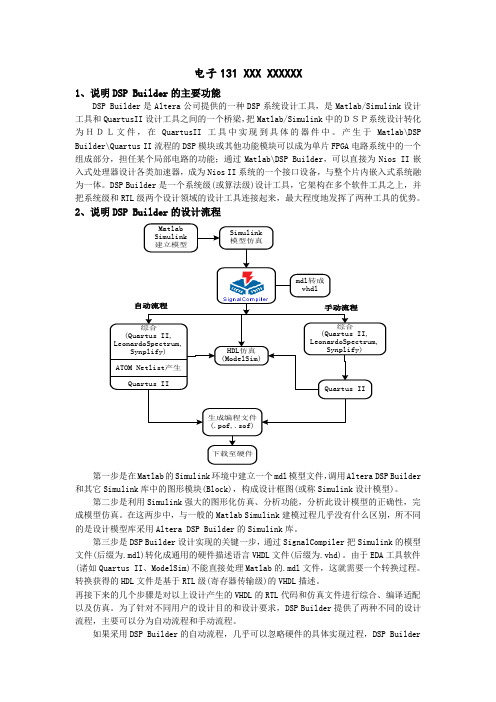

电子131 XXX XXXXXX1、说明DSP Builder 的主要功能DSP Builder 是Altera 公司提供的一种DSP 系统设计工具,是Matlab/Simulink 设计工具和QuartusII 设计工具之间的一个桥梁,把Matlab/Simulink 中的DSP系统设计转化为HDL文件,在QuartusII 工具中实现到具体的器件中。

产生于Matlab\DSP Builder\Quartus II 流程的DSP 模块或其他功能模块可以成为单片FPGA 电路系统中的一个组成部分,担任某个局部电路的功能;通过Matlab\DSP Builder ,可以直接为Nios II 嵌入式处理器设计各类加速器,成为Nios II 系统的一个接口设备,与整个片内嵌入式系统融为一体。

DSP Builder 是一个系统级(或算法级)设计工具,它架构在多个软件工具之上,并把系统级和RTL 级两个设计领域的设计工具连接起来,最大程度地发挥了两种工具的优势。

2、说明DSP Builder 的设计流程 Simulink 模型仿真综合(Quartus II,LeonardoSpectrum,Synplify)ATOM Netlist产生Quartus II HDL仿真(ModelSim)综合(Quartus II,LeonardoSpectrum,Synplify)Quartus II 生成编程文件(.pof,.sof)下载至硬件自动流程手动流程mdl转成vhdlMatlabSimulink建立模型第一步是在Matlab 的Simulink 环境中建立一个mdl 模型文件,调用Altera DSP Builder 和其它Simulink 库中的图形模块(Block),构成设计框图(或称Simulink 设计模型)。

第二步是利用Simulink 强大的图形化仿真、分析功能,分析此设计模型的正确性,完成模型仿真。

现代DSP技术课件dspbuilder设计五至九章

第5 章

LogicLock优化技术

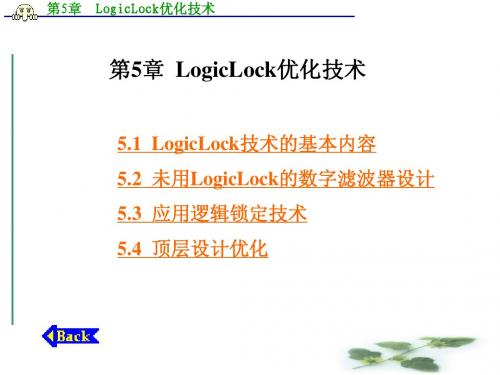

FPGA 传统设计流程 设计 LogicLock 设计流程 设计、优化 和仿真测试

模块集成 模块集成 优化

仿真测试

仿真测试

图5-1 FPGA的传统设计流程与 使用了逻辑锁定优化技术的流程的比较

第5 章

LogicLock优化技术

如上所述,在传统设计流程中常常发生的情况是,

块。

比较图5-1所示的FPGA的传统设计流程与使用了逻辑 锁定(LogiclLock Methodology)优化技术的流程可以发现,

第5 章

LogicLock优化技术

两种设计流程都是把整个设计系统分成若干个模

块(这些模块可以是一个单独的电路功能块,或是电路 中的部分元件,或是部分设计层次),在对每一模块单 独设计好后,再把它们拼起来形成一个完整的系统。 所不同的是,前者将系统中的各模块分别设计,并集 成为系统,然后对整个系统进行优化和测试;而后者 则将系统中的各模块分别设计和优化,并保持优化结 果,最后进行模块集成和系统测试。

第5 章

LogicLock优化技术

在系统适配中,虽然原设计模块的锁定区域是浮

动的,但在该区域中构成该模块的电路元件与该区域 的相对位置是不变的。因此,只要高层电路系统的适

配与原低层模块的锁定适配是在同一系列的FPGA中,

就能保证原模块的性能不变。 此外,这种保持了原特性的浮动模块的作用类似 一个已优化好的独立的电路元件,它不仅能作为原高 层设计中的一个电路模块,还能进行多模块例化(同模 块复制,或能移植到其它电路系统中)。

第5 章

LogicLock优化技术

对此,Quartus II提供了一个优秀的设计技术,即

逻辑锁定技术。使用这一技术,可以将设计好的电路 系统或某一底层模块约束到FPGA中某个指定的区域上,

DSP Builder

1.说明DSP Builder的主要功能DSP Builder在算法友好的开发环境中帮助设计人员生成DSP设计硬件表征,从而缩短了DSP设计周期。

已有的MATLAB函数和Simulink模块可以和Altera DSP Builder模块以及Altera知识产权(IP)MegaCore功能相结合,将系统级设计实现和DSP 算法开发相链接。

DSP Builder支持系统、算法和硬件设计共享一个公共开发平台。

设计人员可以使用DSP Builder模块迅速生成Simulink系统建模硬件。

DSP Builder包括比特和周期精度的Simulink模块,涵盖了算法和存储功能等基本操作。

可以使用DSP Builder模型中的MegaCore功能实现复杂功能的集成。

Altera还提供DSP Builder高级模块集,这一Simulink库实现了时序驱动的Simulink综合。

Altera MegaCore是高级参数化IP功能,例如有限冲击响应(FIR)滤波器和快速傅立叶变换(FFT)等,经过配置能够迅速方便的达到系统性能要求。

MegaCore功能支持Altera的IP评估特性,使您在购买许可之前,便可以验证功能及其时序。

Altera IP MegaStore网站上为DSP Builder和IP评估流程提供DSP IP完整介绍DSP Builder SignalCompiler模块读取由DSP Builder和MegaCore模块构建的Simulink建模文件(.mdl),生成VHDL文件和工具命令语言(Tcl)脚本,进行综合、硬件实施和仿真。

图示为DSP Builder设计流程。

DSP Builder是一个系统级(或算法级)设计工具,它构架在多个软件工具之上,并把系统级和RTL级两个设计领域的设计工具连接起来,最大程度地发挥了两种工具的优势【10】。

DSP Builder依赖于Math Works公司的数学分析工具Matlab/Simulink,以Simulink的Blockset出现,可以在Simulink中进行图形化设计和仿真,同时又通过Signal Compiler可以把Matlab/Simulink的设计文件(.mdl)转成相应的硬件描述语言VHDL设计文件(.vhd),以及用于控制综合与编译的TCL脚本。

DSP_Builder设计深入

KX

康芯科技

10.1 FIR数字滤波器设计

3、16阶FIR滤波器模型设计

xin模块:(Altbus) 库:Altera DSP Builder中IO & Bus库 参数“Bus Type”设为“signed Integer” 参数“Node Type”设为“Input port” 参数“number of bits”设为“9” yout模块:(Altbus) 库:Altera DSP Builder中IO & Bus库 参数“Bus Type”设为“signed Integer” 参数“Node Type”设为“Output port” 参数“number of bits”设为“20”

10.1.4 使用FIR IP Core设计FIR滤波器

KX

康芯科技

KX

1.3阶常数系数FIR滤波器设计

康芯科技

10.1.2 使用DSP Builder设计FIR滤波器

图10-1 3阶FIR滤波器结构

KX

康芯科技

10.1 FIR数字滤波器设计

10.1.2 使用DSP Builder设计FIR滤波器

1.3阶常数系数FIR滤波器设计 Chirp Signal模块:(Chirp Signal) 库:Simulink中Sources库 参数“Initial Frequency(Hz)”设为“0.1” 参数“Target time”设为“10” 参数“Frequency at target time(Hz)”设为“1” 参数“Interpret vectors parameters as 1-D”选中 Gain模块:(Gain) 库:Simulink中Math Operations库 参数“Gain”设为“127” 参数“Multiplication”设为“Element wise(K.*u)” Scope模块:(Scope) 库:simulink中sinks库 参数“Number of Axes”为“2”

eda第9章 dsp builder设计初步课件

Earn the fundamentals of DSP Builder through this course. Explore the basic concepts, applications, and tools of DSP Builder. Simplify and optimize your DSP designs.

概述

介绍D S P Build er的基本概念、应用领域和组成部分,帮助您构建更简化和优化的DS P设计。

DSP Builder的基本原理

使用函数分块图提高抽象层次,流水线增强资源利用率,并通过数据流图进行优化,使 D S P 设计更高效。

DSP Builder的设计流程

1

整体架构设计

确定D S P系统的整体框架和功能模块

中断控制与处理

管理系统中断的触发和处理,确保实时响应 和数据一致性。

数据流调度控制

调整数据流的处理顺序和速率,以提高系统 的吞吐量。

时序分析与优化

分析和优化系统的时序性能,避免时序冲突 和不确定性。

DSP Builder设计案例

图像处理算法设计

使用D S P Build er设计图像处理算法,实现图像 增强和图像识别。

DSP算法设计

2

的交互关系。

设计和优化D S P算法以满足实时信号

处理要求。

3

硬件IP选择与修改

选取合适的硬件IP并根据需求进行定

系统仿真与测试

4

制。

使用仿真和测试技术验证DS P系统的 功能和性能。

DSP Builder的常用功能

数据类型与格式控制

灵活处理不同类型和格式的数据,实现多样 化的Build er设计音频数据处理模块,实现 音频效果和声音识别。

DSPBuilder系统设计工具PPT课件

第21页/共80页

•4.加入正弦波产生模 块

•(1) 在Simulink Library Browser界面 点击Simulink中的 Sources库,从中找到 Sine Wave模块。

•

(3) 选择File→New→Model命令,建立

一个新的模型文件。

•

(4) 选择File→S第a16v页e/共命80页令,保存文件到指定

第17页/共80页

•2.加入SignalCompiler模块

• (1) 在Simulink Library Browser界面中,打 开Altera DSP Builder文件夹。

Quartus II

HDL仿真 (ModelSim)

生成编程文件 (.pof,.sof)

下载至硬件

第12页/共80页

mdl转成 vhdl

手动流程

综合 (Quartus II, LeonardoSpectrum,

Synplify)

Quartus II

对于DSP Builder设计,Altera提 供自动和手动两种综合、编译流程。如果 DSP Builder模型是顶层设计,则两种综 合与编译流程都可以使用;如果DSP Builder模型不是顶层设计,而是非DSP Builder硬件设计中的一个独立模块,则 只能使用手动综合、编译流程,在DSP Builder软件之外建立顶层编译设置,包

DSP Builder的调频信号发生器

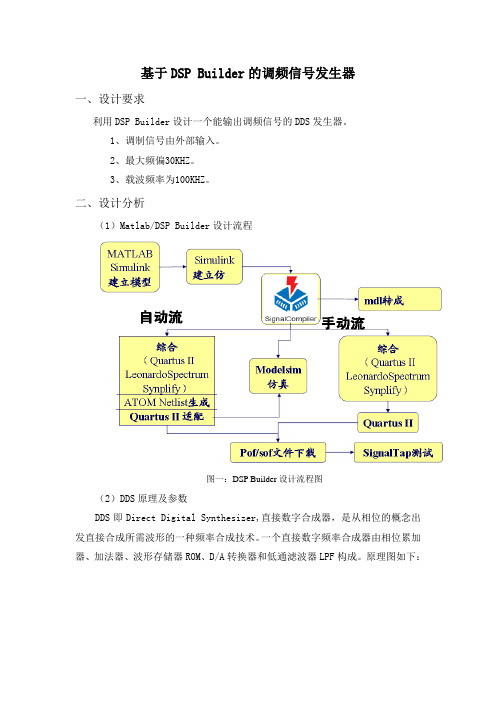

基于DSP Builder的调频信号发生器一、设计要求利用DSP Builder设计一个能输出调频信号的DDS发生器。

1、调制信号由外部输入。

2、最大频偏30KHZ。

3、载波频率为100KHZ。

二、设计分析(1)Matlab/DSP Builder设计流程图一:DSP Builder设计流程图(2)DDS原理及参数DDS即Direct Digital Synthesizer,直接数字合成器,是从相位的概念出发直接合成所需波形的一种频率合成技术。

一个直接数字频率合成器由相位累加器、加法器、波形存储器ROM、D/A转换器和低通滤波器LPF构成。

原理图如下:图二:DDS 原理框图其K 为频率控制字,P 为相位控制字、fc 为参考时钟频率,N 为相位累加器的字长,D 为ROM 数据位及D/A 转换器的字长。

相位累加器在时钟fc 的控制下以步长K 作累加,输出的N 位二进制码与相位控制字P 相加后作为波形ROM 的地址,对波形ROM 进行寻址,波形ROM 输出D 位的幅度码S (n )进D/A 转换器变成阶梯波S (t ),再经过低通滤波器平滑后就可以得到合成的信号波形。

相位寄存器每经过2N/M 个s f 时钟后回到初始状态,相应地正弦查询表经过一个循环回到初始位置,整个DDS 系统输出一个正弦波。

输出正弦波的频率计算: 0f =M 2s N f 先确定系统的分辨率f ∆,最高输出频率max f ,相位累加器位数N ,频率控制字M 。

(3)FM 调制原理设调制信号为t A t m m m ωcos )(=,载波信号为)cos()(t A t V c c ω=,则调频信号为]sin cos[)(t m t A t S m f c FM ωω+=。

三、电路设计四、Simulink仿真仿真结果如下:由上图可清楚得看到,输出信号的频率随着调制信号的变化而变化。

在调制信号的波峰处,输出信号频率达到最大值130KHZ;相应的,在调制信号的波谷处,输出信号频率为最小值70KHZ。

基于DSP Builder数字滤波器的设计与实现毕业设计

摘要数字滤波器是现代数字信号处理系统的重要组成部分之一,具有模拟滤波器所无法替代的新特性,因此在通信、语音与图像处理、自动控制等领域有着广泛的应用,它对于降低噪声、提高信噪比及信号的频谱纯度等方面有着重要的意义。

数字滤波器根据单位脉冲响应的不同,可分为FIR(有限长脉冲响应)滤波器和IIR(无限长脉冲响应)滤波器,FIR的优点在于具有良好的相位特性,IIR的优点在于具有良好的幅频特性,可以根据不同的系统性能要求选择不同的滤波器。

目前滤波器的主要实现方法有三种,分别是:单片通用数字滤波器集成电路、采用DSP器件和FPGA(现场可编程门阵列)器件。

本文采用FPGA器件来实现滤波器的设计,在实现方法上先用MATLAB/Simulink工具箱建立滤波器模型,然后用SignalCompiler把Simulink的模型文件(后缀是.mdl)转化为硬件描述语言VHDL文件,最后利用QuartusII完成滤波器的仿真、配置、编译和下载。

本文最后用实例介绍了FIR数字滤波器和IIR数字滤波器的实现过程。

关键词:数字滤波器通信集成电路 DSP FPGAAbstractDigital filter is a digital signal processing system is one of the important component, analog filters cannot be replaced by the new characteristic, therefore in the communication, speech and image processing, automatic control and other fields have a wide range of applications, it can reduce noise, improve the signal to noise ratio and signal spectrum purity has important significance. Digital filter according to unit impulse response of different, can be divided into FIR ( finite impulse response filter ) and IIR ( infinite impulse response ) filter, FIR have the advantages of good phase characteristics, IIR have the advantages of good amplitude-frequency characteristics, according to different system performance requirements of different filter. The filter main realizing methods has three kinds, respectively is: the monolithic integrated circuit, digital filter with DSP device and FPGA ( field programmable gate array ) device. This paper uses FPGA to realize filter design, the realization method on the first MA TLAB / Simulink toolbox to establish filter model, then use SignalCompiler the Simulink model file ( the suffix is . MDL ) into the VHDL hardware description language file, finally using QuartusII complete filter simulation, configure, compile and download. Finally, examples of the FIR digital filter and IIR digital filter implementation process.Keywords: digital filter communication integrated circuit DSP FPGA目录1.绪论 (1)1.1研究背景 (1)1.2研究现状 (1)1.3本课题研究内容方法 (3)2.相关知识简介 (5)2.1 数字滤波器概述 (5)2.1.1 数字滤波器的定义 (5)2.1.2 数字滤波器的分类 (6)2.1.3 FIR和IIR数字滤波器的比较 (6)2.1.4 数字滤波器的设计要求和方法 (8)2.2 设计软件简介 (9)2.3 软件安装问题 (10)3.数字滤波器的总体设计方案 (12)3.1 FIR和IIR设计方法概述 (12)3.2 滤波器设计方法比较 (12)4. FIR设计实例 (16)4.1 FIR数字滤波器原理 (16)4.2 16阶FIR滤波器 (16)5. IIR设计实例 (27)5.1 IIR数字滤波器原理 (27)5.2 使用DSP B UILDER设计IIR滤波器 (30)5.2.1 4阶直接Ⅱ型IIR滤波器设计 (30)5.2.2 4阶级联型IIR滤波器设计 (32)6.总结 (38)参考文献 (40)致谢 (41)1.绪论1.1 研究背景当今,数字信号处理(DSP:Digtal Signal Processing)技术正飞速发展,它不但自成一门学科,更是以不同形式影响和渗透到其他学科:它与国民经济息息相关,与国防建设紧密相连;它影响或改变着我们的生产、生活方式,因此受到人们普遍的关注。

现代DSP技术课件dspbuilder设计一至四章

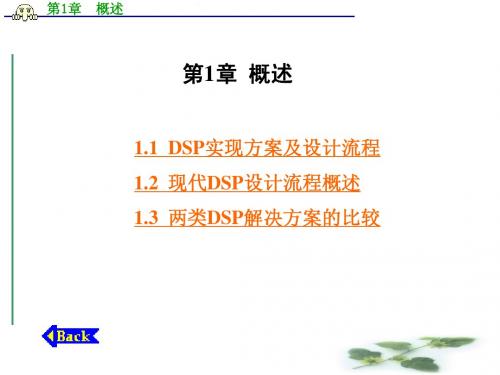

第1 章

概述

为了满足 DSP 技术领域中的各种需求以及顺应

DSP市场的发展,DSP应用系统的实现方式和目标器件 的品种类型、结构特点乃至开发技术本身都经历着不 断的改善和变革。 1.1.1 常用DSP应用器件及其性能特点 如前所述, DSP 作为数字信号的算法的实现方案 有多种,对于不同的应用领域、适用范围和指标要求, 可以选用不同的解决方案和 DSP 系统的实现器件。目

第1 章

概述

现代大容量、高速度的FPGA的出现,克服了上述 方案的诸多不足。在这些FPGA中,一般都内嵌有可配 置的高速 RAM 、 PLL 、 LVDS 、 LVTTL 以及硬件乘法 累加器等DSP模块。用FPGA来实现数字信号处理可以 很好地解决并行性和速度问题,而且其灵活的可配置 特性,使得FPGA构成的DSP系统非常易于修改、易于 测试及硬件升级。

第1 章

概述

1.1 DSP实现方案及设计流程

不断发展的数字信号处理(DSP,Digital Signal Processing)技术迅速地扩展到了其应用领域,如3 G移 动通信、网络会议、多媒体系统、雷达卫星系统、医 学仪器、实时图像识别与处理、联合战术无线电系统、 智能基站,以及民用电器等。所有这一切在功能实现、 性能指标与成本方面都在不断增加其要求。

第1 章

概述

在利用FPGA进行DSP系统的开发应用上,已有了

全新的设计工具和设计流程。DSP Builder就是Altera公 司推出的一个面向DSP开发的系统级工具。它是作为 MATLAB的一个Simulink工具箱(ToolBox)出现的。 MATLAB是功能强大的数学分析工具,广泛应用于科 学计算和工程计算,可以进行复杂的数字信号处理系 统的建模、参数估计、性能分析。Simulink是 MATLAB的一个组成部分,用于图形化建模仿真。

DspBuilder使用讲解

第9章 DDS设计

相位字输入

幅度调制

频率字输入 相位累加器 clk

相位调制器

正 弦 ROM 查找表

送 D/A

图9-3 幅度调制

第9章 DDS设计

9.2 DDS的模块设计

9.2.1 建立DDS模型 首先在Simulink中新建一个模型,调用DSP Builder模

块构成图9-4所示的基本DDS子系统SubDDS。

第9章 DDS设计

9.2.2 DDS模型的使用 在此调用上面设计的DDS子系统SubDDS,构建一个

简单的DDS应用模型,见图9-5。

第9章 DDS设计

图9-5 DDS的使用

第9章 DDS设计

输入相位字为0,频率字为2000000,幅度控制值为 124,设置Simulink的仿真停止时间Stop Time为5,仿 真步进Fixed Step Size设为1e-3。

第9章 DDS设计

由 Delay 模 块 和 Parallel Adder Subtractor 模 块 以 及 Phaseword1模块构成相位累加器,其参数如下:

Parallel Adder Subtractor模块:(Parallel Adder Subtractor) 库:Altera DSP Builder中Arithmetic库 参数“Number of Inputs”设为“2”,“Add(+)Sub(-)”设为

第9章 DDS设计

数据线位宽

相 位 字 输 入同 步 寄存器

N

频 率 字 输 入同 步 N 寄存器

clk 系统时钟

N

M

M

寄存器

相位调制器 相位累加器

正 弦 ROM 查找表

正弦信号输出 D/A

dsp builder 使用方法

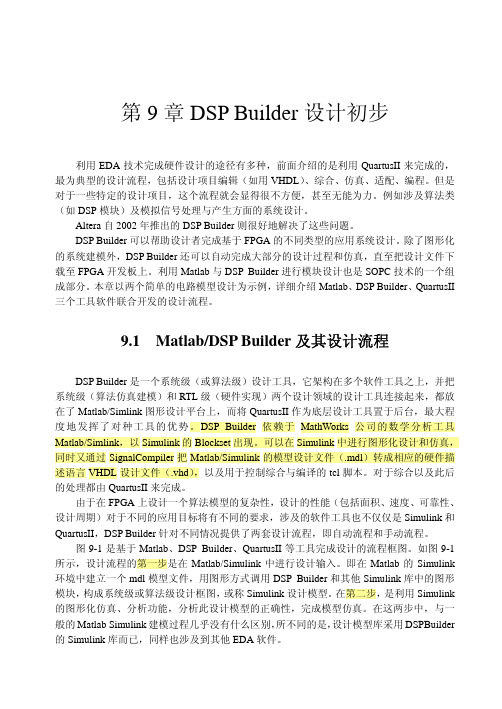

第9章DSP Builder设计初步利用EDA技术完成硬件设计的途径有多种,前面介绍的是利用QuartusII来完成的,最为典型的设计流程,包括设计项目编辑(如用VHDL)、综合、仿真、适配、编程。

但是对于一些特定的设计项目,这个流程就会显得很不方便,甚至无能为力。

例如涉及算法类(如DSP模块)及模拟信号处理与产生方面的系统设计。

Altera自2002年推出的DSP Builder则很好地解决了这些问题。

DSP Builder可以帮助设计者完成基于FPGA的不同类型的应用系统设计。

除了图形化的系统建模外,DSP Builder还可以自动完成大部分的设计过程和仿真,直至把设计文件下载至FPGA开发板上。

利用Matlab与DSP Builder进行模块设计也是SOPC技术的一个组成部分。

本章以两个简单的电路模型设计为示例,详细介绍Matlab、DSP Builder、QuartusII 三个工具软件联合开发的设计流程。

9.1 Matlab/DSP Builder及其设计流程DSP Builder是一个系统级(或算法级)设计工具,它架构在多个软件工具之上,并把系统级(算法仿真建模)和RTL级(硬件实现)两个设计领域的设计工具连接起来,都放在了Matlab/Simlink图形设计平台上,而将QuartusII作为底层设计工具置于后台,最大程度地发挥了对种工具的优势。

DSP Builder依赖于MathWorks公司的数学分析工具Matlab/Simlink,以Simulink的Blockset出现。

可以在Simulink中进行图形化设计和仿真,同时又通过SignalCompiler把Matlab/Simulink的模型设计文件(.mdl)转成相应的硬件描述语言VHDL设计文件(.vhd),以及用于控制综合与编译的tcl脚本。

对于综合以及此后的处理都由QuartusII来完成。

由于在FPGA上设计一个算法模型的复杂性,设计的性能(包括面积、速度、可靠性、设计周期)对于不同的应用目标将有不同的要求,涉及的软件工具也不仅仅是Simulink和QuartusII,DSP Builder针对不同情况提供了两套设计流程,即自动流程和手动流程。

EDA第9章 DSP Builder设计初步

Amp模块:(Altbus) 库:Altera DSP Builder中IO & Bus库 参数“Bus Type”设为“signed Integer” 参数“Node Type”设为“Input port” 参数“number of bits”设为“10”

DDSout模块:(Altbus) 库:Altera DSP Builder中IO & Bus库 参数“Bus Type”设为“signed Integer” 参数“Node Type”设为“Output port” 参数“number of bits”设为“10”

KX

康芯科技

9.2 正弦信号发生器设计

10、放置端口SinCtrl

图9-13 设置SinCtrl

KX

康芯科技

9.2 正弦信号发生器设计

11、放置Product模块

图9-14 设置乘法单元

KX

康芯科技

9.2 正弦信号发生器设计

12. 放置输出端口SinOut

图9-15 设置SinOut

13. 设计文件存盘

Phaseword模块:(Altbus) 库:Altera DSP Builder中IO & Bus库 参数“Bus Type”设为“signed Integer” 参数“Node Type”设为“Input port” 参数“number of bits”设为“32”

KX

康芯科技பைடு நூலகம்

9.4 基于DSP Builder的DDS设计

综合 (Quartus II, LeonardoSpectrum, Synplify)

Quartus II

生成编程文件 (.pof,.sof)

第9章 DSP Builder设计初步

K 康芯科技 X

图9-43 打开QuartusII工程的vec仿真激励文件

9.2 正弦信号发生器设计

9.2.5使用QuartusII实现时序仿真

K 康芯科技 X

图9-44设置仿真文件路径

9.2 正弦信号发生器设计

9.2.5使用QuartusII实现时序仿真

K 康芯科技 X

图9-54 Scope波形图

9.3 DSP Builder层次化设计

9.2.5使用QuartusII实现时序仿真

K 康芯科技 X

图9-55 SubSystem设置

9.3 DSP Builder层次化设计

9.2.5使用QuartusII实现时序仿真

K 康芯科技 X

图9-56 编辑singen的“Mask type”

K 康芯科技 X

EDA技术与VHDL 第9章

DSP Builder设计初步

K 康芯科技 X

9.1 Matlab/DSP Builder及其设计流程

Matlab Simulink 建立模型

Simulink 模型仿真

自动流程

综合 (Quartus II, LeonardoSpectrum,

Synplify)

K 康芯科技 X

9.1 Matlab/DSP Builder及其设计流程

自动流程: 1、MATLAB/Simulink建模; 2、系统仿真; 3、DSP Builder完成VHDL转换、综合、适配、下载; 4、嵌入式逻辑分析仪实时测试。

手动流程: 1、MATLAB/Simulink建模; 2、系统仿真; 3、DSP Builder完成VHDL转换、综合、适配; 4、Modelsim对TestBench功能仿真; 5、QuartusII直接完成适配(进行优化设置); 6、QuartusII完成时序仿真; 7、引脚锁定; 8、下载/配置与嵌入式逻辑分析仪等实时测试; 9、对配置器件编程,设计完成。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

康芯科技

EDA技术与VHDL

第9章 DSP Builder设计初步

KX

康芯科技

9.1 Matlab/DSP Builder及其设计流程

Matlab Simulink 建立模型 Simulink 模型仿真

mdl转 成 vhdl 自动流程

手动流程

综合 (Quartus II, LeonardoSpectrum, Synplify) ATOM Netlist产 生 Quartus II HDL仿 真 (ModelSim)

自动流程: 1、MATLAB/Simulink建模; 2、系统仿真; 3、DSP Builder完成VHDL转换、综合、适配、下载; 4、嵌入式逻辑分析仪实时测试。

手动流程: 1、MATLAB/Simulink建模; 2、系统仿真; 3、DSP Builder完成VHDL转换、综合、适配; 4、Modelsim对TestBench功能仿真; 5、QuartusII直接完成适配(进行优化设置); 6、QuartusII完成时序仿真; 7、引脚锁定; 8、下载/配置与嵌入式逻辑分析仪等实时测试; 9、对配置器件编程,设计完成。

综合 (Quartus II, LeonardoSpectrum, Synplify)

Quartus II

生成编程文件 (.pof,.sof)

下载至硬件

图9-1 基于Matlab、DSP Builder、 QuartusII等工具

KX

康芯科技

9.1 Matlab/DSP Builder及其设计流程

9.4.1 DDS模块设计

图9-57 DDS系统

KX

康芯科技

9.4 基于DSP Builder的DDS设计

9.4.1 DDS模块设计

图9-58 DDS子系统SubDDS

KX

康芯科技

9.4 基于DSP Builder的DDS设计

9.4.1 DDS模块设计

Freqword模块:(Altbus) 库:Altera DSP Builder中IO & Bus库 参数“Bus Type”设为“signed Integer” 参数“Node Type”设为“Input port” 参数“number of bits”设为“32”

KX

康芯科技

9.2 正弦信号发生器设计

9.2.2 Simulink模型仿真

1、加入仿真步进模块

图9-16 Step模块

KX

康芯科技

9.2 正弦信号发生器设计

9.2.2 Simulink模型仿真

2、添加波形观察模块

图9-17 Scope模型

KX

康芯科技

9.2 正弦信号发生器设计

2、添加波形观察模块

KX

康芯科技

9.2 正弦信号发生器设计

10、放置端口SinCtrl

图9-13 设置SinCtrl

KX

康芯科技

9.2 正弦信号发生器设计

11、放置Product模块

图9-14 设置乘法单元

KX

康芯科技

9.2 正弦信号发生器设计

12. 放置输出端口SinOut

图9-15 设置SinOut

13. 设计文件存盘

9.2 正弦信号发生器设计

4、设置仿真激励

图9-22 simulink仿真Start

KX

康芯科技

9.2 正弦信号发生器设计

5、启动仿真

图9-23 simulink仿真设置

KX

康芯科技

9.2 正弦信号发生器设计

5、启动仿真

图9-24 有符号输出波形(系统级仿真 )

KX

康芯科技

9.2 正弦信号发生器设计

9.2.5使用QuartusII实现时序仿真

图9-43 打开QuartusII工程的vec仿真激励文件

KX

康芯科技

9.2 正弦信号发生器设计

9.2.5使用QuartusII实现时序仿真

图9-44设置仿真文件路径

KX

康芯科技

9.2 正弦信号发生器设计

9.2.5使用QuartusII实现时序仿真

图9-45 sinout工程的QuartusII仿真波形(门级时序仿真)

9.2 正弦信号发生器设计

2、设置Signal Compiler

图9-34 打开SignalCompiler窗口

KX

康芯科技

9.2 正弦信号发生器设计

3、把模型文件 MDL转换成 VHDL 4、综合 (Synthesis)

5、QuartusII适 配

图9-35 sinout工程 处理信息

KX

康芯科技

图9-18 Scope初始显示

KX

康芯科技

9.2 正弦信号发生器设计

3、Scope参数设置

图9-19 设置Scope参数

KX

康芯科技

9.2 正弦信号发生器设计

3、Scope参数设置

图9-20 sinout全图

KX

康芯科技

9.2 正弦信号发生器设计

4、设置仿真激励

图9-21 设置Step

KX

康芯科技

图9-52 含subsystem的subsint模型

KX

康芯科技

9.3 DSP Builder层次化设计

9.2.5使用QuartusII实现时序仿真

图9-53 Scope1波形图

KX

康芯科技

9.3 DSP Builder层次化设计

9.2.5使用QuartusII实现时序仿真

图9-54 Scope波形图

KX

康芯科技

9.2 正弦信号发生器设计

图9-2 正弦波发生模块原理图

KX

康芯科技

9.2 正弦信号发生器设计

9.2.1 建立设计模型

1、打开Matlab环境

图9-2 正弦波发生模块原理图

KX

康芯科技

9.2 正弦信号发生器设计

9.2.1 建立设计模型

2、建立工作库 cd e:/ mkdir /myprj/sinwave cd /myprj/sinwave

9.2 正弦信号发生器设计

9.2.4 使用ModelSim进行RTL级仿真

图9-36 准备执行tcl文件

KX

康芯科技

9.2 正弦信号发生器设计

9.2.4 使用ModelSim进行RTL级仿真

图9-37 ModelSim仿真 结果

KX

康芯科技

9.2 正弦信号发生器设计

9.2.4 使用ModelSim进行RTL级仿真

KX

康芯科技

9.3 DSP Builder层次化设计

9.2.5使用QuartusII实现时序仿真

图9-55 SubSystem设置

KX

康芯科技

9.3 DSP Builder层次化设计

9.2.5使用QuartusII实现时序仿真

图9-56 编辑singen的“Mask type”

KX

康芯科技

9.4 基于DSP Builder的DDS设计

9-3

KX

康芯科技

9.2 正弦信号发生器设计

8、放置正弦查找表(SinLUT)

图9-11 设置SinLUT

KX

康芯科技

9.2 正弦信号发生器设计

9、放置Delay模块

图9-12 Delay模块及其参数设置窗

KX

康芯科技

9.2 正弦信号发生器设计

10、放置端口SinCtrl

图9-13 设置SinCtrl

5、启动仿真

图9-25 无符号输出波形(系统级仿真)

KX

康芯科技

9.2 正弦信号发生器设计

6、设计成无符号数据输出

图9-26 无符号整数Signed Integer输出电路

KX

康芯科技

9.2 正弦信号发生器设计

7、各模块功能说明

图9-27 SinOut1模块设置

KX

康芯科技

9.2 正弦信号发生器设计

KX

康芯科技

9.2 正弦信号发生器设计

图9-7 放置SignalCompiler

KX

康芯科技

9.2 正弦信号发生器设计

7. 设置IncCount

图9-8 递增递减模块改名为IncCount

KX

康芯科技

9.2 正弦信号发生器设计

7. 设置IncCount

图9-9 设置递增递减模块

KX

康芯科技

9.2 正弦信号发生器设计

KX

康芯科技

9.2 正弦信号发生器设计

3、了解simulink库管理器

图9-2 正弦波发生模块原理图

KX

康芯科技

9.2 正弦信号发生器设计

3、了解simulink库管理器

图9-5 simulink库 管理器

KX

康芯科技

9.2 正弦信号发生器设计

4. simulink的模型文件

图9-6 建立新模型

康芯科技

9.3 DSP Builder层次化设计

9.2.5使用QuartusII实现时序仿真

图9-48 subsin/subsystem子系统图

KX

康芯科技

9.3 DSP Builder层次化设计

9.2.5使用QuartusII实现时序仿真

图9-49 修改子系统名

KX

康芯科技

9.3 DSP Builder层次化设计

KX

康芯科技

9.2 正弦信号发生器设计

5、放置SignalCompilder 6、放置Increment Decrement 7. 设置IncCount

总线类型(Bus Type); 输出位宽(Number of bits); 增减方向(Direction); 开始值(Starting Value); 是否使用控制输入(Use Control Inputs) 时钟相位选择(Clock Phase Selection)