IRF710-713中文资料

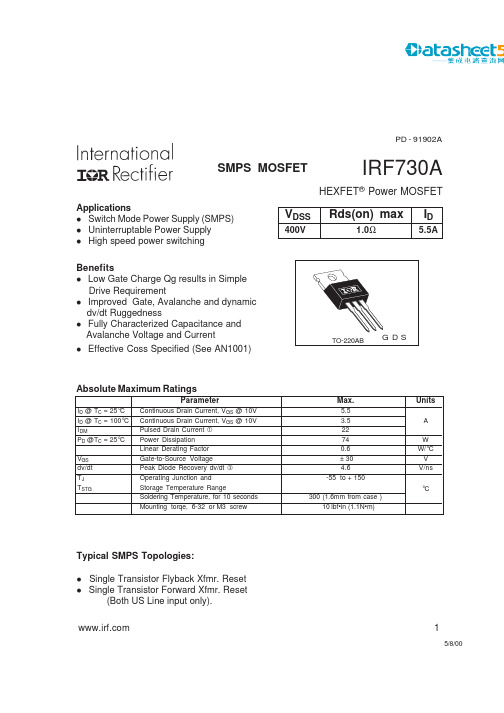

IRF730

VDSS

400V

Rds(on) max

1.0Ω

ID

5.5A

TO-220AB

G DS

Absolute Maximum Ratings

Parameter

ID @ TC = 25°C ID @ TC = 100°C IDM PD @TC = 25°C VGS dv/dt TJ TSTG Continuous Drain Current, VGS @ 10V Continuous Drain Current, VGS @ 10V Pulsed Drain Current Power Dissipation Linear Derating Factor Gate-to-Source Voltage Peak Diode Recovery dv/dt Operating Junction and Storage Temperature Range Soldering Temperature, for 10 seconds Mounting torqe, 6-32 or M3 screw

QG , Total Gate Charge (nC)

Fig 5. Typical Capacitance Vs. Drain-to-Source Voltage

Fig 6. Typical Gate Charge Vs. Gate-to-Source Voltage

100

100

OPERATION IN THIS AREA LIMITED BY RDS(on)

16

VDS = 320V VDS = 200V VDS = 80V

C, Capacitance(pF)

1000

Ciss Coss

12

3位半数字表头芯片ICL7107中文资料

3位半数字表头芯片I C L7107中文资料(总5页)--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--3位半数字表头芯片I C L7107中文资料(1)31/2位双积分型A/D转换器I C L7107功能与特点①I C L7107是31/2位双积分型A/D转换器,属于C M o S大规模集成电路,它的最大显示值为士1999,最小分辨率为100u V,转换精度为士1个字。

②能直接驱动共阳极L E D数码管,不需要另加驱动器件,使整机线路简化,采用士5V两组电源供电,并将第21脚的G N D接第30脚的I N。

③在芯片内部从V+与C O M之间有一个稳定性很高的基准电源,通过电阻分压器可获得所需的基准电压V R E F。

④能通过内部的模拟开关实现自动调零和自动极性显示功能。

⑤输入阻抗高,对输入信号无衰减作用。

⑥整机组装方便,无需外加有源器件,配上电阻、电容和L E D共阳极数码管,就能构成一只直流数字电压表头。

⑦噪音低,温漂小,具有良好的可靠性,寿命长。

⑧芯片本身功耗小于15m w(不包括L E D)。

⑨不设有一专门的小数点驱动信号。

使用时可将L E D共阳极数数码管公共阳极接V+.⑩可以方便的进行功能检查。

图1I C L7107的引脚图及典型电路。

(2)I C L7107引脚功能及主要电气参数V+和V-分别为电源的正极和负极,a u-g u,a T-g T,a H-g H:分别为个位、十位、百位笔画的驱动信号,依次接个位、十位、百位L E D显示器的相应笔画电极。

B c k:千位笔画驱动信号。

接千位L E O显示器的相应的笔画电极。

P M:液晶显示器背面公共电极的驱动端,简称背电极。

O s c l -O S c 3 :时钟振荡器的引出端,外接阻容或石英晶体组成的振荡器。

第38脚至第40脚电容量的选择是根据下列公式来决定:F o s l = R CC O M :模拟信号公共端,简称“模拟地”,使 用时一般与输入信号的负端以及基准电压的负极相连。

ICL7107在数显稳压电源中的应用(多款LM317应用电路方案)

ICL7107在数显稳压电源中的应用(多款LM317应用电路方案)描述一、数显稳压电源原理元件参数:B:220V/25V、150WD0:50V、6A全桥C1:4700μF/50VC2:0.1μFR1:1KLED1:普通发光管D1、D2:1N4001D3:1N4007R2:240ΩR3:4.7KV1:2N3055R4:200Ω、5WD4:1N4001原理图见图1。

220V交流电经变压器变压、整流、滤波后变为30V直流电压,再经LM317三端可调稳压器使电压处于1.25~30V 间某一值,经D3、V1后,电压变为0.05~28.8V间某值;其中R1为LED1限流电阻。

D1、D2用来保护LM317。

V1为2N3055,是功率用低频大功率三极管,最大电流为15A,最大功率115W,最大输入电压60V,工作温度为20℃~70℃。

数字显示电路采用外围元件极少的CMOS集成电路ICL7107为核心元件。

二、ICL7107介绍ICL7107内部结构及工作原理ICL7107工作支持元件最少为5个电容器、4个电阻器、1个电位器以及显示器,加上±5V电源,ICL7107就变成一个完整的3位半数字电压表。

ICL7107内部包括模拟电路和数字电路两大部分,二者是互相联系的。

ICL7107用双积分的方法实现A/D转换。

一方面由控制逻辑产生控制信号,按规定时序将多路模拟开关接通或断开,保证A/D转换正常进行;另一方面模拟电路中的比较器输出信号又控制着数字电路的工作状态和显示结果,如图2所示。

为了使ICL7107电路正常工作,还必须正确选择外部条件。

1.积分电阻RINT。

为保证ICL7107在输入电压范围内线性工作,外接的积分电阻要选择得足够大,可由式RINT=VFS/IINT决定VFS为满度电压(即200mV),IINT为积分电流(一般为4μA),故这里选RINT为50KΩ左右。

2.积分电容CINT。

CINT的取值主要决定于A/D转换器的额定转换速率和积分器额定积分电流,以积分输出不饱和为原则。

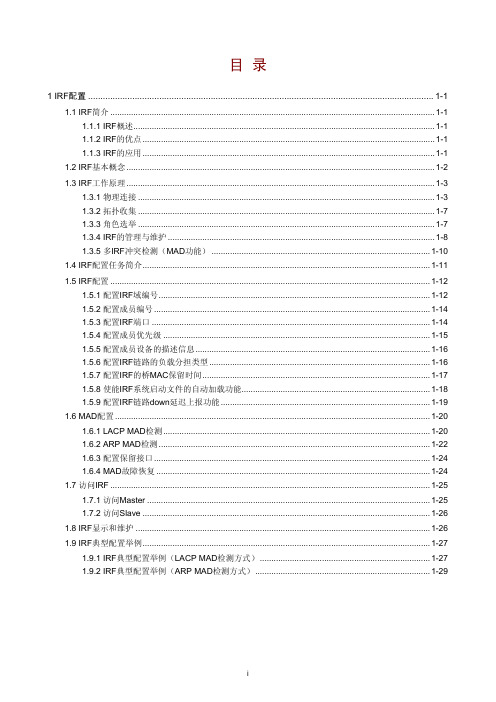

h3c-IRF配置指导-整本手册

4.图标约定 本书使用的图标及其含义如下:

该图标及其相关描述文字代表一般网络设备,如路由器、交换机、防火墙等。

该图标及其相关描述文字代表一般意义下的路由器,以及其他运行了路由协议的设备。

该图标及其相关描述文字代表二、三层交换机,以及运行了二层协议的设备。

资料获取方式

您可以通过 H3C 网站()获取最新的产品资料: H3C 网站与产品资料相关的主要栏目介绍如下: z [服务支持/文档中心]:可以获取硬件安装类、软件配置或维护类等产品资料。

Copyright © 2011 杭州华三通信技术有限公司及其许可者 版权所有,保留一切权利。

未经本公司书面许可,任何单位和个人不得擅自摘抄、复制本书内容的部分或全部,并不得以任何 形式传播。

H3C、

、Aolynk、

、H3Care、

、TOP G、

、IRF、NetPilot、Neocean、

NeoVTL、SecPro、SecPoint、SecEngine、SecPath、Comware、Secware、Storware、NQA、

意义 命令行关键字(命令中保持不变、必须照输的部分)采用加粗字体表示。 命令行参数(命令中必须由实际值进行替代的部分)采用斜体表示。 表示用“[ ]”括起来的部分在命令配置时是可选的。 表示从两个或多个选项中选取一个。 表示从两个或多个选项中选取一个或者不选。

格式 { x | y | ... } * [ x | y | ... ] * &<1-n> #

3.各类标志 本书还采用各种醒目标志来表示在操作过程中应该特别注意的地方,这些标志的意义如下:

该标志后的注释需给予格外关注,不当的操作可能会对人身造成伤害。 提醒操作中应注意的事项,不当的操作可能会导致数据丢失或者设备损坏。 为确保设备配置成功或者正常工作而需要特别关注的操作或信息。 对操作内容的描述进行必要的补充和说明。 配置、操作、或使用设备的技巧、小窍门。

常用晶体管3极管资料大全

* * * * * * * * * * 特征频率 * * * * * * * * * * * * * *

PMOS 场效应 NMOS 场效应 NMOS 场效应 NMOS 场效应 NMOS 场效应 NMOS 场效应 NMOS 场效应 NMOS 场效应 NMOS 场效应 NMOS 场效应 管子类型 NMOS 场效应 NMOS 场效应 NMOS 场效应 NMOS 场效应 NMOS 场效应 NMOS 场效应 NMOS 场效应 NMOS 场效应 NMOS 场效应 NMOS 场效应 NMOS 场效应 NMOS 场效应 PMOS 场效应 PMOS 场效应

2SC4429 2SC4297 2SC4288 2SC4242 2SC4231 2SC4119 2SC4111 2SC4106 晶体管型号 2SC4059 2SC4038 2SC4024 2SC3998 2SC3997 2SC3987 2SC3953 2SC3907 2SC3893 2SC3886 2SC3873 2SC3866 2SC3858 2SC3807 2SC3783 晶体管型号

PNP NPN NPN 反压 Vbe0 60V 40V 160V 50V 30V 120V 45V 80V 300V 300V 50V 50V 150V 60V 20V 反压 Vbe0

160 180 30 电流 Icm 5A 0.2A 1A 0.1A 0.26A 3A 1A 4A 0.1A 0.2A 0.15A 0.1A 2A 0.015A 电流 Icm

1200V 900V 900V 30V 500V 900V 1100V 1100V 20V 20V 500V 500V 100V 20V 300V 反压 Vbe0 36V 60V 35V 80V 30V 45V 60V 35V 60V

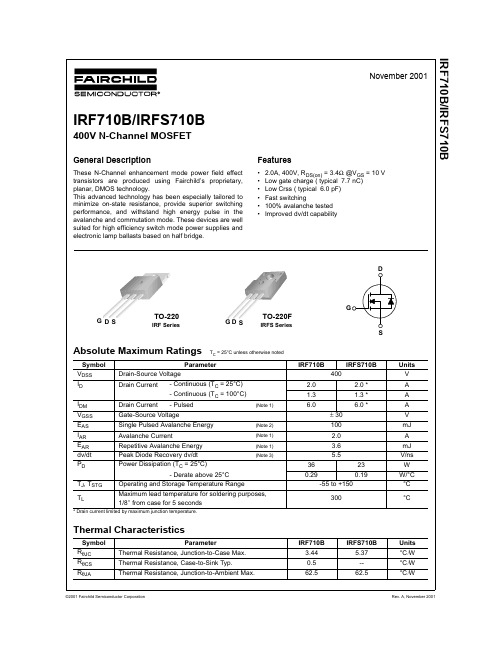

IRF710B中文资料

--

--

1.5

V

trr

Reverse Recovery Time

Qrr

Reverse Recovery Charge

VGS = 0 V, IS = 2.0 A,

-- 210

--

ns

dIF / dt = 100 A/µs

(Note 4)

--

0.9

--

µC

Notes:

1. Repetitive Rating : Pulse width limited by maximum junction temperature 2. L = 44mH, IAS = 2.0A, VDD = 50V, RG = 25 Ω, Starting TJ = 25°C 3. ISD ≤ 2.0A, di/dt ≤ 300A/µs, VDD ≤ BVDSS, Starting TJ = 25°C 4. Pulse Test : Pulse width ≤ 300µs, Duty cycle ≤ 2% 5. Essentially independent of operating temperature

12 10 8 6 4 2 0

0.0

V = 80V DS

V = 200V DS

V = 320V DS

※ Note : I = 2.0 A D

Features

• 2.0A, 400V, RDS(on) = 3.4Ω @VGS = 10 V • Low gate charge ( typical 7.7 nC) • Low Crss ( typical 6.0 pF) • Fast switching • 100% avalanche tested • Improved dv/dt capability

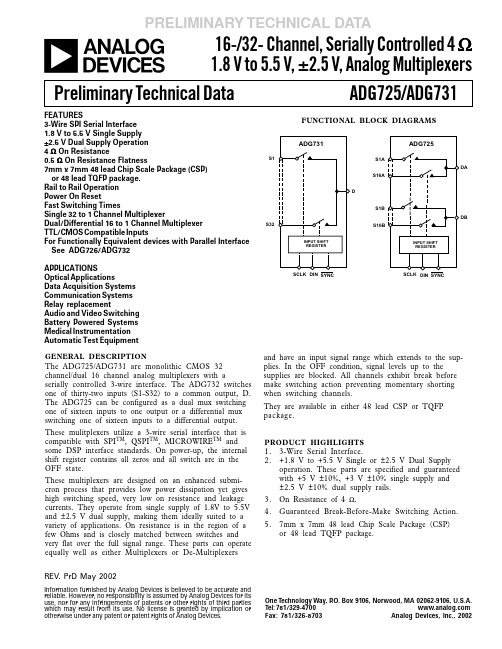

ADG731中文资料

ADG725/ADG731 =REV. PrD May 2002Information furnished by Analog Devices is believed to be accurate andreliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.One T echnology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. T el: 781/ Fax: 781/326-8703Analog Devices, Inc., 200216-/32- Channel, Serially Controlled 4 Ω1.8 V to 5.5 V, ±2.5 V, Analog Multiplexers Preliminary Technical DataPRELIMINARY TECHNICAL DATAFEATURES3-Wire SPI Serial Interface1.8 V to 5.5 V Single Supply±2.5 V Dual Supply Operation4 Ω On Resistance0.5 Ω On Resistance Flatness7mm x 7mm 48 lead Chip Scale Package (CSP)or 48 lead TQFP package.Rail to Rail OperationPower On ResetFast Switching TimesSingle 32 to 1 Channel MultiplexerDual/Differential 16 to 1 Channel MultiplexerTTL/CMOS Compatible InputsFor Functionally Equivalent devices with Parallel InterfaceSee ADG726/ADG732APPLICATIONSOptical ApplicationsData Acquisition SystemsCommunication SystemsRelay replacementAudio and Video SwitchingBattery Powered SystemsMedical InstrumentationAutomatic Test EquipmentGENERAL DESCRIPTIONThe ADG725/ADG731 are monolithic CMOS 32channel/dual 16 channel analog multiplexers with aserially controlled 3-wire interface. The ADG732 switchesone of thirty-two inputs (S1-S32) to a common output, D.The ADG725 can be configured as a dual mux switchingone of sixteen inputs to one output or a differential muxswitching one of sixteen inputs to a differential output.These mulitplexers utilize a 3-wire serial interface that iscompatible with SPI TM, QSPI TM, MICROWIRE TM and some DSP interface standards. On power-up, the internal shift register contains all zeros and all switch are in the OFF state.These multiplexers are designed on an enhanced submi-cron process that provides low power dissipation yet gives high switching speed, very low on resistance and leakage currents. They operate from single supply of 1.8V to 5.5V and ±2.5 V dual supply, making them ideally suited to a variety of applications. On resistance is in the region of a few Ohms and is closely matched between switches and very flat over the full signal range. These parts can operate equally well as either Multiplexers or De-Multiplexers PRODUCT HIGHLIGHTS1.3-Wire Serial Interface.2.+1.8 V to +5.5 V Single or ±2.5 V Dual Supplyoperation. These parts are specified and guaranteedwith +5 V ±10%, +3 V ±10% single supply and±2.5 V ±10% dual supply rails.3.On Resistance of 4 Ω.4.Guaranteed Break-Before-Make Switching Action.5.7mm x 7mm 48 lead Chip Scale Package (CSP)or 48 lead TQFP package.FUNCTIONAL BLOCK DIAGRAMSS1S32SCLK DIN SYNCDS1ADAS16AS1BS16BDBSCLK DIN SYNCand have an input signal range which extends to the sup-plies. In the OFF condition, signal levels up to the supplies are blocked. All channels exhibit break before make switching action preventing momentary shorting when switching channels.They are available in either 48 lead CSP or TQFP package.元器件交易网–2–REV. PrDADG725/ADG731–SPECIFICATIONS 1PRELIMINARY TECHNICAL DATAB Version–40°CParameter+25o C to +85°C Units Test Conditions/Comments ANALOG SWITCH Analog Signal Range 0 V to V DD V On-Resistance (R ON )4Ω typ V S = 0 V to V DD , I DS = 10 mA;5.56Ω max Test Circuit 1On-Resistance Match Between 0.3Ω typ V S = 0 V to V DD , I DS = 10 mA Channels (∆R ON )0.8Ω max On-Resistance Flatness (R FLAT(ON))0.5Ω typ V S = 0 V to V DD , I DS = 10 mA 1Ω max LEAKAGE CURRENTSV DD = 5.5 VSource OFF Leakage I S (OFF)±0.01nA typ V D = 4.5 V/1 V, V S = 1 V/4.5 V;±0.25±0.5nA max Test Circuit 2Drain OFF Leakage I D (OFF)±0.05nA typ V D = 4.5 V/1 V, V S = 1 V/4.5 V; ADG725±0.5±2.5nA max Test Circuit 3ADG731±1±5nA max Channel ON Leakage I D , I S (ON)±0.05nA typ V D = V S = 1 V, or 4.5V; ADG725±0.5±2.5nA max Test Circuit 4ADG726±1±5nA max DIGITAL INPUTSInput High Voltage, V INH 2.4V min Input Low Voltage, V INL 0.8V max Input Current I INL or I INH 0.005µA typ V IN = V INL or V INH±0.1µA max C IN , Digital Input Capacitance 5pF typ DYNAMIC CHARACTERISTICS 2t TRANSITION 40ns typ R L = 300 Ω, C L = 35 pF,Test Circuit 5;60ns max V S1 = 3 V/0 V, V S32 = 0 V/3V Break-Before-Make Time Delay, t D 30ns typ R L = 300 Ω, C L = 35 pF;1ns min V S = 3 V, Test Circuit 6Charge Injection ±5pC typ V S = 0 V, R S = 0 Ω, C L = 1 nF;Test Circuit 7Off Isolation-60dB typ R L = 50 Ω, C L = 5 pF, f = 100 kHz;Test Circuit 8Channel to Channel Crosstalk -60dB typ R L = 50 Ω, C L = 5 pF, f = 100 kHz;Test Circuit 9-3 dB Bandwidth ADG72534MHz typ R L = 50 Ω, C L = 5 pF, Test Circuit 10 ADG73118MHz typ C S (OFF)13pF typ f = 1 MHz C D (OFF) ADG725180pF typ f = 1 MHz ADG731360pF typ f = 1 MHz C D , C S (ON) ADG725200pF typ f = 1 MHz ADG731400pF typ f = 1 MHzPOWER REQUIREMENTS V DD = +5.5 VI DD10µA typ Digital Inputs = 0 V or +5.5 V20µA maxNOTES 1Temperature range is as follows: B Version: –40°C to +85°C.2Guaranteed by design, not subject to production test.Specifications subject to change without notice.(V DD= 5V ± 10%, V SS= 0V, GND = 0 V, unless otherwise noted)元器件交易网–3–REV. PrD ADG725/ADG731PRELIMINARY TECHNICAL DATAB Version–40°CParameter+25o C to +85°CUnits Test Conditions/Comments ANALOG SWITCH Analog Signal Range 0 V to V DD V On-Resistance (R ON )7Ω typ V S = 0 V to V DD , I DS = 10 mA;1112Ω max Test Circuit 1On-Resistance Match Between 0.4Ω typ V S = 0 V to V DD , I DS = 10 mA Channels (∆R ON )1Ω max On-Resistance Flatness (R FLAT(ON))3Ω max V S = 0 V to V DD , I DS = 10 mA LEAKAGE CURRENTSV DD = 3.3 VSource OFF Leakage I S (OFF)±0.01nA typ V S = 3 V/1 V, V D = 1 V/3 V;±0.25±0.5nA max Test Circuit 2Drain OFF Leakage I D (OFF)±0.05nA typ V S = 1 V/3 V, V D = 3 V/1 V; ADG725±0.5±2.5nA max Test Circuit 3ADG731±1±5nA max Channel ON Leakage I D , I S (ON)±0.05nA typ V S = V D = +1 V or +3 V; ADG725±0.5±2.5nA max Test Circuit 4ADG731±1±5nA max DIGITAL INPUTSInput High Voltage, V INH 2.0V min Input Low Voltage, V INL 0.8V max Input Current I INL or I INH 0.005µA typ V IN = V INL or V INH±0.1µA max C IN , Digital Input Capacitance 5pF typ DYNAMIC CHARACTERISTICS 2t TRANSITION 45ns typ R L = 300 Ω, C L = 35 pF Test Circuit 575ns max V S1 = 2 V/0 V, V S32 = 0 V/2 V Break-Before-Make Time Delay, t D 30ns typ R L = 300 Ω, C L = 35 pF;1ns min V S = 2 V,Test Circuit 6Charge Injection ±5pC typ V S = 0 V, R S = 0 Ω, C L = 1 nF;Test Circuit 7Off Isolation-60dB typ R L = 50 Ω, C L = 5 pF, f = 1 MHz;Test Circuit 8Channel to Channel Crosstalk -60dB typ R L = 50 Ω, C L = 5 pF, f = 1 MHz;Test Circuit 9-3 dB Bandwidth ADG72534MHz typ R L = 50 Ω, C L = 5 pF, Test Circuit 10 ADG73118MHz typ C S (OFF)13pF typ f = 1 MHz C D (OFF) ADG725180pF typ f = 1 MHz ADG731360pF typ f = 1 MHz C D , C S (ON) ADG725200pF typ f = 1 MHz ADG731400pF typ f = 1 MHzPOWER REQUIREMENTS V DD = +3.3 VI DD10µA typ Digital Inputs = 0 V or +3.3 V20µA maxNOTES 1Temperature ranges are as follows: B Version: –40°C to +85°C.2Guaranteed by design, not subject to production test.Specifications subject to change without notice.(V DD = 3V ± 10%, V SS = 0V, GND = 0 V, unless otherwise noted)SPECIFICATIONS1元器件交易网–4–REV. PrDADG725/ADG731–SPECIFICATIONS 1PRELIMINARY TECHNICAL DATAB Version–40°CParameter+25o C to +85°C Units Test Conditions/Comments ANALOG SWITCHAnalog Signal Range V SS to V DD V On-Resistance (R ON )4Ω typ V S = V SS to V DD , I DS = 10 mA;5.56Ω max Test Circuit 1On-Resistance Match Between 0.3Ω typ V S = V SS to V DD , I DS = 10 mA Channels (∆R ON )0.8Ω max On-Resistance Flatness (R FLAT(ON))0.5Ω typ V S = V SS to V DD , I DS = 10 mA1Ω max LEAKAGE CURRENTSV DD = +2.75 V, V SS = -2.75 VSource OFF Leakage I S (OFF)±0.01nA typ V S = +2.25 V/-1.25 V, V D = -1.25 V/+2.25 V;±0.25±0.5nA max Test Circuit 2Drain OFF Leakage I D (OFF)±0.05nA typ V S = +2.25 V/-1.25 V, V D = -1.25 V/+2.25 V;±0.5±2.5nA max Test Circuit 3±1±5nA max Channel ON Leakage I D , I S (ON)±0.01nA typ V S = V D = +2.25 V/-1.25 V, Test Circuit 4±0.5±2.5nA max ±1±5nA max DIGITAL INPUTSInput High Voltage, V INH 1.7V min Input Low Voltage, V INL 0.7V max Input Current I INL or I INH 0.005µA typ V IN = V INL or V INH±0.1µA max C IN , Digital Input Capacitance 5pF typ DYNAMIC CHARACTERISTICS 2t TRANSITION 40ns typ R L = 300 Ω, C L = 35 pF Test Circuit 560ns max V S1 = 1.5 V/0 V,V S32 = 0 V/1.5 V Break-Before-Make Time Delay, t D 15ns typ R L = 300 Ω, C L = 35 pF;1ns min V S = 1.5 V, Test Circuit 6Charge Injection ±8pC typ V S = 0 V, R S = 0 Ω, C L = 1 nF; Test 7Off Isolation-60dB typ R L = 50 Ω, C L = 5 pF, f = 1 MHz;Test Circuit 8Channel to Channel Crosstalk -60dB typ R L = 50 Ω, C L = 5 pF, f = 1 MHz;Test Circuit 9-3 dB Bandwidth ADG72534MHz typ R L = 50 Ω, C L = 5 pF, Test Circuit 10ADG73118MHz typ C S (OFF)13pF typ C D (OFF) ADG725180pF typ f = 1 MHz ADG731360pF typ f = 1 MHz C D , C S (ON) ADG725200pF typ f = 1 MHz ADG731400pF typ f = 1 MHzPOWER REQUIREMENTS V DD = +2.75 VI DD 10µA typ Digital Inputs = 0 V or +2.75 V 20µA max I SS10µA typ V SS = -2.75 V20µA maxDigital Inputs = 0 V or +2.75 VNOTES 1Temperature range is as follows: B Version: –40°C to +85°C.2Guaranteed by design, not subject to production test.Specifications subject to change without notice.(V DD= +2.5 V ±10%, V SS= -2.5 V ±10%, GND = 0 V, unless otherwise noted)Dual Supply 元器件交易网元器件交易网PRELIMINARY TECHNICAL DATAADG725/ADG731 TIMING C HARACTERISTICS1,2Parameter Limit at T MIN, T MAX Units Conditions/Commentst133ns min SCLK Cycle timet213ns min SCLK High Timet313ns min SCLK Low Timet413ns min SYNC to SCLK falling edge setup timet540ns min Minimum SYNC low timet65ns min Data Setup Timet7 4.5ns min Data Hold Timet833ns min Minimum SYNC high timeNOTES1See Figure 1.2All input signals are specified with tr =tf = 5ns (10% to 90% of V) and timed from a voltage level of (V IL + V IH)/2.DDSpecifications subject to change without notice.Figure 1.3-Wire Serial Interface Timing Diagram.REV. PrD–5––6–REV. PrDADG725/ADG731PRELIMINARY TECHNICAL DATAABSOLUTE MAXIMUM RATINGS 1(T A = +25°C unless otherwise noted)V DD to V SS +7 VV DD to GND –0.3 V to +7 V V SS to GND +0.3 V to -7 VAnalog Inputs 2V SS - 0.3 V to V DD +0.3 Vor 30 mA, Whichever Occurs FirstDigital Inputs 2-0.3V to V DD +0.3 V or30 mA, Whichever Occurs FirstPeak Current, S or D 60mA(Pulsed at 1 ms, 10% Duty Cycle max)Continuous Current, S or D 30mA Operating Temperature Range Industrial (B Version)–40°C to +85°CCAUTIONESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection.Although the ADG725/ADG731 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.Storage Temperature Range –65°C to +150°C Junction Temperature +150°C48 lead CSP θJA Thermal ImpedanceTBD°C/W 48 lead TQFP θJA Thermal Impedance TBD°C/W Lead Temperature, Soldering (10seconds)300°C IR Reflow, Peak Temperature +220°CNOTES 1Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Only one absolute maximum rating may be applied at any one time.2Overvoltages at SCLK, SYNC , DIN , RS , S or D will be clamped by internal diodes.Current should be limited to the maximum ratings given.ORDERING GUIDEModel Temperature Range Package Description Package Option ADG725BCP -40 o C to +85 o C Chip Scale Package (CSP)CP-48ADG725BSU -40 o C to +85 o C Thin Quad FlatpackSU-48ADG731BCP -40 o C to +85 o C Chip Scale Package (CSP)CP-48ADG731BSU-40 o C to +85 o CThin Quad FlatpackSU-48元器件交易网ADG725/ADG731–7–REV. PrDPRELIMINARY TECHNICAL DATAPIN FUNCTION DESCRIPTIONADG725ADG731Mnemonic Function SCLKSerial Clock Input. Data is clocked into the input shift register on the falling edge of the serial clock input. These devices can accomodate serial input rates of up to 30MHz.R S Active low control input that clears the input register and turns all switches to the OFF condition.DIN Serial Data Input. Data is clocked into the 8-bit input register on the falling edge of the serial clock input.SXX Source. May be an input or output.D X Drain. May be an input or output.V DD Power Supply Input. These parts can be operated from a supply of +1.8V to +5.5V and dual supply of +/-2.5V.G N D Ground reference.SYNCActive Low Control Input. This is the frame synchronization signal for the input data. When SYNC goes low, it powers on the SCLK and DIN buffers and the input shift register is enabled. An 8-bit counter is also enabled. Data is transferred on the falling edges of the following clocks. After 8 falling clock edges, switch conditions are automaticaly updated. SYNC may be used to frame the signal, or just pulled low for a short period of time to enable the counter and input buffers.PIN CONFIGURATIONSCSP & TQFPS28S27S26S25S24S23S22S12S11S10S9S8S7S6S5S4S3S2S21S20S19S18S1S17S 13S 14S 15S 16N CDN CN CS 32S 31S 30S 29V D DV D DN CN CS Y N CD I NS C L KN CN CN CG N DV S SS12B S11B S10B S9B S8B S7B S6B S12A S11AS10A S9A S8A S7A S6A S5A S4AS3A S2A S5B S4B S3B S2B S1A S1BS 13AS 14AS 15AS 16AN CD A N CD BS 16AS 15BS 14BS 13B元器件交易网–8–REV. PrDADG725/ADG731PRELIMINARY TECHNICAL DATATable 2. ADG731 Truth TableA4A3A2A1A0E N C S Switch Condition X X X X X X 1Retains previous switch condition X X X X X 11All Switches OFF 0000000100001002000100030001100400100005001010060011000700111008010000090100100100101000110101100120110000130110100140111000150111100161000000171000100181001000191001100201010000211010100221011000231011100241100000251100100261101000271101100281110000291110100301111000311111132X = Don’t CareTable 1. ADG725 Truth TableA3A2A1A0E N C S A C S B Switch ConditionX X X X X 11Retains previous switch condition X X X X 111All Switches OFF 0000000S1A - DA, S1B - DB 0001000S2A - DA, S2B - DB 0010000S3A - DA, S3B - DB 0011000S4A - DA, S4B - DB 0100000S5A - DA, S5B - DB 0101000S6A - DA, S6B - DB 0110000S7A - DA, S7B - DB 0111000S8A - DA, S8B - DB 1000000S9A - DA, S9B - DB 1001000S10A - DA, S10B - DB 1010000S11A - DA, S11B - DB 1011000S12A - DA, S12B - DB 1100000S13A - DA, S13B - DB 1101000S14A - DA, S14B - DB 1110000S15A - DA, S15B - DB 1111S16A - DA, S16B - DB元器件交易网ADG725/ADG731–9–REV. PrD PRELIMINARY TECHNICAL DATAV DD Most positive power supply potential.V SS Most Negative power supply in a dual supply application. In single supply applications, connect to GND.I DD Positive supply current.I SSNegative supply current.G N D Ground (0 V) reference.S Source terminal. May be an input or output.D Drain terminal. May be an input or output.I N Logic control input.V D (V S )Analog voltage on terminals D, S R ON Ohmic resistance between D and S.∆R ONOn resistance match between any two channels, i.e. R ON max - R ON minR FLAT(ON)Flatness is defined as the difference between the maximum and minimum value of on-resistance as mea sured over the specified analog signal range.I S (OFF)Source leakage current with the switch “OFF.”I D (OFF)Drain leakage current with the switch “OFF.”I D , I S (ON)Channel leakage current with the switch “ON.”V INL Maximum input voltage for logic “0”.V INHMinimum input voltage for logic “1”.I INL (I INH )Input current of the digital input.C S (OFF)“OFF” switch source capacitance. Measured with reference to ground.CD (OFF)“OFF” switch drain capacitance. Measured with reference to ground.C D ,C S (ON)“ON” switch capacitance. Measured with reference to ground.C INDigital input capacitance.t TRANSITION Delay time measured between the 50% and 90% points of the SYNC and the switch “ON” condi tion when switching from one address state to another.t OPEN“OFF” time measured between the 80% points of both switches when switching from one address state to another.Charge A measure of the glitch impulse transferred from the digital input to the analog output during switching.InjectionOff Isolation A measure of unwanted signal coupling through an “OFF” switch.Crosstalk A measure of unwanted signal is coupled through from one channel to another as a result of parasiticcapacitance.On Response The Frequency response of the “ON” switch.Insertion The loss due to the ON resistance of the switch.LossTERMINOLOGY元器件交易网ADG725/ADG731PRELIMINARY TECHNICAL DATA TYPICAL PERFORMANCE CHARACTERISTICSTBDTPC 1. On Resistance vs. V D(V S) for forSingle SupplyTBDTPC 2. On Resistance vs. V D(V S) forDual SupplyTBDTPC 3. On Resistance vs. V D(V S) forDifferent Temperatures, SingleSupplyTBDTPC 4. On Resistance vs. V D(V S) forDifferent Temperatures, SingleSupplyTBDTPC 5. On Resistance vs. V D(V S) forDifferent Temperatures, Dual SupplyTBDTPC 6. Leakage Currents vs. V D(V S)TBDTPC 7. Leakage Currents vs. V D(V S)TBDTPC 8. Leakage Currents vs. V D(V S)TBDTPC 9. Leakage Currents vs.Temperature元器件交易网–10–REV. PrDADG725/ADG731–11–REV. PrD PRELIMINARY TECHNICAL DATATBD TPC 10. Leakage Currents vs.Temperature TBD TPC 11. Supply Currents vs. InputSwitching FrequencyTBD TPC 12. Charge Injection vs. SourceVoltageTBD TPC 13. T ON /T OFF Times vs.TemperatureTBDTPC 14. Off Isolation vs. FrequencyTBDTPC 15. Crosstalk vs. FrequencyTBDTPC 16. On Response vs. Frequency元器件交易网元器件交易网PRELIMINARY TECHNICAL DATAADG725/ADG731GENERAL DESCRIPTIONThe ADG725 and ADG731 are serially controlled, 32channel and dual/differential 16 channel multiplexers re-spectively.POWER ON RESETOn power up of the device, all switches will be in theOFF condition and the internal shift register is filled withzeros and will remain so until a valid write takes place.SERIAL INTERFACEThe ADG725 and ADG731 have a three wire serial inter-face (SYNC, SCLK, and DIN), which is compatible withSPI, QSPI, MICROWIRE interface standards and mostDSP’s. Figure 1 shows the timing diagram of a typicalwrite sequence.Data is written to the 8-bit shift register via DIN underthe control of the SYNC and SCLK signals.When SYNC goes low, the input shift register is enabled.An 8-bit counter is also enabled. Data from DIN isclocked into the shift register on the falling edge ofSCLK. Figures 2 & 3 show the contents of the input shiftregisters for these devices. When the part has receivedeight clock cycles after SYNC has been pulled low, theswitches are automatically updated with the newconfiguration and the input shift register is disabled. WithSYNC held high, any further data or noise on the DINline will have no effect on the shift register.The ADG725 CSA and CSB data bits allow the user theflexibility to change the configuration of either or bothbanks of the multiplexer.–12–REV. PrDADG725/ADG731–13–REV. PrD PRELIMINARY TECHNICAL DATATest Circuit 1.On Resistance.Test Circuit 2.I S (OFF).D Test Circuit 4.I D (ON)Test Circuit 5.Switching Time of Multiplexer, t TRANSITION .Test Circuit 6.Break Before Make Delay, t OPEN .V V DVV DVV OUTTRANSITIONTRANSITIONSYNCV OUT* SIMILAR CONNECTION FOR ADG7250V V V V V V V OUTV 0VV S SYNC*SIMILAR CONNECTION FOR ADG725V 元器件交易网–14–REV. PrDADG725/ADG731PRELIMINARY TECHNICAL DATATest Circuit 7.Charge Injection.Test Circuit 8.OFF IsolationTest Circuit 9.Channel-to-Channel Crosstalk.V *SIMILAR CONNECTION FOR ADG725V*SIMILAR CONNECTION FOR ADG725OFF ISOLATION = 20 LOGOUT V SCHANNEL TO CHANNEL CROSSTALK=20LOG 10(V OUT /V S )*SIMILAR CONNECTION FOR ADG725Test Circuit 10. Bandwidth*SIMILAR CONNECTION FOR ADG725INSERTION LOSS = 20 LOG VOUT WITH SWITCHVOUT WITHOUT SWITCH元器件交易网ADG725/ADG731–15–REV. PrD PRELIMINARY TECHNICAL DATAOUTLINE DIMENSIONSDimensions shown in inches and (mm).48-Lead CSP (CP-48)48-Lead TQFP(SU-48)0.006 (0.17)BSC0.024 (0.60) 0.017 (0.42) 0.012 (0.30) 0.009 (0.23) BSC PIN 1CONTROLLING DIMENSIONS ARE IN MILLIMETERS0.035 (0.90) MAX 0.033 (0.85) NOMREF元器件交易网。

02-IRF配置指导-IRF配置

ICL7107

ICL7107是美国Intersil公司专为数字仪表生产的数字仪V为满幅输入电压一般取200mV或2VINFS表专用芯片。

该芯片集成度高,转换精度高,抗干扰能力强,输出③积分电容CINT可直接驱动发光数码管,只需要很少的外部元件,就可以构成数积分电容取值用下式估算:字仪表模块。

ICL7107芯片用在X线机毫安显示电路中,能使毫CINT=4000×IINT/fosc×VIS安读数显示电路做到使用元件少,可靠性高,调试维修方便。

V为积分器输出幅度。

IS1ICL7107芯片简介④自动稳零电容CAZICL7107是双积分式3位半模数转换器,ICL7107集成电自动稳零电容CAZ大小的选择依系统允许引入的噪声为路内...传统的数字显示测量仪表以集成芯片(比如ICL7107芯片)集成显示为主,或者进行A/D转换后,简单地用单片机技术实现数字显示,单片机技术只是运用于简单的显示作用.由于随着计算机辅助教学在电工电子等教学设备的应用,迫切要求教学设备的硬件结构符合计算机双向控制的要求.特别是在测量仪表上,运用大量的单片机技术可以使许多功能简单实现辨认引脚:芯片的第一脚,是正放芯片,面对型号字符,然后,在芯片的左下方为第一脚。

也可以把芯片的缺口朝左放置,左下角也就是第一脚了。

许多厂家会在第一脚旁边打上一个小圆点作为标记。

知道了第一脚之后,按照反时针方向去走,依次是第 2 至第40 引脚。

(1 脚与40 脚遥遥相对)。

2.牢记关键点的电压:芯片第一脚是供电,正确电压是DC5V 。

第36 脚是基准电压,正确数值是100mV,第26 引脚是负电源引脚,正确电压数值是负的,在-3V 至-5V 都认为正常,但是不能是正电压,也不能是零电压。

芯片第31 引脚是信号输入引脚,可以输入±199.9mV 的电压。

在一开始,可以把它接地,造成“0”信号输入,以方便测试。

3.注意芯片27,28,29 引脚的元件数值,它们是0.22uF,47K,0.47uF 阻容网络,这三个元件属于芯片工作的积分网络,不能使用磁片电容。

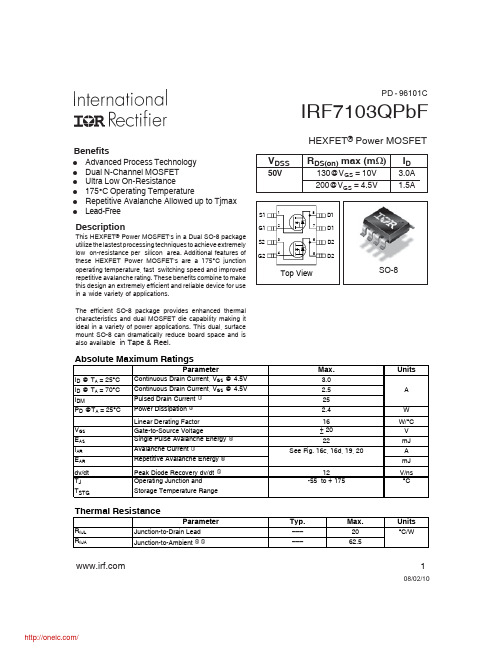

IRF7103QTRPBF;中文规格书,Datasheet资料

HEXFET ® Power MOSFETDescriptionThis HEXFET ® Power MOSFET's in a Dual SO-8 package utilize the lastest processing techniques to achieve extremely low on-resistance per silicon area. Additional features of these HEXFET Power MOSFET's are a 175°C junction operating temperature, fast switching speed and improved repetitive avalanche rating. These benefits combine to make this design an extremely efficient and reliable device for use in a wide variety of applications.The efficient SO-8 package provides enhanced thermal characteristics and dual MOSFET die capability making it ideal in a variety of power applications. This dual, surface mount SO-8 can dramatically reduce board space and is also available in Tape & Reel.08/02/10 1Benefitsl Advanced Process Technology l Dual N-Channel MOSFET l Ultra Low On-Resistancel 175°C Operating Temperaturel Repetitive Avalanche Allowed up to Tjmax lLead-FreeIRF7103QPbFV DSSR DS(on) max (m W)I D50V130@V GS = 10V 3.0A 200@V GS = 4.5V1.5APD - 96101CIRF7103QPbFSource-Drain Ratings and CharacteristicsNotes:Repetitive rating; pulse width limited bymax. junction temperature.Pulse width ≤ 400µs; duty cycle ≤ 2%.Surface mounted on 1 in square Cu boardStarting T J = 25°C, L = 4.9mHR G = 25Ω, I AS = 3.0A. (See Figure 12). I SD ≤ 2.0A, di/dt ≤ 155A/µs, V DD ≤ V (BR)DSS , T J ≤ 175°CLimited by T Jmax , see Fig.16c, 16d, 19, 20 for typical repetitive avalanche performance.ParameterMin.Typ.Max.Units Conditions V (BR)DSSDrain-to-Source Breakdown Voltage 50––––––V V GS = 0V, I D = 250µA∆V (BR)DSS /∆T JBreakdown Voltage Temp. Coefficient –––0.057–––V/°C Reference to 25°C, I D = 1mA ––––––130V GS = 10V, I D = 3.0A–––––– 200V GS = 4.5V, I D = 1.5A V GS(th)Gate Threshold Voltage 1.0––– 3.0V V DS = V GS , I D = 250µA g fs Forward Transconductance 3.4––––––S V DS = 15V, I D = 3.0A –––––– 2.0V DS = 40V, V GS = 0V––––––25V DS = 40V, V GS = 0V, T J = 55°C Gate-to-Source Forward Leakage ––––––100V GS = 20VGate-to-Source Reverse Leakage ––––––-100V GS = -20V Q g Total Gate Charge–––1015I D = 2.0A Q gs Gate-to-Source Charge––– 1.2–––nC V DS = 40V Q gd Gate-to-Drain ("Miller") Charge ––– 2.8–––V GS = 10V t d(on)Turn-On Delay Time ––– 5.1–––V DD = 25V t rRise Time––– 1.7–––I D = 1.0At d(off)Turn-Off Delay Time –––15–––R G = 6.0Ωt f Fall Time––– 2.3–––R D = 25ΩC iss Input Capacitance –––255–––V GS = 0V C oss Output Capacitance–––69–––pF V DS = 25V C rssReverse Transfer Capacitance–––29–––ƒ = 1.0MHzElectrical Characteristics @ T J = 25°C (unless otherwise specified)I GSS µAm ΩR DS(on)Static Drain-to-Source On-Resistance I DSS Drain-to-Source Leakage Current nAnsIRF7103QPbF 3Fig 3. Typical Transfer CharacteristicsFig 2. Typical Output CharacteristicsFig 1. Typical Output Characteristics Fig 4. Normalized On-ResistanceVs. Temperature3.06.09.012.015.0V GS , Gate-to-Source Voltage (V)1.0010.00100.00I D , D r a i n -t o -S o u r c e C u r r en t (Α)V DS , Drain-to-Source Voltage (V)I D , D r a i n -t o -S o u r c e C u r r e n t (A)V DS , Drain-to-Source Voltage (V)I D , D r a i n -t o -S o u r c e C u r r e n t (A )IRF7103QPbFGate-to-Source VoltageFig 5. Typical Capacitance Vs.Drain-to-Source Voltage Fig 8. Maximum Safe Operating AreaForward Voltage1101001000V DS , Drain-toSource Voltage (V)0.010.1110100I D , D r a i n -t o -S o u r c e C u r r e n t (A )110100V DS , Drain-to-Source Voltage (V)10100100010000C , C a p a c i t a n c e (p F )IRF7103QPbF 5Fig 11. Typical Effective Transient Thermal Impedance, Junction-to-AmbientCase TemperatureFig 10a. Switching Time Test CircuitV V d(on)rd(off)fFig 10b. Switching Time WaveformsV DDt 1 , Rectangular Pulse Duration (sec)IRF7103QPbF6Fig 13. Typical On-Resistance Vs. DrainCurrentFig 12. Typical On-Resistance Vs. GateVoltageFig 14. Typical Threshold Voltage Vs.Junction TemperatureFig 15. Typical Power Vs. Time-V GS, Gate -to -Source Voltage (V)R D S (o n ), D r a i n -t o -S o u r ce O n R e s i s t a n c e (Ω)T J , Temperature ( °C )V G S (t h ) G a t e t h r e s h o l d V o l t a g e (V )510152025303540I D , Drain Current (A)0.0000.5001.0001.5002.0002.500R D S (o n ) , D r a i n -t o -S o u r c e O n R e s i s t a n c e (Ω)Time (sec)P o w e r (W )IRF7103QPbF7VDSCurrent Sampling ResistorsV GSFig 17. Gate Charge Test Circuit Fig 18. Basic Gate Charge WaveformVs. Drain CurrentFig 16d. Unclamped Inductive WaveformsFig 16c. Unclamped Inductive Test CircuitI ASV DDIRF7103QPbFFig 19. Typical Avalanche Current Vs.PulsewidthFig 20. Maximum Avalanche EnergyVs. TemperatureNotes on Repetitive Avalanche Curves , Figures 15, 16:(For further info, see AN-1005 at )1. Avalanche failures assumption:Purely a thermal phenomenon and failure occurs at a temperature far in excess of T jmax . This is validated for every part type.2. Safe operation in Avalanche is allowed as long asT jmax is not exceeded.3. Equation below based on circuit and waveforms shown in Figures 12a, 12b.4. P D (ave) = Average power dissipation per single avalanche pulse.5. BV = Rated breakdown voltage (1.3 factor accounts for voltage increase during avalanche).6. I av = Allowable avalanche current.7. ∆T = Allowable rise in junction temperature, not to exceed T jmax (assumed as 25°C in Figure 15, 16). t av = Average time in avalanche. D = Duty cycle in avalanche = t av ·fZ thJC (D, t av ) = Transient thermal resistance, see figure 11)P D (ave) = 1/2 ( 1.3·BV·I av ) = D T/ Z thJCI av = 2D T/ [1.3·BV·Z th ]E AS (AR) = P D (ave)·t avtav (sec)A v a l a n c h e C u r r e n t (A)255075100125150175Starting T J , Junction Temperature (°C)0510152025E A R , A v a l a n c h e E n e r g y (m J )IRF7103QPbFSO-8 Package OutlineIRF7103QPbF10330.00(12.992) MAX.14.40 ( .566 )12.40 ( .488 )NOTES :1. CONTROLLING DIMENSION : MILLIMETER.2. OUTLINE CONFORMS TO EIA-481 & EIA-541.FEED DIRECTIONTERMINAL NUMBER 112.3 ( .484 )11.7 ( .461 )8.1 ( .318 )7.9 ( .312 )NOTES:1. CONTROLLING DIMENSION : MILLIMETER.2. ALL DIMENSIONS ARE SHOWN IN MILLIMETERS(INCHES).3. OUTLINE CONFORMS TO EIA-481 & EIA-541.SO-8 Tape and ReelIR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245, USA Tel: (310) 252-7105TAC Fax: (310) 252-7903Visit us at for sales contact information .08/2010Data and specifications subject to change without notice.This product has been designed and qualified for the Industrial market.Qualification Standards can be found on IR’s Web site.分销商库存信息: IRIRF7103QTRPBF。

【研究】Inconel713C(K418)成分、性能、指标...

Inconel 713C/k418总结Inconel 713C(K418)合金受到国内外学者的广泛关注,对其显微安排、力学功能以及新工艺等进行了较为深入的研讨。

(1)研讨表明,铁含量(0.85%~3.32%)的变化对其显微安排、开裂机理及高温拉伸功能影响较小,但当铁的质量分数超过1%后,使材料的延伸率发生了波动。

(2)该合金铸态组织主要由树枝状y基体、沉淀析出的y相(具有L12有序结构)、沿枝晶臂、晶界以及在y-y'共晶间析出的碳化物组成。

(3)研究指出,涡轮熔模铸造用型壳在浇铸前未清洗干净或型壳结合不牢,可导致涡轮在超转试验的作用力下沿晶界薄弱处产生裂纹。

涡轮凝固过程中由于各部分冷却速度不一致,致使收缩量不同,因而产生了热应力;A1,Ti含量增加可扩大合金的有效结晶温度范围,从而导致热裂的产生。

(4)细晶铸造可显著细化该合金的晶粒度和强化相。

与普通铸造相比,其强度可提高10%~30%,经细晶铸造后合金的低周期疲劳寿命可提高3倍以上。

此外,激光成形修复技术的应用可降低合金的开裂倾向。

Inconel 713C/k418应用合金已广泛用于制造航空、地面和海上燃气轮机涡轮作业叶片、导向叶片和整铸涡轮,航天弹用发动机的整铸涡轮转子和导向器,以及柴油机和汽油机增压涡轮和热挤压模具。

该合金经国内多个厂家长时间出产和实践证明,冶金质量安稳,功能牢靠。

合金选用热等静压处理及随后热处理,能够提高合金的塑性和抗疲惫功能,也能够使经过长时间运用后安排退化和功能下降的零件康复其安排和运用功能。

合金在热腐蚀条件下长时间运用时,须有防护涂层。

合金经800℃长时间时效后会分出少量相,但对功能无明显影响。

高温合金分为三类材料:760℃高温材料、1200℃高温材料和1500℃高温材料,抗拉强度800MPa。

或者说是指在760--1500℃以上及一定应力条件下长期工作的高温金属材料,具有优异的高温强度,良好的抗氧化和抗热腐蚀性能,良好的疲劳性能、断裂韧性等综合性能,已成为军民用燃气涡轮发动机热端部件不可替代的关键材料。

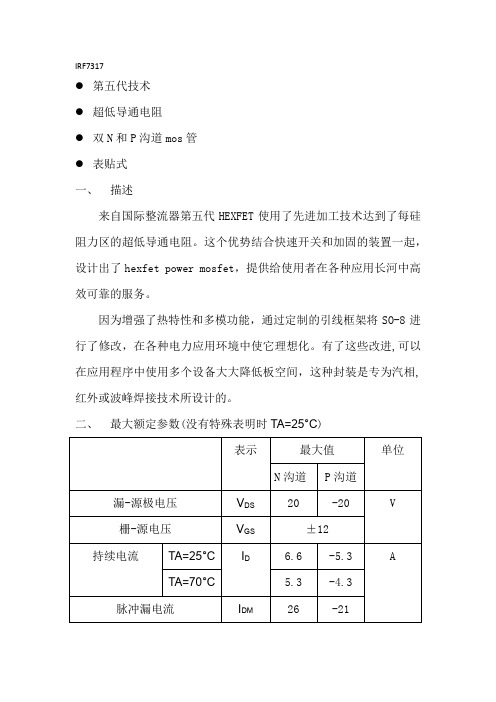

IRF7317功率管中文数据手册

IRF7317

●第五代技术

●超低导通电阻

●双N和P沟道mos管

●表贴式

一、描述

来自国际整流器第五代HEXFET使用了先进加工技术达到了每硅阻力区的超低导通电阻。

这个优势结合快速开关和加固的装置一起,设计出了hexfet power mosfet,提供给使用者在各种应用长河中高效可靠的服务。

因为增强了热特性和多模功能,通过定制的引线框架将SO-8进行了修改,在各种电力应用环境中使它理想化。

有了这些改进,可以在应用程序中使用多个设备大大降低板空间,这种封装是专为汽相,红外或波峰焊接技术所设计的。

二、最大额定参数(没有特殊表明时TA=25°C)

三、热阻评级。

7107数字电压表资料

与多量程电流表对应的是经常需要使用多量程电压表,按照下图配置一组分压电阻,就可以得到量程从 ±200.0mV 至 ±1000V 的 多量程电压表。

3

测量电阻与测量电流或者电压一样重要,俗称“三用表”,利用数字电压表做成的多量程电阻表,采用的是“比例法”测量,因此, 它比起指针万用表的电阻测量来具有非常准确的精度,而且耗电很小,下图示中所配置的一组电阻就叫 “基准电阻” ,就是通过切 换 各个接点得到不同的基准电阻值,再由 Vref 电压与被测电阻上得到的 Vin 电压进行“比例读数”,当 Vref = Vin 时,显示就是 Vin/Vref*1000=1000 ,按照需要点亮屏幕上的小数点,就可以直接读出被测电阻的阻值来了。

数字电压表(数字面板表)是当前电子、电工、仪器、仪表和测量领域大量使用的一种基本测量工具有关数字电压表的书籍和应用已 经非常普及了。这里展示的一份由 ICL7106 A/D 转换电路组成的数字电压表(数字面板表)电路,就是一款最通用和最基本的电路。

与 ICL7106 相似的是 ICL7107 ,前者使用 LCD 液晶显示,后者则是驱动 LED 数码管作为显示,除此之外,两者的应用基本是相 通的。

0mA 。当输入零点电流为 4 mA 的时候,利用 IN- 上面建立起来的电压,抵消掉 IN+ 由于 4mA 出现的无用信号,使得数字电压表 差分输入=0,就实现了 4mA 输入时显示为 0 的要求。随着信号的继续增大,例如到了 20mA ,对数字电压表来说,相当于差分输入 电流为 20-4=16mA ,这个 16mA 在 62.5R 电阻上的压降,就是数字电压表的最大输入信号。这时候,把数字电压表的基准电压调整 到与 16*62.5=1000mV 相等,显示就是 1000 个字!

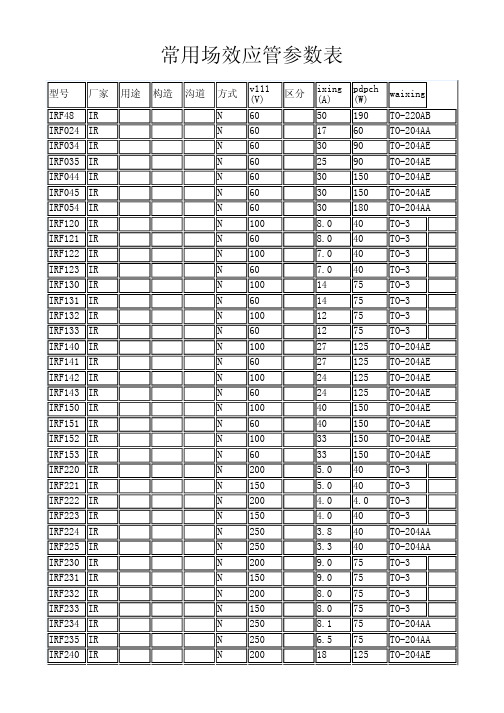

常用场效应管参数表

18 16 16 14 13 30 30 25 25 22 20 3.0 3.0 2.5 2.5 5.5 5.5 4.5 4.5 10 10 8.0 8.0 15 15 13 13 25 22 2.5 2.5 2.0 2.0 4.5 4.5 4.0 4.0 8.0 8.0 7.0

125 125 125 125 125 150 150 150 150 150 150 40 40 40 40 75 75 75 75 125 125 125 125 150 150 150 150 300 300 50 50 50 50 75 75 75 75 125 125 125

IRF9133 IR IRF9140 IR IRF9141 IR IRF9142 IR IRF9143 IR IRF9230 IR IRF9231 IR IRF9232 IR IRF9233 IR IRF9240 IR IRF9241 IR IRF9242 IR IRF9243 IR IRF9510 IR IRF9511 IR IRF9512 IR IRF9513 IR IRF9520 IR IRF9521 IR IRF9522 IR IRF9523 IR IRF9530 IR IRF9531 IR IRF9532 IR IRF9533 IR IRF9540 IR IRF9541 IR IRF9542 IR IRF9543 IR IRF9610 IR IRF9611 IR IRF9612 IR IRF9613 IR IRF9620 IR IRF9621 IR IRF9622 IR IRF9623 IR IRF9630 IR IRF9631 IR IRF9632 IR

TO-3 TO-204AA TO-204AA TO-3 TO-3 TO-3 TO-3 TO-204AE TO-204AE TO-220AB TO-220AB TO-220AB TO-220AB TO-220AB TO-220AB TO-220AB TO-220AB TO-220AB TO-220AB TO-220AB TO-220AB TO-220AB TO-220AB TO-220AB TO-220AB TO-220AB TO-220AB TO-220AB TO-220AB TO-220AB TO-220AB TO-220AB TO-220AB TO-220AB TO-220AB TO-220AB TO-220AB TO-220AB TO-220AB TO-220AB

ICL7135数字表芯片中文资料全

ICL7135数字表芯片中文资料时间:2009-11-07 14:55:50 来源:资料室作者:编号:1254 更新日期20110228 071526(一)ICL7135芯片介绍ICI7135是4位双积分A/D转换芯片,可以转换输出±20000个数字量,有STB选通控制的BCD码输出,与微机接口十分方便.ICL7135具有精度高(相当于14位A/D转换),价格低的优点.其转换速度与时钟频率相关,每个转换周期均有:自校准(调零),正向积分(被测模拟电压积分),反向积分(基准电压积分)和过零检测四个阶段组成,其中自校准时间为10001个脉冲,正向积分时间为10000个脉冲,反向积分直至电压到零为止(最大不超过20001个脉冲).故设计者可以采用从正向积分开始计数脉冲个数,到反向积分为零时停止计数.将计数的脉冲个数减10000,即得到对应的模拟量.图1给出了ICL7135时序,由图可见,当BUSY变高时开始正向积分,反向积分到零时BUSY变低,所以BUSY可以用于控制计数器的启动/停止.ICL7135为DIP28封装,芯片引脚排列如图2所示,引脚功能及含义如下:(1)与供电及电源相关的引脚(共7脚).-V:ICL7135负电源引入端,典型值-5V,极限值-9V;.+V:ICL7135正电源引入端,典型值+5V,极限值+6V;.DGND:数字地,ICL7135正,负电源的低电平基准;.REF:参考电压输入,REF的地为AGND引脚,典型值1V,输出数字量=10000×(VIN/VREF);.AC:模拟地,典型应用中,与DGND(数字地)"一点接地";.INHI:模拟输入正;.INLO:模拟输入负,当模拟信号输入为单端对地时,直接与AC相连.图1 1CL7135时序图2 1CL7135芯片引脚(2)与控制和状态相关的引脚(共12脚).CLKIN:时钟信号输入.当T=80ms时,fcp=125kHz,对50Hz工频干扰有较大抑制能力,此时转换速度为3次/s.极限值fcp=1MHz时,转换速度为25次/s..REFC+:外接参考电容正,典型值1μF..REFC-:外接参考电容负..BUFFO:缓冲放大器输出端,典型外接积分电阻..INTO:积分器输出端,典型外接积分电容..AZIN:自校零端..LOW: 欠量程信号输出端,当输入信号小于量程围的10%时,该端输出高电平..HIGH:过量程信号输出端,当输入信号超过计数围(20001)时,该端输出高电平..STOR:数据输出选通信号(负脉冲),宽度为时钟脉冲宽度的一半,每次A/D转换结束时,该端输出5个负脉冲,分别选通由高到低的BCD码数据(5位),该端用于将转换结果打到并行I/O接口..R/H:自动转换/停顿控制输入.当输入高电平时;每隔40002个时钟脉冲自动启动下一次转换;当输入为低电平时,转换结束后需输入一个大于300ns的正脉冲,才能启动下一次转换..POL:极性信号输出,高电平表示极性为正..BUSY:忙信号输出,高电平有效.正向积分开始时自动变高,反向积分结束时自动变低.(3)与选通和数据输出相关的引脚(共9脚)'.B8~B1:BCD码输出.B8为高位,对应BCD码;.D5:万位选通;.D4~D1:千,百,十,个位选通.ICL7135外接阻容的典型应用如图6所示.由于单片机资源的宝贵,如果采用MCl4433的接口方法,将占用8条以上端口线,下面重点介绍一种利用BUSY信号特点的"转换"方式,大减少了对单片机资源的占用.图3 ICL7135典型应用(二)接口与编程ICL7135与MCS-51的连接可参照MCLl4433与处理器连接方法,依次读出万位到个位的BCD码.本节采用另外一种方法,重点推荐采用计数法进行A/D"转换"的方法.ICL7135与MCS-51连接如图4所示.图4 1CL7135与MCS51连接(1)硬件连接.设MCS-51的外接晶振fosc=6MHz,则ALE输出约为1MHz,将ALE信号输入CD4040的CLK引脚.CD4040是由12个T型触发器组成的串行二进制计数器/分频器,有12个分频输出端,Q1~Q12,最大分频系数为212=4096,由于CD4040的所有输入,输出端都设有缓冲器,所以有较好的噪声容限.CD4040的Q2输出是对ALE进行了22=4分频,故输入ICL7135的时钟为1MHz/4=250kHz,可得TCP=1/250ms=0.004mS,由于一次转换最多需(10001+10000+20001)=40002个脉冲,故转换一次需0.004×40002≈160ms,因此ICL7135的转换速度为6.25次/s.选择这一频率,以牺牲ICL7135抗工频干扰为代价,使MCS-51的16位计数器能一次计数A/D"转换"的CP脉冲数.在满电压输入时,BUSY宽度为正向积分10000个CP脉冲,反向积分20001个CP脉冲(总计30001个CP脉冲).在fosc=6MHz情况下,8031部定时频率为6MHz/12=500kHz,比ICL7135时钟频率250kHz大了1倍.在满刻度电压输入时,定时器计数值应为30 001×2=60002,不超过MCS-51的16位计数的最大可计数值(216),故在BUSY高电平期间,计数器计数值除以2,再减去10000(2710H),余数就是被测电压的数值.(2)程序设计.假定将转换的结果(二进制)存放在R3,R2寄存器中,其中R3存放高位.程序清单如下:JB P3.2,$ ;等待BUSY变低(A/D转换结束)MOV TL0,#0MOV THO,#0 ;16位计数器初值清0MOV TMOD,#01H ;TO定时,方式1(16位定时)JNB P3.2,$ ;等待BUSY变高(A/D转换开始)SETB TR0 ;启动定时JB P3.2,$ ;等待A/D结束CLR TR0 ;停定时CLR CMOV A,THORRC A ;高位除以2MOV R3,A ;存高位MOV A,TL0RRC A ;低位除以2MOV R2,A ;存低位CLR CSUBB A,#10H ;低位减10HMOV R2,AMOV A,R3SUBB A,#27H ;高位减27HMOV R3,ARET提示:现在市场上许多常见的4位半数字万用表就是采用类似上述转换芯片图5 UART接口电路图6 UART接口电路图7 典型应用示意图图8 驱动液晶显示器电路图图9 41/2位数的A/D复用共阳极LED显示屏电路图10 ICL7135的8255,80C48接口电路图11 LM311时钟源.jpg图12 ICL7135的MC6800,MCS650X接口电路。

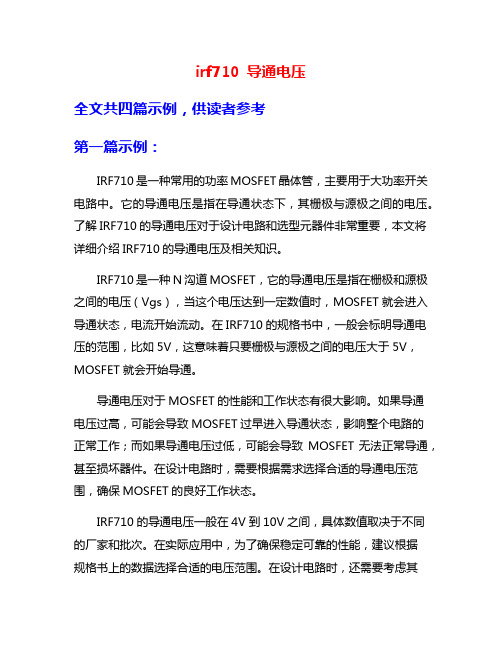

irf710 导通电压

irf710 导通电压全文共四篇示例,供读者参考第一篇示例:IRF710是一种常用的功率MOSFET晶体管,主要用于大功率开关电路中。

它的导通电压是指在导通状态下,其栅极与源极之间的电压。

了解IRF710的导通电压对于设计电路和选型元器件非常重要,本文将详细介绍IRF710的导通电压及相关知识。

IRF710是一种N沟道MOSFET,它的导通电压是指在栅极和源极之间的电压(Vgs),当这个电压达到一定数值时,MOSFET就会进入导通状态,电流开始流动。

在IRF710的规格书中,一般会标明导通电压的范围,比如5V,这意味着只要栅极与源极之间的电压大于5V,MOSFET就会开始导通。

导通电压对于MOSFET的性能和工作状态有很大影响。

如果导通电压过高,可能会导致MOSFET过早进入导通状态,影响整个电路的正常工作;而如果导通电压过低,可能会导致MOSFET无法正常导通,甚至损坏器件。

在设计电路时,需要根据需求选择合适的导通电压范围,确保MOSFET的良好工作状态。

IRF710的导通电压一般在4V到10V之间,具体数值取决于不同的厂家和批次。

在实际应用中,为了确保稳定可靠的性能,建议根据规格书上的数据选择合适的电压范围。

在设计电路时,还需要考虑其他因素,如最大允许的电流、功率损耗、温度特性等,综合考虑才能选型合适的MOSFET晶体管。

第二篇示例:IRF710是一种常见的功率场效应晶体管,广泛应用于电力控制和电子设备中。

在使用IRF710进行工程设计和应用时,需要了解它的一些重要参数,比如导通电压。

导通电压是指场效应晶体管在导通状态下的电压阈值,也是指场效应晶体管开始导通的电压值。

在现实应用中,正确理解和掌握IRF710的导通电压是至关重要的。

IRF710是N沟道MOSFET,其导通电压范围通常为2-4V。

具体的导通电压取决于制造商和具体型号,因此在使用IRF710进行设计时,需要查阅数据手册以了解准确的导通电压值。

713-FET特性与应用电路

ID(mA) Ohmic 36 region 32 28 24 20 16 IDSS 12 8 4

24

Saturation

region

VGS=+2V

+1V

0V

-1V -2V 6 8 10 12 -3VVDS(V)

-VT (a)Output characteristic

Cutoff region (VGS<-4V)

移量。 • 3.如(d),其中R1 = 1K、R2 = 3K,調整RS到ID為步驟(1)的ID

值,量出VD、VS、VG及ID ,重複步驟(2)。(Hint: VD=2.5V) • 4.如(e),其中RD為200Ω串1K可變電阻,調整RD到ID為步驟

(1)的ID值,量出VD、VS、VG及ID ,重複步驟(2)。

拿掉Cs,重複上述步驟記錄在第6步驟. (2 pics) • 3.調整輸入到”最大而不失真”的狀態,記錄Vi跟Vo的振幅大小。 • 4.調整R12使VDS ≧ 6V:

以步驟(3)所得訊號輸入,此時放大器的輸出訊號是否失真?

(1 pic)

• 5.調整R12使VDS = 3V: 以步驟(3)所得訊號輸入,此時放大器的輸出訊號是否失真?

2020/6/6

LAB 3

R 12 C G= 0.05F V in

R2

R 11

V DD

R D= 4.7K C D= 0.05FV O

R S= 2K

C S= 4.7F

A vRR iR i 1 ggm m Rs(Ro//RL)

2020/6/6

LAB 3

R 11

V DD

R 12

R D= 4.7K

C G= 0.05F

SX713 电导率使用说明书

SX713型电导率/TDS/盐度/电阻率测量仪使用说明书成都锐新仪器仪表有限公司RUNSUN INSTRUMENTS INC.SX700系列便携式测量仪1. SX711型pH/mV计2. SX712型ORP计3.SX713型电导率/TDS/盐度/电阻率测量仪4. SX716型溶解氧测量仪5. SX721型pH/ORP计6. SX723型pH/mV/电导率测量仪7. SX725型pH/mV/溶解氧测量仪8. SX726型电导率/溶解氧测量仪9. SX731型pH/ORP/电导率测量仪10. SX736型pH/mV/电导率/溶解氧测量仪11. SX751型pH/ORP/电导率/溶解氧测量仪目录1. 概述-------------------------------------------------------------------------------------------------2. 技术参数-------------------------------------------------------------------------------------------3. 仪器说明------------------------------------------------------------------------------------------- 3.1. LCD显示------------------------------------------------------------------------------------- 3.2. 操作键------------------------------------------------------------------------------------------3.3. 测量信息的储存、回显和清除------------------------------------------------------------4. 电导率测量---------------------------------------------------------------------------------------- 4.1. 准备工作--------------------------------------------------------------------------------------- 4.2. 仪器校准--------------------------------------------------------------------------------------- 4.3. 溶液测试--------------------------------------------------------------------------------------- 4.4. 重要说明--------------------------------------------------------------------------------------- 4.5. 参数设置---------------------------------------------------------------------------------------4.6. 注意事项---------------------------------------------------------------------------------------5. 仪器成套性----------------------------------------------------------------------------------------6. 仪器保证事项------------------------------------------------------------------------------------- 附表Ⅰ仪器参数设置一览表附表Ⅱ仪器恢复出厂设置一览表附表Ⅲ代码符号及缩写一览表3 4 5 5 5 6 7 7 7 7 7 91213 131. 概述:感谢您购买和使用锐新仪器SX713型电导率/TDS/盐度/电阻率测量仪(以下简称仪器)。