Xilinx+ISE下载文件生成步骤

ISE开发环境使用指南[FPGA开发教程

ISE开发环境使用指南简介ISE(Integrated Software Environment)是Xilinx公司开发的一套FPGA设计软件工具。

本文档将为您介绍如何使用ISE开发环境进行FPGA开发,包括环境的安装、基本操作和常见问题解决方法。

环境安装1.在Xilinx官网上下载最新版本的ISE软件。

2.双击安装文件,按照向导指示完成安装过程。

3.完成安装后,打开ISE软件,进行必要的设置和配置。

基本操作创建工程1.打开ISE软件,选择“File” -> “New Project”。

2.在弹出的对话框中输入工程名称和路径,选择FPGA型号等相关参数,点击“Next”。

3.添加源文件和约束文件,点击“Next”。

4.点击“Finish”完成工程创建。

编译工程1.在ISE软件中选择“Project” -> “Run Implementation”进行工程编译。

2.检查编译过程中是否有错误,根据提示进行修正。

下载到FPGA1.将FPGA与电脑连接,选择“Tools” -> “iMPACT”打开下载工具。

2.配置下载参数,选择对应的FPGA型号和文件路径。

3.点击“Program”开始下载程序到FPGA。

常见问题解决方法编译错误•检查代码中是否有语法错误或逻辑问题。

•检查约束文件是否设置正确。

下载失败•检查FPGA与电脑的连接是否正常。

•检查下载工具配置是否正确。

总结通过本文档的介绍,您应该对如何使用ISE开发环境进行FPGA开发有了一定了解。

希望您在实际操作中能够顺利完成项目的开发和调试。

如果遇到任何问题,可以参考本文档中提供的常见问题解决方法或参考Xilinx官方文档进行进一步学习和搜索。

XilinxMCS下载文件的生成与下载

第一步:打开iMPACT软件

第二步:出现iMPACT Project框,选择Cancel

第三步:双击Flow 中的PROM File Formatter

第四步:在出现的Prepare PROM Files中,填写PROM File Name,选择生成PROM存放的路径,然后点击Next

第五步:使用默认设置,点Next

第六步:按图所示,选择PROM

第七步:单击Add,然后点Next

第八步:点击Finish完成

第九步:在弹出的Add Device中点OK

第十步:在弹出的Add Device中选择你要转换的bit文件,双击即可

第十一步:点No

第十二步:点OK

第十三步:双击Generate File,生成MCS文件,可以看到主窗口中出现PROM File Generation Succeeded,即表示MCS文件生成成功

下面将怎么下载MCS文件:第一步:双击Boundary Scan

第二步:在空白处点右键,选择Initialize Chain

第三步:PROM显示为绿色,此时表示要选择的下载文件是下载到该PROM中的,选择刚才生成的MCS文件

第四步:紧接着出现的对话框要求下载bit文件,如若要下载bit文件,此处选择要下载的bit文件,如果不需要则点Cancel

第五步:紧接着出现的对话框根据自己的需要勾选相关的选项,然后点击OK

下载。

ISE程序下载详细教程

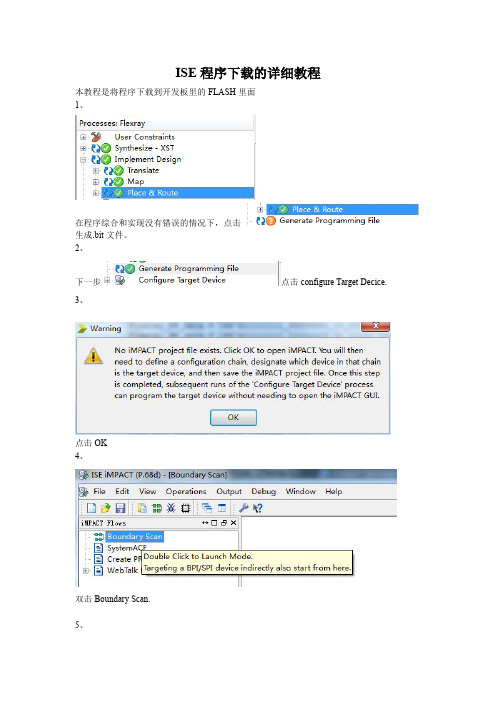

ISE程序下载的详细教程

本教程是将程序下载到开发板里的FLASH里面

1、

在程序综合和实现没有错误的情况下,点击

生成.bit文件。

2、

下一步点击configure Target Decice. 3、

点击OK

4、

双击Boundary Scan.

5、

空白处右键,点击Add Xilinx Device... 6、

找到生成的.bit文件

7、

点击Create PROM File

8、

点击图中蓝色选项

9、

根据FLASH的大小选择,然后点击Add Storage Device 10、

选择存储路径和名称

点击OK

11、

点击OK

选择刚才生成的.bit文件12、

选择NO

13、

点击OK

14、

双击Generate file 15、

生成.mcs文件成功16、

双击第一项

17、

鼠标移到蓝色虚线框中右键

18、

添加生成的.mcs文件

19、

选择存储器型号

20、

点击Program

OK程序已经下载到你的开发板flash里面了。

ISE软件使用说明(两篇)

引言:概述:ISE软件是由Xilinx公司开发的一款集成电路设计工具,使用该软件可以进行数字电路设计、仿真、验证以及实现等多个阶段的工作。

在设计阶段,ISE软件提供了丰富的组件库和设计工具,方便用户进行电路原理图的绘制和逻辑设计。

在验证阶段,ISE软件可以进行功能仿真和时序仿真,以确保设计的正确性和稳定性。

在实现阶段,ISE软件提供了先进的布局与布线工具,能够将设计转化为实际的电路板。

正文内容:1.安装与启动1.1ISE软件安装包1.2安装ISE软件1.3启动ISE软件2.项目管理2.1创建新项目2.2导入已有项目2.3添加设计文件2.4设定项目属性2.5保存和备份项目3.设计流程3.1电路原理图设计3.1.1组件选择3.1.2连接元件3.1.3设置元件属性3.2逻辑设计3.2.1设计约束3.2.2逻辑优化3.2.3时序约束3.3约束文件编辑3.3.1约束规则3.3.2约束语法3.3.3约束检查3.4时序仿真3.4.1创建仿真波形3.4.2设定初始状态3.4.3运行仿真3.5功能仿真3.5.1设置输入信号3.5.2运行仿真3.5.3分析仿真结果4.仿真与验证4.1时序分析4.1.1设定时钟4.1.2时序路径分析4.1.3时序优化4.2时序约束验证4.2.1满足约束4.2.2修复时序错误4.3灵敏度分析4.3.1设定输入敏感性4.3.2分析敏感性4.4逻辑分析4.4.1切换敏感性4.4.2分析逻辑状态5.布局与布线5.1物理约束5.1.1面积约束5.1.2信号完整性约束5.1.3电源与接地约束5.2布局5.2.1网表导入5.2.2管理物理资源5.2.3进行布局布线5.3时序优化5.3.1满足时序约束5.3.2缩短信号传输路径5.3.3优化时钟分配5.4布线5.4.1管理布线资源5.4.2进行布线5.4.3路由与优化5.5设计规约检查5.5.1检查布局布线规约5.5.2修复设计规约错误总结:引言概述:ISE软件是一款功能强大的集成开发环境工具,广泛应用于数字电路设计和实现。

Xilinx ISE的流程、命令和文件

时序分析告:

TRCE:

这个是用来产生偶们最最关心的timingreport的。TRCE会分析你的FPGA的设计并且产生一个后缀名为“.twr”的时序报告。你可以用任何文 本工具打开它,也可以用xilinx的Timing Analyzer。Timing Analyzer比较直观,推荐新手使用。

约束文件:

3种:用户约束文件UCF,网表约束文件NCF,物理约束文件PCF。

UCF由用户输入,NCF由综合工具产生。UCF优先级高。

翻译Translate:

把多个设计文件merge成一个网表文件。

(输入:网表文件EDF(或ngc,ngo)+NCF文件)

Xilinx ISE的流程、命令和文件

电路设计与输入-->功能仿真-->综合优化-->实现过程(翻译、映射、布局布线3个小步骤)-->烧写芯片,在线调试

我的博客:/frog001 email: iamadog3333@

综合优化:

XST:全称为XilinxSynthesis Technology,这是Xilinx ISE里面附带的一个免费的综合工具。

NGDBuild:

这个命令,其实就是translate啦。这是implementation的第一步。它会把所有的netlist和design constraint合并到一起,生成一个ngd文 件供map工具使用。

生成文件:*.ngd

映射Map:

把网表中的逻辑符号(gates)分组到物理组件(slices and IOBS)中。

Synplify生成文件:netlist网表文件 标准edif文件*.edf; 综合约束传递文件*.ncf;

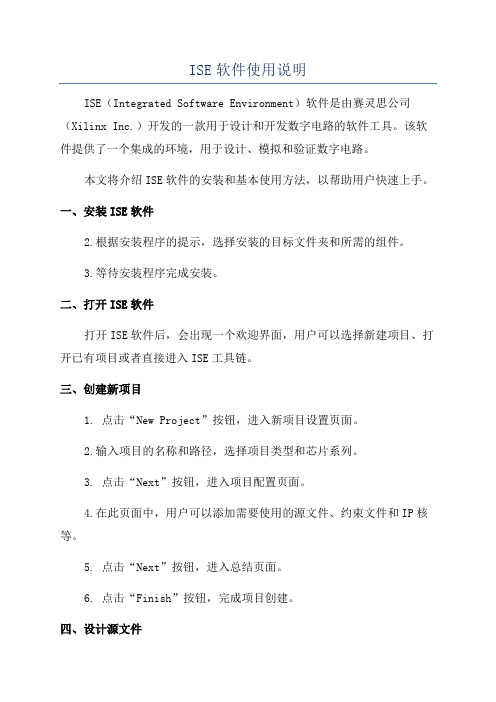

ISE软件使用说明

ISE软件使用说明ISE(Integrated Software Environment)软件是由赛灵思公司(Xilinx Inc.)开发的一款用于设计和开发数字电路的软件工具。

该软件提供了一个集成的环境,用于设计、模拟和验证数字电路。

本文将介绍ISE软件的安装和基本使用方法,以帮助用户快速上手。

一、安装ISE软件2.根据安装程序的提示,选择安装的目标文件夹和所需的组件。

3.等待安装程序完成安装。

二、打开ISE软件打开ISE软件后,会出现一个欢迎界面,用户可以选择新建项目、打开已有项目或者直接进入ISE工具链。

三、创建新项目1. 点击“New Project”按钮,进入新项目设置页面。

2.输入项目的名称和路径,选择项目类型和芯片系列。

3. 点击“Next”按钮,进入项目配置页面。

4.在此页面中,用户可以添加需要使用的源文件、约束文件和IP核等。

5. 点击“Next”按钮,进入总结页面。

6. 点击“Finish”按钮,完成项目创建。

四、设计源文件在ISE软件中,用户可以使用HDL(硬件描述语言)进行设计源文件的编写。

ISE软件支持的HDL语言有VHDL和Verilog。

1. 在项目视图中,右键点击“Source”文件夹,选择“New Source”。

2.在弹出的对话框中,选择源文件类型和语言。

3. 输入文件的名称和路径,点击“Finish”按钮。

五、添加约束文件约束文件用于定义电路的时序、引脚映射等信息,以确保电路的正常工作。

1. 在项目视图中,右键点击“Constraints”文件夹,选择“New Source”。

2.在弹出的对话框中,选择约束文件类型。

3. 输入文件的名称和路径,点击“Finish”按钮。

六、综合与实现在进行综合和实现之前,需要根据设计需求进行一些设置和配置。

1. 在项目视图中,右键点击项目名称,选择“Properties”。

2.在弹出的对话框中,选择“SYNTHESIS”或“IMPLEMENTATION”选项卡。

XilinxISE软件使用过程新(含PROM下载)

Xilinx ISE 13.4软件使用方法本章将以实现一个如图所示的4为加法器为例,来介绍Xilinx ISE13.4开发流程,并且最终下载到实验板BASYS2中运行。

4位加法器C0C 1A0A1A2A B0B1B2B3S0S 1S2S331.建立工程运行Xilinx ISE Design Suite 13.4,初始界面如图F2所示所示F1软件初始状态表软件初始状态表选择File->New Project ,该对话框显示用向导新建工程所需的步骤。

,该对话框显示用向导新建工程所需的步骤。

在Name 栏中输入工程名称(注意:以下所有不能含有中文字符或空格),如“test”。

在Location 栏中选择想要存放的工程位置,如“E:“E:\code\Xilinx\\code\Xilinx\\code\Xilinx\test”test”。

顶层语言选项栏中选择“HDL”语言。

设置向导最终设置效果如图F2所示所示F2路径信息设置表路径信息设置表点击“Next”,进入芯片型号选择界面。

进入芯片型号选择界面。

在本界面中,在本界面中,根据BASYS2实验板上的芯片型号进行相关设置,设置效果如图F3所示。

所示。

F3芯片信息选择表芯片信息选择表点击“Next Next””,出现如图F4所示工程信息汇总表格。

所示工程信息汇总表格。

F4工程信息汇总表工程信息汇总表点击“Finish”完成设置。

完成设置。

2新建V erilog文件在F5所示界面中,如图所示的区域内右击鼠标,选择“New Source”,出现F6对话框。

对话框。

F5在File name栏中键入verilog文件的名称,如“test”。

F6Next””,在本界面中将设置加法器的输入输出引脚数量,如图F1所示点击“Next的加法器共有A、B、C0、S和C1,5组引脚,其中A、B和S为4位总线形式,所示。

因此设置结果如图F7所示。

F7点击“Next”,出现V erilog 新建信息汇总表。

关于Xilinx ISE简单使用方法介绍

output [7:0] y_out,

);

assign y_out = flag ? x_in : 8'b00000000;

endmodule

3.程序语法检查

如下图所示:

或者:

4.创建测试文件(功能仿真数据的建立)

ProjectNew Source。如输入文件名:Two2One_tf(*.v)。

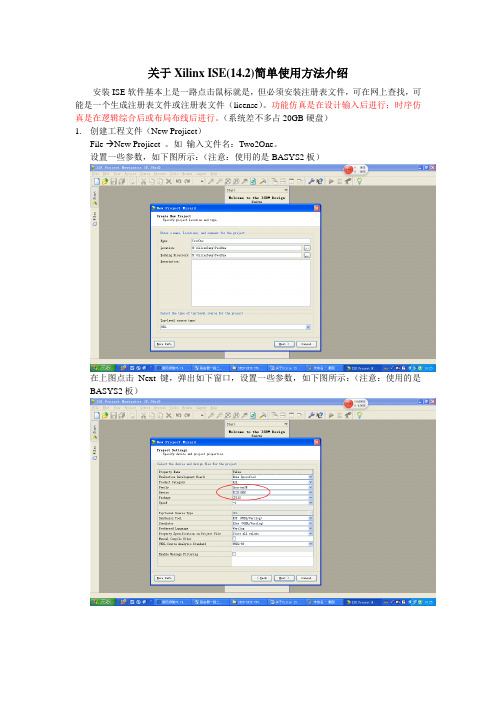

关于Xilinx ISE(14.2)简单使用方法介绍

安装ISE软件基本上是一路点击鼠标就是,但必须安装注册表文件,可在网上查找,可能是一个生成注册表文件或注册表文件(license)。功能仿真是在设计输入后进行;时序仿真是在逻辑综合后或布局布线后进行。(系统差不多占20GB硬盘)

1.创建工程文件(New Projiect)

将运行另外一个程序产生仿真波形图,如下图所示:

详细波形图:

6.管脚适配(为下载做准备)

先创建*.UCF文件

弹出窗口,点击Yes,创建.UCF文件

之后,系统会启动管脚配置程序,然后设计人员根据情况配置管脚,下图为BASYS2板管脚情况,所示:

适配后:

配置好管脚后保存好文件。

7.综合与实现

管脚分配完成之后,必须进行布局布线,如下图所示:

FileNew Projiect。如输入文件名:Two2One。

设置一些参数,如下图所示:(注意:使用的是BASYS2板)

在上图点击Next键,弹出如下窗口,设置一些参数,如下图所示:(注意:使用的是BASYS2板)

2.创建资源文件(New Source)

ProjectNew Source。如输入文件名:One2Two。

选择,如Verilog Test Fxiture,建立用于测试以上资源文件(电路)用的数据文件。建立不同时间段的输入数据,用于产生相应时段的输出波形。

xilinx-ISE在iMPACT下载写好的程序

xilinx-ISE在iMPACT下载写好的程序

在ISE或EDK下生成BIT文件,可通过IMPACT对FPGA进行配制,

bit文件是配制到FPGA内部RAM的,掉电就没有了,

如果需要固化到片外FLASH里面(下载到FLash或EEPROM),则需要将BIT文件转化为mcs文件,通过IMPACT固化到指定的ROM中。

假设已经生成了BIT文件,下面我们来介绍如何进行配制和固化,软件使用的是IMPACT12.2。

一、BIT文件下载

连接好下载器与FPGA开发板JTAG接口,给开发板上电,打开IMPACT软件,

双点击 Boundary Scan,右键选择Initialize Chain,看能否检测到开发板的器件。

JTAG链路中的器件会全部显示出来,双击FPGA器件,添加BIT文件然后点击program就可以了

如果需要固化,则需要将bit文件转换为mcs文件,下面以固化到spi flash为例,xcf rom固化类同。

二、转换BIT文件为MCS文件

点击Create PROM File

弹出下框,按下图流程操作

最后点OK,弹出如下框,点击OK,选择要转换的BIT文件

选中文件后,点击打开

点击generate file,即生成了mcs文件。

三,下载MCS文件

切换到boundary scan,点击add SPI/BPI Flash将生成的MCS文件添加并下载即可,这样就固化到SPI FLASH里去了。

将M0,M1,M2设置成spi flash配制模式,重新上电电试试看,看LED灯是不是跑起来了。

ISE操作说明

ISE操作说明1、双击打开ISE,选择“file->new project”新建一个工程。

2、修改工程保存路径并输入工程名,然后单击next。

3、选定芯片型号如下图所示。

然后一直单击next直到finish。

4、将源文件拷贝到新建的工程中。

5、单击synthesize进行综合。

6、进行引脚分配。

点开User Constraints,双击Assign Package Pins,弹出如下窗口,单击Yes。

7、弹出以下窗口。

8、按以下窗口进行管脚分配。

9、关闭窗口并保存窗口内容。

10、单击Implement Design 进行编译、布局、布线。

11、单击Generate Programing File生成下载文件。

12、单击Configure Device(iMAPCE),进入下载界面。

13、单击finish14、单击Bypass15、选择对应的模块,把**.bit文件加载进来16、加载完成之后会弹出一个警告,单击OK17、右键单击最后一个模块,选择program18、如图选择,单击OK,就可以下载了19、下载完成后,会出现如下图所示的窗口显示program succeeded。

20、以上操作是直接将二进制文件下载到FPGA中,掉电之后将丢失。

为使其重新上电时可自动配置,需要将配置文件下载到prom中保存。

因此,首先要生成prom配置文件。

双击Generate PROM、ACE or JTAG File,进入生成prom配置文件界面。

21、选择“Prepare a PROM File”,单击next。

22、键入要生成的PROM 名称,如下图所示。

23、单击add,添加prom器件。

单击next,直到finish。

24、单击ok。

25、选择二进制文件26、单击No。

27、单击ok。

28、单击Generate File,生成配置文件29、双击Baundary Scan,然后单击重新进行JTAG链扫描。

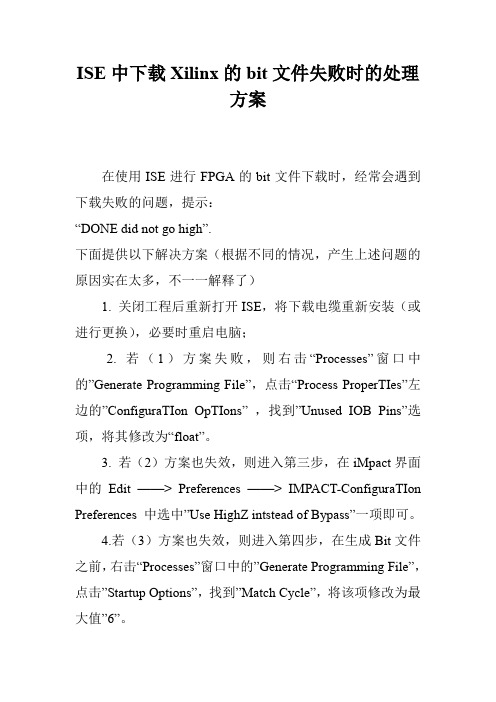

ISE中下载Xilinx的bit文件失败时的处理方案

ISE中下载Xilinx的bit文件失败时的处理

方案

在使用ISE进行FPGA的bit文件下载时,经常会遇到下载失败的问题,提示:

“DONE did not go high”.

下面提供以下解决方案(根据不同的情况,产生上述问题的原因实在太多,不一一解释了)

1. 关闭工程后重新打开ISE,将下载电缆重新安装(或进行更换),必要时重启电脑;

2. 若(1)方案失败,则右击“Processes”窗口中的”Generate Programming File”,点击“Process ProperTIes”左边的”ConfiguraTIon OpTIons” ,找到”Unused IOB Pins”选项,将其修改为“float”。

3. 若(2)方案也失效,则进入第三步,在iMpact界面中的Edit ——> Preferences ——> IMPACT-ConfiguraTIon Preferences 中选中”Use HighZ intstead of Bypass”一项即可。

4.若(3)方案也失效,则进入第四步,在生成Bit文件之前,右击“Processes”窗口中的”Generate Programming File”,点击”Startup Options”,找到”Match Cycle”,将该项修改为最大值”6”。

若以上方案均失效,那实在很抱歉了。

ISE 产生配置文件

1.3如何生成FPGA可以配置文件以及下载步骤1.3.1前言Xilinx Spartan6支持SPI的配置模式。

SPI配置模式对用户来说,无疑是非常有用的。

它不仅简化了硬件电路,而且可以降低硬件成本,同时SPI 芯片的容量又很大,可以满足用户除存储配置文件外存储其他数据的要求,扩展用户应用的范围。

Siga-S16开发板上配置了8Mbit的SPI FLASH,型号为M25P80。

1.3.2 准备工作ISE13.1 版本或更高版本,本演示在ISE13.1 下进行;Siga-S16开发板和USB JTAG仿真器Siga-S16开发板的拨码开关设置为M0:ON, M1:Off,MASTER SPI MODE1.3.3 烧写SPI FLASH1. 启动iMPACT开始—>所有程序—>Xilinx ISE Design Suite 13.1—>ISE—>Accessories—>iMPACT,画面如下:在弹出窗口中选择“Prepare a PROM File”,再选择“OK”。

2.生成mcs 文件生成mcs 文件之前要确定SPI FLASH 的型号以及容量。

在下图弹出的PROM File Formatter界面中的依次选择如下:点击OK后弹出Add Device文件的消息窗口,直接点击OK。

在之后弹出的Add Device文件的窗口选择我们前面ISE中生成的led_test.bit文件,再点击“打开”按钮。

在之后弹出的Add Device文件的消息窗口,直接No。

在之后弹出消息窗口,选择OK完成。

双击ISE iMPACT左边iMPACT Processes界面的“Generate File...”,生成MCS文件。

MCS文件生成成功后在界面会显示“Generate Succeeded”的信息。

3.编程MCS文件到SPI FLASH中双击iMPACT Flows界面下的Boundary Scan选项:再在Boundary Scan界面上右击鼠标,选取Initialize Chain选项:如果出现以下的界面说明已经检测到JTAG链路上的FPGA芯片。

xilinx使用步骤

Xilinx软件使用步骤目录基本操作1. 打开xilinx2. open project3. New project4. 创建新的 .vhd文件5. 建立波形文件6. 综合7. 仿真8. 下载程序到电路板中需要注意的问题1.生成顶层原理图2.建立.ucf文件3. implement时出错的原因4.仿真时的问题基本操作1. 打开xilinx图1 打开xilinx界面2. open project图2 open project图3 查找要打开的.ise文件单击打开后,出现在左侧box中。

图4 open project3. New project顶层文件类型,原理图类型选Schematic,否则选择HDL;单击下一步,通过右侧value各项目,配置器件类型,即FPGA 型号。

注意:此处配置错误的话,综合时会出现放不下或者些不进去的错误。

配置完成后,单击下一步,出现创建源文件对话框如下图所示。

不需做设置更改,直接点击下一步,出现添加现有源对话框如下图所示。

不需做任何设置,直接单击下一步,出现New project information对话框,如下图所示。

确认信息无误后,单击完成,创建的新的project即出现在主页面左侧Sources in project中,如下图所示。

4. 创建新的 .vhd文件右击主页面左侧Sources in project中xc2s200-5pq208,在右键菜单中选择New source,如下图所示;出现New source对话框;左侧选择VHDL Module,右侧输入文件名,如下图所示,单击下一步;出现define vhdl source对话框,输入端口名,输入输出类型和MSB,LSB, 如下图所示,然后单击下一步,出现信息对话框,如下图所示,确认无误后,单击完成。

然后主页面如下图所示:5. 建立波形文件在主页面,编程之后保存。

在如下图所示位置右击.vhd文件,选择new source选项。

xilinx ise13.4安装步骤

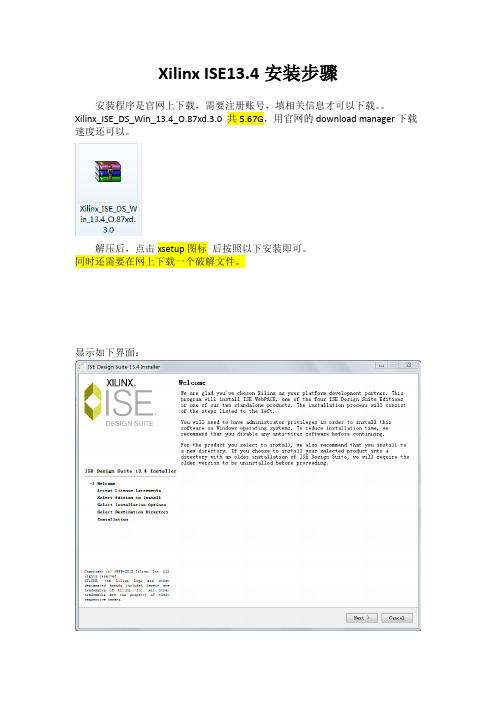

Xilinx ISE13.4安装步骤

安装程序是官网上下载,需要注册账号,填相关信息才可以下载。

Xilinx_ISE_DS_Win_13.4_O.87xd.3.0 共5.67G,用官网的download manager下载速度还可以。

解压后,点击xsetup图标后按照以下安装即可。

同时还需要在网上下载一个破解文件。

显示如下界面:

点击next

选中I accept……,然后next

选中I accept……next,显示如下:

选择需要安装的部分,一般按默认的装

点击next

可以修改默认的目录,然后点击next

直接点击install即可,进入等待当中,可以出去喝个茶,时间比较久,大约一个小时

90%时弹出如下界面

Next

点击Install后

过了一会弹出一个安全框,我点击了安装

之后又弹出一个,同样安装

之后弹出一个有关matlab,我的是2008a,好像不支持,我选择了choose later。

随后显示完成对话框,可以直接点击完成。

同时弹出激活框

选择locate existing license,选择网上下载的license即可。

安装完的启动界面如下:

最后可以打开看看,点击help-manage license……,license管理界面,使用期限。

至此大功告成。

xilinx使用步骤

Xilinx软件使用步骤目录基本操作1. 打开xilinx2. open project3. New project4. 创建新的 .vhd文件5. 建立波形文件6. 综合7. 仿真8. 下载程序到电路板中需要注意的问题1.生成顶层原理图2.建立.ucf文件3. implement时出错的原因4.仿真时的问题基本操作1. 打开xilinx图1 打开xilinx界面2. open project图2 open project图3 查找要打开的.ise文件单击打开后,出现在左侧box中。

图4 open project3. New project顶层文件类型,原理图类型选Schematic,否则选择HDL;单击下一步,通过右侧value各项目,配置器件类型,即FPGA 型号。

注意:此处配置错误的话,综合时会出现放不下或者些不进去的错误。

配置完成后,单击下一步,出现创建源文件对话框如下图所示。

不需做设置更改,直接点击下一步,出现添加现有源对话框如下图所示。

不需做任何设置,直接单击下一步,出现New project information对话框,如下图所示。

确认信息无误后,单击完成,创建的新的project即出现在主页面左侧Sources in project中,如下图所示。

4. 创建新的 .vhd文件右击主页面左侧Sources in project中xc2s200-5pq208,在右键菜单中选择New source,如下图所示;出现New source对话框;左侧选择VHDL Module,右侧输入文件名,如下图所示,单击下一步;出现define vhdl source对话框,输入端口名,输入输出类型和MSB,LSB, 如下图所示,然后单击下一步,出现信息对话框,如下图所示,确认无误后,单击完成。

然后主页面如下图所示:5. 建立波形文件在主页面,编程之后保存。

在如下图所示位置右击.vhd文件,选择new source选项。

XilinxISE软件简单教程课件

Xilinx ISE软件的优缺点

概述Xilinx ISE软件的优点和 缺点,帮助用户全面评估软 件。

Xilinx ISE软件的应用场 景

介绍Xilinx ISE软件广泛应用 于哪些领域和项目,以及其 在每个领域中的优势。

XilinxISE软件简单教程课 件

Xilinx ISE软件简单教程课件为您提供了入门级的教程,让您了解Xilinx ISE软 件的作用、特点以及使用方法。

简介

Xilinx ISE软件是什么?

介绍Xilinx ISE软件是一款功能强大的FPGA开发工具,可以帮助您设计和验证数字电路。

Xilinx ISE软件的作用

解释下载和仿真之间的区别和各自的用途。

3 下载和仿真的流程

讲解下载和仿真的基本步骤,以便用户正确地验证并调试设计。

实例操作

具体实例操作演示

通过示范一个具体的实例,向用户展示Xilinx ISE软 件的使用方法。

实例的说明和分析

对实例进行逐步解析和分析,帮助用户理解设计过 程和结果。

总结

Xilinx ISE软件的功能

解释综合和实现在FPGA设计流 程中的作用和区别。

综合和实现的关系

讨论综合和实现之间的紧密关 联,以及它们在设计迭代中的 作用。

综合和实现的过程

详细描述综合和实现的步骤, 以及如何将设计转换为可下载 的位文件。

下载和仿真

1 下载和仿真的作用

介绍下载和仿真在FPGA设计验证和调试过程中的重要性。

2 下载和仿真的区别

参考资料

相关书籍和文献

提供与Xilinx ISE软件相关的书籍和文献,以便用户进一步学习和深入研究。

光立方开发板程序下载方法及调试过程

光立方开发板程序下载方法及调试过程光立方开发板是一款基于FPGA的硬件开发平台,可执行数字信号处理、数字信号生成、图像和视频处理等任务。

本文将重点介绍在Windows系统下如何下载光立方开发板程序并进行调试。

一、准备工作在开始下载程序之前,我们需要先进行一些准备工作:1.安装Xilinx ISE软件,它是运行并下载FPGA程序的关键软件。

2.下载并安装光立方驱动,并将光立方开发板连接到电脑。

3.下载并安装JTAG烧录器,以便通过JTAG接口向开发板烧录程序。

4.准备好FPGA程序文件。

二、下载程序1.打开Xilinx ISE软件,创建新的工程。

选择FPGA型号并设置工程路径和名称。

2.添加UCF约束文件和FPGA程序文件。

在工程目录下,新建一个.ucf文件,并在ISE工具栏中选择Process-> Generate Programming File。

3.选择工程路径,将程序文件转换成比特流的数据文件。

这个文件后面将用于烧录到开发板上。

4.打开JTAG烧录器软件,然后设置好开发板的连接端口和IP地址。

5.将光立方开发板与电脑连接,并插上电源。

6.在ISE软件中,选择Tools-> iMPACT打开JTAG烧录器。

7.在打开的iMPACT窗口中,选择new project并命名。

8.选择Cable Setup-> Add Cable,将连接端口和IP地址配置给烧录器。

9.在iMPACT软件中选择File-> Open..打开比特流数据文件。

10.右键单击Xilinx硬件设备图标,选择Program,然后程序将开始下载。

下载完成后,iMPACT软件将提示“Successful”.三、调试程序下载完程序后,我们可以开始调试程序。

1.在ISE中打开ISE design suite command prompt,运行openJTAG,连接开发板。

2.连接到开发板后,运行xmd命令,进入调试模式。