Nvision NV1020

华三路由器软件升级指南

NuMicro N9H30系列开发板用户手册说明书

NuMicro®FamilyArm® ARM926EJ-S BasedNuMaker-HMI-N9H30User ManualEvaluation Board for NuMicro® N9H30 SeriesNUMAKER-HMI-N9H30 USER MANUALThe information described in this document is the exclusive intellectual property ofNuvoton Technology Corporation and shall not be reproduced without permission from Nuvoton.Nuvoton is providing this document only for reference purposes of NuMicro microcontroller andmicroprocessor based system design. Nuvoton assumes no responsibility for errors or omissions.All data and specifications are subject to change without notice.For additional information or questions, please contact: Nuvoton Technology Corporation.Table of Contents1OVERVIEW (5)1.1Features (7)1.1.1NuMaker-N9H30 Main Board Features (7)1.1.2NuDesign-TFT-LCD7 Extension Board Features (7)1.2Supporting Resources (8)2NUMAKER-HMI-N9H30 HARDWARE CONFIGURATION (9)2.1NuMaker-N9H30 Board - Front View (9)2.2NuMaker-N9H30 Board - Rear View (14)2.3NuDesign-TFT-LCD7 - Front View (20)2.4NuDesign-TFT-LCD7 - Rear View (21)2.5NuMaker-N9H30 and NuDesign-TFT-LCD7 PCB Placement (22)3NUMAKER-N9H30 AND NUDESIGN-TFT-LCD7 SCHEMATICS (24)3.1NuMaker-N9H30 - GPIO List Circuit (24)3.2NuMaker-N9H30 - System Block Circuit (25)3.3NuMaker-N9H30 - Power Circuit (26)3.4NuMaker-N9H30 - N9H30F61IEC Circuit (27)3.5NuMaker-N9H30 - Setting, ICE, RS-232_0, Key Circuit (28)NUMAKER-HMI-N9H30 USER MANUAL3.6NuMaker-N9H30 - Memory Circuit (29)3.7NuMaker-N9H30 - I2S, I2C_0, RS-485_6 Circuit (30)3.8NuMaker-N9H30 - RS-232_2 Circuit (31)3.9NuMaker-N9H30 - LCD Circuit (32)3.10NuMaker-N9H30 - CMOS Sensor, I2C_1, CAN_0 Circuit (33)3.11NuMaker-N9H30 - RMII_0_PF Circuit (34)3.12NuMaker-N9H30 - RMII_1_PE Circuit (35)3.13NuMaker-N9H30 - USB Circuit (36)3.14NuDesign-TFT-LCD7 - TFT-LCD7 Circuit (37)4REVISION HISTORY (38)List of FiguresFigure 1-1 Front View of NuMaker-HMI-N9H30 Evaluation Board (5)Figure 1-2 Rear View of NuMaker-HMI-N9H30 Evaluation Board (6)Figure 2-1 Front View of NuMaker-N9H30 Board (9)Figure 2-2 Rear View of NuMaker-N9H30 Board (14)Figure 2-3 Front View of NuDesign-TFT-LCD7 Board (20)Figure 2-4 Rear View of NuDesign-TFT-LCD7 Board (21)Figure 2-5 Front View of NuMaker-N9H30 PCB Placement (22)Figure 2-6 Rear View of NuMaker-N9H30 PCB Placement (22)Figure 2-7 Front View of NuDesign-TFT-LCD7 PCB Placement (23)Figure 2-8 Rear View of NuDesign-TFT-LCD7 PCB Placement (23)Figure 3-1 GPIO List Circuit (24)Figure 3-2 System Block Circuit (25)Figure 3-3 Power Circuit (26)Figure 3-4 N9H30F61IEC Circuit (27)Figure 3-5 Setting, ICE, RS-232_0, Key Circuit (28)Figure 3-6 Memory Circuit (29)Figure 3-7 I2S, I2C_0, RS-486_6 Circuit (30)Figure 3-8 RS-232_2 Circuit (31)Figure 3-9 LCD Circuit (32)NUMAKER-HMI-N9H30 USER MANUAL Figure 3-10 CMOS Sensor, I2C_1, CAN_0 Circuit (33)Figure 3-11 RMII_0_PF Circuit (34)Figure 3-12 RMII_1_PE Circuit (35)Figure 3-13 USB Circuit (36)Figure 3-14 TFT-LCD7 Circuit (37)List of TablesTable 2-1 LCD Panel Combination Connector (CON8) Pin Function (11)Table 2-2 Three Sets of Indication LED Functions (12)Table 2-3 Six Sets of User SW, Key Matrix Functions (12)Table 2-4 CMOS Sensor Connector (CON10) Function (13)Table 2-5 JTAG ICE Interface (J2) Function (14)Table 2-6 Expand Port (CON7) Function (16)Table 2-7 UART0 (J3) Function (16)Table 2-8 UART2 (J6) Function (16)Table 2-9 RS-485_6 (SW6~8) Function (17)Table 2-10 Power on Setting (SW4) Function (17)Table 2-11 Power on Setting (S2) Function (17)Table 2-12 Power on Setting (S3) Function (17)Table 2-13 Power on Setting (S4) Function (17)Table 2-14 Power on Setting (S5) Function (17)Table 2-15 Power on Setting (S7/S6) Function (18)Table 2-16 Power on Setting (S9/S8) Function (18)Table 2-17 CMOS Sensor Connector (CON9) Function (19)Table 2-18 CAN_0 (SW9~10) Function (19)NUMAKER-HMI-N9H30 USER MANUAL1 OVERVIEWThe NuMaker-HMI-N9H30 is an evaluation board for GUI application development. The NuMaker-HMI-N9H30 consists of two parts: a NuMaker-N9H30 main board and a NuDesign-TFT-LCD7 extensionboard. The NuMaker-HMI-N9H30 is designed for project evaluation, prototype development andvalidation with HMI (Human Machine Interface) function.The NuMaker-HMI-N9H30 integrates touchscreen display, voice input/output, rich serial port serviceand I/O interface, providing multiple external storage methods.The NuDesign-TFT-LCD7 can be plugged into the main board via the DIN_32x2 extension connector.The NuDesign-TFT-LCD7 includes one 7” LCD which the resolution is 800x480 with RGB-24bits andembedded the 4-wires resistive type touch panel.Figure 1-1 Front View of NuMaker-HMI-N9H30 Evaluation BoardNUMAKER-HMI-N9H30 USER MANUAL Figure 1-2 Rear View of NuMaker-HMI-N9H30 Evaluation Board1.1 Features1.1.1 NuMaker-N9H30 Main Board Features●N9H30F61IEC chip: LQFP216 pin MCP package with DDR (64 MB)●SPI Flash using W25Q256JVEQ (32 MB) booting with quad mode or storage memory●NAND Flash using W29N01HVSINA (128 MB) booting or storage memory●One Micro-SD/TF card slot served either as a SD memory card for data storage or SDIO(Wi-Fi) device●Two sets of COM ports:–One DB9 RS-232 port with UART_0 used 75C3232E transceiver chip can be servedfor function debug and system development.–One DB9 RS-232 port with UART_2 used 75C3232E transceiver chip for userapplication●22 GPIO expansion ports, including seven sets of UART functions●JTAG interface provided for software development●Microphone input and Earphone/Speaker output with 24-bit stereo audio codec(NAU88C22) for I2S interfaces●Six sets of user-configurable push button keys●Three sets of LEDs for status indication●Provides SN65HVD230 transceiver chip for CAN bus communication●Provides MAX3485 transceiver chip for RS-485 device connection●One buzzer device for program applicationNUMAKER-HMI-N9H30 USER MANUAL●Two sets of RJ45 ports with Ethernet 10/100 Mbps MAC used IP101GR PHY chip●USB_0 that can be used as Device/HOST and USB_1 that can be used as HOSTsupports pen drives, keyboards, mouse and printers●Provides over-voltage and over current protection used APL3211A chip●Retain RTC battery socket for CR2032 type and ADC0 detect battery voltage●System power could be supplied by DC-5V adaptor or USB VBUS1.1.2 NuDesign-TFT-LCD7 Extension Board Features●7” resolution 800x480 4-wire resistive touch panel for 24-bits RGB888 interface●DIN_32x2 extension connector1.2 Supporting ResourcesFor sample codes and introduction about NuMaker-N9H30, please refer to N9H30 BSP:https:///products/gui-solution/gui-platform/numaker-hmi-n9h30/?group=Software&tab=2Visit NuForum for further discussion about the NuMaker-HMI-N9H30:/viewforum.php?f=31 NUMAKER-HMI-N9H30 USER MANUALNUMAKER-HMI-N9H30 USER MANUAL2 NUMAKER-HMI-N9H30 HARDWARE CONFIGURATION2.1 NuMaker-N9H30 Board - Front View Combination Connector (CON8)6 set User SWs (K1~6)3set Indication LEDs (LED1~3)Power Supply Switch (SW_POWER1)Audio Codec(U10)Microphone(M1)NAND Flash(U9)RS-232 Transceiver(U6, U12)RS-485 Transceiver(U11)CAN Transceiver (U13)Figure 2-1 Front View of NuMaker-N9H30 BoardFigure 2-1 shows the main components and connectors from the front side of NuMaker-N9H30 board. The following lists components and connectors from the front view:NuMaker-N9H30 board and NuDesign-TFT-LCD7 board combination connector (CON8). This panel connector supports 4-/5-wire resistive touch or capacitance touch panel for 24-bits RGB888 interface.Connector GPIO pin of N9H30 FunctionCON8.1 - Power 3.3VCON8.2 - Power 3.3VCON8.3 GPD7 LCD_CSCON8.4 GPH3 LCD_BLENCON8.5 GPG9 LCD_DENCON8.7 GPG7 LCD_HSYNCCON8.8 GPG6 LCD_CLKCON8.9 GPD15 LCD_D23(R7)CON8.10 GPD14 LCD_D22(R6)CON8.11 GPD13 LCD_D21(R5)CON8.12 GPD12 LCD_D20(R4)CON8.13 GPD11 LCD_D19(R3)CON8.14 GPD10 LCD_D18(R2)CON8.15 GPD9 LCD_D17(R1)CON8.16 GPD8 LCD_D16(R0)CON8.17 GPA15 LCD_D15(G7)CON8.18 GPA14 LCD_D14(G6)CON8.19 GPA13 LCD_D13(G5)CON8.20 GPA12 LCD_D12(G4)CON8.21 GPA11 LCD_D11(G3)CON8.22 GPA10 LCD_D10(G2)CON8.23 GPA9 LCD_D9(G1) NUMAKER-HMI-N9H30 USER MANUALCON8.24 GPA8 LCD_D8(G0)CON8.25 GPA7 LCD_D7(B7)CON8.26 GPA6 LCD_D6(B6)CON8.27 GPA5 LCD_D5(B5)CON8.28 GPA4 LCD_D4(B4)CON8.29 GPA3 LCD_D3(B3)CON8.30 GPA2 LCD_D2(B2)CON8.31 GPA1 LCD_D1(B1)CON8.32 GPA0 LCD_D0(B0)CON8.33 - -CON8.34 - -CON8.35 - -CON8.36 - -CON8.37 GPB2 LCD_PWMCON8.39 - VSSCON8.40 - VSSCON8.41 ADC7 XPCON8.42 ADC3 VsenCON8.43 ADC6 XMCON8.44 ADC4 YMCON8.45 - -CON8.46 ADC5 YPCON8.47 - VSSCON8.48 - VSSCON8.49 GPG0 I2C0_CCON8.50 GPG1 I2C0_DCON8.51 GPG5 TOUCH_INTCON8.52 - -CON8.53 - -CON8.54 - -CON8.55 - -NUMAKER-HMI-N9H30 USER MANUAL CON8.56 - -CON8.57 - -CON8.58 - -CON8.59 - VSSCON8.60 - VSSCON8.61 - -CON8.62 - -CON8.63 - Power 5VCON8.64 - Power 5VTable 2-1 LCD Panel Combination Connector (CON8) Pin Function●Power supply switch (SW_POWER1): System will be powered on if the SW_POWER1button is pressed●Three sets of indication LEDs:LED Color DescriptionsLED1 Red The system power will beterminated and LED1 lightingwhen the input voltage exceeds5.7V or the current exceeds 2A.LED2 Green Power normal state.LED3 Green Controlled by GPH2 pin Table 2-2 Three Sets of Indication LED Functions●Six sets of user SW, Key Matrix for user definitionKey GPIO pin of N9H30 FunctionK1 GPF10 Row0 GPB4 Col0K2 GPF10 Row0 GPB5 Col1K3 GPE15 Row1 GPB4 Col0K4 GPE15 Row1 GPB5 Col1K5 GPE14 Row2 GPB4 Col0K6GPE14 Row2GPB5 Col1 Table 2-3 Six Sets of User SW, Key Matrix Functions●NAND Flash (128 MB) with Winbond W29N01HVS1NA (U9)●Microphone (M1): Through Nuvoton NAU88C22 chip sound input●Audio CODEC chip (U10): Nuvoton NAU88C22 chip connected to N9H30 using I2Sinterface–SW6/SW7/SW8: 1-2 short for RS-485_6 function and connected to 2P terminal (CON5and J5)–SW6/SW7/SW8: 2-3 short for I2S function and connected to NAU88C22 (U10).●CMOS Sensor connector (CON10, SW9~10)–SW9~10: 1-2 short for CAN_0 function and connected to 2P terminal (CON11)–SW9~10: 2-3 short for CMOS sensor function and connected to CMOS sensorconnector (CON10)Connector GPIO pin of N9H30 FunctionCON10.1 - VSSCON10.2 - VSSNUMAKER-HMI-N9H30 USER MANUALCON10.3 - Power 3.3VCON10.4 - Power 3.3VCON10.5 - -CON10.6 - -CON10.7 GPI4 S_PCLKCON10.8 GPI3 S_CLKCON10.9 GPI8 S_D0CON10.10 GPI9 S_D1CON10.11 GPI10 S_D2CON10.12 GPI11 S_D3CON10.13 GPI12 S_D4CON10.14 GPI13 S_D5CON10.15 GPI14 S_D6CON10.16 GPI15 S_D7CON10.17 GPI6 S_VSYNCCON10.18 GPI5 S_HSYNCCON10.19 GPI0 S_PWDNNUMAKER-HMI-N9H30 USER MANUAL CON10.20 GPI7 S_nRSTCON10.21 GPG2 I2C1_CCON10.22 GPG3 I2C1_DCON10.23 - VSSCON10.24 - VSSTable 2-4 CMOS Sensor Connector (CON10) FunctionNUMAKER-HMI-N9H30 USER MANUAL2.2NuMaker-N9H30 Board - Rear View5V In (CON1)RS-232 DB9 (CON2,CON6)Expand Port (CON7)Speaker Output (J4)Earphone Output (CON4)Buzzer (BZ1)System ResetSW (SW5)SPI Flash (U7,U8)JTAG ICE (J2)Power ProtectionIC (U1)N9H30F61IEC (U5)Micro SD Slot (CON3)RJ45 (CON12, CON13)USB1 HOST (CON15)USB0 Device/Host (CON14)CAN_0 Terminal (CON11)CMOS Sensor Connector (CON9)Power On Setting(SW4, S2~S9)RS-485_6 Terminal (CON5)RTC Battery(BT1)RMII PHY (U14,U16)Figure 2-2 Rear View of NuMaker-N9H30 BoardFigure 2-2 shows the main components and connectors from the rear side of NuMaker-N9H30 board. The following lists components and connectors from the rear view:● +5V In (CON1): Power adaptor 5V input ●JTAG ICE interface (J2) ConnectorGPIO pin of N9H30Function J2.1 - Power 3.3V J2.2 GPJ4 nTRST J2.3 GPJ2 TDI J2.4 GPJ1 TMS J2.5 GPJ0 TCK J2.6 - VSS J2.7 GPJ3 TD0 J2.8-RESETTable 2-5 JTAG ICE Interface (J2) Function●SPI Flash (32 MB) with Winbond W25Q256JVEQ (U7); only one (U7 or U8) SPI Flashcan be used●System Reset (SW5): System will be reset if the SW5 button is pressed●Buzzer (BZ1): Control by GPB3 pin of N9H30●Speaker output (J4): Through the NAU88C22 chip sound output●Earphone output (CON4): Through the NAU88C22 chip sound output●Expand port for user use (CON7):Connector GPIO pin of N9H30 FunctionCON7.1 - Power 3.3VCON7.2 - Power 3.3VCON7.3 GPE12 UART3_TXDCON7.4 GPH4 UART1_TXDCON7.5 GPE13 UART3_RXDCON7.6 GPH5 UART1_RXDCON7.7 GPB0 UART5_TXDCON7.8 GPH6 UART1_RTSCON7.9 GPB1 UART5_RXDCON7.10 GPH7 UART1_CTSCON7.11 GPI1 UART7_TXDNUMAKER-HMI-N9H30 USER MANUAL CON7.12 GPH8 UART4_TXDCON7.13 GPI2 UART7_RXDCON7.14 GPH9 UART4_RXDCON7.15 - -CON7.16 GPH10 UART4_RTSCON7.17 - -CON7.18 GPH11 UART4_CTSCON7.19 - VSSCON7.20 - VSSCON7.21 GPB12 UART10_TXDCON7.22 GPH12 UART8_TXDCON7.23 GPB13 UART10_RXDCON7.24 GPH13 UART8_RXDCON7.25 GPB14 UART10_RTSCON7.26 GPH14 UART8_RTSCON7.27 GPB15 UART10_CTSCON7.28 GPH15 UART8_CTSCON7.29 - Power 5VCON7.30 - Power 5VTable 2-6 Expand Port (CON7) Function●UART0 selection (CON2, J3):–RS-232_0 function and connected to DB9 female (CON2) for debug message output.–GPE0/GPE1 connected to 2P terminal (J3).Connector GPIO pin of N9H30 Function J3.1 GPE1 UART0_RXDJ3.2 GPE0 UART0_TXDTable 2-7 UART0 (J3) Function●UART2 selection (CON6, J6):–RS-232_2 function and connected to DB9 female (CON6) for debug message output –GPF11~14 connected to 4P terminal (J6)Connector GPIO pin of N9H30 Function J6.1 GPF11 UART2_TXDJ6.2 GPF12 UART2_RXDJ6.3 GPF13 UART2_RTSJ6.4 GPF14 UART2_CTSTable 2-8 UART2 (J6) Function●RS-485_6 selection (CON5, J5, SW6~8):–SW6~8: 1-2 short for RS-485_6 function and connected to 2P terminal (CON5 and J5) –SW6~8: 2-3 short for I2S function and connected to NAU88C22 (U10)Connector GPIO pin of N9H30 FunctionSW6:1-2 shortGPG11 RS-485_6_DISW6:2-3 short I2S_DOSW7:1-2 shortGPG12 RS-485_6_ROSW7:2-3 short I2S_DISW8:1-2 shortGPG13 RS-485_6_ENBSW8:2-3 short I2S_BCLKNUMAKER-HMI-N9H30 USER MANUALTable 2-9 RS-485_6 (SW6~8) FunctionPower on setting (SW4, S2~9).SW State FunctionSW4.2/SW4.1 ON/ON Boot from USB SW4.2/SW4.1 ON/OFF Boot from eMMC SW4.2/SW4.1 OFF/ON Boot from NAND Flash SW4.2/SW4.1 OFF/OFF Boot from SPI Flash Table 2-10 Power on Setting (SW4) FunctionSW State FunctionS2 Short System clock from 12MHzcrystalS2 Open System clock from UPLL output Table 2-11 Power on Setting (S2) FunctionSW State FunctionS3 Short Watchdog Timer OFFS3 Open Watchdog Timer ON Table 2-12 Power on Setting (S3) FunctionSW State FunctionS4 Short GPJ[4:0] used as GPIO pinS4Open GPJ[4:0] used as JTAG ICEinterfaceTable 2-13 Power on Setting (S4) FunctionSW State FunctionS5 Short UART0 debug message ONS5 Open UART0 debug message OFFTable 2-14 Power on Setting (S5) FunctionSW State FunctionS7/S6 Short/Short NAND Flash page size 2KBS7/S6 Short/Open NAND Flash page size 4KBS7/S6 Open/Short NAND Flash page size 8KBNUMAKER-HMI-N9H30 USER MANUALS7/S6 Open/Open IgnoreTable 2-15 Power on Setting (S7/S6) FunctionSW State FunctionS9/S8 Short/Short NAND Flash ECC type BCH T12S9/S8 Short/Open NAND Flash ECC type BCH T15S9/S8 Open/Short NAND Flash ECC type BCH T24S9/S8 Open/Open IgnoreTable 2-16 Power on Setting (S9/S8) FunctionCMOS Sensor connector (CON9, SW9~10)–SW9~10: 1-2 short for CAN_0 function and connected to 2P terminal (CON11).–SW9~10: 2-3 short for CMOS sensor function and connected to CMOS sensorconnector (CON9).Connector GPIO pin of N9H30 FunctionCON9.1 - VSSCON9.2 - VSSCON9.3 - Power 3.3VCON9.4 - Power 3.3V NUMAKER-HMI-N9H30 USER MANUALCON9.5 - -CON9.6 - -CON9.7 GPI4 S_PCLKCON9.8 GPI3 S_CLKCON9.9 GPI8 S_D0CON9.10 GPI9 S_D1CON9.11 GPI10 S_D2CON9.12 GPI11 S_D3CON9.13 GPI12 S_D4CON9.14 GPI13 S_D5CON9.15 GPI14 S_D6CON9.16 GPI15 S_D7CON9.17 GPI6 S_VSYNCCON9.18 GPI5 S_HSYNCCON9.19 GPI0 S_PWDNCON9.20 GPI7 S_nRSTCON9.21 GPG2 I2C1_CCON9.22 GPG3 I2C1_DCON9.23 - VSSCON9.24 - VSSTable 2-17 CMOS Sensor Connector (CON9) Function●CAN_0 Selection (CON11, SW9~10):–SW9~10: 1-2 short for CAN_0 function and connected to 2P terminal (CON11) –SW9~10: 2-3 short for CMOS sensor function and connected to CMOS sensor connector (CON9, CON10)SW GPIO pin of N9H30 FunctionSW9:1-2 shortGPI3 CAN_0_RXDSW9:2-3 short S_CLKSW10:1-2 shortGPI4 CAN_0_TXDSW10:2-3 short S_PCLKTable 2-18 CAN_0 (SW9~10) Function●USB0 Device/HOST Micro-AB connector (CON14), where CON14 pin4 ID=1 is Device,ID=0 is HOST●USB1 for USB HOST with Type-A connector (CON15)●RJ45_0 connector with LED indicator (CON12), RMII PHY with IP101GR (U14)●RJ45_1 connector with LED indicator (CON13), RMII PHY with IP101GR (U16)●Micro-SD/TF card slot (CON3)●SOC CPU: Nuvoton N9H30F61IEC (U5)●Battery power for RTC 3.3V powered (BT1, J1), can detect voltage by ADC0●RTC power has 3 sources:–Share with 3.3V I/O power–Battery socket for CR2032 (BT1)–External connector (J1)●Board version 2.1NUMAKER-HMI-N9H30 USER MANUAL2.3 NuDesign-TFT-LCD7 -Front ViewFigure 2-3 Front View of NuDesign-TFT-LCD7 BoardFigure 2-3 shows the main components and connectors from the Front side of NuDesign-TFT-LCD7board.7” resolution 800x480 4-W resistive touch panel for 24-bits RGB888 interface2.4 NuDesign-TFT-LCD7 -Rear ViewFigure 2-4 Rear View of NuDesign-TFT-LCD7 BoardFigure 2-4 shows the main components and connectors from the rear side of NuDesign-TFT-LCD7board.NuMaker-N9H30 and NuDesign-TFT-LCD7 combination connector (CON1).NUMAKER-HMI-N9H30 USER MANUAL 2.5 NuMaker-N9H30 and NuDesign-TFT-LCD7 PCB PlacementFigure 2-5 Front View of NuMaker-N9H30 PCB PlacementFigure 2-6 Rear View of NuMaker-N9H30 PCB PlacementNUMAKER-HMI-N9H30 USER MANUALFigure 2-7 Front View of NuDesign-TFT-LCD7 PCB PlacementFigure 2-8 Rear View of NuDesign-TFT-LCD7 PCB Placement3 NUMAKER-N9H30 AND NUDESIGN-TFT-LCD7 SCHEMATICS3.1 NuMaker-N9H30 - GPIO List CircuitFigure 3-1 shows the N9H30F61IEC GPIO list circuit.Figure 3-1 GPIO List Circuit NUMAKER-HMI-N9H30 USER MANUAL3.2 NuMaker-N9H30 - System Block CircuitFigure 3-2 shows the System Block Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-2 System Block Circuit3.3 NuMaker-N9H30 - Power CircuitFigure 3-3 shows the Power Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-3 Power Circuit3.4 NuMaker-N9H30 - N9H30F61IEC CircuitFigure 3-4 shows the N9H30F61IEC Circuit.Figure 3-4 N9H30F61IEC CircuitNUMAKER-HMI-N9H30 USER MANUAL3.5 NuMaker-N9H30 - Setting, ICE, RS-232_0, Key CircuitFigure 3-5 shows the Setting, ICE, RS-232_0, Key Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-5 Setting, ICE, RS-232_0, Key Circuit3.6 NuMaker-N9H30 - Memory CircuitFigure 3-6 shows the Memory Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-6 Memory Circuit3.7 NuMaker-N9H30 - I2S, I2C_0, RS-485_6 CircuitFigure 3-7 shows the I2S, I2C_0, RS-486_6 Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-7 I2S, I2C_0, RS-486_6 Circuit3.8 NuMaker-N9H30 - RS-232_2 CircuitFigure 3-8 shows the RS-232_2 Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-8 RS-232_2 Circuit3.9 NuMaker-N9H30 - LCD CircuitFigure 3-9 shows the LCD Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-9 LCD Circuit3.10 NuMaker-N9H30 - CMOS Sensor, I2C_1, CAN_0 CircuitFigure 3-10 shows the CMOS Sensor,I2C_1, CAN_0 Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-10 CMOS Sensor, I2C_1, CAN_0 Circuit3.11 NuMaker-N9H30 - RMII_0_PF CircuitFigure 3-11 shows the RMII_0_RF Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-11 RMII_0_PF Circuit3.12 NuMaker-N9H30 - RMII_1_PE CircuitFigure 3-12 shows the RMII_1_PE Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-12 RMII_1_PE Circuit3.13 NuMaker-N9H30 - USB CircuitFigure 3-13 shows the USB Circuit.NUMAKER-HMI-N9H30 USER MANUALFigure 3-13 USB Circuit3.14 NuDesign-TFT-LCD7 - TFT-LCD7 CircuitFigure 3-14 shows the TFT-LCD7 Circuit.Figure 3-14 TFT-LCD7 CircuitNUMAKER-HMI-N9H30 USER MANUAL4 REVISION HISTORYDate Revision Description2022.03.24 1.00 Initial version NUMAKER-HMI-N9H30 USER MANUALNUMAKER-HMI-N9H30 USER MANUALImportant NoticeNuvoton Products are neither intended nor warranted for usage in systems or equipment, anymalfunction or failure of which may cause loss of human life, bodily injury or severe propertydamage. Such applications are deemed, “Insecure Usage”.Insecure usage includes, but is not limited to: equipment for surgical implementation, atomicenergy control instruments, airplane or spaceship instruments, the control or operation ofdynamic, brake or safety systems designed for vehicular use, traffic signal instruments, all typesof safety devices, and other applications intended to support or sustain life.All Insecure Usage shall be made at customer’s risk, and in the event that third parties lay claimsto Nuvoton as a result of customer’s Insecure Usage, custome r shall indemnify the damagesand liabilities thus incurred by Nuvoton.。

NVIDIA RTX A5000 说明书

NVIDIA RTX A5000PERFECTLY BALANCED. BLAZING PERFORMANCE.Amplified Performance for ProfessionalsThe NVIDIA RTX ™ A5000 delivers the power, performance, capabilities, and reliability professionals need to bring their boldest ideas to life. Built on the NVIDIA Ampere architecture, the RTX A5000 combines 64 second-generation RT Cores, 256 third-generation Tensor Cores, and 8,192 CUDA ® cores with 24 GB of graphics memory to supercharge rendering, AI, graphics, and compute tasks. Connect two RTX A5000s with NVIDIA NVLink 1 to scale memory and performance with multi-GPU configurations 2, allowing professionals to work with memory intensive tasks such as large models, ultra-high resolution rendering, and complex compute workloads. Support for NVIDIA virtual GPU software increases the versatility for enterprise deployments.NVIDIA RTX professional graphics cards are certified with a broad range of professional applications, tested by leading independent software vendors (ISVs) and workstation manufacturers, and backed by a global team of support specialists. Get the peace of mind needed to focus on what matters with the premier visual computing solution for mission-critical business.SPECIFICATIONSGPU memory 24 GB GDDR6Memory interface 384-bit Memory bandwidth768 GB/s Error-correcting code (ECC)Yes NVIDIA Ampere architecture-based CUDA Cores 8,192NVIDIA third-generation Tensor Cores256NVIDIA second-generation RT Cores64Single-precision performance 27.8 TFLOPS 5RT Core performance 54.2 TFLOPS 5Tensor performance 222.2 TFLOPS 6NVIDIA NVLinkLow profile bridges connect two NVIDIA RTX A5000 GPUs 1NVIDIA NVLink bandwidth 112.5 GB/s (bidirectional)System interface PCI Express 4.0 x16Power consumptionTotal board power: 230 W Thermal solution ActiveForm factor 4.4” H x 10.5” L, dual slot, full height Display connectors 4x DisplayPort 1.4a 7Max simultaneous displays4x 4096 x 2160 @ 120 Hz, 4x 5120 x 2880 @ 60 Hz, 2x 7680 x 4320 @ 60 Hz Power connector 1x 8-pin PCIeEncode/decode engines 1x encode, 2x decode (+AV1 decode) VR readyYesvGPU software support 7NVIDIA vPC/vApps, NVIDIA RTX Virtual Workstation, NVIDIA Virtual Compute ServervGPU profiles supported See the Virtual GPU Licensing Guide Graphics APIs DirectX 12.078, Shader Model 5.178, OpenGL 4.689, Vulkan 1.29Compute APIsCUDA, DirectCompute, OpenCL ™Features>PCI Express Gen 4>Four DisplayPort 1.4a connectors >AV1 decode support >DisplayPort with audio >3D stereo support with stereo connector >NVIDIA GPUDirect ®for Video support>NVIDIA virtual GPU (vGPU) software support >NVIDIA Quadro ® Sync II 3 compatibility >NVIDIA RTX Experience ™>NVIDIA RTX Desktop Manager software >NVIDIA RTX IO support >HDCP 2.2 support>NVIDIA Mosaic 4 technologyNVIDIA RTX A5000 | DATASHEET | APR21To learn more about the NVIDIA RTX A5000, visit /nvidia-rtx-a50001 NVIDIA NVLink sold separately. |2 Connecting two RTX A5000 cards with NVLink to scale performance and memorycapacity to 48GB is only possible if your application supports NVLink technology. Please contact your application provider to confirm their support for NVLink. | 3 Quadro Sync II card sold separately. | 4 Windows 10 and Linux. | 5 Peak rates based on GPU Boost Clock. | 6 Effective teraFLOPS (TFLOPS) using the new sparsity feature. | 7 Display ports are on by default for RTX A5000. Display ports are not active when using vGPU software. | 8 GPU supports DX 12.0 API, hardware feature level 12 + 1. | 9 Product is based on a published Khronos specification and is expected to pass the Khronos conformance testing process when available. Current conformance status can be found at /conformance© 2021 NVIDIA Corporation. All rights reserved. NVIDIA, the NVIDIA logo, CUDA, GPUDirect, NVLink, Quadro, RTX Experience, and RTX are trademarks and/or registered trademarks of NVIDIA Corporation in the U.S. and other countries. Other company and product names may be trademarks of the respective companies with which they are associated. All other trademarks are property of their respective owners.PNY Part Number VCNRTXA5000-PB。

技术资料服务器

4

支持 RAID0,1,1E RAID 存储 支持带电池、高缓存的高性能 RAID 卡 最大支持内置 5 块 3.5 寸 SATA 硬盘或 8 块 3.5 寸 SAS 热插拔硬盘 1 PCI-E 2.0 X16, I/O 扩展槽 1 PCI-E 2.0 X4(in X16 slot), 1 PCI-E X4 (in X8 slot), 2 PCI 32bit/33MHz 集成 I/O 端口 2 个 RJ45 网络接口、4 个 USB 接口、1 个后置 VGA 接口、1 个后置串口、 1 个 PS2 键盘、1 个鼠标接口 集成高性能双千兆网卡,支持网络唤醒,网络冗余,负载均衡等网络高级 特性 500W 单电,支持 600W 双电 集成 32MB 显存显卡 标配 DVD 光驱 支持 CPU 温度、系统电压、风扇转速等的监控;支持 AC 断电恢复 Windows 2003 server 32bit,Windows 2003 server 64bit,Windows 2008 支持操作系统 server 32bit, Windows 2008 server 64bit, RedHat Enterprise Linux5.3 32bit,RedHat Enterprise Linux5.3 64bit(根据所选的配置不同,所 支持的操作系统种类不同) 工作环境温度 电源电压 国际认证 机箱 5℃~35℃ 110-240V ISO9001 国际质量管理体系 ISO14001 国际环境管理体系 塔式:高 433mm,宽 220mm,深 607mm

性能 单路双核、四核英特尔®至强® 处理器(包括 UP 45 纳米处理 器) 可靠 改进型 38°散热机箱 ECC 内存技术 集成 SATA RAID0,1,10

Xeon 3xxx 系列处理器

VENUS继电保护测试仪硬件说明书_新660C

应使插头、耦合器、开关保持随时可操作状态;必须放置外部电源,以便可以随时 开启仪器。 z 连接到 VENUS 上的附件必须满足相关的 IEC 或 ISO 标准(如 IEC 60950 标准,该 标准适用于数据处理设备)。 z VENUS 在海拔低于 2000 米处可以按照额定功率运行。 z 只有受过继电保护测试技术培训及使用过继电保护测试设备的人员才能操作 VENUS。不正确使用 VENUS 会对设备造成严重伤害。 z VENUS 不能用于瓦斯爆炸存在的地方。 z 制造商或授权服务经销商提供服务之前,用户不要对设备内部进行维修。当以下几 种情况发生时,请不要使用 VENUS: a) 电源线或插头损坏。 b) VENUS 不能正常工作。 c) VENUS 已经损坏。 d) VENUS 掉进水里。 e) 如果 VENUS 噪音很大或者突然有尖锐的声音,如果输出的空气太热或味道很难

VENUS 继电保护测试仪硬件说明书

目录

......................................................................................................................................1 第一章 产品功能简介 ................................................................................................................4 第二章 硬件介绍 ........................................................................................................................5

英伟达nvidia NVS系列显卡

英伟达nvidia显卡quadro nvs 3100m参数表以及性能介绍2010-02-03 15:49:05采用nvidia(英伟达)cuda技术的nvidia(英伟达)nvs gpu(图形处理器)可最多搭载48个处理器核心,其大规模计算性能可以加速视频和图片编辑、分析以及地理影像处理,其速度比主流cpu最高提升10倍1nvidia quadro nvs架构如今扩展至商用笔记型计算机市场。

结合领先业界的硬件与软件,开发出一套完整的解决方案,nvidia quadro nvs笔记型计算机解决方案提供符合现今专业人士要求的可靠度、稳定度、易用性,并通过各种商业应用软件的兼容性测试。

不论您身处在办公室或外出,都能透过搭载nvidia quadro nvs 110m的笔记型计算机,随时随地执行各种商务应用。

gpu技术规格:cuada核心 16cuda并行处理器核心 72显存技术规格:显存总容量最大512mmb显存位宽 64-bit核心频率 (mhz) 1470支持的特性:directcomputer 支持opengl 支持directx 10 支持h.264、vc1、mpeg2 视频解码器支持nview显示器管理软件支持hdmi 7.1 声道高清音频支持purevideo高清1080p 支持支持hdmi 1.3 最大1920x1080支持pci express 2.0 支持支持vga 模拟显示器最大 2048x1536支持displayport 多显示器模式最大2560x1600hdcp 内容保护支持全规格蓝光解码支持- 使视频格式转换软件的速度实现最高达10倍的提升,例如elemental公司出品的badaboom软件、pegasys公司出品的tmpgenc 4.0软件。

另外,利用muvee reveal将影集打造成幻灯片电影,还可以利用motiondsp公司出品的vreveal软件自动提升视频片段的清晰度。

AVer Document Camera Setup Guide

Setup your AVer Document Camera from home!Please first identify which AVer document camera you are using to know what software to install.A+ Suite (Sphere2 on Win10/Mac) or Sphere Lite (Chromebooks): AVer U70+, AVer U50, AVer M70HD, AVer 300AFHD, AVer F70W, AVer F50-8M, AVer F17-8M, M17-13MAVerTouch (Win10/Mac): AVer M15W, AVer M15-13M, AVer M70WA+ Interactive Software (Old Version on Win/Mac): V300AF ASIC, SPC300 ASIC, SPC300 +, CP130, CP150, CP300, SPB350, SPB370, CP135, CP155, CP355, V355AF, V310AF, SPB350+, V300AF+, F30, F50, U10, U15, AP20,M50, W30Sphere (Old Version on Win/Mac): PL50, SPB350, SPB370, SPB350+, M50, M70, V300AF+, F50, F30, F15 U15, W30A+ Suite (Sphere2):1.Download the A+ Suite software on your computer, go to:https:///education/support/aplus-suiteSelect the OS you are using to download the software (we will use Win10 in this tutorial)2.Open the downloaded .exe file to start the installationFollow the setup wizard to install the A+ Suite software3.After installation is completed, open the Sphere2 software4.Plug in the power adapter to your document camera and turn it on by pressing the power button (does notapply to U-series doc cams, your document camera may look different than the one pictured)5.Locate a USB port on your computer and connect your camera to it via USB cable that is included6.Select the visualizer icon on the top right of the Sphere2 software and select your camera7.You are now connected to your AVer document camera and can begin teaching!If you own an AVer F70W and wish to connect to your computer wirelessly, please follow this guide: https:///education/downloads/F70WV2-Quick-Guide-EN-v5-2020-02-24.pdfSphere Lite (Chromebook):1.Download the Sphere Lite software on your Chromebook, go to:https:///webstore/detail/sphere-lite/bhmibpbadaengbikmoglphhlhioajdjn?hl=enunch Sphere Lite app after installing3.Plug in the power adapter to your document camera and turn it on by pressing the power button (does notapply to U-series doc cams, your document camera may look different than the one pictured)4.Locate a USB port on your Chromebook and connect your camera to it via USB cable that is included5.Select your camera on the bottom left. You are now connected to your AVer document camera and can beginteaching!AVerTouch:1.Download the AVerTouch software on your computer, go to:https:///education/support/avertouchSelect the OS you are using to download the software (we will use Win10 in this tutorial)2.Unzip the downloaded .zip file3.Open the extracted folder and run the .exe to start the installation4.Follow the setup wizard to install the AVerTouch software5.After installation is completed, open the AVerTouch software6.Plug in the power adapter to your document camera and turn it on by pressing the power button (yourdocument camera may look different than the one pictured)7.Locate a USB port on your computer and connect your camera to it via USB cable that is includedNote: For M15W/M70W users, please make sure WiFi is turned off when trying to do a USB connection 8.The connected visualizer will appear within the AVerTouch software. Click the play icon to connect to thecameraIf you own an AVer M15W/M70W and wish to connect to your computer wirelessly, please follow this guide: M15W: https:///education/downloads/M15W-instruction-manual-EN-2019-12-20.pdfM70W: https:///education/downloads/M70W-instruction-manual-EN-v1-2019-12-20.pdfA+ Interactive Software:1.Download the A+ Interactive Software on your computer, go to:https:///education/support/averplusSelect the OS you are using to download the software2.Unzip the downloaded .zip file3.Open the extracted folder and run the .exe to start the installation4.Follow the setup wizard to install the A+ Interactive Software5.After installation is completed, open the A+ Interactive Software6.Power on and connect your doc cam to your computer via USB cable7.Select your visualizer within the software and you are now connected!Sphere:1.Download the Sphere on your computer, go to:https:///education/support/sphereSelect the OS you are using to download the software2.Run the downloaded .exe to start the installation3.Follow the setup wizard to install the Sphere software4.After installation is completed, open the Sphere Software5.Power on and connect your doc cam to your computer via USB cable6.Select your visualizer within the software and you are now connected!Using your AVer Document Camera with other platforms (Zoom, Skype, Google Hangout).Open up your software of choice and connect your AVer document camera to your computer via USB cable.Select your AVer document camera as your visualizer and you are successfully connected!(Please refer to Zoom, Skype, or Hangout user guides to navigate through their software)Zoom:https:///hc/en-us/articles/201362033-Getting-Started-on-Windows-and-MacSkype:https:///en/skype/windows-desktop/start/Hangout:https:///hangouts/?hl=en#topic=6386410Note: The following AVer doc cams are not UVC compliant and are not compatible with other platforms: F50, M70, PL50, W30, W30HD, Tabcam, 355AF, M50More HelpFor FAQs, technical support, software and instruction manual download, please visit:https:///education/support/Contact InformationAVer Information Inc.668 Mission Ct. Fremont, CA 94539, USAToll-free: 1(877)528-7824Local: 1(408)263-3828********************。

nvflash命令参数

nvflash命令参数一、引言nvflash是一款用于NVIDIA显卡刷写BIOS的工具软件,它提供了丰富的命令参数,可以实现对显卡的各种操作。

本文将对nvflash 命令参数进行详细解析,以帮助读者更好地了解和使用该工具。

二、命令参数解析1. -b 参数:用于备份显卡的BIOS。

使用该参数后,nvflash会将显卡的BIOS保存到当前目录下,以备份为名。

2. -r 参数:用于恢复显卡的BIOS。

使用该参数后,nvflash会将当前目录下以备份为名的BIOS文件刷写回显卡,以恢复原始设置。

3. -f 参数:用于强制刷写显卡的BIOS。

使用该参数后,nvflash 会忽略显卡的保护机制,强制刷写BIOS,慎用。

4. -p 参数:用于指定刷写显卡的PCI总线ID。

使用该参数后,nvflash会只对指定PCI总线ID的显卡进行操作。

5. -u 参数:用于解锁显卡的保护机制。

使用该参数后,nvflash 会解除显卡的保护,允许刷写BIOS。

6. -y 参数:用于自动回答“是”或“否”的问题。

使用该参数后,nvflash会在需要用户确认时自动选择“是”。

7. -s 参数:用于显示显卡的状态信息。

使用该参数后,nvflash 会输出显卡的型号、驱动版本等详细信息。

8. -l 参数:用于列出系统中所有可刷写的显卡。

使用该参数后,nvflash会输出系统中所有显卡的PCI总线ID和型号。

9. -i 参数:用于指定刷写显卡的BIOS文件。

使用该参数后,nvflash会刷写指定路径下的BIOS文件到显卡。

10. -d 参数:用于禁用显卡的保护机制。

使用该参数后,nvflash 会禁用显卡的保护,允许修改显卡的设置。

11. -e 参数:用于擦除显卡的BIOS。

使用该参数后,nvflash会将显卡的BIOS擦除,相当于将显卡恢复到出厂设置。

12. -x 参数:用于导出显卡的BIOS。

使用该参数后,nvflash会将显卡的BIOS导出到当前目录下,以导出为名。

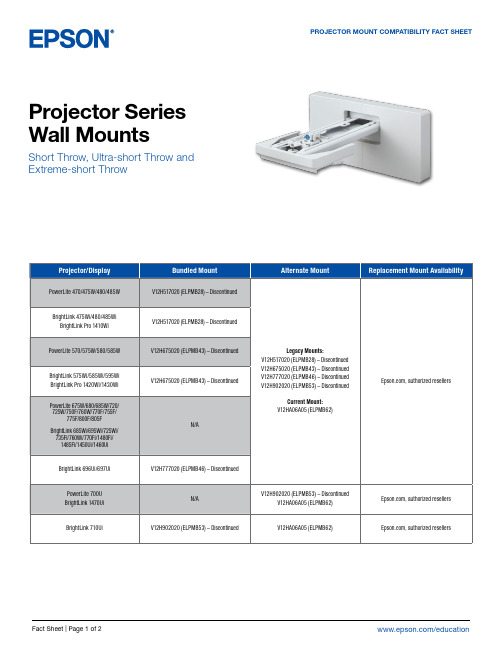

埃森普项目器搭载兼容性信息表说明书

Epson America, Inc. 3131 Katella Ave., Los Alamitos, CA 90720

Epson Canada Limited 185 Renfrew Drive, Markham, Ontario L3R 6G3

www.epson.ca

BrightLink 475Wi/480/485Wi BrightLink Pro 1410Wi

PowerLite 570/575W/580/585W

BrightLink 575Wi/585Wi/595Wi BrightLink Pro 1420Wi/1430Wi

PowerLite 675W/680/685W/720/ 725W/750F/760W/770F/755F/

BrightLink 475Wi/480/485Wi/575Wi/585Wi/ 595Wi/685Wi/695Wi/696Ui/697Ui/710Ui/

725Wi/735Fi/760Wi/770Fi

BrightLink Pro 1410Wi/1420Wi/ 1430Wi/1450Ui/1460Ui/1470Ui

N/A

Legacy Mounts: V12H517020 (ELPMB28) – Discontinued V12H675020 (ELPMB43) – Discontinued V12H777020 (ELPMB46) – Discontinued V12H902020 (ELPMB53) – Discontinued

V12H706020 (ELPMB45) – Discontinued V12H706020 (ELPMB45) – Discontinued

PowerLite L200SX/L200SW/ L210SW/L210SF

NVIDIA 视频编码器 SDK 10.0 迁移指南说明书

NVENC Preset Migration GuideTable of ContentsChapter 1. Introduction (1)Chapter 2. HEVC Preset Migration Table (2)Chapter 3. H264 Preset Migration Table (5)Chapter 1.IntroductionThis document provides table to map the NVENCODE API settings (specifically, preset and rate control mode) from Video Codec SDK 9.1 and earlier to the closest equivalent NVENCODE API settings in Video Codec SDK 10.0 and later. This table can be used as a migration guide to migrate to the new NVENCODE API preset architecture introduced in Video Codec SDK 10.0.In general, it is strongly recommended to use the newer presets and NVENCODE API settings based on desired performance/quality trade-off. It is highly likely that your application may benefit from better quality encoding or higher performance by directly using the new NVENCODE presets, as the new APIs provide much more flexibility than earlier and are easy to understand. Please use the mapping tables in this document only in situations where exactly same performance/quality is desired as was obtained in the older presets.Table 1and Table 2show the mapping between older and newer presets exposed in the NVENCODE API for HEVC and H.264, respectively. Note that there is no support for older presets in AV1A combination of older preset (Column 1), rate control (RC) mode (Column 2) and resolution (Column 3) can be mapped to a new parameters of NVENCODE API: tuning info (Column 4), RC Mode (Column 5), preset (Column 7&9) and multipass (Column 6&8). The newer preset and multipass values will vary based on GPU Architecture and appropriate GPU architecture column must be selected.In some cases, additional settings need to be included for exact mapping, and they are mentioned in columns Features 1 (Column 10 in Table 1 and Column 12 in Table 2) and Features 2 (Column 11 in Table 1 and Column 13 in Table 2).As an example, if someone is using HEVC HQ Preset with VBR_HQ RC Mode for a 1080p encoding on Turing platform, this corresponds to Row 18 in Table 1. The closest settings as per the new NVENCODE API is P6 Preset, RC Mode VBR, Multipass set to 1, FrameIntervalP set to 1, IDR Period set to 60 and GOP Length set to 60.It is important to note that Features 1 and Features 2 are just indicated to get an exact feature match on older presets and most applications would set these based on needs. For example, GOP length may be set to a larger value depending upon the application needs.Chapter 2.HEVC Preset MigrationTableTable 1.HEVC Preset Migration TableChapter 3.H264 Preset Migration Table Table 2.H264 Preset Migration TableH264 Preset Migration TableNoticeThis document is provided for information purposes only and shall not be regarded as a warranty of a certain functionality, condition, or quality of a product. NVIDIA Corporation (“NVIDIA”) makes no representations or warranties, expressed or implied, as to the accuracy or completeness of the information contained in this document and assumes no responsibility for any errors contained herein. NVIDIA shall have no liability for the consequences or use of such information or for any infringement of patents or other rights of third parties that may result from its use. This document is not a commitment to develop, release, or deliver any Material (defined below), code, or functionality.NVIDIA reserves the right to make corrections, modifications, enhancements, improvements, and any other changes to this document, at any time without notice. Customer should obtain the latest relevant information before placing orders and should verify that such information is current and complete.NVIDIA products are sold subject to the NVIDIA standard terms and conditions of sale supplied at the time of order acknowledgment, unless otherwise agreed in an individual sales agreement signed by authorized representatives of NVIDIA and customer (“Terms of Sale”). NVIDIA hereby expressly objects to applying any customer general terms and conditions with regards to the purchase of the NVIDIA product referenced in this document. No contractual obligations are formed either directly or indirectly by this document.NVIDIA products are not designed, authorized, or warranted to be suitable for use in medical, military, aircraft, space, or life support equipment, nor in applications where failure or malfunction of the NVIDIA product can reasonably be expected to result in personal injury, death, or property or environmental damage. NVIDIA accepts no liability for inclusion and/or use of NVIDIA products in such equipment or applications and therefore such inclusion and/or use is at customer’s own risk. NVIDIA makes no representation or warranty that products based on this document will be suitable for any specified use. Testing of all parameters of each product is not necessarily performed by NVIDIA. It is customer’s sole responsibility to evaluate and determine the applicability of any information contained in this document, ensure the product is suitable and fit for the application planned by customer, and perform the necessary testing for the application in order to avoid a default of the application or the product. Weaknesses in customer’s product designs may affect the quality and reliability of the NVIDIA product and may result in additional or different conditions and/or requirements beyond those contained in this document. NVIDIA accepts no liability related to any default, damage, costs, or problem which may be based on or attributable to: (i) the use of the NVIDIA product in any manner that is contrary to this document or (ii) customer product designs.TrademarksNVIDIA, the NVIDIA logo, and cuBLAS, CUDA, CUDA Toolkit, cuDNN, DALI, DIGITS, DGX, DGX-1, DGX-2, DGX Station, DLProf, GPU, Jetson, Kepler, Maxwell, NCCL, Nsight Compute, Nsight Systems, NVCaffe, NVIDIA Deep Learning SDK, NVIDIA Developer Program, NVIDIA GPU Cloud, NVLink, NVSHMEM, PerfWorks, Pascal, SDK Manager, Tegra, TensorRT, TensorRT Inference Server, Tesla, TF-TRT, Triton Inference Server, Turing, and Volta are trademarks and/or registered trademarks of NVIDIA Corporation in the United States and other countries. Other company and product names may be trademarks of the respective companies with which they are associated.Copyright© 2010-2023 NVIDIA Corporation. All rights reserved.NVIDIA Corporation | 2788 San Tomas Expressway, Santa Clara, CA 95051。

NVIDIA NVS产品线二代展示说明书

4096 x 2160 1920 x 1200

― 68 W Active Fansink

NVIDIA NVS 310 v2

DisplayPort 1.2 and 30-bit color 2 display business graphics

CUDA Cores GPU GPU Memory Form Factor PCIe Display Connectors Max Display Configuration Max Board Power DVI-I Single Link or VGA DisplayPort NVIEW Mosaic Thermal Solution MSRP PNY Part Number

Display 2

2560 x 1600 at 60Hz 1920 x 1200 at 60Hz 1600 x 1200 at 60Hz 1920 x 1200 at 120Hz

Display 3

1920 x 1200 at 60Hz 1600 x 1200 at 60Hz

Display 4 1600 x 1200 at 60Hz

NVIDIA NVS Product Line

Enterprise ready business graphics solutions

NVS 310 v2

NVS 315

NVS 510

NVS 810

Frame Buffer CUDA Processor Cores Memory Interface Bus Interface Display Connector Max Displays Per Board Max DisplayPort Resolution Max DVI Resolution Max Analog Resolution Max Power Consumption Cooling System

罗克威尔自动化工业电脑 - 增强写滤镜(EWF)和休眠一次唤醒多次(HORM)配置实用程序说明书

Technical DataEWF and HORM Configuration Utility for Rockwell Automation Industrial ComputersAbout This Publication This publication provides instructions on how to use the Enhanced Write Filter(EWF) and Hibernate Once/Resume Many (HORM) configuration utility. Thisutility is available only on these Rockwell Automation industrial computers thatcome with the Windows Embedded Standard 2009 (WES 2009) operatingsystem:•6155F compact non-display computers•6181F integrated display computersY ou can view or download this publication at/literature.About the EWF and HORM Utility EWF protects a volume from write access by caching writes to another location. This helps extend the life of solid state media and can help reduce possible corruption to the operating system due to unplanned power outages. HORM allows the system to boot from a hibernation file while EWF is enabled.For more information on EWF and HORM, go to the Microsoft website at .Managing EWF EWF can be managed on the run-time image in these two ways:•Rockwell Automation EWF/HORM configuration utility•Microsoft EWFMGR command line utilityThe EWF/HORM configuration utility provides commonly used features of theMicrosoft EWFMGR utility and an easy to use graphical interface.For more information about managing EWF with the EWMGR command lineutility, see the Microsoft website at .2 EWF and HORM Configuration Utility for Rockwell Automation Industrial ComputersStart the Utility The EWF/HORM configuration utility is pre-installed on all WES 2009 imagesand can be found as ‘EWFHORM Utility.exe’ in C:\ProgramFiles\EWFHORM Utility\. A shortcut has been provided for the initialadministrator logon.T o start the utility, double-click the EWFHORM utility shortcut.The shortcut loads the utility and displays this dialog box.TIP Only users with administrator rights can make changes to theEWF/HORM utility.Field Descriptions FieldDescription Overlay Type Displays the current mode of EWF. RAM (Reg) is the only mode supported on Rockwell Automation WES 2009 images and cannot be changed. This mode caches all writes to the physical random access memory (RAM) and the configuration information is stored in the system registry.Protected Drive Displays the volume protected by EWF. This will default to C: and cannot be changed on the run-time image.Overlay Level Some EWF configurations can allow multiple overlays. The RAM (Reg) mode allows only a single overlay and cannot be changed.Available RAM Displays the amount of physical RAM available to the system.EWF can attempt to allocate more physical RAM than is installed on the computer. The system can become unstable and unresponsive if the amount of physical RAM is too low. See Commit Changes to Disk for methods to free up physical RAM.For instructions on adding more RAM, see your computer’s user manual.EWF Status Displays the current status of the EWF. For more information on managing EWF, see the following sections.Overlay SizeDisplays the current size of the overlay size. This must be less than the amount of available RAM or else the system can become unstable. For more information on managing the overlay size, see the following sections.EWF and HORM Configuration Utility for Rockwell Automation Industrial Computers 3Enable EWF The factory image comes with EWF in the disabled state.Follow these steps to enable EWF.1.Click Enable.2.Click Yes to enable EWF.Enabling EWF requires a system restart.3.Click Yes to restart.HORM StatusDisplays the current status of HORM. This is enabled by default. For more information on managing HORM, see Enable HORM and Disable HORM .Hibernate Hibernates the system.HORM must be enabled for the system to hibernate. If hibernation is not enabled on the system, the Hibernate button will put the system into standby.Reboot Restarts the system.CloseCloses the application. Minimizing the application at any time will then display an icon in the system tray.Field DescriptionsFieldDescription TIP Enable is unavailable if EWF is already enabled.4 EWF and HORM Configuration Utility for Rockwell Automation Industrial ComputersOnce EWF is enabled, the status screen displays Enabled.Disable EWF The following method is used to clear the contents of the overlay and disableEWF for RAM (Reg) overlay types.Please see Commit Changes to Disk if you would like to commit changes inaddition to disabling EWF.Follow these steps to disable EWF.1.Click Disable.2.Click Yes to disable EWF.Disabling the EWF requires a system restart.3.Click Yes to restart.4.Once the system restarts, start the utility.5.Click Commit/Disable EWF to complete the disable process.TIP Disable is unavailable if EWF is already disabled.EWF and HORM Configuration Utility for Rockwell Automation Industrial Computers 5This will make sure the overlay is empty and immediately disable EWF.No restart is necessary after this step.6.Click Yes to commit/disable EWF.The EWF state will then change to disabled and all RAM utilized for the overlay will be returned to the operating system.Commit Changes to Disk All changes to a system are lost on a power outage or restart while EWF isenabled, unless they are committed to disk.Follow these steps to commit changes to disk.1.Click Commit.ATTENTION: Enabling EWF for long periods of time can fill theRAM overlay. The system will become unstable if changes are notcommitted to disk or restarted before the physical RAM isdepleted.If the overlay continually becomes full, examine your applications’use of RAM or consider adding more RAM to your system.For more information about adding RAM to your system, see yourcomputer’s user manual.TIP Commit is unavailable if EWF is not enabled.6 EWF and HORM Configuration Utility for Rockwell Automation Industrial Computers2.Click Yes to commit changes. Commiting changes requires a system restart.3.Click Yes to restart.The changes will be committed and EWF will remain enabled once the system restart. Commit Changes and Disable EWF Follow these steps to commit changes and disable EWF.1.Click Commit/Disable EWF.2.Click Yes to commit/disable EWF.No restart is necessary after this step. The changes will be written to diskand EWF will be in a disabled state.TIP The Commit/Disable EWF button is unavailable if EWF is not enabled.EWF and HORM Configuration Utility for Rockwell Automation Industrial Computers 7Enable HORMFollow these steps to enable HORM.1.Click Enable.2.Click Yes to enable HORM. 3.Click Yes to restart. Disable HORM Follow these steps to disable HORM.1.ClickDisable . 2.Click Yes to disable HORM.TIP Enable is unavailable if HORM is already enabled.TIP Disable is unavailable if HORM is disabled.Allen-Bradley, Rockwell Software, Rockwell Automation, and TechConnect are trademarks of Rockwell Automation, Inc.Trademarks not belonging to Rockwell Automation are property of their respective companies.Rockwell Otomasyon Ticaret A.Ş., Kar Plaza İş Merkezi E Blok Kat:6 34752 İçerenköy, İstanbul, T el: +90 (216) 5698400Publication 6000-TD003A-EN-P - April 2010Copyright © 2010 Rockwell Automation, Inc. All rights reserved. Printed in the U.S.A.3.Click Yes to restart.。

PNY NVIDIA NVS 510 for Quad DVI 低配置版 产品规格说明书

PNY Technologies, Inc. 100 Jefferson Road, Parsippany, NJ 07054 | Tel 408 567 5500 | Fax 408 855 0680Features and specifications subject to change without notice. The PNY logo is a registered trademarks of PNY Technologies, Inc. All other trademarks are the property of their respective owners. © 2012 PNY Technologies, Inc. All rights reserved.For more information visit: /nvsNVIDIA ®NVS ™510 for Quad DVI–Low ProfileVCNVS510DVI-PBPRODUCT SPECIFICATIONS:CUDA™ Cores 192GPU Memory 2GB DDR3Memory Interface 128-bit Memory Bandwidth 28.5GB/sSystem InterfacePCI Express 3.0 x16Maximum Power Consumption 33.4W Energy Star Enabling YesThermal Solution Ultra-quiet active fansink Form Factor 2.713” H x 6.30” L, Single Slot Display Connectors Four Mini-DisplayPort DisplayPort 1.2Yes DisplayPort with Audio Yes Mini-DP to DP adapters 4 included Mini-DP to DVI-D SL adapters 4 included Number of Displays Supported 4Maximum DP 1.2 Resolution 3840 × 2160 at 60Hz Maximum DVI-D SL Resolution 1920 × 1200 at 60Hz HDCP Support YesGraphics APIs Shader Model 5.0, OpenGL 4.3, DirectX 11Compute APIs CUDA, DirectCompute, OpenCL NVIEW YesMosaic Mode Yes (Windows 8, 7, and Linux)Warranty3 YearsPNY Part Numbe r - Quad DVIVCNVS510DVI-PBReliably visualize any data across four displays with the power efficient, low-profile form factor NVIDIA ® NVS™ 510 business graphics solution. You get support for advanced DisplayPort 1.2 features like Multi-Stream Technol-ogy and Stream Cloning, plus the capability to natively drive four ultra-high resolution displays at up to 3840 x 2160 in small form-factor systems. The NVS 510 for Quad DVI also includes four locking mini-DisplayPort to DVI-D SL adapters for installations requiring DVI displays or a mix of DVI and DisplayPort monitors.The NVS 510 takes advantage of the latest NVIDIA ® Kepler™ architecture with 2 GB of dedicated graphics memory to deliver more than 3x the perfor-mance of the previous-generation solution—without increasing power. And it’s backed by a super-reliable hardware and software platform and robust IT management tools to enable fast, cost-effective integration, deployment, and support across large enterprises. This makes it the ideal solution for today’s most demanding business user.Package includes:• NVIDIA NVS 510 professional graphics board • Attached full height (ATX) bracket • Included low-profile (SFF) bracket• Four locking mini-DisplayPort to DisplayPort adapters • Four locking mini-DisplayPort to DVI-D SL adapters• Driver DVD for Windows 8, 7, Vista, and XP SP3 (32- and 64-bit)• Printed QuickStart Guide PNY Advantage:PNY provides unsurpassed service and commitment to its professional graphics customers. In addition, PNY delivers a complete solution including the appropriate adapters, cables, brackets, driver DVD and documentation to ensure a quick and successful install.4 × Mini-DisplayPort to DisplayPort4 × Mini-DisplayPort to DVILow Profile BracketFull Height Bracket。

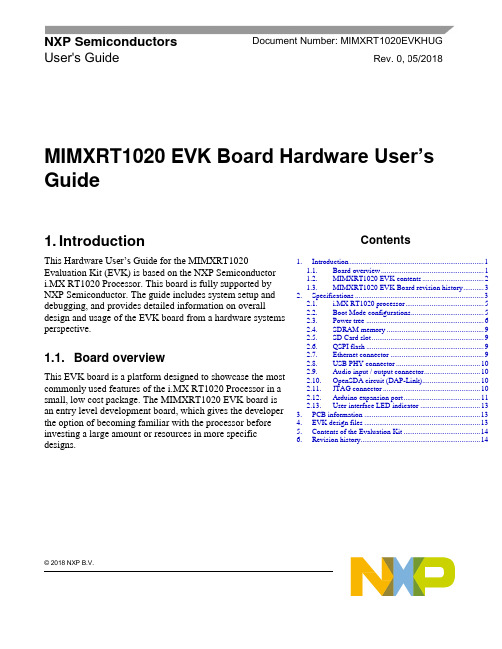

恩智浦 MIMXRT1020 EVK 开发板硬件用户指南说明书

© 2018 NXP B.V.MIMXRT1020 EVK Board Hardware User’sGuide1.IntroductionThis Hardware User’s Guide for the MIMXRT 1020Evaluation Kit (EVK) is based on the NXP Semiconductor i.MX RT1020 Processor. This board is fully supported by NXP Semiconductor. The guide includes system setup and debugging, and provides detailed information on overall design and usage of the EVK board from a hardware systems perspective.1.1. Board overviewThis EVK board is a platform designed to showcase the most commonly used features of the i.MX RT1020 Processor in a small, low cost package. The MIMXRT1020 EVK board is an entry level development board, which gives the developer the option of becoming familiar with the processor before investing a large amount or resources in more specific designs.NXP Semiconductors Document Number: MIMXRT1020EVKHUGUser's GuideRev. 0 , 05/2018Contents1.Introduction ........................................................................ 11.1.Board overview ....................................................... 11.2.MIMXRT1020 EVK contents ................................. 21.3.MIMXRT1020 EVK Board revision history ........... 32.Specifications ..................................................................... 32.1.i.MX RT1020 processor .......................................... 52.2.Boot Mode configurations ....................................... 52.3.Power tree ............................................................... 62.4.SDRAM memory .................................................... 92.5.SD Card slot ............................................................ 92.6.QSPI flash ............................................................... 92.7.Ethernet connector .................................................. B PHY connector ............................................. 102.9.Audio input / output connector .............................. 102.10.OpenSDA circuit (DAP-Link) ............................... 102.11.JTAG connector .................................................... 102.12.Arduino expansion port ......................................... er interface LED indicator ................................ 133.PCB information .............................................................. 134.EVK design files .............................................................. 135.Contents of the Evaluation Kit ......................................... 146.Revision history (14)IntroductionFeatures of the MIMXRT1020 EVK board are shown in Table 11.2. MIMXRT1020 EVK contentsThe MIMXRT1020 EVK contains the following items: •MIMXRT1020 EVK Board•USB Cable (Micro B)Specifications 1.3. MIMXRT1020 EVK Board revision history•Rev A: Prototype.2. SpecificationsThis chapter provides detailed information about the electrical design and practical considerations of the EVK Board, and is organized to discuss each block in the following block diagram of the EVK board.( Figure 1)Figure 1. Block diagramThe overview of the MIMXRT1020 EVK Board is shown in Figure 1 & Figure 2.SpecificationsFigure 2. Overview of the MIMXRT1020 EVK Board (Front side)Figure 3. Overview of the MIMXRT1020 EVK Board (Back side)Specifications 2.1. i.MX RT1020 processorThe i.MX RT1020 is a new processor family featuring NXP's advanced implementation of the Arm® Cortex®-M7 Core. It provides high CPU performance and best real-time response. The i.MX RT1020 provides various memory interfaces, including SDRAM, Raw NAND FLASH, NOR FLASH,SD/eMMC, Quad SPI, HyperBus and a wide range of other interfaces for connecting peripherals, such as WLAN, Bluetooth™, GPS. Same as other i.MX processors, i.MX RT1020 also has rich audio features, including SPDIF and I2S audio interface.The i.MX RT1020 applications processor can be used in areas such as industrial HMI, IoT, motor control and home appliances. The architecture's flexibility enables it to be used in a wide variety of other general embedded applications too. The i.MX processor provides all interfaces necessary to connectp eripherals such as WLAN, Bluetooth™, GPS.The more detail information about i.MX RT1020 can be found in the Datasheet and Reference Manual2.2. Boot Mode configurationsThe device has four boot modes (one is reserved for NXP’s use). The boot mode is selected based on the binary value stored in the internal BOOT_MODE register. Switch (SW8-3 & SW8-4) is used to select the boot mode on the MIMXRT1020 EVK Board.Typically, the internal boot is selected for normal boot, which is configured by external BOOT_CFG GPIOs. The following Table 3 shows the typical Boot Mode and Boot Device settings.NOTEFor more information about boot mode configuration, see the System Boot chapter of theMIMXRT1020 Reference Manual. (waiting for update)For more information about MIMXRT1020 EVK boot device selection and configuration, see the main board schematic. (waiting for update)Specifications2.3. Power treeA DC 5 V external power supply is used to supply the MIMXRT1020 EVK Board at J2, and a slide switch SW1 is used to turn the Power ON/OFF. J23 and J9 also can be used to supply the EVK Board. Different power supply need to configure different Jumper setting of J1. Table 4 shows the details:NOTEFor some computers’ USB, it cannot support 500ma before establishingcommunication. In this case, it is recommended to replace the computer oruse the power adapter(J2) to power the EVK Board.The power tree is shown in Figure 4SpecificationsFigure 4. Power TreeThe power control logic of the MIMXRT1020 EVK board is shown in the Figure 5: •It will power up SNVS, and then PMIC_REQ_ON will be switched on to enable external DC/DC to power up other power domains.•ON/OFF button is used to switch ON/OFF PMIC_REQ_ON to control power modes.•RESET button and WDOG output are used to reset the system power.SpecificationsFigure 5. Power Control Diagram The power rails on the board are shown in Table 5.Specifications2.4. SDRAM memoryOne 256 Mb, 166MHz SDRAM (MT48LC16M16A2P) is used on the EVK Board.2.5. SD Card slotThere is a SD card slot(J15) on the MIMXRT1020 EVK Board. J15 is the Micro SD slot for USDHC1 interface. If the developer wants to boot from the SD Card, the boot device switch (SW8) settings should be: OFF, ON, ON, OFF, as shown in Table 3.2.6. QSPI flashA 64 Mbit QSPI Flash is used on the MIMXRT1020 EVK Board. If the developer wants to boot from the QSPI Flash, the boot device switch(SW8) settings should be: OFF, OFF, ON, OFF, as shown in Table 3.2.7. Ethernet connectorThere is one Ethernet Mac controller in the MIMXRT1020 processor. The Ethernet subsystem of the MIMXRT1020 EVK Board is provided by the KSZ8081RNB 10/100M Ethernet Transceiver (U11) and a RJ45 (J14) with integrated Magnetic.Figure 6. Ethernet Connector RJ45Specifications2.8. USB PHY connectorThe MIMXRT1020 contains a integrated USB 2.0 PHYs capable of connecting to USB host/device systems at the USB low-speed (LS) rate of 1.5 Mbits/s, full-speed (FS) rate of 12 Mbits/s or at the USB 2.0 high-speed (HS) rate of 480 Mbits/s.2.9. Audio input / output connectorThe Audio CODEC used on the MIMXRT1020 EVK Board is Wolfson’s Low Power, high quality Stereo Codec, WM8960.The MIMXRT1020 EVK Board include one headphone interface (J11), one onboard MIC (P1), two speaker interfaces (J12, J13). J11 is a 3.5 mm audio stereo headphone jack, which supports jack detect.2.10. OpenSDA circuit (DAP-Link)The OpenSDA circuit (CMSIS–DAP) is an open-standard serial and debug adapter. It bridges serial and debug communications between a USB host and an embedded target processor.CMSIS-DAP features a mass storage device (MSD) bootloader, which provides a quick and easy mechanism for loading different CMSIS-DAP Applications such as flash programmers, run-control debug interfaces, serial-to-USB converters, and more. Two or more CMSIS-DAP applications can run simultaneously. For example, run-control debug application and serial-to-USB converter runs in parallel to provide a virtual COM communication interface while allowing code debugging via CMSIS-DAP with just single USB connection.For the MIMXRT1020 EVK Board, J23 is the connector between the USB host and the target processor. Jumper to serial downloader mode to use stable DAP-Link debugger function. If developer wants to make OpenSDA going to the bootloader mode, and press SW5 when power on. Meanwhile, the OpenSDA supports drag/drop feature for U-Disk. First, use the seral downloader mode and drag/drop the image file to U-Disk. Then select QSPI Flash as boot device and reset the Board, the image will run.2.11. JTAG connectorJ16 is a standard 20-pin/2.54 mm Box Header Connector for JTAG. The pin definitions are shown in Figure 7. Support SWD by default.SpecificationsFigure 7. JTAG pin definitions2.12. Arduino expansion portJ17 – J20 (unpopulated) is defined as Arduino Interface. The pin definitions of Arduino Interface are shown in Table 6.Specifications2.12.1. Power switchSW1 is a slide switch to control the power of the MIMXRT1020 EVK Board when the power supply is from J2. The function of this switch is listed below:•Sliding the switch to the ON position connects the 5 V power supply to the Evaluation board main power system.•Sliding the switch to OFF position immediately removes all power from the board.2.12.2. ON/OFF buttonSW2 is the ON/OFF button for MIMXRT1020 EVK Board. A short pressing in OFF mode causes the internal power management state machine to change state to ON. In ON mode, a short pressing generates an interrupt (intended to be a software-controllable(power-down). An approximate 5 seconds or more pressing causes a forced OFF. Both boot mode inputs can be disconnected.2.12.3. Reset buttonThere are two Reset Button on the EVK Board. SW5 is the Power Reset Button. Pressing the SW5 in the Power On state will force to reset the system power except SNVS domain. The Processor will be immediately turn off and reinitiate a boot cycle from the Processor Power Off state. SW3 is POR Reset Button.EVK design files 2.12.4. USER buttonSW4 is the USER Button(GPIO5-00) for developers using. Pressing can produce changes in high and low levels.2.13. User interface LED indicatorThere are four LED status indicators located on the EVK Board. The functions of these LEDs include: •Main Power Supply(D3)Green: DC 5V main supply is normal.Red: J2 input voltage is over 5.6V.Off: the board is not powered.•Reset RED LED(D15)•OpenSDA LED(D16)•USER LED(D5)3. PCB informationThe MIMXRT1020 EVK Board is made using standard 2-layer technology. The material used was FR-4. The PCB stack-up information is shown in Table 7.4. EVK design filesThe schematics, layout files, and gerber files (including Silkscreen) can be downloaded from/MIMXRT1020-EVK(waiting for update).Revision history5. Contents of the Evaluation KitNOTEPower adaptor, Micro SD Card are not standard parts of the Evaluation Kit.6. Revision historyTable 9 summarizes the changes made to this document since the initial release.Document Number: MIMXRT1020EVKHUGRev. 0 05/2018How to Reach Us: Home Page: Web Support: /supportInformation in this document is provided solely to enable system and softwareimplementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequenti al or incidental damages. “Typical” parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including “typicals”, must be validated for each customer application by customer’s technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: /SalesTermsandConditions . While NXP has implemented advanced security features, all products may be subject to unidentified vulnerabilities. Customers are responsible for the design and operation of their applications and products to reduce the effect of these vulnerabilities oncustomer’s applications and products, and NXP accepts no liability for any vulne rability that is discovered. Customers should implement appropriate design and operating safeguards to minimize the risks associated with their applications and products NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, , Freescale, the Freescale logo, and Kinetis, are trademarks of NXP B.V. All other product or service names are the property of their respective owners. Arm and Cortex are registered trademarks of Arm Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. © 2018 NXP B.V.。

显卡型号大全【V2.1】

3D Vision

3D Vision

3D Vision

3D Vision

3D Vision

3D Vision

通用计算接口

CUDA

CUDA

CUDA

CUDA

CUDA

CUDA

CUDA

物理加速技术

PhysX

PhysX

PhysX

PhysX

PhysX

PhysX

PhysX

3DMark11分数

5230

4.1

4.1

4.1

4.1

OpenCL

1.1

驱动仅支持1.0

1.1

驱动仅支持1.0

1.1

驱动仅支持1.0

1.1

驱动仅支持1.0

1.1

驱动仅支持1.0

1.1

驱动仅支持1.0

1.1

驱动仅支持1.0

TDP

250W

215W

200W

160W

150W

160W

150W

供电接口

6pin+8pin

6pinX2

6pinX2

PureVideo HD

3D立体技术

3D Vision

3D Vision

3D Vision

3D Vision

3D Vision

通用计算接口

CUDA

CUDA

CUDA

CUDA

CUDA

物理加速技术

PhysX

PhysX

PhysX

PhysX

无

3DMark11分数

2520

3DMarkVantage分数

9900

1680

GeForce500系列

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。