The implementation of portable

基于Java的飞机大战游戏的设计与实现论文

毕业设计(论文)任务书第1页第2页第3页基于Java的飞机大战游戏的设计与实现摘要现如今,随着智能手机的兴起与普及,加上4G(the 4th Generation mobile communication ,第四代移动通信技术)网络的深入,越来越多的IT行业开始向手机行业转移重心。

而手机行业中游戏方面的利润所占比重较大,并且手机游戏大多数则是由Java语言开发研制的。

所以我想顺应时代发展,用学到的Java知识对游戏进行一次深入的了解与创作。

Java语言在我们大学学习中占了很大的比重,其优点甚多:面向对象,可靠,安全,多平台可移植,高性能,多线程等。

面向对象是相对于c语言的面向过程来说的,在面向对象编程中,我们用Java去新建一个对象,调用其方法就能实现我们的目标,并不需要了解这个对象的方法的具体实现过程;Java的可靠安全特点体现Java不支持指针,禁止第三方访问,杜绝了外部风险。

所以使用Java开发游戏,是一个正确的选择。

大学学习即将结束,在毕业之际,我想用我4年里学习的知识为自己编写一个属于自己的游戏——飞机大战游戏,为我的大学生活画上圆满的句号。

关键词:Java游戏;面向对象;可靠安全;多线程Design And Implementation Of Airplane WargameBased On JavaAbstractNowadays, with the emergence and popularization of smart phones, plus 4 g (the 4 th Generation mobile communication, the fourth Generation mobile communication technology) the development of the Internet, more and more in the IT industry began to shift to the mobile phone industry center of gravity. Aspect of the game of the mobile phone industry profits account for a large proportion, and most mobile game is developed by Java language. So I want to keep up with the development of The Times, use Java knowledge for an in-depth understanding of the game and creation.Java language learning in our universities accounted for a large proportion of its many advantages: Object-oriented, reliable, secure, multi-platform portable, high-performance, multi-threading.Object-oriented process-oriented with respect to the terms of the c language, object-oriented programming, specifically we use Java to create a new object, call its methods will be able to achieve our goal,we do not need to know the object's method of implementation ; reliable safety features reflect Java Java does not support pointers to prohibit third-party access, to eliminate the external risk. Therefore, the use of Java development aircraft war game, is the right choice.University coming to an end, on the occasion of the graduation, I want to use my four years studying knowledge and made themselves a game of their own - Aircraft war game for my college life painting satisfactory conclusion.Keywords:Java game; object oriented; reliable and secure; multi thread目录1 引言 (1)1.1 项目背景 (1)1. 2 国内外研究现状 (3)1.3 项目主要工作 (4)1.4 本文组织结构 (6)2 开发平台与开发技术 (7)2. 1 IntelliJ IDEA简介 (7)2. 2 IntelliJ IDEA与Eclipse 、MyEclipse的比较 (8)2. 3 Java (10)3 可行性研究 (13)3. 1 技术可行性 (13)3. 2 经济可行性 (13)3. 3 操作可行性 (14)3. 4 用户使用可行性 (14)3. 5 法律可行性 (14)4 需求分析 (15)4. 1 系统需求概述 (16)4. 2 功能模块设计 (17)4.2.1 游戏状态控制功能模块 (17)4.2.2 游戏难度的调整模块 (17)4.2.3 游戏界面绘画功能模块 (17)4.2.4 玩家游戏控制功能模块 (17)4. 3 游戏难点分析 (18)4.3.1 绘图美化 (18)4.3.2 多线程技术的实现 (18)4.3.3 防碰撞问题的解决 (18)4.3.4 动画的实现 (18)5 飞机大战功能实现 (19)5.1 模型图 (19)5.2 软件功能模块 (19)5.3 游戏首页的实现 (20)5.3.1 界面实现 (20)5.3.2 流程图 (21)5.3.3 核心代码 (22)5.4 游戏开始模块的实现 (24)5.4.1 界面实现 (24)5.4.2 流程图 (25)5.4.3 核心代码 (25)5.5 发射子弹模块的实现 (27)5.5.1 界面实现 (27)5.5.2 流程图 (28)5.5.3 核心代码 (29)5.6 积分模块的实现 (33)5.6.1 界面的实现 (33)5.6.2 核心代码 (34)5.7 防碰撞逻辑 (37)5.7.1 核心代码 (37)5.8 游戏操作的实现 (39)5.8.1 核心代码 (39)5.9 特殊NPC蜜蜂 (41)6 系统测试 (42)6.1 测试的定义及其重要性 (43)6.1.1 测试的定义 (43)6.1.2 测试的重要性 (44)6.2 测试方法 (46)6.3 测试结果 (50)7 结论 (51)参考文献 (52)致谢 (54)外文文献 (55)中文翻译 (63)1 引言1.1 项目背景90后的我们,童年最开始接触电子游戏是在游戏厅,那时候的飞机大战游戏机前,往往人山人海,绚丽多彩的画面,带感操作让人沉醉不能自拔。

Operation Manual

Operation Manual of Portable Data Logger(Version: 1.00)1. Quick Start (3)2. Connecting the Logger to PC (3)3. Setting Up the Logger to Record Data (4)4. Download data from the logger (5)5. Delete all the logs from the logger (6)6. Data Listing Window (6)7. Exporting Logger Data (7)8. File List (8)1. Quick StartFollow the procedure below to quickly start using your data logger:1. Connect the data logger to a free USB port on the computer.2. Start T oAnalyzer 1 software on the PC.3. From the toolbar select Connect.4. Then you can setup or download data, delete data from the logger.5. Unplug the cable from the logger, then the logger is in Standby mode. Press buttonLOG/STD on the logger, then LOG displays on the screen and the logger begins to record.6. Press LOG/STD for about five seconds, the logger will be power on (LOG mode) or off(OFF mode).Note: The logger has three modes:1. LOG: In the mode, the logger samples and records data timely.2. Standby: In the mode, the logger stops to sample and record, but the LCD display ison.3. OFF: In the mode, the logger stops to sample and record, and the LCD display is off.T oAnalyzer cannot connect to the logger also.2. Connecting the Logger to PCT o connect the logger to the computer, follow these steps:1. Connect the USB cable to the logger and to a free USB port on the computer.2. If you are connecting the logger to the PC for the first time, the logger willautomatically be recognized and installed on the computer.3. Start T oAnalyzer 1 analysis software.4. Click the icon3. Setting Up the Logger to Record DataT o set the logger to start recording data, click the: Synchronize the new setup information to the logger. After changing theconfiguration, do not forget clicking this button to make sure that the new configuration is wrote to the logger.lbutton on the toolbar. Once the data is transferred from the logger to the PC, the data graph and data listing windows will be displayed.The graph display will be blank if there are not any logs.Note: Push left mouse button down, and then move to select a rectangle area, when the left mouse button is up, the graph will be redraw with the data in the selected rectangle area. Click right button, then the graph will be redrawing with all the data in the logs file.5. Delete all the logs from the logger.T o erase all data from the logger, connect to the logger, and then clickbutton on the toolbar, and then the data listing window is shown below.The data pane lists the data samples collected by the logging device.The column width of each column is adjustable by using the left mouse button and dragging the column the desired width.7. Exporting Logger DataY ou can use ToAnalyzer to export sample data to a text file or to a Microsoft Excel file or BMP file.ll。

稳定性英文版

HPLC ASSAY with DETERMINATION OF META-FLUOXETINE HCl.ANALYTICAL METHOD VALIDATION10 and 20mg Fluoxetine Capsules HPLC DeterminationFLUOXETINE HClC17H18F3NO•HClM.W. = 345.79CAS — 59333-67-4STABILITY INDICATINGA S S A Y V A L I D A T I O NMethod is suitable for:ýIn-process controlþProduct ReleaseþStability indicating analysis (Suitability - US/EU Product) CAUTIONFLUOXETINE HYDROCHLORIDE IS A HAZARDOUS CHEMICAL AND SHOULD BE HANDLED ONLY UNDER CONDITIONS SUITABLE FOR HAZARDOUS WORK.IT IS HIGHLY PRESSURE SENSITIVE AND ADEQUATE PRECAUTIONS SHOULD BE TAKEN TO AVOID ANY MECHANICAL FORCE (SUCH AS GRINDING, CRUSHING, ETC.) ON THE POWDER.ED. N0: 04Effective Date:APPROVED::HPLC ASSAY with DETERMINATION OF META-FLUOXETINE HCl.ANALYTICAL METHOD VALIDATION10 and 20mg Fluoxetine Capsules HPLC DeterminationTABLE OF CONTENTS INTRODUCTION........................................................................................................................ PRECISION............................................................................................................................... System Repeatability ................................................................................................................ Method Repeatability................................................................................................................. Intermediate Precision .............................................................................................................. LINEARITY................................................................................................................................ RANGE...................................................................................................................................... ACCURACY............................................................................................................................... Accuracy of Standard Injections................................................................................................ Accuracy of the Drug Product.................................................................................................... VALIDATION OF FLUOXETINE HCl AT LOW CONCENTRATION........................................... Linearity at Low Concentrations................................................................................................. Accuracy of Fluoxetine HCl at Low Concentration..................................................................... System Repeatability................................................................................................................. Quantitation Limit....................................................................................................................... Detection Limit........................................................................................................................... VALIDATION FOR META-FLUOXETINE HCl (POSSIBLE IMPURITIES).................................. Meta-Fluoxetine HCl linearity at 0.05% - 1.0%........................................................................... Detection Limit for Fluoxetine HCl.............................................................................................. Quantitation Limit for Meta Fluoxetine HCl................................................................................ Accuracy for Meta-Fluoxetine HCl ............................................................................................ Method Repeatability for Meta-Fluoxetine HCl........................................................................... Intermediate Precision for Meta-Fluoxetine HCl......................................................................... SPECIFICITY - STABILITY INDICATING EVALUATION OF THE METHOD............................. FORCED DEGRADATION OF FINISHED PRODUCT AND STANDARD..................................1. Unstressed analysis...............................................................................................................2. Acid Hydrolysis stressed analysis..........................................................................................3. Base hydrolysis stressed analysis.........................................................................................4. Oxidation stressed analysis...................................................................................................5. Sunlight stressed analysis.....................................................................................................6. Heat of solution stressed analysis.........................................................................................7. Heat of powder stressed analysis.......................................................................................... System Suitability stressed analysis.......................................................................................... Placebo...................................................................................................................................... STABILITY OF STANDARD AND SAMPLE SOLUTIONS......................................................... Standard Solution...................................................................................................................... Sample Solutions....................................................................................................................... ROBUSTNESS.......................................................................................................................... Extraction................................................................................................................................... Factorial Design......................................................................................................................... CONCLUSION...........................................................................................................................ED. N0: 04Effective Date:APPROVED::HPLC ASSAY with DETERMINATION OF META-FLUOXETINE HCl.ANALYTICAL METHOD VALIDATION10 and 20mg Fluoxetine Capsules HPLC DeterminationBACKGROUNDTherapeutically, Fluoxetine hydrochloride is a classified as a selective serotonin-reuptake inhibitor. Effectively used for the treatment of various depressions. Fluoxetine hydrochloride has been shown to have comparable efficacy to tricyclic antidepressants but with fewer anticholinergic side effects. The patent expiry becomes effective in 2001 (US). INTRODUCTIONFluoxetine capsules were prepared in two dosage strengths: 10mg and 20mg dosage strengths with the same capsule weight. The formulas are essentially similar and geometrically equivalent with the same ingredients and proportions. Minor changes in non-active proportions account for the change in active ingredient amounts from the 10 and 20 mg strength.The following validation, for the method SI-IAG-206-02 , includes assay and determination of Meta-Fluoxetine by HPLC, is based on the analytical method validation SI-IAG-209-06. Currently the method is the in-house method performed for Stability Studies. The Validation was performed on the 20mg dosage samples, IAG-21-001 and IAG-21-002.In the forced degradation studies, the two placebo samples were also used. PRECISIONSYSTEM REPEATABILITYFive replicate injections of the standard solution at the concentration of 0.4242mg/mL as described in method SI-IAG-206-02 were made and the relative standard deviation (RSD) of the peak areas was calculated.SAMPLE PEAK AREA#15390#25406#35405#45405#55406Average5402.7SD 6.1% RSD0.1ED. N0: 04Effective Date:APPROVED::HPLC ASSAY with DETERMINATION OF META-FLUOXETINE HCl.ANALYTICAL METHOD VALIDATION10 and 20mg Fluoxetine Capsules HPLC DeterminationED. N0: 04Effective Date:APPROVED::PRECISION - Method RepeatabilityThe full HPLC method as described in SI-IAG-206-02 was carried-out on the finished product IAG-21-001 for the 20mg dosage form. The method repeated six times and the relative standard deviation (RSD) was calculated.SAMPLENumber%ASSAYof labeled amountI 96.9II 97.8III 98.2IV 97.4V 97.7VI 98.5(%) Average97.7SD 0.6(%) RSD0.6PRECISION - Intermediate PrecisionThe full method as described in SI-IAG-206-02 was carried-out on the finished product IAG-21-001 for the 20mg dosage form. The method was repeated six times by a second analyst on a different day using a different HPLC instrument. The average assay and the relative standard deviation (RSD) were calculated.SAMPLENumber% ASSAYof labeled amountI 98.3II 96.3III 94.6IV 96.3V 97.8VI 93.3Average (%)96.1SD 2.0RSD (%)2.1The difference between the average results of method repeatability and the intermediate precision is 1.7%.HPLC ASSAY with DETERMINATION OF META-FLUOXETINE HCl.ANALYTICAL METHOD VALIDATION10 and 20mg Fluoxetine Capsules HPLC DeterminationLINEARITYStandard solutions were prepared at 50% to 200% of the nominal concentration required by the assay procedure. Linear regression analysis demonstrated acceptability of the method for quantitative analysis over the concentration range required. Y-Intercept was found to be insignificant.RANGEDifferent concentrations of the sample (IAG-21-001) for the 20mg dosage form were prepared, covering between 50% - 200% of the nominal weight of the sample.Conc. (%)Conc. (mg/mL)Peak Area% Assayof labeled amount500.20116235096.7700.27935334099.21000.39734463296.61500.64480757797.52000.79448939497.9(%) Average97.6SD 1.0(%) RSD 1.0ED. N0: 04Effective Date:APPROVED::HPLC ASSAY with DETERMINATION OF META-FLUOXETINE HCl.ANALYTICAL METHOD VALIDATION10 and 20mg Fluoxetine Capsules HPLC DeterminationED. N0: 04Effective Date:APPROVED::RANGE (cont.)The results demonstrate linearity as well over the specified range.Correlation coefficient (RSQ)0.99981 Slope11808.3Y -Interceptresponse at 100%* 100 (%) 0.3%ACCURACYACCURACY OF STANDARD INJECTIONSFive (5) replicate injections of the working standard solution at concentration of 0.4242mg/mL, as described in method SI-IAG-206-02 were made.INJECTIONNO.PEAK AREA%ACCURACYI 539299.7II 540599.9III 540499.9IV 5406100.0V 5407100.0Average 5402.899.9%SD 6.10.1RSD, (%)0.10.1The percent deviation from the true value wasdetermined from the linear regression lineHPLC ASSAY with DETERMINATION OF META-FLUOXETINE HCl.ANALYTICAL METHOD VALIDATION10 and 20mg Fluoxetine Capsules HPLC DeterminationED. N0: 04Effective Date:APPROVED::ACCURACY OF THE DRUG PRODUCTAdmixtures of non-actives (placebo, batch IAG-21-001 ) with Fluoxetine HCl were prepared at the same proportion as in a capsule (70%-180% of the nominal concentration).Three preparations were made for each concentration and the recovery was calculated.Conc.(%)Placebo Wt.(mg)Fluoxetine HCl Wt.(mg)Peak Area%Accuracy Average (%)70%7079.477.843465102.27079.687.873427100.77079.618.013465100.0101.0100%10079.6211.25476397.910080.8011.42491799.610079.6011.42485498.398.6130%13079.7214.90640599.413080.3114.75632899.213081.3314.766402100.399.618079.9920.10863699.318079.3820.45879499.418080.0820.32874899.599.4Placebo, Batch Lot IAG-21-001HPLC ASSAY with DETERMINATION OF META-FLUOXETINE HCl.ANALYTICAL METHOD VALIDATION10 and 20mg Fluoxetine Capsules HPLC DeterminationED. N0: 04Effective Date:APPROVED::VALIDATION OF FLUOXETINE HClAT LOW CONCENTRATIONLINEARITY AT LOW CONCENTRATIONSStandard solution of Fluoxetine were prepared at approximately 0.02%-1.0% of the working concentration required by the method SI-IAG-206-02. Linear regression analysis demonstrated acceptability of the method for quantitative analysis over this range.ACCURACY OF FLUOXETINE HCl AT LOW CONCENTRATIONThe peak areas of the standard solution at the working concentration were measured and the percent deviation from the true value, as determined from the linear regression was calculated.SAMPLECONC.µg/100mLAREA FOUND%ACCURACYI 470.56258499.7II 470.56359098.1III 470.561585101.3IV 470.561940100.7V 470.56252599.8VI 470.56271599.5(%) AverageSlope = 132.7395299.9SD Y-Intercept = -65.872371.1(%) RSD1.1HPLC ASSAY with DETERMINATION OF META-FLUOXETINE HCl.ANALYTICAL METHOD VALIDATION10 and 20mg Fluoxetine Capsules HPLC DeterminationSystem RepeatabilitySix replicate injections of standard solution at 0.02% and 0.05% of working concentration as described in method SI-IAG-206-02 were made and the relative standard deviation was calculated.SAMPLE FLUOXETINE HCl AREA0.02%0.05%I10173623II11503731III10103475IV10623390V10393315VI10953235Average10623462RSD, (%) 5.0 5.4Quantitation Limit - QLThe quantitation limit ( QL) was established by determining the minimum level at which the analyte was quantified. The quantitation limit for Fluoxetine HCl is 0.02% of the working standard concentration with resulting RSD (for six injections) of 5.0%. Detection Limit - DLThe detection limit (DL) was established by determining the minimum level at which the analyte was reliably detected. The detection limit of Fluoxetine HCl is about 0.01% of the working standard concentration.ED. N0: 04Effective Date:APPROVED::HPLC ASSAY with DETERMINATION OF META-FLUOXETINE HCl.ANALYTICAL METHOD VALIDATION10 and 20mg Fluoxetine Capsules HPLC DeterminationED. N0: 04Effective Date:APPROVED::VALIDATION FOR META-FLUOXETINE HCl(EVALUATING POSSIBLE IMPURITIES)Meta-Fluoxetine HCl linearity at 0.05% - 1.0%Relative Response Factor (F)Relative response factor for Meta-Fluoxetine HCl was determined as slope of Fluoxetine HCl divided by the slope of Meta-Fluoxetine HCl from the linearity graphs (analysed at the same time).F =132.7395274.859534= 1.8Detection Limit (DL) for Fluoxetine HClThe detection limit (DL) was established by determining the minimum level at which the analyte was reliably detected.Detection limit for Meta Fluoxetine HCl is about 0.02%.Quantitation Limit (QL) for Meta-Fluoxetine HClThe QL is determined by the analysis of samples with known concentration of Meta-Fluoxetine HCl and by establishing the minimum level at which the Meta-Fluoxetine HCl can be quantified with acceptable accuracy and precision.Six individual preparations of standard and placebo spiked with Meta-Fluoxetine HCl solution to give solution with 0.05% of Meta Fluoxetine HCl, were injected into the HPLC and the recovery was calculated.HPLC ASSAY with DETERMINATION OF META-FLUOXETINE HCl.ANALYTICAL METHOD VALIDATION10 and 20mg Fluoxetine Capsules HPLC DeterminationED. N0: 04Effective Date:APPROVED::META-FLUOXETINE HCl[RECOVERY IN SPIKED SAMPLES].Approx.Conc.(%)Known Conc.(µg/100ml)Area in SpikedSampleFound Conc.(µg/100mL)Recovery (%)0.0521.783326125.735118.10.0521.783326825.821118.50.0521.783292021.55799.00.0521.783324125.490117.00.0521.783287220.96996.30.0521.783328526.030119.5(%) AVERAGE111.4SD The recovery result of 6 samples is between 80%-120%.10.7(%) RSDQL for Meta Fluoxetine HCl is 0.05%.9.6Accuracy for Meta Fluoxetine HClDetermination of Accuracy for Meta-Fluoxetine HCl impurity was assessed using triplicate samples (of the drug product) spiked with known quantities of Meta Fluoxetine HCl impurity at three concentrations levels (namely 80%, 100% and 120% of the specified limit - 0.05%).The results are within specifications:For 0.4% and 0.5% recovery of 85% -115%For 0.6% recovery of 90%-110%HPLC ASSAY with DETERMINATION OF META-FLUOXETINE HCl.ANALYTICAL METHOD VALIDATION10 and 20mg Fluoxetine Capsules HPLC DeterminationED. N0: 04Effective Date:APPROVED::META-FLUOXETINE HCl[RECOVERY IN SPIKED SAMPLES]Approx.Conc.(%)Known Conc.(µg/100mL)Area in spikedSample Found Conc.(µg/100mL)Recovery (%)[0.4%]0.4174.2614283182.66104.820.4174.2614606187.11107.370.4174.2614351183.59105.36[0.5%]0.5217.8317344224.85103.220.5217.8316713216.1599.230.5217.8317341224.81103.20[0.6%]0.6261.3918367238.9591.420.6261.3920606269.81103.220.6261.3920237264.73101.28RECOVERY DATA DETERMINED IN SPIKED SAMPLESHPLC ASSAY with DETERMINATION OF META-FLUOXETINE HCl.ANALYTICAL METHOD VALIDATION10 and 20mg Fluoxetine Capsules HPLC DeterminationED. N0: 04Effective Date:APPROVED::REPEATABILITYMethod Repeatability - Meta Fluoxetine HClThe full method (as described in SI-IAG-206-02) was carried out on the finished drug product representing lot number IAG-21-001-(1). The HPLC method repeated serially, six times and the relative standard deviation (RSD) was calculated.IAG-21-001 20mg CAPSULES - FLUOXETINESample% Meta Fluoxetine % Meta-Fluoxetine 1 in Spiked Solution10.0260.09520.0270.08630.0320.07740.0300.07450.0240.09060.0280.063AVERAGE (%)0.0280.081SD 0.0030.012RSD, (%)10.314.51NOTE :All results are less than QL (0.05%) therefore spiked samples with 0.05% Meta Fluoxetine HCl were injected.HPLC ASSAY with DETERMINATION OF META-FLUOXETINE HCl.ANALYTICAL METHOD VALIDATION10 and 20mg Fluoxetine Capsules HPLC DeterminationED. N0: 04Effective Date:APPROVED::Intermediate Precision - Meta-Fluoxetine HClThe full method as described in SI-IAG-206-02 was applied on the finished product IAG-21-001-(1) .It was repeated six times, with a different analyst on a different day using a different HPLC instrument.The difference between the average results obtained by the method repeatability and the intermediate precision was less than 30.0%, (11.4% for Meta-Fluoxetine HCl as is and 28.5% for spiked solution).IAG-21-001 20mg - CAPSULES FLUOXETINESample N o:Percentage Meta-fluoxetine% Meta-fluoxetine 1 in spiked solution10.0260.06920.0270.05730.0120.06140.0210.05850.0360.05560.0270.079(%) AVERAGE0.0250.063SD 0.0080.009(%) RSD31.514.51NOTE:All results obtained were well below the QL (0.05%) thus spiked samples slightly greater than 0.05% Meta-Fluoxetine HCl were injected. The RSD at the QL of the spiked solution was 14.5%HPLC ASSAY with DETERMINATION OF META-FLUOXETINE HCl.ANALYTICAL METHOD VALIDATION10 and 20mg Fluoxetine Capsules HPLC DeterminationSPECIFICITY - STABILITY INDICATING EVALUATIONDemonstration of the Stability Indicating parameters of the HPLC assay method [SI-IAG-206-02] for Fluoxetine 10 & 20mg capsules, a suitable photo-diode array detector was incorporated utilizing a commercial chromatography software managing system2, and applied to analyze a range of stressed samples of the finished drug product.GLOSSARY of PEAK PURITY RESULT NOTATION (as reported2):Purity Angle-is a measure of spectral non-homogeneity across a peak, i.e. the weighed average of all spectral contrast angles calculated by comparing all spectra in the integrated peak against the peak apex spectrum.Purity Threshold-is the sum of noise angle3 and solvent angle4. It is the limit of detection of shape differences between two spectra.Match Angle-is a comparison of the spectrum at the peak apex against a library spectrum.Match Threshold-is the sum of the match noise angle3 and match solvent angle4.3Noise Angle-is a measure of spectral non-homogeneity caused by system noise.4Solvent Angle-is a measure of spectral non-homogeneity caused by solvent composition.OVERVIEWT he assay of the main peak in each stressed solution is calculated according to the assay method SI-IAG-206-02, against the Standard Solution, injected on the same day.I f the Purity Angle is smaller than the Purity Threshold and the Match Angle is smaller than the Match Threshold, no significant differences between spectra can be detected. As a result no spectroscopic evidence for co-elution is evident and the peak is considered to be pure.T he stressed condition study indicated that the Fluoxetine peak is free from any appreciable degradation interference under the stressed conditions tested. Observed degradation products peaks were well separated from the main peak.1® PDA-996 Waters™ ; 2[Millennium 2010]ED. N0: 04Effective Date:APPROVED::HPLC ASSAY with DETERMINATION OF META-FLUOXETINE HCl.ANALYTICAL METHOD VALIDATION10 and 20mg Fluoxetine Capsules HPLC DeterminationFORCED DEGRADATION OF FINISHED PRODUCT & STANDARD 1.UNSTRESSED SAMPLE1.1.Sample IAG-21-001 (2) (20mg/capsule) was prepared as stated in SI-IAG-206-02 and injected into the HPLC system. The calculated assay is 98.5%.SAMPLE - UNSTRESSEDFluoxetine:Purity Angle:0.075Match Angle:0.407Purity Threshold:0.142Match Threshold:0.4251.2.Standard solution was prepared as stated in method SI-IAG-206-02 and injected into the HPLC system. The calculated assay is 100.0%.Fluoxetine:Purity Angle:0.078Match Angle:0.379Purity Threshold:0.146Match Threshold:0.4272.ACID HYDROLYSIS2.1.Sample solution of IAG-21-001 (2) (20mg/capsule) was prepared as in method SI-IAG-206-02 : An amount equivalent to 20mg Fluoxetine was weighed into a 50mL volumetric flask. 20mL Diluent was added and the solution sonicated for 10 minutes. 1mL of conc. HCl was added to this solution The solution was allowed to stand for 18 hours, then adjusted to about pH = 5.5 with NaOH 10N, made up to volume with Diluent and injected into the HPLC system after filtration.Fluoxetine peak intensity did NOT decrease. Assay result obtained - 98.8%.SAMPLE- ACID HYDROLYSISFluoxetine peak:Purity Angle:0.055Match Angle:0.143Purity Threshold:0.096Match Threshold:0.3712.2.Standard solution was prepared as in method SI-IAG-206-02 : about 22mg Fluoxetine HCl were weighed into a 50mL volumetric flask. 20mL Diluent were added. 2mL of conc. HCl were added to this solution. The solution was allowed to stand for 18 hours, then adjusted to about pH = 5.5 with NaOH 10N, made up to volume with Diluent and injected into the HPLC system.Fluoxetine peak intensity did NOT decrease. Assay result obtained - 97.2%.ED. N0: 04Effective Date:APPROVED::HPLC ASSAY with DETERMINATION OF META-FLUOXETINE HCl.ANALYTICAL METHOD VALIDATION10 and 20mg Fluoxetine Capsules HPLC DeterminationSTANDARD - ACID HYDROLYSISFluoxetine peak:Purity Angle:0.060Match Angle:0.060Purity Threshold:0.099Match Threshold:0.3713.BASE HYDROLYSIS3.1.Sample solution of IAG-21-001 (2) (20mg/capsule) was prepared as per method SI-IAG-206-02 : An amount equivalent to 20mg Fluoxetine was weight into a 50mL volumetric flask. 20mL Diluent was added and the solution sonicated for 10 minutes. 1mL of 5N NaOH was added to this solution. The solution was allowed to stand for 18 hours, then adjusted to about pH = 5.5 with 5N HCl, made up to volume with Diluent and injected into the HPLC system.Fluoxetine peak intensity did NOT decrease. Assay result obtained - 99.3%.SAMPLE - BASE HYDROLYSISFluoxetine peak:Purity Angle:0.063Match Angle:0.065Purity Threshold:0.099Match Threshold:0.3623.2.Standard stock solution was prepared as per method SI-IAG-206-02 : About 22mg Fluoxetine HCl was weighed into a 50mL volumetric flask. 20mL Diluent was added. 2mL of 5N NaOH was added to this solution. The solution was allowed to stand for 18 hours, then adjusted to about pH=5.5 with 5N HCl, made up to volume with Diluent and injected into the HPLC system.Fluoxetine peak intensity did NOT decrease - 99.5%.STANDARD - BASE HYDROLYSISFluoxetine peak:Purity Angle:0.081Match Angle:0.096Purity Threshold:0.103Match Threshold:0.3634.OXIDATION4.1.Sample solution of IAG-21-001 (2) (20mg/capsule) was prepared as per method SI-IAG-206-02. An equivalent to 20mg Fluoxetine was weighed into a 50mL volumetric flask. 20mL Diluent added and the solution sonicated for 10 minutes.1.0mL of 30% H2O2 was added to the solution and allowed to stand for 5 hours, then made up to volume with Diluent, filtered and injected into HPLC system.Fluoxetine peak intensity decreased to 95.2%.ED. N0: 04Effective Date:APPROVED::HPLC ASSAY with DETERMINATION OF META-FLUOXETINE HCl.ANALYTICAL METHOD VALIDATION10 and 20mg Fluoxetine Capsules HPLC DeterminationSAMPLE - OXIDATIONFluoxetine peak:Purity Angle:0.090Match Angle:0.400Purity Threshold:0.154Match Threshold:0.4294.2.Standard solution was prepared as in method SI-IAG-206-02 : about 22mg Fluoxetine HCl were weighed into a 50mL volumetric flask and 25mL Diluent were added. 2mL of 30% H2O2 were added to this solution which was standing for 5 hours, made up to volume with Diluent and injected into the HPLC system.Fluoxetine peak intensity decreased to 95.8%.STANDARD - OXIDATIONFluoxetine peak:Purity Angle:0.083Match Angle:0.416Purity Threshold:0.153Match Threshold:0.4295.SUNLIGHT5.1.Sample solution of IAG-21-001 (2) (20mg/capsule) was prepared as in method SI-IAG-206-02 . The solution was exposed to 500w/hr. cell sunlight for 1hour. The BST was set to 35°C and the ACT was 45°C. The vials were placed in a horizontal position (4mm vials, National + Septum were used). A Dark control solution was tested. A 2%w/v quinine solution was used as the reference absorbance solution.Fluoxetine peak decreased to 91.2% and the dark control solution showed assay of 97.0%. The difference in the absorbance in the quinine solution is 0.4227AU.Additional peak was observed at RRT of 1.5 (2.7%).The total percent of Fluoxetine peak with the degradation peak is about 93.9%.SAMPLE - SUNLIGHTFluoxetine peak:Purity Angle:0.093Match Angle:0.583Purity Threshold:0.148Match Threshold:0.825 ED. N0: 04Effective Date:APPROVED::HPLC ASSAY with DETERMINATION OF META-FLUOXETINE HCl.ANALYTICAL METHOD VALIDATION10 and 20mg Fluoxetine Capsules HPLC DeterminationSUNLIGHT (Cont.)5.2.Working standard solution was prepared as in method SI-IAG-206-02 . The solution was exposed to 500w/hr. cell sunlight for 1.5 hour. The BST was set to 35°C and the ACT was 42°C. The vials were placed in a horizontal position (4mm vials, National + Septum were used). A Dark control solution was tested. A 2%w/v quinine solution was used as the reference absorbance solution.Fluoxetine peak was decreased to 95.2% and the dark control solution showed assay of 99.5%.The difference in the absorbance in the quinine solution is 0.4227AU.Additional peak were observed at RRT of 1.5 (2.3).The total percent of Fluoxetine peak with the degradation peak is about 97.5%. STANDARD - SUNLIGHTFluoxetine peak:Purity Angle:0.067Match Angle:0.389Purity Threshold:0.134Match Threshold:0.8196.HEAT OF SOLUTION6.1.Sample solution of IAG-21-001-(2) (20 mg/capsule) was prepared as in method SI-IAG-206-02 . Equivalent to 20mg Fluoxetine was weighed into a 50mL volumetric flask. 20mL Diluent was added and the solution was sonicated for 10 minutes and made up to volume with Diluent. 4mL solution was transferred into a suitable crucible, heated at 105°C in an oven for 2 hours. The sample was cooled to ambient temperature, filtered and injected into the HPLC system.Fluoxetine peak was decreased to 93.3%.SAMPLE - HEAT OF SOLUTION [105o C]Fluoxetine peak:Purity Angle:0.062Match Angle:0.460Purity Threshold:0.131Match Threshold:0.8186.2.Standard Working Solution (WS) was prepared under method SI-IAG-206-02 . 4mL of the working solution was transferred into a suitable crucible, placed in an oven at 105°C for 2 hours, cooled to ambient temperature and injected into the HPLC system.Fluoxetine peak intensity did not decrease - 100.5%.ED. N0: 04Effective Date:APPROVED::。

MIPS芯片架构说明

MIPS32™ Architecture For Programmers Volume I: Introduction to the MIPS32™ArchitectureDocument Number: MD00082Revision 2.00June 8, 2003MIPS Technologies, Inc.1225 Charleston RoadMountain View, CA 94043-1353Copyright © 2001-2003 MIPS Technologies Inc. All rights reserved.Copyright ©2001-2003 MIPS Technologies, Inc. All rights reserved.Unpublished rights (if any) reserved under the copyright laws of the United States of America and other countries.This document contains information that is proprietary to MIPS Technologies, Inc. ("MIPS Technologies"). Any copying,reproducing,modifying or use of this information(in whole or in part)that is not expressly permitted in writing by MIPS Technologies or an authorized third party is strictly prohibited. At a minimum, this information is protected under unfair competition and copyright laws. Violations thereof may result in criminal penalties and fines.Any document provided in source format(i.e.,in a modifiable form such as in FrameMaker or Microsoft Word format) is subject to use and distribution restrictions that are independent of and supplemental to any and all confidentiality restrictions. UNDER NO CIRCUMSTANCES MAY A DOCUMENT PROVIDED IN SOURCE FORMAT BE DISTRIBUTED TO A THIRD PARTY IN SOURCE FORMAT WITHOUT THE EXPRESS WRITTEN PERMISSION OF MIPS TECHNOLOGIES, INC.MIPS Technologies reserves the right to change the information contained in this document to improve function,design or otherwise.MIPS Technologies does not assume any liability arising out of the application or use of this information, or of any error or omission in such information. Any warranties, whether express, statutory, implied or otherwise, including but not limited to the implied warranties of merchantability orfitness for a particular purpose,are excluded. Except as expressly provided in any written license agreement from MIPS Technologies or an authorized third party,the furnishing of this document does not give recipient any license to any intellectual property rights,including any patent rights, that cover the information in this document.The information contained in this document shall not be exported or transferred for the purpose of reexporting in violation of any U.S. or non-U.S. regulation, treaty, Executive Order, law, statute, amendment or supplement thereto. The information contained in this document constitutes one or more of the following: commercial computer software, commercial computer software documentation or other commercial items.If the user of this information,or any related documentation of any kind,including related technical data or manuals,is an agency,department,or other entity of the United States government ("Government"), the use, duplication, reproduction, release, modification, disclosure, or transfer of this information, or any related documentation of any kind, is restricted in accordance with Federal Acquisition Regulation12.212for civilian agencies and Defense Federal Acquisition Regulation Supplement227.7202 for military agencies.The use of this information by the Government is further restricted in accordance with the terms of the license agreement(s) and/or applicable contract terms and conditions covering this information from MIPS Technologies or an authorized third party.MIPS,R3000,R4000,R5000and R10000are among the registered trademarks of MIPS Technologies,Inc.in the United States and other countries,and MIPS16,MIPS16e,MIPS32,MIPS64,MIPS-3D,MIPS-based,MIPS I,MIPS II,MIPS III,MIPS IV,MIPS V,MIPSsim,SmartMIPS,MIPS Technologies logo,4K,4Kc,4Km,4Kp,4KE,4KEc,4KEm,4KEp, 4KS, 4KSc, 4KSd, M4K, 5K, 5Kc, 5Kf, 20Kc, 25Kf, ASMACRO, ATLAS, At the Core of the User Experience., BusBridge, CoreFPGA, CoreLV, EC, JALGO, MALTA, MDMX, MGB, PDtrace, Pipeline, Pro, Pro Series, SEAD, SEAD-2, SOC-it and YAMON are among the trademarks of MIPS Technologies, Inc.All other trademarks referred to herein are the property of their respective owners.Template: B1.08, Built with tags: 2B ARCH MIPS32MIPS32™ Architecture For Programmers Volume I, Revision 2.00 Copyright © 2001-2003 MIPS Technologies Inc. All rights reserved.Table of ContentsChapter 1 About This Book (1)1.1 Typographical Conventions (1)1.1.1 Italic Text (1)1.1.2 Bold Text (1)1.1.3 Courier Text (1)1.2 UNPREDICTABLE and UNDEFINED (2)1.2.1 UNPREDICTABLE (2)1.2.2 UNDEFINED (2)1.3 Special Symbols in Pseudocode Notation (2)1.4 For More Information (4)Chapter 2 The MIPS Architecture: An Introduction (7)2.1 MIPS32 and MIPS64 Overview (7)2.1.1 Historical Perspective (7)2.1.2 Architectural Evolution (7)2.1.3 Architectural Changes Relative to the MIPS I through MIPS V Architectures (9)2.2 Compliance and Subsetting (9)2.3 Components of the MIPS Architecture (10)2.3.1 MIPS Instruction Set Architecture (ISA) (10)2.3.2 MIPS Privileged Resource Architecture (PRA) (10)2.3.3 MIPS Application Specific Extensions (ASEs) (10)2.3.4 MIPS User Defined Instructions (UDIs) (11)2.4 Architecture Versus Implementation (11)2.5 Relationship between the MIPS32 and MIPS64 Architectures (11)2.6 Instructions, Sorted by ISA (12)2.6.1 List of MIPS32 Instructions (12)2.6.2 List of MIPS64 Instructions (13)2.7 Pipeline Architecture (13)2.7.1 Pipeline Stages and Execution Rates (13)2.7.2 Parallel Pipeline (14)2.7.3 Superpipeline (14)2.7.4 Superscalar Pipeline (14)2.8 Load/Store Architecture (15)2.9 Programming Model (15)2.9.1 CPU Data Formats (16)2.9.2 FPU Data Formats (16)2.9.3 Coprocessors (CP0-CP3) (16)2.9.4 CPU Registers (16)2.9.5 FPU Registers (18)2.9.6 Byte Ordering and Endianness (21)2.9.7 Memory Access Types (25)2.9.8 Implementation-Specific Access Types (26)2.9.9 Cache Coherence Algorithms and Access Types (26)2.9.10 Mixing Access Types (26)Chapter 3 Application Specific Extensions (27)3.1 Description of ASEs (27)3.2 List of Application Specific Instructions (28)3.2.1 The MIPS16e Application Specific Extension to the MIPS32Architecture (28)3.2.2 The MDMX Application Specific Extension to the MIPS64 Architecture (28)3.2.3 The MIPS-3D Application Specific Extension to the MIPS64 Architecture (28)MIPS32™ Architecture For Programmers Volume I, Revision 2.00i Copyright © 2001-2003 MIPS Technologies Inc. All rights reserved.3.2.4 The SmartMIPS Application Specific Extension to the MIPS32 Architecture (28)Chapter 4 Overview of the CPU Instruction Set (29)4.1 CPU Instructions, Grouped By Function (29)4.1.1 CPU Load and Store Instructions (29)4.1.2 Computational Instructions (32)4.1.3 Jump and Branch Instructions (35)4.1.4 Miscellaneous Instructions (37)4.1.5 Coprocessor Instructions (40)4.2 CPU Instruction Formats (41)Chapter 5 Overview of the FPU Instruction Set (43)5.1 Binary Compatibility (43)5.2 Enabling the Floating Point Coprocessor (44)5.3 IEEE Standard 754 (44)5.4 FPU Data Types (44)5.4.1 Floating Point Formats (44)5.4.2 Fixed Point Formats (48)5.5 Floating Point Register Types (48)5.5.1 FPU Register Models (49)5.5.2 Binary Data Transfers (32-Bit and 64-Bit) (49)5.5.3 FPRs and Formatted Operand Layout (50)5.6 Floating Point Control Registers (FCRs) (50)5.6.1 Floating Point Implementation Register (FIR, CP1 Control Register 0) (51)5.6.2 Floating Point Control and Status Register (FCSR, CP1 Control Register 31) (53)5.6.3 Floating Point Condition Codes Register (FCCR, CP1 Control Register 25) (55)5.6.4 Floating Point Exceptions Register (FEXR, CP1 Control Register 26) (56)5.6.5 Floating Point Enables Register (FENR, CP1 Control Register 28) (56)5.7 Formats of Values Used in FP Registers (57)5.8 FPU Exceptions (58)5.8.1 Exception Conditions (59)5.9 FPU Instructions (62)5.9.1 Data Transfer Instructions (62)5.9.2 Arithmetic Instructions (63)5.9.3 Conversion Instructions (65)5.9.4 Formatted Operand-Value Move Instructions (66)5.9.5 Conditional Branch Instructions (67)5.9.6 Miscellaneous Instructions (68)5.10 Valid Operands for FPU Instructions (68)5.11 FPU Instruction Formats (70)5.11.1 Implementation Note (71)Appendix A Instruction Bit Encodings (75)A.1 Instruction Encodings and Instruction Classes (75)A.2 Instruction Bit Encoding Tables (75)A.3 Floating Point Unit Instruction Format Encodings (82)Appendix B Revision History (85)ii MIPS32™ Architecture For Programmers Volume I, Revision 2.00 Copyright © 2001-2003 MIPS Technologies Inc. All rights reserved.Figure 2-1: Relationship between the MIPS32 and MIPS64 Architectures (11)Figure 2-2: One-Deep Single-Completion Instruction Pipeline (13)Figure 2-3: Four-Deep Single-Completion Pipeline (14)Figure 2-4: Four-Deep Superpipeline (14)Figure 2-5: Four-Way Superscalar Pipeline (15)Figure 2-6: CPU Registers (18)Figure 2-7: FPU Registers for a 32-bit FPU (20)Figure 2-8: FPU Registers for a 64-bit FPU if Status FR is 1 (21)Figure 2-9: FPU Registers for a 64-bit FPU if Status FR is 0 (22)Figure 2-10: Big-Endian Byte Ordering (23)Figure 2-11: Little-Endian Byte Ordering (23)Figure 2-12: Big-Endian Data in Doubleword Format (24)Figure 2-13: Little-Endian Data in Doubleword Format (24)Figure 2-14: Big-Endian Misaligned Word Addressing (25)Figure 2-15: Little-Endian Misaligned Word Addressing (25)Figure 3-1: MIPS ISAs and ASEs (27)Figure 3-2: User-Mode MIPS ISAs and Optional ASEs (27)Figure 4-1: Immediate (I-Type) CPU Instruction Format (42)Figure 4-2: Jump (J-Type) CPU Instruction Format (42)Figure 4-3: Register (R-Type) CPU Instruction Format (42)Figure 5-1: Single-Precisions Floating Point Format (S) (45)Figure 5-2: Double-Precisions Floating Point Format (D) (45)Figure 5-3: Paired Single Floating Point Format (PS) (46)Figure 5-4: Word Fixed Point Format (W) (48)Figure 5-5: Longword Fixed Point Format (L) (48)Figure 5-6: FPU Word Load and Move-to Operations (49)Figure 5-7: FPU Doubleword Load and Move-to Operations (50)Figure 5-8: Single Floating Point or Word Fixed Point Operand in an FPR (50)Figure 5-9: Double Floating Point or Longword Fixed Point Operand in an FPR (50)Figure 5-10: Paired-Single Floating Point Operand in an FPR (50)Figure 5-11: FIR Register Format (51)Figure 5-12: FCSR Register Format (53)Figure 5-13: FCCR Register Format (55)Figure 5-14: FEXR Register Format (56)Figure 5-15: FENR Register Format (56)Figure 5-16: Effect of FPU Operations on the Format of Values Held in FPRs (58)Figure 5-17: I-Type (Immediate) FPU Instruction Format (71)Figure 5-18: R-Type (Register) FPU Instruction Format (71)Figure 5-19: Register-Immediate FPU Instruction Format (71)Figure 5-20: Condition Code, Immediate FPU Instruction Format (71)Figure 5-21: Formatted FPU Compare Instruction Format (71)Figure 5-22: FP RegisterMove, Conditional Instruction Format (71)Figure 5-23: Four-Register Formatted Arithmetic FPU Instruction Format (72)Figure 5-24: Register Index FPU Instruction Format (72)Figure 5-25: Register Index Hint FPU Instruction Format (72)Figure 5-26: Condition Code, Register Integer FPU Instruction Format (72)Figure A-1: Sample Bit Encoding Table (76)MIPS32™ Architecture For Programmers Volume I, Revision 2.00iii Copyright © 2001-2003 MIPS Technologies Inc. All rights reserved.Table 1-1: Symbols Used in Instruction Operation Statements (2)Table 2-1: MIPS32 Instructions (12)Table 2-2: MIPS64 Instructions (13)Table 2-3: Unaligned Load and Store Instructions (24)Table 4-1: Load and Store Operations Using Register + Offset Addressing Mode (30)Table 4-2: Aligned CPU Load/Store Instructions (30)Table 4-3: Unaligned CPU Load and Store Instructions (31)Table 4-4: Atomic Update CPU Load and Store Instructions (31)Table 4-5: Coprocessor Load and Store Instructions (31)Table 4-6: FPU Load and Store Instructions Using Register+Register Addressing (32)Table 4-7: ALU Instructions With an Immediate Operand (33)Table 4-8: Three-Operand ALU Instructions (33)Table 4-9: Two-Operand ALU Instructions (34)Table 4-10: Shift Instructions (34)Table 4-11: Multiply/Divide Instructions (35)Table 4-12: Unconditional Jump Within a 256 Megabyte Region (36)Table 4-13: PC-Relative Conditional Branch Instructions Comparing Two Registers (36)Table 4-14: PC-Relative Conditional Branch Instructions Comparing With Zero (37)Table 4-15: Deprecated Branch Likely Instructions (37)Table 4-16: Serialization Instruction (38)Table 4-17: System Call and Breakpoint Instructions (38)Table 4-18: Trap-on-Condition Instructions Comparing Two Registers (38)Table 4-19: Trap-on-Condition Instructions Comparing an Immediate Value (38)Table 4-20: CPU Conditional Move Instructions (39)Table 4-21: Prefetch Instructions (39)Table 4-22: NOP Instructions (40)Table 4-23: Coprocessor Definition and Use in the MIPS Architecture (40)Table 4-24: CPU Instruction Format Fields (42)Table 5-1: Parameters of Floating Point Data Types (45)Table 5-2: Value of Single or Double Floating Point DataType Encoding (46)Table 5-3: Value Supplied When a New Quiet NaN Is Created (47)Table 5-4: FIR Register Field Descriptions (51)Table 5-5: FCSR Register Field Descriptions (53)Table 5-6: Cause, Enable, and Flag Bit Definitions (55)Table 5-7: Rounding Mode Definitions (55)Table 5-8: FCCR Register Field Descriptions (56)Table 5-9: FEXR Register Field Descriptions (56)Table 5-10: FENR Register Field Descriptions (57)Table 5-11: Default Result for IEEE Exceptions Not Trapped Precisely (60)Table 5-12: FPU Data Transfer Instructions (62)Table 5-13: FPU Loads and Stores Using Register+Offset Address Mode (63)Table 5-14: FPU Loads and Using Register+Register Address Mode (63)Table 5-15: FPU Move To and From Instructions (63)Table 5-16: FPU IEEE Arithmetic Operations (64)Table 5-17: FPU-Approximate Arithmetic Operations (64)Table 5-18: FPU Multiply-Accumulate Arithmetic Operations (65)Table 5-19: FPU Conversion Operations Using the FCSR Rounding Mode (65)Table 5-20: FPU Conversion Operations Using a Directed Rounding Mode (65)Table 5-21: FPU Formatted Operand Move Instructions (66)Table 5-22: FPU Conditional Move on True/False Instructions (66)iv MIPS32™ Architecture For Programmers Volume I, Revision 2.00 Copyright © 2001-2003 MIPS Technologies Inc. All rights reserved.Table 5-23: FPU Conditional Move on Zero/Nonzero Instructions (67)Table 5-24: FPU Conditional Branch Instructions (67)Table 5-25: Deprecated FPU Conditional Branch Likely Instructions (67)Table 5-26: CPU Conditional Move on FPU True/False Instructions (68)Table 5-27: FPU Operand Format Field (fmt, fmt3) Encoding (68)Table 5-28: Valid Formats for FPU Operations (69)Table 5-29: FPU Instruction Format Fields (72)Table A-1: Symbols Used in the Instruction Encoding Tables (76)Table A-2: MIPS32 Encoding of the Opcode Field (77)Table A-3: MIPS32 SPECIAL Opcode Encoding of Function Field (78)Table A-4: MIPS32 REGIMM Encoding of rt Field (78)Table A-5: MIPS32 SPECIAL2 Encoding of Function Field (78)Table A-6: MIPS32 SPECIAL3 Encoding of Function Field for Release 2 of the Architecture (78)Table A-7: MIPS32 MOVCI Encoding of tf Bit (79)Table A-8: MIPS32 SRL Encoding of Shift/Rotate (79)Table A-9: MIPS32 SRLV Encoding of Shift/Rotate (79)Table A-10: MIPS32 BSHFL Encoding of sa Field (79)Table A-11: MIPS32 COP0 Encoding of rs Field (79)Table A-12: MIPS32 COP0 Encoding of Function Field When rs=CO (80)Table A-13: MIPS32 COP1 Encoding of rs Field (80)Table A-14: MIPS32 COP1 Encoding of Function Field When rs=S (80)Table A-15: MIPS32 COP1 Encoding of Function Field When rs=D (81)Table A-16: MIPS32 COP1 Encoding of Function Field When rs=W or L (81)Table A-17: MIPS64 COP1 Encoding of Function Field When rs=PS (81)Table A-18: MIPS32 COP1 Encoding of tf Bit When rs=S, D, or PS, Function=MOVCF (81)Table A-19: MIPS32 COP2 Encoding of rs Field (82)Table A-20: MIPS64 COP1X Encoding of Function Field (82)Table A-21: Floating Point Unit Instruction Format Encodings (82)MIPS32™ Architecture For Programmers Volume I, Revision 2.00v Copyright © 2001-2003 MIPS Technologies Inc. All rights reserved.vi MIPS32™ Architecture For Programmers Volume I, Revision 2.00 Copyright © 2001-2003 MIPS Technologies Inc. All rights reserved.Chapter 1About This BookThe MIPS32™ Architecture For Programmers V olume I comes as a multi-volume set.•V olume I describes conventions used throughout the document set, and provides an introduction to the MIPS32™Architecture•V olume II provides detailed descriptions of each instruction in the MIPS32™ instruction set•V olume III describes the MIPS32™Privileged Resource Architecture which defines and governs the behavior of the privileged resources included in a MIPS32™ processor implementation•V olume IV-a describes the MIPS16e™ Application-Specific Extension to the MIPS32™ Architecture•V olume IV-b describes the MDMX™ Application-Specific Extension to the MIPS32™ Architecture and is notapplicable to the MIPS32™ document set•V olume IV-c describes the MIPS-3D™ Application-Specific Extension to the MIPS64™ Architecture and is notapplicable to the MIPS32™ document set•V olume IV-d describes the SmartMIPS™Application-Specific Extension to the MIPS32™ Architecture1.1Typographical ConventionsThis section describes the use of italic,bold and courier fonts in this book.1.1.1Italic Text•is used for emphasis•is used for bits,fields,registers, that are important from a software perspective (for instance, address bits used bysoftware,and programmablefields and registers),and variousfloating point instruction formats,such as S,D,and PS •is used for the memory access types, such as cached and uncached1.1.2Bold Text•represents a term that is being defined•is used for bits andfields that are important from a hardware perspective (for instance,register bits, which are not programmable but accessible only to hardware)•is used for ranges of numbers; the range is indicated by an ellipsis. For instance,5..1indicates numbers 5 through 1•is used to emphasize UNPREDICTABLE and UNDEFINED behavior, as defined below.1.1.3Courier TextCourier fixed-width font is used for text that is displayed on the screen, and for examples of code and instruction pseudocode.MIPS32™ Architecture For Programmers Volume I, Revision 2.001 Copyright © 2001-2003 MIPS Technologies Inc. All rights reserved.Chapter 1 About This Book1.2UNPREDICTABLE and UNDEFINEDThe terms UNPREDICTABLE and UNDEFINED are used throughout this book to describe the behavior of theprocessor in certain cases.UNDEFINED behavior or operations can occur only as the result of executing instructions in a privileged mode (i.e., in Kernel Mode or Debug Mode, or with the CP0 usable bit set in the Status register).Unprivileged software can never cause UNDEFINED behavior or operations. Conversely, both privileged andunprivileged software can cause UNPREDICTABLE results or operations.1.2.1UNPREDICTABLEUNPREDICTABLE results may vary from processor implementation to implementation,instruction to instruction,or as a function of time on the same implementation or instruction. Software can never depend on results that areUNPREDICTABLE.UNPREDICTABLE operations may cause a result to be generated or not.If a result is generated, it is UNPREDICTABLE.UNPREDICTABLE operations may cause arbitrary exceptions.UNPREDICTABLE results or operations have several implementation restrictions:•Implementations of operations generating UNPREDICTABLE results must not depend on any data source(memory or internal state) which is inaccessible in the current processor mode•UNPREDICTABLE operations must not read, write, or modify the contents of memory or internal state which is inaccessible in the current processor mode. For example,UNPREDICTABLE operations executed in user modemust not access memory or internal state that is only accessible in Kernel Mode or Debug Mode or in another process •UNPREDICTABLE operations must not halt or hang the processor1.2.2UNDEFINEDUNDEFINED operations or behavior may vary from processor implementation to implementation, instruction toinstruction, or as a function of time on the same implementation or instruction.UNDEFINED operations or behavior may vary from nothing to creating an environment in which execution can no longer continue.UNDEFINED operations or behavior may cause data loss.UNDEFINED operations or behavior has one implementation restriction:•UNDEFINED operations or behavior must not cause the processor to hang(that is,enter a state from which there is no exit other than powering down the processor).The assertion of any of the reset signals must restore the processor to an operational state1.3Special Symbols in Pseudocode NotationIn this book, algorithmic descriptions of an operation are described as pseudocode in a high-level language notation resembling Pascal. Special symbols used in the pseudocode notation are listed in Table 1-1.Table 1-1 Symbols Used in Instruction Operation StatementsSymbol Meaning←Assignment=, ≠Tests for equality and inequality||Bit string concatenationx y A y-bit string formed by y copies of the single-bit value x2MIPS32™ Architecture For Programmers Volume I, Revision 2.00 Copyright © 2001-2003 MIPS Technologies Inc. All rights reserved.1.3Special Symbols in Pseudocode Notationb#n A constant value n in base b.For instance10#100represents the decimal value100,2#100represents the binary value 100 (decimal 4), and 16#100 represents the hexadecimal value 100 (decimal 256). If the "b#" prefix is omitted, the default base is 10.x y..z Selection of bits y through z of bit string x.Little-endian bit notation(rightmost bit is0)is used.If y is less than z, this expression is an empty (zero length) bit string.+, −2’s complement or floating point arithmetic: addition, subtraction∗, ×2’s complement or floating point multiplication (both used for either)div2’s complement integer divisionmod2’s complement modulo/Floating point division<2’s complement less-than comparison>2’s complement greater-than comparison≤2’s complement less-than or equal comparison≥2’s complement greater-than or equal comparisonnor Bitwise logical NORxor Bitwise logical XORand Bitwise logical ANDor Bitwise logical ORGPRLEN The length in bits (32 or 64) of the CPU general-purpose registersGPR[x]CPU general-purpose register x. The content of GPR[0] is always zero.SGPR[s,x]In Release 2 of the Architecture, multiple copies of the CPU general-purpose registers may be implemented.SGPR[s,x] refers to GPR set s, register x. GPR[x] is a short-hand notation for SGPR[ SRSCtl CSS, x].FPR[x]Floating Point operand register xFCC[CC]Floating Point condition code CC.FCC[0] has the same value as COC[1].FPR[x]Floating Point (Coprocessor unit 1), general register xCPR[z,x,s]Coprocessor unit z, general register x,select sCP2CPR[x]Coprocessor unit 2, general register xCCR[z,x]Coprocessor unit z, control register xCP2CCR[x]Coprocessor unit 2, control register xCOC[z]Coprocessor unit z condition signalXlat[x]Translation of the MIPS16e GPR number x into the corresponding 32-bit GPR numberBigEndianMem Endian mode as configured at chip reset (0→Little-Endian, 1→ Big-Endian). Specifies the endianness of the memory interface(see LoadMemory and StoreMemory pseudocode function descriptions),and the endianness of Kernel and Supervisor mode execution.BigEndianCPU The endianness for load and store instructions (0→ Little-Endian, 1→ Big-Endian). In User mode, this endianness may be switched by setting the RE bit in the Status register.Thus,BigEndianCPU may be computed as (BigEndianMem XOR ReverseEndian).Table 1-1 Symbols Used in Instruction Operation StatementsSymbol MeaningChapter 1 About This Book1.4For More InformationVarious MIPS RISC processor manuals and additional information about MIPS products can be found at the MIPS URL:ReverseEndianSignal to reverse the endianness of load and store instructions.This feature is available in User mode only,and is implemented by setting the RE bit of the Status register.Thus,ReverseEndian may be computed as (SR RE and User mode).LLbitBit of virtual state used to specify operation for instructions that provide atomic read-modify-write.LLbit is set when a linked load occurs; it is tested and cleared by the conditional store. It is cleared, during other CPU operation,when a store to the location would no longer be atomic.In particular,it is cleared by exception return instructions.I :,I+n :,I-n :This occurs as a prefix to Operation description lines and functions as a label. It indicates the instruction time during which the pseudocode appears to “execute.” Unless otherwise indicated, all effects of the currentinstruction appear to occur during the instruction time of the current instruction.No label is equivalent to a time label of I . Sometimes effects of an instruction appear to occur either earlier or later — that is, during theinstruction time of another instruction.When this happens,the instruction operation is written in sections labeled with the instruction time,relative to the current instruction I ,in which the effect of that pseudocode appears to occur.For example,an instruction may have a result that is not available until after the next instruction.Such an instruction has the portion of the instruction operation description that writes the result register in a section labeled I +1.The effect of pseudocode statements for the current instruction labelled I +1appears to occur “at the same time”as the effect of pseudocode statements labeled I for the following instruction.Within one pseudocode sequence,the effects of the statements take place in order. However, between sequences of statements for differentinstructions that occur “at the same time,” there is no defined order. Programs must not depend on a particular order of evaluation between such sections.PCThe Program Counter value.During the instruction time of an instruction,this is the address of the instruction word. The address of the instruction that occurs during the next instruction time is determined by assigning a value to PC during an instruction time. If no value is assigned to PC during an instruction time by anypseudocode statement,it is automatically incremented by either 2(in the case of a 16-bit MIPS16e instruction)or 4before the next instruction time.A taken branch assigns the target address to the PC during the instruction time of the instruction in the branch delay slot.PABITSThe number of physical address bits implemented is represented by the symbol PABITS.As such,if 36physical address bits were implemented, the size of the physical address space would be 2PABITS = 236 bytes.FP32RegistersModeIndicates whether the FPU has 32-bit or 64-bit floating point registers (FPRs).In MIPS32,the FPU has 3232-bit FPRs in which 64-bit data types are stored in even-odd pairs of FPRs.In MIPS64,the FPU has 3264-bit FPRs in which 64-bit data types are stored in any FPR.In MIPS32implementations,FP32RegistersMode is always a 0.MIPS64implementations have a compatibility mode in which the processor references the FPRs as if it were a MIPS32 implementation. In such a caseFP32RegisterMode is computed from the FR bit in the Status register.If this bit is a 0,the processor operates as if it had 32 32-bit FPRs. If this bit is a 1, the processor operates with 32 64-bit FPRs.The value of FP32RegistersMode is computed from the FR bit in the Status register.InstructionInBranchDelaySlotIndicates whether the instruction at the Program Counter address was executed in the delay slot of a branch or jump. This condition reflects the dynamic state of the instruction, not the static state. That is, the value is false if a branch or jump occurs to an instruction whose PC immediately follows a branch or jump, but which is not executed in the delay slot of a branch or jump.SignalException(exce ption, argument)Causes an exception to be signaled, using the exception parameter as the type of exception and the argument parameter as an exception-specific argument). Control does not return from this pseudocode function - the exception is signaled at the point of the call.Table 1-1 Symbols Used in Instruction Operation StatementsSymbolMeaning。

les AS gR学生手册英文

Deploying with Oracle JDeveloper

To deploy an application with JDeveloper, perform the following steps: 1. Create the deployment profile. 2. Configure the deployment profile. 3. Create an application server connection to the target

第十六页,共33页,

Planning the Deployment Process

The deployment process includes:

1. Packaging code as J2EE applications or modules

2. Selecting a parent application

including those in a cluster

第十页,共33页,

Deploying with admin_client.jar

The admin_client.jar tool: • Is a command-line utility • Is executed by using the following basic command:

– defaultDataSource to select the data source used by the application for management of data by EJB entities

– dataSourcesPath to specify a application-specific data sources

通用串行总线2.0规范 英文翻译

Universal Serial Bus Specification Revision 2.0Introduction1.1 MotivationThe original motivation for the Universal Serial Bus (USB) came from three interrelated considerations:• Connection of the PC to the telephoneIt is well understood that the merge of computing and communication will be the basis for the next generation of productivity applications. The movement of machine-oriented and human-oriented data types from one location or environment to another depends on ubiquitous and cheap connectivity. Unfortunately, the computing and communication industries have evolved independently. The USB provides a ubiquitous link that can be used across a wide range of PC-to-telephone interconnects.• Ease-of-useThe lack of flexibility in reconfiguring the PC has been acknowledged as the Achilles’ heel to its further deployment. The combination of user-friendly graphical interfaces and the hardware and software mechanisms associated with new-generation bus architectures have made computers less confrontational and easier to reconfigure. However, from the end user’s point of view, the PC’s I/O interfaces, such as serial/parallel ports, keyboard/mouse/joystick interfaces, etc., do not have the attributes of plug-and-play.• Port expansionThe addition of external peripherals continues to be constrained by port availability. The lack of a bidirectional, low-cost, low-to-mid speed peripheral bus has held back the creative proliferation of peripherals such as telephone/fax/modem adapters, answering machines, scanners, PDA’s, keyboards, mice, etc. Existing interconnects are optimized for one or two point products. As each new function or capability is added to the PC, a new interface has been defined to address this need. The more recent motivation for USB 2.0 stems from the fact that PCs have increasingly higher performance and are capable of processing vast amounts of data. At the same time, PC peripherals have added more performance and functionality. User applications such as digital imaging demand a high performance connection between the PC and these increasingly sophisticated peripherals. USB 2.0 addresses this need by adding a third transfer rate of 480 Mb/s to the 12 Mb/s and 1.5 Mb/s originally defined for USB. USB 2.0 is a natural evolution of USB, delivering the desired bandwidth increase while preserving the original motivations for USB and maintaining full compatibility with existing peripherals. Thus, USB continues to be the answer to connectivity for the PC architecture. It is a fast, bi-directional, isochronous, low-cost, dynamically attachable serial interface that is consistent with the requirements of the PC platform of today and tomorrow.1.2 Objective of the SpecificationThis document defines an industry-standard USB. The specification describes the bus attributes, the protocol definition, types of transactions, bus management, and the programming interface required to design and build systems and peripherals that are compliant with this standard.The goal is to enable such devices from different vendors to interoperate in an open architecture.The specification is intended as an enhancement to the PC architecture, spanning portable, business desktop, and home environments. It is intended that the specification allow system OEMs and peripheral developers adequate room for product versatility and market differentiation without the burden of carrying obsolete interfaces or losing compatibility.1.3 Scope of the DocumentThe specification is primarily targeted to peripheral developers and system OEMs, but provides valuable information for platform operating system/ BIOS/ device driver, adapter IHVs/ISVs, and platform/adapter controller vendors. This specification can be used for developing new products and associated software.1.4 USB Product ComplianceAdopters of the USB 2.0 specification have signed the USB 2.0 Adopters Agreement, which provides them access to a reciprocal royalty-free license from the Promoters and other Adopters to certain intellectual property contained in products that are compliant with the USB 2.0 specification. Adopters can demonstrate compliance with the specification through the testing program as defined by the USB Implementers Forum. Products that demonstrate compliance with the specification will be granted certain rights to use the USB Implementers Forum logo as defined in the logo license.1.5 Document OrganizationChapters 1 through 5 provide an overview for all readers, while Chapters 6 through 11 contain detailed technical information defining the USB.• Peripheral implementers should particularly read Chapters 5 through 11.• USB Host Controller implementers should particularly read Chapters 5 through 8, 10, and 11. • USB device driver implementers should particularly read Chapters 5, 9, and 10.This document is complemented and referenced by the Universal Serial Bus Device Class Specifications. Device class specifications exist for a wide variety of devices. Please contact the USB Implementers Forum for further details.Readers are also requested to contact operating system vendors for operating system bindings specific to the USB.BackgroundThis chapter presents a brief description of the background of the Universal Serial Bus (USB), including design goals, features of the bus, and existing technologies.2.1 Goals for the Universal Serial BusThe USB is specified to be an industry-standard extension to the PC architecture with a focus on PC peripherals that enable consumer and business applications. The following criteria were applied in defining the architecture for the USB:• Ease-of-use for PC peripheral expansion• Low-cost solution that supports transfer rates up to 480 Mb/s• Full support for real-time data for voice, audio, and video• Protocol flexibility for mixed-mode isochronous data transfers and asynchronous messaging • Integration in commodity device technology• Comprehension of various PC configurations and form factors• Provision of a standard interface capable of quick diffusion into product• Enabling new classes of devices that augment the PC’s cap ability• Full backward compatibility of USB 2.0 for devices built to previous versions of the specification2.2 T axonomy of Application SpaceFigure 2-1 describes a taxonomy for the range of data traffic workloads that can be serviced over a USB. As can be seen, a 480 Mb/s bus comprehends the high-speed, full-speed, and low-speed data ranges. Typically, high-speed and full-speed data types may be isochronous, while low-speed data comes from interactive devices. The USB is primarily a PC bus but can be readily applied to other host-centric computing devices. The software architecture allows for future extension of the USB by providing support for multiple USB Host Controllers.Figure 2-1. Application Space T axonomy2.3 Feature ListThe USB Specification provides a selection of attributes that can achieve multiple price/performance integration points and can enable functions that allow differentiation at thesystem and component level.Features are categorized by the following benefits:Easy to use for end user• Single model for cabling and connectors• Electrical details isolated from end user (e.g., bus terminations)• Self-identifying peripherals, automatic mapping of function to driver and configuration • Dynamically attachable and reconfigurable peripheralsWide range of workloads and applications• Suitable for device bandwidths ranging from a few kb/s to several hundred Mb/s• Supports isochronous as well as asynchronous transfer types over the same set of wires • Supports concurrent operation of many devices (multiple connections)• Supports up to 127 physical devices• Supports transfer of multiple data and message streams between the host and devices• Allows compound devices (i.e., peripherals composed of many functions)• Lower protocol overhead, resulting in high bus utilizationIsochronous bandwidth• Guaranteed bandwidth and low latencies appropriate for telephony, audio, video, etc.Flexibility• Supports a wide range of packet sizes, which allows a range of device buffering options • Allows a wide range of device data rates by accommodating packet buffer size and latencies • Flow control for buffer handling is built into the protocolRobustness• Error handling/fault recovery mechanism is built into the protocol• Dynamic insertion and removal of devices is identified in user-perceived real-time• Supports identification of faulty devicesSynergy with PC industry• Protocol is simple to implement and integrate• Consistent with the PC plug-and-play architecture• Leverages existing operating system interfacesLow-cost implementation• Low-cost subchannel at 1.5 Mb/s• Optimized for integration in peripheral and host hardware• Suitable for development of low-cost peripherals• Low-cost cables and connectors• Uses commodity technologiesUpgrade path• Architecture upgradeable to support multiple USB Host Controllers in a systemArchitectural OverviewThis chapter presents an overview of the Universal Serial Bus (USB) architecture and key concepts. The USB is a cable bus that supports data exchange between a host computer and a wide range of simultaneously accessible peripherals. The attached peripherals share USB bandwidth through a hostscheduled, token-based protocol. The bus allows peripherals to be attached, configured, used, and detached while the host and other peripherals are in operation.Later chapters describe the various components of the USB in greater detail.3.1 USB System DescriptionA USB system is described by three definitional areas:• USB interconnect• USB devices• USB hostThe USB interconnect is the manner in which USB devices are connected to and communicate with the host. This includes the following:• Bus Topology: Connection model between USB devices and the host.• Inter-layer Relationships: In terms of a capability stack, the USB tasks that are performed at each layer in the system.• Data Flow Models: The manner in which data moves in the system over the USB between producers and consumers.• USB Schedule: The USB provides a shared interconnect. Access to the interconnect is scheduled in order to support isochronous data transfers and to eliminate arbitration overhead.USB devices and the USB host are described in detail in subsequent sections.3.1.1 Bus T opologyThe USB connects USB devices with the USB host. The USB physical interconnect is a tiered star topology. A hub is at the center of each star. Each wire segment is a point-to-point connection between the host and a hub or function, or a hub connected to another hub or function. Figure 3-1 illustrates the topology of the USB.Due to timing constraints allowed for hub and cable propagation times, the maximum number of tiers allowed is seven (including the root tier). Note that in seven tiers, five non-root hubs maximum can be supported in a communication path between the host and any device. A compound device (see Figure 3-1) occupies two tiers; therefore, it cannot be enabled if attached at tier level seven. Only functions can be enabled in tier seven.Figure 3-1. Bus T opology3.1.1.1 USB HostThere is only one host in any USB system. The USB interface to the host computer system is referred to as the Host Controller. The Host Controller may be implemented in a combination of hardware, firmware, or software. A root hub is integrated within the host system to provide one or more attachment points.Additional information concerning the host may be found in Section 4.9 and in Chapter 10.3.1.1.2 USB DevicesUSB devices are one of the following:• Hubs, which provide additional attachment points to the USB• Functions, which provide capabilities to the system, such as an ISDN connection, a digital joystick, or speakersUSB devices present a standard USB interface in terms of the following:• Their comprehension of the USB protocol• Their response to standard USB operations, such as configuration and reset• Their standard capability descriptive informationAdditional information concerning USB devices may be found in Section 4.8 and in Chapter 9.3.2 Physical InterfaceThe physical interface of the USB is described in the electrical (Chapter 7) and mechanical (Chapter 6) specifications for the bus.3.2.1 ElectricalThe USB transfers signal and power over a four-wire cable, shown in Figure 3-2. The signaling occurs over two wires on each point-to-point segment.There are three data rates:• The USB high-speed signaling bit rate is 480 Mb/s.• The USB full-speed signaling bit rate is 12 Mb/s.• A limited capability low-speed signaling mode is also defined at 1.5 Mb/s.Figure 3-2. USB CableUSB 2.0 host controllers and hubs provide capabilities so that full-speed and low-speed data can be transmitted at high-speed between the host controller and the hub, but transmitted between the hub and the device at full-speed or low-speed. This capability minimizes the impact that full-speed and low-speed devices have upon the bandwidth available for high-speed devices.The low-speed mode is defined to support a limited number of low-bandwidth devices, such as mice,because more general use would degrade bus utilization.3.2.2 MechanicalThe mechanical specifications for cables and connectors are provided in Chapter 6. All devices have an upstream connection. Upstream and downstream connectors are not mechanically interchangeable, thus eliminating illegal loopback connections at hubs. The cable has four conductors: a twisted signal pair of standard gauge and a power pair in a range of permitted gauges. The connector is four-position, with shielded housing, specified robustness, and ease of attach-detach characteristics.通用串行总线2.0规范介绍1.1 制定动机制定通用串行总线(USB)的原始动机来自于对三个相互关联的方面的综合考虑:•计算机和电话之间的连接计算机运作和通信技术的结合肯定将会成为下一代生产力应用的基础。

ISO1050中文资料_数据手册_参数

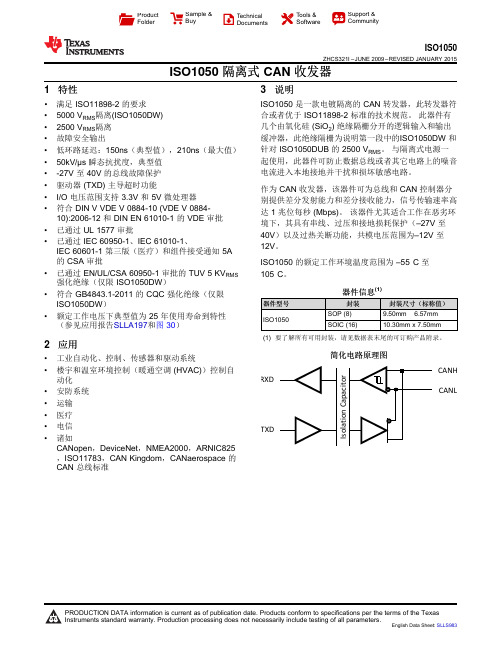

器件型号 ISO1050

器件信息(1)

封装

封装尺寸(标称值)

SOP (8)

9.50mm × 6.57mm

SOIC (16)

10.30mm x 7.50mm

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

简化电路原理图

CANH RXD

CANL

TXD

1பைடு நூலகம்

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

English Data Sheet: SLLS983

ISO1050

ZHCS321I – JUNE 2009 – REVISED JANUARY 2015

目录

1 特性.......................................................................... 1 2 应用.......................................................................... 1 3 说明.......................................................................... 1 4 修订历史记录 ........................................................... 2 5 Pin Configuration and Functions ......................... 5 6 Specifications......................................................... 6

软件工程总结具体

软件工程总结具体第一篇:软件工程总结具体第一章1.什么是软件危机?它有哪些典型表现?为什么会产生软件危机?软件危机是指在计算机软件的开发和维护过程中所遇到的一系列严重问题。

这些问题表现在以下几个方面:(1)用户对开发出的软件很难满意。

(2)软件产品的质量往往靠不住。

(3)一般软件很难维护。

(4)软件生产效率很低。

(5)软件开发成本越来越大。

(6)软件成本与开发进度难以估计。

(7)软件技术的发展远远满足不了计算机应用的普及与深入的需要。

产生软件危机的原因(1)开发人员方面,对软件产品缺乏正确认识,没有真正理解软件产品是一个完整的配置组成。

造成开发中制定计划盲目、编程草率,不考虑维护工作的必要性。

(2)软件本身方面,对于计算机系统来说,软件是逻辑部件,软件开发过程没有统一的、公认的方法论和规范指导,造成软件维护困难。

(3)尤其是随着软件规模越来越大,复杂程度越来越高,原有软件开发方式效率不高、质量不能保证、成本过高、研制周期不易估计、维护困难等一系列问题更为突出,技术的发展已经远远不能适应社会需求。

2.假设自己是一家软件公司的总工程师,当把图1.1给手下的软件工程师们观看,告诉他们及早发现并改正错误的重要性时,有人不同意这个观点,认为要求在错误进入软件之前就清除它们是不现实的,并举例说:“如果一个故障是编码错误造成的,那么,一个人怎么能在设计阶段清楚他呢?”应该怎样反驳他?反驳:发生在编码时期的故障极有可能是需求分析阶段由于操作不当产生的,所以必须及时消除错误,否则,到了后期软件运行和维护阶段再回过头来修改,将会付出更大的代价。

3.什么是软件工程?它有哪些本质特性?怎样用软件工程消除软件危机?软件工程是指导计算机软件开发和维护的工程学科。

(1)它采用工程的概念、原理、技术和方法来开发和维护软件;(2)它将管理技术与当前经过时间考验的而证明是正确的技术方法结合起来;(3)它强调使用生存周期方法学和结构分析和结构技术;(4)经过人们长期的努力和探索,围绕着实现软件优质高产这个目标,从技术到管理两个方面做了大量的努力,逐渐形成了“软件工程学”这一新的学科。

DisplayPort和eDP物理层兼容性测试中必须考虑的因素

Getting down to One data lane…

5 Pins1 data

lane

4 data lanes

AUX+/-, HPDConfig1/2

1 low

MyDP speed line

DisplayPort20 Pins

Power, Ground

Power, Ground

HDMI

Something Good is Happening…

MyDP

Standard DisplayPortComputing

eDP

Embedded Systems

Consumer Electronics

Portables

VESA: 200 members strong!

DisplayPort Technology Rollouts

The AUX Channel enables Link setup and maintenance as well as control for testing.

Tx

Driver

Logic

Decode

Main Link

AUX

Hot Plug Detect

Image buffer

EDID

DPCD

Sink

Key Features of DisplayPort

Hot Plug Detect

TransmitterAUX

Receiver (Sink)

AUX ChannelVery robust channel Setup Link/Maintain Link Test Assistance

uPacket BasedNot based on Raster timings Fixed bit rates

世界遗产运河文化保护传承利用的立法经验与借鉴

中国名城I 城市与运河世界遗产运河文化保护传承利用的立法经验与借鉴**基金项目:国家社科基金项目"文化博弈视阈下大运河国际形象提升路径研究"(编号:18BQJ086)。

田德新摘 要:针对中国大运河文化遗产保护、传承和利用 的立法现状和需求,以联合国科教科文组织的《保护世界文化与自然遗产公约》《实施“保护世界文化与自然遗产 公约”的操作指南》《保护非物质文化遗产公约》《保护和促进文化表现形式多样性公约》的相关文件,以及由保护框架、保护原则和保护模式构成的世界文化遗产保护国际法体系为宏观指导框架,以创造性运用最新科技将运河 开发与周边环保融为一体的米迪运河、多次有效转型其功能与角色,并成功推出里多文化遗产廊道生态旅游项目的 里多运河以及有效化解工业化和城市化副作用的庞特基西斯特水道桥与运河为案例,探析其通过立法来增强运河文 化和自然遗产以及非物质文化遗产保护、传承和利用方面 的经验,供国内借鉴。

关键词:世界遗产运河;米迪运河;庞特基西斯特 水道桥与运河;里多运河;经验Abstract : In answer tx> the legislative status quo and needsfor protecting, inheriting, and utilizing the cultural heritagesof China' s Grand Canal, the present paper explores the veryexperience herein from three representative canals on the UnitedNations Educational, Scientific , and Cultural Organization(UNESCO ) World Heritage List. The three representativecanals are respectively the Canal du Midi, the Rideau Canal,and the British Pontcysyllte Aqueduct & Canal, with the first creatively integrating the canal development with the environmentalprotection of the surroundings via the up-to-date high-tech, thesecond successfully transforming its functions and roles and launchir^the ecological tourism program along the Rideau Canal cultural heritage corridor, and the third efectively defused the side efects ofindustrialization and urbanization. What serve as the macro —theoreticalframeworks are : firstly, a series of U NESCO documents including作者简介田德新,扬州大学特聘教授,扬州大学外国语学院博士生导 师,博士。

照明系统外文翻译