A8283SB中文资料

2A3资料

2A3资料2A3的参考资料:关于2A3毫无疑问RCA的最好听,声音的细腻润泽、弹性和泛音是其他2A3所不能比拟的。

俄罗斯EH 2A3的声音有些令人失望,声音比较平白,弹性也不足够,甚至在中低频部分不如曙光。

曙光2A3是以RCA为蓝本设计的,确也有些RCA的风范,声底与RCA 2A3还是颇有些相似之处的,低频的力度甚至好过RCA 2A3。

胆机(电子管功放):它是音响业界最古老而又经久不衰的长青树,其显著的优点是声音甜美柔和、自然关切,尤其动态范围之大,线性之好,绝非其他器件所能轻意替代。

在晶体管产生后,由于其体积小,耗电省很快便取代了电子管,技术的进步,导致电子管从兴旺走向衰败,令人大有“无可奈何花落去”之感,但是由于近年来人们对电声技术的提高发现电子管放大器能够发出晶体管所不能比拟的音色,所以时至今日电子管在音频领域又迅速走红。

由于电子管是电压控制放大器件,其失真成分绝大多数均为偶次失真,这在音乐表现上刚好是倍频程谐音,故而即使用仪器实测谐波失真较大(一般在2%以上),听起来非但没有生硬刺耳的失真感,反而有一种黄玫瑰般温柔厚实、甜腻动人的韵味,特别适合于播放田园诗般舒缓优雅的古典乐和中国民乐。

尤其在表现如(高山流水)、“渔舟唱晚”,“胡笳十八拍” 、“平沙落雁”等古筝古琴的空灵、通透、饱满、飘逸上,确有一种超凡脱俗、纤尘不染,甚至靓到不食人间烟火而返朴归真的感觉。

随着现代科技的进步,电子管(特别是一些老牌子电子管厂如长沙曙光、北京、PHILIPS以及前苏联生产的优质名管)的寿命得以数倍延长,更使得听厌了冷硬、干涩的数码的老一辈发烧友对电子管那种久违了的甜润柔美倍加怀念。

加上众多生产厂家的因势利导、推波助澜,终于使这个已有大半个世纪生命的耄耋老人重振五十年代的赫赫声威!编辑本段胆机常识一、胆机与晶体机比较胆机与晶体机的比较,这里只谈以下两个问题,即性能价格比和音质特点,在一千元人民币(每台)以下的价格,因胆机无法用此价格生产,人们也不可能用此价格买到好的胆机产品,在此价格虽然能买到晶体机,但也很难买到很好的产品。

KAQW210S中文资料

Fig.8 Voltage vs. current characteristics of output at MOS FET portion Measured portion: across terminals 5,7 and 6,8 pin Ambient temperature: 25°C

Fig.9 Off state leakage current Across terminals 5,7 and 6,8 pin Ambient temperature: 25°C

(Ta=25°C)

Max.

Unit V mA mA V uA pF Ω ms ms

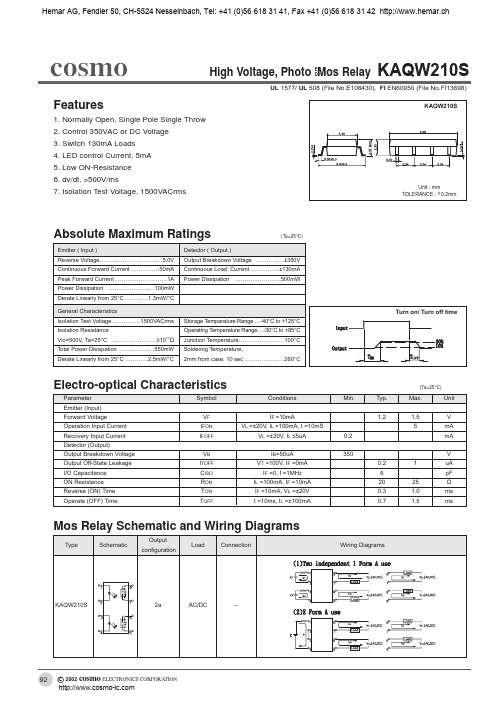

Mos Relay Schematic and Wiring Diagrams

Type Schematic Output configuration Load Connection Wiring Diagrams

KAQW210S

2a

AC/DC

–

92

c 2002 cosmo ELECTRONICS CORPORATION

Hemar AG, Fendler 50, CH-5524 元器件交易网 Nesselnbach, Tel: +41 (0)56 618 31 41, Fax +41 (0)56 618 31 42

LED Operate Current (mA)

Ambient Temperature Ta (°C)

Ambient Temperature Ta (°C)

LED Turn off Current (mA)

Tun off Time Msec

Ambient Temperature Ta (°C)

Fig.7 LED dropout voltage vs. ambient temperature LED current: 5 to 50mA

A8293

DescriptionIntended for analog and digital satellite receivers, this single low noise block converter regulator (LNBR) is a monolithic linear and switching voltage regulator, specifically designed to provide the power and the interface signals to an LNB down converter via coaxial cable. The A8293 requires few external components, with the boost switch and compensation circuitry integrated inside of the device. A high switching frequency is chosen to minimize the size of the passive filtering components, further assisting in cost reduction. The high levels of component integration ensure extremely low noise and ripple figures. The A8293 has been designed for high efficiency, utilizing the Allegro ® advanced BCD process. The integrated boost switch has been optimized to minimize both switching and static losses. To further enhance efficiency, the voltage drop across the tracking regulator has been minimized.For DiSEqC™ communications, several schemes are available for generating tone signals, all the way down to no-load, and using either the internal clock or an external time source.Features and Benefits▪ 2-wire serial I 2C™ -compatible interface: control (write) and status (read)▪ LNB voltages (7 programmable levels) compatible with all common standards▪ Tracking switch-mode power converter for lowest dissipation ▪ Integrated converter switches and current sensing ▪ Provides up to 700 mA load current▪ Static current limit circuit allows full current at startup and 13→18 V output transition; reliably starts wide load range ▪ Push-pull output stage minimizes 13→18 V and 18→13 V output transition times for highly capacitive loads▪ Adjustable rise/fall time via external timing capacitor ▪ Built-in tone oscillator, factory-trimmed to 22 kHz facilitates DiSEqC™ tone encoding, even at no-load ▪ Four methods of 22 kHz tone generation, via I 2C™ data bits and/or external pin ▪ Auxiliary modulation input ▪ LNB overcurrent with timer▪Diagnostics for output voltage level, input supply UVLOSingle LNB Supply and Control V oltage RegulatorContinued on the next page…Functional Block DiagramA8293L1Packages:20-contact, 4 × 4 mmMLP/QFN (suffix ES)28 contact, 5 × 5 mm MLP/QFN (suffix ET)Package Thermal Characteristics*Package R θJA (°C/W)PCB ES 37 (estimated)4-layer ET324-layer* Additional information is available on the Allegro website.Selection GuidePart Number Packing 1DescriptionA8293SESTR-T 27 in. reel, 1500 pieces/reel12 mm carrier tape ES package, MLP/QFN surface mount 4 mm × 4 mm × 0.75 mm nominal height A8293SETTR-T 2,37 in. reel, 1500 pieces/reel12 mm carrier tapeET package, MLP/QFN surface mount 5 mm × 5 mm × 0.90 mm nominal height1Contact Allegro for additional packing options.2Leadframe plating 100% matte tin.3This variant is in production but has been determined to be NOT FOR NEW DESIGN. This classi fi cation indicates that saleof this device is currently restricted to existing customer applications. The variant should not be purchased for new design ap-plications because obsolescence in the near future is probable. Status date change September 21, 2010.A comprehensive set of fault registers are provided, which comply with all the common standards, including: overcurrent, thermal shutdown, undervoltage, and power not good.The device uses a 2-wire bidirectional serial interface, compatible with the I 2C™ standard, that operates up to 400 kHz.The A8293 is supplied in two lead (Pb) free MLP/QFN packages: ES, 20-contact, 4 mm × 4 mm, 0.75 nominal overall height, and ET, 28-contact, 5 mm × 5 mm, 0.90 nominal overall height.Description (continued)Absolute Maximum RatingsCharacteristic SymbolConditionsRating UnitsLoad Supply Voltage, VIN pin V IN 30V Output Current*I OUTInternally Limited A Output Voltage; LNB and BOOST pins –1 to 33 V Output Voltage; LX pin –1 to 30V Output Voltage; VCP pin –1 to 41 V Logic Input Voltage, EXTM pin –0.3 to 5 V Logic Input Voltage, other pins –0.3 to 7 V Logic Output Voltage–0.3 to 7 V Operating Ambient Temperature T A –20 to 85 °C Junction Temperature T J (max) 150°C Storage TemperatureT stg –55 to 150°C*Output current rating may be limited by duty cycle, ambient temperature, and heat sinking. Under any set of conditions, do not exceed thespecified current ratings, or a junction temperature, T J , of 150°C.PAD1514131211123456789102019181716L N BG N DL XV I NN CN CG N DV R E GS D A A D D FLOAT GND NC SCL IRQBOOST VCP TCAP FLOAT EXTMTerminal List TableName Number FunctionES ET ADD 1011Address selectFLOAT 4, 155, 22These pins must not be connected to anything; do not ground these pins BOOST 11Tracking supply voltage to linear regulator EXTM 56External modulation input GND 7, 148, 19Signal ground GNDLX 1927Boost switch ground IRQ 1114Interrupt request LNB 2028Output voltage to LNB LX 1826Inductor drive point NC 6, 13, 164, 7, 13, 15-18, 20, 21, 23, 24No connectionPAD Pad PadExposed pad; connect to the ground plane, for thermal dissipation SCL 1212I 2C™-compatible clock input SDA 910I 2C™-compatible data input/outputTCAP 33Capacitor for setting the rise and fall time of the LNB output VCP 22Gate supply voltage VIN 1725Supply input voltage VREG89Analog supplyDevice Pin-out Diagram(Top View)PAD 21201918171615123456789101112131428272625242322L N BG N D L XL XV I N N C N CF L O A TG N DV R E GS D A A D D S C L N C I R Q NC NC GND NC NC NC NC BOOST VCP TCAP NC FLOAT EXTM NCES PackageET PackageELECTRICAL CHARACTERISTICS at TA= 25°C, V IN = 9 to 16 V, unless noted otherwise1Characteristics Symbol Test Conditions Min.Typ.Max.Units GeneralSet-Point Accuracy, Load and Line Regulation Err Relative to selected V LNB target level,I LOAD = 0 to 450 mA–3.0–+3.0%Supply Current I IN(Off)ENB bit = 0, LNB output disabled, V IN = 12 V––10.0mA I IN(On)ENB bit = 1, LNB output enabled,I LOAD = 0 mA, V IN = 12 V––19.0mABoost Switch On Resistance R DS(on)BOOST I LOAD = 450 mA–300–mΩSwitching Frequency f SW320352384kHz Switch Current Limit I LIMSW V IN = 9 V, V OUT = 19.0 V– 2.7–ALinear Regulator Voltage Drop∆V REG V BOOST – V LNB, no tone signal,I LOAD = 450 mA–800–mVTCAP Pin CurrentI CHG TCAP capacitor (C7) charging–12.5–10–7.5μA I DISCHG TCAP capacitor (C7) discharging7.51012.5μAOutput Voltage Rise Time2t r(VLNB)For V LNB 13 →18 V; C TCAP = 5.6 nF,I LOAD = 450 mA–500–μsOutput Voltage Pull-Down Time2t f(VLNB)For V LNB 18 →13 V; C LOAD = 100 μF,I LOAD = 0 mA–12.5–msOutput Reverse Current I RLNB ENB bit = 0, V LNB = 33 V , BOOST capacitor(C5) fully charged–15mARipple and Noise on LNB Output3V rip,n(pp)20 MHz BWL; reference circuit shown inFunctional Block diagram; contact Allegro foradditional information on application circuitboard design–30–mV PPProtection CircuitryOutput Overcurrent Limit4I LIMLNB V BOOST – V LNB = 800 mV–700800mA Overcurrent Disable Time t DIS–48–ms VIN Undervoltage Lockout Threshold V UVLO V IN falling7.057.357.65V VIN Turn On Threshold V IN(th)V IN rising7.407.708.00V Undervoltage Hysteresis V UVLOHYS–350–mV Thermal Shutdown Threshold2T J–165–°C Thermal Shutdown Hysteresis2∆T J–20–°C Power Not Good Flag Set PNG SET With respect to V LNB778593% Power Not Good Flag Reset PNG RESET With respect to V LNB829098% Power Not Good Hysteresis PNG HYS With respect to V LNB–5–% ToneTone Frequency f TONE202224kHz Tone Amplitude, Peak-to-Peak V TONE(pp)I LOAD = 0 to 450 mA, C LOAD = 750 nF400620800mVContinued on the next page…Tone Duty Cycle DC TONE I LOAD = 0 to 450 mA, C LOAD = 750 nF 405060%Tone Rise Time t rTONE I LOAD = 0 to 450 mA, C LOAD = 750 nF 51015μs Tone Fall Time t fTONE I LOAD = 0 to 450 mA, C LOAD = 750 nF51015μs EXTM Logic Input V EXTM(H) 2.0––VV EXTM(L)––0.8V EXTM Input Leakage I EXTMLKG–1–1μAI 2C™-Compatible Interface Logic Input (SDA,SCL) Low Level V SCL(L)––0.8V Logic Input (SDA,SCL) High Level V SCL(H) 2.0––V Logic Input Hysteresis V I2CIHYS –150–mV Logic Input CurrentI I2CI V I2CI = 0 to 7 V –10<±1.010μA Logic Output Voltage SDA and IRQ V t2COut(L)I LOAD = 3 mA ––0.4V Logic Output Leakage SDA and IRQ V t2CLKG V t2COut = 0 to 7 V––10μA SCL Clock Frequency f CLK ––400kHz Output Fall Timet fI2COut V t2COut(H) to V t2COut(L)––250ns Bus Free Time Between Stop/Start t BUF 1.3––μs Hold Time Start Condition t HD:STA 0.6––μs Setup Time for Start Condition t SU:STA 0.6––μs SCL Low Time t LOW 1.3––μs SCL High Time t HIGH 0.6––μs Data Setup Timet SU:DAT 100––nsData Hold Timet HD:DAT For t HD:DAT (min) , the master device must provide a hold time of at least 300 ns for the SDA signal in order to bridge the undefined region of the SCL signal falling edge 0–900ns Setup Time for Stop Condition t SU:STO 0.6––μs I 2C™ Address SettingADD Voltage for Address 0001,000Address10–0.7V ADD Voltage for Address 0001,001Address2 1.3– 1.7V ADD Voltage for Address 0001,010Address3 2.3– 2.7V ADD Voltage for Address 0001,011Address43.3–5.0V1Operation at 16 V may be limited by power loss in the linear regulator.2Guaranteed by worst case process simulations and system characterization. Not production tested.3LNB output ripple and noise are dependent on component selection and PCB layout. Refer to the Application Schematic and PCB layoutrecommendations. Not production tested.4Current from the LNB output may be limited by the choice of Boost components.ELECTRICAL CHARACTERISTICS (continued) at T A = 25°C, V IN = 9 to 16 V, unless noted otherwise 1CharacteristicsSymbol Test ConditionsMin.Typ.Max.Units I 2C™ Interface Timing DiagramHIGH LOW SDA SCLProtectionThe A8293 has a wide range of protection features and fault diag-nostics which are detailed in the Status Register section.Boost Converter/Linear RegulatorThe A8293 solution contains a tracking current-mode boost converter and linear regulator. The boost converter tracks the requested LNB voltage to within 800 mV, to minimize power dissipation. Under conditions where the input voltage, V BOOST , is greater than the output voltage, V LNB, the linear regulator must drop the differential voltage. When operating in these conditions, care must be taken to ensure that the safe operating temperature range of the A8293 is not exceeded.The boost converter operates at 352 kHz typical: 16 times the internal 22 kHz tone frequency. All the loop compensation, current sensing, and slope compensation functions are provided internally.The A8293 has internal pulse-by-pulse current limiting on the boost converter and DC current limiting on the LNB output to protect the IC against short circuits. When the LNB output is shorted, the LNB output current is limited to 700 mA typical, and the IC will be shut down if the overcurrent condition lasts for more than 48 ms. If this occurs, the A8293 must be reenabled for normal operation. The system should provide sufficient time between successive restarts to limit internal power dissipation; a minimum of 2 s is recommended.At extremely light loads, the boost converter operates in a pulse-skipping mode. Pulse skipping occurs when the BOOST voltage rises to approximately 450 mV above the BOOST target output voltage. Pulse skipping stops when the BOOST voltage drops 200 mV below the pulse skipping level.In the case that two or more set top box LNB outputs are con-nected together by the customer (e.g., with a splitter), it is pos-sible that one output could be programmed at a higher voltage than the other. This would cause a voltage on one output that is higher than its programmed voltage (e.g., 19 V on the output of a 13 V programmed voltage). The output with the highest voltage will effectively turn off the other outputs. As soon as this voltage is reduced below the value of the other outputs, the A8293 output will auto-recover to their programmed levels.Charge Pump.Generates a supply voltage above the internal tracking regulator output to drive the linear regulator control. Slew Rate Control. During either start-up, or when the output voltage at the LNB pin is transitioning, the output voltage rise and fall times can be set by the value of the capacitor connected from the TCAP pin to GND (C TCAP or C7 in the Applications Schematic). Note that during start-up, the BOOST pin is pre-charged to the input voltage minus a voltage drop. As a result, the slew rate control for the BOOST pin occurs from this voltage.The value of C TCAP can be calculated using the following for-mula:C TCAP = (I TCAP × 6) / SR ,where SR is the required slew rate of the LNB output voltage,in V/s, and I TCAP is the TCAP pin current specified in the data sheet. The recommended value for C TCAP, 10 nF, should provide satisfactory operation for most applications. However, in some cases, it may be necessary to increase the value of C TCAP to avoid activating the current limit of the LNB output. One such situa-tion is when two set-top boxes are connected in parallel. If this is the case, the following formula can be used to calculate C TCAP:C TCAP≥ (I TCAP × 6)(2 × C BOOST) / I LIMLNB ,C TCAP≥ (10 μA × 6)(2 × 100 μF) / 500 mA = 24 nF .The minimum value of C TCAP is 2.2 nF. There is no theoretical maximum value of C TCAP however too large a value will prob-ably cause the voltage transition specification to be exceeded. Tone generation is unaffected by the value of C TCAP .Pull-Down Rate Control.In applications that have to operate at very light loads and that require large load capacitances (in the order of tens to hundreds of microfarads), the output linear stage provides approximately 40 mA of pull-down capability. This ensures that the output volts are ramped from 18 V to 13 V in a reasonable amount of time.ODT (Overcurrent Disable Time)If the LNB output current exceeds 700 mA, typical, for more than 48 ms, then the LNB output will be disabled and the OCP bit will be set.Short Circuit HandlingIf the LNB output is shorted to ground, the LNB output current will be clamped to 700 mA, typical. If the short circuit condition lasts for more than 48 ms, the A8293 will be disabled and the OCP bit will be set.Auto-RestartAfter a short circuit condition occurs, the host controller should periodically reenable the A8293 to check if the short circuit hasFunctional Descriptionbeen removed. Consecutive startup attempts should allow at least 2 s of delay between restarts.In-Rush CurrentAt start-up or during an LNB reconfiguration event, a tran-sient surge current above the normal DC operating level can be provided by the A8293. This current increase can be as high as 700 mA, typical, for as long as required, up to a maximum of48 ms.Tone GenerationThe A8293 solution offers four options for tone generation, providing maximum flexibility to cover every application. The EXTM pin (external modulation), in conjunction with the I2C™ control bits: TMODE (tone modulation) and TGATE (tone gate), provide the necessary control. The TMODE bit controls whether the tone source is either internal or external (via the EXTM pin). Both the EXTM pin and TGATE bit determine the 22 kHz con-trol, whether gated or clocked.Four options for tone generation are shown in figure 1. Note that when using option 4, when EXTM stops clocking, the LNB volts park at the LNB voltage, either plus or minus half the tone signal amplitude, depending on the state of EXTM. For example, if the EXTM is held low, the LNB DC voltage is the LNB pro-grammed voltage minus 325 mV (typical).EXTM TMODE TGATE ToneEXTM TMODETGATE ToneEXTM TMODE TGATE ToneEXTM TMODE TGATE ToneOption 1 – Use internal tone, gated by the TGATE bit. Option 2 – Use internal tone, gated by the EXTM pin. Option 3 – Use external tone, gated by the TGATE bit. Figure 1. Options for tone generationI 2C™-Compatible InterfaceThis is a serial interface that uses two bus lines, SCL and SDA,to access the internal Control and Status registers of the A8293.Data is exchanged between a microcontroller (master) and theA8293 (slave). The clock input to SCL is generated by the master,while SDA functions as either an input or an open drain output,depending on the direction of the data.Timing ConsiderationsThe control sequence of the communication through the I 2C™-compatible interface is composed of several steps in sequence: 1. Start Condition. Defined by a negative edge on the SDA line,while SCL is high.2. Address Cycle. 7 bits of address, plus 1 bit to indicate read (1)or write (0), and an acknowledge bit. The first five bits of the address are fixed as: 00010. The four optional addresses, de-fined by the remaining two bits, are selected by the ADD input. The address is transmitted MSB first.3. Data Cycles. Write – 6 bits of data and 2 bits for addressing four internal control registers, followed by an acknowledge bit. See Control Register section for more information. Read – Two status registers, where register 1 is read first, followed by register 2, then register 1, and so on. At the start of any read sequence, register 1 is always read first. Data is transmitted MSB first.4. Stop Condition. Defined by a positive edge on the SDA line,while SCL is high. Except to indicate a Start or Stop condi-tion, SDA must be stable while the clock is high. SDA canonly be changed while SCL is low. It is possible for the Start or Stop condition to occur at any time during a data transfer. The A8293 always responds by resetting the data transfer sequence. The Read/Write bit is used to determine the data transfer direc-tion. If the Read/Write bit is high, the master reads the contents of 1 2 3 4 5 6 7 8 9SCL1 2 3 4 5 6 7 8 9SCL1 2 3 4 5 6 7 8 9SCL Write to RegisterRead One Byte from RegisterRead Multiple Bytes from RegisterFigure 2. I 2C™ Interface. Read and write sequences.register 1, followed by register 2 if a further read is performed. If the Read/Write bit is low, the master writes data to one of the two Control registers. Note that multiple writes are not permitted. All write operations must be preceded with the address.The Acknowledge bit has two functions. It is used by the mas-ter to determine if the slave device is responding to its address and data, and it is used by the slave when the master is reading data back from the slave. When the A8293 decodes the 7-bit ad-dress field as a valid address, it responds by pulling SDA low during the ninth clock cycle.During a data write from the master, the A8293 also pulls SDA low during the clock cycle that follows the data byte, in order to indicate that the data has been successfully received. In both cas-es, the master device must release the SDA line before the ninth clock cycle, in order to allow this handshaking to occur.During a data read, the A8293 acknowledges the address in the same way as in the data write sequence, and then retains control of the SDA line and send the data from register 1 to the master. On completion of the eight data bits, the A8293 releases the SDA line before the ninth clock cycle, in order to allow the master to acknowledge the data. If the master holds the SDA line low dur-ing this Acknowledge bit, the A8293 responds by sending the data from register 2 to the master. Data bytes continue to be sent to the master until the master releases the SDA line during the Acknowledge bit. When this is detected, the A8293 stops sending data and waits for a stop signal. Interrupt RequestThe A8293 also provides an interrupt request pin, IRQ, which is an open-drain, active-low output. This output may be connect-ed to a common IRQ line with a suitable external pull-up and can be used with other I 2C™-compatible devices to request attention from the master controller.The IRQ output becomes active when either the A8293 first recognizes a fault condition, or at power-on, when the main sup-ply, V IN , and the internal logic supply, V REG , reach the correct operating conditions. It is only reset to inactive when the I 2C™ master addresses the A8293 with the Read/Write bit set (caus-ing a read). Fault conditions are indicated by the TSD, VUV , and OCP bits, and are latched in the Status register. See the Status register section for full description.The DIS and PNG status bits do not cause an interrupt. The PNG bit is continually updated, apart from the DIS bit, which changes when the LNB is either disabled, faulted, or is enabled. When the master recognizes an interrupt, it addresses allslaves connected to the interrupt line in sequence, and then reads the status register to determine which device is requesting atten-tion. The A8293 latches all conditions in the Status register until the completion of the data read. The action at the resampling point is further defined in the Status Register section. The bits in the Status register are defined such that the all-zero condition in-dicates that the A8293 is fully active with no fault conditions. When V IN is initially applied, the I 2C™-compatible interface does not respond to any requests until the internal logic supply V REG has reached its operating level. Once V REG has reached this point, the IRQ output goes active, and the VUV bit is set. After the A8293 acknowledges the address, the IRQ flag is reset. After the master reads the status registers, the registers are updated with the VUV reset.Status Register 1Address Start R Stop1 2 3 4 5 6 7 8 9SCL IRQFaultEventReloadStatus RegisterRead after InterruptFigure 3. I 2C™ Interface. Read sequences after interrupt request.Control Registers (I2C™-Compatible Write Register) All main functions of the A8293 are controlled through the I2C™-compatible interface via the 8-bit Control registers. As the A8293 contains numerous control options, it is necessary to have two control registers. Each register contains up to 6 bits of data (bit 0 to bit 5), followed by 2 bits for the register address (bit 6 and bit 7). The power-up states for the control functions are all 0s.The following tables define the control bits for each address and the settings for output voltage:Table 1. Control Register Address (I1, I0) = 00 Bit Name Function0VSEL0See table 3, Output Voltage Amplitude Selection 1VSEL12VSEL23VSEL30: LNB = Low range1: LNB = High range4ODT 1 (recommended): The ODT functions are always enabled, but setting 1 recommended at all times.5ENB0: Disable LNB Output1: Enable LNB Output6I0Address Bit: 07I1Address Bit: 0Bit 0 VSEL0 These three bits provide incremental control over the voltage on the LNB output.Bit 1 VSEL1 The available voltages provide the necessary levels for all the common standards Bit 2 VSEL2 plus the ability to add line compensation in increments of 333 mV. The voltage levels are defined in table 3, Output V oltage Amplitude Selection.Bit 3 VSEL3 Switches between the low level and high level output voltages on the LNB output.0 selects the low level voltage and 1 selects the high level. The low-level center voltageis 12.709 V nominal and the high level is 18.042 V nominal. These may be increasedin steps of 333 mV using the VSEL2, VSEL1 and VSEL0 control register bits.Bit 4 ODT The overcurrent disable timer is always enabled.Bit 5 ENB Enables the LNB output. When set to 1 the LNB output is switched on. When set to 0, the LNB output is disabled.Bit 6 I0 AddressBit 7 I1 AddressTable 2. Control Register Address (I1, I0) = 10 and 11Bit Name Function0: External Tone0TMODE1: Internal Tone0: Tone Gated Off1TGATE1: Tone Gated On2-Not Used (0 recommended)3-Not Used4-Not Used5-Not Used6I0Address Bit: 07I1Address Bit: 1Bit 0 TMODE Tone Mode. Selects between the use of an external 22 kHz logic signal or the use of the internal 22 kHz oscillator to control the tone generation on the LNB output. A 0selects the external tone and a 1 selects the internal tone. See the Tone Generationsection for more informationBit 1 TGATE Tone Gate. Allows either the internal or external 22 kHz tone signals to be gated, unless the EXTM is selected for gating. When set to 0, the selected tone (viaTMODE) is off. When set to 1, the selected tone is on. See Tone Generation Sectionfor more information.Bit 2 – Not Used.Bit 3 – Not Used.Bit 4 – Not Used.Bit 5 – Not Used.Bit 6 I0 Address.Bit 7 I1 Address.Table 3. Output Voltage Amplitude Selection VSEL3VSEL2VSEL1VSEL0LNB (V) 000012.709 000113.042 001013.375 010014.042 100018.042 101018.709 101119.042Status Registers (I2C™-Compatible Read Register)The main fault conditions: overcurrent (OCP), undervoltage (VUV) and overtemperature (TSD), are all indicated by setting the relevant bits in the Status registers. In all fault cases, once the bit is set, it remains latched until the A8293 is read by the I2C™ master, assuming the fault has been resolved.The current status of the LNB output is indicated by the dis-able bit, DIS. The DIS bit is set when either a fault occurs or if the LNB is disabled intentionally. This bit is latched, and is reset when the LNB is commanded on again. The power not good (PNG) is the only bit which may be reset without an I2C™ read sequence. Table 4 summarizes the condition of each bit when set and how it is reset.As the A8293 has a comprehensive set of status reporting bits, it is necessary to have two Status registers. When performing a multiple read function, register 1 is read followed by register 2, then register 1 again and so on. Whenever a new read function is performed, register 1 is always read first.The normal sequence of the master in a fault condition will be to detect the fault by reading the Status registers, then rereading the Status registers until the status bit is reset indicating the fault condition is reset. The fault may be detected either by continuously polling, by responding to an interrupt request (IRQ), or by detect-ing a fault condition externally and performing a diagnostic poll of all slave devices. Note that the fully-operational condition of the Status registers is all 0s, to simplify checking of the Status bit.Table 4. Status Register Bit SettingStatus Bit Function SetReset Condition–Not used–Not usedDIS LNB disabled, either intentionally ordue to faultLatched LNB enabled and no faultOCP Overcurrent Latched I2C™ read and fault removed PNG Power not good Non-latched LNB volts in range–Not used–Not usedTSD Thermal shutdown Latched I2C™ read and fault removed VUV Undervoltage Latched I2C™ read and fault removedTable 5. Status Register 1Bit Name Function0DIS LNB output disabled1–Not Used2OCP Overcurrent3–Not Used4PNG Power Not Good5–Not Used6TSD Thermal Shutdown7VUV V IN UndervoltageBit 0 DIS LNB Output Disabled. DIS is used to indicate the current condition of the LNB output. At power-on, or if a fault condition occurs, DIS will be set. This bit changingto 1 does not cause the IRQ to activate because the LNB output may be disabled in-tentionally by the I2C™ master. This bit will be reset at the end of a write sequenceif the LNB output is enabled.Bit 1 – Not used.Bit 2 OCP Overcurrent. If the LNB output detects an overcurrent condition, for greater than48 ms, the LNB output will be disabled. The OCP bit will be set to indicate that anovercurrent has occurred and the disable bit, DIS, will be set. The Status register isupdated on the rising edge of the 9th clock pulse in the data read sequence, where theOCP bit is reset in all cases, allowing the master to reenable the LNB output.If the overcurrent timer is not enabled, the device operate in current limit indefinitelyand the OCP bit will be set. If the overcurrent condition is removed, the OCP bit willautomatically be reset. Note that if the overcurrent operates long enough, and a ther-mal shutdown occurs, the LNB output will be disabled and the TSD bit will be set.Bit 3 – Not used.Bit 4 PNG Power Not Good. Set to 1 when the LNB output is enabled and the LNB voltage is below 85% of the programmed voltage. The PNG is reset when the LNB volts arewithin 90% of the programmed LNB voltage.Bit 5 – Not used.Bit 6 TSD Thermal Shutdown. 1 indicates that the A8293 has detected an overtemperature condition and has disabled the LNB output. The disable bit, DIS, will also be set.The status of the overtemperature condition is sampled on the rising edge of the 9thclock pulse in the data read sequence. If the condition is no longer present, then theTSD bit will be reset, allowing the master to reenable the LNB output if required. Ifthe condition is still present, then the TSD bit will remain at 1.Bit 7 VUV Undervoltage Lockout. 1 indicates that the A8293 has detected that the input sup-ply, V IN is, or has been, below the minimum level and an undervoltage lockout hasoccurred disabling the LNB outputs. The disable bit, DIS, will also be set and theA8293 will not reenable the output until so instructed by writing the relevant bit intothe control registers. The status of the undervoltage condition is sampled on the risingedge of the 9th clock pulse in the data read sequence. If the condition is no longerpresent, then the VUV bit will be reset allowing the master to reenable the LNB out-put if required. If the condition is still present, then the VUV bit will remain at 1.。

七年级英语(上册)Unit1语法+知识点汇总

Unit 1 My name’s Gina.语法专项:形容词性物主代词教材典句1. W hat ’ s his name ? 他叫什么名字?— His name ’s Eric . 他的名字叫埃里克。

2.What’s her name ? 她叫什么名字?—She’s Mary . 她叫玛丽。

3. What’s your telephone number , Li Xin ? 李欣,你的电话号码是什么?以上句子中分别含有形容词性物主代词his , her, your, 今天我们就来学习一下形容词性物主代词的用法。

语法全解物主代词是表示所有关系的代词,是人称代词的属格形式。

它分第一人称、第二人称和第三人称,每个人称又分单数和复数。

物主代词可分为形容词性物主代词和名词性物主代词。

本单元主要涉及形容词性物主代词。

第一人称第二人称第三人称单数复数单数复数单数复数形容词 Our Our Your Your His Her Its Their 性物主我的我们的你的你们的他的她的它的他、她、代词它们的形容词性物主代词的用法与形容词的用法相似,可以修饰名词,一般放在被修饰的名词之前,不能单独使用。

如果名词前面还有其他的定语,物主代词要放在其他定语的前面。

my pen 我的钢笔my red pen 我的红色钢笔your name 你的名字his mother 他的母亲练一练:① . Please send ________ best wishes to Mary . A. IB. meC. myD. mine ②. __Does Miss White like sports ?__ Yes, _________ favorite sport is tennis . A. he_____ pen .A. red myB. he redC. red hisD. herred④. __ I ’m Linda. What ’s your name ? _________ name is Lucy .A. IB. MeC. MyD. Mine4.介绍自己:(1)My name’s+名字我的名字叫......( 2) I ’ m+名字我是......5. 询问姓名(1)What ’s your name? 你叫什么名字?----Alan. 艾伦。

SG2813中文资料

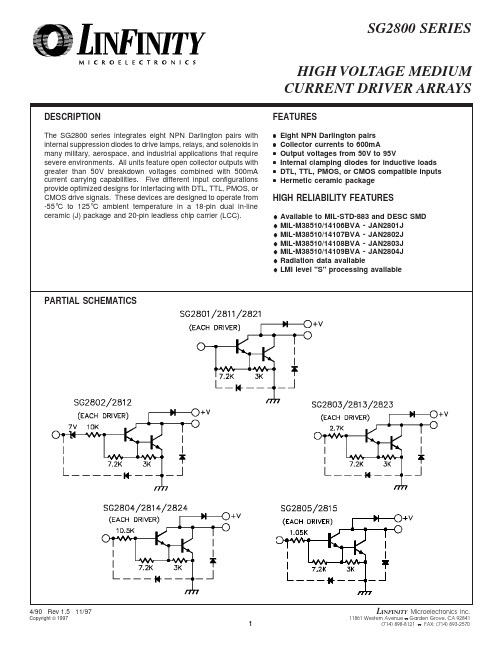

DESCRIPTIONThe SG2800 series integrates eight NPN Darlington pairs with internal suppression diodes to drive lamps, relays, and solenoids in many military, aerospace, and industrial applications that require severe environments. All units feature open collector outputs with greater than 50V breakdown voltages combined with 500mA current carrying capabilities. Five different input configurations provide optimized designs for interfacing with DTL, TTL, PMOS, or CMOS drive signals. These devices are designed to operate from -55°C to 125°C ambient temperature in a 18-pin dual in-line ceramic (J) package and 20-pin leadless chip carrier (LCC).FEATURES•Eight NPN Darlington pairs•Collector currents to 600mA•Output voltages from 50V to 95V•Internal clamping diodes for inductive loads •DTL, TTL, PMOS, or CMOS compatible inputs •Hermetic ceramic packageHIGH RELIABILITY FEATURES♦Available to MIL-STD-883 and DESC SMD♦MIL-M38510/14106BVA - JAN2801J♦MIL-M38510/14107BVA - JAN2802J♦MIL-M38510/14108BVA - JAN2803J♦MIL-M38510/14109BVA - JAN2804J♦Radiation data available♦LMI level "S" processing availableHIGH VOLTAGE MEDIUM CURRENT DRIVER ARRAYSPARTIAL SCHEMATICSABSOLUTE MAXIMUM RATINGS (Note 1)Continuous Collector Current, I C(SG2800, 2820) ......................................................(SG2810) ...............................................................Operating Junction TemperatureHermetic (J, L Packages) .........................................Plastic (N Package) ..................................................Storage Temperature Range ..........................Lead Temperature (Soldering 10 sec.) .........................Output Voltage, V CE(SG2800, 2810 series) ................................................(SG2820 series) ..........................................................Input Voltage, V IN(SG2802,3,4 series) ....................................................Continuous Input Current, I IN ........................................50V 95V 30V 25mA500mA 600mA 150°C 150°C -65°C to 150°C 300°CNote 1. Values beyond which damage may occur.J Package:Thermal Resistance-Junction to Case , θJC .................. 25°C/W Thermal Resistance-Junction to Ambient , θJA ...............70°C/W N Package:Thermal Resistance-Junction to Case , θJC .................. 30°C/W Thermal Resistance-Junction to Ambient , θJA .............. 60°C/W L Package:Thermal Resistance-Junction to Case , θJC .................. 35°C/W Thermal Resistance-Junction to Ambient , θJA .............120°C/WTHERMAL DATANote A.Junction Temperature Calculation: T J = T A + (P D x θJA ).Note B.The above numbers for θJC are maximums for the limitingthermal resistance of the package in a standard mount-ing configuration. The θJA numbers are meant to be guidelines for the thermal performance of the device/pc-board system. All of the above assume no ambient airflow.Output Voltage, V CESG2800, SG2820 series ..............................................SG2810 series .............................................................50V 95VPeak Collector Current, I CSG2800, SG2820 series .........................................SG2810 series ........................................................Operating Ambient Temperature Range ........350mA 500mA -55°C to 125°CNote 2. Range over which the device is functional.RECOMMENDED OPERATING CONDITIONS (Note 2)SELECTION GUIDEDevice V CE Max I C Max Logic Inputs SG280150V 500mA General Purpose PMOS, CMOS SG280250V 500mA 14V-25V PMOS SG280350V 500mA 5V TTL, CMOSSG280450V 500mA 6V-15V CMOS, PMOS SG281150V 600mA General Purpose PMOS, CMOS SG281250V600mA14V-25V PMOSDevice V CE Max I C Max Logic Inputs SG281350V 600mA 5V TTL, CMOSSG281450V 600mA 6V-15V CMOS, PMOS SG281550V 600mA High Output TTL SG282195V 500mA General Purpose PMOS, CMOS SG282395V 500mA 5V TTL, CMOSSG282495V500mA6V-15V CMOS, PMOSCHARACTERISTIC CURVESFIGURE 4.INPUT CHARACTERISTICS - SG2802FIGURE 5.INPUT CHARACTERISTICS - SG2803FIGURE 6.INPUT CHARACTERISTICS - SG2804FIGURE 7.PEAK COLLECTOR CURRENT VS. DUTY CYCLEFIGURE 1.OUTPUT CHARACTERISTICS FIGURE 2.OUTPUT CURRENT VS. INPUT VOLTAGE FIGURE 3.OUTPUT CURRENT VS. INPUT CURRENTNote 1. Contact factory for JAN and DESC product availability.2. All parts are viewed from the top.3. See Selection Guide for specific device types.CONNECTION DIAGRAMS & ORDERING INFORMATION (See Notes Below)AmbientTemperature Range Part No. (Note 3)PackageConnection Diagram18-PIN CERAMIC DIP J - PACKAGESG28XXJ/883B -55°C to 125°C JAN2801J -55°C to 125°C JAN2802J -55°C to 125°C JAN2803J -55°C to 125°C JAN2804J-55°C to 125°C SG2803J/DESC -55°C to 125°C SG2821J/DESC -55°C to 125°C SG2823J/DESC -55°C to 125°C SG2824J/DESC -55°C to 125°C SG28XXJ-55°C to 125°C18-PIN PLASTIC DIP N- PACKAGESG2803N 0°C to 70°C SG2823N 0°C to 70°C 20-PIN CERAMICLEADLESS CHIP CARRIER L- PACKAGESG28XXL/883B -55°C to 125°C SG2803L/DESC -55°C to 125°C SG2821L/DESC -55°C to 125°C SG2823L/DESC -55°C to 125°C SG2824L/DESC -55°C to 125°C SG28XXL-55°C to 125°C1849319201214151716876513121110176543281110121314151716918。

aax (mmbta42)晶体管 技术参数

AAX (MMBTA42) 晶体管技术参数摘要:AAX (MMBTA42) 是一种常用的 NPN 型晶体管,它具有优良的性能和稳定性,广泛应用于各种电子设备中。

本文将对 AAX (MMBTA42) 晶体管的技术参数进行详细介绍,包括其主要特性、电气参数、尺寸和封装形式等方面的内容。

通过对这些技术参数的了解,可以更好地应用和选用 AAX (MMBTA42) 晶体管,为电子设备的设计和制造提供可靠的技术支持。

一、主要特性AAX (MMBTA42) 晶体管具有以下主要特性:1. 高频率响应:AAX (MMBTA42) 晶体管具有出色的高频率响应特性,适用于高频放大和振荡电路。

2. 低噪声系数:AAX (MMBTA42) 晶体管的噪声系数较低,可以有效减小信号的干扰和失真。

3. 高电流增益:AAX (MMBTA42) 晶体管具有较高的电流增益,适用于需要较大信号放大的电路设计。

4. 低饱和电压:AAX (MMBTA42) 晶体管的饱和电压较低,可以减小功耗和提高电路效率。

二、电气参数AAX (MMBTA42) 晶体管的典型电气参数如下:1. 最大耐压:AAX (MMBTA42) 晶体管的最大耐压为 75V,可以满足大多数电子设备的工作电压要求。

2. 最大电流:AAX (MMBTA42) 晶体管的最大连续电流为 500mA,最大脉冲电流为 1A,能够满足电路的大电流要求。

3. 最大功率:AAX (MMBTA42) 晶体管的最大功率为 625mW,在一定的散热条件下可以实现可靠的工作。

4. 管脚电阻:AAX (MMBTA42) 晶体管的管脚电阻较小,有利于降低传输线的损耗和提高电路的稳定性。

三、尺寸和封装形式AAX (MMBTA42) 晶体管的尺寸和封装形式如下:1. 封装类型:AAX (MMBTA42) 晶体管常见的封装类型为 SOT-23,便于在电路板上进行焊接和安装。

2. 外形尺寸:AAX (MMBTA42) 晶体管的外形尺寸为 2.9mm x1.3mm x 1.1mm,适合于紧凑型电子设备的设计和布局。

8288简介

1.6 8288总线控制器在MN//MX信号为低电平的系统状态下,为了译出/S0,/S1和/S2状态线,必须使用8288总线控制器,用以产生系统总线信号。

为了将几个微处理器接到一组系统总线上,或者为了给一个8086提供几组系统总线,也可使用8288总线控制器。

8288总线控制器的基本作用是译出/S0,/S1和/S2三个状态信号的意义但这些功能用个简单的3-8译码器即可完成。

8288除此之外还有下列功能:(1)8288能产生系统总线或仅有I/O装置的总线的控制信号。

(2)可浮空系统总线信号,以允许直接存储器访问,或仲裁总线优先权。

(3)两根写控制线提供备用的先行控制输出是专为慢速存储器或I/O装置而设计的。

(4)可以封装控制信号,作为多总线或多微理器结构中实行存储器保护逻辑的一种方法。

(5)产生线路驱动器所需的信号。

(6)产生简单或复合中断逻辑所需的控制信号。

8288总线控制器是利用双极工艺制作的,为20引脚的双列直插封装,所有信号为TTL 电平兼容。

1.6.1 8288总线控制器信号与引脚分配图1.56示出了8288的信号与引脚分配。

从前面已介绍过的8086的读写总线周期的时序可知读写控制信号出现低脉冲要比写控制信号提前约一个时钟周期。

8288产生两个备用写控制信号,其时序与读控制信号相同。

这些备用写控制信号被称为先行写控制信号,因为它们要比标准的写控制信号提前一个时钟周期出现低电平。

所以,8288系统总线控制信号可概括如下:/MRDC是存储器读控制信号。

/MWTC是存储器写控制信号。

/AMWC是存储器写控制信号,其时序与MRDC一致。

/INTA是存储器读控制信号,它在两个中断响应总线周期期间输出。

/IORC是I/O装置读控制信号。

/IOWC是I/O装置写控制信号。

/AIOWC是备用I/O装置写控制信号,其时序与/IORC一致。

连接在总线上的装置大致都用/IOWC和/MWTC,或者用/AIOWC和/AMWC,但不会四种信号都用。

流通领域现代供应链体系建设试点项目申报材料

附件1杭州市流通领域现代供应链体系建设试点项目申报材料(封面)供应链名称:建设方向:申报单位(公章):项目地址:项目负责人:联系电话:(请务必填写手机)传真:电子邮箱:- 1 -附件2供应链基本情况表- 2 -附件3企业申报表填报单位(公章)单位:万元- 3 -- 4 -附件4供应链项目建设绩效目标表承担单位(盖章):(年度季度)- 5 -- 6 -- 7 -- 8 -附件5项目实施方案编写提纲一、试点单位基本情况(一)企业注册资本、上年度年营业收入及纳税情况、所属行业、在该行业中的地位及排名,企业的优势和亮点。

(二)现有物流设施、设备、托盘、包装等情况(含标准、非标)。

(三)供应链体系建设情况(四)企业建立标准体系情况(设施标准、管理标准、技术标准、服务标准)。

(五)上年企业经营收支情况,物流成本占比等。

二、总体思路与目标(一)总体思路例如:从物流基础设施建设,发挥物流基础性、先导性作用,加强公共服务性强的物流基础设施建设,完善城乡高效配送体系,推动物流企业向供应链服务商转型。

(二)总体目标围绕试点文件提出的指标和绩效评价指标,结合企业自身情况提出项目建设目标。

三、建设内容根据试点文件的支持范围,提出企业的建设内容,突出供- 9 -应链创新与应用,突出在供应链中的作用与效果。

四、进度安排(一)前期准备阶段(二)组织实施阶段(三)评估验收阶段五、投资预算(一)总投资预算明细(二)年度资金使用计划(三)资金筹措与分配方案(四)财务分析六、实施保障(一)资金保障总投资、资金筹措渠道及分类预算。

(二)组织和人员保障1.成立专门组织机构,项目负责人简历、业绩,项目拟投入的人员情况。

2.自主开发、研发平台(系统)的,需附研发人员名单(学历、专业、职务、合同岗位)(三)制度保障试点项目承担单位及联合体各方任务分工。

(四)基础设施保障七、项目正式运营后产生的经济效益和社会效益分析- 10 -经济效益,行业影响,社会影响效果分析等(尽可能用数字描述)。

HSMS-2823中文资料

Package Lead Code Identification

SINGLE 3

TOP VIEW

SERIES 3

COMMON ANODE 3

12 #0

UNCONNECTED PAIR

34

12 #2

RING QUAD 34

12 #3

BRIDGE QUAD 34

12 #5

12 #7

12 #8

COMMON CATHODE

Surface Mount RF Schottky Barrier Diodes

Technical Data

HSMS-28XX Series

Features

• Surface Mount SOT-23/SOT143 Package

• Low Turn-On Voltage (As Low as 0.34 V at 1 mA)

Note that HP’s manufacturing techniques assure that dice found in pairs and quads are taken from adjacent sites on the wafer, assuring the highest degree of match.

∆VF - FORWARD VOLTAGE DIFFERENCE (mV) IF - FORWARD CURRENT (mA)

30

30

30

30

10

85°C

1

55°C

25°C

–5°C 0.1

–35°C

0.01 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9

VF - FORWARD VOLTAGE (V)

8286介绍

March 1997

CMOS Octal Bus Transceiver

Features

Description

• Full Eight Bit Bi-Directional Bus Interface

• Industry Standard 8286 Compatible Pinout

• High Drive Capability - B Side IOL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20mA - A Side IOL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12mA

(EQ. 2)

A6

B6

where tR = 20ns, VCC = 5.0V, CL = 300pF on each eight out-

puts.

A7

B7

I = (80 × 300 × 10–12) × (5.0V × 0.8) ⁄ (20 × 10–9)

(EQ. 3)

= 480mA

OE T

Gated Inputs

The Intersil 82C8X series of bus drivers eliminates these conditions by turning off data inputs when data is latched (STB = logic zero for the 82C82/83H) and when the device is disabled (OE = logic one for the 82C86H/87H). These gated inputs disconnect the input circuitry from the VCC and ground power supply pins by turning off the upper P-channel and lower N-channel (See Figures 1 and 2). No current flow from VCC to GND occurs during input transitions and invalid logic states from floating inputs are not transmitted. The next stage is held to a valid logic level internal to the device.

七年级英语上册Unit 1语法+知识点

Unit?1??My?name’s?Gina.?语法专项:形容词性物主代词?教材典句?1.?W?hat’s?his?name???他叫什么名字??—His?name’s?Eric?.?他的名字叫埃里克。

?2.?What’s?her?name???她叫什么名字??—She’s?Mary?.?她叫玛丽。

?3.?What’s?your?telephone?number?,?Li?Xin???李欣,你的电话号码是什么??不能??③.?This?is?________?pen?.?A.?red?my????B.?he?red?????C.?red?his?????D.?her?red??④.?__?I’m?Linda.?What’s?your?name???_________?name?is?Lucy?.?A.?I??????B.?Me??????C.?My???????D.?Mine??4.?介绍自己:??(1)My?name’s+名字???我的名字叫......??(2)I’m+名字?????我是......?5.?询问姓名???(1)What’s?your?name??你叫什么名字??----Alan.艾伦。

/?My?name’s?Alan.我的名字叫艾伦。

?/??I’m?Alan.?我叫艾伦。

?What’s?=?What?is??name’s?=?name?is??I’m?=?I?am?(2)What’s?his?name???他叫什么名字?His?name’s?Eric?他的名字叫埃里克。

/??He’s?Eric?.??他叫埃里克。

??(?He’s?=?He?is?)?(3)What’s?her?name?她叫什么名字????????Her?name’s?Mary.??她的名字叫玛丽。

/?She’s?Mary.??她叫玛丽。

?????(?She’s?=?She?is?)⑴.?“t?。

当问①10岁)。

FOXBORO I A Series HARDWARE产品规格说明书

FOXBORO ®The FBM214 HART ® Communication Input Interface Module provides eight input channels, each accepting a 4 to 20mA analog signal or a digital HART signal superimposed on a 4 to 20 mA analog input signal.FEATURESKey features of the FBM214 module are:Eight analog input channels, each accepting oneof the following inputs:•Standard 4 to 20 mA analog sensor signal •Digital HART Frequency Shift Keying (FSK) signal superimposed on a 4 to 20 mA analog input signal.FSK modem dedicated to each input channel forbi-directional digital communications with a HART field deviceAnalog to digital conversion of each of the 4to20mA input signals from the HART devicesSupport for the HART universal commandsnecessary to interface the field device with the I/A Series ® system databaseGalvanic isolation of the group of 8 inputchannels from ground and module logicCompact, rugged design suitable for enclosure inClass G3 (harsh) environmentsHigh accuracy achieved by sigma-delta dataconversions for each channelTermination Assemblies (TAs) for locally orremotely connecting field wiring to the FBM214Termination Assemblies for per channel internallyand/or externally loop powered transmitters.PSS 21H-2Z14 B4 Page 2OVERVIEWThe FBM214 HART Communication Input Interface Module contains eight 4to20mA group isolated analog input channels. The FBM214 supports any mix of standard 4to20mA devices and HART devices.The FBM214 serves as a HART communications field device host, enabling the I/A Series system to request and receive two digital messages per second from the field device. The message pass-through capability can be used to support HART universal, common practice, and device-specific commands, but not the burst communication mode. These commands are implemented using the Intelligent Field Device Configurator (IFDC — refer toPSS 21S-8A3 B3 for details).The FBM214 provides a common isolated power supply to power all eight channels. Optionally, the channels can be powered by an external power supply. However, when a common external power supply is used with two or more channels, a Cable Balun module is required to prevent channel cross talk.COMPACT DESIGNThe FBM214 has a compact design, with a rugged extruded aluminum exterior for physical protection of the circuits. Enclosures specially designed for mounting the FBMs provide various levels of environmental protection, up to harsh environments per ISA Standard S71.04.HIGH ACCURACYFor high accuracy, the module incorporates a Sigma-Delta converter which can provide new analog input values for each channel every 100 milliseconds.VISUAL INDICATORSLight-emitting diodes (LEDs) incorporated into the front of the module provide visual indication of the module’s operational status, and communication activity on the channels.EASY REMOVAL/REPLACEMENTThe module can be removed/replaced without removing field device termination cabling, power, or communications cabling.FIELDBUS COMMUNICATIONA Fieldbus Communication Module or a Control Processor interfaces the redundant 2 Mbps module Fieldbus used by the FBMs. The FBM214 module accepts communication from either path (A or B) of the redundant 2 Mbps fieldbus – should one path fail or be switched at the system level, the module continues communication over the active path.The use of an external power supply common to two or more loops requires a Cable Balun Module to maintain communication signal line balance.MODULAR BASEPLATE MOUNTINGThe module mounts on a modular baseplate which accommodates up to four or eight FBMs. The modular baseplate is either DIN rail mounted or rack mounted, and includes signal connectors for redundant fieldbus, redundant independent dc power, and termination cables.TERMINATION ASSEMBLIESField input signals connect to the FBM subsystem via DIN rail mounted TAs. The TAs used with theFBM214 are described in “TERMINATION ASSEMBLIES AND CABLES” on page8.PSS 21H-2Z14 B4Page 3CABLE BALUN MODULEThe Cable Balun module is used to maintain digital communication line balance for HART Transmitter to FBM loops that are powered from a common external power supply. This powering effectively connects one line of each loop together. Without the Baluns, in each loop so powered, the common connection at the external power supply, would cause near end crosstalk at the system end of the loop wiring cable. Loops using FBM internal power source do not require Baluns.The Cable Balun module contains multiple Baluns. One Balun segment is interconnected in each loop powered from an external power supply per the diagram above. There is one Cable Balun module.Figure 1. Cable Balun Module Cable Balun ModuleModule Model ModulePart No.No. of Balunsin the ModuleCBM-4P0903SV4PSS 21H-2Z14 B4Page 4FUNCTIONAL SPECIFICATIONSField Device ChannelsVERSION SUPPORTEDHART Protocol v6INTERFACE8 group-isolated channelsCOMMUNICATION TO THE DEVICEPoint-to-point, master/slave, asynchronous, half-duplex, at 1200 baud.ERROR CHECKINGParity on each byte, and one CRC check byte.SPEED2 messages per secondFASTEST ALLOWED ECB BLOCK PERIOD500 msecMAXIMUM DISTANCE (FBM214 TO FIELDDEVICE)Meets HART FSK physical layer specificationHCF_SPEC-54, Revision 8.1 [up to 3030 m(10000ft)](1).COMPLIANCE VOLTAGE18 V dc minimum at 20.5 mACURRENT INPUTSSense Resistor61.9 Ω nominalTotal Input Resistance280 Ω minimumAccuracy (Includes Nonlinearity)±0.03% of full scaleTemperature Coefficient50 ppm/ºCResolution15 bitsUpdate Rate100 msIntegration Time500 msCommon Mode Rejection>100 db at 50 or 60 HzNormal Mode Rejection>35 db at 50 or 60 HzMAXIMUM LOOP RESISTANCE280 Ω (not including the field device)(2)LOOP POWER SUPPLY PROTECTIONEach channel is galvanically group isolated,current limited and voltage regulated. All inputsare limited by their design to less than 30 mA. Ifthe current limit circuit shorts out, the current islimited to about 85 mA.FBM INPUT IMPEDANCE280 Ω minimumFBM INTERNAL POWER FOR FIELD DEVICE24 V dc ±10% common power supply for allchannels. Loop load limited to one device perchannel.ISOLATIONThe channels are not galvanically isolated fromeach other, but are galvanically isolated (bothoptical and transformer isolation) as a group from ground and module logic. Inputs use an internal FBM isolated power supply for field power. Themodule withstands, without damage, a potential of 600 V ac applied for one minute between the group-isolated channels and earth (ground).CAUTIONThis does not imply that these channels areintended for permanent connection tovoltages of these levels. Exceeding the limitsfor input voltages, as stated elsewhere in thisspecification, violates electrical safety codesand may expose users to electric shock. Fieldbus CommunicationCommunicates with its associated FCM or FCP via the redundant 2 Mbps module FieldbusHEAT DISSIPATION4 W (maximum)(1)The maximum allowable distance decreases when the loop is operated through an intrinsic safety barrier. The maximum distance ofthe field device from the FBM is a function of compliance voltage, wire gauge and voltage drop at the device.(2)In an intrinsic safety application, if a zener barrier is used between the FBM and the field device, the power supply must be set at24V dc +5%, -1%. There are no specific constraints with the use of galvanic barriers.PSS 21H-2Z14 B4Page 5 FUNCTIONAL SPECIFICATIONS (CONTINUED)Power RequirementsINPUT VOLTAGE RANGE (REDUNDANT)24V dc ±5%CONSUMPTION7 W (maximum)Regulatory ComplianceELECTROMAGNETIC COMPATIBILITY (EMC) European EMC Directive 89/336/EECMeets:EN 50081-2 Emission standardEN 50082-2 Immunity standardEN 61326 Annex A (Industrial Levels) CISPR 11, Industrial Scientific and Medical(ISM) Radio-frequency Equipment -Electromagnetic Disturbance Characteristics- Limits and Methods of MeasurementMeets Class A LimitsIEC 61000-4-2 ESD ImmunityContact 4 kV, air 8 kVIEC 61000-4-3 Radiated Field Immunity10 V/m at 80 to 1000 MHzIEC 61000-4-4 Electrical FastTransient/Burst Immunity2 kV on I/O, dc power and communicationlinesIEC 61000-4-5 Surge Immunity2kV on ac and dc power lines; 1kV on I/Oand communications linesIEC 61000-4-6 Immunity to ConductedDisturbances Induced by Radio frequencyFields10 V (rms) at 150 kHz to 80 MHz on I/O,dc power and communication linesIEC 61000-4-8 Power Frequency MagneticField Immunity30 A/m at 50 and 60 HzPRODUCT SAFETY (FBM AND CABLE BALUN) Underwriters Laboratories (UL) for U.S. andCanadaUL/UL-C listed as suitable for use inUL/UL-C listed Class I, Groups A-D;Division 2; temperature code T4 enclosurebased systems. These modules are also ULand UL-C listed as associated apparatus forsupplying non-incendive communicationcircuits for Class I, Groups A-D hazardouslocations when connected to specifiedI/A Series® processor modules as describedin the I/A Series DIN Rail MountedSubsystem User’s Guide (B0400FA). Wherepower is supplied by the FBM,communications circuits also meet therequirements for Class2 as defined inArticle725 of the National Electrical Code(NFPA No.70) and Section 16 of theCanadian Electrical Code (CSA C22.1).Conditions for use are as specified in theI/A Series DIN Rail Mounted SubsystemUser’s Guide (B0400FA).European Low Voltage Directive 73/23/EECand Explosive Atmospheres (ATEX) directive94/9/ECCENELEC (DEMKO) certified as EEx nA IICT4 for use in CENELEC certified Zone 2enclosure certified as associated apparatusfor supplying non-incendive field circuits forZone 2, Group IIC, potentially explosiveatmospheres when connected to specifiedI/A Series processor modules as describedin the I/A Series DIN Rail MountedSubsystem User’s Guide (B0400FA). Also,see Table1 on page9.Calibration RequirementsCalibration of the module or termination assembly is not required.PSS 21H-2Z14 B4Page 6ENVIRONMENTAL SPECIFICATIONS(3)OperatingTEMPERATUREModule-20 to +70°C (-4 to +158°F)Termination AssemblyPVC-20 to +50°C (-4 to +122°F)PA-20 to +70°C (-4 to +158°F) RELATIVE HUMIDITY5 to 95% (noncondensing)ALTITUDE-300 to +3,000m (-1,000 to +10,000ft)StorageTEMPERATURE-40 to +70°C (-40 to +158°F)RELATIVE HUMIDITY5 to 95% (noncondensing)ALTITUDE-300 to +12,000m (-1,000 to +40,000ft) ContaminationSuitable for use in Class G3 (Harsh) environments as defined in ISA Standard S71.04, based on exposure testing according to EIA Standard 364-65, Class III. Vibration7.5 m/S2 (0.75 g) from 5 to 500 Hz(3)The environmental limits of this module may be enhanced by the type of enclosure containing the module. Refer to the applicableProduct Specification Sheet (PSS) which describes the specific type of enclosure that is to be used.PSS 21H-2Z14 B4Page 7 PHYSICAL SPECIFICATIONSMountingMODULEFBM214 mounts on a modular baseplate. Thebaseplate can be mounted on a DIN rail(horizontally or vertically), or horizontally on a19-inch rack using a mounting kit. Refer toPSS21H-2W6B4 for details.TERMINATION ASSEMBLYThe TA mounts on a DIN rail and accommodates multiple DIN rail styles including 32mm (1.26in) and 35mm 1.38in).MassMODULE284 g (10 oz) approximateTERMINATION ASSEMBLYCompression181 g (0.40 lb) approximateRing Lug249 g (0.55 lb) approximateDimensions – ModuleHEIGHT102 mm (4 in)114 mm (4.5 in) including mounting lugsWIDTH45 mm (1.75 in)DEPTH104 mm (4.11 in)Dimensions – Termination AssemblySee page10.Part NumbersFBM214 MODULEP0922VTTERMINATION ASSEMBLIESSee “FUNCTIONAL SPECIFICATIONS –TERMINATION ASSEMBLIES” on page8. Termination CablesCABLE LENGTHSUp to 30 m (98 ft)CABLE MATERIALSPolyurethane or Hypalon®/XLPTERMINATION CABLE TYPEType 1 – See Table2 on page9.CABLE CONNECTION – TA25-pin male D-subminiatureConstruction – Termination AssemblyMATERIALPolyvinyl Chloride (PVC), compressionPolyamide (PA), compressionPVC, ring lugFAMILY GROUP COLORGreen – communicationTERMINAL BLOCKS3 tiers, 8 positionsField Termination ConnectionsCOMPRESSION-TYPE ACCEPTED WIRINGSIZESSolid/Stranded/AWG0.2 to 4 mm2/0.2 to 2.5 mm2/24 to 12 AWGStranded with Ferrules0.2 to 2.5 mm2 with or without plastic collarRING-LUG TYPE ACCEPTED WIRING SIZES#6 size connectors (0.375 in (9.5 mm))0.5 to 4 mm2/22 AWG to 12 AWGPSS 21H-2Z14 B4Page 8TERMINATION ASSEMBLIES AND CABLESField input signals connect to the FBM subsystem via DIN rail mounted Termination Assemblies, which are electrically passive.TAs for the FBM214 are available in the following forms: Compression screw type using Polyvinyl Chloride(PVC) materialCompression screw type using Polyamide (PA) material Ring lug type using PVC material.See the following “FUNCTIONAL SPECIFICATIONS –TERMINATION ASSEMBLIES” for a list of TAs used with the FBM214.The FBM214 provides sufficient loop resistance to allow use of the HART Hand-Held Terminal, or PC20 Intelligent Field Device Configurator (PSS 2A-1Z3 E).A removable termination cable connects the DIN railmounted TA to the FBM via a field connector on the baseplate in which the FBM is installed. Termination cables are available in the following materials: PolyurethaneHypalon XLP .Termination cables are available in a variety of lengths, up to 30 meters (98feet), allowing the Termination Assembly to be mounted in either theenclosure or in an adjacent enclosure. See Table 2 for a list of termination cables used with the TAs forthe FBM214.FUNCTIONAL SPECIFICATIONS – TERMINATION ASSEMBLIESFBM Type Input SignalTA Part NumberTermination TA Cable TACertification PVC (a)(a)PVC is polyvinyl chloride rated from -20 to +50°C (-4 to +122°F).PA is Polyamide rated from -20 to +70°C (-4 to +158°F).PA (a)Type (b)(b) C = TA with compression terminals; RL = TA with ring lug terminals.Type (c)(c)See Table 2 for cable part numbers and specifications.Type (d)(d)See Table 1 for Termination Assembly certification definitions.FBM2148 input channels, 4 to 20mA analog signal, alone or with HART signal superimposedP0916BX P0926EA P0926TD CRL11, 2PSS 21H-2Z14 B4Page 9Table 1. Certification for Termination AssembliesType Certification (a)(a)All TAs are UL/UL-C listed to comply with applicable ordinary location safety standards for fire and shock hazards. Hazardous locationtypes comply with ATEX directive for II 3 G use. They also comply with the requirements of the European Low Voltage Directive. All listings/certifications require installation and use within the constraints specified in DIN Rail Mounted Subsystem User’s Guide (B0400FA) and the conditions stated in UL and DEMKO reports.Type 1TAs are UL/UL-C listed as suitable for use in Class I; Groups A-D; Division 2 temperature code T4 hazardous locations. They are CENELEC (DEMKO) certified EEx nA IIC T4 for use in Zone 2 potentially explosive atmospheres.Type 2TAs are UL/UL-C listed as associated apparatus for supplying non-incendive field circuits Class I; Groups A-D; Division 2 hazardous locations when connected to specified DIN rail mounted FBMs and field circuits meeting entity parameter constraints specified in DIN Rail Mounted Subsystem User’s Guide (B0400FA). They are also CENELEC (DEMKO) certified as associated apparatus for supplying field circuits for Group IIC, Zone 2 potentially explosive atmospheres. Field circuits are also Class 2 limited energy (60 V dc, 30 V ac, 100 VA or less) if customer-supplied equipment meets Class 2 limits.Table 2. Cables Types and Part NumbersCable Lengthm (ft) Type 1P/PVC (a)Type 1H/XLPE (b)Cable Lengthm (ft) Type 1P/PVC (a)Type 1H/XLPE (b)0.5 (1.6)P0916DA P0916VA 10.0 (32.8) P0916DE P0916VE 1.0 (3.2) P0916DB P0916VB 15.0 (49.2) P0916DF P0916VF 2.0 (6.6)P0931RM P0931RR 20.0 (65.6) P0916DG P0916VG 3.0 (9.8) P0916DC P0916VC 25.0 (82.0) P0916DH P0916VH 5.0 (16.4)P0916DDP0916VD30.0 (98.4)P0916DJP0916VJ(a)P/PVC is polyurethane outer jacket and semi-rigid PVC primary conductor insulation.(b)H/XLPE is Hypalon outer jacket and XLPE (cross-linked polyethylene) primary conductor insulation.PSS 21H-2Z14 B4Page 10DIMENSIONS – NOMINALRELATED PRODUCT SPECIFICATION SHEETSCompression Termination AssemblyRing Lug Termination Assembly(a) Overall width – for determining DIN rail loading.(b) Height above DIN rail (add to DIN rail height for total).PSS NumberDescriptionPSS 21H-2W1 B3DIN Rail Mounted FBM Subsystem OverviewPSS 21H-2W2 B3DIN Rail Mounted FBM Equipment, Agency CertificationsPSS 21H-2Z14 B4Page 11PSS 21H-2Z14 B4 Page 12IPS Corporate Headquarters 5601 Granite Parkway Suite 1000 Plano, TX 75024United States of AmericaFoxboro Global Client Support Inside U.S.: 1-866-746-6477 Outside U.S.: 1-508-549-2424 or contact your local Foxboro representative.Facsimile: 1-508-549-4999Invensys, Foxboro, I/A Series and the IPS Logo are trademarks of Invensys plc, its subsidiaries, and affiliates. All other brand names may be trademarks of their respective owners.Copyright 2002-2010 Invensys Systems, Inc.All rights reservedMB 21A Printed in U.S.A. 0210。

5833中文资料

5833中⽂资料Designed to reduce logic supply current, chip size, and system cost, the UCN5833A/EP integrated circuits offer high-speed operation for thermal printers. These devices can also be used to drive multi-plexed LED displays or incandescent lamps within their 125 mA peak output current rating. The combination of bipolar and MOS technolo-gies gives BiMOS II smart power ICs an interface flexibility beyond the reach of standard buffers and power driver circuits.These 32-bit drivers have bipolar open-collector npn Darlington outputs, a CMOS data latch for each of the drivers, a 32-bit CMOS shift register, and CMOS control circuitry. The high-speed CMOS shift registers and latches allow operation with most microprocessor-based systems at data input rates above 3.3 MHz. Use of these drivers with TTL may require input pull-up resistors to ensure an input logic high.The UCN5833A is supplied in a 40-pin dual in-line plastic package with 0.600" (15.24 mm) row spacing. At an ambient temperature of +75°C, all outputs of the DlP-packaged device will sustain 50 mA continuously. For high-density applications, the UCN5833EP is available. This 44-lead plastic chip carrier (quad pack) is intended for surface-mounting on solder lands with 0.050" (1.27 mm) centers.CMOS serial data outputs permit cascading for applications requiring additional drive lines.FEATURESI To 3.3 MHz Data Input Rate I 30 V Minimum Output Breakdown I Darlington Current-Sink Outputs I Low-Power CMOS Logic and LatchesBiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVERAlways order by complete part number:Part Number Package UCN5833A 40-Pin DIP UCN5833EP 44-Lead PLCCData Sheet 26185.16A*58335833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVER115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000SERIAL DATA IN POWER STROBE OUT OUT OUT OUT OUT OUT 123456OUT7OUT 8OUT 9OUTOUT OUTOUT OUTLOGIC SUPPLY OUT OUT Dwg. No. A-13,051TYPICAL OUTPUT DRIVERSUBOUT115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000Copyright ? 1986, 1995, Allegro MicroSystems, Inc.5833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVERTRUTH TABLEL = Low Logic Level H = High Logic Level X = Irrelevant P = Present State R = Previous StateELECTRICAL CHARACTERISTICS at T A = +25°C, V DD = 5 V (unless otherwise noted).Limits CharacteristicSymbol Test Conditions Min.Max.Units Output Leakage Current I CEX V OUT = 30 V, T A = 70°C —10µA Collector-Emitter V CE(SAT)l OUT = 50 mA — 1.2V l OUT = 100 mA— 1.7V Input VoltageV IN(1) 3.5 5.3V V IN(0)-0.3+0.8V Input Currentl IN(1)V IN = 5.0 V — 1.0µA l IN(0)V IN = 0 V —-1.0µA Serial Output VoltageV OUT(1)I OUT = -200 µA 4.5—V V OUT(0)I OUT = 200 µA—0.3V Supply Currentl DD One output ON, l OUT = 100 mA — 1.0mA All outputs OFF—50µA Output Rise Time t r l OUT = 100 mA, 10% to 90%—500ns Output Fall Timet fl OUT = 100 mA, 90% to 10%—500nsNOTE: Positive (negative) current is defined as going into (coming out of) the specified device pin.Saturation Voltage5833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVER115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000TIMING CONDITIONS(V DD = 5.0 V, Logic Levels are V DD and Ground)A.Minimum Data Active Time Before Clock Pulse(Data Set-Up Time)..........................................................................75 ns B.Minimum Data Active Time After Clock Pulse(Data Hold Time).............................................................................75 ns C.Minimum Data Pulse Width ................................................................150 ns D.Minimum Clock Pulse Width...............................................................150 nsE.Minimum Time Between Clock Activation and Strobe.......................300 nsF.Minimum Strobe Pulse Width .............................................................100 nsG.Typical Time Between Strobe Activation andOutput Transition ...........................................................................500 nsDwg. No. A-12,276ASerial Data present at the input is transferred to the shift register on the logic “0” to logic “1” transition of the CLOCK input pulse. On succeeding CLOCK pulses, the registers shift data information towards the SERIAL DATA OUTPUT. The SERIAL DATA must appear at the input prior to the rising edge of the CLOCK input waveform.Information present at any register is transferred to its respective latch when the STROBE is high (serial-to-parallel conversion). The latches will continue to accept new data as long as the STROBE is held high. Applications where the latches are bypassed (STROBE tied high) will require that the OUTPUT ENABLE input be low during serial data entry.When the OUTPUT ENABLE input is low, all of the output buffers are disabled (OFF) without affecting the information stored in the latches or shift register. With the OUTPUT ENABLE input high, the outputs are controlled by the state of the latches.CLOCK DATA INSTROBE NOUTPUT ENABLEOUT5833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVERNOTES:1.Exact body and lead configuration at vendor’s option within limits shown.2.Lead spacing tolerance is non-cumulative.3.Lead thickness is measured at seating plane or below.UCN5833ADimensions in Inches (controlling dimensions)Dimensions in Millimeters (for reference only)123Dwg. MA-003-40 mm20421123Dwg. MA-003-40 in2045833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVER115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000UCN5833EPDimensions in Inches (controlling dimensions)Dimensions in Millimeters (for reference only)Dwg. MA-005-44A mm0.53340Dwg. MA-005-44A in0.021740NOTES:1.Exact body and lead configuration at vendor’s option within limits shown.2.Lead spacing tolerance is non-cumulative.5833BiMOS II 32-BITSERIAL-INPUT,LATCHED DRIVERThe products described here are manufactured under one or more U.S. patents or U.S. patents pending.Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.Allegro products are not authorized for use as critical components in life-support devices or systems without express written approval.The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsi-bility for its use; nor for any infringement of patents or other rights of third parties which may result from its use. 5833BiMOS II 32-BIT SERIAL-INPUT,LATCHED DRIVER115 Northeast Cutoff, Box 15036Worcester, Massachusetts 01615-0036 (508) 853-5000POWERINTERFACE DRIVERSFunctionOutput Ratings*Part Number ?SERIAL-INPUT LATCHED DRIVERS8-Bit (saturated drivers)-120 mA 50 V?58958-Bit 350 mA 50 V 58218-Bit 350 mA 80 V 58228-Bit 350 mA 50 V?58418-Bit 350 mA 80 V?58428-Bit (constant-current LED driver)75 mA 17 V 62758-Bit (DMOS drivers)250 mA 50 V 65958-Bit (DMOS drivers)350 mA 50 V?6A5958-Bit (DMOS drivers)100 mA 50 V 6B59510-Bit (active pull-downs)-25 mA 60 V 5810-F and 6809/1012-Bit (active pull-downs)-25 mA 60 V 5811 and 681116-Bit (constant-current LED driver)75 mA 17 V 627620-Bit (active pull-downs)-25 mA 60 V 5812-F and 681232-Bit (active pull-downs)-25 mA 60 V 5818-F and 681832-Bit100 mA 30 V 583332-Bit (saturated drivers)100 mA 40 V 5832PARALLEL-INPUT LATCHED DRIVERS4-Bit350 mA 50 V?58008-Bit -25 mA 60 V 58158-Bit350 mA 50 V?58018-Bit (DMOS drivers)100 mA 50 V 6B2738-Bit (DMOS drivers)250 mA 50 V 6273SPECIAL-PURPOSE DEVICESUnipolar Stepper Motor Translator/Driver 1.25 A 50 V?5804Addressable 8-Bit Decoder/DMOS Driver 250 mA 50 V6259Addressable 8-Bit Decoder/DMOS Driver 350 mA 50 V?6A259Addressable 8-Bit Decoder/DMOS Driver 100 mA 50 V 6B259Addressable 28-Line Decoder/Driver 450 mA30 V6817*Current is maximum specified test condition, voltage is maximum rating. See specification for sustaining voltagelimits.Negative current is defined as coming out of (sourcing) the output.Complete part number includes additional characters to indicate operating temperature range and package style. Internal transient-suppression diodes included for inductive-load protection.。

常见矿物:名称,化学式,产地,用途

15-10-21

常见矿物:名称,化学式,产地,用途

Sb 2 S 3

湖南

冶金

/s?__biz=MjM5MDE5ODYwNg==&mid=203577578&idx=1&sn=e57887e3ea98283cf5d5dea10acdc485&scene=2&from=timeline&isappi… 3/17

15-10-21

硅酸盐工业

湖南

硅酸盐工业

49 黄河矿 50 黄铁矿 51 黄铜矿

Huanghoite Pyrite

Chalcopyrite

SaCe[CO 3 ]F FeS 2

CuFeS 2

湖南、辽宁 化学工业

山西吉林

冶金

52 辉铋矿

Bis m uthinite

Bi 2 S 3

湖南

冶金

Antimonite (Stibuite 53 辉锑矿

87 透闪石

பைடு நூலகம்

Trem olite

88 锡石

Cas s iterite

89 香花石 Hsianghualite

90 雄黄

Realgar

91 阳起石

Actinolite

92 叶蜡石

Pyorphyllit

93 萤石

Fluorite

94 硬玉

95 硬锰矿

96 黝铜矿

97 针铁矿

98 正长石

99 自然金

10 自然铜

59 金刚石

Diamond

C

山东

珠宝业、磨具

60 金云母

Phlogopite

KMg 3 [AlSi 3 O 10 ](F,OH) 2

西门子828D参数

驱动器调试5.5 SINAMICS 驱动常用参数SINAMICS S120 的参数有CU 控制单元参数、ALM 电源模块参数、SERVO 轴参数; 其中 R 参数为只读参数,P 参数为可读可写参数。

参数说明参数 参数归属 参数值 说明驱动就绪,可以运行 10驱动就绪,但是缺少驱动使能或者驱动有报警 33拓扑结构错误:硬件连接出错或者在更换备件时拓扑结构比较等级P9906未设为3 CU_I 35初次上电,驱动未调试 0驱动就绪,可以运行 32启动准备,等待ON/OFF1信号,对应PCU X20.1 44启动禁止,电源模块EP 使能未接通 ALM 45启动禁止,电源模块有报警 0驱动就绪,可以运行 23启动准备,等待电源模块运行使能P864,对于SLM, 对应PCU X20.1 31启动准备,等待驱动ON/OFF1使能,对应NC/PLC 接口使能信号V380x0002.1和 V380x4001.7 43启动禁止,ON/OFF3使能丢失,对应PCU X20.2 R2 SERVO 45启动禁止,模块有报警 R20SERVO 平滑后的速度设定值 R21SERVO 平滑后的速度实际值 R26ALM/SERVO 平滑后的直流母线电压 R27ALM/SERVO 平滑后的电流实际值 R35SERVO 电机温度 R36ALM/SERVO 模块超温I 2t R37ALM/SERVO 模块温度 R46ALM/SERVO 丢失的使能信号 R61SERVO 电机编码器速度实际值 R67ALM/SERVO 最大的驱动输出电流 R68ALM/SERVO 电流实际值 R722SINAMICS_I R722.0 PCU X20.1端子状态R722.1 PCU X20.2端子状态 P9CU_I 驱动状态,P9≠0表示驱动处于调试状态 P10ALM/SERVO ALM 或SERVO 状态,P10≠0表示模块处于调试状态 P495SERVO 轴BERO 信号输入定义 P971SERVO P971=1自动变0,轴参数存储 P977CU_I P977=1自动变0,所有驱动参数存储 P1460[0]SERVO 伺服速度环增益 P1462[0]SERVO 伺服速度环积分时间 P3985ALM/SERVO 模块控制优先权定义 P9906 CU_I拓扑比较等级设定NC调试6 NC调试重要事项NC的调试必须在制造商口令(“EVENING”)下进行。

七年级英语上册Unit语法知识点

七年级英语上册U n i t语法知识点It was last revised on January 2, 2021U n i t1M y n a m e’s G i n a. 语法专项:形容词性物主代词教材典句1.What’shisname他叫什么名字?—Hisname’sEric.他的名字叫埃里克。

2.What’shername她叫什么名字?—She’sMary.她叫玛丽。

3.What’syourtelephonenumber,LiXin李欣,你的电话号码是什么?以上句子中分别含有形容词性物主代词his,her,your,今天我们就来学习一下形容词性物主代词的用法。

语法全解物主代词是表示所有关系的代词,是人称代词的属格形式。

它分第一人称、第二人称和第三人称,每个人称又分单数和复数。

物主代词可分为形容词性物主代词和名词性物主代词。

本单元主要涉及形容词性物主代词。

形容词性物主代词的用法与形容词的用法相似,可以修饰名词,一般放在被修饰的名词之前,不能单独使用。

如果名词前面还有其他的定语,物主代词要放在其他定语的前面。

mypen我的钢笔myredpen我的红色钢笔yourname你的名字hismother他的母亲练一练:①.Pleasesend________bestwishestoMary.A.IB.meC.myD.mine②.__DoesMissWhitelikesports__Yes,_________favoritesportistennis.A.heB.sheC.hisD.her③.Thisis________pen.A.redmyB.heredC.redhisD.herred④.__I’mLinda.What’syourname_________nameisLucy.A.IB.MeC.MyD.Mine4.介绍自己:(1)Myname’s+名字我的名字叫......(2)I’m+名字我是......5.询问姓名(1)What’syourname?你叫什么名字?----Alan.艾伦。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。