LPC2000系列ARM

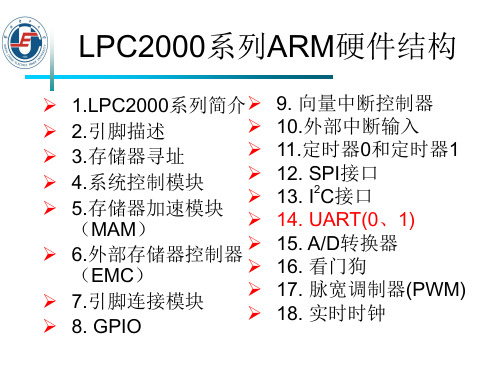

LPC2000系列ARM硬件结构与功能简介

1.4 处理器状态及模式

用户和系统模式

处理器模式 用户 用户 系统 系统 快中断 中断 管理 中止 未定义 说明 备注 不能直接切换到其它模式 (usr) 正常程序工作模式 (usr) 用于支持操作系统的特 与用户模式类似,但具有可以 (sys) (sys) 权任务等 直接切换到其它模式等特权 而且它们使用完全相同的寄存器组。 (fiq) (irq) (svc) (abt) (und) 支持高速数据传输及通 系统模式是特权模式,不受用 FIQ异常响应时进入此模式 道处理

ARM公司简介

ARM是Advanced RISC Machines的缩写,它是 一家微处理器行业的知名企业,该企业设计了大量 高性能、廉价、耗能低的RISC (精简指令集)处 理器。 公司的特点是只设计芯片,而不生产。 它将技术授权给世界上许多著名的半导体、软件和 OEM厂商,并提供服务。

1.2 ARM体系结构简介

(svc) 操作系统保护代码 (abt) (und) 用于支持虚拟内存和/或 存储器保护 支持硬件协处理器的软 件仿真

1.4 处理器状态及模式

特权模式

处理器模式 用户 系统 系统 说明 用于支持操作系统的特 权任务等 备注 不能直接切换到其它模式 与用户模式类似,但具有可以 直接切换到其它模式等特权 (usr) 正常程序工作模式 (sys) (sys)

处理器模式说明备注用户usr正常程序工作模式不能直接切换到其它模式系统sys用于支持操作系统的特权任务等与用户模式类似但具有可以直接切换到其它模式等特权快中断fiq支持高速数据传输及通道处理fiq异常响应时进入此模式中断irq用于通用中断处理irq异常响应时进入此模式管理svc操作系统保护代码系统复位和软件中断响应时进入此模式中止abt用于支持虚拟内存和或存储器保护在arm7tdmi没有大用处未定义und支持硬件协处理器的软件仿真未定义指令异常响应时进入此模式14处理器状态及模式?处理器模式14处理器状态及模式?特权模式处理器模式说明备注用户usr正常程序工作模式不能直接切换到其它模式系统sys用于支持操作系统的特权任务等与用户模式类似但具有可以直接切换到其它模式等特权快中断fiq支持高速数据传输及通道处理fiq异常响应时进入此模式中断irq用于通用中断处理irq异常响应时进入此模式管理svc操作系统保护代码系统复位和软件中断响应时进入此模式中止abt用于支持虚拟内存和或存储器保护在arm7tdmi没有大用处未定义und支持硬件协处理器的软件仿真未定义指令异常响应时进入此模式除用户模式外其它模式均为特权模式

arm 嵌入式系统基础教程 - 广州周立功单片机发展有限公司

ARM嵌入式系统基础教程周立功等编著北京航空航天大学出版社2005年1月定价:32.00元内容简介本书是《ARM嵌入式系统系列教程》中的理论课教材。

以PHILIPS公司LPC2000系列ARM微控制器为例,深入浅出地介绍嵌入式系统开发的各个方面。

全书共分为3部分:第1章和第2章为理论部分,主要介绍嵌入式系统的概念及开发方法。

第3~5章为基础部分,主要介绍ARM7体系结构、指令系统及LPC2000系列ARM微控制器的结构原理。

第6~8章为应用部分,主要以LPC2000系列微控制器为例介绍如何设计嵌入式系统,包括硬件的设计、μC/OSII的移植以及建立软件开发平台的方法。

本书可以作为高等院校电子、自动化、机电一体化计算机等相关专业嵌入式系统课程的教材,也可作为从事嵌入式系统应用开发工程师的参考资料。

本书配套多媒体教学课件。

序1. ARM嵌入式系统的发展趋势由于网络与通信技术的发展,嵌入式系统在经历了近20年的发展历程后,又进入了一个新的历史发展阶段,即从普遍的低端应用进入到一个高、低端并行发展,并且不断提升低端应用技术水平的时代,其标志是近年来32位MCU的发展。

32位MCU的应用不会走8位机百花齐放、百余种型号系列齐上阵的道路,这是因为在8位机的低端应用中,嵌入对象与对象专业领域十分广泛而复杂;而当前32位MCU的高端应用则多集中在网络、通信和多媒体技术领域,32位MCU将会集中在少数厂家发展的少数型号系列上。

在嵌入式系统高端应用的发展中,曾经有众多的厂家参与,很早就有许多8位嵌入式MCU厂家实施了8位、16位和32位机的发展计划。

后来,8位和32位机的技术扩展侵占了16位机的发展空间。

传统电子系统智能化对8位机的需求使这些厂家将主要精力放在8位机的发展上,形成了32位机发展迟迟不前的局面。

当网络、通信和多媒体信息家电业兴起后,出现了嵌入式系统高端应用的市场;而在嵌入式系统的高端应用中,进行多年技术准备的ARM公司适时地推出了32位ARM系列嵌入式微处理器,以其明显的性能优势和知识产权平台扇出的运行方式,迅速形成32位机高端应用的主流地位,以至于使不少传统嵌入式系统厂家放弃了自己的32位发展计划,转而使用ARM内核来发展自己的32位MCU。

ARM嵌入式系统基础教程第二版课后习题答案

第1章嵌入式系统概述(1)举出3个本书中未提到的嵌入式系统的例子。

答:键盘、鼠标、扫描仪。

(2)什么叫嵌入式系统?答:嵌入到对象体系中的专用计算机应用系统。

(3)什么叫嵌入式处理器?嵌入式处理器分为哪几类?答:嵌入式处理器是为完成特殊的应用而设计的特殊目的的处理器。

分为3类:1.注重尺寸、能耗和价格;2.关注性能;3.关注全部4个需求——性能、尺寸、能耗和价格。

(4)什么是嵌入式操作系统?为何要使用嵌入式操作系统?答:嵌入式操作系统是操作系统的一种类型,是在传统操作系统的基础上加入符合嵌入式系统要求的元素发展而来的。

原因:1.提高了系统的可靠性;2.提高了开发效率,缩短了开发周期。

3.充分发挥了32位CPU的多任务潜力。

第2章 ARM7体系结构1.基础知识(1)ARM7TDMI中的T、D、M、I的含义是什么?答:T:高密度16位Thumb指令集扩展;D:支持片上调试;M:64位乘法指令;I:Embedded ICE硬件仿真功能模块。

(2)ARM7TDMI采用几级流水线?使用何种存储器编址方式?答:3级;冯·诺依曼结构。

(3)ARM处理器模式和ARM处理器状态有何区别?答:ARM处理器模式体现在不同寄存器的使用上;ARM处理器状态体现在不同指令的使用上。

(4)分别列举ARM的处理器模式和状态?答:ARM的处理器模式:用户模式、系统模式、管理模式、中止模式、未定义模式、中断模式、快速模式;ARM的处理器状态:ARM状态、Thumb状态。

(5)PC和LR分别使用哪个寄存器?答:PC:R15;LR:R14。

(6)R13寄存器的通用功能是什么?答:堆栈指针SP。

(7)CPSR寄存器中哪些位用来定义处理器状态?答:位31~28:N、Z、C、V,条件代码标志位;27~8:保留位;7~0:I、F、T、M4~0,控制标志位。

(8)描述一下如何禁止IRQ和FIQ的中断。

答:当控制位I置位时,IRQ中断被禁止,否则允许IRQ中断使能;当控制位F置位时,FIQ 中断被禁止,否则允许FIQ中断使能。

周立功 LPC2000系列ARM微控制器应用开发教程说明书

个人电脑已经是64位了,您还在使用8位微控制器吗?尽管一般情况下嵌入式系统对CPU处理能力的要求比个人电脑(对CPU处理能力的要求)低,但随着人们生活的提高和技术的进步,嵌入式系统对CPU处理能力的要求也稳步的提高,大量高速的与MCS51体系结构兼容的微控制器的出现就证明了这一点。

但8位微控制器受限于体系结构,处理能力的提高始终有限。

而16位系统在性能上与8位机相比始终没有太大优势,成本上与32位系统相比也没有什么优势,未来一段时间嵌入式微控制器的发展方向必然是32位系统。

基于ARM体系结构的32位系统占领了32位嵌入式系统的大部分分额,但长期以来,基于ARM体系结构的32位系统仅在嵌入式式系统的高端(通讯领域、PDA)等场合使用,要么以专用芯片的面貌出现,要么以位处理器的庙貌出现,并没有出现性价比高的通用的微控制器。

PHILIPS发现了这个空当,推出了性价比很高LPC2000系列微控制器,让更多的嵌入式系统具有32位的处理能力。

这也预示着32位系统即将成为嵌入式系统的主流。

基于ARM体系结构的芯片在中国推广已经有好几年了,关于ARM的图书也出了不少。

关于ARM的图书主要有以下几类:1.关于ARM内核的图书,主要读者是芯片设计者,内容主要是介绍芯片设计的。

2.芯片应用类图书,主要是芯片的生产商或代理商编写,主要读者为应用工程师。

3.开发板类图书,主要介绍相应的ARM开发板,给应用者一些参考。

以上3类图书的侧重点都不是ARM应用开发教学,用于大学本科教学不太适合。

为了方便高等院校教学方便,笔者编写了这本教材。

不过,因为嵌入式系统牵涉的知识太广,一本教材无法深入论述。

为此,笔者还会推出多本被套图书以便学生知识扩展。

第1章嵌入式系统概述 (1)1.1嵌入式系统 (1)1.1.1 现实中的嵌入式系统 (1)1.1.2 嵌入式系统的概念 (2)1.1.3 嵌入式系统的未来 (2)1.2嵌入式处理器 (2)1.2.1 简介 (2)1.2.2 分类 (3)1.3嵌入式操作系统 (4)1.3.1 简介 (4)1.3.2 基本概念 (5)1.3.3 使用实时操作系统的必要性 (8)1.3.4 实时操作系统的优缺点 (8)1.3.5 常见的嵌入式操作系统 (8)第2章嵌入式系统工程设计 (14)2.1嵌入式系统项目开发生命周期 (14)2.1.1 概述 (14)2.1.2 识别需求 (15)2.1.3 提出方案 (17)2.1.4 执行项目 (19)2.1.5 结束项目 (21)2.2嵌入式系统工程设计方法简介 (22)2.2.1 由上而下与由下而上 (22)2.2.2 UML系统建模 (22)2.2.3 面向对象OO的思想 (23)第3章ARM7体系结构 (25)3.1简介 (25)3.1.1 ARM (25)3.1.2 ARM的体系结构 (25)3.1.3 ARM处理器核简介 (26)3.2ARM7TDMI (27)3.2.1 简介 (27)3.2.2 三级流水线 (28)3.2.4 存储器接口 (28)3.3ARM7TDMI的模块和内核框图 (29)3.4体系结构直接支持的数据类型 (31)3.5处理器状态 (32)3.6处理器模式 (32)3.7内部寄存器 (33)3.7.1 简介 (33)3.7.2 ARM状态寄存器集 (33)3.7.3 Thumb状态寄存器集 (35)3.8程序状态寄存器 (37)3.8.1 简介 (37)3.8.2 条件代码标志 (38)3.8.3 控制位 (38)3.8.4 保留位 (39)3.9异常 (39)3.9.1 简介 (39)3.9.2 异常入口/出口汇总 (39)3.9.3 进入异常 (40)3.9.4 退出异常 (41)3.9.5 快速中断请求 (41)3.9.6 中断请求 (41)3.9.7 中止 (41)3.9.8 软件中断指令 (42)3.9.9 未定义的指令 (42)3.9.10 异常向量 (42)3.9.11 异常优先级 (43)3.10中断延迟 (43)3.10.1 最大中断延迟 (43)3.10.2 最小中断延迟 (44)3.11复位 (44)3.12存储器及存储器映射I/O (44)3.12.1 简介 (44)3.12.2 地址空间 (44)3.12.3 存储器格式 (45)3.12.4 未对齐的存储器访问 (46)3.12.5 指令的预取和自修改代码 (47)3.13寻址方式简介 (51)3.14ARM7指令集简介 (52)3.14.1 简介 (52)3.14.2 ARM指令集 (52)3.14.3 Thumb指令集 (54)3.15协处理器接口 (56)3.15.1 简介 (56)3.15.2 可用的协处理器 (56)3.15.3 关于未定义的指令 (57)3.16调试接口简介 (57)3.16.1 典型调试系统 (57)3.16.2 调试接口 (58)3.16.3 EmbeddedICE-RT (58)3.16.4 扫描链和JTAG接口 (59)3.17ETM接口简介 (59)第4章ARM7TDMI(-S)指令系统 (61)4.1ARM处理器寻址方式 (61)4.2指令集介绍 (64)4.2.1 ARM指令集 (64)4.2.2 Thumb指令集 (90)第5章LPC2000系列ARM硬件结构 (112)5.1简介 (112)5.1.1 描述 (112)5.1.2 特性 (112)5.1.3 器件信息 (113)5.1.4 结构概述 (113)5.2引脚配置 (114)5.2.1 引脚排列及封装信息 (114)5.2.2 LPC2114/2124的引脚描述 (116)5.2.3 LPC2210/2212/2214的引脚描述 (120)5.2.4 引脚功能选择使用示例 (126)5.3存储器寻址 (126)5.3.1 片内存储器 (126)5.3.3 存储器映射 (127)5.3.4 预取指中止和数据中止异常 (131)5.3.5 存储器重映射及引导块 (132)5.3.6 启动代码相关部分 (134)5.4系统控制模块 (136)5.4.1 系统控制模块功能汇总 (136)5.4.2 引脚描述 (137)5.4.3 寄存器描述 (137)5.4.4 晶体振荡器 (138)5.4.5 复位 (139)5.4.6 外部中断输入 (142)5.4.7 外部中断应用示例 (145)5.4.8 存储器映射控制 (146)5.4.9 PLL(锁相环) (148)5.4.10 VPB分频器 (153)5.4.11 功率控制 (154)5.4.12 唤醒定时器 (156)5.4.13 启动代码相关部分 (156)5.5存储器加速模块(MAM) (158)5.5.1 描述 (158)5.5.2 MAM结构 (159)5.5.3 MAM的操作模式 (160)5.5.4 MAM配置 (161)5.5.5 寄存器描述 (161)5.5.6 MAM使用注意事项 (162)5.5.7 启动代码相关部分 (162)5.6外部存储器控制器(EMC) (163)5.6.1 特性 (163)5.6.2 概述 (163)5.6.3 引脚描述 (164)5.6.4 寄存器描述 (164)5.6.5 外部存储器接口 (166)5.6.6 典型总线时序 (168)5.6.7 外部存储器选择 (168)5.6.8 启动代码相关部分 (169)5.7引脚连接模块 (170)5.7.1 介绍 (170)5.7.2 寄存器描述 (170)5.7.3 引脚功能控制 (173)5.7.4 启动代码相关部分 (173)5.8.1 特性 (175)5.8.2 描述 (175)5.8.3 结构 (176)5.8.4 寄存器描述 (177)5.8.5 中断源 (181)5.8.6 VIC使用事项 (183)5.8.7 VIC应用示例 (184)5.8.8 启动代码相关部分 (185)5.9GPIO (186)5.9.1 特性 (186)5.9.2 应用 (186)5.9.3 引脚描述 (187)5.9.4 寄存器描述 (187)5.9.5 GPIO使用注意事项 (189)5.9.6 GPIO应用示例 (189)5.10UART 0 (189)5.10.1 特性 (189)5.10.2 引脚描述 (190)5.10.3 应用 (190)5.10.4 结构 (190)5.10.5 寄存器描述 (191)5.10.6 使用示例 (198)5.11UART1 (200)5.11.1 特性 (200)5.11.2 引脚描述 (200)5.11.3 应用 (201)5.11.4 结构 (202)5.11.5 寄存器描述 (203)5.12I2C接口 (211)5.12.1 特性 (211)5.12.2 应用 (211)5.12.3 引脚描述 (211)5.12.4 I2C接口描述 (211)5.12.5 I2C操作模式 (214)5.12.6 寄存器描述 (225)5.13SPI接口 (228)5.13.1 特性 (228)5.13.2 引脚描述 (228)5.13.3 描述 (229)5.13.5 寄存器描述 (235)5.14定时器0和定时器1 (237)5.14.1 描述 (237)5.14.2 特性 (237)5.14.3 应用 (238)5.14.4 管脚描述 (238)5.14.5 结构 (239)5.14.6 寄存器描述 (239)5.14.7 定时器举例操作 (244)5.14.8 使用示例 (245)5.15脉宽调制器(PWM) (247)5.15.1 特性 (247)5.15.2 引脚描述 (248)5.15.3 描述 (248)5.15.4 结构 (249)5.15.5 寄存器描述 (251)5.15.6 使用示例 (256)5.16A/D转换器 (258)5.16.1 特性 (258)5.16.2 描述 (258)5.16.3 引脚描述 (258)5.16.4 寄存器描述 (259)5.16.5 操作 (261)5.16.6 使用示例 (261)5.17实时时钟 (262)5.17.1 特性 (262)5.17.2 描述 (262)5.17.3 结构 (262)5.17.4 RTC中断 (263)5.17.5 闰年计算 (264)5.17.6 寄存器描述 (264)5.17.7 混合寄存器组 (265)5.17.8 完整时间寄存器 (267)5.17.9 时间计数器组 (268)5.17.10 报警寄存器组 (269)5.17.11 基准时钟分频器(预分频器) (269)5.17.12 RTC使用注意事项 (271)5.17.13 使用示例 (271)5.18看门狗 (274)5.18.2 应用 (274)5.18.3 描述 (274)5.18.4 结构 (275)5.18.5 寄存器描述 (275)5.18.6 使用示例 (277)5.19本章小结 (278)第6章接口技术与硬件设计 (280)6.1最小系统 (280)6.1.1 框图 (280)6.1.2 电源 (280)6.1.3 时钟 (284)6.1.4 复位及复位芯片配置 (284)6.1.5 存储器系统 (287)6.1.6 调试与测试接口 (288)6.1.7 完整的最小系统 (289)6.2片内外设 (291)6.2.1 GPIO(通用I/O) (291)6.2.2 UART、MODEM (295)6.2.3 I2C (298)6.2.4 SPI (304)6.3总线接口 (308)6.3.1 并行SRAM (308)6.3.2 并行FALSH (314)6.3.3 USB(D12)接口 (328)6.3.4 液晶接口 (332)6.3.5 网络接口 (341)6.4其它外设 (350)6.4.1 并行打印机接口 (350)6.4.2 CF卡及IDE硬盘接口 (356)第7章移植µC/OS-II到ARM7 (362)7.1µC/OS-II简介 (362)7.1.1 概述 (362)7.1.2 µC/OS-II的特点 (362)7.2移植规划 (363)7.2.1 编译器的选择 (363)7.2.2 任务模式的取舍 (363)7.3移植µC/OS-II (363)7.3.1 概述 (363)7.3.2 关于头文件includes.h和config.h (364)7.3.3 编写OS_CPU.H (365)7.3.4 编写Os_cpu_c.c文件 (366)7.3.5 编写Os_cpu_a.s (371)7.3.6 关于中断及时钟节拍 (374)7.4移植代码应用到LPC2000 (376)7.4.1 编写或获取启动代码 (376)7.4.2 挂接SWI软件中断 (376)7.4.3 中断及时钟节拍中断 (377)7.4.4 编写应用程序 (377)7.5本章小结 (379)第8章嵌入式系统开发平台 (380)8.1如何建立嵌入式系统开发平台 (380)8.1.1 使用平台开发是大势所趋 (380)8.1.2 建立开发平台的方法 (383)8.1.3 编写自己的软件模块 (384)8.2数据队列 (384)8.2.1 简介 (384)8.2.2 API函数集 (384)8.3串口驱动 (387)8.3.1 简介 (387)8.3.2 API函数集 (387)8.4MODEM接口模块 (389)8.4.1 简介 (389)8.4.2 MODEM的状态 (389)8.4.3 API函数集 (389)8.5I2C总线模块 (390)8.5.1 简介 (390)8.5.2 API函数集 (391)8.6SPI总线模块 (392)8.6.1 简介 (392)8.6.2 API函数集 (392)第1章嵌入式系统概述1.1 嵌入式系统经过几十年的发展,嵌入式系统已经在很大程度改变了人们的生活、工作和娱乐方式,而且这些改变还在加速。

电路的ARM单片机控制器的设计——

电路的ARM单片机控制器的设计——buck-boost电路的ARM单片机控制器的设计摘要本文提出了一种基于ARM的一种新型BUCK-BOOST(AC-AC)电路控制器设计。

在斩控式AC-AC变换中,控制电路绝大部分还是采用PWM发生模块进行模拟控制,这些模块斩波频率高,可以进行简单的PID控制,但也有模拟电路固有的缺点:元器件老化,温度漂移,系统不灵活,精度不高,开发速度慢等问题。

本文针对于这些问题,用ARM嵌入式处理器LPC2114设计了一种新型控制器。

由于CPU直接参与闭环控制,能显著降低系统硬件成本,同时不存在温度漂移等问题,一旦调试正常就能长期稳定运行;另外,通过软件版本改变系统功能,灵活实现复杂的控制算法。

因此,随着微处理器价格的降低和技术的成熟,数字控制技术必将在高性能,智能化DC/DC和斩控式AC-AC变换器中得到应用和发展。

本文对系统的结构和原理进行了具体分析,详细介绍了采用ARM嵌入式处理器作为控制器的设计方法和控制策略,并进行了软件的设计,实现了BUCK-BOOT电路的全数字控制。

关键词:ARM ,控制器,BUCK-BOOSTDesign of ARM one-chip computer controller of buck-boost circuitAbstractThis article proposed one kind based on ARM one kind of new BUCK-BOOST (AC-AC) the circuit controller design. In cuts controls type AC-AC, in the transformation, the control circuit major part uses PWM to have the module to carry on the simulation control, these modules cut the wave frequency to be high, may carry on the simple PID control, but also has the analogous circuit inherent shortcoming: the primary device aging and temperature drifting ,the system is not nimble, the precision is not high, the development speed is slow and so on. in view of this, this article design its controller with ARM Inserted type processor LPC2114, has carried on the concrete analysis to the system structure and the principle, in detail, the article introduced the design method and the control strategy with ARM inserted type processor to be the controller ,and have carried on the software design, has realized the BUCK-BOOT electric circuit entire numerical control.Because CPU direct participation closed-loop control, then can remarkably reduce the system hardware cost, at the same time does not have the temperature drifting problem, once debugs normally can the long-term stability movement; Moreover, we can through change system function through software edition, nimble realize complex control algorithm. Therefore, along with micro processor price reducing and the technical maturity, the numerical control technology will certainly get application and the development in the high performance, intellectualized DC/DC and BUCK-BOOST AC-AC converter.Key words: ARM, controller, BUCK-BOOST目录摘要 (I)Abstract (II)1绪论 (1)1.1选题背景及目的 (1)1.2ARM的发展 (1)1.3设计完成的任务 (2)1.4设计要求及参数设定 (3)2系统硬件设计 (4)2.1主电路拓扑结构分析 (4)2.2ARM单片机的选择及外围电路的设计 (7)2.3检测电路 (7)2.3.1全波整流电路 (8)2.3.2 滤波电路 (10)2.4IGBT驱动电路的设计 (11)2.5同步电路 (13)2.6键盘显示 (14)3软件设计 (16)3.1初始化 (16)3.1.1脉宽调制器的设置 (16)3.1.2 A/D转换器的设置 (17)3.1.3 GPIO的设置: (18)3.2PID控制策略 (18)3.3键盘与显示 (22)结论 (27)致谢 (28)参考文献 (29)附录A(英文文献) (30)附录B(中文翻译) (37)1绪论1.1选题背景及目的随着Internet的普及,我们已经进入了网络时代,进入了后PC时代。

第6章 LPC2000系列微处理器片上外设接口

保留

保留 保留 EINT2 保留 EINT3 保留 保留 保留 保留 保留 保留

00

00 00 00 00 00 00 00 00 00 00 00

管脚功能选择寄存器1(PINSEL1 )

引脚名称 PINSEL1位 00 01 10 11 复位值

P0.16

P0.17 P0.18 P0.19 P0.20 P0.21 P0.22 P0.23

作为输入功能时,引脚处于高阻态。

14

GPIO相关寄存器描述——IOxSET

out in IOxDIR IOxCLR IOxSET 1 0

PINSELx

IOxPIN

IOxSE T 31 : 0

描述 输出置位。IOxSET[0]对应于Px.0 … IOxPIN[31]对应于Px.31引脚

复位值 0

当引脚设臵为GPIO输出模式时,可使用该寄存器从引脚输出高电平。 向某位写入1使对应引脚输出高电平。写入0无效。

第6章 LPC2000系列微处理器 片上外设接口

6.1 引脚连接模块 6.2 GPIO原理及应用 6.3 外部中断输入 6.4 定时计数电路 6.5 UART串行接口 6.6 片上一些其它常用接口(SPI、I2C、 A/D、WDT、PWM及RTC)

嵌入式系统 实验报告

使能 IRQ 中断。

4 装载并使能外中断;

5 选用 DebugInExram 生成目标,然后编译连接工程。

6 选择【Project】->【Debug】,启动 AXD 进行 JTAG 仿真调试。

7 全速运行程序,LED 闪烁;

8 每一次按键 Key,蜂鸣器就会转换静音或鸣响状态。

四.测试数据及运行结果

1

五.总结

1.实验过程中遇到的问题及解决办法;

由于本次实验较简单,且我们之前学习的微机原理课程也进行了流水灯的设

计实验,所以对于本次实验,我完成地很顺利,在实验中没有遇到问题。

2.对设计及调试过程的心得体会。

本次实验是本学期该课程我们进行的第一次实验,总的来说,实验不是很难,

设计过程也相对简单,其主要目的是让我们熟悉一下实验环境,并且能在实验环

6

五.总结 1.实验过程中遇到的问题及解决办法;

实验第一次运行时,蜂鸣器一直处于鸣响状态,及时按了按键,蜂鸣器还是 一直鸣叫,不产生外中断。后来仔细检查了程序,发现原来是忘记使能 EINT0 中 断了,加上 VICIntEnable = 1<<0x0e 代码,程序就能正常运行了。 2. 对设计及调试过程的心得体会。

境下进行简单的实验操作,为之后的实验打下坚实的基础。

六.附录:源代码(电子版)

#include "config.h"

const uint32 LEDS8 = 0xFF << 18;//P1[25:18]控制 LED1~LED8,低电平点亮

const uint32 KEY = 1 << 16;

//P0.16 连接 KEY1

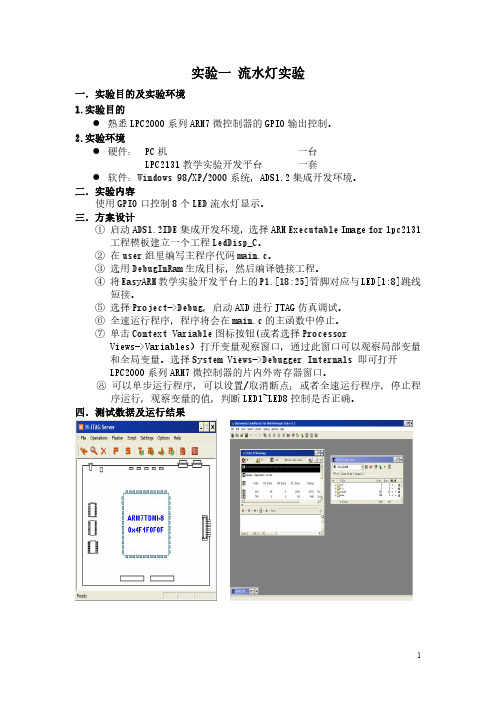

三.方案设计

① 启动 ADS1.2IDE 集成开发环境,选择 ARM Executable Image for lpc2131

中山大学嵌入式系统练习与参考答案

思考与练习1、 ARM7TDMI 中的T、D、M、I 的含义是什么?答:T 表示支持高密度Thumb 指令集;D 表示支持片上调试;M 表示增加了64 位乘法指令;I 表示带有EmbededICE 观察点硬件。

2、分别列举ARM 的处理器模式和状态。

答:ARM 处理器共有7 种运行模式。

分别是用户模式(User,usr),快速中断模式(FIQ ,fiq),外部中断模式(IRQ,irq),特权模式(Supervisor,svc),数据访问模式(Abort,abt),未定义指令中止模式(Undefined, und),系统模式(System,sys)。

ARM 处理器有两种状态,ARM 状态(执行32 位字方式的ARM 指令)和Thumb 状态(执行16 位半字方式的Thumb 指令)。

3、 PC 和LR 分别使用哪个寄存器?答:PC 使用了R15 寄存器。

LR 使用了R14 寄存器。

4、定义R0=0x12345678,假设使用存储指令将R0 的值放在0x4000 单元中。

如果存储器格式为大端格式可,请写出在执行加载指令将存储器0x4000 单元的内容取出存放到R2 寄存器操作后所得R2 的值。

如果存储器格式为小端格式,所得的R2 的值又为多少?低地址0x4000 单元的字节内容分别是多少?答:按大端模式将数据0x12345678 保存在地址0x4000 处,则数据高位存放在地址此时按大端模式从地址0x4000 处的1 字数据读取到R2 则其内容为0x12345678。

如果按小端模式将数据0x12345678 保存在地址0x4000 处,则数据低位存放在此时用按小端模式从地址0x4000 读取1 字数据到R2,将会得到0x12345678。

5、简单描述一下ARM7 的三级流水线,并说明其对程序设计的影响?答:ARM7TDMI 使用流水线来增加处理器指令流的速度。

这样可使几个操作同时进行,并使处理和存储器系统连续操作,能提供0.9MIPS/MHz 的指令执行速度。

LPC2000系列中断嵌套设计

LPC2000系列中断嵌套设计1.中断服务程序的编译器支持ARM编译器提供为编写FIQ和IRQ中断服务程序而设置的关键字,它们可以用于C函数前,所以可以C编写整个中断服务程序。

下面就是一个在Keil ARM编译器环境下的典型例子:void IRQ_Handler __irq{// Clear the source of the interrupt// Additional statements// Update the VIC by writing to VIC Vector Address Register}通过使用__irq关键字,编译器将为上面的函数添加下面的代码(1)在函数入口处,工作寄存器(包括ATPCS的敏感(易被破坏的)寄存器)被压栈;(2)在函数返回处,出栈上面保存的寄存器;(3)使用SUBS PC,R14,#4从中断服务程序中返回。

这条指令恢复了PC和CPSR。

注意:使用这个关键字的情况下,SPSR_irq没有被保存。

这就是使用关键字的方法处理中断不能实现嵌套的一个原因。

2.使用关键字来处理中断嵌套时出现的问题两个主要的原因都是跟LR_irq和SPSR_irq这两个寄存器有关。

如果一个中断服务程序重新使能中断,调用一个子程序,在子程序中发生了中断,这时,子程序的返回地址(保存在LR_irq中)将被破坏。

下面我们以一个例子来说明:void IRQ_Handler __irq{//reenable intertupts......foo();//地址A}当PC跳转到IRQ_Handler的时候(执行完0x18处的指令后),从ISR返回的地址已经写入LR_irq了。

假定它已经压栈(SP_irq)了。

现在,foo()函数被调用,LR_irq的值被foo调用处的下一条指令的地址所覆盖。

再进一步假设,在foo函数中运行的时候,一个更高优先级的中断发生了。

这时,LR_irq又被返回到foo函数被中断的地方的地址所覆盖,所以这就破坏了返回到IRQ_Handler的地址(即上面的函数中的" 地址A":译者注)。

LPC2000系列ARM

▪定时器0/1为两个独立的带可 编程32位预分频器的32位定时 器/计数器,具有捕获和匹配输 出功能;

▪具有4/8路10位ADC,可以设 置为多路循环采样模式。10位 转换时间最短为2.44us;

ARM7 局部总线 SRAM Flash 外部中断 TIMER0/1 ADC 通用I/O PWM0 实时时钟

ARM7TDMI-S CPU

系统功能

AHB总线

VIC

AHB To VPB

桥

EMC

I2C串行接口

SPI串行接口

UART0 & 1

CAN

看门狗定时器

系统控制 周立功单片机

第5章 目录

1.简介 2.引脚配置 3.存储器寻址 4.系统控制模块 5.存储器加速模块 6.外部存储器控制器 7.引脚连接模块 8. 向量中断控制器 9.GPIO

地址空间 0xFFFFFFFF

片外存储器 片内存储器

外部存储器 Boot Block

0x80000000 0x7FFFE000

内部SRAM

0x40000000

内部Flash 0x00000000周立功单片机

5.3 存储器寻址

• 不同芯片内部存储器分布

0x40001FFF 0x40000000 0x0003FFFF

▪AHB外设分配了2M字节的地 址范围,它位于4G字节ARM寻 址空间的最顶端。每个AHB外 设都分配了16KB的地址空间。

▪LPC2000系列微控制器的外设 功能(除中断控制器)都连接 到VPB总线。AHB到VPB的桥将 VPB总线与AHB总线相连。VPB 外设也分配了2M字节的地址范 围,从3.5GB地址点开始。每 个VPB外设都分配了16KB的地 址空间。

ARM体系结构——ARM简介

LPC2000系列CPU的核心是ARM7,由于其C语言编译器已经考虑到了许多复杂的因素,所以作为初学者无需成为一个专家就可以使用LPC2000。但是为了能够设计出可靠的应用系统和培养学习新技术的能力,作为初学者确实需要对CPU的运作机制及其独特的性能有更加深入的理解。

在连载的文章中,我们将着眼于ARM7内核,处理器状态与模式,内部寄存器,程序状态寄存器,异常、中断及其向量表和存储系统的学习,这是成为一个应用工程师必备的基础。

ARM1136JF-S就是为了进行快速浮点运算,而在ARM1136J-S增加了向量浮点单元。

9.Xscale

Xscale处理器将Intel处理器技术和ARM体系结构融为一体,致力于为手提式通信和消费电子类设备提供理想的解决方案。并提供全性能、高性价比、低功耗的解决方案,支持16位Thumb指令和集成数字信号处理(DSP)指令。

ARM926EJ-S发布于2000年,ARM9E系列为综合处理器,包括ARM926EJ-S和带有高速缓存处理器宏单元的ARM966E-S、ARM946E-S。该系列强化了数字信号处理(DSP)功能,可应用于需要DSP与微控制器结合使用的情况,将Thumb技术和DSP都扩展到ARM指令集中,并具有EmbeddedICE-RT逻辑(ARM的基于EmbeddedICE JTAG软件调试的增强版本),更好地适应了实时系统的开发需要。同时其内核在ARM9处理器内核的基础上使用了Jazelle增强技术,该技术支持一种新的Java操作状态,允许在硬件中执行Java字节码。

5.ARM7系列

ARM7TDMI是ARM公司1995年推出的第一个处理器内核,是目前用量最多的一个内核。ARM7系列包括ARM7TDMI、ARM7TDMI-S、带有高速缓存处理器宏单元的ARM720T和扩充了Jazelle的ARM7EJ-S。该系列处理器提供Thumb 16位压缩指令集和EmbeddedICE JTAG软件调试方式,适合应用于更大规模的SoC设计中。其中ARM720T高速缓存处理宏单元还提供8KB缓存、读缓冲和具有内存管理功能的高性能处理器,支持Linux和Windows CE 等操作系统。

ARM嵌入式系统试题及答案

一、嵌入式系统基本概念1、什么是嵌入式系统?有何特点?答:所谓嵌入式,实际上是“嵌入式计算机系统”,的简称,它是相对于通用计算机系统而言,注重于发展独立的单芯片技术。

嵌入式系统是“控制、监视或者辅助装置、机器和设备运行的装置”。

特点:(1)嵌入式系统是将先进的计算机技术,半导体技术以及电子技术与各行业的具体应用相结合的产物,这一点就决定了他必然是一个技术密集,资金密集,高度分散,不断创新的知识集成系统。

(2)系统内核小(3)专用性强(4)系统精简(5)系统软件要求(6)嵌入式软件开发要走向标准化,需要使用多任务的操作系统。

(7)嵌入式系统本身并不具备在其上进行进一步开发的能力。

2、举例在你的身边常见到的嵌入式系统产品,谈一谈你对“嵌入式系统”的初步理解。

答:产品有:洗衣机,空调,手机。

嵌入式系统就是内置小计算机系,可以对机器进行智能控制的系统。

3、嵌入式系统的3个基本特点?答:(1)专用性(2)嵌入型(3)计算机系统4、什么是嵌入式处理器,嵌入式处理器可以分为几大类?答:嵌入式处理机是嵌入式的核心,是控制,辅助系统运行的硬件单元。

分类:四大类(1)嵌入式微处理器(2)嵌入式微控制器(3)嵌入式DSP处理器(4)SoC片上系统5、广泛使用的三种类型的操作系统?答:多道批处理操作系统、分时操作系统以及实时操作系统。

6、列举常见的4种嵌入式操作系统?说明你对嵌入式操作系统的基本认识,嵌入式操作系统在嵌入式系统开发中的必要性。

答:嵌入式Linux、Win CE、VxWorks、μC/OS-II没有操作系统的计算机效率十分底下,把操作系统嵌入到计算机中,可以提高系统的可靠性,开发效率,缩短了开发周期。

二、ARM7体系结构7、什么是RISC?什么是CISC?答:RISC是精简指令集计算机的缩写。

CISC是复杂指令集计算机的缩写。

8、举出2个ARM公司当前应用比较多的ARM处理器核?答:ARM7系列、ARM9系列、ARM10系列、ARM11系列、intel的Xscale系列和MPCore系列。

第4章__LPC2000系列ARM硬件结构

保留,用户软件不要向这些位写入1。

复位值 0 0

0

未定义

UnIIR提供状态代码用于指示一个挂起中断的中断源和优先级。在访问 UnIIR过程中,中断被冻结。如果在访问UnIIR时产生了中断,该中断将被 记录,在下次访问UnIIR时可以读出,避免了中断的丢失。

4.14 UART(0、1)

• UART中断示意图

复位值 0 0 0

0 未定义

UnIER可以控制UARTn的4个中断源。其中RBR中断使能包括两个中断, 一个是接收数据可用(RDA)中断,一个是接收超时中断(CTI)。稍后将 对各中断源作详细介绍。

4.14 UART(0、1)

• 中断标识寄存器

UnIIR 0

3:1

7:3

描述

中断挂起。1:没有挂起的中断;0:至少有一个中断被挂起。

4.14 UART(0、1)

• 中断源说明

RLS中断:该中断为最高优先级。它在UARTn发生 下面的错误时产生中断:

1、溢出错误(OE) 2、奇偶错误(PE) 3、帧错误(FE) 4、间隔中断(BI) 通过查看UnLSR[4:1]可以了解到产生该中断的错误 条件。读取UnLSR时清除该中断;

• 中断源说明

4.14 UART(0、1)

• 中断使能寄存器

UnIER 0 1 2

3 7:4

描述 RBR中断使能。1:使能RDA中断;0:禁止RDA中断。 THRE中断使能。1:使能THRE中断;0:禁止THRE中断。 Rx线状态中断使能。1:使能Rx线状态中断;0:禁止Rx线状态中断; 该中断状态可从UnLSR[4:1]读出。 Modem中断使能。 1:禁止Modem中断;0:禁止Rx线状态中断; 该中断状态可从U1MSR[3:0]读取。注:只有UART1具有。 保留,用户软件不要向这些位写入1。

第4章 LPC2000系列ARM硬件结构

当T0TC = T0MR0时,若T0MCR[0] = 0,则匹配中断禁止; 当T0TC = T0MR0时,若T0MCR[0] = 1,则匹配中断使能。

T0MCR[0] = 1 定时器0计数值TC = 定时器0匹配值MR0 T0MCR[3]

0

1

计数器复位

0

5

匹配功能

匹配功能

匹配寄存器0(MR0) 匹配寄存器1(MR1) 匹配寄存器2(MR2) 匹配寄存器3(MR3) 匹配控制寄存器(MCR) MAT[3:0] 外部匹配寄存器(EMR)

描述 访问 复位值

比 较 器

定 时 器 计 数 值

名称

MCR

MR0 MR1 MR2 MR3 EMR

读写

读写 读写 读写 读写 读写

0

0 0 0 0 0

6

匹配功能寄存器描述-匹配控制寄存器

匹配功能

匹配控制寄存器 用于控制在发生匹配 时定时器所执行的操 作。

位 0 功能 中断(MR0)

匹配寄存器0(MR0) 匹配寄存器1(MR1) 匹配寄存器2(MR2) 匹配寄存器3(MR3) 匹配控制寄存器(MCR) MAT[3:0] 外部匹配寄存器(EMR)

向量IRQ通道15

定时器1

通道5

FIQ

非向量IRQ通道

19

定时器中断

匹配中断 LPC2000系列ARM定时器计数溢出时不会产生中断, 但是匹配时可以产生中断。每个定时器都具有4个匹配寄 存器(MR0~MR3),可以用来存放匹配值。 当计数值 = 匹配值时,产生匹配中断。

20

定时器中断

匹配中断

1

4.11 定时器0、1

ARM嵌入式系统基础教程习题答案__周立功.

第一章思虑与练习1、举出 3 个书籍中未提到的嵌入式系统的例子。

答 :红绿灯控制 ,数字空调 ,机顶盒2、什么叫嵌入式系统嵌入式系统:以应用为中心、以计算机技术为基础、软件硬件可裁剪、适应应用系统对功能、靠谱性、成本、体积、功耗严格要求的专用计算机系统。

3、什么叫嵌入式办理器?嵌入式办理器分为哪几类?嵌入式办理器是为达成特别的应用而设计的特别目的的办理器。

嵌入式微办理器 (Embedded Microprocessor Unit, EMPU) 嵌入式微控制器 (Microcontroller Unit, MCU)嵌入式 DSP办理器(Embedded Digital Signal Processor, EDSP)嵌入式片上系统(System On Chip)4、什么是嵌入式操作系统?为何要使用嵌入式操作系统?是一段在嵌入式系统启动后第一履行的背景程序,第一,嵌入式及时操作系统提升了系统的靠谱性。

其次,提升了开发效率,缩短了开发周期。

再次,嵌入式及时操作系统充散发挥了32 位 CPU的多任务潜力。

第二章1、嵌入式系统项目开发的生命周期分哪几个阶段?各自的详细任务是什么?项目的生命周期一般分为辨别需求、提出解决方案、履行项目和结束项目 4 个阶段。

辨别需求阶段的主要任务是确认需求,剖析投资利润比,研究项目的可行性,剖析厂商所应具备的条件。

提出解决方案阶段由各厂商向客户提交标书、介绍解决方案。

履行项目阶段细化目标,拟订工作计划,协调人力和其余资源;按期监控进展,剖析项目误差,采纳必需举措以实现目标。

结束项目阶段主要包含移交工作成就,帮助客户实现商务目标;系统交接给保护人员;结清各样款项。

2、为何要进行风险剖析?嵌入式项目主要有哪些方面的风险?在一个项目中,有很多的要素会影响到项目进行,所以在项目进行的早期,在客户和开发团队都还未投入大批资源以前,风险的评估能够用来预估项目进行可能会遭受的难题。

需求风险;时间风险;资秋风险;项目管理风险3、何谓系统规范?拟订系统规范的目的是什么?规格拟订阶段的目的在于将客户的需求,由模糊的描绘,变换成存心义的量化数据。

周立功_第5章 LPC2000系列ARM硬件结构(5-8)

这些引脚与P1、P2和P3口GPIO功能复用,所 以在使用外部总线前首先要正确设置PINSEL2寄存 器。可以在硬件上对引脚BOOT1:0设定,复位时 微处理器自动初始化PINSEL2。或者在软件上字节 初始化PINSEL2,这只适用于片内FLASH引导程序 运行的系统中。

周立功单片机

外部存储器总线接口描述

配置寄存器 BCFG0 BCFG1 BCFG2 BCFG3

周立功单片机

外部存储器总线接口描述

接口引脚描述:

引脚名 D[31:0] A[23:0] OE BLS WE CS[3:0] 类型 输入/输出 输出 输出 输出 输出 输出 引脚描述 外部存储器数据线 外部存储器地址线 输出使能信号,低有效 字节定位选择信号,低有效 写使能信号,低有效 芯片选择信号,低有效

周立功单片机

5.6 外部存储器控制器(EMC)

相关寄存器

存储器组配置寄存器0~3(BCFG0~3):

位 功能 23:16 保留 15:11 WST2 10 RBLE 9:5 WST1 4 保留 3:0 IDCY

外部存储器读访问波形(WST1=0):

XCLK CS OE WE/BLS Addr Data

ARM局部总线

Flash 存储器组0 总线 接口

预取指缓存 分支跟踪缓存

2×128位

Flash 存储器组1

预取指缓存 分支跟踪缓存

2×128位

当程序向后跳转时,尝试从分 支跟踪缓存区取指。 如果程序跳转出缓存的范围, CPU将要停止,等待若干个周 期,直到正确的指令从Flash中 被读出。

数据缓存区 选择

周立功单片机

外部存储器控制器概述

外部静态存储器控制器 是一个AHB总线上的从模 块。 只有LPC2200系列的微 控制器含有EMC模块 。 EMC模块为AHB系统总 线和外部存储器件之间提 供了一个接口。

LPC2000系列ARM硬件结构

U0FCR

CPU内核通过VPB接口对UART0的寄存器进行读写访问

2.发送数据的通道

周立功单片机

• UART0内部结构示意图

U0IIR

U0IER

U0DLM U0DLL

与CPU内 核相连

VPB 接口

U0THR

TxD0

U0TSR

U0LCR U0RBR

U0LSR U0RSR

RxD0

U0FCR

接收缓存 接收移位寄存器

在需要将多位数据同时输出到某几个IO口线时,通常使用 IOxSET和IOxCLR来实现,在某些情况下也可以使用IOxPIN寄存 器实现。后者可以在多个IO口上直接输出0和1电平。

本例将8位无符号整数变量Data的值输出到P0.0~P0.7。

使用IOxSET和IOxCLR实现:

#define DataBus 0xFF

周立功单片机

• GPIO相关寄存器描述——IOxCLR

PINSELx

IOxSET out

1

in

0

IOxDIR

IOxCLR

IOxPIN

IOxCLR

描述

31 : 0 输出清零。IOxCLR[0]对应于Px.0 … IOxCLR[31]对应于Px.31引脚

复位值 未定义

当引脚设置为GPIO输出模式时,可使用该寄存器从引脚输出低电平。 向某位写入1使对应引脚输出低电平。写入0无效。

IOxSET

描述

31 : 0 输出置位。IOxSET[0]对应于Px.0 … IOxPIN[31]对应于Px.31引脚

复位值 未定义

当引脚设置为GPIO输出模式时,可使用该寄存器从引脚输出高电平。 向某位写入1使对应引脚输出高电平。写入0无效。

LPC2000系列ARM-CAN控制器驱动程序的使用指南

1.2 管脚描述...........................................................................................................................4

第 2 章 CAN 控制器驱动程序的编写 ...................................................................................28

2.1 驱动程序的结构.............................................................................................................28

表13can验收过滤器和中央can寄存器名称afmrsffsasffgrpsaeffsaeffgrpsaendoftableluterradluterrcantxsrcanrxsrcanmsr描述访问rwrwrwrwrwrwrororororo复位值100000000x003f3f0000地址验收过滤器寄存器标准帧单个起始地址寄存器标准帧组起始地址寄存器扩展帧起始地址寄存器扩展帧组起始地址寄存器af表格终止寄存器lut错误地址寄存器lut错误寄存器can集中发送状态寄存器can集中接受状态寄存器can集中其他状态寄存器0xe003c0000xe003c0040xe003c0080xe003c00c0xe003c0100xe003c0140xe003c0180xe003c01c0xe00400000xe00400040xe0040008表14can1can2can3和can4控制器寄存器映射名称描述访问can1地址amp

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

▪在LPC2119/2129/2290/2292 等芯片中包含CAN总线接口;

▪看门狗定时器带有内部分频器, 可以方便设置溢出时间,在软 件使能看门狗后只有复位可以 禁止(具有调试模式);

器件型号 引脚数 LPC2114 64 LPC2124 64 LPC2210 144 LPC2212 144 LPC2214 144 LPC2119 64 LPC2129 64 LPC2194 64 LPC2290 144 LPC2292 144 LPC2294 144 LPC2131 64 LPC2132 64 LPC2134 64 LPC2136 64 LPC2138 64

第5章 LPC2000系列ARM 硬件结构

周立功单片机

第5章 目录

1.简介 2.引脚配置 3.存储器寻址 4.系统控制模块 5.存储器加速模块 6.外部存储器控制器 7.引脚连接模块 8. 向量中断控制器 9.GPIO

10.UART0 11.UART1 12.I2C接口 13.SPI接口 14.定时器0/1 15.脉宽调制器(PWM) 16.A/D转换器 17.实时时钟 18.看门狗

ARM7 局部总线 SRAM Flash 外部中断 TIMER0/1 ADC 通用I/O PWM0 实时时钟

ARM7TDMI-S CPU

系统功能

AHB总线

VIC

AHB To VPB

桥

EMC

I2C串行接口

SPI串行接口

UART0 & 1

CAN

看门狗定时器

系统控制 周立功单片机

• 芯片内部各单元简介

▪具有两个完全独立的SPI控制 器,遵循SPI规范,可配置为SPI 主机或从机;

片内RAM 16KB 16KB 16KB 16KB 16KB 16KB 16KB 16KB 16KB 16KB 16KB 8KB 16KB 16KB 16KB 32KB

片内Flash 128KB 256KB - 128KB 256KB 128KB 256KB 256KB - 256KB 256KB 32KB 64KB 128KB 256KB 512KB

▪外部中断有4路多引脚输入, 可用于CPU掉电唤醒;

▪定时器0/1为两个独立的带可 编程32位预分频器的32位定时 器/计数器,具有捕获和匹配输 出功能;

▪具有4/8路10位ADC,可以设 置为多路循环采样模式。10位 转换时间最短为2.44us;

ARM7 局部总线 SRAM Flash 外部中断 TIMER0/1 ADC 通用I/O PWM0 实时时钟

▪系统功能包括维持芯片工作的 一些基本功能,如系统时钟、 复位等;

▪向量中断控制器(VIC)可以 减少中断的响应时间,最多可 以管理32各中断请求;

▪外部存储器控制器(EMC)支 持4个BANK的外部SRAM或 Flash,每个BANK最多16MB;

▪I2C串行接口为标准的I2C总线 接口,支持最高速度400kb;

ARM7 局部总线 SRAM Flash 外部中断 TIMER0/1 ADC 通用I/O PWM0 实时时钟

ARM7TDMI-S CPU

系统功能

AHB总线

VIC

AHB To VPB

桥

EMC

I2C串行接口

SPI串行接口

UART0 & 1

CAN

看门狗定时器

系统控制 周立功单片机

• 芯片内部各单元简介

▪内部存储器包括无等待SRAM 和Flash;

周立功单片机

5.1 简介

• LPC2000系列微控制器概述

LPC2000系列微控制器基于ARM7TDMI-S CPU内核。支持ARM和Thumb指令集,芯片内集 成丰富外设,而且具有非常低的功率消耗。使该 系列微控制器特别适用于工业控制、医疗系统、 访问控制和POS机等场合。

周立功单片机

• LPC2000系列器件信息

ARM7 局部总线 SRAM Flash 外部中断 TIMER0/1 ADC 通用I/O PWM0 实时时钟

ARM7TDMI-S CPU

系统功能

AHB总线

VIC

AHB To VPB

桥

EMC

I2C串行接口

SPI串行接口

UART0 &a制 周立功单片机

• 芯片内部各单元简介

▪系统控制模块包括一些与其它 外设无关的功能,如功率控制 等;

▪AHB外设分配了2M字节的地 址范围,它位于4G字节ARM寻 址空间的最顶端。每个AHB外 设都分配了16KB的地址空间。

▪LPC2000系列微控制器的外设 功能(除中断控制器)都连接 到VPB总线。AHB到VPB的桥将 VPB总线与AHB总线相连。VPB 外设也分配了2M字节的地址范 围,从3.5GB地址点开始。每 个VPB外设都分配了16KB的地 址空间。

ARM7 局部总线 SRAM Flash 外部中断 TIMER0/1 ADC 通用I/O PWM0 实时时钟

ARM7TDMI-S CPU

系统功能

AHB总线

VIC

AHB To VPB

桥

EMC

I2C串行接口

SPI串行接口

UART0 & 1

CAN

看门狗定时器

系统控制 周立功单片机

• 芯片内部框图

▪LPC2000系列微控制器将 ARM7TDMI-S配置为小端模式 (Little-endian)。

周立功单片机

第5章 目录

1.简介 2.引脚配置 3.存储器寻址 4.系统控制模块 5.存储器加速模块 6.外部存储器控制器 7.引脚连接模块 8. 向量中断控制器 9.GPIO

10.UART0 11.UART1 12.I2C接口 13.SPI接口 14.定时器0/1 15.脉宽调制器(PWM) 16.A/D转换器 17.实时时钟 18.看门狗

10位AD通道数 4 4 8 8 8 4 4 4 8 8 8 8 8

双8路 双8路 双8路

CAN控制器 备注

-

-

-

-

-

带外部

-

存储器

-

接口

2

-

2

-

4

-

2

带外部

2

存储器

4

接口

-

-

-

-

带1路

-

DAC

-

周立功单片机

• 芯片内部框图

LPC2000系列微控制器包含四 大部分: ▪ARM7TDMI-S CPU ▪ARM7局部总线及相关部件 ▪AHB高性能总线及相关部件 ▪VLSI外设总线及相关部件