DP1Users_Manual_cs

NVIDIA DOCA DPA执行单元管理工具用户指南说明书

NVIDIA DOCA DPA Execution Unit Management ToolUser GuideTable of ContentsChapter 1. Introduction (1)Chapter 2. Execution Unit Objects (3)Chapter 3. dpaeumgmt Commands (4)3.1. General Commands (4)3.2. Execution Unit Group Commands (4)3.2.1. EU Group Command Flags and Arguments (4)3.2.2. Info EU Group (5)3.2.3. Create EU Group (5)3.2.4. Destroy EU Group (6)3.2.5. Query EU Group (6)3.2.6. Apply EU Group (6)3.3. EU Partition Commands (7)3.3.1. EU Partition Command Flags and Arguments (7)3.3.2. Info EU Partition (7)3.3.3. Create EU Partition (8)3.3.4. Destroy EU Partition (8)3.3.5. Query EU Partition (8)Chapter 4. vHCAs and Partitions (9)Chapter 5. Known Limitations (10)Chapter 1.IntroductionThis table introduces important terms for understanding this document:The DPA EU management tool can run either on the host machine or on the target DPU and allows users to manage the DPA's EUs which are the basic resource of the DPA. TheIntroductiontool enables the resource control of EUs to optimize computation resources usage of the DPA before using DOCA FlexIO SDK API.Without EU allocation, a DPA software thread would lack access to the hardware pipeline/CPU time resource, and consequently not be able to execute. dpaeumgmt serves the following main usages:‣Running a DPA software thread with strict affinity on a DPA EU (i.e., running a DPA thread using only the specific preselected EU). For this purpose, dpaeumgmt provides an option to query the maximum EU ID allowed to use.‣Allowing a DPA software thread to run over a DPA EU from a group of EUs:‣Once a EU group is created, it is allocated a subset of EUs.‣dpaeumgmt provides an ID to the created group which can be used to run DPA applications with group affinity where the affinity ID would be the same as thatgroup's ID.‣EU partition management - the ability to manage EU partitions.When the software stack wishes to run a DPA thread with group affinity type, one of the available EUs from the group's collection is used for the execution.Note: A DPA thread may execute if and only if there is an available EU for it.Chapter 2.Execution Unit ObjectsUpon boot, a default EU partition is automatically created. The default EU partition possesses all the system's EUs. The DPA partition manager function is the only function that belongs to it and can therefore control the entire resources of the system.When running a DPA thread with none affinity, the EU chosen for the DPA thread to run with comes from the partition's pool of EUs. Namely, from the EUs belonging only to the DPA device's current partition which were not assigned to any EU groups (on the current partition). If the aforementioned group of EUs (i.e., the partition's default EU group) is empty, the DPA thread would fail to run with none affinity.Chapter 3.dpaeumgmt Commandsdpaeumgmt enables users to create, destroy, and query EU objects.Note: dpaeumgmt tool must run with root privileges and users must execute sudo mststart before using it.Top-level dpaeumgmt command syntax:Usage: dpaeumgmt {help|version|eu_group|partition}Type "./dpaeumgmt help"for detailed help3.1. General Commands‣Print basic usage information for the tool:dpaeumgmt -h‣Print a detailed help menu of the tool's commands:dpaeumgmt help‣Print version information:dpaeumgmt version3.2. Execution Unit Group Commands The commands listed in the following subsections are used to configure EU groups. 3.2.1. EU Group Command Flags and ArgumentsThe following table lists the flags relevant for eu_group commands. Arguments for the flags must be used within quotes (if more than one) and without extra spaces.3.2.2. Info EU GroupPrint information on the relevant DPA resources for the EU groups:dpaeumgmt eu_group info --dpa_device <device>Example:$ sudo ./dpaeumgmt eu_group info -d mlx5_0Max number of DPA EU groups: 15Max number of DPA EUs in one DPA EU group: 190Max DPA EU number available to use: 190Max EU group name length is 15 chars3.2.3. Create EU GroupCreate an EU group with the specified name on the provided device's partition. The EUs indicated by the range are taken from the DPA device's EU partition.dpaeumgmt eu_group create --dpa_device <device> --name_group <name> --range_eus<range>Example:$ sudo ./dpaeumgmt eu_group create -d mlx5_0 -n "HG hello world1" -r "6-8,16,55,70" Group created successfully-EU group ID: 1EU group name: HG hello worldMember EUs are: 6,7,8,16,55,70Note: After successfully creating an EU group, users can run a DPA thread using groupaffinity with the affinity type set to the group's ID.3.2.4. Destroy EU GroupDestroy a EU group that exists on the device's partition with either the provided group name or ID.dpaeumgmt eu_group destroy --dpa_device <device> [--name_group <name> | --id_group <id>]Example:$ sudo ./dpaeumgmt eu_group destroy -d mlx5_0 -g 1Group with group id: 1, was destroyed successfully3.2.5. Query EU GroupQuery EU groups residing on the provided device's partition. If one of the optional parameters is used, the command only queries the specific group and prints it if it exists: dpaeumgmt eu_group query --dpa_device <device> [--name_group <name> | --id_group<id>]Example:$ sudo ./dpaeumgmt eu_group query -d mlx5_01) EU group ID: 1EU group name: HG hello worldMember EUs are: 6,7,8,16,55,70In total there are 1 EU groups configured.More options:$ sudo ./dpaeumgmt eu_group query -d mlx5_0 -n "HG hello world"$ sudo ./dpaeumgmt eu_group query -d mlx5_0 -g 13.2.6. Apply EU GroupApply the EU groups provided in the file on the device's partition:dpaeumgmt eu_group apply --dpa_device <device> --file_groups <file>File format example:{"eu_groups": [{ "name": "hg1", "range": "178-180"},{ "name": "hg2", "range": "2-10"}]}Note: The command removes all the previous EU groups defined on the EU partition thatthe DPA device belongs to and applies the ones from the file.Example:$ sudo ./dpaeumgmt eu_group apply -d mlx5_0 --file_groups example.json1) EU group ID: 1EU group name: hg1Member EUs are: 178,179,1801) EU group ID: 2EU group name: hg2Member EUs are: 2,3,4,5,6,7,8,9,10In total there are 2 EU groups configured.3.3. EU Partition CommandsThe commands listed in the following subsections are used to configure EU partitions.3.3.1. EU Partition Command Flags andArgumentsThe following table lists the flags relevant for EU partition commands. Arguments for the flags must be used within quotes (if more than one) and without extra spaces.3.3.2. Info EU PartitionPrint the relevant DPA resources of the EU partitions:dpaeumgmt partition info --dpa_device <device>Example:$ sudo ./dpaeumgmt partition info -d mlx5_0Max number of DPA EU partitions: 15Max number of VHCAs associated with a single partition: 32Max number of DPA EU groups: 15Note- an allocation of a partition consumes from the number of DPA EU *groups*available to createMax DPA EU number available to use: 1903.3.3. Create EU PartitionCreate an EU partition on the DPA device:dpaeumgmt partition create --dpa_device <device> --vhca_list <id_list> --range_eus <range> --max_num_eu_group <max_num>Example:$ sudo ./dpaeumgmt partition create -d mlx5_0 -v 1 -r 10-20 -m 2Partition created successfully-EU Partition ID: 1Maximal number of groups: 2The partition has a total of 1 associated VHCA IDs, namely: 1Partition's member EUs are: 10,11,12,13,14,15,16,17,18,19,203.3.4. Destroy EU PartitionDestroy an EU partition that exists on the device's partition:dpaeumgmt partition destroy --dpa_device <device> --id_partition <id> Example:$ sudo ./dpaeumgmt partition destroy -d mlx5_0 -p 1Partition with partition id: 1, was destroyed successfully3.3.5. Query EU PartitionQuery EU partitions that reside on the provided device's partition and print out the partition if it exists:dpaeumgmt partition query --dpa_device <device> [--id_partition <id>] Example:$ sudo ./dpaeumgmt partition query -d mlx5_0 -p 1EU Partition ID: 1Maximal number of groups: 2The partition has a total of 1 associated VHCA IDs, namely: 1Partition's member EUs are: 10,11,12,13,14,15,16,17,18,19,20More options:$ sudo ./dpaeumgmt partition query -d mlx5_0Chapter 4.vHCAs and PartitionsThe following diagram illustrates the ownership and control of a partition by a vHCA and also which vHCAs have claim to (i.e., can use) a partition.Chapter 5.Known Limitations‣Currently, dpaeumgmt is only supported on the DPU not the host‣dpaeumgmt should run before creating a DPA process so all resources are configured ahead of time‣Running the tool over a device with an existing DPA process results in failure‣The EU group name assigned by the user must be unique for every EU group on a specific partition or the EU group create command fails‣The creation of an EU partition consumes from the number of EU groups allowed on the vHCA's partition it is created on:‣ 1 group for the partition itself due to a default group created for each partition ‣<max_num> of groups which is the user's input provided upon partition creation ‣Creating groups or running DPA threads in general (with any affinity) on interfaces other than ECPF, requires a configuration of a valid partition for the specific vHCA ‣Only the default partition is exposed to the real EU numbers, all other partitions the user creates use virtual EUs‣For example, if a user creates a partition with the range of EUs 20-40, querying the partition info from one of its virtual HCAs (vHCAs) would display EUs from0-20. Therefore, the EU whose real number is 39 in this example would correspond to the virtual EU number 19.‣Group IDs on a non-default partition are virtual.‣Different partitions can have completely distinct groups, even if they have the same ID.‣The affinity ID parameter, specified on the FlexIO API, can distinguish between the groups according to the vHCA and application it is running on.‣vHCA ID overlap is not allowed on EU partitions‣It is not possible to query vHCA IDs with dpaeumgmt, these are assumed to be known by the user beforehand‣Partition destruction fails if there are EU objects that exist on that partition‣It is not possible to know which EU has been chosen to run on‣Every vHCA sees the partition it belongs to, and its resources, as the entire world. It only sees:Known Limitations‣Groups and partitions it created‣The number of EUs it was given‣The max_num_eu_group of the partition it belongs to‣No guarantee regarding EU group ID that will be given on group creation‣The default groups (of every partition) cannot be managed by the user‣The EU numbers available are between 0 and the max DPA EU number available to use minus 1 (the upper limit can be queried using the info command specified above)‣dpaeumgmt does not support virtual functions (VFs)‣It is not possible to create partitions on other vHCAs other than the DPA partition manager function‣There are at most 16 hardware EU group entitiesNoticeThis document is provided for information purposes only and shall not be regarded as a warranty of a certain functionality, condition, or quality of a product. NVIDIA Corporation nor any of its direct or indirect subsidiaries and affiliates (collectively: “NVIDIA”) make no representations or warranties, expressed or implied, as to the accuracy or completeness of the information contained in this document and assume no responsibility for any errors contained herein. NVIDIA shall have no liability for the consequences or use of such information or for any infringement of patents or other rights of third parties that may result from its use. This document is not a commitment to develop, release, or deliver any Material (defined below), code, or functionality.NVIDIA reserves the right to make corrections, modifications, enhancements, improvements, and any other changes to this document, at any time without notice.Customer should obtain the latest relevant information before placing orders and should verify that such information is current and complete.NVIDIA products are sold subject to the NVIDIA standard terms and conditions of sale supplied at the time of order acknowledgement, unless otherwise agreed in an individual sales agreement signed by authorized representatives of NVIDIA and customer (“Terms of Sale”). NVIDIA hereby expressly objects to applying any customer general terms and conditions with regards to the purchase of the NVIDIA product referenced in this document. No contractual obligations are formed either directly or indirectly by this document.NVIDIA products are not designed, authorized, or warranted to be suitable for use in medical, military, aircraft, space, or life support equipment, nor in applications where failure or malfunction of the NVIDIA product can reasonably be expected to result in personal injury, death, or property or environmental damage. NVIDIA accepts no liability for inclusion and/or use of NVIDIA products in such equipment or applications and therefore such inclusion and/or use is at customer’s own risk.NVIDIA makes no representation or warranty that products based on this document will be suitable for any specified use. Testing of all parameters of each product is not necessarily performed by NVIDIA. It is customer’s sole responsibility to evaluate and determine the applicability of any information contained in this document, ensure the product is suitable and fit for the application planned by customer, and perform the necessary testing for the application in order to avoid a default of the application or the product. Weaknesses in customer’s product designs may affect the quality and reliability of the NVIDIA product and may result in additional or different conditions and/or requirements beyond those contained in this document. NVIDIA accepts no liability related to any default, damage, costs, or problem which may be based on or attributable to: (i) the use of the NVIDIA product in any manner that is contrary to this document or (ii) customer product designs.No license, either expressed or implied, is granted under any NVIDIA patent right, copyright, or other NVIDIA intellectual property right under this document. Information published by NVIDIA regarding third-party products or services does not constitute a license from NVIDIA to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property rights of the third party, or a license from NVIDIA under the patents or other intellectual property rights of NVIDIA.Reproduction of information in this document is permissible only if approved in advance by NVIDIA in writing, reproduced without alteration and in full compliance with all applicable export laws and regulations, and accompanied by all associated conditions, limitations, and notices.THIS DOCUMENT AND ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS, AND OTHER DOCUMENTS (TOGETHER AND SEPARATELY, “MATERIALS”) ARE BEING PROVIDED “AS IS.” NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY, OR OTHERWISE WITH RESPECT TO THE MATERIALS, AND EXPRESSLY DISCLAIMS ALL IMPLIED WARRANTIES OF NONINFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE. TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL NVIDIA BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF NVIDIA HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Notwithstanding any damages that customer might incur for any reason whatsoever, NVIDIA’s aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms of Sale for the product.TrademarksNVIDIA, the NVIDIA logo, and Mellanox are trademarks and/or registered trademarks of Mellanox Technologies Ltd. and/or NVIDIA Corporation in the U.S. and in other countries. The registered trademark Linux® is used pursuant to a sublicense from the Linux Foundation, the exclusive licensee of Linus Torvalds, owner of the mark on a world¬wide basis. Other company and product names may be trademarks of the respective companies with which they are associated.Copyright© 2023 NVIDIA Corporation & affiliates. All rights reserved.NVIDIA Corporation | 2788 San Tomas Expressway, Santa Clara, CA 95051。

DP安装手册

HP Data Protector 安装和使用手册目录1安装 Data Protector (2)2 DP软件图形界面中各部分的说明 (3)2.1 添加磁带库 (3)2.2 Clients模块 (3)2.3 Users模块 (5)2.4 Devices & Media模块 (6)2.5 Backup模块 (8)2.5.1 文件系统备份 (8)2.5.2 oracle的备份 (11)3 备份策略的几点说明: (13)1安装 Data Protector插入Windows 安装DVD-ROM,然后运行\i386\setup.exe 启动此向导。

5. 选择Cell Manager,然后按照此向导完成各个步骤(在各个步骤中都使用默认值)。

6. 在帐户信息(Account information) 窗口中,输入您在步骤3 中创建的用户帐户的用户名和密码2DP软件图形界面中各部分的说明2.1 添加磁带库点击“add Device ”NEXT直到添加完成2.2 Clients模块本章节将介绍DP图形界面中各部分的功能,在安装配置过程中也是按照加Clients →加Users →建Media Pool、Devices →定制Backup脚本的顺序来操作的。

DP软件安装后,Cell Manager将自动成为Clients的一员,缺省将安装Disk Agent,Media Agent和User Interface,同时它也将作为一个Installation Server。

添加Client缺省采用的是远程安装的方式,只要在Client上按右键→Add Clients →写入主机名或IP地址,就将看到下图,选择要安装的Components,系统将自动传安装文件到远程主机,并自动安装。

当然也可以采用手工安装,即在Client上手工安装Agent再从Cell Manager中import进来。

2.3 Users模块DP缺省有三种组模式:admin,operator,user,每个组的权限如下示意图。

浪潮Cinder主机插件用户手册说明书

浪潮存储平台主机插件用户手册文档版本发布日期适用版本尊敬的用户:衷心感谢您选用浪潮存储!浪潮存储秉承“云存智用运筹新数据”的新存储之道,致力于为您提供符合新数据时代需求的存储产品和解决方案。

本手册用于帮助您更详细地了解和便捷地使用本存储,涉及的截图仅为示例,最终界面请以实际设备显示的界面为准。

由于产品版本升级或其他原因,本手册内容会不定期进行更新,如有变动恕不另行通知。

除非另有约定,本手册仅作为使用指导,本手册中的所有陈述、信息和建议不构成任何明示或暗示的担保。

浪潮拥有本手册的版权,保留随时修改本手册的权利。

未经浪潮许可,任何单位和个人不得以任何形式复制本手册的内容。

如果您对本手册有任何疑问或建议,请向浪潮电子信息产业股份有限公司垂询。

技术服务电话:4008600011地址:中国济南市浪潮路1036号浪潮电子信息产业股份有限公司邮编:250101在您正式使用本存储之前,请先阅读以下声明。

只有您阅读并且同意以下声明后,方可正式开始使用本存储。

如果您对以下声明有任何疑问,请和您的供货商联系或直接与我们联系。

如您在开始使用本系统前未就以下声明向我们提出疑问,则默认您已经同意了以下声明。

1.请不要自行拆卸本存储的机箱及机箱内任何硬件设备。

在本存储出现任何硬件故障或您希望对硬件进行任何升级时,请您将机器的详细硬件配置反映给我们的客户服务中心。

2.请不要将本存储的设备与任何其他型号的相应设备混用。

本存储的内存、CPU、CPU散热片、风扇、硬盘托架、硬盘等都是特殊规格的。

3.在使用本存储时遇到任何软件问题,请您首先和相应软件的提供商联系。

由提供商和我们联系,以方便我们共同沟通和解决您遇到的问题。

对于数据库、网络管理软件或其他网络产品的安装、运行问题,我们尤其希望您能够这样处理。

4.上架安装本存储前,请先仔细阅读相关产品手册中的快速安装指南。

我们致力于产品功能和性能的持续提升,部分功能及操作与手册描述可能会有所差异,但不会影响使用。

Fujitsu STYLISTIC Q7311 商品说明书

Data SheetFujitsu STYLISTIC Q7311Tablet Mobility Meets Notebook ProductivityThe FUJITSU Tablet STYLISTIC Q7311 is a highly durable and secure 2-in-1 detachable that meets the demands of today’s mobile professionals. Its 33.8 cm (13.3-inch) FHD anti-glare display comes with pen and touch support. The latest 11th generation Intel® Core™ i7 vPro® processor technology and Intel® Thunderbolt™ 4 ensure excellent performance, even when you’re on the go.Combined tablet mobility and notebook productivity in one device - whereever you areThe robust IP42 compliant housing with reinforced corners and port caps protects your device from damages, even outside the office.Highly durable IP42 compliant housing with reinforced cornersPort caps that protect the interfaces like the new Intel® Thunderbolt™ 4 from water spills Optional backlit keyboard dock with LAN and charging port Optional TPU cover for more robustness Always connected and instantly readyConvenience at workSign documents legally secure. The pen is automatically charged within seconds when stored in its pen garage, that protects it also from being lost. Ready whenever you need it. 33.8 cm (13.3-inch) Full HD anti-glare touch display Supporting pen with 4K pressure levelsPen garage with inductive charging functionLean, agile and secureMore freedom to work safely from anywhere at anytime without compromises in security and data protection – integrated IR Cam with Windows Hello support, fingerprint sensor and Smartcard reader protect your device like a mansion.Weight starting at 800 grams, the device offers you ultimate portability Fingerprint sensor & IR Camera supporting Windows Hello Smartcard readerKensington lock supportUp to 10 hours battery runtimeIntel® Iris® Xe GraphicsComponentsBase unit STYLISTIC Q7311Operating systemsOperating system pre-installed Windows 11 Pro. Fujitsu recommends Windows 11 Pro for business.Windows 11 HomeWindows 10 Pro. Fujitsu recommends Windows 11 Pro for business.Operating system compatible FREE Upgrade to Windows 11**Upgrade timing may vary by device. Features and app availability may vary by region. Certain features requirespecific hardware (see aka.ms/windows11-spec).Operating system notes Internet connectivityWindows 10 Support: After the end of the product life Fujitsu will continue to test and support all upcoming Window10 releases for a period of maximum 5 years – depending on the available extension of hardware services throughFujitsu Warranty top ups. For details please see “Fujitsu Service Statement for Windows 10 Semi-Annual-ChannelSupport” at .Processor Intel® Core™ i7-1185G7 processor (4 Cores / 8 Threads)Intel® Core™ i5-1145G7 processor (4 Cores / 8 Threads)Intel® Core™ i5-1135G7 processor (4 Cores / 8 Threads) ** Processor only for retail, SMB, education and governmentHard disk drives (internal)SSD PCIe, SSD 512GB Value PCIe G3 M.2 FDE, SEDSSD PCIe, SSD 512GB MS PCIe G3 M.2 FDE, SEDSSD PCIe, SSD 256GB Value PCIe G3 M.2 FDE, SEDSSD PCIe, SSD 1TB Value PCIe G3 M.2 FDE, SEDSSD PCIe, SSD 1TB MS PCIe G3 M.2 FDE, SEDHard disk notes One Gigabyte equals one billion bytes, when referring to hard disk drive capacity.Accessible capacity may vary, also depending on used software.Up to 20 GB of HDD space is reserved for system recoveryInterface add on cards/components(optional)4G/ LTE (optional)(Downlink speed up to 300 Mbit/s, Uplink speed up to 150 Mbit/s)Display33.8 cm (13.3-inch), IPS, FHD, 1,920 x 1,080 pixel, Anti-glare touchscreen, 400 cd/m², 1500:1MultimediaCamera Front: HD Cam (0.9MP) with LEDFront: IR Cam (0.9MP) supporting Windows Hello with LEDRear: 5M with LEDBase unitBase unit STYLISTIC Q7311General system informationChipset Integrated in CPUSupported capacity RAM (min.)8 GBSupported capacity RAM (max.)16 GBMemory notes8 GB onboard or 16 GB onboardDual channel supportLPDDR4x (4,266 MHz)LAN notes Virtual MAC address. LAN connector via optional keyboard docking, cradle or optional USB to LAN adapter. Integrated WLAN Intel WiFi 6 AX201 - WLAN, BT, SRD cat. 1General system informationBIOS version UEFI Specification 2.7BIOS features InsydeH2O BIOSAudio type On boardAudio codec Realtek ALC255Audio features2x digital array microphones, 2x built-in speakers (stereo)Waterproof / Spillproof IP42Disinfectable noMIL-STD tested Yes, selected MIL-STD-810H tests passed.MIL-STD-810H test results are not a guarantee of future performance under identified test conditions.Accidental damage is not covered under standard international limited warranty.DisplayDiagonal Size33.8 cm (13.3-inch)Display Technology IPSDisplay type Anti-glare touchscreenDisplay Resolution type FHDBrightness - typical400 cd/m²Contrast - typical1500:1Viewing angle (h/v) - typical178°/178°Display notes Wide-view high-bright LED display (for enhanced outdoor viewing)Integrated ambient light sensor for automatic backlight adjustment to the working environment.Toughened glassSensors Ambient Light SensorCompassGyroscopeProximityDigitizer / Touch Technology Wacom Digitizer for pen (AES) input plus capacitive 10 finger multi-touch screenPen AES4k pressure levelPen garageinductive chargingAmbient light sensor IntegratedAmbient light sensor notes While enabled, the ambient light sensor automatically adjusts the display backlightGraphicsBase unit STYLISTIC Q7311TFT resolution (HDMI)up to 4,096 x 2,160 @ 60 HzGraphics brand name Intel® Iris® Xe Graphics (with Dual channel memory)Graphics features 4 Display Support (3 external, 1 internal)HDCP supportDirectX® 12OpenGL® 4.5Graphics notes Shared memory depending on main memory size and operating system3D acceleratorInterfacesDC-in1Audio: line-out / headphone 1 (combo port with Audio line-in)Audio: line-in / microphone 1 (combo port with Audio line-out)Internal microphones2x digital array microphonesUSB 2.0 total1USB 3.2 Gen1 (5 Gbps) total 1 x Type-AUSB 4.0 Gen3 (20 Gbps) total 1 x Type-C Intel® Thunderbolt™ 4 (with Power Delivery functionality)USB Type-C 1 USB 4 Gen3 Thunderbolt™4, Power Delivery (15W)HDMI 1 v1.4Ethernet (RJ-45)-Memory card slots 1 (USH-I) SD 3.0 StandardSD/microSD card: 2GBSDHC/microSDHC card: 32GBSDXC/microSDXC card: 2TBSmartCard slot optionalSIM card slot 1 (Nano-SIM, only for models with integrated 4G/LTE module)Interface Module notes LAN and VGA available via conversion cable.Docking connector for Port Replicator 1 (Cradle)Kensington Lock support1Port Replicator interfaces (optional)USB Type-C PR CradleDC-in 1 (19V/90W required) 1 (19V)Power on switch1---Audio: line-in---1Audio: line-in / line-out1---Audio: line-out---1Audio: comments Combo jack for headset usage---USB 3.2 Gen1 (5 Gbps) total---3DisplayPort1x V1.2 1VGA1x1HDMI text1x------Interface Notes3x Type-A - 5V/0.9A, 4.5W1x Type-C - 15W1x Type-C - Up to 60 W (PD v2.0-1.1) power output toclient or 4.5W inputKensington Lock support no1Ethernet (RJ-45)1 1 (10/100/1000)---Notes Number of simultaneous used displays and its possibleresolutions and frequencies depend on mobile systemand display interface type.Please consult always also the manual of the connectedclient.Wireless technologiesAntennas2x dual band for WLAN, 2x for LTE, Bluetooth shared with WLANBluetooth V5.1Integrated WLAN Intel WiFi 6 AX201 - WLAN, BT, SRD cat. 1WLAN encryption WPA/WPA2/WPA3 (Wi-Fi Protected Access)WLAN notes Import and usage according to country-specific regulations.Integrated WWAN LTE Sierra Wireless EM7421 (Cat.7) - UMTS, LTEWWAN notes Including GPS functionalityImport and usage according to country-specific regulations.LTE Connection Manager (if configured with 4G/LTE)GPS Embedded in 4G module if configured with WWANPower supplyAC adapter19 V / 65 W (3.42 A)20 V / 65 W (3.25 A) Type CNotes65W AC Adapter for usage with system/ min. 90W AC Adapter for usage with Cradle Rated voltage range100 V - 240 V (AC Input)Rated frequency range50 Hz - 60 Hz1st battery Li-Ion battery 3-cell, 38 WhBattery features Quick Charge: 80% in 1hRuntime 1st battery10 hBattery notes Battery runtime information is based on worldwide acknowledged BAPCo® MobileMark® 2018. Refer to www.bapco.com for additional details.The BAPCo® MobileMark® Benchmark provides results that enable direct product comparisons betweenmanufacturers. It does not guarantee any specific battery runtime which actually can be lower and may varydepending on product model, configuration, application and power management settings. The battery capacitydecreases slightly with every re-charge and over its lifetime.Dimensions / Weight / EnvironmentalDimensions (W x D x H)315 x 200.9 x 10.5 mm12.4 x 0.79 x 0.42 inchWeight from 0.800 kg slate only, weight of keyboard docking from 0.465 kgWeight (lbs)from 1.75 lbs slate only, weight of keyboard docking from 1.25 lbsWeight notes Weight may vary depending on actual configurationOperating ambient temperature 5 - 35 °C (41 - 95 °F); Packed -10 - 60 °C (14 - 140 °F)Operating relative humidity Running: 20 - 80% (relative humidity); Packed: 20 - 80% (relative humidity)Product STYLISTIC Q7311Germany GSEurope CECBGlobal TCO Certified 8.0EPEAT® Silver (dedicated regions), depending on configurationMicrosoft Operating Systems (HCT / HCL entry / WHQL)MIL-STD-810H testedRoHS (Restriction of hazardous substances)WEEE (Waste electrical and electronic equipment)Russia EACChina CCCCompliance link https:///sites/certificatesAdditional SoftwareAdditional software (preinstalled)Adobe® Reader® (pdf reader)CyberLink YouCam (webcam software)Fujitsu Display ManagerFujitsu DeskUpdate (driver and utility tool)ShockSensor UtilityPower Saving UtilityFujitsu Plugfree Network (network management utility)EasyGuide online user documentationMicrosoft Office (1 month trial for new Microsoft® Office 365 customers. Buy Microsoft Office.)Additional software (optional)Recovery DVD for Windows®Drivers & Utilities DVD (DUDVD) optionalCyberLink PowerDVD BD (playback software for Blu-ray Disc™)CyberLink PowerDVD DVD (playback software for DVD)CyberLink YouCam (webcam software)Nero (backup and burning software)ManageabilitySecurityPhysical Security Kensington Lock supportSystem and BIOS Security Absolute Persistence® technology capable BIOSEraseDiskTrusted Platform Module (TPM 2.0)User Security Hard disk passwordUser and supervisor BIOS passwordEmbedded fingerprint sensor (optional)Smartcard reader (optional)SystemLock BIOS SmartCard securityAuthConductor Client Basic (secure authentication solution)Packaging informationWarranty Warranty period2 years (for countries within EMEIA)Warranty type Bring-in Service / Collect & Return Service (depending on country)Product Support - the perfect extension Recommended Service 9x5, Onsite Response Time: Next Business DaySpare Parts availabilityat least 5 years after shipment, for details see https:///Recommended AccessoriesThunderbolt™ 4 Port ReplicatorFirst Thunderbolt™ Port Replicator on the market providing enhancedsecurity and full support of Intel® AMT (vPro®).The universal port can easily connect almost everything with a single cable and high speed-data transfer. This smart workspace solution keeps your desk clean and tidy.Order Code: FPCPR401BPUSB Type-C Port Replicator 2Connect to your peripherals. Adapt to the task on demand. The universal USB Type-C interface supports you to get your peripheral devicesconnected easily. Multiply your USB ports to connect your peripherals as well as your external display via HDMI, DisplayPort or VGA.You also can charge your external USB devices without the need of any additional charger.Order Code:S26391-F3327-L100STYLISTIC Q7311, Q7310 andSTYLISTIC Q5010 Family Cradle Flexibility, expandability, desktop replacement, investment protection – to name just a few benefits of Fujitsu’s docking options.Order Code: S26391-F3397-L100USB Type-C AC AdapterRecharge your notebook or tablet at work, at home or on the road with this USB Type-C power source easily. Order Code: S26391-F3326-L502LAN Conversion Cable (USB toLAN) for STYLISTIC Q The FUJITSU USB Type-A to LAN Conversion Cable enables you to connect your compatible STYLISTIC Tablet to a wired network connection. GBit-LAN via USB conversion cable is limited to 480 Mbit/s due to USB 2.0specification. (Picture similar to product)Order Code:S26391-F3398-L840Tablet Stand for STYLISTIC QdevicesThe tablet stand is designed for STYLISTIC devices like latest STYLISTIC Q7312 and can be used universally. Fits for STYLISTIC Q5 and Q7 and the Type-C as well as the Thunderbolt ™ 4 port replicator can be fixed on the stand.Order Code: FPCSK769BPAES PenTake your creativity to the next level, with the most natural pen experience with the AES Pen with replacement stylus tips. With pen nibs that are very thin, you can experience the writing and signing behavior of an ink pen. The pen fits in the device’s integrated pen garage.Order Code:S26391-F3389-L500Car Adapter USB-C-QCOne Car Adapter fits all.Independent of your mobile device charging method this car adapter will fulfill all major requirements and standards for fast charging vendorbrand-independent notebooks and all mobile devices. The Car Adapter USB-C-QC supports USB PD with PPS, Quick Charge (QC), Apple- and Samsung charge.Order Code: S26391-F2613-L630CANVAS HANSEN 14The PLEVIER CANVAS HANSEN 14 leather and canvas case is a compact and classic carrier for on the go. Available for notebooks up to 14 inches with two compartments and two accessory sections, protection for your device ensured. A subtle design canvas and nappa leather shade.Order Code:S26391-F1193-L67Bumper Case KitThe protective bump case kit is designed to prevent damages to yourSTYLISTIC Q7. Openings of the cover allow you to access all ports andbuttons whilest the hand strap on the back of the case gives you a firm grip while working with your tablet outside the office. The integrated stand solution enhances your productivity.Order Code: S26391-F3396-L200Folio Cover STYLISTIC Q7311/Q7310The Folio Cover for the STYLISTIC Q7311 and Q7310 is a thin, tailored protective sleeve for your Fujitsu tablet. It keeps the device safe from damage on the go, and brings a touch of style to your daily work. It can even be used as a stand if you need to display a presentation or watch a clip and fits even the device is connected to its keyboard dock.Inclination stand style 120 to 150 degreeOrder Code:S26391-F3509-L100Wireless Mouse WI860 BTCThe Wireless Mouse WI860 BTC can be paired with up to 3 different clients, 2x Bluetooth and 1x wireless USB Type-C dongle.With the blue optical sensor, it works on nearly all surfaces with an 3-step adjustable DPI selector (800/1600/2400).The mouse charges wirelessly through Qi or by USB Type-C cable.A utility button on the side is programmable. The default functions are optimized for Teams calls.Order Code:S26381-K474-L100Order Code: FPCKG453BPContactAddress: x-xx-x, street, city, state, ZIP code, country Phone: xx-xxxx-xxxx Fax : xx-xxxx-xxxxEmail:********************.com Website: /[country]2023-08-02 CE-ENdelivery subject to availability. Any liability that the data and illustrations are complete, actual or correct is excluded. Designations may be trademarks and/or copyrights of the respective manufacturer, the use of which by third parties for their own purposes may infringe the rights of such ownerMore informationAll rights reserved, including intellectual property rights. Changes to technical data reserved. Delivery subject to availability. Any liability that the data and illustrations are complete, actual or correct is excluded.Designations may be trademarks and/or copyrights of the respective manufacturer, the use of which by third parties for their own purposes may infringe the rights of such owner.For further information see /terms_of_use.html Copyright © Fujitsu Technology Solutions。

Ultimaker S5 安装和使用手册说明书

Ultimaker S5安装和使用手册原始手册 v1.820182免责声明请仔细阅读并理解本安装和使用手册的内容。

如果未阅读本手册,可能会导致人身伤害、打印效果低劣或 Ultimaker S5 受损。

务必确保使用本 3D 打印机的所有人都知道并理解本手册的内容,以便能够充分利用 Ultimaker S5。

由于设备的装配、搬运、存放、使用或处置*条件或方法不受我们控制,也可能不在我们的知晓范围内 因此对于因装配、搬运、存放、使用或处置本产品*产生的,或以任何方式与之相关的损失、人身伤害、设备损坏或费用,我们概不负责,并明确否定此类责任。

本文档中的信息来自于可靠的来源。

但是,这些信息在准确性方面并没有任何明示或隐含的保证。

Ultimaker S5 的预期用途Ultimaker 3D 打印机专为利用 Ultimaker 材料实现熔丝制造而设计和建造,用于商业/业务环境。

Ultimaker 3D 打印机集精确性和速度于一体,是制作概念模型、功能样件和进行小规模生产的理想机器。

虽然我们在使用 Ultimaker Cura 打印 3D 模型方面已经达到很高标准,但用户依然有责任确认并验证打印对象的应用是否符合预期用途,对于严格管制领域(医疗器械和航空)的应用,这一点尤为重要。

虽然Ultimaker采用开放式材料平台,但 Ultimaker 材料匹配打印机能够取得最佳打印效果,并且,我们已努力确保材料属性与机器设置匹配。

* 我们遵循 WEEE 指令。

版权所有 © 2018 Ultimaker。

全球范围内保留所有权利。

本语言版本的手册由制造商验证(原始手册)。

未经 Ultimaker 事先书面许可,本手册的任何部分,包括图片,都不得以打印、复印、微缩拍摄或任何其他方式复制和/或公布。

免责声明 2前言 4认证 5安全与合规 61.1 安全信息 71.2 危险 8简介 92.1 Ultimaker S5 的主要组件 102.2 规格 11拆箱 123.1 拆箱 133.2 安装硬件配件 15首次使用设置 174.1 打印平台板选择 184.2 PrintCore 安装 194.3 装填材料 204.4 网络安装和固件更新 224.5 安装 Ultimaker Cura 23操作 245.1 触摸屏 255.2 材料 265.3 利用 Ultimaker Cura 准备打印成品 285.4 开始打印 305.5 取下打印成品 325.6 卸下支撑材料 335.7 更改打印机配置 355.8 校准 36维护 396.1 更新固件 406.2 材料搬运和存放 416.3 维护计划 426.4 清洁打印机 436.5 轴润滑 476.6 检查轴隙 486.7 检查短皮带的张力 496.8 检查打印头前风扇中是否有残渣 506.9 检查喷嘴盖的质量 516.10 润滑 Z 电机的导向螺丝 536.11 清洁进料装置 546.12 清洁 PrintCore 556.13 润滑进料装置齿轮 586.14 更换鲍登管 596.15 清洁系统风扇 616.16 润滑铰链 62故障排除 637.1 错误消息 647.2 PrintCore 故障排除 657.3 打印质量问题 66本文档是 Ultimaker S5 的安装和使用手册。

PLX SDK User Manual

User’s Manual

Version 4.40 March 2006

© 2006, PLX Technology, Inc. All rights reserved.

PLX Technology, Inc. retains the right to make changes to this product at any time, without notice. Products may have minor variations to this publication. PLX assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of PLX products.

PLX Technology and the PLX logo are registered trademarks of PLX Technology, Inc.

Other brands and names are the property of their respective owners.

PLX SOFTWARE LICENSE AGREEMENT

LICENSE Copyright © 2006 PLX Technology,

Inc.

This PLX Software License agreement is a legal agreement between you and PLX Technology, Inc. for the PLX Software, which is provided on the enclosed PLX CD-ROM. PLX Technology owns this PLX Software. The PLX Software is protected by copyright laws and international copyright treaties, as well as other intellectual property laws and treaties, and is licensed, not sold. If you are a rightful possessor of the PLX Software, PLX grants you a license to use the PLX Software as part of or in conjunction with a PLX chip on a per project basis. PLX grants this permission provided that the above copyright notice appears in all copies and derivatives of the PLX Software. Use of any supplied runtime object modules or derivatives from the included source code in any product without a PLX Technology, Inc. chip is strictly prohibited. You obtain no rights other than those granted to you under this license. You may copy the PLX Software for backup or archival purposes. You are not authorized to use, merge, copy, display, adapt, modify, execute, distribute or transfer, reverse assemble, reverse compile, decode, or translate the PLX Software except to the extent permitted by law.

NXP SCM-i.MX 6 Series Yocto Linux 用户指南说明书

© 2017 NXP B.V.SCM-i.MX 6 Series Yocto Linux User'sGuide1. IntroductionThe NXP SCM Linux BSP (Board Support Package) leverages the existing i.MX 6 Linux BSP release L4.1.15-2.0.0. The i.MX Linux BSP is a collection of binary files, source code, and support files that can be used to create a U-Boot bootloader, a Linux kernel image, and a root file system. The Yocto Project is the framework of choice to build the images described in this document, although other methods can be also used.The purpose of this document is to explain how to build an image and install the Linux BSP using the Yocto Project build environment on the SCM-i.MX 6Dual/Quad Quick Start (QWKS) board and the SCM-i.MX 6SoloX Evaluation Board (EVB). This release supports these SCM-i.MX 6 Series boards:• Quick Start Board for SCM-i.MX 6Dual/6Quad (QWKS-SCMIMX6DQ)• Evaluation Board for SCM-i.MX 6SoloX (EVB-SCMIMX6SX)NXP Semiconductors Document Number: SCMIMX6LRNUGUser's GuideRev. L4.1.15-2.0.0-ga , 04/2017Contents1. Introduction........................................................................ 1 1.1. Supporting documents ............................................ 22. Enabling Linux OS for SCM-i.MX 6Dual/6Quad/SoloX .. 2 2.1. Host setup ............................................................... 2 2.2. Host packages ......................................................... 23.Building Linux OS for SCM i.MX platforms .................... 3 3.1. Setting up the Repo utility ...................................... 3 3.2. Installing Yocto Project layers ................................ 3 3.3. Building the Yocto image ....................................... 4 3.4. Choosing a graphical back end ............................... 4 4. Deploying the image .......................................................... 5 4.1. Flashing the SD card image .................................... 5 4.2. MFGTool (Manufacturing Tool) ............................ 6 5. Specifying displays ............................................................ 6 6. Reset and boot switch configuration .................................. 7 6.1. Boot switch settings for QWKS SCM-i.MX 6D/Q . 7 6.2. Boot switch settings for EVB SCM-i.MX 6SoloX . 8 7. SCM uboot and kernel repos .............................................. 8 8. References.......................................................................... 8 9.Revision history (9)Enabling Linux OS for SCM-i.MX 6Dual/6Quad/SoloX1.1. Supporting documentsThese documents provide additional information and can be found at the NXP webpage (L4.1.15-2.0.0_LINUX_DOCS):•i.MX Linux® Release Notes—Provides the release information.•i.MX Linux® User's Guide—Contains the information on installing the U-Boot and Linux OS and using the i.MX-specific features.•i.MX Yocto Project User's Guide—Contains the instructions for setting up and building the Linux OS in the Yocto Project.•i.MX Linux®Reference Manual—Contains the information about the Linux drivers for i.MX.•i.MX BSP Porting Guide—Contains the instructions to port the BSP to a new board.These quick start guides contain basic information about the board and its setup:•QWKS board for SCM-i.MX 6D/Q Quick Start Guide•Evaluation board for SCM-i.MX 6SoloX Quick Start Guide2. Enabling Linux OS for SCM-i.MX 6Dual/6Quad/SoloXThis section describes how to obtain the SCM-related build environment for Yocto. This assumes that you are familiar with the standard i.MX Yocto Linux OS BSP environment and build process. If you are not familiar with this process, see the NXP Yocto Project User’s Guide (available at L4.1.15-2.0.0_LINUX_DOCS).2.1. Host setupTo get the Yocto Project expected behavior on a Linux OS host machine, install the packages and utilities described below. The hard disk space required on the host machine is an important consideration. For example, when building on a machine running Ubuntu, the minimum hard disk space required is about 50 GB for the X11 backend. It is recommended that at least 120 GB is provided, which is enough to compile any backend.The minimum recommended Ubuntu version is 14.04, but the builds for dizzy work on 12.04 (or later). Earlier versions may cause the Yocto Project build setup to fail, because it requires python versions only available on Ubuntu 12.04 (or later). See the Yocto Project reference manual for more information.2.2. Host packagesThe Yocto Project build requires that the packages documented under the Yocto Project are installed for the build. Visit the Yocto Project Quick Start at /docs/current/yocto-project-qs/yocto-project-qs.html and check for the packages that must be installed on your build machine.The essential Yocto Project host packages are:$ sudo apt-get install gawk wget git-core diffstat unzip texinfo gcc-multilib build-essential chrpath socat libsdl1.2-devThe i.MX layers’ host packages for the Ubuntu 12.04 (or 14.04) host setup are:$ sudo apt-get install libsdl1.2-dev xterm sed cvs subversion coreutils texi2html docbook-utils python-pysqlite2 help2man make gcc g++ desktop-file-utils libgl1-mesa-dev libglu1-mesa-dev mercurial autoconf automake groff curl lzop asciidocThe i.MX layers’ host packages for the Ubuntu 12.04 host setup are:$ sudo apt-get install uboot-mkimageThe i.MX layers’ host packages for the Ubuntu 14.04 host s etup are:$ sudo apt-get install u-boot-toolsThe configuration tool uses the default version of grep that is on your build machine. If there is a different version of grep in your path, it may cause the builds to fail. One workaround is to rename the special versi on to something not containing “grep”.3. Building Linux OS for SCM i.MX platforms3.1. Setting up the Repo utilityRepo is a tool built on top of GIT, which makes it easier to manage projects that contain multiple repositories that do not have to be on the same server. Repo complements the layered nature of the Yocto Project very well, making it easier for customers to add their own layers to the BSP.To install the Repo utility, perform these steps:1.Create a bin folder in the home directory.$ mkdir ~/bin (this step may not be needed if the bin folder already exists)$ curl /git-repo-downloads/repo > ~/bin/repo$ chmod a+x ~/bin/repo2.Add this line to the .bashrc file to ensure that the ~/bin folder is in your PATH variable:$ export PATH=~/bin:$PATH3.2. Installing Yocto Project layersAll the SCM-related changes are collected in the new meta-nxp-imx-scm layer, which is obtained through the Repo sync pointing to the corresponding scm-imx branch.Make sure that GIT is set up properly with these commands:$ git config --global "Your Name"$ git config --global user.email "Your Email"$ git config --listThe NXP Yocto Project BSP Release directory contains the sources directory, which contains the recipes used to build, one (or more) build directories, and a set of scripts used to set up the environment. The recipes used to build the project come from both the community and NXP. The Yocto Project layers are downloaded to the sources directory. This sets up the recipes that are used to build the project. The following code snippets show how to set up the SCM L4.1.15-2.0.0_ga Yocto environment for the SCM-i.MX 6 QWKS board and the evaluation board. In this example, a directory called fsl-arm-yocto-bsp is created for the project. Any name can be used instead of this.Building Linux OS for SCM i.MX platforms3.2.1. SCM-i.MX 6D/Q quick start board$ mkdir fsl-arm-yocto-bsp$ cd fsl-arm-yocto-bsp$ repo init -u git:///imx/fsl-arm-yocto-bsp.git -b imx-4.1-krogoth -m scm-imx-4.1.15-2.0.0.xml$ repo sync3.2.2. SCM-i.MX 6SoloX evaluation board$ mkdir my-evb_6sxscm-yocto-bsp$ cd my-evb_6sxscm-yocto-bsp$ repo init -u git:///imx/fsl-arm-yocto-bsp.git -b imx-4.1-krogoth -m scm-imx-4.1.15-2.0.0.xml$ repo sync3.3. Building the Yocto imageNote that the quick start board for SCM-i.MX 6D/Q and the evaluation board for SCM-i.MX 6SoloX are commercially available with a 1 GB LPDDR2 PoP memory configuration.This release supports the imx6dqscm-1gb-qwks, imx6dqscm-1gb-qwks-rev3, and imx6sxscm-1gb-evb. Set the machine configuration in MACHINE= in the following section.3.3.1. Choosing a machineChoose the machine configuration that matches your reference board.•imx6dqscm-1gb-qwks (QWKS board for SCM-i.MX 6DQ with 1 GB LPDDR2 PoP)•imx6dqscm-1gb-qwks-rev3 (QWKS board Rev C for SCM-i.MX 6DQ with 1GB LPDDR2 PoP) •imx6sxscm-1gb-evb (EVB for SCM-i.MX 6SX with 1 GB LPDDR2 PoP)3.4. Choosing a graphical back endBefore the setup, choose a graphical back end. The default is X11.Choose one of these graphical back ends:•X11•Wayland: using the Weston compositor•XWayland•FrameBufferSpecify the machine configuration for each graphical back end.The following are examples of building the Yocto image for each back end using the QWKS board for SCM-i.MX 6D/Q and the evaluation board for SCM-i.MX 6SoloX. Do not forget to replace the machine configuration with what matches your reference board.3.4.1. X11 image on QWKS board Rev C for SCM-i.MX 6D/Q$ DISTRO=fsl-imx-x11 imx6dqscm-1gb-qwks-rev3 source fsl-setup-release.sh -b build-x11$ bitbake fsl-image-gui3.4.2. FrameBuffer image on evaluation board for SCM-i.MX 6SX$ DISTRO=fsl-imx-fb MACHINE=imx6sxscm-1gb-evb source fsl-setup-release.sh –b build-fb-evb_6sxscm$ bitbake fsl-image-qt53.4.3. XWayland image on QWKS board for SCM-i.MX 6D/Q$ DISTRO=fsl-imx-xwayland MACHINE=imx6dqscm-1gb-qwks source fsl-setup-release.sh –b build-xwayland$ bitbake fsl-image-gui3.4.4. Wayland image on QWKS board for SCM-i.MX 6D/Q$ DISTRO=fsl-imx-wayland MACHINE=imx6dqscm-1gb-qwks source fsl-setup-release.sh -b build-wayland$ bitbake fsl-image-qt5The fsl-setup-release script installs the meta-fsl-bsp-release layer and configures theDISTRO_FEATURES required to choose the graphical back end. The –b parameter specifies the build directory target. In this build directory, the conf directory that contains the local.conf file is created from the setup where the MACHINE and DISTRO_FEATURES are set. The meta-fslbsp-release layer is added into the bblayer.conf file in the conf directory under the build directory specified by the –e parameter.4. Deploying the imageAfter the build is complete, the created image resides in the <build directory>/tmp/deploy/images directory. The image is (for the most part) specific to the machine set in the environment setup. Each image build creates the U-Boot, kernel, and image type based on the IMAGE_FSTYPES defined in the machine configuration file. Most machine configurations provide the SD card image (.sdcard), ext4, and tar.bz2. The ext4 is the root file system only. The .sdcard image contains the U-Boot, kernel, and rootfs, completely set up for use on an SD card.4.1. Flashing the SD card imageThe SD card image provides the full system to boot with the U-Boot and kernel. To flash the SD card image, run this command:$ sudo dd if=<image name>.sdcard of=/dev/sd<partition> bs=1M && syncFor more information about flashing, see “P reparing an SD/MMC Card to Boot” in the i.MX Linux User's Guide (document IMXLUG).Specifying displays4.2. MFGTool (Manufacturing Tool)MFGTool is one of the ways to place the image on a device. To download the manufacturing tool for the SCM-i.MX 6D/Q and for details on how to use it, download the SCM-i.MX 6 Manufacturing Toolkit for Linux 4.1.15-2.0.0 under the "Downloads" tab from /qwks-scm-imx6dq. Similarly, download the manufacturing tool for the SCM-i.MX 6SoloX evaluation board under the "Downloads" tab from /evb-scm-imx6sx.5. Specifying displaysSpecify the display information on the Linux OS boot command line. It is not dependent on the source of the Linux OS image. If nothing is specified for the display, the settings in the device tree are used. Find the specific parameters in the i.MX 6 Release Notes L4.1.15-2.0.0 (available at L4.1.15-2.0.0_LINUX_DOCS). The examples are shown in the following subsections. Interrupt the auto-boot and enter the following commands.5.1.1. Display options for QWKS board for SCM-i.MX 6D/QHDMI displayU-Boot > setenv mmcargs 'setenv bootargs console=${console},${baudrate} ${smp}root=${mmcroot} video=mxcfb0:dev=hdmi,1920x1080M@60,if=RGB24'U-Boot > run bootcmd5.1.2. Display options for EVB for SCM-i.MX 6SXNote that the SCM-i.MX 6SX EVB supports HDMI with a HDMI accessory card (MCIMXHDMICARD) that plugs into the LCD connector on the EVB.Accessory boards:•The LVDS connector pairs with the NXP MCIMX-LVDS1 LCD display board.•The LCD expansion connector (parallel, 24-bit) pairs with the NXP MCIMXHDMICARD adapter board.LVDS displayU-Boot > setenv mmcargs 'setenv bootargs console=${console},${baudrate} ${smp}root=${mmcroot} ${dmfc} video=mxcfb0:dev=ldb,1024x768M@60,if=RGB666 ldb=sep0'U-Boot > run bootcmdHDMI display (dual display for the HDMI as primary and the LVDS as secondary)U-Boot > setenv mmcargs 'setenv bootargs console=${console},${baudrate} ${smp}root=${mmcroot} video=mxcfb0:dev=hdmi,1920x1080M@60,if=RGB24video=mxcfb1:dev=ldb,LDBXGA,if=RGB666'U-Boot > run bootcmdLCD displayu-boot > setenv mmcargs 'setenv bootargs ${bootargs}root=${mmcroot} rootwait rw video=mxcfb0:dev=lcd,if=RGB565'u-boot> run bootcmd6. Reset and boot switch configuration6.1. Boot switch settings for QWKS SCM-i.MX 6D/QThere are two push-button switches on the QWKS-SCMIMX6DQ board. SW1 (SW3 for QWKS board Rev B) is the system reset that resets the PMIC. SW2 is the i.MX 6Dual/6Quad on/off button that is needed for Android.There are three boot options. The board can boot either from the internal SPI-NOR flash inside the SCM-i.MX6Dual/6Quad or from either of the two SD card slots. The following table shows the switch settings for the boot options.Table 1.Boot configuration switch settingsBoot from top SD slot (SD3)Boot from bottom SD slot (SD2)Boot from internal SPI NORDefault1.References6.2. Boot switch settings for EVB SCM-i.MX 6SoloXThis table shows the jumper configuration to boot the evaluation board from the SD card slot SD3.7. SCM uboot and kernel repositoriesThe kernel and uboot patches for both SCM-i.MX 6 QWKS board and evaluation board are integrated in specific git repositories. Below are the git repos for SCM-i.MX 6 uboot and kernel:uBoot repo: /git/cgit.cgi/imx/uboot-imx.gitSCM Branch: scm-imx_v2016.03_4.1.15_2.0.0_gakernel repo: /git/cgit.cgi/imx/linux-imx.gitSCM branch: scm-imx_4.1.15_2.0.0_ga8. References1.For details about setting up the Host and Yocto Project, see the NXP Yocto Project User’s Guide(document IMXLXYOCTOUG).2.For information about downloading images using U-Boot, see “Downloading images usingU-Boot” in the i.MX Linux User's Guide (document IMXLUG).3.For information about setting up the SD/MMC card, see “P reparing an SD/MMC card to boot” inthe i.MX Linux User's Guide (document IMXLUG).9. Revision historyDocument Number: SCMIMX6LRNUGRev. L4.1.15-2.0.0-ga04/2017How to Reach Us: Home Page: Web Support: /supportInformation in this document is provided solely to enable system and softwareimplementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequentia l or incidental damages. “Typical”parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including “typicals,” must be valida ted for each customer application by customer’s technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: /SalesTermsandConditions .NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, Freescale, and the Freescale logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners.ARM, the ARM Powered logo, and Cortex are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. © 2017 NXP B.V.。

易普特B5交换机快速配置指南说明书

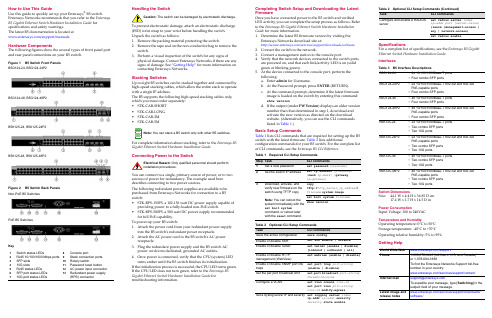

How to Use This GuideUse this guide to quickly set up your Enterasys ®B5 switch.Enterasys Networks recommends that you refer to the Enterasys B5 Gigabit Ethernet Switch Hardware Installation Guide for specifications and safety warnings.The latest B5 documentation is located at /support/manuals.Hardware ComponentsThe following figures show the several types of front panel port and rear panel connections on your B5 switch.Figure 1B5 Switch Front PanelsB5G124-24, B5G124-24P2B5G124-48, B5G124-48P2B5K125-24, B5K125-24P2B5K125-48, B5K125-48P2Figure 2 B5 Switch Back PanelsNon-PoE B5 SwitchesPoE B5 SwitchesKey1Switch status LEDs8Console port2RJ45 10/100/1000 Mbps ports 9Stack connection ports 3SFP slots 10Rotary switch410G slots11Password reset button 5RJ45 status LEDs 12AC power input connector 6SFP port status LEDs 13Redundant power supply 710G port status LEDs(RPS) connectorHandling the SwitchTo prevent electrostatic damage, attach an electrostatic discharge (ESD) wrist strap to your wrist before handling the switch.Unpack the switch as follows:1.Remove the packing material protecting the switch.2.Remove the tape seal on the non ‐conductive bag to remove theswitch.3.Perform a visual inspection of the switch for any signs ofphysical damage. Contact Enterasys Networks if there are any signs of damage. See “Getting Help” for more information on contacting Enterasys Networks.Stacking SwitchesUp to eight B5 switches can be stacked together and connected by high ‐speed stacking cables, which allow the entire stack to operate with a single IP address.The B5 supports the following high ‐speed stacking cables only, which you must order separately:•STK ‐CAB ‐SHORT •STK ‐CAB ‐LONG •STK ‐CAB ‐2M •STK ‐CAB ‐5MFor complete information about stacking, refer to the Enterasys B5 Gigabit Ethernet Switch Hardware Installation Guide.Connecting Power to the SwitchYou can connect to a single, primary source of power, or to two sources of power for redundancy. The example used here describes connecting to two power sources.The following redundant power supplies are available to be purchased from Enterasys Networks for connection to a B5 switch:•STK ‐RPS ‐150PS, a 102‐156 watt DC power supply capable ofproviding power to a fully ‐loaded non ‐PoE switch.•STK ‐RPS ‐500PS, a 500 watt DC power supply recommendedfor full PoE capability.To power ‐up your B5 switch:1.Attach the power cord from your redundant power supplyinto the B5 switch’s redundant power receptacle.2.Attach the AC power cord to the B5 switch’s AC powerreceptacle.3.Plug the redundant power supply and the B5 switch ACpower cords into dedicated, grounded AC outlets.4.Once power is connected, verify that the CPU (system) LEDturns amber until the B5 switch finishes its initialization.If the initialization process is successful, the CPU LED turns green. If the CPU LED does not turn green, refer to the Enterasys B5 Gigabit Ethernet Switch Hardware Installation Guide for troubleshooting information.Caution:The switch can be damaged by electrostatic discharge.You can stack a B5 switch only with other B5 switches.Only qualified personnel should perform Completing Switch Setup and Downloading the Latest FirmwareOnce you have connected power to the B5 switch and verified LED activity, you can complete the setup process as follows. Refer to the Enterasys B5 Gigabit Ethernet Switch Hardware Installation Guide for more information.1.Determine the latest B5 firmware version by visiting theEnterasys Networks download site at:/services/support/downloads/software2.Connect the switch to the network.3.Connect a management station to the console port.4.Verify that the network devices connected to the switch portsare powered on, and that each link/activity LED is on (solid green or blinking green).5.At the device connected to the console port, perform thefollowing:a.Enter admin for Username.b.At the Password prompt, press ENTER (RETURN).c.At the command prompt, determine if the latest firmwareimage is loaded on the switch by entering this command:show versiond.If the output (under FW Version ) displays an older versionnumber than that determined in step 1, download and activate the new version as directed on the download website. (Alternatively, you can use the CLI commands listed in Table 1.)Basic Setup CommandsTable 1 lists CLI commands that are required for setting up the B5 switch with the latest firmware. Table 2 lists additionalconfiguration commands for your B5 switch. For the complete list of CLI commands, see the Enterasys B5 CLI Reference .Table 1Required CLI Setup CommandsStep TaskCLI commands1Set a new password set password [username ]2Set the switch IP addressset ip address ip-address [mask ip-mask ] [gateway ip-gateway ]3Download, activate, and verify new firmware on the switch using TFTP copyNote: You can reboot the system immediately with the set boot systemcommand, or reboot later with the reset command.copytftp://tftp_server_ip_address /filename system:image set boot system filenameshow version Table 2Optional CLI Setup CommandsTaskCLI commands Save the active configuration save configEnable or disable SSH set ssh enable | disable Enable or disable Telnet set telnet {enable | disable} [inbound | outbound | all]Enable or disable HTTP management (WebView)set webview {enable | disable}Enable or disable SNMP port link trapsset port trap port-string{enable | disable}Set the per port broadcast limit set port broadcast port-string threshold-valueConfigure a VLANset vlan create vlan-id set port vlan port-string vlan-id modify-egress Set a Syslog server IP and severity set logging server indexip-addr ip-addr severity severity state enableSpecificationsFor a complete list of specifications, see the Enterasys B5 Gigabit Ethernet Switch Hardware Installation Guide . InterfacesSwitch DimensionsSize:44.1 W x 4.4 H x 36.85 D cm 17.4 W x 1.7 H x 14.5 D inPower ConsumptionInput Voltage: 100 to 240VACTemperature and HumidityOperating temperature: 0°C to 50°C Storage temperature: ‐40°C to +70°C Operating relative humidity: 5% to 95%Getting HelpConfigure and enable a RADIUS serverset radius server index ip-addr port [secret-value ]{realm {management-access | any | network-access} set radius enableTable 3B5 Interface DescriptionsB5G124-24•24 10/100/1000Base-T ports •Four combo SFP portsB5G124-24P2•24 10/100/1000Base-T 802.3af and 802.3at PoE-capable ports •Four combo SFP portsB5G124-48•48 10/100/1000Base-T ports •Four combo SFP portsB5G124-48P2•48 10/100/1000Base-T 802.3af and 802.3at PoE-capable ports •Four combo SFP portsB5K125-24•24 10/100/1000Base-T ports •Two combo SFP ports •Two 10G portsB5K125-24P2•24 10/100/1000Base-T 802.3af and 802.3at PoE-capable ports •Two combo SFP ports •Two 10G portsB5K125-48•48 10/100/1000Base-T ports •Two combo SFP ports •Two 10G portsB5K125-48P2•48 10/100/1000Base-T 802.3af and 802.3at PoE-capable ports •Two combo SFP ports •Two 10G portsWorld Wide Web /support/Phone1-800-872-8440 (toll-free in U.S. and Canada) or 1-978-684-1888To find the Enterasys Networks Support toll-free number in your country:/services/support/contact/Internet mail*********************To expedite your message, type [Switching ] in the subject field of your message.Latest image and release notes/services/support/downloads/software/Table 2Optional CLI Setup Commands (Continued)TaskCLI commandsRelated DocumentsThe latest B5 documentation is located online at: /support/manualsWarrantyWarranty information for the B5 switch is located online at:/support/warranty.aspx/company/literature/enterasys ‐lw ‐ds.pdfNoticeEnterasys Networks reserves the right to make changes in specifications and other information contained in this document and its web site without prior notice. The reader should in all cases consult Enterasys Networks to determine whether any such changes have been made.The hardware, firmware, or software described in this document is subject to change without notice.IN NO EVENT SHALL ENTERASYS NETWORKS BE LIABLE FOR ANY INCIDENTAL,INDIRECT, SPECIAL, OR CONSEQUENTIAL DAMAGES WHATSOEVER (INCLUDING BUT NOT LIMITED TO LOST PROFITS) ARISING OUT OF OR RELATED TO THIS DOCUMENT, WEB SITE, OR THE INFORMATION CONTAINED IN THEM, EVEN IF ENTERASYS NETWORKS HAS BEEN ADVISED OF, KNEW OF, OR SHOULD HAVE KNOWN OF, THE POSSIBILITY OF SUCH DAMAGES.Enterasys Networks,Inc.50 Minuteman Road Andover, MA 01810© 2010 Enterasys Networks,Inc. All rights reserved.Part Number:9034512‐02December 2010ENTERASYS, ENTERASYS NETWORKS, ENTERASYS SECURE NETWORKS, NETSIGHT, ENTERASYS NETSIGHT, and any logos associated therewith, are trademarks or registeredtrademarks of Enterasys Networks, Inc., in the United States and/or other countries. For a complete list of Enterasys trademarks, see /company/trademarks.aspx .All other product names mentioned in this manual may be trademarks or registered trademarks of their respective companies.Regulatory Compliance InformationFederal Communications Commission (FCC) NoticeThis device complies with Part 15 of the FCC rules. Operation is subject to the following twoconditions: (1) this device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.NOTE:This equipment has been tested and found to comply with the limits for a class A digital device, pursuant to Part 15 of the FCC rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercialenvironment. This equipment uses, generates, and can radiate radio frequency energy and if not installed in accordance with the operator’s manual, may cause harmful interference to radiocommunications. Operation of this equipment in a residential area is likely to cause interference in which case the user will be required to correct the interference at his own expense.WARNING:Changes or modifications made to this device which are not expressly approved by the party responsible for compliance could void the user’s authority to operate the equipment.Industry Canada NoticeThis digital apparatus does not exceed the class A limits for radio noise emissions from digital apparatus set out in the Radio Interference Regulations of the Canadian Department of Communications.Le présent appareil numérique n’émet pas de bruits radioélectriques dépassant les limitesapplicables aux appareils numériques de la class A prescrites dans le Règlement sur le brouillage radioélectrique édicté par le ministère des Communications du Canada.Class A ITE NoticeWARNING:This is a Class A product. In a domestic environment this product may cause radio interference in which case the user may be required to take adequate measures.Clase A. Aviso de ITEADVERTENCIA: Este es un producto de Clase A. En un ambiente doméstico este producto puede causar interferencia de radio en cuyo caso puede ser requerido tomar medidas adecuadas.Klasse A ITE AnmerkungWARNHINWEIS: Dieses Produkt zählt zur Klasse A ( Industriebereich ). In Wohnbereichen kann es hierdurch zu Funkstörungen kommen, daher sollten angemessene Vorkehrungen zum Schutz getroffen werden.VCCI NoticeThis is a class A product based on the standard of the Voluntary Control Council for Interference by Information Technology Equipment (VCCI). If this equipment is used in a domestic environment, radio disturbance may arise. When such trouble occurs, the user may be required to take corrective actions.BSMI EMC Statement — TaiwanThis isa class A product. In a domestic environment this product may cause radio interference in which case the user may be required to take adequate measures.AS/NZS CISPR 22Hazardous SubstancesThis product complies with the requirements of European Directive, 2002/95/EC, Restriction of Hazardous Substances (RoHS) in Electrical and Electronic Equipment.European Waste Electrical and Electronic Equipment (WEEE) NoticeIn accordance with Directive 2002/96/EC of the European Parliament on waste electrical and electronic equipment (WEEE):1.The symbol above indicates that separate collection of electrical and electronic equipment isrequired and that this product was placed on the European market after August 13, 2005, the date of enforcement for Directive 2002/96/EC.2.When this product hasreached the end of its serviceable life, it cannot be disposed of as unsortedmunicipal waste. It must be collected and treated separately.3.It has been determined by the European Parliament that there are potential negative effects onthe environment and human health as a result of the presence of hazardous substances in electrical and electronic equipment.4.It is the users’ responsibility to utilize the available collection system to ensure WEEE is properlytreated.For information about the available collection system, please go to/services/support/or contact Enterasys Customer Support at 353 61 705586 (Ireland).Safety InformationClass 1 Laser TransceiversThe single mode interface modules use Class 1 laser transceivers. Read the following safety information before installing or operating these modules.The Class 1 laser transceivers use an optical feedback loop to maintain Class 1 operation limits. This control loop eliminates the need for maintenance checks or adjustments. The output is factory set, and does not allow any user adjustment. Class 1 Laser transceivers comply with the following safety standards:•21 CFR 1040.10 and 1040.11 U.S. Department of Health and Human Services (FDA).•IEC Publication 825 (International Electrotechnical Commission).•CENELEC EN 60825 (European Committee for Electrotechnical Standardization).When operating within their performance limitations, laser transceiver output meets the Class 1 accessible emission limit of all three standards. Class 1 levels of laser radiation are not considered hazardous.When the connector is in place, all laser radiation remains within the fiber. The maximum amount of radiant power exiting the fiber (under normal conditions) is ‐12.6 dBm or 55 x 10‐6 watts.Removing the optical connector from the transceiver allows laser radiation to emit directly from the optical port. The maximum radiance from the optical port (under worst case conditions) is 0.8 W cm ‐2 or 8 x 103 W m 2 sr ‐1.Do not use optical instruments to view the laser output. The use of optical instruments to view laser output increases eye hazard. When viewing the output optical port, power must be removed from the network adapter.Safety ComplianceWarning: Fiber Optic Port SafetyWhen using a fiber optic media expansion module, never look at the transmit laser while it is powered on. Also, never look directly at the fiber TX port and fiber cable ends when they are poweredon.Avertissment: Ports pour fibres optiques - sécurité sur le plan optiqueNe regardez jamais le laser tant qu’il est sous tension. Ne regardezjamais directement le port TX (Transmission) à fibres optiques et les emboutsde câbles à fibres optiques tant qu ʹils sont sous tension.Warnhinweis: Faseroptikanschlüsse - Optische SicherheitNiemals ein Übertragungslaser betrachten, während dieseseingeschaltet ist. Niemals direkt auf den Faser ‐TX ‐Anschluß und auf die Faserkabelenden schauen, während diese eingeschaltet sind.Declaration of ConformityApplication of Council Directive(s):2004/108/EC2006/95/ECManufacturer’s Name:Enterasys Networks,Inc.Manufacturer’s Address:50 Minuteman RoadAndover, MA 01810USAEuropean Representative Address:Enterasys Networks Ltd.Nexus House, Newbury Business ParkLondon Road, NewburyBerkshire RG14 2PZ, EnglandConformance toDirective(s)/Product Standards:EC Directive 2004/108/ECEN 55022:2006EN 55024:1998EN 61000‐3‐2:2006EN 61000‐3‐3:1995EC Directive 2006/95/EC EN 60950‐1:2006EN 60825‐1:2007EN 60825‐2:2004Equipment Type/Environment:Information Technology Equipment,for use in a Commercialor Light Industrial Environment.Enterasys Networks,Inc. declares that the equipment packaged with this notice conforms to the above directives.Enterasys ®B5Gigabit Ethernet SwitchQuick ReferenceB5G124-24, B5G124-24P2B5G124-48, B5G124-48P2B5K125-24, B5K125-24P2B5K125-48, B5K125-48P2P/N 9034512-02。

Nuvoton NK-N9H20用户指南说明书

NK-N9H20User ManualThe information described in this document is the exclusive intellectual property ofNuvoton Technology Corporation and shall not be reproduced without permission from Nuvoton. Nuvoton is providing this document only for reference purposes of NuMicro™ microcontroller based system design. Nuvoton assumes no responsibility for errors or omissions.All data and specifications are subject to change without notice.For additional information or questions, please contact: Nuvoton Technology Corporation.Oct. 02, 2019Table of Contents1Overview (3)2NuDesign HMI-N9H20 Board Introduction (4)2.1NuDesign HMI-N9H20 Jumper Description (8)2.2Pin Assignment for Extended Connectors (11)2.3NuDesign HMI-N9H20/TFT-LCD4.3/SPI2UART(B) PCB Placement (15)2.4NuDesign HMI-N9H20 N9H20K51N’s Control Pin Functions (20)2.5NuDesign HMI-N9H20 BOM (23)2.6NuDesign TFT-LCD4.3 BOM (26)2.7NuDesign SPI2UART(B) BOM (26)3NuDesign HMI-N9H20 Schematics (27)3.1NuDesign HMI-N9H20 Function Blocks Schematic (27)3.2NuDesign HMI-N9H20 N9H20K51N MPU Schematic (28)3.3NuDesign HMI-N9H20 Power Supply Schematic (29)3.4NuDesign HMI-N9H20 Keys and Configuration Schematic (29)3.5NuDesign HMI-N9H20 USB2.0 and SD0 Interface Schematic (30)3.6NuDesign HMI-N9H20 NAND and SPI Flash Memory Schematic (30)3.7NuDesign HMI-N9H20 Headphone Schematic (31)3.8NuDesign HMI-N9H20 JTAG and UART Schematic (32)3.9NuDesign HMI-N9H20 Audio Codec Controller Schematic (33)3.10NuDesign TFT-LCD4.3 LCD Controller Schematic (34)3.11NuDesign SPI2UART(B) Controller Schematic (35)4Revision History (36)Oct. 02, 20191 OverviewThe NK-N9H20 system includes boards NuDesign HMI-N9H20 and NuDesign TFT-LCD4.3 that is a general development board for N9H20K51N series by which users can develop and verify the application program easily. The NuDesign HMI-N9H20 includes Audio controller, USB 2.0 HS Device controller, SPI to UART controller, 24-bit LCD controller and integrated 32MB DDR2 memory, SRAM and external device with DMA request and ack.Oct. 02, 20192 NuDesign HMI-N9H20 Board IntroductionThe following figures show the NuDesign HMI-N9H20 development board, in which the front and back integrated 32-bit microcontroller embeds an outstanding CPU core ARM926EJ-S, runs up to 192MHz, with 16KB I-cache, 16 KB D-cache and MMU,32KB embedded SRAM and 12KB IBR(Internal Boot ROM) for booting from USB and SPI FLASH; Audio controller NAU8822A is a low power, high quality CODEC for portable and general purpose audio applications, it includes drivers for speaker, headphone, and differential or stereo line outputs, and integrates preamps for stereo differential microphones, significantly reducing external component requirements. The board also supports several extended connections. Users can use it to develop and verify applications to emulate the real behavior.Figure 2-1 NuDesign HMI-N9H20 PCB Board (Front)Figure 2-2 NuDesign HMI-N9H20 PCB Board (Back) Oct. 02, 2019Figure 2-3 NuDesign TFT-LCD4.3 PCB Board (Front) Oct. 02, 2019Figure 2-4 NuDesign TFT-LCD4.3 PCB Board (Back) Oct. 02, 2019Oct. 02, 2019 Figure 2-5 NuDesign SPI2UART(B) PCB Board (Front)2.1 NuDesign HMI-N9H20 Jumper Description2.1.1 Power Source●CON3: 5V DC Adaptor input connector.●CON4 & CON5: External Battery connector.●S3: Power ON/OFF Switch.Source Power port VIN VD33 CON3 Connect to 5V DC Adaptor 5V DC 3.3V S3 VD33 & VD18 Power Enable PWREN of U2 & U3 DC 3.3V Table 2-1 System Power ConnectorsOct. 02, 20192.1.2 LED Indicators2.1.3 Debug Connectors●CON11: Connector in target board NuDesign HMI-N9H20 (U1,●CN2: Connector in target board NuDesign SPI2UART(B) (U2, MINI58FDE)Oct. 02, 20192.1.4 USB Connectors●CON6: Mini USB Connector (USB 2.0 HS Device).2.1.5 Extended Connectors●CON1 and CON2: Show all extended pins in NuDesign HMI-N9H20.2.1.6 Buttons and JUMPER●K1~K6: Key pad button in NuDesign HMI-N9H20.●SW3: Reset button in NuDesign HMI-N9H20.●JP1: System configuration setting in NuDesign HMI-N9H20.2.1.7 Audio Connectors●CON9: Headphone Positive Output or Line Output Right and HeadphoneNegative Output or Line Output Left.Oct. 02, 20192.2 Pin Assignment for Extended ConnectorsThe NuDesign HMI-N9H20 provides the N9H20K5DN target chip functions on board and several extended connectors (NU1, NU2, NU3, NU4, NU5 and NU6) for user applications. The following table is the pin assignment for NuDesign HMI-N9H20.Oct. 02, 2019Oct. 02, 2019Oct. 02, 2019Oct. 02, 20192.3 NuDesign HMI-N9H20/TFT-LCD4.3/SPI2UART(B) PCB Placement The following figure shows the NuDesign each PCB placement.Figure 2-3 NuDesign HMI-N9H20 PCB Placement (Front) Oct. 02, 2019Figure 2-4 NuDesign HMI-N9H20 PCB Placement (Back) Oct. 02, 2019Figure 2-5 NuDesign TFT-LCD4.3 PCB Placement (Front) Oct. 02, 2019Figure 2-6 NuDesign TFT_LCD4.3 PCB Placement (Back) Oct. 02, 2019Oct. 02, 2019 Figure 2-7 NuDesign SPI2UART(B) PCB Placement (Front)2.4 NuDesign HMI-N9H20 N9H20K51N’s Control Pin FunctionsThe following table shows the NuDesign HMI-N9H20 Function Control Pins Assignment.Pin No. GPIO ADC AUDIO CMOS I2C I2S JTAG LCM-80 LCM NAND SD SPI SYSTEM UART USB3 GPB.0 SP_CLKO SD1_D1 UHL_DP14 GPB.14 SDA LMVSYNC5 GPB.13 SCL WDT_RSTn6 GPD.12 SPI0_CLK7 GPD.13 SPI0_CS0nOct. 02, 2019Oct. 02, 2019Table 2-13 N9H20K51N Pin Functions Assignment2.5 NuDesign HMI-N9H20 BOMOct. 02, 2019Oct. 02, 2019Oct. 02, 20192.6 NuDesign TFT-LCD4.3 BOM2.7 NuDesign SPI2UART(B) BOMOct. 02, 20193 NuDesign HMI-N9H20 Schematics3.1 NuDesign HMI-N9H20 Function Blocks SchematicOct. 02, 20193.2 NuDesign HMI-N9H20 N9H20K51N MPU SchematicOct. 02, 20193.3 NuDesign HMI-N9H20 Power Supply Schematic3.4 NuDesign HMI-N9H20 Keys and Configuration Schematic3.5 NuDesign HMI-N9H20 USB2.0 and SD0 Interface Schematic3.6 NuDesign HMI-N9H20 NAND and SPI Flash Memory SchematicOct. 02, 2019Oct. 02, 20193.7 NuDesign HMI-N9H20 Headphone SchematicOct. 02, 20193.8 NuDesign HMI-N9H20 JTAG and UART SchematicOct. 02, 20193.9 NuDesign HMI-N9H20 Audio Codec Controller SchematicOct. 02, 20193.10 NuDesign TFT-LCD4.3 LCD Controller SchematicOct. 02, 20193.11 NuDesign SPI2UART(B) Controller SchematicOct. 02, 2019 4 Revision HistoryImportant NoticeNuvoton Products are neither intended nor warranted for usage in systems or equipment, any malfunction or failure of which may cause loss of human life, bodily injury or severe property damage. Such applications are deemed, “Insecure Usage”.Insecure usage includes, but is not limited to: equipment for surgical implementation, atomic energy control instruments, airplane or spaceship instruments, the control or operation of dynamic, brake or safety systems designed for vehicular use, traffic signal instruments, all types of safety devices, and other applications intended to support or sustain life. All Insecure Usage shall be made at customer’s risk, and in the event that third parties lay claims to Nuvoton as a result of customer’s Insecure Usage, customer shall indemnify the damages and liabilities thus incurred by Nuvoton.。

西门子 SIMATIC 组态硬件和通讯连接, STEP 7 V5.3 版本 手册

更多支持

如果有任何技术问题,请联系西门子代表或代理商。 您可以在下列网页中查找联系人: /automation/partner

培训中心

西门子提供了很多培训教程,帮助您熟悉 SIMATIC S7 自动化系统。请联系当地的 培训中心,或位于德国纽伦堡(D 90327)的培训总部,以获取详细信息。 电话: 网址: +49 (911) 895-3200.

在线帮助中的主题“新增内容?”中极好地概括和介绍了最新的 STEP 7 新内容。

组态硬件和通讯连接,STEP 7 V5.3 版本 A5E00446503-01

iii

前言

STEP 7 文档包

本手册是文档包“STEP 7 基本信息”的一部分。 下表显示了 STEP 7 文档的总览:

文档 STEP 7 基础信息 • • • • • • STEP 7 V5.3,使用入门手册 使用 STEP 7 V5.3 编程 组态硬件和通讯连接,STEP 7 V5.3 版 本 从 S5 到 S7,变频器手册 用于 S7-300/400 的梯形图(LAD)/功能 块图(FBD)/语句表(STL)手册 S7-300/400 的标准功能及系统功能 提供了参考信息,并描述了编程语 6ES7810-4CA07-8BW1 言 LAD、FBD、STL、标准功能以 及系统功能,扩充了 STEP 7 基础 信息的范围。 用途 订货号

亚洲/澳洲(北京) 技术支持和授权

当地时间: 周一至周五, 8:00 - 5:00 PM 电话: 传真: +86 10 64 75 75 75 +86 10 64 74 74 74 格林威治 标准时间: +8:00

电子邮件: adsupport@

电子邮件: simatic.hotline@

ideskptopx操作手册

iDesktopX/iDesktop操作手册是为了帮助用户更好地使用iDesktopX/iDesktop软件而编写的指南。

手册主要包括以下内容:

1.概述:简要介绍iDesktopX/iDesktop的用途、特点和优势,以便用户了解

该软件的基本情况。

2.安装与配置:详细介绍如何安装和配置iDesktopX/iDesktop软件,包括硬

件要求、软件安装步骤、配置文件设置等,以确保软件正常运行。

3.界面与功能:介绍iDesktopX/iDesktop的界面和功能,包括桌面管理、图

标管理、任务管理、窗口管理等功能,以便用户能够熟练使用该软件。

4.定制与个性化:提供iDesktopX/iDesktop的定制和个性化建议,包括主题

设置、壁纸更换、快捷键设置等,以便用户根据自己的需求和习惯进行个性化设置。

5.常见问题与解决方案:列出使用iDesktopX/iDesktop过程中可能遇到的问

题和解决方法,帮助用户快速解决遇到的问题。

同时提供软件的日常维护和保养建议,以延长软件的使用寿命。

总之,iDesktopX/iDesktop操作手册旨在为用户提供全面而详细的软件使用指导和支持,帮助用户更好地发挥iDesktopX/iDesktop软件的性能并提高工作效率。

通过仔细阅读和遵循操作手册的指导,用户可以顺利地使用iDesktopX/iDesktop 软件进行桌面管理和个性化设置。

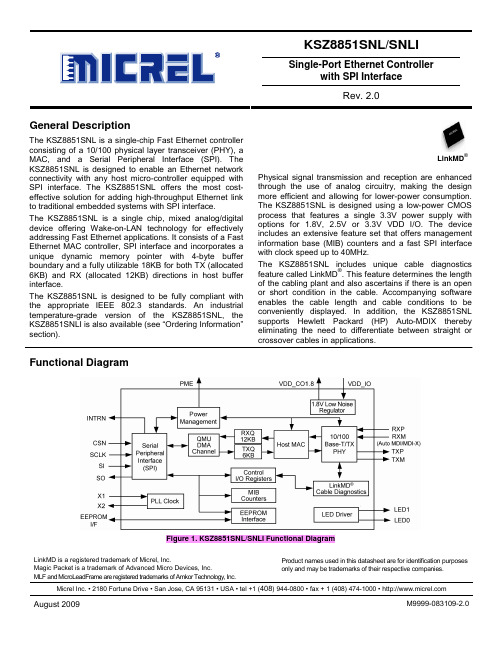

ksz8851snl_ds