ATMEGA16A-AU中文资料

ATmega16中文数据手册

4

ATmega16(L)

2466G–AVR–10/03

Hale Waihona Puke ATmega16(L)端口 D(PD7..PD0) 端口 D 为 8 位双向 I/O 口, 具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动特 性,可以输出和吸收大电流。作为输入使用时,若内部上拉电阻使能,则端口被外部电路 拉低时将输出电流。在复位过程中,即使系统时钟还未起振,端口 D 处于高阻状态。 端口 D 也可以用做其他不同的特殊功能,请参见 P61。 RESET XTAL1 XTAL2 AVCC AREF 复位输入引脚。持续时间超过最小门限时间的低电平将引起系统复位。门限时间见 P36Table 15。持续时间小于门限间的脉冲不能保证可靠复位。 反向振荡放大器与片内时钟操作电路的输入端。 反向振荡放大器的输出端。 AVCC 是端口 A 与 A/D 转换器的电源。 不使用 ADC 时, 该引脚应直接与 VCC 连接。 使用 ADC 时应通过一个低通滤波器与 VCC 连接。 A/D 的模拟基准输入引脚。 本数据手册包含了一些简单的代码例子以说明如何使用芯片各个不同的功能模块。这些 例子都假定在编译之前已经包含了正确的头文件。有些 C 编译器在头文件里并没有包含 位定义,而且各个 C 编译器对中断处理有自己不同的处理方式。请注意查阅相关文档以 获取具体的信息。

SPI

USART

+ -

COMP. INTERFACE

PORTB DIGITAL INTERFACE

PORTD DIGITAL INTERFACE

PORTB DRIVERS/BUFFERS

PORTD DRIVERS/BUFFERS

PB0 - PB7

PD0 - PD7

3

Atmega16多功能示波器 毕业设计

一、开展本课题的意义及工作内容:课题意义:数字存储示波器是集数据采集和模拟示波器优点于一身的一种精密测量设备,可以将其看作带有显示功能的数据采集系统,亦可将其看作是具有量化存储功能的模拟示波器。

与数据采集系统比,它一般有很多优点:如(1)更宽的输入频带;(2)更高的采样速率;(3)更深的存储深度,并有着数据采集系统所不具备的:直观屏幕显示功能;等效采样等等。

工作内容:利用单片机设计数字存储示波器。

用软件和硬件相结合快速把模拟信号转换为数字量,核心是用avr 单片机内带的10位AD 的转换器技术。

其模拟量通过示波器显示出来。

包括:数据采集模块,数据存储模块,数据输出模块。

二、课题预期达到的效果:(1)要求单边输入,不需要加入前级,可测0-5V 20K 以下任意波形。

双边输入,需要接入前级电路。

+ - 5V 范围。

(2)要求仪器的输入阻抗大于100k,垂直分辨率为12级/div ,水平分辨率为12点/div ;设示波器显示屏水平刻度为7div ,垂直刻度为4div 。

(3)要求设置2s/div 、0.2ms/div 二档扫描速度,仪器的频率范围为DC~500hz ,误差≤5%,。

(4)要求设置1.0V/div 、1.2V/div 二挡垂直灵敏度,误差≤5%。

(5)观测波形无明显失真。

二、文献综述(1) 前言示波器是最常用的一种电子测量仪器,能够直接有效地将被测信号显示出来,方便观察和测试被测信号的各种参数,完成其它测量仪器达不到的目的,是电子工程师完成电路设计、调试的有利工具。

主要研究内容目标特色 数字存储示波器是随着数字集成电路技术的发展而出现的新型智能化示波器,已经成为电子测量领域的基础测试仪器。

随着新技术、新器件的发展,它正在向宽带化、模块化、多功能和网络化的方向发展。

数字存储示波器的优势是可以实现高带宽及强大的分析功能.现在高端数字存储示波器的实时带宽已达到20GHZ ,可以广泛应用于各种千兆以太网、光通讯等测试领域。

ATmega16实验板使用说明书

Atmega16实验板说明书硬件资料介绍 (2)调试软件安装 (3)编译环境的使用 (8)建立新的工程 (15)资料和例程 (18)注意:使用时先把调试器和开发板用数据线连起来,再插上USB线;停止使用时应先断开USB线切断电源,才能拔下数据线,否则可能会损坏调试器。

硬件资料介绍实验套件共分3部分,开发板,调试器,数据线(1根usb线,1根串口线)。

开发板文件夹图片/原理图里面有开发板的原理图图片和protel dxp 原理图文件。

如果开发板是没有焊好的套件可以对照元器件参数表和已焊好的图片(图片文件夹里有)先把开发板焊接完成。

焊接完成后先用万用表测量一下5V 与GND 之间是否短路,确定没有短路之后,插上USB 线接到电脑上,弹上开关SW1电源指示灯D1亮,说明电源已接通。

调试器调试软件安装要实现开发调试需要安装三个软件:PL2303驱动,avr studio 4,WinAVR。

这三个软件都在软件这个文件夹里。

首先安装usb驱动PL2303,如图点下一步。

点完成就可以了。

然后把调试器和电脑通过USB线联机。

如图这时调试器上的电源指示灯和信号指示灯都亮,而且电脑开始发现新硬件,新硬件可以安装使用。

这说明已经建立起连接,然后右击我的电脑—>属性—>硬件—>设备管理器,打开设备管理器界面,点开端口(COM和LPT)的“+”如图。

其中的Prolific usb-to-Serial Comm Port(COMx)就是调试器的usb设备。

端口号是多少根据个人电脑情况可能有差异。

下面我们要修改端口号,因为调试器里只提供COM1-COM3的通讯。

双击Prolific usb-to-Serial Comm Port(COMx)选项,弹出端口设置对话框,如图然后选端口设置—>高级,在端口号中选一个没有被占用且3以内的COM口,我的电脑上没有串口,我选的是COM1,如图然后点确定,重新打开设备管理器再看一下端口情况。

ATMEGA16A中文资料

ATMEGA16A中文资料高性能,低功耗AVR 8-bit微控制器•高级RISC建筑– 131条指令–绝大多数为单时钟周期执行– 32 x 8通用工作寄存器–全静态工作–高达16吞吐量在MIPS 16 MHz–片2—cycle乘数高耐久性非易失性内存段– 16K字节的程序存储器,在系统内可编程Flash– 512字节的EEPROM– 1K字节内部SRAM–写/擦除周期:10,000闪光/ 100,000的EEPROM–数据保存:在20年85°C/100年在25°C(1)–可选引导具有独立锁定Bits代码段•在系统编程的片上引导程序•真Read-While-Write操作–锁编程软件安全JTAG (IEEE std。

1149.1兼容)接口–边界扫描功能根据JTAG标准–广泛的片上调试支持–编程闪存,EEPROM,熔丝位和锁定Bits通过JTAG接口外设特点–两个8—bit定时器/计数器具有独立预分频器和比较模式–一个16-bit定时器/计数器具有独立预分频器,比较功能和捕捉模式–实时计数器具有独立振荡器–四PWM频道– 8-channel, 10-bit ADC• 8单端通道• 7在TQFP 包装差分通道只有• 2在1x, 10x,差分通道具有可编程增益或200x–面向字节的两线串行接口可编程串行USART的––主/从串行接口SPI–可编程看门狗定时器具有独立片内振荡器–片内模拟比较器单片机的特殊功能–上电复位和可编程的掉电检测–内部振荡器校准RC–外部和内部中断源– 6种睡眠模式:空闲,ADC降噪,省电,省电,待机和扩展待机I / O和封装– 32可编程I / O线– 40—pin PDIP, 44—lead TQFP,和44—pad QFN/MLF 工作电压– 2。

7为- 5。

5V ATmega16A速度等级– 0 —为16 MHz ATmega16A功耗@ 1 MHz, 3V,和25°C为ATmega16A–活动:0。

ATMEGA16的寄存器详细说明

ISC01

ISC00

INT0中断

0

0

低电平中断

0

1

INT1 引脚上任意的逻辑电平变化都将引发中断

1

0

下降沿中断

1

1

上升沿中断

3.通用中断屏蔽寄存器 GICR

bit7

bit6

bit5

INT1

INT0

INT2

INT1:使能外部中断请求1 INT0:使能外部中断请求0 INT2:使能外部中断请求2

4.通用中断标志寄存器 GIFR

0x24

INT2

外部中断请求2

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ 6

☆萧联珠☆

☆azhu_uestc@

Atmega16 寄存器

20

0x26

TIMER0 COMP

21

0x28

SPM_RDY

定时器/ 计数器0 比较匹配 保存程序存储器内容就绪

1.状态寄存器 SREG

定时器/计数器1事件捕捉

7

0x0c

TIMER1 COMPA

定时器/计数器1比较匹配 A

8

0x0e

TIMER1 COMPB

定时器/计数器1比较匹配B

9

0x10

TIMER1 OVF

定时器/计数器1溢出

10

0x12

TIMER0 OVF

定时器/计数器0溢出

11

0x14

SPI,STC

SPI 串行传输结束

12

0x16

Bit4

Bit3

Bit2

Bit1

Bit0

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ 4

Atmega16单片机介绍

Atmega16单片机介绍ATmega16是基于增强的AVR RISC结构的低功耗8 位CMOS微控制器。

由于其先进的指令集以及单时钟周期指令执行时间,ATmega16 的数据吞吐率高达1 MIPS/MHz,从而可以缓减系统在功耗和处理速度之间的矛盾。

ATmega16 AVR 内核具有丰富的指令集和32 个通用工作寄存器。

所有的寄存器都直接与算逻单元(ALU) 相连接,使得一条指令可以在一个时钟周期内同时访问两个独立的寄存器。

这种结构大大提高了代码效率,并且具有比普通的CISC 微控制器最高至10 倍的数据吞吐率。

ATmega16 有如下特点:16K字节的系统内可编程Flash(具有同时读写的能力,即RWW),512 字节EEPROM,1K 字节SRAM,32 个通用I/O 口线,32 个通用工作寄存器,用于边界扫描的JTAG 接口,支持片内调试与编程,三个具有比较模式的灵活的定时器/ 计数器(T/ C),片内/外中断,可编程串行USART,有起始条件检测器的通用串行接口,8路10位具有可选差分输入级可编程增益(TQFP 封装) 的ADC ,具有片内振荡器的可编程看门狗定时器,一个SPI 串行端口,以及六个可以通过软件进行选择的省电模式。

工作于空闲模式时CPU 停止工作,而USART、两线接口、A/D 转换器、SRAM、T/C、SPI 端口以及中断系统继续工作;掉电模式时晶体振荡器停止振荡,所有功能除了中断和硬件复位之外都停止工作;在省电模式下,异步定时器继续运行,允许用户保持一个时间基准,而其余功能模块处于休眠状态;ADC 噪声抑制模式时终止CPU 和除了异步定时器与ADC 以外所有I/O 模块的工作,以降低ADC 转换时的开关噪声;Standby 模式下只有晶体或谐振振荡器运行,其余功能模块处于休眠状态,使得器件只消耗极少的电流,同时具有快速启动能力;扩展Standby 模式下则允许振荡器和异步定时器继续工作。

ATMEGA16A中文资料#(精选.)

ATMEGA16A中文资料高性能,低功耗AVR 8-bit微控制器•高级RISC建筑– 131条指令–绝大多数为单时钟周期执行– 32 x 8通用工作寄存器–全静态工作–高达16吞吐量在MIPS 16 MHz–片2-cycle乘数高耐久性非易失性内存段– 16K字节的程序存储器,在系统内可编程Flash– 512字节的EEPROM– 1K字节内部SRAM–写/擦除周期:10,000闪光/ 100,000的EEPROM–数据保存:在20年85°C/100年在25°C(1)–可选引导具有独立锁定Bits代码段•在系统编程的片上引导程序•真Read-While-Write操作–锁编程软件安全JTAG (IEEE std. 1149.1兼容)接口–边界扫描功能根据JTAG标准–广泛的片上调试支持–编程闪存,EEPROM,熔丝位和锁定Bits通过JTAG接口外设特点–两个8-bit定时器/计数器具有独立预分频器和比较模式–一个16-bit定时器/计数器具有独立预分频器,比较功能和捕捉模式–实时计数器具有独立振荡器–四PWM频道– 8-channel, 10-bit ADC• 8单端通道• 7在TQFP 包装差分通道只有• 2在1x, 10x,差分通道具有可编程增益或200x–面向字节的两线串行接口可编程串行USART的––主/从串行接口SPI–可编程看门狗定时器具有独立片内振荡器–片内模拟比较器单片机的特殊功能–上电复位和可编程的掉电检测–内部振荡器校准RC–外部和内部中断源– 6种睡眠模式:空闲,ADC降噪,省电,省电,待机和扩展待机I / O和封装– 32可编程I / O线– 40-pin PDIP, 44-lead TQFP,和44-pad QFN/MLF 工作电压– 2.7为- 5.5V ATmega16A速度等级– 0 -为16 MHz ATmega16A功耗@ 1 MHz, 3V,和25°C为ATmega16A–活动:0.6 mA–空闲模式:0.2 mA–掉电模式:< 1µA1.引脚配置图1-1.接脚分布 ATmega16A2.概述该ATmega16A是一种低功耗微控制器CMOS 8-bit关于加强AVR基础的RISC 架构.通过执行在一个时钟周期,ATmega16A强大的指令实现吞吐量接近每1 MIPS MHz允许系统设计师能够优化功耗与处理速度.2.1 框图该AVR内核具有丰富的指令与32一般工作寄存器的设置.所有32寄存器都直接连接到算术逻辑单元(ALU),允许两个独立寄存器进行访问的,单一的在一个时钟周期执行的指令.由此产生的建筑是提高了代码效率,同时实现吞吐量达快十倍con-ventional CISC微控制器.该ATmega16A提供了以下功能:16K字节的系统内可编程Flash程序存储器Read-While-Write能力,512字节EEPROM,1K字节SRAM, 32 通用I / O线,32通用工作寄存器,用于边界JTAG接口扫描,片上调试支持和编程,三个灵活定时器/计数器与com-削减模式,内部和外部中断,串行可编程的USART,一个字节为导向两线串行接口,一个8-channel, 10-bit ADC可选差分输入级与可编程增益(TQFP 包装只),一个可编程看门狗定时器内部振荡器的振荡器,一个SPI串行端口,以及六个软件设置省电模式.空闲模式停止在CPU同时允许的USART,两线接口,A / D转换器,SRAM,定时器/计数器,SPI口,外中断系统继续工作.掉电模式,保存寄存器内容,但冻结振荡器,禁用,直到下一个外部间的所有其他芯片功能,rupt或硬件复位.在省电模式下,异步定时器继续运行,允许用户保持一个时间基准,而其余的设备正在睡觉.该ADC降噪模式停止CPU和所有的I /除了异步定时器和O模块ADC,以最大限度地降低开关噪声在ADC转换.在待机模式下,crystal/reso- nator振荡器运行,而在器件其它部分在睡觉.这允许非常快速启动结合低功耗.在扩展待机模式下,主振荡器和异步定时器继续运行.该设备是采用Atmel的高密度非易失性内存技术.在上闪存芯片ISP允许程序存储器进行重新编程,通过SPI串行在系统接口,由传统的非易失性存储器编程,或者通过片内引导程序运行在AVR核心.引导程序可以使用任何下载的应用程序接口在应用程序闪存方案.在Boot区软件将继续运行而应用Flash区更新,提供真正的Read-While-Write操作.通过结合一8-bit RISC CPU与系统内可编程闪存集成在一个芯片,Atmel的ATmega16A是一个功能强大的单片机,它提供了高度灵活和成本有效解决了许多嵌入式控制应用.该ATmega16A AVR是支持了若干方案和系统开发工具套件包括:C编译器,宏汇编,程序调试器/模拟器,在线仿真器,和评价kits.2.22.2.1引脚说明VCC数字供电电压.2.2.2GND地面.2.2.3端口A (PA7:PA0)作为一个港口的A / D转换器的模拟输入.端口A也可作为8-bit双向I / O端口,如果A / D转换器不使用.港口pins 可提供内部上拉电阻(每个位选中). PA口输出缓冲器具有sym-既吸收大电流驱动器和源能力韵律特征.当pins PA0到PA7作为投入使用的和被外部拉低,将输出电流,如果他们的内部上拉电阻器被激活.港口是一个pins三态时,复位过程中,即使系统时钟没有运行.港口B (PB7:PB0)港口B是8-bit双向I /内部上拉电阻(每个位选中)O端口.该港口B输出缓冲器具有高汇和源对称的驱动特性能力.作为输入,端口B pins被外部拉低时将输出电流若拉电阻器被激活.港口B pins为三态时,复位过程中,即使系统时钟没有运行.港口B也可以用不同的特殊功能的ATmega16A作为上市职能页面57.2.2.5港口C (PC7:PC0)港口C是8-bit双向I /内部上拉电阻(每个位选中)O端口.该港口C输出缓冲器具有高汇和源对称的驱动特性能力.作为输入,端口C pins被外部拉低时将输出电流若拉电阻器被激活.港口C pins为三态时,复位过程中,即使系统时钟没有运行.如果JTAG接口使能,上拉电阻器pins PC5(TDI), PC3(TMS)和PC2(TCK)将被激活,即使发生复位.港口C还担任了JTAG接口功能和其他的特殊功能ATmega16A作为上市页面60.2.2.6港口D (PD7:PD0)港口D是8-bit双向I /内部上拉电阻(每个位选中)O端口.该港口D输出缓冲器具有高汇和源对称的驱动特性能力.作为输入,端口D pins被外部拉低时将输出电流若拉电阻器被激活.港口D pins为三态时,复位过程中,即使系统时钟没有运行.港口D也可以用不同的特殊功能的ATmega16A作为上市职能页面622.2.7复位复位输入.此管脚上出现了比最小脉冲长度较长的低级别将产生复位,即使系统时钟没有运行.最小脉冲宽度是由于在表27-2页296.更短的脉冲则不能保证可靠复位.2.2.8XTAL1输入到反相振荡放大器和输入到内部时钟工作电路.2.2.9XTAL2振荡器的输出反相放大器.AVCCAVCC是端口A和A / D转换的电源.它应该从外部con- 连接到VCC,即使ADC不使用.如果ADC使用,它应该连接到VCC通过一个低通滤波器.2.2.11AREFAREF是为A / D转换器的模拟参考引脚.3.资源一个开发工具,应用手册和说明书一整套可供下载/avr.注意:1.4.数据保留可靠性鉴定结果表明,该预测数据保留故障率要少得多比1 PPM对在20或85°C年100年在25°C5. 寄存器摘要注释:1.当OCDEN保险丝未编程,OSCCAL的寄存器总是访问该地址.请参阅调试ger具体文件的详细信息如何使用OCDR 寄存器.2.请参考详细的USART如何访问UBRRH与UCSRC寄存器的描述.3.对于未来的产品兼容,保留bits应写入零,如果访问.保留的I / O内存地址不应该被写入.4.状态标志清零记录一些人对他们的逻辑.请注意,CBI和SBI指示将操作所有在我bits / O的寄存器,记录一旗一回任何内容设置,从而扫清了国旗.指令的CBI和SBI 与寄存器$00工作$1F只.6.指令集汇总8.包装信息44A40P644M19.勘误表本节中的版本号是指该ATmega16A器件版本.9.1ATmega16A牧师. N的转速. Q••••第一个模拟比较器的转换可能会推迟中断可能会丢失记录在异步定时器定时器寄存器IDCODE的面具输入数据TDI读数使用ST或STS设置EERE位EEPROM触发意外的中断请求1.第一个模拟比较器的转换可能会推迟如果该设备是由一个缓慢上升VCC,第一个模拟比较器转换将需要更长的时间比预期的一些设备.问题的修复程序/解决方法当器件上电或复位,禁用然后启用theAnalog比较在第一次转换.2.中断可能会丢失记录在异步定时器定时器寄存器中断将被丢失,如果是一个计时器寄存器定时器时钟同步时写入异步定时器/计数器寄存器(TCNTx)是0x00.问题的修复程序/解决方法务必检查异步定时器/计数器寄存器也没有,也不值0xFF前记录 0x00到异步定时器控制寄存器(TCCRx),异步定时器计数器寄存器(TCNTx),或异步输出比较寄存器 (OCRx).3. IDCODE的面具输入数据TDI该JTAG指令IDCODE的是不能正常工作.数据到成功的设备在更新取代由all-ones - DR的.解决方法问题的修正/––如果ATmega16A是唯一的设备在扫描链,问题是不可见的.选择通过发出IDCODE指令的ID设备ATmega16A 寄存器或通过输入TAP控制器Test-Logic-Reset读出状态它的设备ID 寄存器和可能的数据内容从设备的成功扫描链.发出指示,而旁路读数的ATmega16A设备ID的边界扫描链上的设备寄存器.如果在边界所有设备的设备IDs扫描链必须被捕获同时,ATmega16A必须拳头链中的设备.–4. 读数 EEPROM的使用ST或STS设置EERE位触发意外的中断请求.读数 EEPROM的使用ST或STS命令设置在EERE EECR reg-位ister触发一个意想不到的EEPROM的中断请求.解决方法问题的修正/始终使用OUT或SBI要在EERE EECR10.修订历史数据表请注意,本节所指页码提及这个文件.该本节中提到的修订是指对文件的修改.致8154B – 07/091.2.更新“勘误表”第343.更新了与 Atmel的新地址的最后一页.致8154A – 06/081.初始的版本(在ATmega16 / L的基于数据表的修订2466R-AVR-05/08)变化做comparted ATmega16 / L的数据表修改2466R-AVR-05/08: -更新的说明“堆栈指针”页上12.-所有的电气特性会移至“电气特性”页上293.- 寄存器描述转移到分节在每章末尾.-新增“速度等级”第295.-在新图“典型特征”页上305.-新“订购信息”13.最新文件仅供参考已改成word文本。

ATMEGA16A中文资料

ATMEGA16A中文资料高性能,低功耗AVR 8-bit微控制器•高级RISC建筑– 131条指令–绝大多数为单时钟周期执行– 32 x 8通用工作寄存器–全静态工作–高达16吞吐量在MIPS 16 MHz–片2-cycle乘数高耐久性非易失性存段– 16K字节的程序存储器,在系统可编程Flash– 512字节的EEPROM– 1K字节部SRAM–写/擦除周期:10,000闪光/ 100,000的EEPROM–数据保存:在20年85°C/100年在25°C(1)–可选引导具有独立锁定Bits代码段•在系统编程的片上引导程序•真Read-While-Write操作–锁编程软件安全JTAG (IEEE std. 1149.1兼容)接口–边界扫描功能根据JTAG标准–广泛的片上调试支持–编程闪存,EEPROM,熔丝位和锁定Bits通过JTAG接口外设特点–两个8-bit定时器/计数器具有独立预分频器和比较模式–一个16-bit定时器/计数器具有独立预分频器,比较功能和捕捉模式–实时计数器具有独立振荡器–四PWM频道– 8-channel, 10-bit ADC• 8单端通道• 7在TQFP 包装差分通道只有• 2在1x, 10x,差分通道具有可编程增益或200x–面向字节的两线串行接口可编程串行USART的––主/从串行接口SPI–可编程看门狗定时器具有独立片振荡器–片模拟比较器单片机的特殊功能–上电复位和可编程的掉电检测–部振荡器校准RC–外部和部中断源– 6种睡眠模式:空闲,ADC降噪,省电,省电,待机和扩展待机I / O和封装– 32可编程I / O线– 40-pin PDIP, 44-lead TQFP,和44-pad QFN/MLF 工作电压– 2.7为- 5.5V ATmega16A速度等级– 0 -为16 MHz ATmega16A功耗 1 MHz, 3V,和25°C为ATmega16A–活动:0.6 mA–空闲模式:0.2 mA–掉电模式:< 1µA1.引脚配置图1-1.接脚分布 ATmega16A2.概述该ATmega16A是一种低功耗微控制器CMOS 8-bit关于加强AVR基础的RISC 架构.通过执行在一个时钟周期,ATmega16A强大的指令实现吞吐量接近每1 MIPS MHz允许系统设计师能够优化功耗与处理速度.2.1 框图该AVR核具有丰富的指令与32一般工作寄存器的设置.所有32寄存器都直接连接到算术逻辑单元(ALU),允许两个独立寄存器进行访问的,单一的在一个时钟周期执行的指令.由此产生的建筑是提高了代码效率,同时实现吞吐量达快十倍con-ventional CISC微控制器.该ATmega16A提供了以下功能:16K字节的系统可编程Flash程序存储器Read-While-Write能力,512字节EEPROM,1K字节SRAM, 32 通用I / O线,32通用工作寄存器,用于边界JTAG接口扫描,片上调试支持和编程,三个灵活定时器/计数器与com-削减模式,部和外部中断,串行可编程的USART,一个字节为导向两线串行接口,一个8-channel, 10-bit ADC可选差分输入级与可编程增益(TQFP 包装只),一个可编程看门狗定时器部振荡器的振荡器,一个SPI串行端口,以及六个软件设置省电模式.空闲模式停止在CPU同时允许的USART,两线接口,A / D转换器,SRAM,定时器/计数器,SPI口,外中断系统继续工作.掉电模式,保存寄存器容,但冻结振荡器,禁用,直到下一个外部间的所有其他芯片功能,rupt或硬件复位.在省电模式下,异步定时器继续运行,允许用户保持一个时间基准,而其余的设备正在睡觉.该ADC降噪模式停止CPU和所有的I /除了异步定时器和O模块ADC,以最大限度地降低开关噪声在ADC转换.在待机模式下,crystal/reso- nator振荡器运行,而在器件其它部分在睡觉.这允许非常快速启动结合低功耗.在扩展待机模式下,主振荡器和异步定时器继续运行.该设备是采用Atmel的高密度非易失性存技术.在上闪存芯片ISP允许程序存储器进行重新编程,通过SPI串行在系统接口,由传统的非易失性存储器编程,或者通过片引导程序运行在AVR核心.引导程序可以使用任何下载的应用程序接口在应用程序闪存方案.在Boot区软件将继续运行而应用Flash区更新,提供真正的Read-While-Write操作.通过结合一8-bit RISC CPU与系统可编程闪存集成在一个芯片,Atmel的ATmega16A是一个功能强大的单片机,它提供了高度灵活和成本有效解决了许多嵌入式控制应用.该ATmega16A AVR是支持了若干方案和系统开发工具套件包括:C编译器,宏汇编,程序调试器/模拟器,在线仿真器,和评价kits.2.22.2.1引脚说明VCC数字供电电压.2.2.2GND地面.2.2.3端口A (PA7:PA0)作为一个港口的A / D转换器的模拟输入.端口A也可作为8-bit双向I / O端口,如果A / D转换器不使用.港口pins 可提供部上拉电阻(每个位选中). PA口输出缓冲器具有sym-既吸收大电流驱动器和源能力韵律特征.当pins PA0到PA7作为投入使用的和被外部拉低,将输出电流,如果他们的部上拉电阻器被激活.港口是一个pins三态时,复位过程中,即使系统时钟没有运行.港口B (PB7:PB0)港口B是8-bit双向I /部上拉电阻(每个位选中)O端口.该港口B输出缓冲器具有高汇和源对称的驱动特性能力.作为输入,端口B pins被外部拉低时将输出电流若拉电阻器被激活.港口B pins为三态时,复位过程中,即使系统时钟没有运行.港口B也可以用不同的特殊功能的ATmega16A作为上市职能页面57.2.2.5港口C (PC7:PC0)港口C是8-bit双向I /部上拉电阻(每个位选中)O端口.该港口C输出缓冲器具有高汇和源对称的驱动特性能力.作为输入,端口C pins被外部拉低时将输出电流若拉电阻器被激活.港口C pins为三态时,复位过程中,即使系统时钟没有运行.如果JTAG接口使能,上拉电阻器pins PC5(TDI), PC3(TMS)和PC2(TCK)将被激活,即使发生复位.港口C还担任了JTAG接口功能和其他的特殊功能ATmega16A作为上市页面60.2.2.6港口D (PD7:PD0)港口D是8-bit双向I /部上拉电阻(每个位选中)O端口.该港口D输出缓冲器具有高汇和源对称的驱动特性能力.作为输入,端口D pins被外部拉低时将输出电流若拉电阻器被激活.港口D pins为三态时,复位过程中,即使系统时钟没有运行.港口D也可以用不同的特殊功能的ATmega16A作为上市职能页面622.2.7复位复位输入.此管脚上出现了比最小脉冲长度较长的低级别将产生复位,即使系统时钟没有运行.最小脉冲宽度是由于在表27-2页296.更短的脉冲则不能保证可靠复位.2.2.8XTAL1输入到反相振荡放大器和输入到部时钟工作电路.2.2.9XTAL2振荡器的输出反相放大器.AVCCAVCC是端口A和A / D转换的电源.它应该从外部con- 连接到VCC,即使ADC不使用.如果ADC使用,它应该连接到VCC通过一个低通滤波器.2.2.11AREFAREF是为A / D转换器的模拟参考引脚.3.资源一个开发工具,应用手册和说明书一整套可供下载www.atmel./avr.注意:1.4.数据保留可靠性鉴定结果表明,该预测数据保留故障率要少得多比1 PPM对在20或85°C年100年在25°C5. 寄存器摘要注释:1.当OCDEN保险丝未编程,OSCCAL的寄存器总是访问该地址.请参阅调试ger具体文件的详细信息如何使用OCDR 寄存器.2.请参考详细的USART如何访问UBRRH与UCSRC寄存器的描述.3.对于未来的产品兼容,保留bits应写入零,如果访问.保留的I / O存地址不应该被写入.4.状态标志清零记录一些人对他们的逻辑.请注意,CBI和SBI指示将操作所有在我bits / O的寄存器,记录一旗一回任何容设置,从而扫清了国旗.指令的CBI和SBI 与寄存器$00工作$1F只.6.指令集汇总8.包装信息44A40P644M19.勘误表本节中的版本号是指该ATmega16A器件版本.9.1ATmega16A牧师. N的转速. Q••••第一个模拟比较器的转换可能会推迟中断可能会丢失记录在异步定时器定时器寄存器IDCODE的面具输入数据TDI读数使用ST或STS设置EERE位EEPROM触发意外的中断请求1.第一个模拟比较器的转换可能会推迟如果该设备是由一个缓慢上升VCC,第一个模拟比较器转换将需要更长的时间比预期的一些设备.问题的修复程序/解决方法当器件上电或复位,禁用然后启用theAnalog比较在第一次转换.2.中断可能会丢失记录在异步定时器定时器寄存器中断将被丢失,如果是一个计时器寄存器定时器时钟同步时写入异步定时器/计数器寄存器(TCNTx)是0x00.问题的修复程序/解决方法务必检查异步定时器/计数器寄存器也没有,也不值0xFF前记录 0x00到异步定时器控制寄存器(TCCRx),异步定时器计数器寄存器(TCNTx),或异步输出比较寄存器 (OCRx).3. IDCODE的面具输入数据TDI该JTAG指令IDCODE的是不能正常工作.数据到成功的设备在更新取代由all-ones - DR的.解决方法问题的修正/––如果ATmega16A是唯一的设备在扫描链,问题是不可见的.选择通过发出IDCODE指令的ID设备ATmega16A 寄存器或通过输入TAP控制器Test-Logic-Reset读出状态它的设备ID 寄存器和可能的数据容从设备的成功扫描链.发出指示,而旁路读数的ATmega16A设备ID的边界扫描链上的设备寄存器.如果在边界所有设备的设备IDs扫描链必须被捕获同时,ATmega16A必须拳头链中的设备.–4. 读数 EEPROM的使用ST或STS设置EERE位触发意外的中断请求.读数 EEPROM的使用ST或STS命令设置在EERE EECR reg-位ister触发一个意想不到的EEPROM的中断请求.解决方法问题的修正/始终使用OUT或SBI要在EERE EECR10.修订历史数据表请注意,本节所指页码提及这个文件.该本节中提到的修订是指对文件的修改.致8154B – 07/091.2.更新“勘误表”第343.更新了与 Atmel的新地址的最后一页.致8154A – 06/081.初始的版本(在ATmega16 / L的基于数据表的修订2466R-AVR-05/08)变化做comparted ATmega16 / L的数据表修改2466R-AVR-05/08: -更新的说明“堆栈指针”页上12.-所有的电气特性会移至“电气特性”页上293.- 寄存器描述转移到分节在每章末尾.-新增“速度等级”第295.-在新图“典型特征”页上305.-新“订购信息”13.。

AVR教程系列一(6):ATmega16 简介(一)

ATmega16 简介ATmega16是基于增强的AVR RISC结构的低功耗8 位CMOS微控制器。

由于其先进的指令集以及单时钟周期指令执行时间,ATmega16 的数据吞吐率高达1 MIPS/MHz,从而可以缓减系统在功耗和处理速度之间的矛盾。

ATmega16 AVR 内核具有丰富的指令集和32 个通用工作寄存器。

所有的寄存器都直接与算逻单元(ALU) 相连接,使得一条指令可以在一个时钟周期内同时访问两个独立的寄存器。

这种结构大大提高了代码效率,并且具有比普通的CISC 微控制器最高至10 倍的数据吞吐率。

ATmega16 有如下特点:16K字节的系统内可编程Flash(具有同时读写的能力,即RWW),512 字节EEPROM,1K 字节SRAM,32 个通用I/O 口线,32 个通用工作寄存器,用于边界扫描的JTAG 接口,支持片内调试与编程,三个具有比较模式的灵活的定时器/ 计数器(T/C),片内/外中断,可编程串行USART,有起始条件检测器的通用串行接口,8路10位具有可选差分输入级可编程增益(TQFP 封装) 的ADC ,具有片内振荡器的可编程看门狗定时器,一个SPI 串行端口,以及六个可以通过软件进行选择的省电模式。

工作于空闲模式时CPU 停止工作,而USART、两线接口、A/D 转换器、SRAM、T/C、SPI 端口以及中断系统继续工作;掉电模式时晶体振荡器停止振荡,所有功能除了中断和硬件复位之外都停止工作;在省电模式下,异步定时器继续运行,允许用户保持一个时间基准,而其余功能模块处于休眠状态; ADC 噪声抑制模式时终止CPU 和除了异步定时器与ADC 以外所有I/O 模块的工作,以降低ADC 转换时的开关噪声; Standby 模式下只有晶体或谐振振荡器运行,其余功能模块处于休眠状态,使得器件只消耗极少的电流,同时具有快速启动能力;扩展Standby 模式下则允许振荡器和异步定时器继续工作。

ATMEGA16

ATMEGA16ATmega16是基于增强的AVR RISC结构的低功耗8 位CMOS微控制器。

由于其先进的指令集以及单时钟周期指令执行时间,ATmega16 的数据吞吐率高达1 MIPS/MHz,从而可以减缓系统在功耗和处理速度之间的矛盾。

ATmega16 AVR 内核具有丰富的指令集和32 个通用工作寄存器。

所有的寄存器都直接与运算逻单元(ALU) 相连接,使得一条指令可以在一个时钟周期内同时访问两个独立的寄存器。

这种结构大大提高了代码效率,并且具有比普通的CISC 微控制器最高至10 倍的数据吞吐率。

ATmega16 有如下特点:16K字节的系统内可编程Flash(具有同时读写的能力,即RWW),512 字节EEPROM,1K 字节SRAM,32 个通用I/O 口线,32 个通用工作寄存器,用于边界扫描的JTAG 接口,支持片内调试与编程,三个具有比较模式的灵活的定时器/ 计数器(T/C),片内/外中断,可编程串行USART,有起始条件检测器的通用串行接口,8路10位具有可选差分输入级可编程增益(TQFP 封装) 的ADC ,具有片内振荡器的可编程看门狗定时器,一个SPI 串行端口,以及六个可以通过软件进行选择的省电模式。

工作于空闲模式时CPU 停止工作,而USART、两线接口、A/D 转换器、SRAM、T/C、SPI 端口以及中断系统继续工作;掉电模式时晶体振荡器停止振荡,所有功能除了中断和硬件复位之外都停止工作;在省电模式下,异步定时器继续运行,允许用户保持一个时间基准,而其余功能模块处于休眠状态; ADC 噪声抑制模式时终止CPU 和除了异步定时器与ADC 以外所有I/O 模块的工作,以降低ADC 转换时的开关噪声; Standby 模式下只有晶体或谐振振荡器运行,其余功能模块处于休眠状态,使得器件只消耗极少的电流,同时具有快速启动能力;扩展Standby 模式下则允许振荡器和异步定时器继续工作。

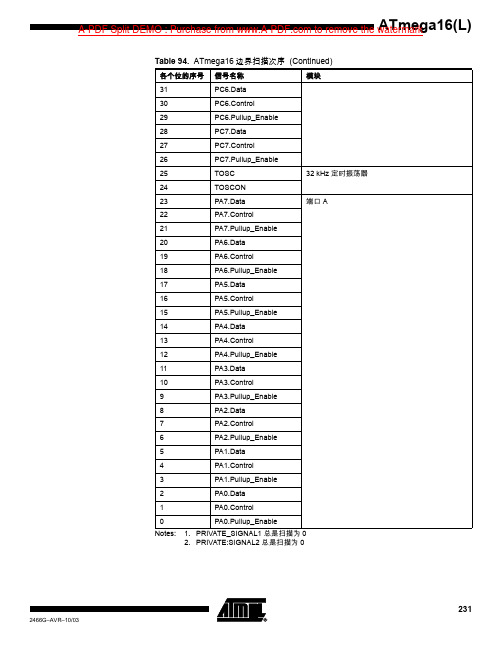

atmega16中文资料.0004

29

PC6.Pullup_Enable

28

PC7.Data

27

PC7.Control

26

PC7.Pullup_Enable

25

TOSC

32 kHz 定时振荡器

24

TOSCON

23

PA7.Data

端口 A

22

PA7.Control

21

PA7.Pullup_Enable

20

PA6.Data

19

PA6.Control

RWW 区

如果 Boot Loader 软件是对 RWW 区内的某一页进行编程,则可以从 Flash 中读取代码, 但只限于 NRWW 区内的代码。在 Flash 编程期间,用户软件必须保证没有对 RWW 区的 读访问。如果用户软件在编程过程中试图读取位于 RWW 区的代码 ( 如通过 call/jmp/lpm 指令或中断 ),软件可能会终止于一个未知状态。为了避免这种情况的发生,需要禁止中 断或将其转移到 Boot Loader 区。 Boot Loader 总是位于 NRWW 存储区。只要 RWW 区 处于不能读访问的状态,存储程序存储器控制和状态寄存器 (SPMCSR) 的 RWW 区忙标 志位 RWWSB 置位。编程结束后,要在读取 位于 RWW 区的代码之前通过软件清除 RWWSB。具体如何清除RWWSB请参见P238 “保存程序存储器控制寄存器 – SPMCR” 。

No Read-While-Write (NRWW) Section

Z-pointer Addresses NRWW Section

CPU is Halted during the Operation

234 ATmega16(L)

atmega16a-au数据手册_编程_烧写

P B 4(S S ) P B 3(A I N 1/O C 0) P B 2(A I N 0/I N T 2) P B 1(T 1) P B 0(X C K /T 0) G N D V C C P A 0(A D C 0) P A 1(A D C 1) P A 2(A D C 2) P A 3(A D C 3)(I N T 1) (O C 1B ) (O C 1A ) (I C P 1) (O C 2)P D 3 P D 4 P D 5 P D 6 P D 7 V C C G N D (S C L )P C 0 (S D A )P C 1 (T C K )P C 2 (T M S )P C 31. Pin ConfigurationsFigure 1-1.Pinout ATmega16APDIP(XCK/T0) PB0(T1) PB1 (INT2/AIN0) PB2 (OC0/AIN1) PB3(SS) PB4 (MOSI) PB5 (MISO) PB6 (SCK) PB7 RESET VCC GND XTAL2 XTAL1 (RXD) PD0 (TXD) PD1 (INT0) PD2 (INT1) PD3 (OC1B) PD4 (OC1A) PD5 (ICP1) PD6(MOSI) PB5 (MISO) PB6 (SCK) PB7 RESET VCC GND XTAL2 XTAL1 (RXD) PD0 (TXD) PD1 (INT0) PD2TQFP/QFN/MLFPA0 (ADC0) PA1 (ADC1) PA2 (ADC2) PA3 (ADC3) PA4 (ADC4) PA5 (ADC5) PA6 (ADC6) PA7 (ADC7) AREF GND AVCCPC7 (TOSC2) PC6 (TOSC1) PC5 (TDI) PC4 (TDO) PC3 (TMS) PC2 (TCK) PC1 (SDA) PC0 (SCL) PD7 (OC2)PA4 (ADC4) PA5 (ADC5) PA6 (ADC6) PA7 (ADC7) AREF GND AVCCPC7 (TOSC2) PC6 (TOSC1) PC5 (TDI) PC4 (TDO)NOTE:Bottom pad should be soldered to ground.2.OverviewThe ATmega16A is a low-power CMOS8-bit microcontroller based on the AVR enhanced RISCarchitecture.By executing powerful instructions in a single clock cycle,the ATmega16Aachieves throughputs approaching1MIPS per MHz allowing the system designer to optimizepower consumption versus processing speed.LOGICSPI2.1Block DiagramFigure 2-1.Block DiagramPA0 - PA7PC0 - PC7VCCPORTA DRIVERS/BUFFERSPORTC DRIVERS/BUFFERSGNDAVCCPORTA DIGITAL INTERFACEPORTC DIGITAL INTERFACEAREFMUX &ADCADCINTERFACETWIPROGRAM COUNTERPROGRAM FLASHSTACKPOINTERSRAMTIMERS/ COUNTERSINTERNALOSCILLATOROSCILLATORXTAL1INSTRUCTION REGISTERGENERAL PURPOSEWATCHDOGTIMEROSCILLATORREGISTERSXXTAL2INSTRUCTIONDECODERY MCU CTRL. & TIMINGRESETZCONTROLLINESAVR CPUALUSTATUS REGISTERINTERRUPTUNITEEPROMINTERNAL CALIBRATED OSCILLATORPROGRAMMINGUSART+ -COMP . INTERFACEPORTB DIGITAL INTERFACEPORTB DRIVERS/BUFFERSPB0 - PB7PORTD DIGITAL INTERFACEPORTD DRIVERS/BUFFERSPD0 - PD7The AVR core combines a rich instruction set with32general purpose working registers.All the 32registers are directly connected to the Arithmetic Logic Unit(ALU),allowing two independent registers to be accessed in one single instruction executed in one clock cycle.The resulting architecture is more code efficient while achieving throughputs up to ten times faster than con-ventional CISC microcontrollers.The ATmega16A provides the following features:16K bytes of In-System Programmable Flash Program memory with Read-While-Write capabilities,512bytes EEPROM,1K byte SRAM,32 general purpose I/O lines,32general purpose working registers,a JTAG interface for Boundary-scan,On-chip Debugging support and programming,three flexible Timer/Counters with com-pare modes,Internal and External Interrupts,a serial programmable USART,a byte oriented Two-wire Serial Interface,an8-channel,10-bit ADC with optional differential input stage with programmable gain(TQFP package only),a programmable Watchdog Timer with Internal Oscil-lator,an SPI serial port,and six software selectable power saving modes.The Idle mode stops the CPU while allowing the USART,Two-wire interface,A/D Converter,SRAM,Timer/Counters, SPI port,and interrupt system to continue functioning.The Power-down mode saves the register contents but freezes the Oscillator,disabling all other chip functions until the next External Inter-rupt or Hardware Reset.In Power-save mode,the Asynchronous Timer continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping.The ADC Noise Reduction mode stops the CPU and all I/O modules except Asynchronous Timer and ADC,to minimize switching noise during ADC conversions.In Standby mode,the crystal/reso-nator Oscillator is running while the rest of the device is sleeping.This allows very fast start-up combined with low-power consumption.In Extended Standby mode,both the main Oscillator and the Asynchronous Timer continue to run.The device is manufactured using Atmel’s high density nonvolatile memory technology.The On-chip ISP Flash allows the program memory to be reprogrammed in-system through an SPI serial interface,by a conventional nonvolatile memory programmer,or by an On-chip Boot program running on the AVR core.The boot program can use any interface to download the application program in the Application Flash memory.Software in the Boot Flash section will continue to run while the Application Flash section is updated,providing true Read-While-Write operation.By combining an8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega16A is a powerful microcontroller that provides a highly-flexible and cost-effective solution to many embedded control applications.The ATmega16A AVR is supported with a full suite of program and system development tools including:C compilers,macro assemblers,program debugger/simulators,in-circuit emulators, and evaluation kits.2.2Pin Descriptions2.2.1VCCDigital supply voltage.2.2.2GNDGround.2.2.3Port A(PA7:PA0)Port A serves as the analog inputs to the A/D Converter.Port A also serves as an8-bit bi-directional I/O port,if the A/D Converter is not used.Port pinscan provide internal pull-up resistors(selected for each bit).The Port A output buffers have sym-metrical drive characteristics with both high sink and source capability.When pins PA0to PA7are used as inputs and are externally pulled low,they will source current if the internal pull-upresistors are activated.The Port A pins are tri-stated when a reset condition becomes active,even if the clock is not running.2.2.4Port B(PB7:PB0)Port B is an8-bit bi-directional I/O port with internal pull-up resistors(selected for each bit).ThePort B output buffers have symmetrical drive characteristics with both high sink and sourcecapability.As inputs,Port B pins that are externally pulled low will source current if the pull-upresistors are activated.The Port B pins are tri-stated when a reset condition becomes active,even if the clock is not running.Port B also serves the functions of various special features of the ATmega16A as listed on page57.2.2.5Port C(PC7:PC0)Port C is an8-bit bi-directional I/O port with internal pull-up resistors(selected for each bit).ThePort C output buffers have symmetrical drive characteristics with both high sink and sourcecapability.As inputs,Port C pins that are externally pulled low will source current if the pull-upresistors are activated.The Port C pins are tri-stated when a reset condition becomes active,even if the clock is not running.If the JTAG interface is enabled,the pull-up resistors on pinsPC5(TDI),PC3(TMS)and PC2(TCK)will be activated even if a reset occurs.Port C also serves the functions of the JTAG interface and other special features of theATmega16A as listed on page60.2.2.6Port D(PD7:PD0)Port D is an8-bit bi-directional I/O port with internal pull-up resistors(selected for each bit).ThePort D output buffers have symmetrical drive characteristics with both high sink and sourcecapability.As inputs,Port D pins that are externally pulled low will source current if the pull-upresistors are activated.The Port D pins are tri-stated when a reset condition becomes active,even if the clock is not running.Port D also serves the functions of various special features of the ATmega16A as listed on page62.2.2.7RESETReset Input.A low level on this pin for longer than the minimum pulse length will generate areset,even if the clock is not running.The minimum pulse length is given in T able27-2on page296.Shorter pulses are not guaranteed to generate a reset.2.2.8XTAL1Input to the inverting Oscillator amplifier and input to the internal clock operating circuit.2.2.9XTAL2Output from the inverting Oscillator amplifier.2.2.10AVCCAVCC is the supply voltage pin for Port A and the A/D Converter.It should be externally con-nected to V CC,even if the ADC is not used.If the ADC is used,it should be connected to V CCthrough a low-pass filter.2.2.11AREFAREF is the analog reference pin for the A/D Converter.3.ResourcesA comprehensive set of development tools,application notes and datasheets are available fordownload on4.Data RetentionReliability Qualification results show that the projected data retention failure rate is much lessthan1PPM over20years at85°C or100years at25°C.5.Register SummaryNotes: 1.When the OCDEN Fuse is unprogrammed,the OSCCAL Register is always accessed on this address.Refer to the debug-ger specific documentation for details on how to use the OCDR Register.2.Refer to the USART description for details on how to access UBRRH and UCSRC.3.For compatibility with future devices,reserved bits should be written to zero if accessed.Reserved I/O memory addressesshould never be written.4.Some of the Status Flags are cleared by writing a logical one to them.Note that the CBI and SBI instructions will operate onall bits in the I/O Register,writing a one back into any flag read as set,thus clearing the flag.The CBI and SBI instructionswork with registers$00to$1F only.6.Instruction Set Summary采购电子元器件选择万联芯城,万联芯城只售电子元器件原装现货,物料型号充足,类别多样,万联芯城拥有大型现代化仓储系统,为客户提供一站式电子元器件物料配套,只需提交BOM表,立即可以报价。

ATmega16单片机中文技术资料

ATmega16单片机中文技术资料一、概述ATmega16是一款高性能、低功耗的8位微控制器,由Atmel公司推出。

它基于AVR增强型RISC结构,拥有丰富的外设资源和灵活的编程特性,广泛应用于工业控制、消费电子、通信设备等领域。

二、主要特性1. 内核:AVR增强型RISC结构,最高工作频率为16MHz。

2. 存储:16KB的程序存储器(Flash)、512B的EEPROM和1KB 的SRAM。

3. 外设接口:32个通用I/O口、8个通道的10位ADC、2个8位定时器/计数器、1个16位定时器/计数器、1个串行通信接口(USART)、1个串行外设接口(SPI)和1个两线接口(TWI)。

4. 工作电压:2.7V至5.5V,支持低功耗模式。

5. 封装:采用TQFP和PDIP封装,便于嵌入式系统设计。

三、引脚功能1. VCC:电源正极,接2.7V至5.5V电压。

2. GND:电源负极,接地。

3. PA0PA7:端口A,具有通用I/O、模拟输入和外围设备功能。

4. PB0PB7:端口B,具有通用I/O、JTAG接口和外围设备功能。

5. PC0PC7:端口C,具有通用I/O、模拟输入和外围设备功能。

6. PD0PD7:端口D,具有通用I/O和外围设备功能。

7. XTAL1/XTAL2:晶振输入/输出,用于外部晶振或陶瓷谐振器。

8. AVCC:模拟电源,为ADC和模拟电路提供电源。

10.RESET:复位输入,低电平有效。

四、编程与开发1. 编程语言:支持C语言和汇编语言编程。

2. 开发工具:可使用Atmel Studio、AVR Studio等集成开发环境进行程序编写、编译和调试。

3. 烧录方式:通过ISP、JTAG、HVPP等接口进行程序烧录。

本文档旨在为您提供ATmega16单片机的中文技术资料,帮助您更好地了解这款微控制器,为您的项目开发提供支持。

后续内容将详细介绍ATmega16的外设功能、编程方法及应用实例。

AVR教程系列一(12):ATmega16 简介(六)

A VR教程系列一(12):ATmega16 简介(六) ATmega16 操纵与状态寄存器MCUCSRAVR 操纵与状态寄存器提供了有关引起AVR复位的复位源的信息。

Bit 4 – JTRF: JTAG 复位标志通过JTAG 指令AVR_RESET 能够使JTAG 复位寄存器置位,并引发MCU 复位,并使JTRF 置位。

上电复位将使其清零,也能够通过写”0” 来清除。

Bit 3 – WDRF: 看门狗复位标志看门狗复位发生时置位。

上电复位将使其清零,也能够通过写”0” 来清除。

Bit 2 – BORF: 掉电检测复位标志掉电检测复位发生时置位。

上电复位将使其清零,也能够通过写”0” 来清除。

Bit 1 – EXTRF: 外部复位标志外部复位发生时置位。

上电复位将使其清零,也能够通过写”0” 来清除。

Bit 0 – PORF: 上电复位标志上电复位发生时置位。

只能通过写”0” 来清除。

为了使用这些复位标志来识别复位条件,用户应该尽早读取此寄存器的数据,然后将其复位。

假如在其他复位发生之前将此寄存器复位,则后续复位源能够通过检查复位标志来熟悉。

ATmega16 基准电压使能信号与启动时间ATmega16 具有片内能隙基准源,用于掉电检测,或者者是作为模拟比较器或者ADC的输入。

ADC 的2.56V 基准电压由此片内能隙基准源产生。

电压基准的启动时间可能影响其工作方式。

启动时间列于Table 16。

为了降低功耗,能够操纵基准源仅在如下情况打开:1. BOD 使能 ( 熔丝位BODEN 被编程)2. 能隙基准源连接到模拟比较器(ACSR 寄存器的ACBG 置位)3. ADC 使能因此,当BOD 被禁止时,置位ACBG 或者使能ADC 后要启动基准源。

为了降低掉电模式的功耗,用户能够禁止上述三种条件,并在进入掉电模式之前关闭基准源。

ATmega16 看门狗定时器看门狗定时器由独立的1 Mhz 片内振荡器驱动。

单片机atmega16

ATmega16单片机Atmega16单片机介绍ATmega16是基于增强的AVR RISC结构的低功耗8 位CMOS微控制器。

由于其先进的指令集以及单时钟周期指令执行时间,ATmega16 的数据吞吐率高达1 MIPS/MHz,从而可以减缓系统在功耗和处理速度之间的矛盾。

ATmega16 AVR 内核具有丰富的指令集和32 个通用工作寄存器。

所有的寄存器都直接与运算逻单元(ALU) 相连接,使得一条指令可以在一个时钟周期内同时访问两个独立的寄存器。

这种结构大大提高了代码效率,并且具有比普通的CISC 微控制器最高至10 倍的数据吞吐率。

ATmega16 有如下特点:16K字节的系统内可编程Flash(具有同时读写的能力,即RWW),512 字节EEPROM,1K 字节SRAM,32 个通用I/O 口线,32 个通用工作寄存器,用于边界扫描的JTAG 接口,支持片内调试与编程,三个具有比较模式的灵活的定时器/ 计数器(T/C),片内/外中断,可编程串行USART,有起始条件检测器的通用串行接口,8路10位具有可选差分输入级可编程增益(TQFP 封装) 的ADC ,具有片内振荡器的可编程看门狗定时器,一个SPI 串行端口,以及六个可以通过软件进行选择的省电模式。

工作于空闲模式时CPU 停止工作,而USART、两线接口、A/D 转换器、SRAM、T/C、SPI 端口以及中断系统继续工作;掉电模式时晶体振荡器停止振荡,所有功能除了中断和硬件复位之外都停止工作;在省电模式下,异步定时器继续运行,允许用户保持一个时间基准,而其余功能模块处于休眠状态;ADC 噪声抑制模式时终止CPU 和除了异步定时器与ADC 以外所有I/O 模块的工作,以降低ADC 转换时的开关噪声;Standby 模式下只有晶体或谐振振荡器运行,其余功能模块处于休眠状态,使得器件只消耗极少的电流,同时具有快速启动能力;扩展Standby 模式下则允许振荡器和异步定时器继续工作。

atmega16中文资料.0003

154

ATmega16(L)

2466G–AVR–10/03

ATmega16(L)

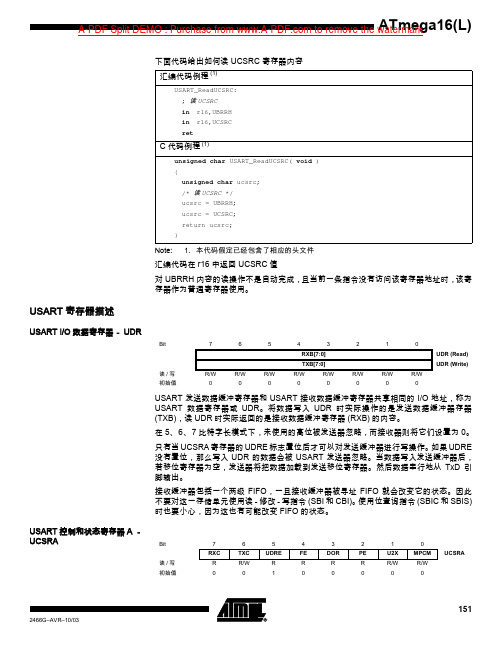

USART 波特率寄存器- UBRRL 和 UBRRH

UCSRC寄存器与UBRRH寄存器共用相同的I/O地址。 对该寄存器的访问, 请参见P151“访 问 UBRRH/ UCSRC 寄存器 ” 。 • Bit 15 – URSEL: 寄存器选择 通过该位选择访问 UCSRC 寄存器或 UBRRH 寄存器。当读 UBRRH 时,该位为 0 ;当 写 UBRRH 时, URSEL 为 0。 • Bit 14:12 – 保留位 这些位是为以后的使用而保留的。为了与以后的器件兼容,写 UBRRH 时将这些位清零。 • Bit 11:0 – UBRR11:0: USART 波特率寄存器 这个 12 位的寄存器包含了 USART 的波特率信息。其中 UBRRH 包含了 USART 波特率 高 4 位, UBRRL 包含了低 8 位。波特率的改变将造成正在进行的数据传输受到破坏。写 UBRRL 将立即更新波特率分频器。

ATmega16(L) A-PDF Split DEMO : Purchase from to remove the watermark

下面代码给出如何读 UCSRC 寄存器内容 汇编代码例程 (1)

USART_ReadUCSRC: ; 读 UCSRC in in ret r16,UBRRH r16,UCSRC

Bit 读/写 初始值

7 RXCIE R/W 0

6 TXCIE R/W 0

5 UDRIE R/W 0

AVR教程系列一(10):ATmega16 简介(9)

ATmega16 简介〔四〕ATmega16 时钟系统及其分布时钟系统及其分布Figure 11为AVR的主要时钟系统及其分布。

这些时钟并不需要同时工作。

为了降低功耗,可以通过使用不同的睡眠模式来禁止无需工作的模块的时钟。

时钟系统详见Figure 11。

CPU 时钟- clkCPUCPU时钟与操作AVR内核的子系统相连,如通用存放器文件、状态存放器及保留仓库指针的数据存储器。

终止CPU 时钟将使内核遏制工作和计算。

I/O 时钟- clkI/OI/O时钟用于主要的I/O 模块,如按时器/ 计数器、SPI 和USART。

I/O 时钟还用于外部中断模块。

要注意的是有些外部中断由异步逻辑检测,因此即使I/O 时钟遏制了这些中断仍然可以得到监控。

此外, USI 模块的起始条件检测在没有clkI/O 的情况下也是异步实现的,使得这个功能在任何睡眠模式下都可以正常工作。

Flash 时钟- clkFLASHFlash 时钟控制Flash 接口的操作。

此时钟通常与CPU 时钟同时挂起或激活。

异步按时器时钟- clkASY异步按时器时钟允许异步按时器/ 计数器与LCD 控制器直接由外部32 kHz 时钟晶体驱动。

使得此按时器/ 计数器即使在睡眠模式下仍然可以为系统提供一个实不时钟。

ADC 时钟- clkADCADC具有专门的时钟。

这样可以在ADC工作的时候遏制CPU和I/O时钟以降低数字电路产生的噪声,从而提高ADC 转换精度。

ATmega16 时钟源ATmega16芯片有如下几种通过Flash熔丝位进行选择的时钟源。

时钟输入到AVR时钟发生器,再分配到相应的模块。

不同的时钟选项将在后续局部进行介绍。

当CPU 自掉电模式或省电模式唤醒之后,被选择的时钟源用来为启动过程按时,包管振荡器在开始执行指令之前进入不变状态。

当CPU从复位开始工作时,还有额外的延迟时间以包管在MCU 开始正常工作之前电源达到不变电平。

这个启动时间的按时由看门狗振荡器完成。

AVR教程系列一(12):ATmega16 简介(六)

ATmega16 简介(六)ATmega16 控制和状态寄存器MCUCSRAVR 控制和状态寄存器提供了有关引起AVR复位的复位源的信息。

? Bit 4 – JTRF: JTAG 复位标志通过JTAG 指令AVR_RESET 可以使JTAG 复位寄存器置位,并引发MCU 复位,并使JTRF 置位。

上电复位将使其清零,也可以通过写”0” 来清除。

? Bit 3 – WDRF: 看门狗复位标志看门狗复位发生时置位。

上电复位将使其清零,也可以通过写”0” 来清除。

? Bit 2 – BORF: 掉电检测复位标志掉电检测复位发生时置位。

上电复位将使其清零,也可以通过写”0” 来清除。

? Bit 1 – EXTRF: 外部复位标志外部复位发生时置位。

上电复位将使其清零,也可以通过写”0” 来清除。

? Bit 0 – PORF: 上电复位标志上电复位发生时置位。

只能通过写”0” 来清除。

为了使用这些复位标志来识别复位条件,用户应该尽早读取此寄存器的数据,然后将其复位。

如果在其他复位发生之前将此寄存器复位,则后续复位源可以通过检查复位标志来了解。

ATmega16 基准电压使能信号和启动时间ATmega16 具有片内能隙基准源,用于掉电检测,或者是作为模拟比较器或ADC的输入。

ADC 的2.56V 基准电压由此片内能隙基准源产生。

电压基准的启动时间可能影响其工作方式。

启动时间列于Table 16。

为了降低功耗,可以控制基准源仅在如下情况打开:1. BOD 使能 ( 熔丝位BODEN 被编程)2. 能隙基准源连接到模拟比较器(ACSR 寄存器的ACBG 置位)3. ADC 使能因此,当BOD 被禁止时,置位ACBG 或使能ADC 后要启动基准源。

为了降低掉电模式的功耗,用户可以禁止上述三种条件,并在进入掉电模式之前关闭基准源。

ATmega16 看门狗定时器看门狗定时器由独立的1 Mhz 片内振荡器驱动。

这是VCC = 5V 时的典型值。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Features•High-performance, Low-power AVR® 8-bit Microcontroller •Advanced RISC Architecture–131 Powerful Instructions – Most Single-clock Cycle Execution –32 x 8 General Purpose Working Registers–Fully Static Operation–Up to 16 MIPS Throughput at 16 MHz–On-chip 2-cycle Multiplier•High Endurance Non-volatile Memory segments–16K Bytes of In-System Self-programmable Flash program memory–512 Bytes EEPROM–1K Byte Internal SRAM–Write/Erase Cycles: 10,000 Flash/100,000 EEPROM–Data retention: 20 years at 85°C/100 years at 25°C(1)–Optional Boot Code Section with Independent Lock Bits•In-System Programming by On-chip Boot Program•True Read-While-Write Operation–Programming Lock for Software Security•JTAG (IEEE std. 1149.1 Compliant) Interface–Boundary-scan Capabilities According to the JTAG Standard–Extensive On-chip Debug Support–Programming of Flash, EEPROM, Fuses, and Lock Bits through the JTAG Interface •Peripheral Features–Two 8-bit Timer/Counters with Separate Prescalers and Compare Modes–One 16-bit Timer/Counter with Separate Prescaler, Compare Mode, and Capture Mode–Real Time Counter with Separate Oscillator–Four PWM Channels–8-channel, 10-bit ADC•8 Single-ended Channels•7 Differential Channels in TQFP Package Only•2 Differential Channels with Programmable Gain at 1x, 10x, or 200x –Byte-oriented Two-wire Serial Interface–Programmable Serial USART–Master/Slave SPI Serial Interface–Programmable Watchdog Timer with Separate On-chip Oscillator–On-chip Analog Comparator•Special Microcontroller Features–Power-on Reset and Programmable Brown-out Detection–Internal Calibrated RC Oscillator–External and Internal Interrupt Sources–Six Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, Standby and Extended Standby•I/O and Packages–32 Programmable I/O Lines–40-pin PDIP, 44-lead TQFP, and 44-pad QFN/MLF•Operating Voltages–2.7 - 5.5V for ATmega16A•Speed Grades–0 - 16 MHz for ATmega16A•Power Consumption @ 1 MHz, 3V, and 25°C for ATmega16A–Active: 0.6 mA–Idle Mode: 0.2 mA–Power-down Mode: < 1µA 8-bit Microcontrollerwith 16K BytesIn-System ProgrammableATmega16A Summary1.Pin ConfigurationsFigure 1-1.Pinout ATmega16A2.OverviewThe ATmega16A is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISCarchitecture. By executing powerful instructions in a single clock cycle, the ATmega16Aachieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimizepower consumption versus processing speed.2.1Block DiagramFigure 2-1.Block DiagramThe AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than con-ventional CISC microcontrollers.The ATmega16A provides the following features: 16K bytes of In-System Programmable Flash Program memory with Read-While-Write capabilities, 512 bytes EEPROM, 1K byte SRAM, 32 general purpose I/O lines, 32 general purpose working registers, a JTAG interface for Boundary-scan, On-chip Debugging support and programming, three flexible Timer/Counters with com-pare modes, Internal and External Interrupts, a serial programmable USART, a byte oriented Two-wire Serial Interface, an 8-channel, 10-bit ADC with optional differential input stage with programmable gain (TQFP package only), a programmable Watchdog Timer with Internal Oscil-lator, an SPI serial port, and six software selectable power saving modes. The Idle mode stops the CPU while allowing the USART, Two-wire interface, A/D Converter, SRAM, Timer/Counters, SPI port, and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next External Inter-rupt or Hardware Reset. In Power-save mode, the Asynchronous Timer continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping. The ADC Noise Reduction mode stops the CPU and all I/O modules except Asynchronous Timer and ADC, to minimize switching noise during ADC conversions. In Standby mode, the crystal/reso-nator Oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low-power consumption. In Extended Standby mode, both the main Oscillator and the Asynchronous Timer continue to run.The device is manufactured using Atmel’s high density nonvolatile memory technology. The On-chip ISP Flash allows the program memory to be reprogrammed in-system through an SPI serial interface, by a conventional nonvolatile memory programmer, or by an On-chip Boot program running on the AVR core. The boot program can use any interface to download the application program in the Application Flash memory. Software in the Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega16A is a powerful microcontroller that provides a highly-flexible and cost-effective solution to many embedded control applications.The ATmega16A AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, in-circuit emulators, and evaluation kits.2.2Pin Descriptions2.2.1VCCDigital supply voltage.2.2.2GNDGround.2.2.3Port A (PA7:PA0)Port A serves as the analog inputs to the A/D Converter.Port A also serves as an 8-bit bi-directional I/O port, if the A/D Converter is not used. Port pinscan provide internal pull-up resistors (selected for each bit). The Port A output buffers have sym-metrical drive characteristics with both high sink and source capability. When pins PA0 to PA7are used as inputs and are externally pulled low, they will source current if the internal pull-upresistors are activated. The Port A pins are tri-stated when a reset condition becomes active,even if the clock is not running.2.2.4Port B (PB7:PB0)Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). ThePort B output buffers have symmetrical drive characteristics with both high sink and sourcecapability. As inputs, Port B pins that are externally pulled low will source current if the pull-upresistors are activated. The Port B pins are tri-stated when a reset condition becomes active,even if the clock is not running.Port B also serves the functions of various special features of the ATmega16A as listed on page57.2.2.5Port C (PC7:PC0)Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). ThePort C output buffers have symmetrical drive characteristics with both high sink and sourcecapability. As inputs, Port C pins that are externally pulled low will source current if the pull-upresistors are activated. The Port C pins are tri-stated when a reset condition becomes active,even if the clock is not running. If the JTAG interface is enabled, the pull-up resistors on pinsPC5(TDI), PC3(TMS) and PC2(TCK) will be activated even if a reset occurs.Port C also serves the functions of the JTAG interface and other special features of theATmega16A as listed on page 60.2.2.6Port D (PD7:PD0)Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). ThePort D output buffers have symmetrical drive characteristics with both high sink and sourcecapability. As inputs, Port D pins that are externally pulled low will source current if the pull-upresistors are activated. The Port D pins are tri-stated when a reset condition becomes active,even if the clock is not running.Port D also serves the functions of various special features of the ATmega16A as listed on page62.2.2.7RESETReset Input. A low level on this pin for longer than the minimum pulse length will generate areset, even if the clock is not running. The minimum pulse length is given in Table 27-2 on page296. Shorter pulses are not guaranteed to generate a reset.2.2.8XTAL1Input to the inverting Oscillator amplifier and input to the internal clock operating circuit.2.2.9XTAL2Output from the inverting Oscillator amplifier.2.2.10AVCCAVCC is the supply voltage pin for Port A and the A/D Converter. It should be externally con-nected to V CC, even if the ADC is not used. If the ADC is used, it should be connected to V CCthrough a low-pass filter.2.2.11AREFAREF is the analog reference pin for the A/D Converter.3.ResourcesA comprehensive set of development tools, application notes and datasheets are available fordownload on /avr.4.Data RetentionReliability Qualification results show that the projected data retention failure rate is much lessthan 1 PPM over 20 years at 85°C or 100 years at 25°C.5.Register SummaryAddress Name Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Page $3F ($5F)SREG I T H S V N Z C9 $3E ($5E)SPH–––––SP10SP9SP812 $3D ($5D)SPL SP7SP6SP5SP4SP3SP2SP1SP012 $3C ($5C)OCR0Timer/Counter0 Output Compare Register85 $3B ($5B)GICR INT1INT0INT2–––IVSEL IVCE47, 69 $3A ($5A)GIFR INTF1INTF0INTF2–––––69 $39 ($59)TIMSK OCIE2TOIE2TICIE1OCIE1A OCIE1B TOIE1OCIE0TOIE085, 115, 134 $38 ($58)TIFR OCF2TOV2ICF1OCF1A OCF1B TOV1OCF0TOV085, 115, 134 $37 ($57)SPMCR SPMIE RWWSB–RWWSRE BLBSET PGWRT PGERS SPMEN255 $36 ($56)TWCR TWINT TWEA TWSTA TWSTO TWWC TWEN–TWIE200 $35 ($55)MCUCR SM2SE SM1SM0ISC11ISC10ISC01ISC0036, 67 $34 ($54)MCUCSR JTD ISC2–JTRF WDRF BORF EXTRF PORF41, 68, 249 $33 ($53)TCCR0FOC0WGM00COM01COM00WGM01CS02CS01CS0082 $32 ($52)TCNT0Timer/Counter0 (8 Bits)84$31(1) ($51)(1)OSCCAL Oscillator Calibration Register31 OCDR On-Chip Debug Register231$30 ($50)SFIOR ADTS2ADTS1ADTS0–ACME PUD PSR2PSR1065,87,134,205,225 $2F ($4F)TCCR1A COM1A1COM1A0COM1B1COM1B0FOC1A FOC1B WGM11WGM10109$2E ($4E)TCCR1B ICNC1ICES1–WGM13WGM12CS12CS11CS10112$2D ($4D)TCNT1H Timer/Counter1 – Counter Register High Byte113$2C ($4C)TCNT1L Timer/Counter1 – Counter Register Low Byte113$2B ($4B)OCR1AH Timer/Counter1 – Output Compare Register A High Byte114$2A ($4A)OCR1AL Timer/Counter1 – Output Compare Register A Low Byte114$29 ($49)OCR1BH Timer/Counter1 – Output Compare Register B High Byte114$28 ($48)OCR1BL Timer/Counter1 – Output Compare Register B Low Byte114$27 ($47)ICR1H Timer/Counter1 – Input Capture Register High Byte114$26 ($46)ICR1L Timer/Counter1 – Input Capture Register Low Byte114$25 ($45)TCCR2FOC2WGM20COM21COM20WGM21CS22CS21CS20130$24 ($44)TCNT2Timer/Counter2 (8 Bits)133$23 ($43)OCR2Timer/Counter2 Output Compare Register133$22 ($42)ASSR––––AS2TCN2UB OCR2UB TCR2UB133$21 ($41)WDTCR–––WDTOE WDE WDP2WDP1WDP042$20(2) ($40)(2)UBRRH URSEL–––UBRR[11:8]170 UCSRC URSEL UMSEL UPM1UPM0USBS UCSZ1UCSZ0UCPOL169$1F ($3F)EEARH–––––––EEAR819 $1E ($3E)EEARL EEPROM Address Register Low Byte19 $1D ($3D)EEDR EEPROM Data Register20 $1C ($3C)EECR––––EERIE EEMWE EEWE EERE20 $1B ($3B)PORTA PORTA7PORTA6PORTA5PORTA4PORTA3PORTA2PORTA1PORTA065 $1A ($3A)DDRA DDA7DDA6DDA5DDA4DDA3DDA2DDA1DDA065 $19 ($39)PINA PINA7PINA6PINA5PINA4PINA3PINA2PINA1PINA065 $18 ($38)PORTB PORTB7PORTB6PORTB5PORTB4PORTB3PORTB2PORTB1PORTB065 $17 ($37)DDRB DDB7DDB6DDB5DDB4DDB3DDB2DDB1DDB065 $16 ($36)PINB PINB7PINB6PINB5PINB4PINB3PINB2PINB1PINB066 $15 ($35)PORTC PORTC7PORTC6PORTC5PORTC4PORTC3PORTC2PORTC1PORTC066 $14 ($34)DDRC DDC7DDC6DDC5DDC4DDC3DDC2DDC1DDC066 $13 ($33)PINC PINC7PINC6PINC5PINC4PINC3PINC2PINC1PINC066 $12 ($32)PORTD PORTD7PORTD6PORTD5PORTD4PORTD3PORTD2PORTD1PORTD066 $11 ($31)DDRD DDD7DDD6DDD5DDD4DDD3DDD2DDD1DDD066 $10 ($30)PIND PIND7PIND6PIND5PIND4PIND3PIND2PIND1PIND066 $0F ($2F)SPDR SPI Data Register145 $0E ($2E)SPSR SPIF WCOL–––––SPI2X144 $0D ($2D)SPCR SPIE SPE DORD MSTR CPOL CPHA SPR1SPR0143 $0C ($2C)UDR USART I/O Data Register166 $0B ($2B)UCSRA RXC TXC UDRE FE DOR PE U2X MPCM167 $0A ($2A)UCSRB RXCIE TXCIE UDRIE RXEN TXEN UCSZ2RXB8TXB8168 $09 ($29)UBRRL USART Baud Rate Register Low Byte170 $08 ($28)ACSR ACD ACBG ACO ACI ACIE ACIC ACIS1ACIS0205 $07 ($27)ADMUX REFS1REFS0ADLAR MUX4MUX3MUX2MUX1MUX0221 $06 ($26)ADCSRA ADEN ADSC ADATE ADIF ADIE ADPS2ADPS1ADPS0223 $05 ($25)ADCH ADC Data Register High Byte224 $04 ($24)ADCL ADC Data Register Low Byte224 $03 ($23)TWDR Two-wire Serial Interface Data Register202 $02 ($22)TWAR TWA6TWA5TWA4TWA3TWA2TWA1TWA0TWGCE203Address Name Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Page $01 ($21)TWSR TWS7TWS6TWS5TWS4TWS3–TWPS1TWPS0202 $00 ($20)TWBR Two-wire Serial Interface Bit Rate Register200 Notes: 1.When the OCDEN Fuse is unprogrammed, the OSCCAL Register is always accessed on this address. Refer to the debug-ger specific documentation for details on how to use the OCDR Register.2.Refer to the USART description for details on how to access UBRRH and UCSRC.3.For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addressesshould never be written.4.Some of the Status Flags are cleared by writing a logical one to them. Note that the CBI and SBI instructions will operate onall bits in the I/O Register, writing a one back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers $00 to $1F only.6.Instruction Set SummaryMnemonics Operands Description Operation Flags#ClocksARITHMETIC AND LOGIC INSTRUCTIONSADD Rd, Rr Add two Registers Rd ← Rd + Rr Z,C,N,V,H1 ADC Rd, Rr Add with Carry two Registers Rd ← Rd + Rr + C Z,C,N,V,H1 ADIW Rdl,K Add Immediate to Word Rdh:Rdl ← Rdh:Rdl + K Z,C,N,V,S2 SUB Rd, Rr Subtract two Registers Rd ← Rd - Rr Z,C,N,V,H1 SUBI Rd, K Subtract Constant from Register Rd ← Rd - K Z,C,N,V,H1 SBC Rd, Rr Subtract with Carry two Registers Rd ← Rd - Rr - C Z,C,N,V,H1 SBCI Rd, K Subtract with Carry Constant from Reg.Rd ← Rd - K - C Z,C,N,V,H1 SBIW Rdl,K Subtract Immediate from Word Rdh:Rdl ← Rdh:Rdl - K Z,C,N,V,S2 AND Rd, Rr Logical AND Registers Rd ← Rd • Rr Z,N,V1 ANDI Rd, K Logical AND Register and Constant Rd ← Rd • K Z,N,V1OR Rd, Rr Logical OR Registers Rd ← Rd v Rr Z,N,V1ORI Rd, K Logical OR Register and Constant Rd ← Rd v K Z,N,V1 EOR Rd, Rr Exclusive OR Registers Rd ← Rd ⊕ Rr Z,N,V1 COM Rd One’s Complement Rd ← $FF − Rd Z,C,N,V1 NEG Rd Two’s Complement Rd ← $00 − Rd Z,C,N,V,H1 SBR Rd,K Set Bit(s) in Register Rd ← Rd v K Z,N,V1 CBR Rd,K Clear Bit(s) in Register Rd ← Rd • ($FF - K)Z,N,V1INC Rd Increment Rd ← Rd + 1Z,N,V1 DEC Rd Decrement Rd ← Rd − 1 Z,N,V1 TST Rd Test for Zero or Minus Rd ← Rd • Rd Z,N,V1 CLR Rd Clear Register Rd ← Rd ⊕ Rd Z,N,V1 SER Rd Set Register Rd ← $FF None1 MUL Rd, Rr Multiply Unsigned R1:R0 ← Rd x Rr Z,C2 MULS Rd, Rr Multiply Signed R1:R0 ← Rd x Rr Z,C2 MULSU Rd, Rr Multiply Signed with Unsigned R1:R0 ← Rd x Rr Z,C2 FMUL Rd, Rr Fractional Multiply Unsigned R1:R0 ← (Rd x Rr) << 1Z,C2FMULS Rd, Rr Fractional Multiply Signed R1:R0 ← (Rd x Rr) << 1Z,C2 FMULSU Rd, Rr Fractional Multiply Signed with Unsigned R1:R0 ← (Rd x Rr) << 1Z,C2 BRANCH INSTRUCTIONSRJMP k Relative Jump PC ← PC + k + 1None2 IJMP Indirect Jump to (Z)PC ← Z None2 JMP k Direct Jump PC ←k None3 RCALL k Relative Subroutine Call PC ← PC + k + 1None3 ICALL Indirect Call to (Z)PC ←Z None3 CALL k Direct Subroutine Call PC ←k None4 RET Subroutine Return PC ← STACK None4 RETI Interrupt Return PC ← STACK I4 CPSE Rd,Rr Compare, Skip if Equal if (Rd = Rr) PC ← PC + 2 or 3None 1 / 2 / 3 CP Rd,Rr Compare Rd − Rr Z, N,V,C,H 1 CPC Rd,Rr Compare with Carry Rd − Rr − C Z, N,V,C,H1CPI Rd,K Compare Register with Immediate Rd − K Z, N,V,C,H1 SBRC Rr, b Skip if Bit in Register Cleared if (Rr(b)=0) PC ← PC + 2 or 3 None 1 / 2 / 3 SBRS Rr, b Skip if Bit in Register is Set if (Rr(b)=1) PC ← PC + 2 or 3None 1 / 2 / 3 SBIC P, b Skip if Bit in I/O Register Cleared if (P(b)=0) PC ← PC + 2 or 3 None 1 / 2 / 3 SBIS P, b Skip if Bit in I/O Register is Set if (P(b)=1) PC ← PC + 2 or 3None 1 / 2 / 3 BRBS s, k Branch if Status Flag Set if (SREG(s) = 1) then PC←PC+k + 1None 1 / 2 BRBC s, k Branch if Status Flag Cleared if (SREG(s) = 0) then PC←PC+k + 1None 1 / 2 BREQ k Branch if Equal if (Z = 1) then PC ← PC + k + 1None 1 / 2 BRNE k Branch if Not Equal if (Z = 0) then PC ← PC + k + 1None 1 / 2 BRCS k Branch if Carry Set if (C = 1) then PC ← PC + k + 1None 1 / 2 BRCC k Branch if Carry Cleared if (C = 0) then PC ← PC + k + 1None 1 / 2 BRSH k Branch if Same or Higher if (C = 0) then PC ← PC + k + 1None 1 / 2 BRLO k Branch if Lower if (C = 1) then PC ← PC + k + 1None 1 / 2 BRMI k Branch if Minus if (N = 1) then PC ← PC + k + 1None 1 / 2 BRPL k Branch if Plus if (N = 0) then PC ← PC + k + 1None 1 / 2 BRGE k Branch if Greater or Equal, Signed if (N ⊕ V= 0) then PC ← PC + k + 1None 1 / 2 BRLT k Branch if Less Than Zero, Signed if (N ⊕ V= 1) then PC ← PC + k + 1None 1 / 2 BRHS k Branch if Half Carry Flag Set if (H = 1) then PC ← PC + k + 1None 1 / 2 BRHC k Branch if Half Carry Flag Cleared if (H = 0) then PC ← PC + k + 1None 1 / 2 BRTS k Branch if T Flag Set if (T = 1) then PC ← PC + k + 1None 1 / 2BRTC k Branch if T Flag Cleared if (T = 0) then PC ← PC + k + 1None 1 / 2 BRVS k Branch if Overflow Flag is Set if (V = 1) then PC ← PC + k + 1None 1 / 2 BRVC k Branch if Overflow Flag is Cleared if (V = 0) then PC ← PC + k + 1None 1 / 2 BRIE k Branch if Interrupt Enabled if ( I = 1) then PC ← PC + k + 1None 1 / 2 BRID k Branch if Interrupt Disabled if ( I = 0) then PC ← PC + k + 1None 1 / 2 DATA TRANSFER INSTRUCTIONSMOV Rd, Rr Move Between Registers Rd ← Rr None1 MOVW Rd, Rr Copy Register Word Rd+1:Rd ← Rr+1:Rr None1 LDI Rd, K Load Immediate Rd ←K None1 LD Rd, X Load Indirect Rd ← (X)None2 LD Rd, X+Load Indirect and Post-Inc.Rd ← (X), X ← X + 1None2 LD Rd, - X Load Indirect and Pre-Dec.X ← X - 1, Rd ← (X)None2 LD Rd, Y Load Indirect Rd ← (Y)None2 LD Rd, Y+Load Indirect and Post-Inc.Rd ← (Y), Y ← Y + 1None2 LD Rd, - Y Load Indirect and Pre-Dec.Y ← Y - 1, Rd ← (Y)None2 LDD Rd,Y+q Load Indirect with Displacement Rd ← (Y + q)None2 LD Rd, Z Load Indirect Rd ← (Z)None2 LD Rd, Z+Load Indirect and Post-Inc.Rd ← (Z), Z ← Z+1None2 LD Rd, -Z Load Indirect and Pre-Dec.Z ← Z - 1, Rd ← (Z)None2 LDD Rd, Z+q Load Indirect with Displacement Rd ← (Z + q)None2 LDS Rd, k Load Direct from SRAM Rd ← (k)None2 ST X, Rr Store Indirect(X) ← Rr None2 ST X+, Rr Store Indirect and Post-Inc.(X) ← Rr, X ← X + 1None2 ST- X, Rr Store Indirect and Pre-Dec.X ← X - 1, (X) ← Rr None2 ST Y, Rr Store Indirect(Y) ← Rr None2 ST Y+, Rr Store Indirect and Post-Inc.(Y) ← Rr, Y ← Y + 1None2 ST- Y, Rr Store Indirect and Pre-Dec.Y ← Y - 1, (Y) ← Rr None2 STD Y+q,Rr Store Indirect with Displacement(Y + q) ← Rr None2 ST Z, Rr Store Indirect(Z) ← Rr None2 ST Z+, Rr Store Indirect and Post-Inc.(Z) ← Rr, Z ← Z + 1None2 ST-Z, Rr Store Indirect and Pre-Dec.Z ← Z - 1, (Z) ← Rr None2 STD Z+q,Rr Store Indirect with Displacement(Z + q) ← Rr None2 STS k, Rr Store Direct to SRAM(k) ← Rr None2 LPM Load Program Memory R0 ← (Z)None3 LPM Rd, Z Load Program Memory Rd ← (Z)None3 LPM Rd, Z+Load Program Memory and Post-Inc Rd ← (Z), Z ← Z+1None3 SPM Store Program Memory(Z) ← R1:R0None-IN Rd, P In Port Rd ←P None1 OUT P, Rr Out Port P ← Rr None1 PUSH Rr Push Register on Stack STACK ← Rr None2 POP Rd Pop Register from Stack Rd ← STACK None2 BIT AND BIT-TEST INSTRUCTIONSSBI P,b Set Bit in I/O Register I/O(P,b) ←1None2 CBI P,b Clear Bit in I/O Register I/O(P,b) ←0None2 LSL Rd Logical Shift Left Rd(n+1) ← Rd(n), Rd(0) ← 0Z,C,N,V1 LSR Rd Logical Shift Right Rd(n) ← Rd(n+1), Rd(7) ← 0Z,C,N,V1 ROL Rd Rotate Left Through Carry Rd(0)←C,Rd(n+1)← Rd(n),C←Rd(7)Z,C,N,V1 ROR Rd Rotate Right Through Carry Rd(7)←C,Rd(n)← Rd(n+1),C←Rd(0)Z,C,N,V1 ASR Rd Arithmetic Shift Right Rd(n) ← Rd(n+1), n=0:6Z,C,N,V1 SWAP Rd Swap Nibbles Rd(3:0)←Rd(7:4),Rd(7:4)←Rd(3:0)None1 BSET s Flag Set SREG(s) ← 1SREG(s)1 BCLR s Flag Clear SREG(s) ← 0 SREG(s)1 BST Rr, b Bit Store from Register to T T ← Rr(b)T1 BLD Rd, b Bit load from T to Register Rd(b) ←T None1 SEC Set Carry C ←1C1 CLC Clear Carry C ← 0 C1 SEN Set Negative Flag N ←1N1 CLN Clear Negative Flag N ← 0 N1 SEZ Set Zero Flag Z ←1Z1 CLZ Clear Zero Flag Z ← 0 Z1 SEI Global Interrupt Enable I ←1I1 CLI Global Interrupt Disable I ← 0 I1 SES Set Signed Test Flag S ←1S1 CLS Clear Signed Test Flag S ← 0 S1 SEV Set Twos Complement Overflow.V ←1V1 CLV Clear Twos Complement Overflow V ← 0 V1SET Set T in SREG T ←1T1 CLT Clear T in SREG T ← 0 T1 SEH Set Half Carry Flag in SREG H ←1H1 CLH Clear Half Carry Flag in SREG H ← 0 H1 MCU CONTROL INSTRUCTIONSNOP No Operation None1 SLEEP Sleep(see specific descr. for Sleep function)None1 WDR Watchdog Reset(see specific descr. for WDR/timer)None1 BREAK Break For On-Chip Debug Only None N/A7.Ordering InformationNote: 1.Pb-free packaging complies to the European Directive for Restriction of Hazardous Substances (RoHS directive). AlsoHalide free and fully Green.Speed (MHz)Power Supply Ordering Code Package Operation Range 162.7 - 5.5V A Tmega16A-AU (1)A Tmega16A-PU (1)A Tmega16A-MU (1)44A 40P644M1Industrial (-40o C to 85o C)Package Type44A44-lead, Thin (1.0 mm) Plastic Gull Wing Quad Flat Package (TQFP)40P640-pin, 0.600” Wide, Plastic Dual Inline Package (PDIP)44M144-pad, 7 x 7 x 1.0 mm body, lead pitch 0.50 mm, Quad Flat No-Lead/Micro Lead Frame Package (QFN/MLF)8.Packaging Information 44A9.ErrataThe revision letter in this section refers to the revision of the ATmega16A device.9.1ATmega16A rev. N to rev. Q•First Analog Comparator conversion may be delayed•Interrupts may be lost when writing the timer registers in the asynchronous timer•IDCODE masks data from TDI input•Reading EEPROM by using ST or STS to set EERE bit triggers unexpected interrupt request1.First Analog Comparator conversion may be delayedIf the device is powered by a slow rising V CC, the first Analog Comparator conversion willtake longer than expected on some devices.Problem Fix/WorkaroundWhen the device has been powered or reset, disable then enable theAnalog Comparatorbefore the first conversion.2.Interrupts may be lost when writing the timer registers in the asynchronous timerIf one of the timer registers which is synchronized to the asynchronous timer2 clock is writ-ten in the cycle before a overflow interrupt occurs, the interrupt may be lost.Problem Fix/WorkaroundAlways check that the Timer2 Timer/Counter register, TCNT2, does not have the value 0xFFbefore writing the Timer2 Control Register, TCCR2, or Output Compare Register, OCR23.IDCODE masks data from TDI inputThe JTAG instruction IDCODE is not working correctly. Data to succeeding devices arereplaced by all-ones during Update-DR.Problem Fix / Workaround–If ATmega16A is the only device in the scan chain, the problem is not visible.–Select the Device ID Register of the ATmega16A by issuing the IDCODE instructionor by entering the Test-Logic-Reset state of the TAP controller to read out thecontents of its Device ID Register and possibly data from succeeding devices of thescan chain. Issue the BYPASS instruction to the ATmega16A while reading theDevice ID Registers of preceding devices of the boundary scan chain.–If the Device IDs of all devices in the boundary scan chain must be capturedsimultaneously, the ATmega16A must be the fist device in the chain.4.Reading EEPROM by using ST or STS to set EERE bit triggers unexpected interruptrequest.Reading EEPROM by using the ST or STS command to set the EERE bit in the EECR reg-ister triggers an unexpected EEPROM interrupt request.Problem Fix / WorkaroundAlways use OUT or SBI to set EERE in EECR.10.Datasheet Revision HistoryPlease note that the referring page numbers in this section are referred to this document. Thereferring revision in this section are referring to the document revision.Rev. 8154A – 06/081. Initial revision (Based on the A Tmega16/L datasheet revision 2466R-AVR-05/08)Changes done comparted A Tmega16/L datasheet revision 2466R-AVR-05/08:- Updated description in “Stack Pointer” on page 12.- All Electrical characteristics is moved to “Electrical Characteristics” on page 293.- Register descriptions are moved to sub sections at the end of each chapter.- Added “Speed Grades” on page 295.- New graphs in “Typical Characteristics” on page 305.- New “Ordering Information” on page 13.Headquarters InternationalAtmel Corporation 2325 Orchard Parkway San Jose, CA 95131 USATel: 1(408) 441-0311 Fax: 1(408) 487-2600Atmel AsiaRoom 1219Chinachem Golden Plaza77 Mody Road TsimshatsuiEast KowloonHong KongTel: (852) 2721-9778Fax: (852) 2722-1369Atmel EuropeLe Krebs8, Rue Jean-Pierre TimbaudBP 30978054 Saint-Quentin-en-Yvelines CedexFranceTel: (33) 1-30-60-70-00Fax: (33) 1-30-60-71-11Atmel Japan9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTel: (81) 3-3523-3551Fax: (81) 3-3523-7581Product ContactWeb SiteTechnical Supportavr@Sales Contact/contactsLiterature Requests/literatureDisclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise,to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL’S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL’S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel’s products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.© 2008 Atmel Corporation. All rights reserved. Atmel®, logo and combinations thereof, AVR® and others are registered trademarks or trade-marks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.。