LC866412中文资料

PSL-646U线路保护测控装置(多合一)技术说明书_V3.00_印刷

目录

版本声明 1. 概述 ............................................................................................................................................................ 1

国电南自 DL/T 1075-2007

PSL-646U 线路保护测控装置(多合一)

技术说明书

国电南京自动化股份有限公司 GUODIAN NANJING AUTOMATION CO.,LTD

PSL-646U 线路保护测控装置

技术说明书 (多合一)

V 3.00 国电南京自动化股份有限公司

2015 年 3 月

版本声明

z 本说明书适用于 PSL-646U 线路保护测控装置(多合一)。保护的设计标准引用了国网公司 Q/GDW 766 -2014《10kV~110(66)kV 线路保护及辅助装置标准化设计规范》。

z 本说明书适用于 PSL-646U 线路保护测控装置(多合一)V3.00 及以上版本的保护软件。

1.1. 保护功能配置 ...................................................................................................................................... 1 1.2. 测控功能配置 ..............................................

PSL 641U线路保护测控装置技术说明书V1.22

国 电 南 自Q/GDNZ.JB051-2011PSL 641U线路保护测控装置技术说明书国电南京自动化股份有限公司GUODIAN NANJING AUTOMATION CO.,LTDPSL 641U线路保护测控装置技术说明书编写审核批准V 1.22国电南京自动化股份有限公司2011年3月版本声明本说明书适用于PSL 641U线路保护测控装置V1.22版本。

a)软件PSL 641U V1.22b)硬件PSL 641U线路保护测控装置硬件模件版本修改记录表序号 模件名称 初始版本(2006-02) 第一次修改版本(2008-08)第二次修改版本1 交流模件 PSL 640U-AC.A-A-11(12)2 CPU模件 E03-CPU.A-A E03-CPU.B-A3 面板模件 E03-PNL.A-A4 DIO模件 PSL 640U-DIO.A-A5 TRIP模件 PSL 640U-TRIP.A-A PSL 640U-TRIP.A-B6 电源模件 EDP 03-PWR.A-A7 母板模件 E03-MB.A-A E03-MB.A-B89PSL 641U线路保护测控装置产品说明书版本修改记录表109876543 V1.22 平台版本升级 PSL 641UV1.22 2011.32 V1.10 改进版本 PSL 641UV1.10 2009.041 V1.00 初始版本 PSL 641UV1.00 2007.04序号说明书版本号修改摘要软件版本号修改日期* 技术支持 电话:(025)51183073传真:(025)51183077* 本说明书可能会被修改,请注意核对实际产品与说明书的版本是否相符* 2007年4月 第2版 第1次印刷* 国电南自技术部监制目 录1概述 (1)1.1保护功能配置 (1)1.2测量和控制 (1)2技术参数 (2)2.1保护元件精确工作范围 (2)2.2保护元件定值误差 (2)2.3保护整组动作时间 (2)2.4通信接口 (2)3保护功能及原理 (3)3.1相间过电流保护 (3)3.1.1相间方向元件 (3)3.1.2低电压闭锁元件 (3)3.1.3负序过电压闭锁元件 (3)3.2相间电流反时限元件 (3)3.3零序过电流 (4)3.3.1零序方向元件 (4)3.3.2零序反时限元件 (4)3.3.3零序电流告警元件 (4)3.4合闸加速 (4)3.5三相重合闸 (4)3.5.1充电条件 (5)3.5.2启动方式 (5)3.5.3重合闸方式 (5)3.5.4闭锁条件 (5)3.5.5二次重合闸 (5)3.6手动同期合闸 (5)3.7低频减载 (6)3.8低压减载 (6)3.9过负荷 (6)3.10小电流接地选线 (7)3.11TV断线 (7)3.11.1母线TV断线 (7)3.11.2线路抽取电压断线 (7)4端子说明 (8)4.1总端子图 (8)4.2交流模件端子X1定义 (8)4.3CPU模件端子X2定义 (9)4.4DI0模件端子X3定义 (10)4.5DI0模件端子X4定义 (10)4.6TRIP模件端子X5定义 (11)4.7TRIP模件端子X6定义(请注意装置使用的TRIP板型号) (11)5定值整定说明 (13)5.1保护定值清单及说明 (13)5.2运行参数清单及说明 (15)5.3软压板清单及说明 (16)6装置信息代码表 (17)6.1事件信息表 (17)6.2告警信息表 (17)6.3软压板信息表 (18)6.4遥信量信息表 (18)6.5遥测信息表 (19)6.6遥控量信息表 (20)7装置二次接线示意图 (21)1概述PSL 641U线路保护测控装置以电流电压保护为基本配置,同时集成了各种测量和控制功能,适用于66kV及以下电压等级的配电线路。

atc中文手册

A T24C256中文资料2009-11-15 09:43特性???? 与1MHz I2C 总线兼容???? 到伏工作电压范围???? 低功耗CMOS 技术???? 写保护功能当WP 为高电平时进入写保护状态???? 64 字节页写缓冲器???? 自定时擦写周期???? 100,000 编程/擦写周期???? 可保存数据100 年???? 8 脚DIP SOIC 封装???? 温度范围商业级工业级和汽车级概述CAT24WC256 是一个256K 位串行CMOS E2PROM 内部含有32768 个字节每字节为8 位CATALYST 公司的先进CMOS 技术实质上减少了器件的功耗CAT24WC256 有一个64 字节页写缓冲器该器件通过I2C 总线接口进行操作管脚描述管脚名称功能A0 A1 地址输入SDA 串行数据/地址SCL 串行时钟WP 写保护Vcc + 电源Vss 地NC 未连接极限参数工作温度工业级-55 +125商业级0 +75贮存温度-65 +150各管脚承受电压 Vcc+Vcc 管脚承受电压 +封装功率损耗Ta=25焊接温度(10 秒) 300口输出短路电流100mA功能描述CAT24WC256 支持I2C 总线数据传送协议I2C 总线协议规定任何将数据传送到总线的器件作为发送器任何从总线接收数据的器件为接收器数据传送是由产生串行时钟和所有起始停止信号的主器件控制的CAT24WC256 是作为从器件被操作的主器件和从器件都可以作为发送器或接收器但由主器件控制传送数据发送或接收的模式管脚描述SCL 串行时钟CAT24WC256 串行时钟输入管脚用于产生器件所有数据发送或接收的时钟这是一个输入管脚SDA 串行数据/地址双向串行数据/地址管脚用于器件所有数据的发送或接收SDA 是一个开漏输出管脚可与其它开漏输出或集电极开路输出进行线或wire-ORWP 写保护当WP 脚连接到Vcc 所有内存变成写保护只能读当WP 引脚连接到Vss 或悬空允许器件进行读/写操作A0 A1 器件地址输入这些管脚为硬连线或者不连接对于单总线系统最多可寻址4 个CAT24WC256 器件参阅器件寻址当这些引脚没有连接时其默认值为0I2C 总线协议I2C 总线协议定义如下1 只有在总线空闲时才允许启动数据传送2 在数据传送过程中当时钟线为高电平时数据线必须保持稳定状态不允许有跳变时钟线为高电平时数据线的任何电平变化将被看作总线的起始或停止信号起始信号时钟线保持高电平期间数据线电平从高到低的跳变作为I2C 总线的起始信号停止信号时钟线保持高电平期间数据线电平从低到高的跳变作为I2C 总线的停止信号器件寻址主器件通过发送一个起始信号启动发送过程然后发送它所要寻址的从器件的地址8 位从器件地址的高5 位固定为10100 见图5 接下来的2 位A1 A0 为器件的地址位最多可以连接4 个器件到同一总线上这些位必须与硬连线输入脚A1 A0 相对应从器件地址的最低位作为读写控制位1表示对从器件进行读操作0 表示对从器件进行写操作在主器件发送起始信号和从器件地址字节后CAT24WC256 监视总线并当其地址与发送的从地址相符时响应一个应答信号通过SDA 线CAT24WC256 再根据读写控制位R/W 的状态进行读或写操作应答信号I2C 总线数据传送时每成功地传送一个字节数据后接收器都必须产生一个应答信号应答的器件在第9 个时钟周期时将SDA 线拉低表示其已收到一个8 位数据CAT24WC256 在接收到起始信号和从器件地址之后响应一个应答信号如果器件已选择了写操作则在每接收一个8 位字节之后响应一个应答信号当CAT24WC256 工作于读模式时在发送一个8 位数据后释放SDA 线并监视一个应答信号一旦接收到应答信号CAT24WC256 继续发送数据如主器件没有发送应答信号器件停止传送数据并等待一个停止信号写操作字节写在字节写模式下主器件发送起始信号和从器件地址信息R/W 位置0 给从器件在从器件送回应答信号后主器件发送两个8 位地址字写入CAT24WC256 的地址指针主器件在收到从器件的应答信号后再发送数据到被寻址的存储单元CAT24WC256 再次应答并在主器件产生停止信号后开始内部数据的擦写在内部擦写过程中CAT24WC256 不再应答主器件的任何请求页写在页写模式下单个写周期内CAT24WC256 最多可以写入64 个字节数据页写操作的启动和字节写一样不同在于传送了一字节数据后主器件允许继续发送63 个字节每发送一个字节后CAT24WC256 将响应一个应答位且内部低6 位地址加1 高位地址保持不变如果主器件在发送停止信号之前发送大于64 个字节地址计数器将自动翻转先前写入的数据被覆盖当所有64 字节接收完毕主器件发送停止信号内部编程周期开始此时所有接收到的数据在单个写周期内写入CAT24WC256应答查询可以利用内部写周期时禁止数据输入这一特性一旦主器件发送停止位指示主器件操作结束时CAT24WC256 启动内部写周期应答查询立即启动包括发送一个起始信号和进行写操作的从器件地址如果CAT24WC256 正在进行内部写操作将不会发送应答信号如果CAT24WC256 已经完成了内部写操作将发送一个应答信号主器件可以继续对CAT24WC256 进行下一次读写操作写保护写保护操作特性可使用户避免由于不当操作而造成对存储区域内部数据的改写当WP 管脚接高时整个寄存器区全部被保护起来而变为只可读取CAT24WC256 可以接收从器件地址和字节地址但是装置在接收到第一个数据字节后不发送应答信号从而避免寄存器区域被编程改写读操作CAT24WC256 读操作的初始化方式和写操作时一样仅把R/W 位置为1 有三种不同的读操作方式立即/当前地址读选择/随机读和连续读立即/当前地址读的地址计数器内容为最后操作字节的地址加1 也就是说如果上次读/写的操作地址为N 则立即读的地址从地址N+1 开始如果N=E 此处E=32767 则计数器将翻转到0 且继续输出数据CAT24WC256接收到从器件地址信号后R/W 位置1 它首先发送一个应答信号然后发送一个8 位字节数据主器件不需发送一个应答信号但要产生一个停止信号选择/随机读选择/随机读操作允许主器件对寄存器的任意字节进行读操作主器件首先通过发送起始信号从器件地址和它想读取的字节数据的地址执行一个伪写操作在CAT24WC256 应答之后主器件重新发送起始信号和从器件地址此时R/W 位置1 CAT24WC256 响应并发送应答信号然后输出所要求的一个8 位字节数据主器件不发送应答信号但产生一个停止信号连续读连续读操作可通过立即读或选择性读操作启动在CAT24WC256 发送完一个8 位字节数据后主器件产生一个应答信号来响应告知CAT24WC256 主器件要求更多的数据对应每个主机产生的应答信号CAT24WC256 将发送一个8 位数据字节当主器件不发送应答信号而发送停止位时结束此操作从CAT24WC256 输出的数据按顺序由N 到N+1 输出读操作时地址计数器在CAT24WC256 整个地址内增加这样整个寄存器区域在可在一个读操作内全部读出当读取的字节超过E 此处E=32767计数器将翻转到零并继续输出数据字节。

使用手册课件_31

AC6412 使用手册wwlab2002/4目录一、简介⏹介绍⏹性能⏹原理说明二、安装与设置⏹安装⏹开关选择⏹随机端子板ACS641⏹其他配套端子板⏹常用信号的连接、处理。

三、编程⏹软件安装⏹开关量⏹计数器⏹中断处理四、I/O功能说明五、附录⏹DB68插座、DIO插座⏹AC6412示意图一、AC6412说明AC6412板简介AC6412是一款通用光电隔离I/O板,具有32路输入、32路输出、二路16位计数器。

采用PCI总线支持即插即用、无需地址跳线。

AC6412的32路输入支持5-24伏输入,同时输出为大功率集电极开路输出(OC输出),可以方便的驱动继电器、LED等负载。

输出级同时提供了上拉电阻,借用外部电源可以直接输出电压。

AC6412输入通道“0”支持中断,中断号由PCI自动分配。

输入通道“28、29”可以应用为计数器通道“0、1”,计数器长度为16BIT,减法计数器。

计数器具有初始化、计数溢出标志。

主要特点、性能:⏹32路隔离输入、32路隔离输出。

输入、输出采用高密度68针插座,输入、输出全部在一个插座接线。

⏹最大隔离电压大于:500伏。

⏹输入、输出共地。

⏹输入范围:5-24伏,对应输入吸入电流:2-12毫安。

⏹输入响应时间:50微秒,最大输入频率:10KHz。

⏹32路输出为集电极开路输出,性能:最大输出电流(下拉):100毫安/路,耐压:30伏输出压降:1伏输出建立时间小于50微秒,最大输出频率10KHz。

输出级为达林顿输出,末级采用MC1413或等同芯片。

⏹输入通道“0”支持中断。

中断低电平有效。

⏹输入通道“28、29”可以作为计数器输入通道“0、1”。

计数最大频率10KHz,计数器为:16位减法计数器,支持初始化计数数值、计数溢出标志。

计数器为下降边沿有效。

⏹PCI总线,符合PCI 标准⏹AC6412占用64个I/O选通空间(自动分配)。

附表:项目数量范围速度描述开关量输入32 5-24伏10KHz开关量输出32 3-24伏10KHz 开路输出计数 2 5-24伏10KHz 公用通道28、29,下降边沿有效中断 1 5-24伏10KHz 公用通道0,低电平有效随机部件:●AC6412卡、说明书、驱动光盘。

atc中文手册

A T24C256中文资料2009-11-15 09:43特性与1MHz I2C 总线兼容1.8 到6.0 伏工作电压范围低功耗CMOS 技术写保护功能当WP 为高电平时进入写保护状态64 字节页写缓冲器自定时擦写周期100,000 编程/擦写周期可保存数据100 年8 脚DIP SOIC 封装温度范围商业级工业级和汽车级概述CAT24WC256 是一个256K 位串行CMOS E2PROM 内部含有32768 个字节每字节为8 位CATALYST 公司的先进CMOS 技术实质上减少了器件的功耗CAT24WC256 有一个64 字节页写缓冲器该器件通过I2C 总线接口进行操作管脚描述管脚名称功能A0 A1 地址输入SDA 串行数据/地址SCL 串行时钟WP 写保护Vcc +1.8V 6.0V 电源Vss 地NC 未连接极限参数工作温度工业级-55 +125商业级0 +75贮存温度-65 +150各管脚承受电压-2.0V Vcc+2.0VVcc 管脚承受电压-2.0V +7.0V封装功率损耗Ta=25 1.0W焊接温度(10 秒) 300口输出短路电流100mA功能描述CAT24WC256 支持I2C 总线数据传送协议I2C 总线协议规定任何将数据传送到总线的器件作为发送器任何从总线接收数据的器件为接收器数据传送是由产生串行时钟和所有起始停止信号的主器件控制的CAT24WC256 是作为从器件被操作的主器件和从器件都可以作为发送器或接收器但由主器件控制传送数据发送或接收的模式管脚描述SCL 串行时钟CAT24WC256 串行时钟输入管脚用于产生器件所有数据发送或接收的时钟这是一个输入管脚SDA 串行数据/地址双向串行数据/地址管脚用于器件所有数据的发送或接收SDA 是一个开漏输出管脚可与其它开漏输出或集电极开路输出进行线或wire-ORWP 写保护当WP 脚连接到Vcc 所有内存变成写保护只能读当WP 引脚连接到Vss 或悬空允许器件进行读/写操作A0 A1 器件地址输入这些管脚为硬连线或者不连接对于单总线系统最多可寻址4 个CAT24WC256 器件参阅器件寻址当这些引脚没有连接时其默认值为0I2C 总线协议I2C 总线协议定义如下1 只有在总线空闲时才允许启动数据传送2 在数据传送过程中当时钟线为高电平时数据线必须保持稳定状态不允许有跳变时钟线为高电平时数据线的任何电平变化将被看作总线的起始或停止信号起始信号时钟线保持高电平期间数据线电平从高到低的跳变作为I2C 总线的起始信号停止信号时钟线保持高电平期间数据线电平从低到高的跳变作为I2C 总线的停止信号器件寻址主器件通过发送一个起始信号启动发送过程然后发送它所要寻址的从器件的地址8 位从器件地址的高5 位固定为10100 见图5 接下来的2 位A1 A0 为器件的地址位最多可以连接4 个器件到同一总线上这些位必须与硬连线输入脚A1 A0 相对应从器件地址的最低位作为读写控制位1表示对从器件进行读操作0 表示对从器件进行写操作在主器件发送起始信号和从器件地址字节后CAT24WC256 监视总线并当其地址与发送的从地址相符时响应一个应答信号通过SDA 线CAT24WC256 再根据读写控制位R/W 的状态进行读或写操作应答信号I2C 总线数据传送时每成功地传送一个字节数据后接收器都必须产生一个应答信号应答的器件在第9 个时钟周期时将SDA 线拉低表示其已收到一个8 位数据CAT24WC256 在接收到起始信号和从器件地址之后响应一个应答信号如果器件已选择了写操作则在每接收一个8 位字节之后响应一个应答信号当CAT24WC256 工作于读模式时在发送一个8 位数据后释放SDA 线并监视一个应答信号一旦接收到应答信号CAT24WC256 继续发送数据如主器件没有发送应答信号器件停止传送数据并等待一个停止信号写操作字节写在字节写模式下主器件发送起始信号和从器件地址信息R/W 位置0 给从器件在从器件送回应答信号后主器件发送两个8 位地址字写入CAT24WC256 的地址指针主器件在收到从器件的应答信号后再发送数据到被寻址的存储单元CAT24WC256 再次应答并在主器件产生停止信号后开始内部数据的擦写在内部擦写过程中CAT24WC256 不再应答主器件的任何请求页写在页写模式下单个写周期内CAT24WC256 最多可以写入64 个字节数据页写操作的启动和字节写一样不同在于传送了一字节数据后主器件允许继续发送63 个字节每发送一个字节后CAT24WC256 将响应一个应答位且内部低6 位地址加1 高位地址保持不变如果主器件在发送停止信号之前发送大于64 个字节地址计数器将自动翻转先前写入的数据被覆盖当所有64 字节接收完毕主器件发送停止信号内部编程周期开始此时所有接收到的数据在单个写周期内写入CAT24WC256应答查询可以利用内部写周期时禁止数据输入这一特性一旦主器件发送停止位指示主器件操作结束时CAT24WC256 启动内部写周期应答查询立即启动包括发送一个起始信号和进行写操作的从器件地址如果CAT24WC256 正在进行内部写操作将不会发送应答信号如果CAT24WC256 已经完成了内部写操作将发送一个应答信号主器件可以继续对CAT24WC256 进行下一次读写操作写保护写保护操作特性可使用户避免由于不当操作而造成对存储区域内部数据的改写当WP 管脚接高时整个寄存器区全部被保护起来而变为只可读取CAT24WC256 可以接收从器件地址和字节地址但是装置在接收到第一个数据字节后不发送应答信号从而避免寄存器区域被编程改写读操作CAT24WC256 读操作的初始化方式和写操作时一样仅把R/W 位置为1 有三种不同的读操作方式立即/当前地址读选择/随机读和连续读立即/当前地址读的地址计数器内容为最后操作字节的地址加1 也就是说如果上次读/写的操作地址为N 则立即读的地址从地址N+1 开始如果N=E 此处E=32767 则计数器将翻转到0 且继续输出数据CAT24WC256接收到从器件地址信号后R/W 位置1 它首先发送一个应答信号然后发送一个8 位字节数据主器件不需发送一个应答信号但要产生一个停止信号选择/随机读选择/随机读操作允许主器件对寄存器的任意字节进行读操作主器件首先通过发送起始信号从器件地址和它想读取的字节数据的地址执行一个伪写操作在CAT24WC256 应答之后主器件重新发送起始信号和从器件地址此时R/W 位置1 CAT24WC256 响应并发送应答信号然后输出所要求的一个8 位字节数据主器件不发送应答信号但产生一个停止信号连续读连续读操作可通过立即读或选择性读操作启动在CAT24WC256 发送完一个8 位字节数据后主器件产生一个应答信号来响应告知CAT24WC256 主器件要求更多的数据对应每个主机产生的应答信号CAT24WC256 将发送一个8 位数据字节当主器件不发送应答信号而发送停止位时结束此操作从CAT24WC256 输出的数据按顺序由N 到N+1 输出读操作时地址计数器在CAT24WC256 整个地址内增加这样整个寄存器区域在可在一个读操作内全部读出当读取的字节超过E 此处E=32767计数器将翻转到零并继续输出数据字节。

LC866420B中文资料

CMOS IC LC866448B/44B/40B/36B/32B/28B/24B/20B/16B/12B/08B8-Bit Single Chip MicrocontrollerPreliminaryOverviewThe LC866448B/44B/40B/36B/32B/28B/24B/20B/16B/12B/08B microcontrollers are 8-bit single chip microcontrollers with the following on-chip functional blocks:- CPU : Operable at a minimum bus cycle time of 0.5µs (microsecond)- On-chip ROM Maximum Capacity : 48K bytes- On-chip RAM Capacity : 1152/768/640/512 bytes(LC866448B/44B/40B/36B/32B/28B/24B/20B/16B/12B/08B)- 16-bit timer /counter (or two 8-bit timers)- 16-bit timer /PWM (or two 8-bit timers)- 8-channel × 8-bit AD converter- Two 8-bit synchronous serial-interface circuits (1-channel × 16bit, 1-channel × 8bit)- 14-source 10-vectored interrupt systemAll of the above functions are fabricated on a single chip.Features(1) Read-Only Memory (ROM) : LC866448B 49152 × 8 bits : LC866444B 45056 × 8 bits : LC866440B 40960 × 8 bits : LC866436B 36864 × 8 bits : LC866432B 32768 × 8 bits : LC866428B 28672 × 8 bits : LC866424B 24576 × 8 bits : LC866420B 20480 × 8 bits : LC866416B 16384 × 8 bits : LC866412B 12288 × 8 bits : LC866408B 8192 × 8 bits (2) Random Access Memory (RAM) : LC866448B/44B/40B/36B 1152 × 8 bits : LC866432B/28B/24B 768 × 8 bits : LC866420B/16B 640 × 8 bits : LC866412B/08B 512 × 8 bits (3) Bus Cycle Time/Instruction Cycle TimeThe LC866448B/44B/40B/36B/32B/28B/24B/20B/16B/12B/08B are constructed to read ROM twice within one instruction cycle. It has 1.7 times more performance capability within the same instruction cycle compared to our 4-bit microcomputers (LC66000 series).Bus cycle time indicates the speed to read ROM.Bus cycle timeCycle timeClock dividerSystem clock oscillation Oscillation FrequencyVoltage 0.5µs 1µs 1/1 Ceramic resonator oscillation 6MHz 4.5V to 6.0V 2µs 4µs 1/1 Ceramic resonator oscillation 3MHz 2.5V to 6.0V 7.5µs 15µs 1/1 RC resonator oscillation 800kHz 2.5V to 6.0V 183µs 366µs1/2Crystal oscillation32.768kHz2.5V to 6.0V(4) Ports- Input/output ports : 1 port (8 terminals : port 1) Input/output programmable in a bit - 15V withstand Input/Output ports : 2 ports (12 terminals) Input/output port programmable in nibble unit : 1 port (8 terminals : port 0)(When the N-channel open drain output is selected, the data in a bit can be inputted.) Input/output port programmable in a bit : 1 port (4 terminals : port 3) - Input port : 2 ports (14 terminals : port 7,8) - VFD output port : 38 terminals Large current output for digit : 16 terminals Pull-down resistor option available - Other function Input/output port : 1 port (6 terminals : port E) Input port : 2 ports (16 terminals : port C,D) (5) VFD automatic dislay controller-Segment/digit output pattern programmable Any segment/digit combination available VFD parallel-drive available - 16-step dimmer function available (6) AD converter- 8-channel × 8-bit AD converter (7) Serial-interface- 1 channel × 16-bit serial-interface circuits - 1 channel × 8-bit serial-interface circuits - LSB first / MSB first function available- Internal 8-bit baud-rate generator in common with two serial-interface circuits(8) Timer- Timer 016-bit timer/counter2-bit prescaler + 8-bit programmable prescalerMode 0 : Two 8-bit timers with programmable prescalerMode 1 : 8-bit timer with programmable prescaler + 8-bit counterMode 2 : 16-bit timer with programmable prescalerMode 3 : 16-bit counterThe resolution of Timer is tCYC. (tCYC: cycle time)- Timer 116-bit timer/PWMMode 0 : Two 8-bit timersMode 1 : 8-bit timer + 8-bit PWMMode 2 : 16-bit timerMode 3 : Variable-bit PWM (9-16 bits)In Mode 0 and Mode 1,the resolution of Timer and PWM is tCYC.In Mode 2 and Mode 3,the resolution of Timer and PWM selectable: tCYC or 1/2 tCYC by program - Base timerEvery 500ms overflow system for a clock application (using 32.768kHz crystal oscillation for Base timer clock)Every 976µs, 3.9ms, 15.6ms, 62.5ms overflow system (using 32.768kHz crystal oscillation for Base timer clock)The Base timer clock selectable; 32.768kHz crystal oscillation, System clock, and programmable prescaler output of Timer 0(9) Buzzer output- The Buzzer sound frequency selectable; 4KHz, 2KHz (using 32.768kHz crystal oscillation for Basetimer clock)(10) Remote-control receiver circuit (Shares with the P73/INT3/T0IN terminal)- Noise Rejection function (the time constant of noize rejection filter: 1tCYC/16tCYC/64tCYC)(tCYC: instruction cycle time)- Switch Polarity function(11) Watchdog timer- The watchdog timer is taken on RC outside- Watchdog timer operation selectable: interrupt system, system reset(12) Interrupt system- 14-source 10-vectored interrupts :1. External interrupt INT0 (include watchdog timer)2. External interrupt INT13. External interrupt INT2, Timer/counter T0L (Lower 8-bit)4. External interrupt INT3, Base timer5. Timer/counter T0H (Upper 8-bit)6. Timer T1L, Timer T1H7. Serial-interface SIO08. Serial-interface SIO19. AD converter10. VFD automatic display controller, Port 0- Built-in Interrupt Priority control registerMicrocontroller allows 3 levels of interrupt; low level, high level, and highest level of multiplex interrupt. It can specify a low level or a high level interrupt priority from INT2/T0L through port 0(i.e. the above interrupt number from three through ten). It can also specify a low level or the highest level interruptpriority to INT0 and INT1.(13) Real-time service operationThe Real-Time Service (RTS) functions the 4-byte data-transfer between the Special Function Registers at acknowledging the interrupt request.The RTS starts within 1 instruction cycle-time and completes within 5 instructions cycle-time after occurring the interrupt request.(14) Subroutine stack levels- 128 levels (Max.): Stack area included in RAM area (15) Multiplication and division16-bit × 8-bit (7 instruction cycle times) 16-bit / 8-bit (7 instruction cycle times) (16) Three oscillation circuits- On-chip RC oscillation circuit using for the system clock. - On-chip CF oscillation circuit using for the system clock.- On-chip crystal oscillation circuit using for the system clock and for time-base clock. (17) Standby function- HALT mode functionThe HALT mode is used to reduce power dissipation. In this operation mode, program execution is stopped. This operation mode can be released by interrupt request signals or the initial system reset request signal. - HOLD mode functionThe HOLD mode is used to freeze all the oscillations;RC (internal), CF and Crystal oscillations. This mode can be released by the following operations. • Reset terminal (RES ) set to Low level• P70/INT0/T0IN, P71/INT1/T0IN terminals set to assigned level (programmable) • Input a Port 0 interrupt condition(18) Factory shipment• QFP80E delivery form(19) Development support toolsEvaluation (EVA) chip : LC866097 EPROM version : LC86E6449 One time version : LC86P6449 Emulator : EVA-86000 + ECB866400 (Evaluation chip board) + POD866400 (POD)Notice for use1. Set VDD=4.0V to 6.0V at using S16 to S37 as input port.2. Follow the under table.Frequency range of the system clock Voltage range Clock Divider Note15kHz to 30kHz 1/1 Can not use 1/2 divider30kHz to 6MHz 4.5V to 6.0V 1/1,1/215kHz to 30kHz 1/1 Can not use 1/2 divider30kHz to 1.5MHz 1/1,1/2 1.5MHz to 3MHz 2.5V to 6.0V 1/2 Can not use 1/1 divider 4.5V to 6.0V 1/1,1/2Internal RC oscillation 2.5V to 6.0V 1/2 Can not use 1/1 dividerPin AssignmentQIP80EPackage Dimension (unit : mm)3174SANYO : QIP-80EP00 P01 P02 P03 P04 P05 P06 P07 VSS2 P10/SO0 P11/SI0/SB0 P12/SCK0 P13/SO1 P14/SI1/SB1 P15/SCK1 P16/BUZ S15/T15 S14/T14 S13/T13 S12/T12 S11/T11 S10/T10 S9/T9 S8/T8 S7/T7 S6/T6 S5/T5 S4/T4 S3/T3 S2/T2 S1/T1 S0/T0P 17/P W M 0P 30P 31P 32P 33P 70/I N T 0R E S X T 1/P 74X T 2/P 75V S S 1C F 1C F 2V D D 1P 80/A N 0P 81/A N 1P 82/A N 2P 83/A N 3P 84/A N 4P 85/A N 5P 86/A N 6P 87/A N 7P 71/I N T 1P 72/I N T 2/T 0I N P 73/I N T 3/T 0I NS 37/P E 5 S 36/P E 4 S 35/P E 3 S 34/P E 2 S 33/P E 1 S 32/P E 0 S 31/P D 7 S 30/P D 6 S 29/P D 5 S 28/P D 4 S 27/P D 3 S 26/P D 2 S 25/P D 1 S 24/P D 0 S 23/P C 7 S 22/P C 6 S 21/P C 5 S 20/P C 4 S 19/P C 3 S 18/P C 2 S 17/P C 1 S 16/P C 0 V P V D D 265 66 67 68 69 70 71 72 73 74 75 76 77 78 79 8040 39 38 37 36 35 34 33 32 31 30 29 28 27 26 251 2 3 4 5 6 7 8 9 10 11 12 13 14 15 1617 18 19 20 21 22 23 2464 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41System Block DiagramPin description**A state of pins at resetPin name Input/output mode A state of pull-up resistor specified at pull-up optionPort 0 Input Fixed pull-up resistor OFFPorts 1,3 Input Programmable pull-up resistor OFFPorts 70,71,72,73 Input Fixed pull-up resistor OFFS0/T0 to S15/T15 P channel Transistor OFFS16 to S37 P channel Transistor OFF[Notes]When connecting to the power supply, the power pins must be connected like following figure.In case for the LC866448B/44B/40B/36B/32B/28B/24B/20B/16B/12B/08BIn case for the LC866432A/28A/24A/20A/16A/12A/08A*1 Each of the power pins, VDD1 and VDD2, should be connected the capacitors for reducing the noise into the VDD1 pin.1. Absolute Maximum Ratings at VSS1=VSS2=0V and Ta=25°C2. Recommended Operating Range at Ta=-30°C to +70°C, VSS1=VSS2=0VRatings Parameter Symbol Pins ConditionsVDD[V] min. typ. max.unitFmCF(1) CF1,CF2 •6MHz(ceramic resonatoroscillation)•Refer to figure 1 4.5 to 6.0 To bedeter-mined6 Tobedeter-minedFmCF(2) CF1,CF2 •3MHz(ceramic resonatoroscillation)•Refer to figure 1 2.5 to 6.0 To bedeter-mined3 Tobedeter-minedFmRC RC oscillation 2.5 to 6.0 0.3 0.8 3.0 MHzOscillationfrequencyrange(Note 1)FsXtal XT1,XT2 •32.768kHz(crystal oscillation)•Refer to figure 22.5 to 6.0 32.768 kHztmsCF(1) CF1,CF2 •6MHz(ceramic resonatoroscillation)•Refer to figure 34.5 to 6.0 0..1 3.04.5 to 6.0 0.1 3.0tmsCF(2) CF1,CF2 •3MHz(ceramic resonatoroscillation) •Refer to figure 3 2.5 to 6.0 0.1 3.0ms 4.5 to 6.0 0.7 0.8Oscillationstabilizingtime period(Note 1)tssXtal XT1,XT2 •32.768kHz(crystal oscillation) •Refer to figure 3 2.5 to 6.0 1.4 2.2s(Note 1) The oscillation constant is shown on table 1 and table 2.3. Electrical Characteristics at Ta=-30°C to +70°C, VSS1=VSS2=0V4. Serial input/output characteristics / Ta=-30°C to +70°C, VSS1=VSS2=0VRatingsParameter Symbol Pins Conditions VDD[V] min. typ. max. unitCycle t CKCY (1) 2 Low Level pulse width t CKL (1) 1 I n p u t c l o c kHigh Level pulse widtht CKH (1) SCK0,SCK1 Refer to figure 5 2.5 to 6.0 1 Cycle t CKCY (2) 2 Low Level pulse widtht CKL (2) 1/2t CKCY S e r i a l c l o c kO u t p u t c l o c kHigh Level pulse widtht CKH (2) SCK0,SCK1 •Use pull-up resistor (1k Ω) in the open drain output. •Refer to figure 5 2.5 to 6.01/2t CKCY t CYC4.5 to 6.0 0.1 Data set-up timet ICK 2.5 to 6.0 0.44.5 to 6.0 0.1 S e r i a l i n p u tData hold time t CKI •SI0,SI1 •SB0,SB1 •Data set-up to SCK0,1 •Data hold fromSCK0,1•Refer to figure 52.5 to 6.0 0.44.5 to 6.0 7/12 t CYC +0.2 Output delay time (External clock using for serial transfer clock) t CKO(1) 2.5 to 6.0 7/12t CYC +1 4.5 to 6.0 1/3 t CYC+0.2 S e r i a l o u t p u t Output delay time (Internal clock using for serialtransfer clock) t CKO(2) •SO0,SO1 •SB0,SB1 •Use pull-up resistor (1k Ω) inthe open drainoutput. •Data hold from SCK0,1 •Refer to figure 5 2.5 to 6.01/3t CYC +1µs5. Pulse Input Conditions at Ta=-30°C to +70°C, VSS1=VSS2=0V6. AD Converter Characteristics at Ta=-30°C to + 70°C, VSS1=VSS2=0VRatings Parameter Symbol Pins ConditionsVDD[V] min. typ. max.unit Resolution N 4.5to6.0 8 bitAbsolute precision (Note 2) ET 4.5to6.0 ±1.5 LSBAD conversion time =16 × tCYC(ADCR2=0)(Note 3)15.68(tCYC=0.98µs)65.28(tCYC=4.08µs)Conversion time tCADAD conversion time =32 × tCYC(ADCR2=1)(Note 3) 4.5 to 6.031.36(tCYC=0.98µs)130.56(tCYC=4.08µs)µsAnalog input voltage range VAIN 4.5to6.0VSSVDDV IAINH VAIN=VDD4.5to6.0 1Analog portinput current IAINL AN0 to AN7VAIN=VSS 4.5to6.0-1µA(Note 2) Absolute precision excepts the quantizing error (±1/2 LSB).(Note 3) The conversion time means the time from executing the AD conversion instruction to setting the complete digital conversion value to the register.7. Current Dissipation Characteristics at Ta=-30°C to +70°C, VSS1=VSS2=0VRatingsParameter Symbol Pins Conditions VDD[V] min. typ. max.unitIDDOP(1) •FmCF=6MHz Ceramic resonator oscillation•FsXtal=32.768kHzcrystal oscillation •System clock : CF oscillation •Internal RC oscillation stops •1/1 divided 4.5 to 6.0 10 25 IDDOP(2) 4.5 to 6.0 3 9 IDDOP(3) •FmCF=3MHz Ceramic resonator oscillation•FsXtal=32.768kHz crystal oscillation •System clock : CF oscillation •Internal RC oscillation stops •1/2 divided2.5 to 4.5 1.5 5 IDDOP(4) 4.5 to 6.0 0.73.4 IDDOP(5) •FmCF=0Hz(The oscillation stops)•FsXtal=32.768kHzcrystal oscillation •System clock : RC oscillation •1/2 divided2.5 to 4.5 0.4 2.8mA IDDOP(6) 4.5 to 6.0 35 130 Current dissipation during basic operation (Note 4) IDDOP(7) •FmCF=0Hz (The oscillation stops)•FsXtal=32.768kHz crystal oscillation•System clock : 32.768kHz •Internal RC oscillation stops •1/2 divided2.5 to 4.5 15 70µAContinue.RatingsParameter Symbol Pins Conditions VDD[V] min. typ. max.unitIDDHALT(1) •HALT mode •FmCF=6MHzCeramic resonatoroscillation•FsXtal=32.768kHz crystal oscillation •System clock : CF oscillation •Internal RC oscillation stops •1/1 divided4.5 to 6.0 5 14 IDDHALT(2) 4.5 to 6.0 2.2 7 IDDHALT(3) •HALT mode•FmCF=3MHz Ceramic resonator oscillation•FsXtal=32.768kHz crystal oscillation•System clock : CF oscillation •Internal RC oscillation stops •1/2 divided 2.5 to 4.5 0.8 4mA IDDHALT(4) 4.5 to 6.0 400 1600 IDDHALT(5) •HALT mode FmCF=0Hz (The oscillation stops)•FsXtal=32.768kHz crystal oscillation •System clock : RC oscillation •1/2 divided2.5 to 4.5 200 1300 IDDHALT(6) 4.5 to 6.0 25 100 Current dissipation in HALT mode (Note 4) IDDHALT(7) •HALT modeFmCF=0Hz (The oscillation stops)•FsXtal=32.768kHz crystal oscillation •System clock : crystal oscillation •Internal RC oscillation stops •1/2 divided2.5 to 4.5 8 55 IDDHOLD(1) 4.5 to 6.0 0.05 30 Current dissipation in HOLD mode (Note 4)IDDHOLD(2) HOLD mode2.5 to 4.5 0.02 20µA(Note 4) The currents of the output transistors and the pull-up MOS transistors are ignored.Table 1. Ceramic resonator oscillation recommended constant (main-clock)Oscillation typeMaker OscillatorC1C2CSA6.00MG 33pF 33pF MurataCST6.00MGW on chip KBR-6.0MSB 33pF 33pF PBRC6.00A(chip type) 33pF 33pFKBR-6.0MKC6MHz ceramic resonator oscillationKyoceraPBRC6.00B(chip type)on chipCSA3.00MG 33pF33pFMurata CST3.00MGW on chip3MHz ceramic resonator oscillationKyocera KBR-3.0MS 47pF 47pF* Both C1 and C2 must be use K rank (±10%) and SL characteristics.Table 2. Crystal oscillation guaranteed constant (sub-clock)Oscillation typeMaker Oscillator C3 C4 Rd 32.768kHz crystal oscillationEPSONC-002RX18pF18pF680k Ω* Both C3 and C4 must be use J rank (±5%) and CH characteristics.(Not in need of high precision, use K rank (±10%) and SL characteristics.)(Notes) • Please place the oscillation-related parts as close to the oscillation pins as possible with the shortest possible pattern length since the circuit pattern affects the oscillation frequency.• If you use other oscillators herein, we provide no guarantee for the characteristics.Figure 1 Main-clock circuitFigure 2 Sub-clock circuit Ceramic resonator oscillationCrystal oscillationFigure 3 Oscillation stable timeFigure 4 Reset circuitFigure 5 Serial input / output test conditionFigure 6 Pulse input timing condition<Timing><AC timing point><Test load>(Note) Fix the value of C RES , R RES that issure to reset until 200µs, after Power supply has been over inferior limit of supply voltage.RESVDDLC866448B/44B/40B/36B/32B/28B/24B/20B/16B/12B/08B No.6699-21/21memo: PS 元器件交易网。

施耐德P64x系列

主要保护功能

>> 87T变压器差动保护

如 右图 - 3 所 示,比率制动 的 变 压器 差动 保 护 具 有三折线比率制动特性。当变压器发生内部故障 时,将产生差动电流。制动电流仅为流过被保护 元 件 的 电 流,如 负 载 电 流 或 外 部 穿 越 性 故 障 电 流。启动段为水平特性,方便调试,然后为第一段 斜率(K1);K1采用低斜率特性,以提高内部故障 的灵敏性,同时允许调压带来的电流误差和任何 CT变比带来的误差电流。当电流大于额定值后, 外部严重故障将有可能导致CT饱和,因此将抬高 到第二 段 斜率 段。P 6 4x在 K 2比率制动段内具 有 暂态制动特性以确保对CT拐点电压要求最低。

为增强热复制性能,可采用环境温度或油温进行 补偿。保护装置通过安装的RTD插件选项实现与 相应位置PT100测试探头连接(户外,或变压器 油箱内)。此外,如果对相应探头位置使用绝对测 量温度,可直接为每一探头设定告警或跳闸点。 可允许接入十个温度探测器,通过PSL可编程逻 辑方案可对散热马达和风扇进行额外控制。

>> 断路器失灵保护

断路器失灵保护可以通过P64x内部保护启动,也 可以通过外部保护启动。当外部线路或母线保护 只用于跳一台(或多台)断路器时,P64x具有为每

台断路器启动断路器失灵保护方案,全部采用快 速低电流判据,支持重跳该断路器或跳近区断路 器功能。

监视功能

P64x提供VTS功能,检测单相,二相或三相PT断 线(P643和P645型号装有三相PT输入模件)。 同时装置还提供CTS功能,用于检测相CT断线。 利用“差动CTS”功能(专利技术),装置智能性 地比 较 所 有C T 端 负 序不平 衡电 流,以 判 定 哪 组 CT发生故障。此比较元件可检测所有CT短路,开 路,以及不带固定延时的断线。此CTS功能可用 于当CT发生断线时闭锁差动保护,或选择暂时性 降低差动保护灵敏度以避免保护误动。CTS确保 了差动保护元件的实时稳定性,及可适用于REF 保护。

8846用户手册(1)

目录

章节 1

标题

页

章概述和技术指标.................................................................................. 1-1

概述 ................................................................................................................... 1-3 用户文件 ........................................................................................................... 1-3 关于本手册 ....................................................................................................... 1-3 安全信息 ........................................................................................................... 1-4

®

8845A/8846A Digital Multimeter

用户手册

July 2006, Rev. 2, 6/08 (Simplified Chinese)

© 2006, 2007, 2008 Fluke Corporation. Specifications subject to change without notice. All rights reserved. All product names are trademarks of their respective companies.

CA 6418CN 接地回路电阻钳表用户手册说明书

接地回路电阻钳表C.A 6418CN -用户手册您刚刚购买了接地回路电阻钳表C.A 6418,感谢您对我们的信任。

为了更好地使用您的设备,请:仔细阅读本用户操作手册,依照注意事项操作测量类别的定义测量类别IV为对低电压设备的测量。

例如:能源供应、仪表和保护装置。

测量类别III为对建筑安装的测量。

例如:配电盘、断路器、固定工业机器或设备。

测量类别II为对直接连接到低压设备的电路的测量。

例如:家用电器和便携式工具的电源。

使用注意事项对于类别IV电压100V以下或类别III电压150V以下的测量,该设备符合IEC 61010-2-032安全标准。

不遵守安全说明可能会导致触电、火灾、爆炸、设备和装置的损坏。

操作人员和/或主管部门必须仔细阅读并了解各项使用注意说明。

使用该设备前必须充分认识和了解电气危害的风险。

如果您没有依照说明使用该设备,则其提供的保护可能会受到影响,从而使您处于危险之中。

此设备可能包含的所有系统的安全性均由系统组装商负责。

请勿在超过指定频率的情况下使用钳子。

否则,磁路会达到危险温度。

请勿在电压网络或类别高于上述测量类型的情况中使用本设备。

请遵守使用环境。

如果设备损坏、不完整或未正确关闭,请勿使用本设备。

每次使用之前,请检查外壳绝缘状况。

所有部件损坏,包含绝缘体的损坏(即使部分损坏,都应当记录报修或更换。

使用设备前,请确保它完全干燥。

如果设备潮湿,在连接或使用前,必须将设备完全干燥。

使用设备时,请勿将手指放在防护装置之外。

请避免测量头受到任何撞击,尤其是铁的部位。

保持铁的表面清洁。

任何程度的污垢都可能导致钳子故障。

始终使用个人安全保护。

任何故障排除或计量检查程序都必须由合格并经授权的人员进行。

目录1. 介绍 (4)1.1. 介绍 (4)1.2. 设备介绍 (4)1.3. 功能按键 (6)1.4. 显示屏 (6)1.5. 电池安装 (7)1.6. 设置日期和时间 (7)2. 使用 (8)2.1. 概述 (8)2.2. 阻抗和电流的测量 (8)2.3. 电流测量 (10)2.4. 设备设置(SET-UP) (11)2.5. 调节 (12)2.6. 错误 (14)2.7. 自动待机 (14)2.8. 数据储存 (15)3. 技术参数 (17)3.1. 基本参数 (17)3.2. 电气规格 (17)3.3. 应用领域变量 (18)3.4. 电源 (19)3.5. 使用环境 (19)3.6. 机械性能 (20)3.7. 符合国际标准 (20)3.8. 电磁兼容性(CEM) (20)4. 产品维护 (21)4.1. 产品清洁 (21)4.2. 电池更换 (21)5. 质保 (23)1. 介绍1.1. 介绍1.1.1. 包装配置便携箱内含仪器,还包含:4节LR6或AA电池。

25LC640中文资料

- Protect none, 1/4, 1/2, or all of array

• Built-in write protection

- Power on/off data protection circuitry

- Write enable latch

- Write protect pin

• Sequential read

Input

0.5 VCC

Output

0.5 VCC

Note 1: For VCC ≤ 4.0V

2: For VCC > 4.0V

TABLE 1-2: DC CHARACTERISTICS

All parameters apply over the Commercial (C): Tamb = 0°C to +70°C

CINT

—

(all inputs and outputs)

7

pF

Operating Current

ICC Read

—

—

ICC Write

—

—

1

mA

500

µA

5

mA

3

mA

Standby Current

ICCS

—

—

5

µA

1

µA

Note: This parameter is periodically sampled and not 100% tested.

0°C to +70°C -40°C to +85°C -40°C to +125°C

DESCRIPTION

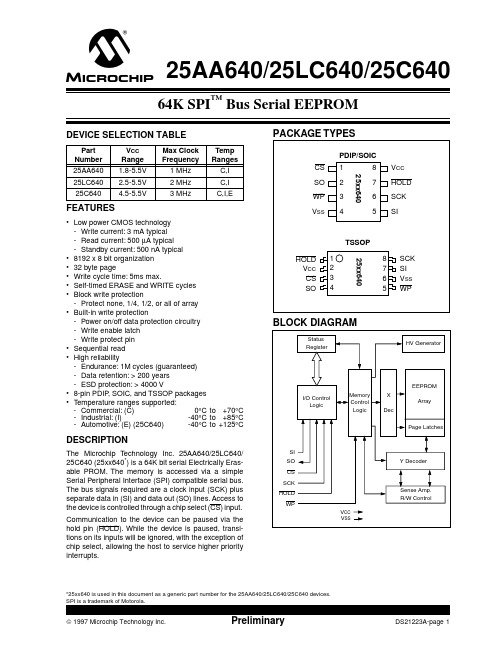

The Microchip Technology Inc. 25AA640/25LC640/ 25C640 (25xx640*) is a 64K bit serial Electrically Erasable PROM. The memory is accessed via a simple Serial Peripheral Interface (SPI) compatible serial bus. The bus signals required are a clock input (SCK) plus separate data in (SI) and data out (SO) lines. Access to the device is controlled through a chip select (CS) input.

DG642中文资料

FEATURESD Wide Bandwidth: 500 MHzD Low Crosstalk at 5 MHz: –85 dB D Low r DS(on): 5D TTL Logic CompatibleD Fast Switching: tD Single Supply CompatibilitySPECIFICATIONSParameter Analog SwitchAnalog Signal RangeDrain-Source On-ResistanceCMax b Unit8V889WTYPICAL CHARACTERISTICS 6543210C u r r e n t (m A )Charge Injection vs. V DTEST CIRCUITSS3 VIN3 VGNDV OUTR L75 W R LDocument Number: 70058 S-52433—Rev. E, S FaxBack 408-970-56004-9APPLICATIONS Power SuppliesPower supply flexibility is a useful feature of the DG641/642/643 series. It can be operated from a single positive supply (V+) if required (V– connected to ground). Note that the analog signal must not exceed V– by more than –0.3 V to prevent forward biasing the substrate p-n junction. The use of a V– supply has a number of advantages:1.It allows flexibility in analog signal handling, i.e., with V– =–5 V and V+ = 12 V; up to "5-V ac signals can be controlled.2.The value of on capacitance [C S(on)] may be reduced. Aproperty known as ‘the body-effect’ on the DMOS switch devices causes various parametric effects to occur. One of these effects is the reduction in C S(on) for an increasing V body-source. Note however that to increase V–normally requires V+ to be reduced (since V+ to V– = 21 V max.). A reduction in V+ causes an increase in r DS(on), hence a compromise has to be achieved. It is also useful to note that tests indicate that optimum video linearity performance (e.g., differential phase and gain) occurs when V– is around –3 V.3.V– eliminates the need to bias the analog signal usingpotential dividers and large coupling capacitors. DecouplingIt is an established rf design practice to incorporate sufficient bypass capacitors in the circuit to decouple the power supplies to all active devices in the circuit. The dynamic performance of the DG641/642/643 series is adversely affected by poor decoupling of power supply pins. Also, of even more significance, since the substrate of the device is connected to the negative supply, adequate decoupling of this pin is essential. Suitable decoupling capacitors are 1- to 10-m F tantalum bead, plus 10- to 100-nF ceramic or polyester. Rules:1.Decoupling capacitors should be incorporated on allpower supply pins (V+, V–). (See Figure 7).2.They should be mounted as close as possible to thedevice pins.3.Capacitors should be of a suitable type with good highfrequency characteristics – tantalum bead and/or ceramic disc types are adequate.++–3 VGNDs+15 VDG64XV+V–S1S2S3S4D1D2D3D4C1C2C1C2C1 = 10 m F TantalumC2 = 0.1 m F CeramicFIGURE 7.Supply DecouplingBoard LayoutPCB layout rules for good high frequency performance must also be observed to achieve the performance boasted by these analog switches. Some tips for minimizing stray effects are:e extensive ground planes on double sided PCB,separating adjacent signal paths. Multilayer PCB is even better.2.Keep signal paths as short as practically possible, with allchannel paths of near equal length.3.Careful arrangement of ground connections is also veryimportant. Star connected system grounds eliminate signal current, flowing through ground path parasitic resistance, from coupling between channels.Figure 8 shows a 4-channel video multiplexer using a DG641.In Figure 9, two coax cables terminated on 75 W bring two video signals to the DG642 switch. The two drains tied together lower the on-state capacitance. An Si582 video amplifier drives a double terminated 75-W cable. The double terminated coax cable eliminates line reflections.。

LCD12864中文资料

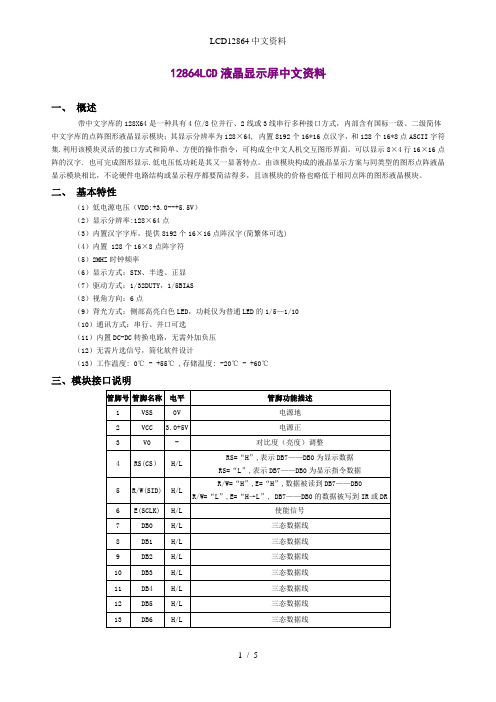

12864LCD液晶显示屏中文资料一、概述带中文字库的128X64是一种具有4位/8位并行、2线或3线串行多种接口方式,内部含有国标一级、二级简体中文字库的点阵图形液晶显示模块;其显示分辨率为128×64, 内置8192个16*16点汉字,和128个16*8点ASCII字符集.利用该模块灵活的接口方式和简单、方便的操作指令,可构成全中文人机交互图形界面。

可以显示8×4行16×16点阵的汉字. 也可完成图形显示.低电压低功耗是其又一显著特点。

由该模块构成的液晶显示方案与同类型的图形点阵液晶显示模块相比,不论硬件电路结构或显示程序都要简洁得多,且该模块的价格也略低于相同点阵的图形液晶模块。

二、基本特性(1)低电源电压(VDD:+3.0--+5.5V)(2)显示分辨率:128×64点(3)内置汉字字库,提供8192个16×16点阵汉字(简繁体可选)(4)内置 128个16×8点阵字符(5)2MHZ时钟频率(6)显示方式:STN、半透、正显(7)驱动方式:1/32DUTY,1/5BIAS(8)视角方向:6点(9)背光方式:侧部高亮白色LED,功耗仅为普通LED的1/5—1/10(10)通讯方式:串行、并口可选(11)内置DC-DC转换电路,无需外加负压(12)无需片选信号,简化软件设计(13)工作温度: 0℃ - +55℃ ,存储温度: -20℃ - +60℃三、模块接口说明*注释1:如在实际应用中仅使用串口通讯模式,可将PSB接固定低电平,也可以将模块上的J8和“GND”用焊锡短接。

*注释2:模块内部接有上电复位电路,因此在不需要经常复位的场合可将该端悬空。

*注释3:如背光和模块共用一个电源,可以将模块上的JA、JK用焊锡短接。

控制器接口信号说明:1、RS,R/W的配合选择决定控制界面的4种模式:2、E信号● 忙标志:BF BF标志提供内部工作情况.BF=1表示模块在进行内部操作,此时模块不接受外部指令和数据.BF=0时,模块为准备状态,随时可接受外部指令和数据.利用STATUS RD 指令,可以将BF读到DB7总线,从而检验模块之工作状态.● 字型产生ROM(CGROM)字型产生ROM(CGROM)提供8192个此触发器是用于模块屏幕显示开和关的控制。

stc8a8k64s4a12中文资料_数据手册_参数

3.4.3 LQFP48 封装尺寸图(9mm*9mm) ................................................................................... 59

3.4.4 LQFP44 封装尺寸图(12mm*12mm) ............................................................................... 60

3.8.3 STC8F8K64S4A12 应用线路图............................................................................................ 67

3.8.4 STC8F2K64S4 应用线路图 .................................................................................................. 67

3.7 STC8 系列单片机命名规则............................................................................................................. 65

3.8 应用线路图 ....................................................................................................................................... 66

3.5 STC8 系列单片机选型价格一览表 ................................................................................................. 63

25LC640中文翻译资料

25LC640中文翻译资料山东泰开自动化李凯设备选择表(25AA640 25C640 )64K SPI 总线串口EEPROM:封装类型:方块图特征:●低功率COMS工艺-写电流:3mA标准-读电流:500u标准-待机电流:500nA标准●8192×8位组织●32字节页●写周期时间:5mA最大●自动同步擦除和写入周期●块写入保护-未保护,1/4,1/2,或全部数组●内置的写保护-电源开/关数据保护电路-写允许锁存器-写保护管脚●连续读●高可靠性-耐久度:1M周期(可保证的)-数据保持:大于200年-静电防护:大于4000V●8脚PDIP,SOPC,和TSSOP封装●温度范围支持;-商业级:(C) 0℃至 +70℃-工业级:(I) -40℃至 +85℃-汽车级:(E) -40℃至 +125℃说明:美国微芯科技公司的25AA640/25LC640/25C640(25XX640)是64K比特电可擦除PROM。

这个存储器的使用通道是简单串行外围接口(SPI)兼容串行总线。

这个总线信号需要时钟输入(SCK)加单独数据在(SI)和数据输出(SO)连线。

进入装置的控制是通过芯片选择(CS)输入。

通信到装置能够暂停通道保持管脚(HOLD)。

虽然装置是暂停,转变在输入将是忽略,除了志片的选择,允许主动服务较高优先级的中断。

1.0电气特性图形1-1: AC 测试电路1.1 最大等级Vcc .................................7.0V全部输入和输出w.r.t.Vss...-0.6至Vcc+1.0V储存温度.....................-65℃至150℃引线的焊接温度(10秒) (300)静电保护在全部管脚...................4kV注意:强调以上这些列出关于“最大等级”可能引出永久损伤到设备。

这强调的等级仅和设备的功能操作,而且那些或任何其它的条件超出那些声明在说明书的操作表中是未隐含的。

常用4000系列标准数字电路的中文名称资料

常用4000系列标准数字电路的中文名称资料74系列芯片功能大全(点击型号查货)常用74系列标准数字电路的中文名称资料器件代号器件名称74 74LS 74HCCD4000 双3输入端或非门+单非门TI 7400 TTL 2输入端四与非门00 四2输入端与非门√√√CD4001 四2输入端或非门HIT/NSC/TI/GOL 7401 TTL 集电极开路2输入端四与非门01 四2输入端与非门(OC) √√CD4002 双4输入端或非门NSC7402 TTL 2输入端四或非门02 四2输入端或非门√√√CD4006 18位串入/串出移位寄存器NSC 7403 TTL 集电极开路2输入端四与非门03 四2输入端与非门(OC) √√CD4007 双互补对加反相器NSC 7404 TTL 六反相器04 六反相器√√√CD4008 4位超前进位全加器NSC 7405 TTL 集电极开路六反相器05 六反相器(OC) √√CD4009 六反相缓冲/变换器NSC 7406 TTL 集电极开路六反相高压驱动器06 六高压输出反相器(OC,30V) √√CD4010 六同相缓冲/变换器NSC 7407 TTL 集电极开路六正相高压驱动器07 六高压输出缓冲,驱动器(OC,30V)√√√CD4011 四2输入端与非门HIT/TI7408 TTL 2输入端四与门08 四2输入端与门√√√CD4012 双4输入端与非门NSC7409 TTL 集电极开路2输入端四与门09 四2输入端与门(OC) √√√CD4013 双主-从D型触发器FSC/NSC/TOS 7410 TTL 3输入端3与非门10 三3输入端与非门√√√CD4014 8位串入/并入-串出移位寄存器NSC7411 TTL 3输入端3与门11 三3输入端与门√√CD4015 双4位串入/并出移位寄存器TI 7412 TTL 开路输出3输入端三与非门12 三3输入端与非门(OC) √√√CD4016 四传输门FSC/TI7413 TTL 4输入端双与非施密特触发器13 双4输入端与非门√√√CD4017 十进制计数/分配器FSC/TI/MOT 7414 TTL 六反相施密特触发器14 六反相器√√√CD4018 可预制1/N计数器NSC/MOT 7415 TTL 开路输出3输入端三与门15 三3输入端与门(OC) √√CD4019 四与或选择器PHI 7416 TTL 开路输出六反相缓冲/驱动器16 六高压输出反相器(OC,15V) √CD4020 14级串行二进制计数/分频器FSC 7417 TTL 开路输出六同相缓冲/驱动器17 六高压输出缓冲,驱动器(OC,15V)√CD4021 08位串入/并入-串出移位寄存器PHI/NSC 7420 TTL 4输入端双与非门20 双4输入端与非门√√√CD4022 八进制计数/分配器NSC/MOT7421 TTL 4输入端双与门21 双4输入端与门√√√CD4023 三3输入端与非门NSC/MOT/TI 7422 TTL 开路输出4输入端双与非门22 双4输入端与非门(OC) √√CD4024 7级二进制串行计数/分频器NSC/MOT/TI 7427 TTL 3输入端三或非门25 双4输入端或非门(有选通端) √√√CD4025 三3输入端或非门NSC/MOT/TI 7428 TTL 2输入端四或非门缓冲器26 四2输入端高压输出与非缓冲器√√√CD4026 十进制计数/7段译码器NSC/MOT/TI7430 TTL 8输入端与非门27 三3输入端或非门√√√CD4027 双J-K触发器NSC/MOT/TI7432 TTL 2输入端四或门28 四2输入端或非缓冲器√√√CD4028 BCD码十进制译码器NSC/MOT/TI 7433 TTL 开路输出2输入端四或非缓冲器30 8输入端与非门√√√CD4029 可预置可逆计数器NSC/MOT/TI 7437 TTL 开路输出2输入端四与非缓冲器32 四2输入端或门√√√CD4030 四异或门NSC/MOT/TI/GOL 7438 TTL 开路输出2输入端四与非缓冲器33 四2输入端或非缓冲器(OC) √√CD4031 64位串入/串出移位存储器NSC/MOT/TI 7439 TTL 开路输出2输入端四与非缓冲器37 四2输入端与非缓冲器√√CD4032 三串行加法器NSC/TI7440 TTL 4输入端双与非缓冲器38 四2输入端与非缓冲器(OC) √√CD4033 十进制计数/7段译码器NSC/TI 7442 TTL BCD—十进制代码转换器40 双4输入端与非缓冲器√√√CD4034 8位通用总线寄存器NSC/MOT/TI 7445 TTL BCD—十进制代码转换/驱动器42 4线-10线译码器(BCD输入) √√CD4035 4位并入/串入-并出/串出移位寄存NSC/MOT/TI 7446 TTL BCD—7段低有效译码/驱动器43 4线-10线译码器(余3码输入) √CD4038 三串行加法器NSC/TI 7447 TTL BCD—7段高有效译码/驱动器44 4线-10线译码器(余3葛莱码输入) √CD4040 12级二进制串行计数/分频器NSC/MOT/TI 7448 TTL BCD—7段译码器/内部上拉输出驱动48 4线-7段译码器√CD4041 四同相/反相缓冲器NSC/MOT/TI 7450 TTL 2-3/2-2输入端双与或非门49 4线-7段译码器√CD4042 四锁存D型触发器NSC/MOT/TI 7451 TTL 2-3/2-2输入端双与或非门50 双2路2-2输入与或非门√√√CD4043 4三态R-S锁存触发器("1"触发) NSC/MOT/TI 7454 TTL 四路输入与或非门51 2路3-3输入,2路2-2输入与或非门√√√CD4044 四三态R-S锁存触发器("0"触发) NSC/MOT/TI 7455 TTL 4输入端二路输入与或非门52 4路2-3-2-2输入与或门√CD4046 锁相环NSC/MOT/TI/PHI 7473 TTL 带清除负触发双J-K触发器53 4路2-2-2-2输入与或非门√CD4047 无稳态/单稳态多谐振荡器NSC/MOT/TI 7474 TTL 带置位复位正触发双D触发器54 4路2-3-3-2输入与或非门√√CD4048 4输入端可扩展多功能门NSC/HIT/TI 7476 TTL 带预置清除双J-K触发器55 2路4-4输入与或非门√CD4049 六反相缓冲/变换器NSC/HIT/TI 7483 TTL 四位二进制快速进位全加器60 双4输入与扩展器√√CD4050 六同相缓冲/变换器NSC/MOT/TI 7485 TTL 四位数字比较器61 三3输入与扩展器√CD4051 八选一模拟开关NSC/MOT/TI 7486 TTL 2输入端四异或门62 4路2-3-3-2输入与或扩展器√CD4052 双4选1模拟开关NSC/MOT/TI 7490 TTL 可二/五分频十进制计数器64 4路4-2-3-2输入与或非门√CD4053 三组二路模拟开关NSC/MOT/TI 7493 TTL 可二/八分频二进制计数器65 4路4-2-3-2输入与或非门(OC) √CD4054 液晶显示驱动器NSC/HIT/TI 7495 TTL 四位并行输入\输出移位寄存器70 与门输入J-K触发器√CD4055 BCD-7段译码/液晶驱动器NSC/HIT/TI 7497 TTL 6位同步二进制乘法器71 与或门输入J-K触发器√CD4056 液晶显示驱动器NSC/HIT/TI 74107 TTL 带清除主从双J-K触发器72 与门输入J-K触发器√CD4059 “N”分频计数器NSC/TI 74109 TTL 带预置清除正触发双J-K触发器74 双上升沿D型触发器√√CD4060 14级二进制串行计数/分频器NSC/TI/MOT 74112 TTL 带预置清除负触发双J-K触发器78 双D型触发器√√CD4063 四位数字比较器NSC/HIT/TI 74121 TTL 单稳态多谐振荡器85 四位数值比较器√CD4066 四传输门NSC/TI/MOT74122 TTL 可再触发单稳态多谐振荡器86 四2输入端异或门√√√CD4067 16选1模拟开关NSC/TI74123 TTL 双可再触发单稳态多谐振荡器87 4位二进制原码/反码√CD4068 八输入端与非门/与门NSC/HIT/TI 74125 TTL 三态输出高有效四总线缓冲门95 4位移位寄存器√CD4069 六反相器NSC/HIT/TI74126 TTL 三态输出低有效四总线缓冲门101 与或门输入J-K触发器√CD4070 四异或门NSC/HIT/TI74132 TTL 2输入端四与非施密特触发器102 与门输入J-K触发器√CD4071 四2输入端或门NSC/TI74133 TTL 13输入端与非门107 双主-从J-K触发器√CD4072 双4输入端或门NSC/TI 74136 TTL 四异或门108 双主-从J-K触发器√CD4073 三3输入端与门NSC/TI74138 TTL 3-8线译码器/复工器109 双主-从J-K触发器√CD4075 三3输入端或门NSC/TI 74139 TTL 双2-4线译码器/复工器110 与门输入J-K触发器√CD4076 四D寄存器74145 TTL BCD—十进制译码/驱动器111 双主-从J-K触发器√√CD4077 四2输入端异或非门HIT 74150 TTL 16选1数据选择/多路开关112 双下降沿J-K触发器√CD4078 8输入端或非门/或门74151 TTL 8选1数据选择器113 双下降沿J-K触发器√CD4081 四2输入端与门NSC/HIT/TI 74153 TTL 双4选1数据选择器114 双下降沿J-K触发器√CD4082 双4输入端与门NSC/HIT/TI 74154 TTL 4线—16线译码器116 双4位锁存器√CD4085 双2路2输入端与或非门74155 TTL 图腾柱输出译码器/分配器120 双脉冲同步驱动器√CD4086 四2输入端可扩展与或非门74156 TTL 开路输出译码器/分配器121 单稳态触发器√√√CD4089 二进制比例乘法器74157 TTL 同相输出四2选1数据选择器122 可重触发单稳态触发器√√√CD4093 四2输入端施密特触发器NSC/MOT/ST 74158 TTL 反相输出四2选1数据选择器123 可重触发双稳态触发器√√√CD4094 8位移位存储总线寄存器NSC/TI/PHI 74160 TTL 可预置BCD异步清除计数器125 四总线缓冲器√√√CD4095 3输入端J-K触发器74161 TTL 可予制四位二进制异步清除计数器126 四总线缓冲器√√√CD4096 3输入端J-K触发器74162 TTL 可预置BCD同步清除计数器128 四2输入端或非线驱动器√√√CD4097 双路八选一模拟开关74163 TTL 可予制四位二进制同步清除计数器132 四2输入端与非门√√√CD4098 双单稳态触发器74164 TTL 八位串行入/NSC/MOT/TI 并行输出移位寄存器CD4099 8位可寻址锁存器NSC/MOT/ST 74165 TTL 八位并行入/串行输出移位寄存器CD40100 32位左/右移位寄存器74166 TTL 八位并入/串出移位寄存器74169 TTL 二进制四位加/减同步计数器CD40101 9位奇偶较验器74170 TTL 开路输出4×4寄存器堆CD40102 8位可预置同步BCD减法计数器74173 TTL 三态输出四位D型寄存器CD40103 8位可预置同步二进制减法计数器74174 TTL 带公共时钟和复位六D触发器CD40104 4位双向移位寄存器74175 TTL 带公共时钟和复位四D触发器CD40105 先入先出FI-FD寄存器74180 TTL 9位奇数/偶数发生器/校验器CD40106 六施密特触发器NSC\TI 74181 TTL 算术逻辑单元/函数发生器CD40107 双2输入端与非缓冲/驱动器HAR\TI 74185 TTL 二进制—BCD代码转换器CD40108 4字×4位多通道寄存器74190 TTL BCD同步加/减计数器CD40109 四低-高电平位移器74191 TTL 二进制同步可逆计数器CD40110 十进制加/减,计数,锁存,译码驱动ST 74192 TTL 可预置BCD 双时钟可逆计数器CD40147 10-4线编码器NSC\MOT 74193 TTL 可预置四位二进制双时钟可逆计数器CD40160 可预置BCD加计数器NSC\MOT 74194 TTL 四位双向通用移位寄存器CD40161 可预置4位二进制加计数器NSC\MOT 74195 TTL 四位并行通道移位寄存器CD40162 BCD加法计数器NSC\MOT 74196 TTL 十进制/二-十进制可预置计数锁存器CD40163 4位二进制同步计数器NSC\MOT 74197 TTL 二进制可预置锁存器/计数器CD40174 六锁存D型触发器74221 TTL 双/单稳态多NSC\TI\MOT 谐振荡器CD40175 四D型触发器NSC\TI\MOT 74240 TTL 八反相三态缓冲器/线驱动器CD40181 4位算术逻辑单元/函数发生器74241 TTL 八同相三态缓冲器/线驱动器CD40182 超前位发生器74243 TTL 四同相三态总线收发器CD40192 可预置BCD加/减计数器(双时钟) NSC\TI 74244 TTL 八同相三态缓冲器/线驱动器CD40193 可预置4位二进制加/减计数器NSC\TI 74245 TTL 八同相三态总线收发器CD40194 4位并入/串入-并出/串出移位寄存NSC\MOT 74247 TTL BCD—7段15V输出译码/驱动器CD40195 4位并入/串入-并出/串出移位寄存NSC\MOT 74248 TTL BCD—7段译码/升压输出驱动器CD40208 4×4多端口寄存器74249 TTL BCD—7段译码/开路输出驱动器74251 TTL 三态输出8选1数据选择器/复工器CD4501 4输入端双与门及2输入端或非门74253 TTL 三态输出双4选1数据选择器/复工器CD4502 可选通三态输出六反相/缓冲器74256 TTL 双四位可寻址锁存器CD4503 六同相三态缓冲器74257 TTL 三态原码四2选1数据选择器/复工器CD4504 六电压转换器74258 TTL 三态反码四2选1数据选择器/复工器CD4506 双二组2输入可扩展或非门74259 TTL 八位可寻址锁存器/3-8线译码器CD4508 双4位锁存D型触发器74260 TTL 5输入端双或非门CD4510 可预置BCD码加/减计数器74266 TTL 2输入端四异或非门CD4511 BCD锁存,7段译码,驱动器74273 TTL 带公共时钟复位八D触发器CD4512 八路数据选择器74279 TTL 四图腾柱输出S-R锁存器CD4513 BCD锁存,7段译码,驱动74283 TTL 4位二进制全器(消隐) 加器CD4514 4位锁存,4线-16线译码器74290 TTL 二/五分频十进制计数器CD4515 4位锁存,4线-16线译码器74293 TTL 二/八分频四位二进制计数器CD4516 可预置4位二进制加/减计数器74295 TTL 四位双向通用移位寄存器CD4517 双64位静态移位寄存器74298 TTL 四2输入多路带存贮开关CD4518 双BCD同步加计数器74299 TTL 三态输出八位通用移位寄存器CD4519 四位与或选择器74322 TTL 带符号扩展端八位移位寄存器CD4520 双4位二进制同步加计数器74323 TTL 三态输出八位双向移位/存贮寄存器CD4521 24级分频器74347 TTL BCD—7段译码器/驱动器CD4522 可预置BCD同步1/N计数器74352 TTL 双4选1数据选择器/复工器CD4526 可预置4位二进制同步1/N计数器74353 TTL 三态输出双4选1数据选择器/复工器CD4527 BCD比例乘法器74365 TTL 门使能输入三态输出六同相线驱动器CD4528 双单稳态触发器74366 TTL 门使能输入三态输出六反相线驱动器CD4529 双四路/单八路模拟开关74367 TTL 4/2线使能输入三态六同相线驱动器CD4530 双5输入端优势逻辑门74368 TTL 4/2线使能输入三态六反相线驱动器CD4531 12位奇偶校验器74373 TTL 三态同相八D锁存器CD4532 8位优先编码器74374 TTL 三态反相八D锁存器CD4536 可编程定时器74375 TTL 4位双稳态锁存器CD4538 精密双单稳74377 TTL 单边输出公共使能八D锁存器CD4539 双四路数据选择器74378 TTL 单边输出公共使能六D锁存器CD4541 可编程序振荡/计时器74379 TTL 双边输出公共使能四D锁存器CD4543 BCD七段锁存译码,驱动器74380 TTL 多功能八进制寄存器CD4544 BCD七段锁存译码,驱动器74390 TTL 双十进制计数器CD4547 BCD七段译码/大电流驱动器74393 TTL 双四位二进制计数器CD4549 函数近似寄存器74447 TTL BCD—7段译码器/驱动器CD4551 四2通道模拟开关74450 TTL 16:1多路转接复用器多工器CD4553 三位BCD计数器74451 TTL 双8:1多路转接复用器多工器CD4555 双二进制四选一译码器/分离器74453 TTL 四4:1多路转接复用器多工器CD4556 双二进制四选一译码器/分离器74460 TTL 十位比较器CD4558 BCD八段译码器74461 TTL 八进制计数器CD4560 "N"BCD加法器74465 TTL 三态同相2与使能端八总线缓冲器CD4561 "9"求补器74466 TTL 三态反相2与使能八总线缓冲器CD4573 四可编程运算放大器74467 TTL 三态同相2使能端八总线缓冲器CD4574 四可编程电压比较器74468 TTL 三态反相2使能端八总线缓冲器CD4575 双可编程运放/比较器74469 TTL 八位双向计数器CD4583 双施密特触发器74490 TTL 双十进制计数器74491CD4584 六施密特触发器74498 TTL 八进制移位寄存器CD4585 4位数值比较器74502 TTL 八位逐次逼近寄存器CD4599 8位可寻址锁存器74503 TTL 八位逐次逼近寄存器74533 TTL 三态反相八D锁存器74534 TTL 三态反相八D锁存器74540 TTL 八位三态反相输出总线缓冲器74563 TTL 八位三态反相输出触发器74564 TTL 八位三态反相输出D触发器74573 TTL 八位三态输出触发器74574 TTL 八位三态输出D触发器74645 TTL 三态输出八同相总线传送接收器74670 TTL 三态输出4×4寄存器堆。

lc86l芯片技术规格和用户手册

lc86l芯片技术规格和用户手册

(最新版)

目录

1.介绍 lc86l 芯片

2.技术规格

3.用户手册

4.总结

正文

lc86l 芯片是一款性能优越的芯片,被广泛应用于各种电子设备中。

为了更好地使用这款芯片,我们需要对其技术规格和用户手册有所了解。

首先,让我们来了解一下 lc86l 芯片的技术规格。

这款芯片具有高速、低噪声和低功耗的特点,可以满足不同设备的需求。

它的工作电压范围为 1.8V 至3.6V,工作温度范围为 -40°C 至 85°C,具有较强的稳定性。

此外,lc86l 芯片还支持多种通信协议,如 I2C、SPI 和 UART 等,方便用户进行配置和控制。

在了解了 lc86l 芯片的技术规格后,我们来看看它的用户手册。

用户手册中包含了如何使用这款芯片的详细步骤和方法。

首先,需要对芯片进行初始化,包括设置工作模式、时钟频率和通信协议等。

接下来,可以根据实际需求配置芯片的各项参数,如增益、偏置和采样率等。

最后,可以通过相应的接口对芯片进行控制,实现数据采集、处理和传输等功能。

总之,lc86l 芯片是一款性能出色的芯片,其技术规格和用户手册为用户提供了详细的使用指南。

第1页共1页。

lc86l芯片技术规格和用户手册

lc86l芯片技术规格和用户手册

摘要:

1.引言

2.lc86l 芯片的技术规格

3.lc86l 芯片的用户手册

4.结论

正文:

【引言】

lc86l 芯片是一款性能稳定、功能强大的芯片,被广泛应用于各种电子设备中。

为了帮助用户更好地了解和使用这款芯片,本文将详细介绍lc86l 芯片的技术规格和用户手册。

【lc86l 芯片的技术规格】

lc86l 芯片的技术规格主要包括以下几个方面:

1.工作电压:lc86l 芯片的工作电压范围为3.3v-5v,适应各种电压环境。

2.工作温度:lc86l 芯片的工作温度范围为-40℃-85℃,适应各种温度环境。

3.输入输出接口:lc86l 芯片拥有丰富的输入输出接口,可以满足各种应用场景的需求。

4.功耗:lc86l 芯片的功耗低,可以长时间稳定工作。

【lc86l 芯片的用户手册】

lc86l 芯片的用户手册主要包括以下几个方面:

1.芯片安装和使用方法:手册中详细介绍了如何正确安装和使用lc86l 芯片。

2.芯片的编程方法:手册中详细介绍了如何对lc86l 芯片进行编程,包括编程语言、编程工具和编程方法等。

3.芯片的调试方法:手册中详细介绍了如何对lc86l 芯片进行调试,包括调试工具、调试方法和调试技巧等。

4.芯片的维护和保养方法:手册中详细介绍了如何对lc86l 芯片进行维护和保养,包括清洁、存储和更换等。

【结论】

总的来说,lc86l 芯片是一款性能优秀、使用简单的芯片。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PreliminaryOverviewThe LC86E6449 is a CMOS 8-bit single chip microcontroller with UVEPROM for the LC866400 series.This microcontroller has the function and the pin description of the LC866400 series mask ROM version, and 48K-byte EPROM. The program data is rewritable. It is suitable to develop the program.Features(1) Option switching by EPROM dataThe option function of the LC866400 series can be specified by the EPROM data.LC86E6449 can be checked the function of the trial pieces using the mass production board. (2) Internal one-time EPROM capacity : 49408 bytes (3) Internal RAM capacity : 1152 bytesUsed EPROM or RAM capacity are equal ROM or RAM capacity of mask ROM version which applies LC86E6449.Mask ROM versionEPROM capacityRAM capacityLC866448 49152 bytes 1152 bytes LC866444 45056 bytes 1152 bytes LC866440 40960 bytes 1152 bytes LC866436 36864 bytes 1152 bytes LC866432 32768 bytes 768 bytes LC866428 28672 bytes 768 bytes LC866424 24576 bytes 768 bytes LC866420 20480 bytes 640 bytes LC866416 16384 bytes 640 bytes LC866412 12288 bytes 512 bytes LC8664088192 bytes512 bytes8-Bit Single Chip Microcontrollerwith the UVEPROM LC86E6449CMOS IC(4) Operating supply voltage : 4.5V to 6.0V(5) Instruction cycle time : 1.0µs to 366µs(6) Operating temperature : +10°C to +40°C(7) The pin compatible with the LC866400 series mask ROM devices(8) Applicable mask ROM version : LC866448/LC866444/LC866440/LC866436//LC866432/LC866428/LC866424/LC866420/LC866416/LC866412/LC866408 (9) Operating temperature : QFC80E (with window)Notice for useLC86E6449 is provided for the first release and small shipping of the LC866400 series.At using, take notice of the followings.(1) A point of difference LC86E6449 and LC866400 seriesItem LC86E6449 LC866448/44/40/36/32/28/24/20/16/12/08Operation after reset releasing The option is specified until 3ms aftergoing to a ‘H’ level to the reset terminalby dgrees. The program is executedfrom 00H of the program counter.The program is executed from 00H of theprogram counter immediately after going toa ‘H’ level to reset terminal.Pull-down resistor of the following pins •S0/T0 – S6/T6•S7/T7 – S15/T15 •S16 – S27•S28 – S37 Pull-down resistorprovided/not providedNot providedProvided (fixed)Provided (fixed)Not providedPull-down resistorprovided/not providedSpecified by the optionProvided (fixed)Specified by the optionSpecified by the optionOperating supplyVoltage range (VDD)4.5V to 6.0V 2.5V to 6.0VOperating temperaturerange (Topg)+10°C to +40°C -30°C to +70°C“L” level hold Tr. of thehigh voltage withstand inputterminalPower dissipationRefer to ‘electrical characteristics’ on the semiconductor news.LC86E6449 uses 256 bytes that is addressed on FF00H to FFFFH in the program memory as the option configuration data area. This option configuration cannot execute all options which LC866400 series have. Next tables show the options that correspond and not correspond to LC86E6449.• A kind of the option corresponding of the LC86E6449A kind of option Pins, Circuits Contents of the option 1. N-channel open drain output 2. CMOS output*1 Port 01. Pull-up MOS Tr. proveded2. Pull-up MOS Tr. not provided*2Port 1*11. Input : Programmable pull-up MOS Tr. Output : N-channel open drain2. Input : Programmable pull-up MOS Tr. Output : CMOS Input/output form of Input/output portsPort 3*11. Input : No Programmable pull-up MOS Tr. Output : N-channel open drain2. Input : Programmable pull-up MOS Tr. Output : CMOS Pull-up MOS Tr. of input portsPort 7 *1 1. No Pull-up MOS Tr.2. Pull-up MOS Tr.*1) Specified in a bit*2) Specified in nibble unit. The port of N-channel open drain output does not have the Pull-up MOS Tr..• A kind of the option not corresponding of the LC86E6449A kind of optionPins, Circuits LC86E6449 LC866448/44/40/36/32/28/24/20/16/12/08 Pull-down resistor of the high voltageWithstand output terminals•S0/T0 to S6/T6 •S16 to S27 •S28 to S37Not provided Provided (fixed) Not providedSpecified by the option Specified by the option Specified by the option(2) OptionThe option data is created by the option specified program “SU86K.EXE”. The created option data is linked to the program area by linkage loader “L86K.EXE”.LC86E6449 and LC866400 series use 256 bytes that is addressed on 0FF00H to 0FFFFH in the program memory as the option specified data area. These program memory capacity are 61440 bytes that is addressed on 0000H to BFFFH.LC866448 LC866444 LC866440 LC866436 LC866432 LC866428LC866424 LC866420 LC866416 LC866412 LC866408(1) Specification of optionProgramming data for EPROM of the LC86E6449 is required.Debugged evaluation file (EVA file) must be converted to an INTEL-HEX formatted file (HEX file) with file converter program, EVA2HEX.EXE. The HEX file is used as the programming data for the LC86E6449.(2) How to program for the EPROMLC86E6449 can be programmed by the EPROM programmer with attachment ; W86EP6448Q. • Recommended EPROM programmerProductor EEPROM programmer AdvantestR4945, R4944, R4943Andou AF-9704 AVAL PKW-1100, PKW-3000 Minato electronicsMODEL 1890A• “27512 (Vpp=12.5V) Intel high speed programming” mode available. The address must be set to “0 to 0FFFFH” and a jumper (DASEC) must be set to ‘OFF’ at programming.(3) How to use the data security function“Data security” is the disabled function to read the data of the EPROM. The following is the process in order to execute the data security. 1. Set ‘ON’ the jumper of attachment.2. Program again. Then EPROM programmer displays the error.The error means normally activity of the data security.It is not a trouble of the EPROM programmer or the LSI.Notes• Data security is not executed when the data of all address have ‘FFH’ at the sequence 2 above.• The programming by a sequential operation “BLANK ⇒PROGRAM ⇒VERIFY” cannot be executed data security at the sequence 2 above.• Set to ‘OFF’ the jumper after executing the data security.W86EP6448QData security of LSINot data security(4) How to eliminateThe programming data can be erased by using the EPROM eraser.(5) ShieldingThe UVEPROM (ultraviolet erasable programmable ROM) is in it. Put the seal on the window in use.Pin AssignmentSANYO: QFC80ES15/T15 S14/T14 S13/T13 S12/T12 S11/T11 S10/T10 S9/T9 S8/T8 S7/T7 S6/T6 S5/T5 S4/T4 S3/T3 S2/T2 S1/T1 S0/T0S 37/P E 5 S 36/P E 4 S 35/P E 3 S 34/P E 2 S 33/P E 1 S 32/P E 0 S 31/P D 7 S 30/P D 6 S 29/P D 5 S 28/P D 4 S 27/P D 3 S 26/P D 2 S 25/P D 1 S 24/P D 0 S 23/P C 7 S 22/P C 6 S 21/P C 5 S 20/P C 4 S 19/P C 3 S 18/P C 2 S 17/P C 1 S 16/P C 0 V P V D D 2P 17/P W M 0P 30P 31P 32P 33P 70/I N T 0R E S X T 1P 74X T 2/P 75V S S 1C F 1C F 2V D D 1P 80/A N 0P 81/A N 1P 82/A N 2P 83/A N 3P 84/A N 4P 85/A N 5P 86/A N 6P 87/A N 7P 71/I N T 1P 72/I N T 2/T 0I N P 73/I N T 3/T 0I NP00 P01 P02 P03 P04 P05 P06 P07 VSS2 P10/SO0 P11/SI0/SB0 P12/SCK0 P13/SO1 P14/SI1/SB1 P15/SCK1 P16/BUZ 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 8040 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 6463626160595857565554535251504948474645444342411 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24System Block DiagramLC86E6449 Pin descriptionCF1 I Input pin for the ceramic resonator oscillation - - CF2 O Output pin for the ceramic resonator oscillation - - ♦ All of port options except the pull-up resistor option of port 0 can be specified in a bit unit.*1 Memory select input for data security*2 Output enable input*3 Chip enable input*4 Connect like the following figure to reduce noise into a VDD1 terminal.*5 TA ! EPROM control signal input*6 S0/T0 to S6/T6 : not provided the pull-down resistor*7 S7/T7 to S15/T15 : provided the pull-down resistor (fixed)*8 S16 to S27 : provided the pull-down resistor (fixed)*9 S28 to S31 : not provided the pull-down resistor*10 S32 to S37 : not provided the pull-down resistor[Notes]When connecting to the power supply, the power pins must be connected like following figure.For the LC866448B/44B/40B/36BFor the LC866432A/28A/24A/20A/16A/12A/08A1. Absolute Maximum Ratings at VSS1=VSS2=0V and Ta=25°C2. Recommended Operating Range at Ta=+10°C to +40°C, VSS1=VSS2=0VRatings Parameter Symbol Pins ConditionsVDD[V] min. typ. max.unit tmsCF(1) CF1,CF2 •6MHz(ceramic resonatoroscillation)•Refer to figure 34.5 to 6.0tmsCF(2) CF1,CF2 •3MHz(ceramic resonatoroscillation)•Refer to figure 3 4.5 to 6.0msOscillationstabilizingtime period(Note 1)tssXtal XT1,XT2 •32.768kHz(crystal oscillation)•Refer to figure 34.5 to 6.0 s (Note 1) The oscillation constant is shown on table 1 and table 2.3. Electrical Characteristics at Ta=+10°C to +40°C, VSS1=VSS2=0V4. Serial Input/Output Characteristics at Ta=+10°C to +40°C, VSS1=VSS2=0VRatingsParameter Symbol Pins Conditions VDD[V] min. typ. max.unitCycle t CKCY (1) 2 Low Level pulse width t CKL (1) 1 I n p u t c l o c kHigh Level pulse widtht CKH (1) SCK0,SCK1 Refer to figure 5 4.5 to 6.0 1 Cycle t CKCY (2) 2 Low Level pulse widtht CKL (2) 1/2t CKCY S e r i a l c l o c kO u t p u t c l o c k High Level pulse widtht CKH (2) SCK0,SCK1 •Use pull-up resistor (1k Ω) in the open drain output. •Refer to figure 5 4.5 to 6.01/2t CKCY t CYCData set-up timet ICK 0.1S e r i a l i n p u tData hold timet CKI •SI0,SI1 •SB0,SB1 •Data set-up to SCK0,1 •Data hold from SCK0,1 •Refer to figure 5 4.5 to 6.0 0.1 Output delay time (External clock using for serialtransfer clock)t CKO(1) 7/12 t CYC+0.2 S e r i a l o u t p u t Output delay time (Internal clock using for serialtransfer clock)t CKO(2) •SO0,SO1 •SB0,SB1 •Use pull-up resistor (1k Ω) in the open drain output. •Data hold from SCK0,1 •Refer to figure 5 4.5 to 6.0 1/3 t CYC +0.2 µs5. Pulse Input Conditions at Ta=+10°C to +40°C, VSS1=VSS2=0V6. AD Converter Characteristics at Ta=+10°C to + 40°C, VSS1=VSS2=0VRatings Parameter Symbol Pins ConditionsVDD[V] min. typ. max.unit Resolution N 4.5to6.0 8 bitAbsolute precision (Note 2) ET 4.5to6.0 ±1.5 LSBAD conversion time =16 × tCYC(ADCR2=0)(Note 3)15.68(tCYC=0.98µs)65.28(tCYC=4.08µs)Conversion time tCADAD conversion time =32 × tCYC(ADCR2=1)(Note 3) 4.5 to 6.031.36(tCYC=0.98 µs)130.56(tCYC=4.08µs)µsAnalog input voltage range VAIN 4.5to6.0VSSVDDV IAINH VAIN=VDD4.5to6.0 1Analog portinput current IAINL AN0 to AN7VAIN=VSS 4.5to6.0-1µA(Note 2) Absolute precision excepts the quantizing error (±1/2 LSB).(Note 3) The conversion time means the time from executing the AD conversion instruction to setting the complete digital conversion value to the register.7. Current Dissipation Characteristics at Ta=+10°C to +40°C, VSS1=VSS2=0VRatingsParameter Symbol Pins Conditions VDD[V] min. typ. max.unitIDDOP(1) •FmCF=6MHz Ceramic resonator oscillation•FsXtal=32.768kHzcrystal oscillation •System clock : CF oscillation •Internal RC oscillation stops •1/1 divided4.5 to 6.0 14 33 IDDOP(2) •FmCF=3MHz Ceramic resonator oscillation•FsXtal=32.768kHz crystal oscillation •System clock : CF oscillation •Internal RC oscillation stops •1/2 divided4.5 to 6.0 6 18IDDOP(3) •FmCF=0Hz (The oscillation stops)•FsXtal=32.768kHz crystal oscillation •System clock : RC oscillation •1/2 divided4.5 to 6.0 4 13Current dissipation during basic operation (Note 4) IDDOP(4) •FmCF=0Hz (The oscillation stops)•FsXtal=32.768kHz crystal oscillation •System clock : 32.768kHz •Internal RC oscillation stops •1/2 divided4.5 to 6.0 3 10mAContinue.RatingsParameter Symbol Pins Conditions VDD[V] min. typ. max.unitIDDHALT(1) •HALT mode •FmCF=6MHzCeramic resonatoroscillation•FsXtal=32.768kHz crystal oscillation •System clock : CF oscillation •Internal RC oscillation stops •1/1 divided4.5 to 6.0 5 14 IDDHALT(2) •HALT mode •FmCF=3MHz Ceramic resonator oscillation•FsXtal=32.768kHz crystal oscillation •System clock : CF oscillation •Internal RC oscillation stops •1/2 divided4.5 to 6.0 2.2 7mA IDDHALT(3) •HALT mode FmCF=0Hz (The oscillation stops)•FsXtal=32.768kHz crystal oscillation •System clock : RC oscillation •1/2 divided4.5 to 6.0 400 1600Current dissipation in HALT mode (Note 4) IDDHALT(4) •HALT mode FmCF=0Hz (The oscillation stops)•FsXtal=32.768kHz crystal oscillation •System clock : crystal oscillation •Internal RC oscillation stops •1/2 divided4.5 to 6.0 25 100Current dissipation in HOLD mode (Note 4)IDDHOLD(1) HOLD mode4.5 to 6.0 0.05 30 µA(Note 4) The currents of the output transistors and the pull-up MOS transistors are ignored.Table 1. Ceramic resonator oscillation recommended constant (main-clock)Oscillation type Maker OscillatorC1C2Murataon chip6MHz ceramic resonatoroscillation KyoceraMurata on chip3MHz ceramic resonatoroscillationKyocera* Both C1 and C2 must be use K rank (±10%) and SL characteristics.Table 2. Crystal oscillation guaranteed constant (sub-clock)Oscillation type Maker OscillatorC3 C4 Rd32.768kHz crystal oscillation* Both C3 and C4 must be use J rank (±5%) and CH characteristics.(Not in need of high precision, use K rank (±10%) and SL characteristics.)(Notes) • Please place the oscillation-related parts as close to the oscillation pins as possible with the shortest possible pattern length since the circuit pattern affects the oscillation frequency.• If you use other oscillators herein, we provide no guarantee for the characteristics.Figure 1 Main-clock circuit Figure 2 Sub-clock circuit Ceramic resonator oscillation Crystal oscillationFigure 3 Oscillation stable timeFigure 4 Reset circuit(Note) Fix the value of C RES , R RES that issure to reset until 200µs, after Power supply has been over inferior limit of supply voltage.VDDFigure 5 Serial input / output test conditionFigure 6 Pulse input timing condition<AC timing point><Timing><Test load>SCK0 SCK1 SI0 SI1 SO0, SO1SB0, SB1memo:。