L-Edit画与门和或门简明教程

LEdit简明教程PPT课件

• 3.设计参数设置

• 在版图设计之前必须对有关参数进行设置。执行Setup/ Design子命令,进 入设置参数对话框,如图所示,共有6个标签页。

• (1)“Technology (工艺参数) ”标签页图 3.6 工艺参数设置标签页

• ①“Technolo gy name ”(工艺名称)栏:填写设计所用的工艺名称。当要从 一个文件拷贝一个单元到另一个文件时,L-Edit将比较两个文件所用的工艺是否 相同。如果工艺不同,L-Edit将显示警告信息。

• 选中“Select drawn objects”选项表示对象 在创建后将自动被选中,这样对该对象可立即进行 编辑操作。

2021/8/8

第18页/共194页

2021/8/8

图3.8 选择参数设置标签页

第19页/共194页

• (4)“Drawing”标签页 • 用于绘图参数的设置,设置窗口如图所示。

2021/8/8

第8页/共194页

• “Paste To Cursor”选项表示将剪贴板上的图形粘贴到鼠标指针上, 选中该选项后,在粘贴对象时,被复制的对象会跟随光标指针出现 在绘图区,并随光标一起移动,点击鼠标的任何键时,被复制的对 象固定到绘图区。在粘贴到绘图区之前,还可以对该对象进行水平 (H)、垂直(V)镜像与旋转(R)操作;“Auto-Panning”选 项用于自动平移窗口,选中该选项后,在执行Draw(绘图)、 Move(移动)或Edit(编辑)操作时,当鼠标指针碰到绘图窗口边 缘时,L-Edit将自动平移窗口。

• “Create rules on”栏用于设置标尺放置的位置。选中“Current layer”选项表示将标尺放于当前图层 上,也可通过图层选择框中的下拉列表,选取放置标尺的图层。

实例讲解与门、或门、非门电路

实例讲解与门、或门、非门电路门电路是(数字电路)中最基本的逻辑单元。

它可以使输出(信号)与输入信号之间产生一定的逻辑关系。

在数字电路中,信号大都是用电位(电平)高低两种状态表示,利用门电路的逻辑关系可以实现对信号的转换。

最基本的门电路有与门电路,或门电路,非门电路等。

与门电路与门电路是指只有在一件事情的所有条件都具备时,事情才会发生。

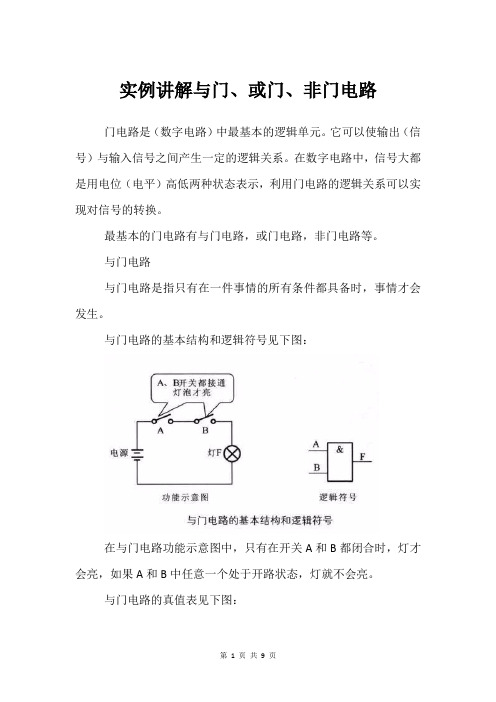

与门电路的基本结构和逻辑符号见下图:在与门电路功能示意图中,只有在开关A和B都闭合时,灯才会亮,如果A和B中任意一个处于开路状态,灯就不会亮。

与门电路的真值表见下图:一般情况下,最简单的与门电路可以用(二极管)和(电阻器)组成。

由二极管和电阻器构成的与门电路见下图:图中A,B为两个输入变量,F为输出变量,当A,B均为高电平,F为高电平,A,B只要有一个为低电平,F就为低电平。

或门电路或门电路是指只要有一个或一个以上条件满足时,事情就会发生。

或门电路的基本结构和逻辑符号见下图:上图中,只要开关A,B中有一个闭合,(电流)就能通过开关进入灯,灯点亮,只有两个开关都断开,灯才不会亮。

或门电路真值表见下图:同与门电路一样,最简单的或门电路也是由二极管和电阻器构成的。

见下图:图中A,B为两个输入变量,F为输出变量。

当A,B均为低电平,F才为低电平,A,B只要有一个为高电平,或两个都为高电平,F为高电平。

非门电路非门电路又叫“否”运算,也称求“反”运算,因此非门电路又称为反相器。

非门电路的基本结构和逻辑符号见下图:在非门电路中,当开关A闭合时,电路短路,灯F不亮;如果开关断开,灯亮。

非门电路的真值表见下图。

最基本的非门电路是利用晶体三极管的开关特性构成的。

可以实现非逻辑关系。

由晶体三极管和外围元件组成的非门电路如下:上图中,A为输入变量,Y为输出变量,利用晶体三极管的反相放大特性,当A为低电平,三极管截止,输出端Y为高电平。

当输入高电平,三极管处于饱和区,输出端Y为低电平。

利用非门电路构成的反相器主要有三种,有DTL型、TTL型和C-MOS等,如下图所示。

L-EDIT_使用技巧

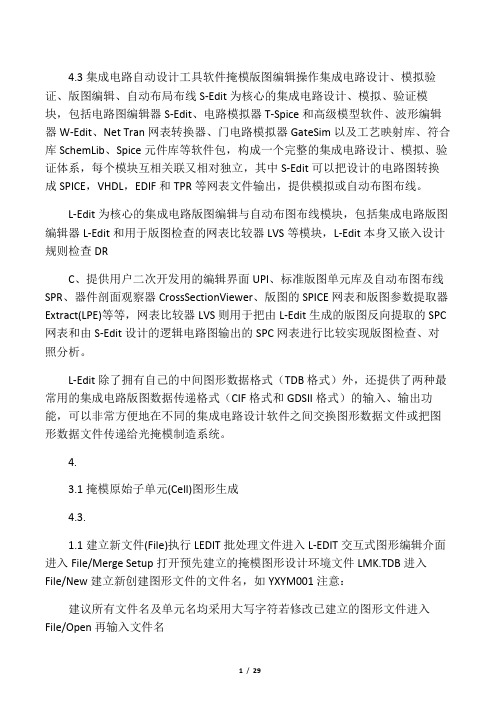

4.3集成电路自动设计工具软件掩模版图编辑操作集成电路设计、模拟验证、版图编辑、自动布局布线S-Edit为核心的集成电路设计、模拟、验证模块,包括电路图编辑器S-Edit、电路模拟器T-Spice和高级模型软件、波形编辑器W-Edit、Net Tran网表转换器、门电路模拟器GateSim以及工艺映射库、符合库SchemLib、Spice元件库等软件包,构成一个完整的集成电路设计、模拟、验证体系,每个模块互相关联又相对独立,其中S-Edit可以把设计的电路图转换成SPICE,VHDL,EDIF和TPR等网表文件输出,提供模拟或自动布图布线。

L-Edit为核心的集成电路版图编辑与自动布图布线模块,包括集成电路版图编辑器L-Edit和用于版图检查的网表比较器LVS等模块,L-Edit本身又嵌入设计规则检查DRC、提供用户二次开发用的编辑界面UPI、标准版图单元库及自动布图布线SPR、器件剖面观察器CrossSectionViewer、版图的SPICE网表和版图参数提取器Extract(LPE)等等,网表比较器LVS则用于把由L-Edit生成的版图反向提取的SPC 网表和由S-Edit设计的逻辑电路图输出的SPC网表进行比较实现版图检查、对照分析。

L-Edit除了拥有自己的中间图形数据格式(TDB格式)外,还提供了两种最常用的集成电路版图数据传递格式(CIF格式和GDSII格式)的输入、输出功能,可以非常方便地在不同的集成电路设计软件之间交换图形数据文件或把图形数据文件传递给光掩模制造系统。

4.3.1掩模原始子单元(Cell)图形生成4.3.1.1建立新文件(File)执行LEDIT批处理文件进入L-EDIT交互式图形编辑介面进入File/Merge Setup打开预先建立的掩模图形设计环境文件LMK.TDB进入File/New建立新创建图形文件的文件名,如YXYM001注意:建议所有文件名及单元名均采用大写字符若修改已建立的图形文件进入File/Open再输入文件名4.3.1.2建立新单元(Cell)进入Cell/New建立新创建图形原始单元名,如YSDY001。

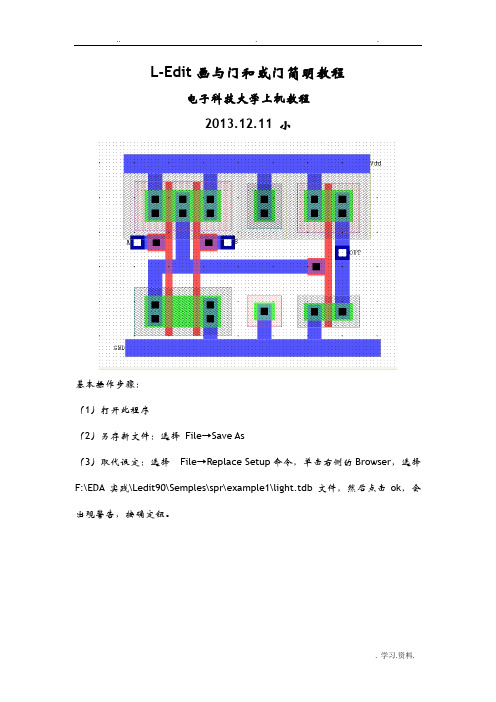

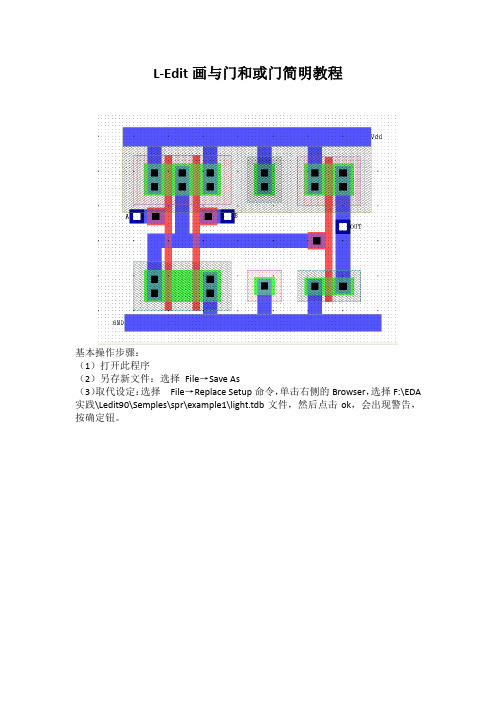

L-Edit画与门和或门简明教程

L-Edit画与门和或门简明教程电子科技大学上机教程2013.12.11 小基本操作步骤:(1)打开此程序(2)另存新文件:选择File→Save As(3)取代设定:选择File→Replace Setup命令,单击右侧的Browser,选择F:\EDA实践\Ledit90\Semples\spr\example1\light.tdb文件,然后点击ok,会出现警告,按确定钮。

(4)绘制N Well图层:横向34格,纵向19格绘制图层信息在窗口左下角显示(有图层类型,宽度,长度,坐标等)绘图完成后,通过alt+鼠标左键或者直接用鼠标滚轮来调整图层大小和位置。

Ctrl+鼠标滚轮来调整窗口大小。

home键将图层放置到整个绘图窗口中心位置。

(5)绘制Active图层:横向22格,纵向9格(6)绘制P Select图层:横向28格,纵向14格(7)绘制Poly 图层:据横向2 格,纵向14格完成后进行DRC检查,单击工具栏按钮,或者T ools→DRC,在检查完毕后会出现DRC检查结果,No DRC errors found 说明没有设计规则错误如果有错误,选中Display DRC Error Navigator 复选框,点击OK,会出现错误提示窗口,展开错误标记。

双击Error3,在版图中出现错误提示,这时可以通过alt+鼠标左键来调整图形大小位置来消除DRC错误,最后点击DRC图标,反复修改,直到错误消除,这时绘图窗口将会恢复之前的状态。

(8)绘制Active Contact 图层:横纵2格,然后DRC检查(9)绘制Metal1 图层:纵横4格,DRC检查(最好每步完成后都马上进行DRC 检查,注意,在此之后将不再提示DRC检查,但每步之后最好检查)其中重复的一些操作可以通过复制来完成,该操作通过Ground 来完成。

鼠标拖动选中要复制图形,选择Draw→Ground(或直接Ctrl+G),完成后所选中区域将会变成一个整体,可以对组件进项复制、移动操作。

LEdit绘制版图 共201页

2019/7/13

图3.41 绘制N Well

(8)截面观察:L-Edit具有截面观察

功能,可以观察该版图设计流片后的 断面情况。选择Tools/Cross-Section子 命令(或单击按钮),打开Generate Cross-Section对话框,如图3.42所示。

2019/7/13

2019/7/13

2019/7/13

图3.47 设计规则检查

执行File/Open命令打开错误记录文件 Cell0.drc,其内容如图3.48所示,有一个错误, 版图设计违反了设计规则4.6,并标出发生错 误的坐标范围。

2019/7/13

2019/7/13

图3.48 设计规则检查结果

选择执行Tools/DRC命令,打开Design Rule Check对话框,单击其中Setup按钮会出现 Setup Design Rule对话框(或单击图标), 再从其中的Rules list列表框选择4.6 Not Existing选项,可知观察该设计规则的规定, 如图3.49所示。

设定结果为1个栅格的距离等于1个坐标单位也等于1 个Micron。

2019/7/13

2019/7/13

图3.39 栅格的设定

(6)图层的设置:在Layers面板的下拉列表中选取 图层。PMOS版图需要用到N Well、Active、N Select、P select、Ploy、Matal1、Matal2、Active Contact、Via等图层。图3.40 设置设计规则对话框

2019/7/13

3.6 视图的操作

每个窗口显示一个单元版图的一部分。显示在窗口中 的版图的子集称为视图。可以用平移(Panning)当 前窗口的方法来显示版图中不同区域的视图,也可以 用缩放(Zooming)使在窗口中显示版图的较大或较 小区域的视图。在版图绘制中,移动和编辑的任何 阶 段都可以做平移和缩放操作。

L-Edit画与门和或门简明教程

L-Edit画与门和或门简明教程基本操作步骤:(1)打开此程序(2)另存新文件:选择File→Save As(3)取代设定:选择File→Replace Setup命令,单击右侧的Browser,选择F:\EDA 实践\Ledit90\Semples\spr\example1\light.tdb文件,然后点击ok,会出现警告,按确定钮。

(4)绘制N Well图层:横向34格,纵向19格绘制图层信息在窗口左下角显示(有图层类型,宽度,长度,坐标等)绘图完成后,通过alt+鼠标左键或者直接用鼠标滚轮来调整图层大小和位置。

Ctrl+鼠标滚轮来调整窗口大小。

home键将图层放置到整个绘图窗口中心位置。

(5)绘制Active图层:横向22格,纵向9格(6)绘制P Select图层:横向28格,纵向14格(7)绘制Poly 图层:据横向2 格,纵向14格完成后进行DRC检查,单击工具栏按钮,或者Tools→DRC,在检查完毕后会出现DRC检查结果,No DRC errors found 说明没有设计规则错误如果有错误,选中Display DRC Error Navigator 复选框,点击OK,会出现错误提示窗口,展开错误标记。

双击Error3,在版图中出现错误提示,这时可以通过alt+鼠标左键来调整图形大小位置来消除DRC错误,最后点击DRC图标,反复修改,直到错误消除,这时绘图窗口将会恢复之前的状态。

(8)绘制Active Contact 图层:横纵2格,然后DRC检查(9)绘制Metal1 图层:纵横4格,DRC检查(最好每步完成后都马上进行DRC 检查,注意,在此之后将不再提示DRC检查,但每步之后最好检查)其中重复的一些操作可以通过复制来完成,该操作通过Ground 来完成。

鼠标拖动选中要复制图形,选择Draw→Ground(或直接Ctrl+G),完成后所选中区域将会变成一个整体,可以对组件进项复制、移动操作。

《LEdit绘制版》课件

这个PPT课件将会向大家介绍LEdit绘制版的各种功能和用途,包括基础和高级 教程、实战演练以及未来发展方向。让我们开始吧!

什么是LEdit绘制版

制图软件

LEdit绘图软件是一款流程图绘制工具,是制作 流程图、UML图、组织结构图和ER图的利器。

高效省事

LEdit绘制版可帮助用户快速制作各种流程图, 提高效率,用于项目管理非常实用。

表和关系。

制作项目流程图

用LEdit绘制版

优缺点

• 优点:LEdit绘制版具备直观、高效、免费等 特点,可以帮助用户轻松地制作各种流程图

• 形缺。点:在一些高端的图形设计领域,它的功 能还相对较弱。

未来发展方向

• 增强软件的多功能性,加强与其它软件的数 据交互性和扩展性;

组织结构图

LEdit绘制版还适用于组织结构图的制作,用于企业 的各种机构和职务的描绘。

ER图

LEdit绘制版最常用于数据库ER图的制作,是开发数 据库的关键步骤。

LEdit绘制版基础教程

1

安装和启动

下载并安装LEdit绘制版软件,双击图标启动应用程序,并熟悉软件界面和功能。

2

界面介绍

了解LEdit绘制版的各个元素和控件,包括菜单、工具栏、画布和属性面板等。

易于使用

LEdit绘图软件具有友好的界面和易于操作的功 能,即使没有图形绘制经验也能很好地使用它。

完全免费

LEdit绘制版是一个完全免费的软件,不用在学 习和应用时花费大量资金。

LEdit绘制版的应用场景

流程图

LEdit绘制版被广泛应用于各种类型的流程图的制作, 如项目管理、业务流程等。

UML图

LEdit绘制版也是一款UML图制作利器,可用于面向 对象的软件开发。

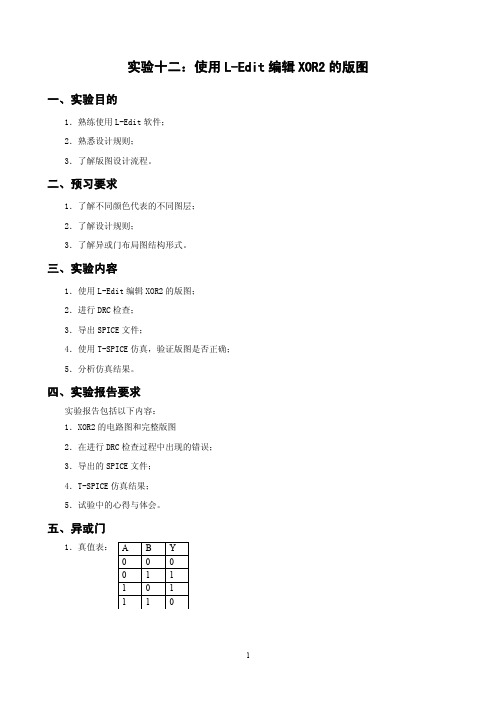

实验十二:使用L-Edit编辑XOR2的版图

四、实验报告要求

实验报告包括以下内容: 1.XOR2 的电路图和完整版图 2.在进行 DRC 检查过程中出现的错误; 3.导出的 SPICE 文件; 4.T-SPICE 仿真结果; 5.试验中的心得与体会。

五、异或门

1.真值表: A 0 0 1 1 B 0 1 0 1 Y 0 1 1 0

1

2.逻辑表达式: y A B A B 二输入异或门电路的构成可有以下几种方式: (1) y a b a b 两个两输入与非门(2*4 个 MOS 管) 一个两输入或非门(4 个 MOS 管) 五个倒相器(5*2 个 MOS 管) 共需 22 个 MOS 管(11NMOS 管,11PMOS 管) (2) y a b a b 三个两输入与非门(3*4 个 MOS 管) 二个倒相器(2*2 个 MOS 管) 共需 16 个 MOS 管(8 个 NMOS 管,8 个 PMOS 管) (3) y a b a b 利用 CMOS 传输门和倒相器来设计电路 一个 CMOS 传输门(2 个 MOS 管) 二个倒相器(2*2 个 MOS 管) 共需 6 个 MOS 管(3 个 NMOS 管,3 个 PMOS 管) 3.电路图:

5.重新命名:将 Cell0 的名称重新命名,可选择 Cell——Rename 命令,打开 Rename Cell Cell0 对话框, 将 cell0 名称改成 XOR2。 6.复制组件:选择 Cell——Copy 命令,打开 Select Cell to Copy 对话框,单击其中的 Browser 按钮,在出 现的对话框中选择第八次实验(反相器版图设计)所做的 inv.tdb,再在 Select Cell to Copy 对话框中选择 Basecontactn 组件,如图所示,单击 OK 按钮,则可将 Basecontactn 组件复制至 ex11.tdb 文件中。之后再 以同样的方式将 Basecontactp、input、nmos、pmos、out 组件复制到 ex11.tdb 文件中。

Ledit使用技巧(陈老师)

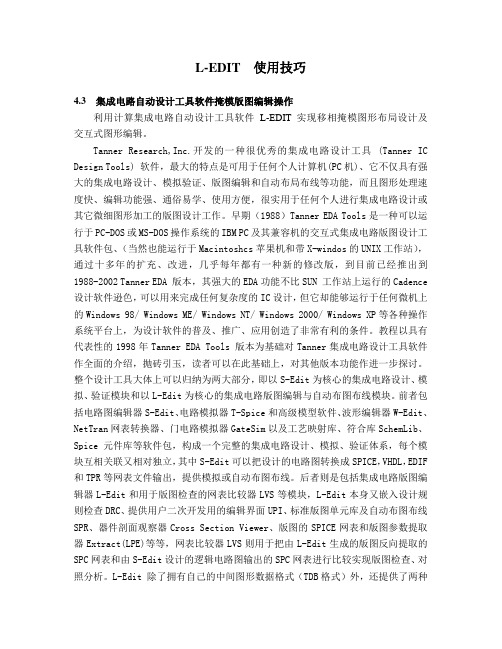

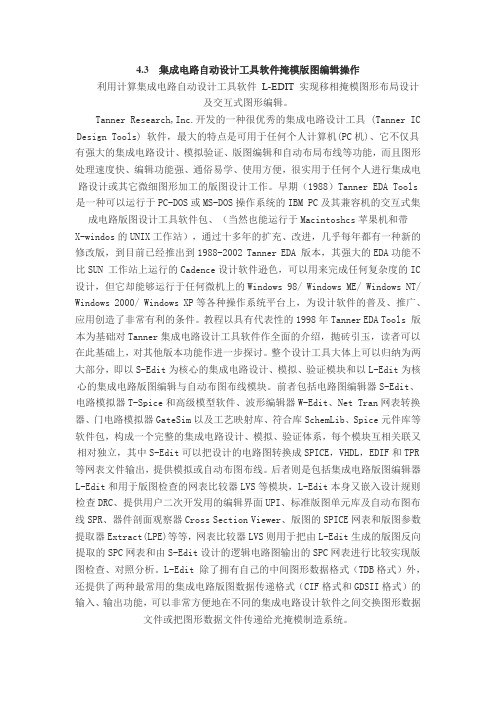

L-EDIT 使用技巧4.3 集成电路自动设计工具软件掩模版图编辑操作利用计算集成电路自动设计工具软件L-EDIT 实现移相掩模图形布局设计及交互式图形编辑。

Tanner Research,Inc.开发的一种很优秀的集成电路设计工具 (Tanner IC Design Tools) 软件,最大的特点是可用于任何个人计算机(PC机)、它不仅具有强大的集成电路设计、模拟验证、版图编辑和自动布局布线等功能,而且图形处理速度快、编辑功能强、通俗易学、使用方便,很实用于任何个人进行集成电路设计或其它微细图形加工的版图设计工作。

早期(1988)Tanner EDA Tools是一种可以运行于PC-DOS或MS-DOS操作系统的IBM PC及其兼容机的交互式集成电路版图设计工具软件包、(当然也能运行于Macintoshcs苹果机和带X-windos的UNIX工作站),通过十多年的扩充、改进,几乎每年都有一种新的修改版,到目前已经推出到1988-2002 Tanner EDA 版本,其强大的EDA功能不比SUN 工作站上运行的Cadence 设计软件逊色,可以用来完成任何复杂度的IC设计,但它却能够运行于任何微机上的Windows 98/ Windows ME/ Windows NT/ Windows 2000/ Windows XP等各种操作系统平台上,为设计软件的普及、推广、应用创造了非常有利的条件。

教程以具有代表性的1998年Tanner EDA Tools 版本为基础对Tanner集成电路设计工具软件作全面的介绍,抛砖引玉,读者可以在此基础上,对其他版本功能作进一步探讨。

整个设计工具大体上可以归纳为两大部分,即以S-Edit为核心的集成电路设计、模拟、验证模块和以L-Edit为核心的集成电路版图编辑与自动布图布线模块。

前者包括电路图编辑器S-Edit、电路模拟器T-Spice和高级模型软件、波形编辑器W-Edit、NetTran网表转换器、门电路模拟器GateSim以及工艺映射库、符合库SchemLib、Spice元件库等软件包,构成一个完整的集成电路设计、模拟、验证体系,每个模块互相关联又相对独立,其中S-Edit可以把设计的电路图转换成SPICE,VHDL,EDIF 和TPR等网表文件输出,提供模拟或自动布图布线。

L-EDIT_使用技巧

4.3 集成电路自动设计工具软件掩模版图编辑操作利用计算集成电路自动设计工具软件L-EDIT 实现移相掩模图形布局设计及交互式图形编辑。

Tanner Research,Inc.开发的一种很优秀的集成电路设计工具 (Tanner IC Design Tools) 软件,最大的特点是可用于任何个人计算机(PC机)、它不仅具有强大的集成电路设计、模拟验证、版图编辑和自动布局布线等功能,而且图形处理速度快、编辑功能强、通俗易学、使用方便,很实用于任何个人进行集成电路设计或其它微细图形加工的版图设计工作。

早期(1988)Tanner EDA Tools 是一种可以运行于PC-DOS或MS-DOS操作系统的IBM PC及其兼容机的交互式集成电路版图设计工具软件包、(当然也能运行于Macintoshcs苹果机和带X-windos的UNIX工作站),通过十多年的扩充、改进,几乎每年都有一种新的修改版,到目前已经推出到1988-2002 Tanner EDA 版本,其强大的EDA功能不比SUN 工作站上运行的Cadence设计软件逊色,可以用来完成任何复杂度的IC 设计,但它却能够运行于任何微机上的Windows 98/ Windows ME/ Windows NT/ Windows 2000/ Windows XP等各种操作系统平台上,为设计软件的普及、推广、应用创造了非常有利的条件。

教程以具有代表性的1998年Tanner EDA Tools 版本为基础对Tanner集成电路设计工具软件作全面的介绍,抛砖引玉,读者可以在此基础上,对其他版本功能作进一步探讨。

整个设计工具大体上可以归纳为两大部分,即以S-Edit为核心的集成电路设计、模拟、验证模块和以L-Edit为核心的集成电路版图编辑与自动布图布线模块。

前者包括电路图编辑器S-Edit、电路模拟器T-Spice和高级模型软件、波形编辑器W-Edit、Net Tran网表转换器、门电路模拟器GateSim以及工艺映射库、符合库SchemLib、Spice元件库等软件包,构成一个完整的集成电路设计、模拟、验证体系,每个模块互相关联又相对独立,其中S-Edit可以把设计的电路图转换成SPICE,VHDL,EDIF和TPR 等网表文件输出,提供模拟或自动布图布线。

LEdit简明教程 ppt课件

“Paste To Cursor”选项表示将剪贴板上的图形粘贴 到鼠标指针上,选中该选项后,在粘贴对象时,被复 制的对象会跟随光标指针出现在绘图区,并随光标一 起移动,点击鼠标的任何键时,被复制的对象固定到 绘图区。在粘贴到绘图区之前,还可以对该对象进行 水平(H)、垂直(V)镜像与旋转(R)操作; “Auto-Panning”选项用于自动平移窗口,选中该选 项后,在执行Draw(绘图)、Move(移动)或Edit (编辑)操作时,当鼠标指针碰到绘图窗口边缘时, L-Edit将自动平移窗口。

2020/7/28

2020/7/28

图3.6 工艺参数设置标签页

②“Technology units”栏:用于设置工艺单位,共有6种: Microns(微米)、Mils(密耳)、Millimeters(毫米)、 Centimeters(厘米)、Inches(英吋)和Other(自定义单位)。 如选用Other选项,还需在其右边的填充框内输入自定义工艺单位 的名称(通常是Lambda)。

2020/7/28

10.1 L-Edit的窗口介绍

图3.1为L-Edit的窗口,包括标题栏、工具栏、 位置显示区、鼠标功能说明、状态栏、绘图区 等项目。还有层的定义区,用以定义现在要进 行绘制和编辑的层。

2020/7/28

工具栏 位置显示区

层定义区

标题栏

鼠标功能说 明

状态栏

2020/7/28

图3.1 L-Edit窗

2020/7/28

2020/7/28

图3.4 调色板

2.应用参数设置 执行Setup /ABiblioteka plication子命令进入应用设置对

话框,如图3.5所示,包括热键和鼠标作用的 某些设定。 (1)配置文件设置栏 “Workgroup”填充框用来指定设计组应用配 置文件的路径和名称。“User”填充框用来指 定设计者应用配置文件的路径和名称。

ledit简介

序言L-Edit是Tanner Tools 的全定制版图编辑工具,它的最大特点是速度快,功能强,使用方便和分层设计。

它的屏幕刷新、放大和缩小功能及文件存取速度比其他版图编辑器件快很多;L-edit对掩膜版层数、分层数和单元数的处理没有限制,基本图形有矩形、多边形、园、线和标注等,并可处理900,450和任意角;输入输出有TDB、CIF和GDSⅡ三种格式;可在绘图机和普通打印机上实现输出硬拷贝;在设计版图时一旦发现有错,可以通过“undo”命令回到以前任意一个编辑状态。

版图(逻辑、电路)设计,采用正向设计,通过对逻辑的仿真,优化达到功能要求或自动布局布线,完成最终的版图设计工作,429总线普遍应用于航空领域,以429总线协议为基础开发专用集成电路,具有广泛的应用前景。

IC47101型坐标变换预处理器电路是429总线协议和专用集成电路相结合的较好范例。

L-Edit版图编辑软件的使用和429总线的布局布线一、L-Edit版图编辑软件的使用1.几个术语在使用L-Edit时应先搞清楚几个术语:文件、单元、掩膜层和层次。

一个文件(后缀为.TDB)就是一个设计或版图库,它可以驻留在磁盘中,也可以在编辑时装入内存。

用户可以在内存中装入任意多个文件,一个文件可以由任意多个单元组成,不仅同一个文件中的单元可以互相拷贝,而且不同文件中的单元也可以互相拷贝。

在一个典型设计中,这些单元可以有一定的层次关系,也可以相互独立(如库文件)。

单元又可以由任意数量的掩膜层组成。

2.基本操作(1)鼠标使用:在L-Edit中鼠标的地位很重要,它不仅是编辑图形的必要条件,而且对L-Edit的基本控制也是通过它完成的。

依据鼠标的指(pointing)、点、按(clicking)、拖动(dragging)和双点(double-clicking)等操作就可以建立、移动和选择目标,以及从L-Edit的下拉菜单中选择命令。

L-Edit希望使用三键鼠标,如使用了两键鼠标,则中键的功能由按下ALT建的同时按下左键来实现。

L-EDIT_使用技巧

4.3 集成电路自动设计工具软件掩模版图编辑操作集成电路设计、模拟验证、版图编辑、自动布局布线S-Edit为核心的集成电路设计、模拟、验证模块,包括电路图编辑器S-Edit、电路模拟器T-Spice和高级模型软件、波形编辑器W-Edit、Net Tran网表转换器、门电路模拟器GateSim以及工艺映射库、符合库SchemLib、Spice元件库等软件包,构成一个完整的集成电路设计、模拟、验证体系,每个模块互相关联又相对独立,其中S-Edit可以把设计的电路图转换成SPICE,VHDL,EDIF和TPR 等网表文件输出,提供模拟或自动布图布线。

L-Edit为核心的集成电路版图编辑与自动布图布线模块,包括集成电路版图编辑器L-Edit和用于版图检查的网表比较器LVS等模块,L-Edit本身又嵌入设计规则检查DRC、提供用户二次开发用的编辑界面UPI、标准版图单元库及自动布图布线SPR、器件剖面观察器Cross Section Viewer、版图的SPICE网表和版图参数提取器Extract(LPE)等等,网表比较器LVS则用于把由L-Edit生成的版图反向提取的SPC网表和由S-Edit设计的逻辑电路图输出的SPC网表进行比较实现版图检查、对照分析。

L-Edit 除了拥有自己的中间图形数据格式(TDB 格式)外,还提供了两种最常用的集成电路版图数据传递格式(CIF格式和GDSII 格式)的输入、输出功能,可以非常方便地在不同的集成电路设计软件之间交换图形数据文件或把图形数据文件传递给光掩模制造系统。

4.3.1 掩模原始子单元(Cell)图形生成4.3.1.1 建立新文件(File)执行 LEDIT批处理文件进入L-EDIT交互式图形编辑介面进入 File/Merge Setup 打开预先建立的掩模图形设计环境文件LMK.TDB 进入 File/New 建立新创建图形文件的文件名,如YXYM001注意: 建议所有文件名及单元名均采用大写字符若修改已建立的图形文件进入 File/Open 再输入文件名4.3.1.2 建立新单元(Cell)进入 Cell/New 建立新创建图形原始单元名,如YSDY001 。

ledit阵列布尔运算

ledit阵列布尔运算

Ledit阵列可以执行布尔运算,其中包括以下操作:

1.与运算(AND):如果两个输入位都是1,则输出为1,否则为0。

2.或运算(OR):只要有一个输入位是1,则输出为1,否则为0。

3.非运算(NOT):将输入位值取反,即将1变为0,0变为1。

4.异或运算(XOR):只有当两个输入位值不同时,输出位才为1,

否则为0。

5.与非运算(NAND):与运算的结果取反,即如果两个输入位都是1,则输出为0,否则为1。

6.或非运算(NOR):或运算的结果取反,即只要有一个输入位是1,则输出为0,否则为1。

7.异或非运算(XNOR):异或运算的结果取反,即如果两个输入位值

相等,则输出为1,否则为0。

在Ledit阵列中,这些运算可以通过选择合适的逻辑门来实现。

例如:- 与运算可以通过使用and门来实现。

- 或运算可以通过使用or门来实现。

- 非运算可以通过使用not门来实现。

- 异或运算可以通过使用xor门来实现。

- 与非运算可以通过使用nand门来实现。

- 或非运算可以通过使用nor门来实现。

- 异或非运算可以通过组合使用xor门和not门来实现。

在实际设计中,需要根据具体的需求选择适合的运算方式,并将它们组合成一个完整的电路,以实现所需的逻辑功能。

第九章 l-edit

When you release the DRAW mouse button, the Edit Object(s)—Ports dialog appears and prompts for the Port name. At this point you can also modify other attributes of the port, including GDSII data type, text size, coordinates, text orientation, and text alignment. If you don’t specify a placement configuration, the text is automatically placed horizontally on the screen at the lower center of the port.

Drawing Tools

绘图工具条

Display Modes You can display the Drawing toolbar in three modes: orthogonal, 45 degrees, and all angle. There are two ways to change the display mode: Place the pointer in the Drawing toolbar and click the MENU (right) mouse button. Select Orthogonal, 45 Degrees, or All Angle in the pop-up menu. Use Setup > Application and select the General tab. In the Drawing mode drop-down list choose Orthogonal, 45 Degrees, or All Angle.

L-Edit简明教程

L-Edit简明教程L-EDIT简明教程利用计算集成电路自动设计工具软件 L-EDIT 实现移相掩模图形布局设计及交互式图形编辑。

Tanner Research,Inc.开发的一种很优秀的集成电路设计工具(Tanner IC Design Tools) 软件,最大的特点是可用于任何个人计算机(PC机)、它不仅具有强大的集成电路设计、模拟验证、版图编辑和自动布局布线等功能,而且图形处理速度快、编辑功能强、通俗易学、使用方便,很实用于任何个人进行集成电路设计或其它微细图形加工的版图设计工作。

早期(1988)Tanner EDA Tools 是一种可以运行于PC-DOS或MS-DOS操作系统的IBM PC及其兼容机的交互式集成电路版图设计工具软件包、(当然也能运行于Macintoshcs苹果机和带X-windos的UNIX工作站),通过十多年的扩充、改进,几乎每年都有一种新的修改版,到目前已经推出到1988-2002 Tanner EDA 版本,其强大的EDA功能不比SUN 工作站上运行的Cadence设计软件逊色,可以用来完成任何复杂度的IC设计,但它却能够运行于任何微机上的Windows 98/ Windows ME/ Windows NT/ Windows 2000/ Windows XP等各种操作系统平台上,为设计软件的普及、推广、应用创造了非常有利的条件。

教程以具有代表性的1998年Tanner EDA T ools 版本为基础对Tanner集成电路设计工具软件作全面的介绍,抛砖引玉,读者可以在此基础上,对其他版本功能作进一步探讨。

整个设计工具大体上可以归纳为两大部分,即以S-Edit为核心的集成电路设计、模拟、验证模块和以L-Edit为核心的集成电路版图编辑与自动布图布线模块。

前者包括电路图编辑器S-Edit、电路模拟器T-Spice和高级模型软件、波形编辑器W-Edit、NetTran网表转换器、门电路模拟器GateSim以及工艺映射库、符合库SchemLib、Spice元件库等软件包,构成一个完整的集成电路设计、模拟、验证体系,每个模块互相关联又相对独立,其中S-Edit可以把设计的电路图转换成SPICE,VHDL,EDIF和TPR等网表文件输出,提供模拟或自动布图布线。

L-EDIT_使用技巧

4.3集成电路自动设计工具软件掩模版图编辑操作集成电路设计、模拟验证、版图编辑、自动布局布线S-Edit为核心的集成电路设计、模拟、验证模块,包括电路图编辑器S-Edit、电路模拟器T-Spice和高级模型软件、波形编辑器W-Edit、Net Tran网表转换器、门电路模拟器GateSim以及工艺映射库、符合库SchemLib、Spice元件库等软件包,构成一个完整的集成电路设计、模拟、验证体系,每个模块互相关联又相对独立,其中S-Edit可以把设计的电路图转换成SPICE,VHDL,EDIF和TPR等网表文件输出,提供模拟或自动布图布线。

L-Edit为核心的集成电路版图编辑与自动布图布线模块,包括集成电路版图编辑器L-Edit和用于版图检查的网表比较器LVS等模块,L-Edit本身又嵌入设计规则检查DRC、提供用户二次开发用的编辑界面UPI、标准版图单元库及自动布图布线SPR、器件剖面观察器CrossSectionViewer、版图的SPICE网表和版图参数提取器Extract(LPE)等等,网表比较器LVS则用于把由L-Edit生成的版图反向提取的SPC 网表和由S-Edit设计的逻辑电路图输出的SPC网表进行比较实现版图检查、对照分析。

L-Edit除了拥有自己的中间图形数据格式(TDB格式)外,还提供了两种最常用的集成电路版图数据传递格式(CIF格式和GDSII格式)的输入、输出功能,可以非常方便地在不同的集成电路设计软件之间交换图形数据文件或把图形数据文件传递给光掩模制造系统。

4.3.1掩模原始子单元(Cell)图形生成4.3.1.1建立新文件(File)执行LEDIT批处理文件进入L-EDIT交互式图形编辑介面进入File/Merge Setup打开预先建立的掩模图形设计环境文件LMK.TDB进入File/New建立新创建图形文件的文件名,如YXYM001注意:建议所有文件名及单元名均采用大写字符若修改已建立的图形文件进入File/Open再输入文件名4.3.1.2建立新单元(Cell)进入Cell/New建立新创建图形原始单元名,如YSDY001。

LEDIT使用技巧

4.3 集成电路自动设计工具软件掩模疆域编写操作集成电路设计、模拟验证、疆域编写、自动布局布线S-Edit为核心的集成电路设计、模拟、考证模块,包含电路图编写器S-Edit、电路模拟器 T-Spice和高级模型软件、波形编写器 W-Edit、Net Tran 网表变换器、门电路模拟器GateSim以及工艺映照库、切合库 SchemLib、Spice元件库等软件包,构成一个完好的集成电路设计、模拟、考证系统,每个模块互有关系又相对独立,此中 S-Edit能够把设计的电路图变换成SPICE,VHDL,EDIF和 TPR等网表文件输出,供给模拟或自动布图布线。

L-Edit 为核心的集成电路疆域编写与自动布图布线模块,包含集成电路疆域编写器 L-Edit 和用于疆域检查的网表比较器LVS等模块, L-Edit 自己又嵌入设计规则检查 DRC、供给用户二次开发用的编写界面UPI、标准疆域单元库及自动布图布线SPR、器件剖面察看器 CrossSectionViewer、疆域的 SPICE网表和疆域参数提取器Extract(LPE)等等,网表比较器 LVS则用于把由 L-Edit 生成的疆域反向提取的 SPC网表和由 S-Edit设计的逻辑电路图输出的 SPC网表进行比较实现疆域检查、对照剖析。

L-Edit 除了拥有自己的中间图形数据格式( TDB格式)外,还供给了两种最常用的集成电路疆域数据传达格式(CIF格式和GDSII格式)的输入、输出功能,能够特别方便地在不一样的集成电路设计软件之间互换图形数据文件或把图形数据文件传达给光掩模制造系统。

4.3.1 掩模原始子单元 (Cell)图形生成4.3.1.1 成立新文件 (File)履行 LEDIT批办理文件进入 L-EDIT交互式图形编写介面进入 File/Merge Setup 翻开早先成立的掩模图形设计环境文件 LMK.TDB进入File/New 成立新创立图形文件的文件名,如YXYM001注意:建议所有文件名及单元名均采纳大写字符若改正已成立的图形文件进入File/Open 再输入文件名4.3.1.2 成立新单元 (Cell)进入 Cell/New 成立新创立图形原始单元名,如YSDY001。

三输入与或门设计

《集成电路版图设计》实验(一):三输入与或门设计一.设计目的1、掌握使用Ledit软件绘制基本的元器件单元版图。

2、掌握数字电路基本单元CMOS版图的绘制方法,并利用CMOS版图设计简单的门电路,然后对其进行基本的DRC检查。

3、学习标准逻辑单元的版图绘制。

二.设计原理(一)设计步骤:1、设计参数设置:包括工艺参数设置(理解 Technology Unit 和Technology Setup的关系)、栅格设置(理解显示栅格、鼠标栅格和定位栅格)、选择参数设置等2、布局布线:安排各个晶体管、基本单元、复杂单元在芯片上的位置,并且设计走线,实现管间、门间、单元间的互连。

4、尺寸确定:确定晶体管尺寸(W、L)、互连尺寸(连线宽度)以及晶体管与互连之间的相对尺寸等(此次实验可以忽略)。

5、版图编辑(Layout Editor ):规定各个工艺层上图形的形状、尺寸和位置。

6、布局布线(Place and route ):给出版图的整体规划和各图形间的连接。

7、版图检查(Layout Check ):设计规则检验(DRC,Design RuleCheck),能够找到DRC规则在版图的应用点。

(二)设计目标:1、满足电路功能、性能指标、质量要求。

2、尽可能达到面积的最小化,以提高集成度,降低成本。

3、尽可能缩短连线,以减少复杂度,缩短延时、改善可靠性。

三.设计内容用CMOS工艺设计一个三输入与或门F=A+B﹡C,进行基本的DRC 检查。

四.评价标准本次的实验作业旨在让同学通过亲身实践,对所学的CMOS集成电路设计有一个更系统更全面的了解,并且通过软件的使用,达到将来参与电路设计工作的的入门练习作用。

五.部分设计规则描述设计规则是设计人员与工艺人员之间的接口与“协议”,版图设计必须无条件的服从的准则,可以极大地避免由于短路、断路造成的电路失效和容差以及寄生效应引起的性能劣化。

设计规则主要包括几何规则、电学规则以及走线规则。

LEdit实验指导书[1]

![LEdit实验指导书[1]](https://img.taocdn.com/s3/m/87ca53c51ed9ad51f11df2a5.png)

MEMS原理实验(L-Edit)指导书电子信息科学与技术前言近年来,集成电路设计的发展非常迅速,许多设计必须借助于计算机辅助设计软件来完成,而大部分软件是在工作站上执行的,虽然其功能强大,但是价格昂贵,不利于初学者学习使用。

目前,在个人电脑上开发的Tanner Pro工具为用户提供了完整电路设计的环境,为初学者进入VLSI设计领域提供了帮助。

Tanner集成电路设计软件是由Tanner Research 公司开发的基于Windows 平台的用于集成电路设计的工具软件。

该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。

其中的L-Edit版图编辑器在国内应用广泛,具有很高知名度,它不仅可以用于传统的集成电路设计,还可以用于MEMS版图设计,具有强大的集成电路设计、模拟验证、版图编辑和自动布局布线等功能,图形处理速度快、编辑功能强、通俗易学、使用方便,很适用于个人进行集成电路设计或其它微细图形加工的版图设计工作。

将其作为《MEMS原理》课程的实验课程,旨在通过对L-edit学习,掌握版图设计的基本流程。

实验一L-Edit的使用一、实验目的1、了解TANNER Pro软件的构成及其功能;2、熟悉版图设计工具L-Edit的使用环境;3、掌握L-Edit的使用方法;二、基本原理1、版图设计的概念:版图设计是创建器件或者系统的工程制图的物理描述过程,而这一物理描述遵守有制造工艺、设计流程以及通过仿真显示为可行的性能要求所带来的一系列约束。

2、TANNER Pro简介Tanner Tools Pro是一套集成电路设计软件,包含S-Edit, T-Spice, W-Edit, L-Edit 与LVS,各软件的主要功能整理如表1所示。

Tanner Pro 的设计流程如图1所示。

将要设计的电路先以S-Edit编辑出电路图,再将该电路图输出成SPICE文件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

L-Edit画与门和或门简明教程电子科技大学上机教程2013.12.11 小基本操作步骤:(1)打开此程序(2)另存新文件:选择File→Save As(3)取代设定:选择File→Replace Setup命令,单击右侧的Browser,选择F:\EDA 实践\Ledit90\Semples\spr\example1\light.tdb文件,然后点击ok,会出现警告,按确定钮。

(4)绘制N Well图层:横向34格,纵向19格绘制图层信息在窗口左下角显示(有图层类型,宽度,长度,坐标等)绘图完成后,通过alt+鼠标左键或者直接用鼠标滚轮来调整图层大小和位置。

Ctrl+鼠标滚轮来调整窗口大小。

home键将图层放置到整个绘图窗口中心位置。

(5)绘制Active图层:横向22格,纵向9格(6)绘制P Select图层:横向28格,纵向14格(7)绘制Poly 图层:据横向2 格,纵向14格完成后进行DRC检查,单击工具栏按钮,或者Tools→DRC,在检查完毕后会出现DRC检查结果,No DRC errors found 说明没有设计规则错误如果有错误,选中Display DRC Error Navigator 复选框,点击OK,会出现错误提示窗口,展开错误标记。

双击Error3,在版图中出现错误提示,这时可以通过alt+鼠标左键来调整图形大小位置来消除DRC错误,最后点击DRC图标,反复修改,直到错误消除,这时绘图窗口将会恢复之前的状态。

(8)绘制Active Contact 图层:横纵2格,然后DRC检查(9)绘制Metal1 图层:纵横4格,DRC检查(最好每步完成后都马上进行DRC 检查,注意,在此之后将不再提示DRC检查,但每步之后最好检查)其中重复的一些操作可以通过复制来完成,该操作通过Ground 来完成。

鼠标拖动选中要复制图形,选择Draw→Ground(或直接Ctrl+G),完成后所选中区域将会变成一个整体,可以对组件进项复制、移动操作。

一个组件不能对其中的单元操作,要调整组件中单元大小位置,可通过选中图形,选择Draw→Unground (或直接Ctrl+U)解除组件来完成。

(10)重新命名:将Cell0 的名称重新命名,可选择Cell—Rename 命令,打开Rename Cell对话框,将cell 名称改成nandpmos(11)新增NMOS 组件:选择Cell→New 命令,打开Create New Cell 对话框,在其中的New cell name 文本框中输入“nandnmos”,单击OK 按钮(12)编辑与非门的NMOS 组件:依照PMOS 组件的编辑流程,建立出Active 图层、N Select 图层、Poly 图层、Active Contact 图层与Metal1 图层。

其中,Active 宽为22个格点,高为9 个格点;Poly 宽为2 个格点,高为14 个格点:N Select宽为18 个格点,高为14个格点;Active Contact 宽皆为2 个格点,高皆为2 个格点:Metal1 宽皆为4 个格点,高皆为4 个格点。

DRC检查(13)设计导览:选择view 按钮,打开Design Navigator 窗口,可以看到Exl0 文件有nandnmos与nandpmos 两个cell (或直接点工具栏中的按钮),双击便可直接进入单元。

(14)编辑非门的PMOS 组件:新建cell,命名为norpmos,建立出N well图层、Active 图层、P Select 图层、Poly 图层、Active Contact 图层与Metal1 图层。

其中,N well 宽为24个格点,高为19个格点;Active 宽为14个格点,高为9 个格点:Poly 宽为2 个格点,高为14 个格点:P Select宽为18 个格点,高为14个格点;Active Contact 宽皆为2 个格点,高皆为2 个格点:Metal1 宽皆为4 个格点,高皆为4 个格点。

DRC检查(15) 编辑非门的NMOS 组件:新建cell,命名为nornmos,建立出Active 图层、N Select 图层、Poly 图层、Active Contact 图层与Metal1 图层其中,Active 宽为14个格点,高为5 个格点;Poly 宽为2 个格点,高为9 个格点:N Select宽为18 个格点,高为9个格点;Active Contact 宽皆为2 个格点,高皆为2 个格点:Metal1 宽皆为4 个格点,高皆为4 个格点。

DRC检查(16)编辑PMOS 保护环(well tap):新建cell,命名为guardpmos,建立出N well 图层、Active 图层、N Select 图层、Active Contact 图层与Metal1 图层其中,N well宽为13个格点,高为19 个格点;Active 宽为6个格点,高为9 个格点;N Select宽为10 个格点,高为13个格点;Active Contact 宽皆为2 个格点,高皆为2 个格点:Metal1 宽皆为4 个格点,高皆为4 个格点。

DRC检查(17)编辑NMOS 保护环(well tap):新建cell,命名为guardnmos,建立出Active 图层、P Select 图层、Active Contact 图层与Metal1 图层其中,Active 宽为6个格点,高为5 个格点;P Select宽为10 个格点,高为9个格点;Active Contact 宽皆为2 个格点,高皆为2 个格点:Metal1 宽皆为4 个格点,高皆为4 个格点。

DRC检查(18)编辑与门:在此,所有的cell 都已建立完毕。

新建cell 命名为and,在and中选择Cell→Instance 命令,打开Select Cell to Instance 对话框,可以看到,在组件列表中有nandpmos,nandnmos , norpmos, nornmos ,guardpmos, guardnmos 这6 组件,选择nandpmos 组件再单击OK 按钮,在编辑画面多出一个nandpmos 组件,然后选择nandnmos 组件再单击OK 按钮,在编辑画面多出一个与nandpmos 重叠的nandnmos 组件,可利用Alt 键加鼠标拖曳的方式分开nandpmos与nandnmos,同样的方法分别添加其余组件。

(19)连接栅极Poly:将放置的组件在and中按位置放置好,然后根据逻辑关系绘制连接栅极的多晶层。

由于电路的pmos 与nmos 的栅极极是要相连的,故直接以Poly图层将pmos 与nmos 的Poly 相连接,绘制出Poly 宽两个格点,绘制后进行DRC检查。

(20)连接源漏极:电路的nmos 漏极与pmos 漏极是相连的,则以Metal1 连接即可,利用Metal1 将图中的nmos 与pmos 的右边扩散区有接触点处相连接,绘制Metal1 宽两个格点、高6 个格点。

绘制后进行DRC检查(21)绘制电源线和地线:由于电路需要有Vdd 电源与GND 电源,电源绘制是以Metal1图层表示,利用Metal1 将图中pmos 上方与nmos 下方各绘制一个宽为72 个格点、高为5 个格点的电源图样,绘制后进行DRC检查(22)加入Vdd 与GND 节点名:单击工具栏中插入节点按钮(),再到编辑窗口中用鼠标左键拖曳出一个与上方电源图样重叠的宽为72 个格点、高为5 个格点的方格后,将出现Edit Object(s)对话框,如图所示。

在On文本框中选中Metal1层,在Port name 文本框中输入节点名称“Vdd”,在Text Alignment 选项组中选择文字相对于框的位置的右边,单击“确定”按钮;同样的方法变出GND。

(23) 连接电源线与地线:根据逻辑关系,将电源线与地线和pmos,nmos,guardpmos,guardnmos 连接起来。

完成后DRC检查。

(24)连接与非门和反相器:先绘制反相器输入端口,先在编辑窗口空白处进行编辑,先绘制Poly Contact 图层2*2,再绘制Poly 图层5*5,接着绘制Metal1 图层4*4使之重叠于Poly Contact 图样上,最后将此输入端口图形群组起来,先选中组合区域部分,再选择Draw→Group 命令,会出现Group 对话框。

在Group CellName 文本框中输入名称portA,之后单击OK 按钮。

将portA移至反相器输入端,连接非门和反相器。

最后DRC检查。

(25)加入输入端口:由于与门有两个输入端口,且输入信号是从栅极(Poly)输入,输入输出信号由Metal2 传入,故一个与门输入端口需要绘制Metal2 图层、Via 图层、Metal1 层、Poly ontact 图层与Poly 图层,才能将信号从Metal2 图层传至Poly 层。

先在编辑窗口空白处进行编辑,最后再移至整个组件的位置。

先绘制Poly Contact 图层2*2,再绘制Poly 图层5*5,接着绘制Metal1 图层10*4使之重叠于Poly Contact 图样上,接着在Metal1 上要绘制Via 图层2*2,Via 图层是用来连接Metal1 图层与Metal2 图层的接触孔,接着绘制Metal2 图层4*4,它要与图层Via 与Metal1 重叠。

DRC检查。

将此输入端口图形群组起来,先选中组合区域部分,再选择Draw→Group 命令,会出现Group 对话框。

在Group CellName 文本框中输入名称portB,之后单击OK 按钮。

将port B 部分移至与非门栅极的位置当成输入端口,结果如图所示。

注意,在放置时Metal1 与Metal1 之间要距离3 个格点以上,并要以设计规则检查无误才可,复制port B 放置到另一个输入端口,通过R键来旋转portB。

最后DRC 检查。

(26)在port B 组件上加入节点名称作为输入点,需利用加入节点按钮。

单击按钮,再在Layers 面板的下拉列表中选择Metal2 选项,使Metal2 图样被选取,再到编辑窗口中用鼠标左键拖曳出一个与port B 组件的Metal2 图样重叠的宽为4 个格点、高为4 个格点的方格后,会出现Edit Object(s)对话框,在Port name 文本框输入输入端口名称“A”,在Text Alignment 选项组选择文字相对于框的位置的左边,再单击“确定”按钮;同样的方法标出B输入端口。

(27)加入输出端口:与门有一个输出端口,先绘制Via 图层,在反相器的Metal1 图层上画出横向两格、纵向两格的方形,接着绘制Metal2 图层4*4,它要与Via与Metal1 图层重叠。