FPGA作业

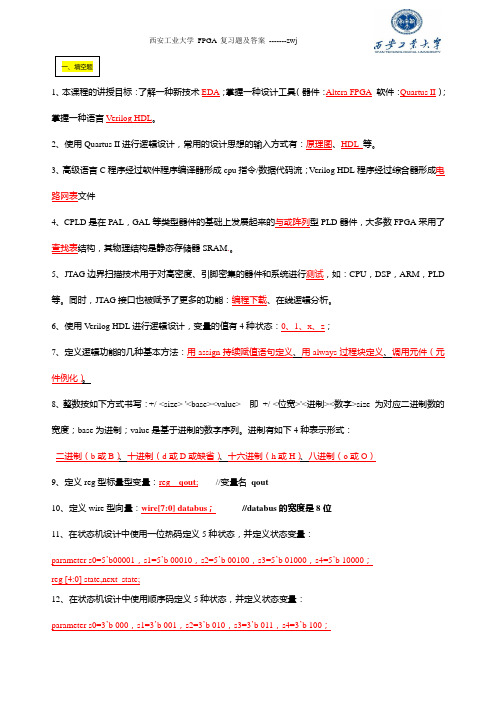

fpga练习题库

fpga练习题库FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,广泛应用于数字电路设计和嵌入式系统开发。

为了帮助读者更好地掌握FPGA的相关知识,本篇文章将提供一套FPGA练习题库,旨在帮助读者巩固理论知识,并通过实践锻炼解决问题的能力。

一、概述本练习题库涵盖了FPGA的多个方面内容,包括Verilog语言编程、数字逻辑设计、时序分析、时钟分频以及外设接口等。

通过完成这些练习题,读者可以更好地理解FPGA的工作原理,掌握FPGA设计的基本方法和技巧。

二、练习题示例1. 编写一个Verilog代码,实现一个4位二进制加法器。

输入端包括两个4位的二进制数A和B,输出端为一个5位的二进制数S(其中前4位为和,最后1位为进位)。

2. 设计一个3:8译码器,使用FPGA实现。

译码器的输入端为3位二进制数A、B和C,输出端为8位译码结果D0-D7。

3. 在FPGA中实现一个时钟分频电路,输入端为一个时钟信号clk,输出端为两个时钟信号clk_div2和clk_div4,在输出端分别将输入时钟的频率分别分为原来的一半和四分之一。

4. 设计一个I2C总线控制器,实现与外部I2C设备的通信。

输入端为数据线SDA和时钟线SCL,输出端为I2C总线的控制信号(包括起始信号、停止信号、数据读写信号等)。

三、注意事项1. 在完成练习题时,建议使用Verilog HDL语言进行编程。

可以选择任何一款FPGA开发板进行搭建和验证。

2. 在编写代码时,注意书写规范和注释,增加代码的可读性和可维护性。

3. 在验证设计时,使用仿真工具进行功能验证,并通过FPGA开发板进行硬件验证。

4. 完成练习题后,可以通过波形验证、逻辑分析仪等工具进行结果检验。

5. 如果遇到问题,可以参考相关教材、文档或搜索引擎搜索相关资料,也可以向论坛、社群等渠道提问,寻求帮助和解答。

四、总结通过完成FPGA练习题库中的各种题目,读者可以提高FPGA设计和应用的能力。

fpga期末考试复习题

fpga期末考试复习题FPGA期末考试复习题一、选择题1. FPGA的全称是什么?A. Field Programmable Gate ArrayB. Fixed Programmable Gate ArrayC. Field Programming Gate ArrayD. Fixed Programming Gate Array2. FPGA与ASIC的主要区别是什么?A. FPGA是可编程的,ASIC是固定的B. FPGA是固定的,ASIC是可编程的C. FPGA和ASIC都是可编程的D. FPGA和ASIC都是固定的3. 下列哪项不是FPGA设计中常用的硬件描述语言?A. VHDLB. VerilogC. C++D. SystemVerilog4. FPGA设计流程中,综合后的下一个步骤是什么?A. 布局与布线B. 仿真C. 测试D. 编程5. 在FPGA设计中,什么是时序约束?A. 逻辑约束B. 物理约束C. 性能约束D. 以上都不是二、简答题1. 简述FPGA设计的基本流程。

2. 解释什么是时钟域交叉,并说明在FPGA设计中如何处理时钟域交叉问题。

3. FPGA与CPLD在结构上有何不同?4. FPGA设计中,同步设计和异步设计的区别是什么?5. 什么是FPGA的资源利用率,如何优化FPGA的资源利用率?三、计算题1. 假设有一个FPGA设计,其最大工作频率为100MHz,要求设计一个时钟分频器,将时钟频率降低到50MHz。

请计算分频器的分频系数。

2. 给定一个FPGA设计,其输入信号的传播延迟为2ns,输出信号的建立时间为3ns,保持时间为1ns。

如果要求设计满足时序要求,计算输出信号的最小时钟周期。

四、论述题1. 论述FPGA在数字信号处理(DSP)领域的应用及其优势。

2. 分析FPGA在嵌入式系统设计中的作用及其与传统微处理器的比较。

五、设计题1. 设计一个简单的FPGA模块,实现4位二进制加法器的功能,并说明其工作原理。

FPGA作业

习题一1 使用`timescale 编译器指令的目的是什么?答:指定延时时间单位,及时间精度。

如` timescale 1ns /100ps表示时间单位为1ns,时间精度为0.1ns。

2 写出产生下图所示波形的变量BullsEye的初始化语句。

答:32b’0010 0000 0000 1111 1111 1100 1110 00003 使用数据流描述方式编写下图所示的异或逻辑的Verilog HDL描述,并使用规定的时延。

答:`timescale 1ns/100psmoduleyihuo(out,a,b);input a, b;output out;wireaf,bf,abf,afb,out;always @( a or b)assign #1 af=~a;assign #1 bf =~b;assign #6 abf = a&bf;assign #6 afb = af&b;assign #10 out=abf|afb;endmodule4下列表达式的位模式是什么?7'o44八进制, 'Bx0二进制, 5'bx110二进制,'hA0十六进制, 10'd2十进制, 'hzF十六进制习题二1.说明参数GATE_DELAY, 参数值为5。

答:parameter GATE_DELAY = 5;2.假定长度为64个字的存储器, 每个字8位,编写Verilog 代码,按逆序交换存储器的内容。

即将第0个字与第63个字交换,第1个字与第62个字交换,依此类推。

答:reg[7:0]Mem[63:0];inti = 0;reg[7:0]temp;always @(i< 31)begintemp = Mem[i];Mem[i] = Mem[63-i];Mem[63-i] = temp;end3. 假定32位总线Address_Bus, 编写一个表达式,计算从第11位到第2 0位的归约与非。

fpga竞赛题目

题目:设计一个FPGA竞赛题目并解释它的要求和解决方法一、题目:数字时钟的设计与实现要求:1. 使用FPGA设计一个数字时钟,包括小时、分钟和秒的显示。

2. 时钟的显示应该具有实时更新功能,即每秒钟更新一次时间。

3. 时钟应该具有手动调整时间的功能,可以通过按键输入小时、分钟和秒。

4. 时钟应该具有闹钟功能,当到达设定的时间时,闹钟会发出声音。

解决方法:1. 首先,我们需要使用FPGA设计一个时钟模块,该模块需要能够处理小时、分钟和秒的计数。

可以使用计数器来实现这一功能。

计数器的计数频率应该足够快,以实现每秒钟更新一次时间的要求。

2. 显示模块可以使用FPGA上的LED或LCD显示屏来实现。

我们需要设计一个驱动程序来控制显示屏的显示内容。

3. 手动调整时间的功能可以通过按键输入来实现。

我们需要设计一个按键检测模块来检测按键的状态,并将按键输入传递给时钟模块。

4. 闹钟功能可以通过在时钟模块中设置一个闹钟时间来实现。

当到达设定的时间时,闹钟模块会触发一个中断,通知驱动程序发出声音。

二、题目:智能家居系统的设计与实现要求:1. 设计一个基于FPGA的智能家居系统,包括灯光、窗帘、空调等设备的控制。

2. 系统应该具有远程控制功能,可以通过手机APP或网页界面进行控制。

3. 系统应该具有自动控制功能,可以根据环境条件(如温度、光照等)自动控制设备。

解决方法:1. 智能家居系统需要使用FPGA作为主控制器,协调各个设备的控制。

我们可以使用FPGA 上的GPIO接口来控制各种设备。

2. 远程控制可以通过手机APP或网页界面的方式实现。

我们可以使用Wi-Fi模块(如ESP32)来实现通信,将用户的控制指令发送给FPGA。

3. 自动控制可以根据环境条件实现。

我们可以使用传感器(如温度、光照传感器)来检测环境条件,并将检测结果传递给FPGA。

FPGA可以根据这些信息来控制各种设备。

总之,这些题目需要使用FPGA的知识和技能来解决,需要熟练掌握FPGA设计、电路设计、软件开发、通信等方面的基础知识。

fpga基础练习题

fpga基础练习题FPGA(现场可编程门阵列)是一种用于实现数字逻辑电路的集成电路技术。

它具有可编程性和灵活性,因此在许多领域都得到广泛应用。

为了帮助大家更好地理解和掌握FPGA的基础知识,以下是一些FPGA基础练习题。

练习题一:FPGA的基本概念描述FPGA的基本原理和特点,并说明FPGA与ASIC(应用特定集成电路)的区别和联系。

练习题二:FPGA的编程语言介绍FPGA常用的编程语言,如VHDL(VHSIC硬件描述语言)和Verilog HDL(硬件描述语言),并比较它们的特点和适用场景。

练习题三:FPGA开发流程以Xilinx为例,详细描述FPGA的开发流程,包括项目创建、设计实现、综合与仿真、下载到FPGA板等步骤,并提及常见的开发工具和软件。

练习题四:FPGA的时序设计解释FPGA的时序设计概念,包括时钟、时钟周期、时钟频率、时钟约束等,并说明如何进行时序约束和时序分析。

练习题五:FPGA的布局布线讨论FPGA的布局布线问题,包括寄存器布局、时钟布线、关键路径等内容,并介绍常用的布局布线工具和技术。

练习题六:FPGA的资源利用说明如何合理利用FPGA的资源,包括LUT(查找表)、片上RAM(Random Access Memory)、DSP(Digital Signal Processing)等,并给出相应的应用示例。

练习题七:FPGA应用案例选择一个具体的应用领域(如通信、图像处理等),并描述FPGA在该领域中的应用案例,包括设计思路、实现方法和性能指标等。

练习题八:FPGA的优缺点总结FPGA的优点和缺点,分析其在不同应用场景中的适用性,并展望FPGA技术的发展趋势。

通过完成以上FPGA基础练习题,相信大家能够更加深入地了解和掌握FPGA的基本概念、编程语言、开发流程、时序设计、布局布线、资源利用、应用案例以及优缺点等方面的知识。

祝愿大家在FPGA的学习和应用中取得好成果!。

FPGA原理与应用综合练习题

第一阶段测验本卷共分为1大题24小题,总分100 分。

本卷得分:100•1.变量和信号的描述正确的是()。

A.变量赋值号是:=2.在EDA中,IP的中文含义是()。

D.知识产权核3.可编程逻辑器件的英文简称是()。

D.PLD4.现场可编程门阵列的英文简称是()。

A.FPGA5.不属于顺序语句的是()。

B.LOOP语句6.VHDL中顺序语句放置位置说法正确的是()。

D.前面的说法都正确7.VHDL运算符优先级的说法正确的是()。

C.逻辑运算的优先级最低8.使用STD_LOGIG_1164使用的数据类型时()。

B.必须在库和包集合中声明9.可以不必声明而直接引用的数据类型是()。

C.BIT10.关于VHDL数据类型,正确的是()。

B.用户可以定义子类型11.关于VHDL数据类型,正确的是()。

D.运算与数据类型无关12.变量和信号的描述正确的是()。

B.信号可以带出进程13.在VHDL语言中,下列对进程(PROCESS)语句的语句结构及语法规则的描述中,不正确的是_____。

C.进程由说明部分、结构体部分、和敏感信号三部分组成;(进程由声明语句、顺序语句、敏感信号列表组成)14.VHDL语言中信号定义的位置是()。

D.结构体中特定位置15.关于1987标准的VHDL语言中,标识符描述正确的是()。

B.下划线不能连用16.描述项目具有逻辑功能的是()。

B.结构体17.一个项目的输入输出端口是定义在()。

A.实体中18.关于VHDL中的数字,请找出以下数字中最大的一个:_____。

(整型数字的表示) A.2#1111_1110#--二进制数,下划线不影响数值大小,只是增强可读性,转换成10进制数为:25419.下列标识符中,_____是不合法的标识符。

(标识符开头必须是英文字符)B.9moon20.LIBRARY___;--库的声明USEIEEE.STD_LOGIC_1164.ALL;--库的引用,引用IEEE库中的std_logic_1164中的所有项目 A.IEEE21.VHDL语言是一种结构化设计语言;一个设计实体(电路模块)包括实体与结构体两部分,结构体描述____。

FPGA试卷+答案+超详细解答

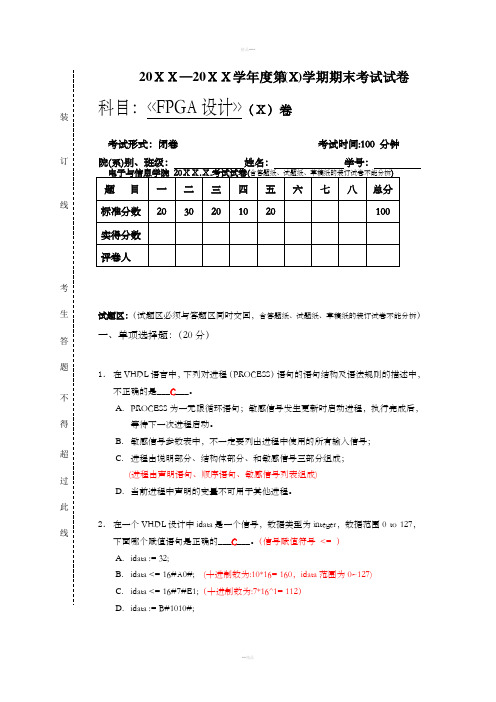

科目:<<FPGA设计>>(X)卷考试形式:闭卷考试时间:100 分钟院(系)别、班级:姓名:学号:20XX.X.考试试卷含答题纸、试题纸、草稿纸的装订试卷不能分拆)试题区:(试题区必须与答题区同时交回,含答题纸、试题纸、草稿纸的装订试卷不能分拆)一、单项选择题:(20分)1.在VHDL语言中,下列对进程(PROCESS)语句的语句结构及语法规则的描述中,不正确的是___C___。

A.PROCESS为一无限循环语句;敏感信号发生更新时启动进程,执行完成后,等待下一次进程启动。

B.敏感信号参数表中,不一定要列出进程中使用的所有输入信号;C.进程由说明部分、结构体部分、和敏感信号三部分组成;(进程由声明语句、顺序语句、敏感信号列表组成)D.当前进程中声明的变量不可用于其他进程。

2.在一个VHDL设计中idata是一个信号,数据类型为integer,数据范围0 to 127,下面哪个赋值语句是正确的___C___。

(信号赋值符号<= )A.idata := 32;B.idata <= 16#A0#; (十进制数为:10*16= 160,idata范围为0~127)C.idata <= 16#7#E1;(十进制数为:7*16^1= 112)D.idata := B#1010#;3.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是___C___。

A.FPGA是基于乘积项结构的可编程逻辑器件;(FPGA芯片基于查找表的可编程逻辑结构)B.FPGA是全称为复杂可编程逻辑器件;(FPGA 现场可编程逻辑门阵列,CPLD才是复杂可编程逻辑器件)C.基于SRAM的FPGA器件,在每次上电后必须进行一次配置;D.在Altera公司生产的器件中,MAX7000系列属FPGA结构。

(MAX7000系列属CPLD结构)4.进程中的变量赋值语句,其变量更新是___A___。

基于FPGA的设计题目

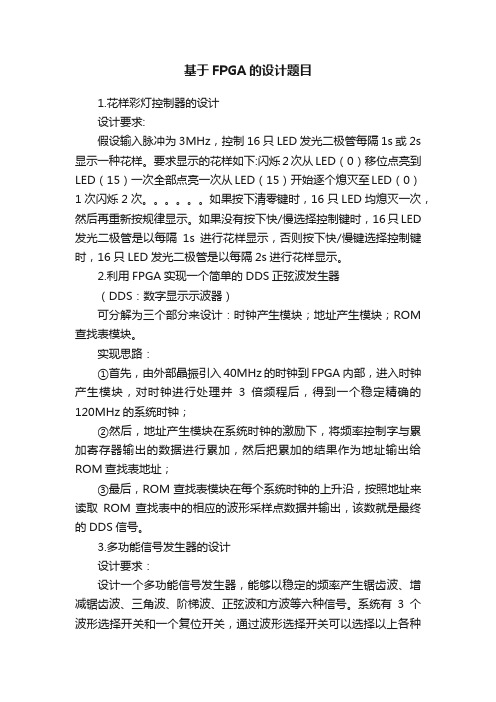

基于FPGA的设计题目1.花样彩灯控制器的设计设计要求:假设输入脉冲为3MHz,控制16只LED发光二极管每隔1s或2s 显示一种花样。

要求显示的花样如下:闪烁2次从LED(0)移位点亮到LED(15)一次全部点亮一次从LED(15)开始逐个熄灭至LED(0)1次闪烁2次。

如果按下清零键时,16只LED均熄灭一次,然后再重新按规律显示。

如果没有按下快/慢选择控制键时,16只LED 发光二极管是以每隔1s进行花样显示,否则按下快/慢键选择控制键时,16只LED发光二极管是以每隔2s进行花样显示。

2.利用FPGA实现一个简单的DDS正弦波发生器(DDS:数字显示示波器)可分解为三个部分来设计:时钟产生模块;地址产生模块;ROM 查找表模块。

实现思路:①首先,由外部晶振引入40MHz的时钟到FPGA内部,进入时钟产生模块,对时钟进行处理并3倍频程后,得到一个稳定精确的120MHz的系统时钟;②然后,地址产生模块在系统时钟的激励下,将频率控制字与累加寄存器输出的数据进行累加,然后把累加的结果作为地址输出给ROM查找表地址;③最后,ROM查找表模块在每个系统时钟的上升沿,按照地址来读取ROM 查找表中的相应的波形采样点数据并输出,该数就是最终的DDS信号。

3.多功能信号发生器的设计设计要求:设计一个多功能信号发生器,能够以稳定的频率产生锯齿波、增减锯齿波、三角波、阶梯波、正弦波和方波等六种信号。

系统有3个波形选择开关和一个复位开关,通过波形选择开关可以选择以上各种不同种类的输出波形;按下复位开关时,系统将复位。

设计实现:由于FPGA只能直接输出数字信号,而多功能信号发生器输出的各种波形均为模拟信号,因此设计信号发生器时,需将FPGA输出的信号通过D/A转换电路将数字信号转换成模拟信号。

多功能信号发生器可由信号产生电路、波形选择电路和D/A转换电路构成。

如下图所示:时钟信号波形输出信号产生电波形选择电路D/A转换电路选择信号4.数字跑表的设计设计要求:设计一个数字跑表,该跑表具有复位、暂停、秒表计时等功能。

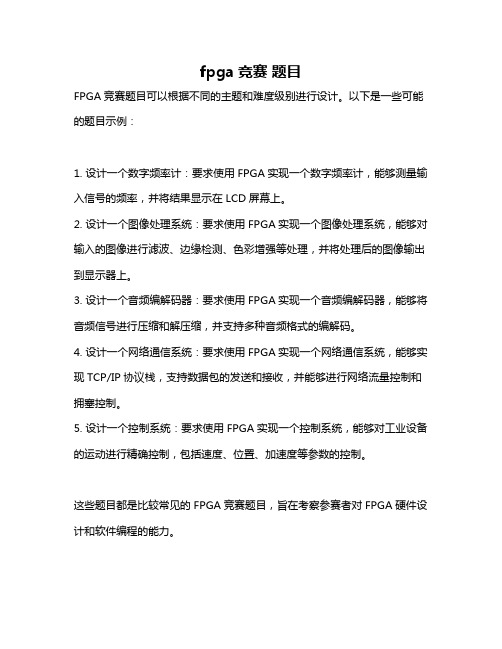

fpga竞赛 题目

fpga竞赛题目

FPGA竞赛题目可以根据不同的主题和难度级别进行设计。

以下是一些可能的题目示例:

1. 设计一个数字频率计:要求使用FPGA实现一个数字频率计,能够测量输入信号的频率,并将结果显示在LCD屏幕上。

2. 设计一个图像处理系统:要求使用FPGA实现一个图像处理系统,能够对输入的图像进行滤波、边缘检测、色彩增强等处理,并将处理后的图像输出到显示器上。

3. 设计一个音频编解码器:要求使用FPGA实现一个音频编解码器,能够将音频信号进行压缩和解压缩,并支持多种音频格式的编解码。

4. 设计一个网络通信系统:要求使用FPGA实现一个网络通信系统,能够实现TCP/IP协议栈,支持数据包的发送和接收,并能够进行网络流量控制和拥塞控制。

5. 设计一个控制系统:要求使用FPGA实现一个控制系统,能够对工业设备的运动进行精确控制,包括速度、位置、加速度等参数的控制。

这些题目都是比较常见的FPGA竞赛题目,旨在考察参赛者对FPGA硬件设计和软件编程的能力。

fpga习题答案

fpga习题答案FPGA习题答案FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,具有广泛的应用领域,包括数字信号处理、通信、图像处理等。

在学习和应用FPGA的过程中,习题是一种常见的练习方式,通过解答习题可以加深对FPGA原理和应用的理解。

本文将为大家提供一些FPGA习题的答案,希望对学习FPGA的同学有所帮助。

习题一:请简述FPGA的工作原理。

答案:FPGA是一种可编程逻辑器件,其工作原理基于可编程逻辑单元(PLU)和可编程互连资源(PIR)。

PLU是FPGA中最基本的单元,由逻辑门、触发器等构成,可以根据用户的需求编程实现不同的逻辑功能。

PIR则是用于连接PLU 的资源,包括线路、开关等。

用户可以通过编程工具将设计好的逻辑电路的描述文件加载到FPGA中,PLU和PIR将根据描述文件的指令进行配置,从而实现用户所需的逻辑功能。

习题二:请列举一些常见的FPGA编程语言。

答案:常见的FPGA编程语言包括VHDL(VHSIC Hardware Description Language)和Verilog。

这两种语言都是硬件描述语言(HDL),用于描述FPGA 中的逻辑电路。

VHDL是一种由美国国防部发起的标准化语言,具有严格的语法和规范。

Verilog则是由美国Gates公司(后来被Cadence收购)开发的语言,更加简洁灵活。

除了VHDL和Verilog,还有一些其他的FPGA编程语言,如SystemVerilog、AHDL等。

习题三:请简述FPGA的时序逻辑和组合逻辑。

答案:FPGA中的逻辑电路可以分为时序逻辑和组合逻辑。

组合逻辑是指逻辑电路的输出只与当前的输入有关,没有记忆功能。

常见的组合逻辑电路包括逻辑门电路、多路选择器等。

时序逻辑则是指逻辑电路的输出不仅与当前的输入有关,还与过去的输入和输出有关,具有记忆功能。

常见的时序逻辑电路包括触发器、计数器等。

fpga实训报告

fpga实训报告一、引言FPGA(Field-Programmable Gate Array)是一种可编程逻辑集成电路,通过在硬件设计中使用现场可编程的逻辑门阵列,实现了对硬件电路的灵活配置和重构。

FPGA广泛应用于数字信号处理、通信系统、嵌入式系统等领域。

本篇报告将介绍我在FPGA实训过程中的学习和实践成果。

二、实训目标本次FPGA实训的主要目标是通过学习和实践,掌握FPGA的基本原理和设计流程。

具体的实训内容包括FPGA的基本结构、开发环境的搭建、逻辑电路的设计与实现等。

三、FPGA基本原理1. FPGA的结构FPGA由可编程逻辑单元(CLB)、输入/输出块(IOB)、全局时钟网络(GCLK)、可编程互连网络等构成。

可编程逻辑单元是FPGA的核心,用于实现逻辑功能;输入/输出块用于与外部系统进行数据交互;全局时钟网络用于传播时钟信号;可编程互连网络用于连接逻辑单元和输入/输出块。

2. FPGA的编程语言FPGA的设计可以使用硬件描述语言(HDL)进行开发。

常用的HDL语言有VHDL和Verilog,开发者可以根据需求选择适合的语言进行设计。

四、实训步骤1. 搭建开发环境在开始实训之前,需要搭建好FPGA的开发环境。

首先,安装相应的开发软件,并配置开发板的驱动程序。

接着,将开发板与计算机连接,并确认连接成功。

2. 设计逻辑电路在FPGA实训中,我首先根据实际需求设计了一组逻辑电路。

通过使用VHDL语言,我实现了数字信号的采样和滤波功能。

为了验证设计的正确性,我使用仿真工具进行了逻辑电路的模拟。

3. 烧写程序设计完成后,我将设计好的逻辑电路通过编译器生成可烧写文件。

然后,将可烧写文件烧写到FPGA芯片中,使其能够正确运行设计好的逻辑电路。

五、实训成果通过本次FPGA实训,我深入了解了FPGA的基本原理和设计流程,掌握了VHDL语言的使用,熟悉了FPGA开发环境的搭建和操作。

最终,我成功实现了一组逻辑电路的功能,并通过烧写程序在FPGA上进行了验证。

FPGA习题集及参考答案

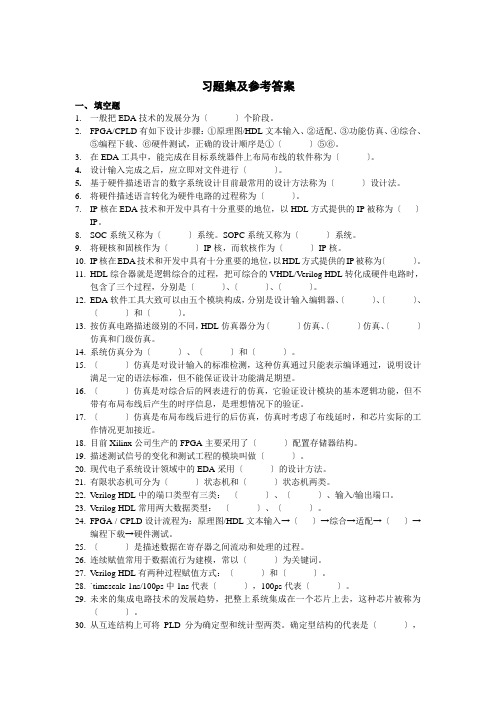

习题集及参考答案一、填空题1.一般把EDA技术的发展分为〔〕个阶段。

2.FPGA/CPLD有如下设计步骤:①原理图/HDL文本输入、②适配、③功能仿真、④综合、⑤编程下载、⑥硬件测试,正确的设计顺序是①〔〕⑤⑥。

3.在EDA工具中,能完成在目标系统器件上布局布线的软件称为〔〕。

4.设计输入完成之后,应立即对文件进行〔〕。

5.基于硬件描述语言的数字系统设计目前最常用的设计方法称为〔〕设计法。

6.将硬件描述语言转化为硬件电路的过程称为〔〕。

7.IP核在EDA技术和开发中具有十分重要的地位,以HDL方式提供的IP被称为〔〕IP。

8.SOC系统又称为〔〕系统。

SOPC系统又称为〔〕系统。

9.将硬核和固核作为〔〕IP核,而软核作为〔〕IP核。

10.IP核在EDA技术和开发中具有十分重要的地位,以HDL方式提供的IP被称为〔〕。

11.HDL综合器就是逻辑综合的过程,把可综合的VHDL/Verilog HDL转化成硬件电路时,包含了三个过程,分别是〔〕、〔〕、〔〕。

12.EDA软件工具大致可以由五个模块构成,分别是设计输入编辑器、〔〕、〔〕、〔〕和〔〕。

13.按仿真电路描述级别的不同,HDL仿真器分为〔〕仿真、〔〕仿真、〔〕仿真和门级仿真。

14.系统仿真分为〔〕、〔〕和〔〕。

15.〔〕仿真是对设计输入的标准检测,这种仿真通过只能表示编译通过,说明设计满足一定的语法标准,但不能保证设计功能满足期望。

16.〔〕仿真是对综合后的网表进行的仿真,它验证设计模块的基本逻辑功能,但不带有布局布线后产生的时序信息,是理想情况下的验证。

17.〔〕仿真是布局布线后进行的后仿真,仿真时考虑了布线延时,和芯片实际的工作情况更加接近。

18.目前Xilinx公司生产的FPGA主要采用了〔〕配置存储器结构。

19.描述测试信号的变化和测试工程的模块叫做〔〕。

20.现代电子系统设计领域中的EDA采用〔〕的设计方法。

21.有限状态机可分为〔〕状态机和〔〕状态机两类。

fpga综合试题及答案【2024版】

可编辑修改精选全文完整版fpga综合试题及答案一、单选题(每题2分,共10分)1. FPGA的全称是什么?A. Field Programmable Gate ArrayB. Field Programmable Graphic ArrayC. Field Programmable General ArrayD. Field Programmable Group Array答案:A2. 下列哪个不是FPGA的编程语言?A. VHDLB. VerilogC. C++D. SystemVerilog答案:C3. FPGA与ASIC的主要区别是什么?A. FPGA是可编程的,ASIC是不可编程的B. FPGA是不可编程的,ASIC是可编程的C. FPGA和ASIC都是可编程的D. FPGA和ASIC都是不可编程的答案:A4. FPGA设计中,通常用于描述硬件行为的是哪类语言?A. 汇编语言B. 高级编程语言C. 硬件描述语言D. 机器语言答案:C5. 下列哪个不是FPGA设计流程中的步骤?A. 编写代码B. 编译C. 布局布线D. 烧录固件答案:D二、多选题(每题3分,共15分)6. 下列哪些是FPGA的优点?A. 可编程B. 可重复使用C. 性能稳定D. 成本低廉答案:A B7. 在FPGA设计中,以下哪些因素会影响设计的性能?A. 逻辑资源的使用B. 时钟频率C. 电源电压D. 布线复杂度答案:A B D8. FPGA设计中,常见的时序问题包括哪些?A. 时钟偏差B. 时钟偏斜C. 时钟抖动D. 时钟漂移答案:A B C9. FPGA设计中,通常需要考虑哪些功耗因素?A. 静态功耗B. 动态功耗C. 热设计功耗D. 电磁干扰答案:A B C10. 下列哪些是FPGA设计中常用的仿真工具?A. ModelSimB. VivadoC. QuartusD. Xilinx ISE答案:A B C三、判断题(每题1分,共5分)11. FPGA设计中,可以使用C语言进行硬件描述。

《基于FPGA的现代数字系统设计》作业参考答案详解

作业答案

信号预处理 放大 采样/保持 AD574

ADData 8 STATUS CS CE A0

rddata 1

8

wren

adram (lpm_ram_dp)

8 rddata rdaddr 6

Control

6 ClkInc wraddr Cntclr

AnalogIn

RC K12_8

地址 计数器

CLK A/D采集系统

作业答案 3.3 设A=4´b1010,B=4´b0011,C=1'b1, 则下式运算结果是什么? (1) ~A 0101 (2) A>>1 0101 (3) {A,B[0],C} 101011 (4) A & B 0010 (5) A ^B 1001 (6) A<B 0

作业答案 3.5 有一个模块名为my_module,其输入/输出 端口情况如题图3.1所示,试写出模块Verilog HDL的描述框架,即模块的定义、端口罗列和端 口定义等。 module my_modudle( AIN, BIN, CIN, CLK, ENABLE, RESET DATA_OUT) Input[3:0] AIN; Input[2:0] BIN; Input[1:0] CIN; Input CLK, ENABLE, RESET; Output[4:0] DATA_OUT; …….

作业答案

3.10 定义一个任务,该任务能计算出一个八位变 量的偶校验位作为该任务的输出,计算结束后,经 过三个时钟周期将该校验位赋给任务的输出。

3.10 task parity(even_bit,odd_bit,input_bus); output even_bit,odd_bit; input[7:0] input_bus; reg even_bit, odd_bit,a; begin odd_bit = ^ input_bus; //产生奇校验位 a = ~odd_bit;end; //产生偶校验位 @(posedge clk) @(posedge clk) @(posedge clk) even_bit=a; end endtask

fpga简单项目案例

fpga简单项目案例

摘要:

1.FPGA 简介

2.FPGA 项目案例一:数字时钟

3.FPGA 项目案例二:图像处理

4.FPGA 项目案例三:通信系统

5.总结

正文:

FPGA(现场可编程门阵列)是一种集成电路,用户可以编程其功能和逻辑。

FPGA 具有高度灵活性,广泛应用于各种数字电路设计中。

下面我们将通过几个简单的项目案例来了解FPGA 的应用。

案例一:数字时钟

数字时钟是一个基本的FPGA 应用,主要功能是将输入的时钟信号转换为特定的时间显示格式。

通过编写相应的硬件描述语言(HDL)程序,我们可以实现时钟的计数、分频等功能,将输入的时钟信号转换为数字时钟信号。

此项目案例可以帮助初学者熟悉FPGA 的基本操作和硬件描述语言的编写。

案例二:图像处理

FPGA 在图像处理领域也有广泛的应用。

例如,我们可以利用FPGA 设计一个图像卷积核,实现图像卷积运算。

卷积核是图像处理中的一种重要算法,通过卷积操作可以实现图像的滤波、边缘检测等功能。

FPGA 的高速运算能力使得图像处理任务可以实时完成,满足实时图像处理的需求。

案例三:通信系统

FPGA 在通信系统中也发挥着重要作用。

例如,我们可以利用FPGA 设计一个数字信号处理(DSP)模块,实现数字信号的调制与解调。

在通信系统中,数字信号的调制与解调是关键环节,通过FPGA 的灵活编程可以实现不同调制解调方式的切换,满足不同通信场景的需求。

综上所述,FPGA 在多个领域具有广泛的应用前景。

通过简单的项目案例,我们可以初步了解FPGA 的功能和优势。

FPGA题及答案

1、本课程的讲授目标:了解一种新技术EDA;掌握一种设计工具(器件:Altera FPGA软件:Quartus II);掌握一种语言Verilog HDL。

2、使用Quartus II进行逻辑设计,常用的设计思想的输入方式有:原理图、HDL 等。

3、高级语言C程序经过软件程序编译器形成cpu指令/数据代码流;Verilog HDL程序经过综合器形成电路网表文件4、CPLD是在PAL,GAL等类型器件的基础上发展起来的与或阵列型PLD器件,大多数FPGA采用了查找表结构,其物理结构是静态存储器SRAM.。

5、JTAG边界扫描技术用于对高密度、引脚密集的器件和系统进行测试,如:CPU,DSP,ARM,PLD 等。

同时,JTAG接口也被赋予了更多的功能:编程下载、在线逻辑分析。

6、使用Verilog HDL进行逻辑设计,变量的值有4种状态:0、1、x、z;7、定义逻辑功能的几种基本方法:用assign持续赋值语句定义、用always过程块定义、调用元件(元件例化)。

8、整数按如下方式书写:+/-<size> '<base><value> 即+/-<位宽>'<进制><数字>size 为对应二进制数的宽度;base为进制;value是基于进制的数字序列。

进制有如下4种表示形式:二进制(b或B)、十进制(d或D或缺省)、十六进制(h或H)、八进制(o或O)9、定义reg型标量型变量:reg qout;//变量名qout10、定义wire型向量:wire[7:0] databus;//databus的宽度是8位11、在状态机设计中使用一位热码定义5种状态,并定义状态变量:parameter s0=5’b00001,s1=5’b 00010,s2=5’b 00100,s3=5’b 01000,s4=5’b 10000;reg [4:0] state,next_state;12、在状态机设计中使用顺序码定义5种状态,并定义状态变量:parameter s0=3’b 000,s1=3’b 001,s2=3’b 010,s3=3’b 011,s4=3’b 100;reg [2:0] state,next_state;1、成为IEEE 标准的HDL 有( CD )A 、ABEL-HDLB 、AHDLC 、VHDLD 、Verilog HDL2、Quartus II 是 ( A )公司的( D )开发工具。

CPLD作业

《CPLD/FPGA原理及应用》作业——正弦信号的发生及传输班级:电信10-2班姓名:晁远征学号:311008001107目录《CPLD/FPGA原理及应用》作业 0——正弦信号的发生及传输 0目录 (1)摘要 (2)硬件原理 (2)一.全局原理 (2)二.FPGA-EP2C5T144C8 (2)三.地址发生器 (4)四.串口通讯 (4)软件部分 (6)一..mif文件的产生 (6)二.ROM的配置 (8)三.FIFO的配置 (11)四.RTL视图 (13)软件部分 (14)一.地址发生器: (14)二.串口发送 (14)参考文献 (21)心得体会 (21)摘要20世纪60年代中期,TI公司大量生产了通用IC,如分别面向商用的军用的74系列和52系列。

这些通用的IC甚至沿用至今,仍是电子工程师们电路板上不可或缺的一部分。

20世纪80年代,出现了可编程逻辑器件,如CPLD和SPLD,它们与ASIC相比,具有可重配置性和较短的开发调试时间,但实现的功能和电路都相对简单。

为了弥补这一需要,Xilinx公司推出了第一块现场可编程逻辑器件,并且在其后的几十年间,FPGA得到了巨大发展。

目前FPGA主流厂商是Altera公司和Xilinx公司,它们的东西大都是类似的,不论从器件上还是开发软件上基本都这样。

FPGA的开发主要用到硬件描述语言,常见的是verilog和VHDL,当然用SOPC Bulider的话,可以用C。

但是片上系统不是FPGA的强项。

FPGA初诞生时,逻辑资源相对匮乏,当时的FPGA主要就用于实现粘合逻辑、中等复杂度的状态机或者是一些复杂度不高的数据处理。

实时控制也是FPGA的一个重要应用。

我比较熟悉verilog HDL,所以代码都用verilog。

Verilog代码主要分可综合的和不可综合的代码。

可综合代码主要用在RTL级,不可综合的主要用来仿真。

(个人是这么认为的)。

FPGA很强大,用它来做一个正弦信号发生器并进行传输实在是大材小用。

FPGA作业modelsim仿真3-8译码器和4-16译码器设计

任务:完成3-8译码器设计,利用modelsim仿真的形式,使用两个3-8译码器完成4-16译码器设计。

一.3-8译码器的仿真因为之后要进行扩展,所以我给这个译码器加上使能端en,高电平有效。

1.程序代码module decoder(data_in, data_out,en);input [2:0] data_in;input en;output reg [7:0] data_out;always @*beginif (!en)data_out=8'b0000_0000; //如果en=0,输出为0else //如果en=1,进行译码case(data_in)3'b000:data_out=8'b0000_0001;3'b001:data_out=8'b0000_0010;3'b010:data_out=8'b0000_0100;3'b011:data_out=8'b0000_1000;3'b100:data_out=8'b0001_0000;3'b101:data_out=8'b0010_0000;3'b110:data_out=8'b0100_0000;3'b111:data_out=8'b1000_0000;endcaseendendmodule2.仿真结果二.4-16译码器的仿真新建模块,使用实例化方式,对两个3-8译码器模块扩展成4.16译码器。

设计方法:将4-16译码器模块的低三位输入连接两个3-8译码器的输入,将最高位输入连接第一个3-8译码器的使能端,将最高位取反后连接第二个3-8译码器的使能端,将两个3-8译码器的输出作为4-16译码器的输出。

1.程序代码一/***decoder_4_16.v文件***/module decoder_4_16(data_in,data_out);input [3:0]data_in;output [15:0] data_out;wire [15:0]data_out;decoder i1(.data_in(data_in[2:0]), //实例化3-8译码器模块 .data_out(data_out[15:8]),.en(data_in[3]));decoder i2(.data_in(data_in[2:0]),.data_out(data_out[7:0]),.en(~(data_in[3])));Endmodule二/***测试文件decoder.tb.v***/`timescale 1ns/1psmodule decoder_test();reg [3:0] data_in;wire [15:0] data_out;decoder_4_16 d1(.data_in(data_in), //实例化4-16译码器.data_out(data_out));initial#200 $stop;initial#10data_in=0;always#10 data_in=data_in+1;endmodule2.仿真结果放大观察三.实验心得通过这次实验,我明白了QUARTUSII FPGA 设计的全过程,掌握了使用MODELSIM进行仿真的方法。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FPGA入门应用

姓名

学院

班级

学号

年月日

一、文本输入法:SUBDESIGN t3_3

(

a,b,c:INPUT;

a_out,b_out,c_out: OUTPUT;

)

BEGIN

IF a THEN

a_out=VCC;

b_out=GND;

c_out=GND;

ELSIF b THEN

a_out=GND;

b_out=VCC;

c_out=GND;

ELSIF c THEN

a_out=GND;

b_out=GND;

c_out=VCC;

ELSE

a_out=GND;

b_out=GND;

c_out=GND;

END IF;

END;

1、输入上述代码,并编译;

2、设置输入信号;

3、运行得输出波形。

二、原理图输入法:

1、实用quartus2编辑好电路图并编译;

2、设置输入波形;

3、得出输出波形。

三、心得:

原理图的输入设计法的主要内容是原件的引入和线的连接,适用于对系统很了解且对系统速率要求较高时,或设计大系统中地时间特性要求较高时。

原理图输入法设计效率较低,但易仿真,便于对型号的观察及电路的调整。

文本输入法就是将使用某种硬件描述语言(HDL)的电路设计文本,如VHDL或Verilog的源程序,进行的编辑输入。

它支持逻辑方程、真值表和状态机等表达方式,主要用于简单的小型设计。

两种输入法共同的突出特点有:语言与芯片工艺无关,利于自顶向下设计,便于模块的划分与移植,可移植性好,具有很强的逻辑描述和仿真功能,而且输入效率很高。