Design of a 1-V Operational Passive Sigma-Delta Modulator

核电常见英文缩略语手册

amperes Asset Management System American Nuclear Insurance American Nuclear Insurance Inspector Argonne National Laboratory Annex Building American Nuclear Society American National Standards Institute Qualification of QAP Audit Personnel for NPP Axial Offset, Auxiliary Operator, or Analog Output Axial Offset Argon-Oxygen Decarburization Anticipated Operational Occurrences Abnormal Operating Procedure Air Operated Valve Advanced Passive1000 MWe nuclear power plant American Petroleum Institute Advanced Passive Plant Applicability Document APY Administrator the General Administration of Quality Supervision, Inspection and Quarantine of PRC Advanced Reactor Corporation Air Conditioning and Refrigeration Institute All Rods Out Annunciator Response Procedure Auxiliary Shield Building American Society of Civil Engineers Atmospheric Steam Discharge Valve American Society of Heating, Refrigeration, and Air Conditioning Engineers Authorized Supplier List Atomic Safety and Licensing Boards Atomic Safety and Licensing Board Panel American Society of Mechanical Engineers QAP Required for Nuc Facilities (incl. Sup 2S-3 & App 2A-3) met by W-QMS American Society for Nondestructive Testing Assemble Auxiliary Steam Supply System American Society of Testing and Materials Assistant Tester

建筑方案 英语

建筑方案英语Architectural Design PlanIntroductionThe architectural design plan is a comprehensive document that outlines the proposed design for a building or structure. It includes various aspects such as the site analysis, concept development, spatial arrangements, materials selection, structural considerations, and sustainable design strategies. The purpose of this plan is to serve as a blueprint for the construction process, ensuring that the design meets the functional, aesthetic, and environmental requirements.Site AnalysisThe first step in the architectural design process is conducting a thorough site analysis. This involves studying the site's geographical location, topography, climate, accessibility, and surrounding context. The information gathered during this phase helps to inform the design decisions and ensure that the building is integrated harmoniously with its surroundings.Concept DevelopmentBased on the site analysis, the next step is to develop a design concept. This involves identifying the key design principles and creating a vision for the building that captures the client's requirements and aspirations. The concept can be influenced by various factors such as the building's purpose, historical references,cultural motifs, or the use of innovative technologies. The goal isto create a unique and meaningful design that responds to the site and the client's needs.Spatial ArrangementsThe spatial arrangements are crucial considerations in architectural design. This entails determining the internal layouts, circulation paths, and functional zoning of the building. Factors such as the activities to be accommodated, the number of occupants, and the desired flow of people and goods within the building are taken into account. The design strives to create well-organized, efficient, and comfortable spaces that promote functionality and user satisfaction.Materials SelectionThe choice of materials is essential in achieving the desired aesthetic and functional qualities of the building. This involves considering factors such as durability, flexibility, cost, availability, environmental impact, and maintenance requirements. The materials selected should also align with the design concept and contribute to the overall sustainability of the project. Examples of materials commonly used in architectural design include concrete, steel, glass, wood, and natural stone.Structural ConsiderationsStructural considerations are crucial for ensuring the stability and safety of the building. This involves analyzing the loads imposed on the structure, determining the appropriate structural system, anddesigning the foundations, columns, beams, and other load-bearing elements. Structural calculations and engineering principles are employed to ensure that the building can withstand various forces such as gravity, wind, seismic activity, and human occupancy.Sustainable Design StrategiesIn today's world, sustainable design strategies are becoming increasingly important in architectural design. This involves incorporating environmentally friendly practices to reduce energy consumption, minimize waste, enhance indoor environmental quality, and promote the use of renewable resources. Sustainable design strategies may include passive solar design, rainwater harvesting, use of recycled materials, energy-efficient systems, and green roofs. These strategies not only help protect the environment but also contribute to the long-term operational efficiency and economic viability of the building.ConclusionThe architectural design plan is a crucial document that guides the development of a building or structure. It encompasses various aspects such as site analysis, concept development, spatial arrangements, materials selection, structural considerations, and sustainable design strategies. By carefully considering these factors, architects can create functional, aesthetically pleasing, and environmentally responsible designs that meet the needs of the client and the surrounding community.。

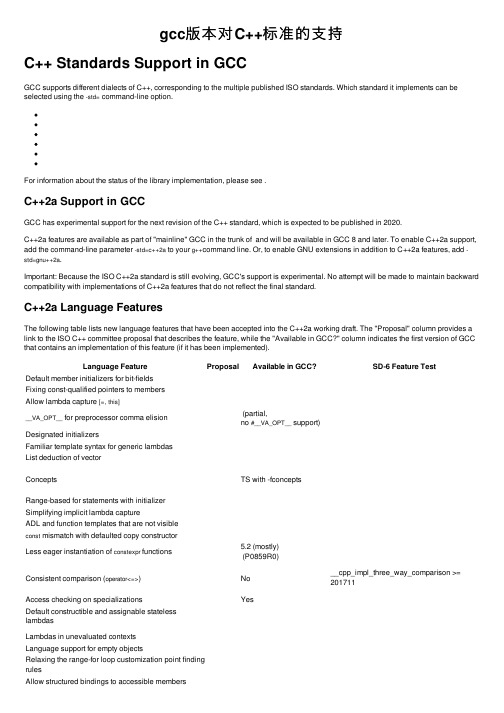

gcc版本对C++标准的支持

gcc版本对C++标准的⽀持C++ Standards Support in GCCGCC supports different dialects of C++, corresponding to the multiple published ISO standards. Which standard it implements can be selected using the -std= command-line option.For information about the status of the library implementation, please see .C++2a Support in GCCGCC has experimental support for the next revision of the C++ standard, which is expected to be published in 2020.C++2a features are available as part of "mainline" GCC in the trunk of and will be available in GCC 8 and later. To enable C++2a support, add the command-line parameter -std=c++2a to your g++command line. Or, to enable GNU extensions in addition to C++2a features, add -std=gnu++2a.Important: Because the ISO C++2a standard is still evolving, GCC's support is experimental. No attempt will be made to maintain backward compatibility with implementations of C++2a features that do not reflect the final standard.C++2a Language FeaturesThe following table lists new language features that have been accepted into the C++2a working draft. The "Proposal" column provides a link to the ISO C++ committee proposal that describes the feature, while the "Available in GCC?" column indicates the first version of GCC that contains an implementation of this feature (if it has been implemented).Language Feature Proposal Available in GCC?SD-6 Feature TestDefault member initializers for bit-fieldsFixing const-qualified pointers to membersAllow lambda capture [=, this]__VA_OPT__ for preprocessor comma elision (partial,no #__VA_OPT__ support)Designated initializersFamiliar template syntax for generic lambdasList deduction of vectorConcepts TS with -fconceptsRange-based for statements with initializerSimplifying implicit lambda captureADL and function templates that are not visibleconst mismatch with defaulted copy constructorLess eager instantiation of constexpr functions 5.2 (mostly) (P0859R0)Consistent comparison (operator<=>)No __cpp_impl_three_way_comparison >= 201711Access checking on specializations Yes Default constructible and assignable statelesslambdasLambdas in unevaluated contextsLanguage support for empty objectsRelaxing the range-for loop customization point findingrulesAllow structured bindings to accessible membersRelaxing the structured bindings customization pointRelaxing the structured bindings customization point finding rulesDown with typename!Allow pack expansion in lambda init-capture Proposed wording for likely and unlikely attributes Deprecate implicit capture of this via [=]Class Types in Non-Type Template Parameters __cpp_nontype_template_parameter_class >= 201806Atomic Compare-and-Exchange with Padding Bits No ()Efficient sized delete for variable sized classes__cpp_impl_destroying_delete >= 201806 Allowing Virtual Function Calls in ConstantExpressionsProhibit aggregates with user-declared constructorsSupport for contract based programming in C++No ()explicit(bool)__cpp_conditional_explicit >= 201806 Signed integers are two's complementchar8_t__cpp_char8_t >= 201811Immediate functions (consteval)No ()std::is_constant_evaluatedNested inline namespacesRelaxations of constexpr restrictions No ()Feature test macros (__cpp_ macros) (__has_cpp_attribute)Modules No ()Coroutines No ()Parenthesized initialization of aggregates No__cpp_aggregate_paren_init >= 201902 Stronger Unicode requirements NoStructured binding extensionsC++17 Support in GCCGCC has experimental support for the latest revision of the C++ standard, which was published in 2017.C++17 features are available as part of "mainline" GCC in the trunk of and in GCC 5 and later. To enable C++17 support, add the command-line parameter -std=c++17 to your g++ command line. Or, to enable GNU extensions in addition to C++17 features, add -std=gnu++17.Important: Because the final ISO C++17 standard is still new, GCC's support is experimental. No attempt will be made to maintain backward compatibility with implementations of C++17 features that do not reflect the final standard.C++17 Language FeaturesThe following table lists new language features that have been accepted into the C++17 working draft. The "Proposal" column provides a link to the ISO C++ committee proposal that describes the feature, while the "Available in GCC?" column indicates the first version of GCC that contains an implementation of this feature (if it has been implemented).Language Feature Proposal Available in GCC?SD-6 Feature Test Removing trigraphsu8 character literals__cpp_unicode_characters >= 201411 Folding expressions__cpp_fold_expressions >= 201411Attributes for namespaces and enumerators (namespaces)(enumerators)__cpp_namespace_attributes >= 201411__cpp_enumerator_attributes >= 201411Nested namespace definitions __cpp_nested_namespace_definitions >= 201411Allow constant evaluation for all non-type templatearguments__cpp_nontype_template_args >= 201411 Extending static_assert__cpp_static_assert >= 201411New Rules for auto deduction from braced-init-listAllow typename in a template template parameterAllow typename in a template template parameter[[fallthrough]] attribute__has_cpp_attribute(fallthrough)[[nodiscard]] attribute ([[gnu::warn_unused_result]])(P0189R1)__has_cpp_attribute(nodiscard)[[maybe_unused]] attribute ([[gnu::unused]])(P0212R1)__has_cpp_attribute(maybe_unused)Extension to aggregate initialization__cpp_aggregate_bases >= 201603 Wording for constexpr lambda__cpp_constexpr >= 201603Unary Folds and Empty Parameter Packs__cpp_fold_expressions >= 201603 Generalizing the Range-Based For Loop__cpp_range_based_for >= 201603 Lambda capture of *this by Value__cpp_capture_star_this >= 201603 Construction Rules for enum class variablesHexadecimal floating literals for C++ 3.0__cpp_hex_float >= 201603Dynamic memory allocation for over-aligned data__cpp_aligned_new >= 201606 Guaranteed copy elision__cpp_guaranteed_copy_elision >= 201606 Refining Expression Evaluation Order for Idiomatic C++constexpr if__cpp_if_constexpr >= 201606Selection statements with initializerTemplate argument deduction for class templates __cpp_deduction_guides >= 201606 __cpp_deduction_guides >= 201611Declaring non-type template parameters with auto __cpp_template_auto >= 201606__cpp_nontype_template_parameter_auto >= 201606Using attribute namespaces without repetitionIgnoring unsupported non-standard attributes YesStructured bindings__cpp_structured_bindings >= 201606 Remove Deprecated Use of the register KeywordRemove Deprecated operator++(bool)Make exception specifications be part of the typesystem__cpp_noexcept_function_type >= 201510 __has_include for C++17Rewording inheriting constructors (core issue 1941 etal)__cpp_inheriting_constructors >= 201511 Inline variables__cpp_inline_variables >= 201606DR 150, Matching of template template arguments__cpp_template_template_args >= 201611 Removing dynamic exception specificationsPack expansions in using-declarations__cpp_variadic_using >= 201611A byte type definitionTechnical SpecificationsGCC also implements experimental support for some language Technical Specifications published by the C++ committee. Important: Because these Technical Specifications are still evolving toward future inclusion in a C++ standard, GCC's supportis experimental. No attempt will be made to maintain backward compatibility with implementations of features that do not reflect the final standard.Technical Specification Document Available in GCC?Compiler Option SD-6 Feature TestConcepts-fconcepts__cpp_concepts >= 201507Transactional Memory (no atomic_cancel)-fgnu-tm__cpp_transactional_memory >= 201505CoroutinesModulesC++14 Support in GCCGCC has full support for the previous revision of the C++ standard, which was published in 2014.This mode is the default in GCC 6.1 and above; it can be explicitly selected with the -std=c++14 command-line flag, or -std=gnu++14 to enable GNU extensions as well.C++14 Language FeaturesThe following table lists new language features that are part of the C++14 standard. The "Proposal" column provides a link to the ISO C++ committee proposal that describes the feature, while the "Available in GCC?" column indicates the first version of GCC that contains an implementation of this feature.Language Feature Proposal Available in GCC?SD-6 Feature TestTweak to certain C++ contextual conversionsBinary literals (GNU)(N3472)__cpp_binary_literals >= 201304Return type deduction for normal functions (N3386)(N3638)__cpp_decltype_auto >= 201304Generalized lambda capture (init-capture) (partial)(N3648)__cpp_init_captures >= 201304Generic (polymorphic) lambda expressions__cpp_generic_lambdas >= 201304Variable templates__cpp_variable_templates >= 201304Relaxing requirements on constexpr functions__cpp_constexpr >= 201304Member initializers and aggregates__cpp_aggregate_nsdmi >= 201304Clarifying memory allocation N/ASized deallocation__cpp_sized_deallocation >= 201309 [[deprecated]] attribute (N3797)__has_cpp_attribute(deprecated) >= 201309Single-quotation-mark as a digit separator (N3797)__cpp_digit_separator >= 201309This feature was briefly part of the C++14 working paper, but was not part of the published standard; as a result, it has been removed from the compiler.Language Feature Proposal Available in GCC?SD-6 Feature TestRuntime-sized arrays with automatic storage duration (Removed from the standard)?.? (GNU VLAs)(N3639)(GNU VLAs)__cpp_runtime_arrays >= 198712C++11 Support in GCCGCC 4.8.1 was the first feature-complete implementation of the 2011 C++ standard, previously known as C++0x.This mode can be selected with the -std=c++11 command-line flag, or -std=gnu++11 to enable GNU extensions as well.For information about C++11 support in a specific version of GCC, please see:Language Feature Proposal Available in GCC?SD-6 Feature Test Rvalue references__cpp_rvalue_references >= 200610 Rvalue references for *this__cpp_ref_qualifiers >= 200710 Initialization of class objects by rvalues YesNon-static data member initializers__cpp_nsdmi >= 200809Variadic templates__cpp_variadic_templates >= 200704 Extending variadic template template parametersInitializer lists__cpp_initializer_lists >= 200806 Static assertions__cpp_static_assert >= 200410auto-typed variablesMulti-declarator autoRemoval of auto as a storage-class specifierNew function declarator syntaxNew wording for C++0x lambdas__cpp_lambdas >= 200907 Declared type of an expression__cpp_decltype >= 200707decltype and call expressionsRight angle bracketsDefault template arguments for function templatesSolving the SFINAE problem for expressionsTemplate aliases__cpp_alias_templates >= 200704 Extern templates YesNull pointer constantStrongly-typed enumsForward declarations for enumsGeneralized attributes __cpp_attributes >= 200809;__has_cpp_attribute(noreturn) >= 200809; __has_cpp_attribute(carries_dependency) == 0 (not implemented)Generalized constant expressions__cpp_constexpr >= 200704 Alignment supportDelegating constructors __cpp_delegating_constructors >= 200604Inheriting constructors__cpp_inheriting_constructors >= 200802 Explicit conversion operatorsNew character types__cpp_unicode_characters >= 200704 Unicode string literals__cpp_unicode_literals >= 200710Raw string literals__cpp_raw_strings >= 200710 Universal character name literalsUser-defined literals__cpp_user_defined_literals >= 200809 Standard Layout TypesDefaulted and deleted functionsExtended friend declarationsExtending sizeofInline namespacesUnrestricted unionsLocal and unnamed types as template argumentsRange-based for__cpp_range_based_for >= 200907 Explicit virtual overridesMinimal support for garbage collection and reachability-based leak detectionNoAllowing move constructors to throw [noexcept]Defining move special member functionsConcurrencySequence points YesAtomic operationsStrong Compare and ExchangeBidirectional FencesMemory modelData-dependency ordering: atomics and memory model(memory_order_consume)Propagating exceptionsAbandoning a process and at_quick_exitAllow atomics use in signal handlers YesThread-local storageDynamic initialization and destruction with concurrency__cpp_threadsafe_static_init >= 200806C99 Features in C++11__func__ predefined identifierC99 preprocessorlong longExtended integral types YesC++98 Support in GCCGCC has full support for the 1998 C++ standard as modified by the 2003 technical corrigendum and some later defect reports, excluding the export feature which was later removed from the language.This mode is the default in GCC versions prior to 6.1; it can be explicitly selected with the -std=c++98 command-line flag, or -std=gnu++98 to enable GNU extensions as well.。

自动化专业英语第三版 王宏文

UNIT 1Electrical NetworksA 电路An electrical circuit or network is composed of elements such as resistors, inductors, and capacito rs connected together in some manner. If the network contains no energy sources, such as batteri es or electrical generators, it is known as a passive network. On the other hand, if one or more en ergy sources are present, the resultant combination is an active network. In studying the behavior of an electrical network, we are interested in determining the voltages and currents that exist wit hin the circuit. Since a network is composed of passive circuit elements, we must first define the electrical characteristics of these elements.电路或电网络由以某种方式连接的电阻器、电感器和电容器等元件组成。

如果网络不包含能源,如电池或发电机,那么就被称作无源网络。

换句话说,如果存在一个或多个能源,那么组合的结果为有源网络。

在研究电网络的特性时,我们感兴趣的是确定电路中的电压和电流。

因为网络由无源电路元件组成,所以必须首先定义这些元件的电特性.In the case of a resistor, the voltage-current relationship is given by Ohm's law, which states that t he voltage across the resistor is equal to the current through the resistor multiplied by the value of the resistance. Mathematically, this is expressed as就电阻来说,电压-电流的关系由欧姆定律给出,欧姆定律指出:电阻两端的电压等于电阻上流过的电流乘以电阻值。

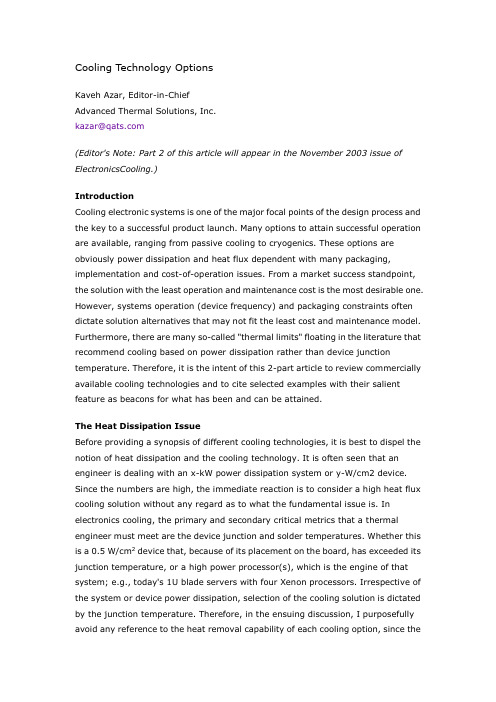

Cooling Technology Options

Cooling Technology OptionsKaveh Azar, Editor-in-ChiefAdvanced Therm al Solutions, Inc.kazar@(Editor's Note: Part 2 of this article will appear in the November 2003 issue of ElectronicsCooling.)IntroductionCooling electronic system s is one of the m ajor focal points of the design process and the key to a successful product launch. Many options to attain successful operation are available, ranging from passive cooling to cryogenics. These options are obviously power dissipation and heat flux dependent with m any packaging, implem entation and cost-of-operation issues. From a m arket success standpoint, the solution with the least operation and m aintenance cost is the m ost desirable one. However, system s operation (device frequency) and packaging constraints often dictate solution alternatives that m ay not fit the least cost and m aintenance m odel. Furthermore, there are m any so-called "thermal limits" floating in the literature that recommend cooling based on power dissipation rather than device junctiontem perature. Therefore, it is the intent of this 2-part article to review comm ercially available cooling technologies and to cite selected exam ples with their salient feature as beacons for what has been and can be attained.The Heat Dissipation IssueBefore providing a synopsis of different cooling technologies, it is best to dispel the notion of heat dissipation and the cooling technology. It is often seen that an engineer is dealing with an x-kW power dissipation system or y-W/cm2 device. Since the num bers are high, the immediate reaction is to consider a high heat flux cooling solution without any regard as to what the fundam ental issue is. In electronics cooling, the primary and secondary critical m etrics that a therm al engineer must m eet are the device junction and solder temperatures. Whether this is a 0.5 W/c m2 device that, because of its placem ent on the board, has exceeded its junction tem perature, or a high power processor(s), which is the engine of that system; e.g., today's 1U blade servers with four Xenon processors. Irrespective of the system or device power dissipation, selection of the cooling solution is dictated by the junction tem perature. Therefore, in the ensuing discussion, I purposefully avoid any reference to the heat rem oval capability of each cooling option, since thecapacity is temperature and space dependent. Further, making any reference to heat rem oval capacity can be misleading.When we look at the heat transport vehicles available in t he m arket, it is quite clear that the technology is well established and extensively docum ented. However, a series of questions are generated when attem pting to transfer this technology to electronics system s. These are:1.Would there be sufficient space to provide a large surface area for heattransfer, or to implement thermal transport (e.g., heat pipe) devices to take the heat out of the system?2.Can we use fluids with higher thermal capacitance/conductivity andsubsequently higher "h" to attain the desired cooling? Would the cost of such fluids allow their implementation in the m arket place?3.Would the existing system packaging allow the use of a higher capacitycooling system?4.Would the m arket be open to a system that is m echanically much m orecom plex and maintenance dem anding than a "simple" air mover?With these questions in mind, the cooling technology can be divided into two broad categories.A. Passive cooling, where nature does the fluid movement (e.g., natural convection) or energy is transported by conduction and/or radiation heat transfer.B. Active cooling, where the fluid m otion is assisted by an external source, a fan in a forced air cooled system, or pump and fan of an immersion or refrigeration cooled system.Considering the four questions that I raised, it is clear that option A is the m ost desired solution from the product standpoint since it has the leastimplem entation-cost and requires, effectively, no m aintenance. However, as the power dissipation increases and packaging space becom es l imited (question 1), option B begins to take hold and becom es the m ethod of choice despite its higher implem entation cost and concerns for the operational reliability.Cooling SystemsWith these two broad categories in mind, let's look at the cooling options that have been developed in the industry.Passive CoolingPassively cooled system s take advantage of all m odes of heat transfer for thermal transport. At the system level, typically, large heat sinks with wide fin-to-fin spacing are used for cooling. Television sets, set-top boxes, pole- or strand-m ounted telecommunications boxes are some of the typical examples in this category. In passively cooled system s, designers typically attem pt to utilize conduction and radiation as the primary m odes of heat transfer to m aximize the therm al transport and to induce higher levels of natural convection. In applications where convection is limited, e.g., space shuttle cooling, radiation heat transfer becom es the sole mode of transport of heat from the source to the sink - space, in the case of the shuttle.Passively cooled devices take advantage of a heat spreader (a conductive plate to spread the heat) and/or heat sinks specifically designed for such conditions. Similar to system s, m aximizing radiation and conduction heat transfer from the device is key for reaching higher levels of power dissipation while meeting device junction tem perature constraints. In space limiting applications, e.g., laptops, heat pipes are often used to efficiently transport the heat from the device to a location where a larger space is available (Figure 1).Figure 1. Heat pipe and heat spreader com bination. (Courtesy of Enertron Corp.)Active CoolingThis class of solutions encom passes an array of cooling techniques that are diverse and extensive. It is not the intent to review each individual cooling solution, ratherto highlight what is available and to provide the salient features of each option. In a broad sense, the cooling options can be categorized as follows:Heat Sinks and Fan-Sinks without Heat PipesExtended surfaces, so-called heat sinks, are by far the m ost commonly used cooling solutions in the electronics industry. The designs, m anufacturing techniques, and materials used in their construction are as diverse as the designers who m ake them. Conventionally they are used in system s with air movers. At tim es, because of airflow inadequacy or spatial constraints, a fan m aybe mounted on the heat sink, the so-called fan-sink. Or, a heat pipe is also used along with the heat sink to improve therm al transport. The interfacial and spreading resistances in addition to the attachm ent, as well as designing the heat sink for the right location on a PCB, are the points of contention.Fluid Flow Management and EnhancementAlthough this by itself can not be considered as a stand alone cooling solution, board and system level fluid flow m anagement has shown great promises. The t echnique involves looking at the flow distribution in the region of interest and attem pting to change the layout, whether a board or system, to rem ove flow stagnation points. As a result, whether a component on a PCB or a PCB in a system, it will have a significantly improved flow-exposure that can often result in the elimination of heat sinks or a lesser capacity cooling solution (Figure 2). This is an area that is often ignored since board or system re-layout are costly if fluid flow optimization is not done a priori.Figure 2. Water flow visualization of a flow over a PCB. On the left, the original layout shows multiple stagnation points. On the right, the flow-optimized layoutshows minimal stagnation points. (From the author's short course: "ExperimentalMethods in Electronics Cooling.")Hybrid CoolingThis simply implies a com bination of liquid and air cooling for high power dissipation electronics, while minimizing contact resistance throughout the system. In this process, the avionics industry has made great strides and produced cooling system s capable of rem oving high heat fluxes. Figure 3 shows one such system [1].Figure 3a, shows a rack/card guide system where the liquid is flowing through the card rack. The heat that is generated within the PCB is conduction through the solid core to the rack where the liquid is used as the transport vehicle to rem ove it from the system. The illustration on the right in Figure 3a shows a thru-card schem e where the PCB core is chambered for fluid passage. Thus the conduction heat transfer from the PCB to the rack, as shown in the figure on the right, is eliminated.Figure 3a. Two hybrid system s for an avionics application: On the left, edge liquid cooling; on the right, thru-card liquid cooling [1].Figure 3b shows the extensive packaging required to m ake such system s happen. Tightly sealed joints and mechanical contacts with least resistance are required to attain the level of therm al performance required for such a cooling option.Figure 3b. Card and rack level packaging required for hybrid cooling [1].Although I have purposefully avoided the discussion of cooling capacity, the exception to the path m ay be m erited here since these system s are not commonly encountered nor discussed in the open literature. Therefore, Figure 4 shows the removal capabilities of the hybrid system s for different cooling arrangements [1].The data depicted in Figure 4 clearly show the advantage of, say, subcooled jet impingement and a conventional cooled system, approximately a factor of 13! However, one cannot overlook the packaging requirements to deliver such a cooling solution, as shown in Figure 3b. The cost of these requirem ents and the attainm entof a high reliability cooling system may not m ake these system s suitable for typical commercially available electronics.Figure 4. Heat removal capacity for different hybrid system as com pared with aconvection cooled system. [1]Thermoelectric Cooler (TEC)TECs are electronic refrigerators that use the electrons to carry energy between the source and sink. The notion of a pump-less refrigerator, albeit highly inefficient, is an attractive concept. However, as shown by a number of researchers in the field, the promise of the TEC being an effective system level cooling solution has not materialized [2]. However, the TEC has been shown to be an enabling technology for spot cooling. One area that has benefited greatly from TEC is optical devices where maintaining a laser tem perature at a set level is a must for proper device operation. Poor device efficiency (30-50%) and reliability are the two limiting factors in the use of TECs in the industry.(End of Part 1)In Part 2 of this article, which will appear in the next issue, we will conclude with a discussion of Closed Loop Cooling, Thermosyphons, Direct Immersion with and without Boiling, Refrigeration Cooling System s, Cryogenics Cooling, and Conclusions.Kaveh Azar, Ph.D.Advanced Therm al Solutions, Inc.89 Access Road #27Norwood, MA 02062Tel: +1 781-769-2800Fax: +1 781-769-9979Em ail: kazar@References for Part 11. Mudawar, I., "Assessment of High-Heat-Flux Thermal managem ent Schem es", Proceedings of ITHERM, Las Vegas, NV, USA, 2000.2. Simons, R., "Application of Thermoelectric Coolers for Module Cooling Enhancem ent", ElectronicsCooling, Vol. 6. No. 2., pp. 18-24.Cooling Technology Options, Part 2Kaveh Azar, Editor-in-ChiefAdvanced Therm al Solutions, Inc.kazar@(Editor's Note: Part 1 of this article appeared in the August 2003 issue of ElectronicsCooling. Illustration references in this part begin with Figure 5.)IntroductionCooling electronic system s is one of the m ajor focal points of the design process and the key to a successful product launch. Many options to attain successful operation are available, ranging from passive cooling to cryogenics. These options are obviously power dissipation and heat flux dependent with m any packaging, implem entation and cost-of-operation issues. From a m arket success standpoint, the solution with the least operation and m aintenance cost is the m ost desirable one. However, system s operation (device frequency) and packaging constraints often dictate solution alternatives that m ay not fit the least cost and m aintenance m odel. Furthermore, there are m any so-called "thermal limits" floating in the literature that recommend cooling based on power dissipation rather than device junctiontem perature. Therefore, it is the intent of this 2-part article to review comm ercially available cooling technologies and to cite select examples with their salient feature as beacons for what has been and can be attained.In part 1 of this article, which appeared in the previous issue, we discussed: The Heat Dissipation Issue, Cooling System s (both passive and active), Heat Sinks and Fan Sinks without Heat Pipes, Fluid Flow Management and Enhancem ent, Hybrid Cooling, and Thermoelectric Coolers (TEC).Closed Loop Liquid CoolingThis is defined as a high capacity, high maintenance cooling system that uses liquid as the coolant and a heat ex changer for heat rem oval from the coolant. Figure 5 shows a schem atic drawing and typical implementation of such a system [3].Figure 5. A closed loop liquid cooling solution. The module at the lower left em ploys liquid jet impingement cooling. The m odule at the lower right uses spray cooling andrepresents an SGI Cray design [3].Different packaging schem es m ay put these cooling system s in other categories, but, in general, the use of closed liquid loops distinguishes these cooling system s from others. The predecessor for this cooling technique and perhaps the first commercial introduction of closed liquid loops in modern electronics (beyond vacuum tubes) is the IBM Thermal Conduction Module (TCM). In this system, a series of spring loaded cylinders conduct the heat from chips to the cooling cham ber. Such cooling solutions are currently used in high priced, large capacity com puters that can allow for the types of packaging and maintenance required to run these system.Figure 6. A thermosyphon cooling system. (Courtesy of Therm acore Corp.)ThermosyphonsThese are heat "transport" system s that use gravity to transfer heat from the source to sink. Although they are transport devices because of their implementation, they can be put into a category of a cooling solution. Figure 6 shows one such a system. The features of the system can be summarized as follows:∙Requires no pump and reservoir/expansion tank, com pared to closed loop cooling solutions.∙Can be m ade compact, so that the evaporator is the size of the m odule.∙Sensitive to orientation and internal fouling.Plumbed system, subject to shock/vibration, leakage, and potential dry-out.Direct Immersion with and without BoilingIn these system s the electronics is immersed in a Fluorinert liquid or mist to transfer the heat from the source to the sink. These are high capacity cooling system s that were deployed with limited success in the industry. The m ost fam ous such system - and som e examples are still in operation - is the Cray super com puter. Theoretically, the m ethodology is perhaps the best technique because the heat source is in direct contact with a high thermal capacity coolant, thus eliminating the nagging interfacial and spreading resistances that are the direct by-product ofconduction-to-convection cooling schem es. Figure 7, shows one such example of immersion cooling from IBM [4].Figure 7. IBM immersion cooling system with liquid or air cooled system s to removethe heat absorbed by the coolant [4].In these system s, depending upon the design and the choice of the coolant, boiling may occur. Research has shown that despite the high heat transfer offered by boiling, coolant fouling is a major concern with a poor reliability implication both for the coolant and the system where the fouling emanates. Irrespective, one can conclude that m ajor packaging, cost, and reliability issues are associated with such system s.Refrigeration Cooling SystemsThis is a relative newcom er to the electronics industry, finding a home in high speed microprocessors. In these system s, sub-cooling is necessary to attain the desired device frequencies. Kryotech is one of the first companies to have introduced refrigeration cooling to the commercial market. Figure 8 shows such a system where a simple, yet novel concept - a refrigeration unit of a size that would typically be used in a dorm room - is used to cool a high-speed m icroprocessor. The evaporator of the refrigerator is placed on the microprocessor to m aintain it at the desired tem perature.Figure 8. The first commercially available refrigerated processor.(Courtesy of Kryotech.)To im plement a refrigeration cooled system, the cycle and process look very similar to what has been commercially available for many years, Figure 9 [3].Figure 9. The com ponents required to form the refrigeration cycle.(IBM High End Z-Server, [3].)A number of system s have com e to the m arket that cover the full spectrum of products. These include individual PC level system s, rack level refrigeration for telecomm equipment, and high capacity (20kW) refrigeration system s. However, as much as the notion of sub-cooling is attractive for reaching the desired device frequencies, the issues of packaging, cost and reliability of m echanical system s continue to cast doubt on the use of such system s in commercial electronics.Cryogenics CoolingThis is perhaps the last frontier in cooling. The system is immersed in cryogenic fluids (e.g., liquid nitrogen) for cooling of super high heat flux devices that require low operating tem peratures. Despite a couple of failed commercial products, cryogenic cooling never found its application in the commercial market place. This failure was attributed to high operating cost, m ajor reliability issues (thus multiple down tim es), and high product cost due to custom development.Reliability issues are uniquely different as they pose the opposite problem to heat. At very low tem peratures, m aterial characteristics are different, and a host of new failure mechanisms with commercial m aterials are encountered. Therefore, to implem ent such a cooling system, a departure from conventional packaging is required. This causes a system to be costly for t ypical commercial use. Cryogenically cooled system s are typically associated with m ilitary and space electronics that can tolerate the high degree of customization and system cost.ConclusionsIn reviewing the broad scope of available cooling solutions, two points have becom e apparent.1.System s with tremendous heat dissipation have been designed andsuccessfully launched in the m arket place. Thus, a broad range of coolingsolutions do exist. Barring som e of the basic physics associated withcryogenics and boiling heat transfer, the underlying principles andfundamentals are also well understood. Therefore, when one is faced with a large heat flux at the device level or overall system power dissipation, areview of the literature and common practi ces is perhaps the best starting point.2.For every high capacity cooling system, whether hybrid or refrigerationcooling, the biggest bottleneck is the packaging. High capacity coolingsolutions do require a departure from conventional packaging techniquesused in the commercial (large m arket) electronics. This is a m atter thatcannot be taken lightly since for the commercial electronics,least-tim e-to-m arket and product-cost are the two prim ary drivers.To expand on the second point, although there are m any excellent works taking place to advance the cooling options, e.g., acousti c com pression (replacing mechanical com pressors), thermionics, device level electronic refrigeration, etc., the commercial electronics m arket is basically cost driven. Thus, air cooling and options to enhance its capacity should not be overlooked. Often, som e upfront engineering m ay avoid the large challenges of high capacity cooling solutions for a market that is not acclimated to these requirements. Considering that the selection of a cooling system is market driven rather than a m atter of best practices, the successful design is the one that gets the product into the m arket first with the least cost.Kaveh Azar, Ph.D.Advanced Therm al Solutions, Inc.89 Access Road #27Norwood, MA 02062Tel: +1 781-769-2800Fax: +1 781-769-9979Em ail: kazar@References for Parts 1 and 21. Mudawar, I., "Assessment of High-Heat-Flux Thermal managem ent Schem es", Proceedings of ITHERM, Las Vegas, NV, USA, 2000.2. Simons, R., "Application of Thermoelectric Coolers for Module Cooling Enhancem ent", ElectronicsCooling, Vol. 6. No. 2.3. NEMI 2000, Electronics Industry Roadmap, VA, USA.4. Chu, R., A personal communication.。

电子元件可靠度作业实务指引(一)

電子元件鑑定試驗(Reliabilty Qualification Test)前言電子元件鑑定的目的是於正式量產前或原料、製程變更時為了確認產品設計結構、使用原料到製造成品之產品能力是否達到設計及客戶(市場)的需求目標。

電子元件從產線製造出來除了確定功能符合需求外,尚需經歷搬運、儲存、PCB插件、PCB焊接、系統組裝、整機包裝、整機運輸、置架、銷售最後到消費者使用。

其間過程所經歷的外在力量、環境衝擊都有可能致使元件損傷乃至失效。

如果只是關注元件供應商的製程能力、良率對後續可能產生的損耗是潛存著極大的風險,以石英諧震(Crystal Resonator)/石英震盪(Crystal Oscillator)元件為例,在搬運、運輸過程的摔落及震盪衝擊,PCB插件時作業員不慎掉落地面,最後到消費者手上的手機中不慎墜落,都有可能造成石英諧震(Crystal Resonator)/石英震盪(Crystal Oscillator)元件中的石英晶片脫落,致使整機不良品的產出、產品使用壽命的減短或產品的失效,最終導致製造資源及自然資源的浪費。

另就PCB打件、焊接業者而言只是經過迴流焊測試過的元件未必能經得起超音波的焊接作業或手焊作業所產生的損壞及損傷影響。

所以只是以製程能力、良率或是實驗室度量的平均壽命(MTTF)來判斷元件的良莠是存在著相當大的盲點的。

即使良率100%的元件如果於PCB打件、(超音波)焊接中有30%的損壞,且也極可能有殘留的應力造成潛在的損傷,那,元件的製程能力、良率及壽命保證又有何意義呢?所以電子元件的製程能力、良率及平均壽命只有在通過各種可能的環境應力考驗才具有相對的意義。

電子元件的可鑑定測試除了功能及壽命測試(可靠度試驗)鑑定外,各種的環境應力模擬鑑定測試是完全不可或缺的。

相關規範1.AEC-汽車產業之行業標準規範AEC Component Technical Committee:一般性電子元件鑑定要求(Common electricalcomponent qualification requirements)1.1.積體電路(IC)元件相關文件說明:a.AEC-Q100 Rev - G是將各類IC產品的鑑定測試項目要求、方法及條件彙整的文件,並包括”設計、結購、能力證明(Certification of Design, Construction and Qualification)”和”鑑定測試計劃及結果(Q100G QUALIFICATION TEST PLAN)”的制式表格。

Integrated-circuit

Integrated circuitIn electronics, an integrated circuit (also known as IC, microcircuit, microchip, silicon chip, or chip) is a miniaturized electronic circuit (consisting mainly of semiconductor devices, as well as passive components) that has been manufactured in the surface of a thin substrate of semiconductor material. Integrated circuits are used in almost all electronic equipment in use today and have revolutionized the world of electronics. Integrated circuits were made possible by experimental discoveries which showed that semiconductor devices could perform the functions of vacuum tubes, and by mid-20th-century technology advancements in semiconductor device fabrication. The integration of large numbers of tiny transistors into a small chip was an enormous improvement over the manual assembly of circuits using electronic components. The integrated circuit's mass production capability, reliability, and building-block approach to circuit design ensured the rapid adoption of standardized ICs in place of designs using discrete transistors.There are two main advantages of ICs over discrete circuits: cost and performance. Cost is low because the chips, with all their components, are printed as a unit by photolithography and not constructed one transistor at a time. Furthermore, much less material is used to construct a circuit as a packaged IC die than as a discrete circuit. Performance is high since the components switch quickly and consume little power (compared to their discrete counterparts) because the components are small and close together. As of 2006, chip areas range from a few square millimeters to around 350 mm2, with up to 1 million transistors per mm2.Among the most advanced integrated circuits are the microprocessors or "cores", which control everything from computers to cellular phones to digital microwave ovens. Digital memory chips and ASICs are examples of other families of integrated circuits that are important to the modern information society. While the cost of designing and developing a complex integrated circuit is quite high, when spread across typically millions of production units the individual IC cost is minimized. The performance of ICs is high because the small size allows short traces which in turn allows low power logic (such as CMOS) to be used at fast switching speeds.ICs have consistently migrated to smaller feature sizes over the years, allowing more circuitry to be packed on each chip. This increased capacity per unit area can be used to decrease cost and/or increase functionality—see Moore's law which, in its modern interpretation, states that the number of transistors in an integrated circuit doublesevery two years. In general, as the feature size shrinks, almost everything improves—the cost per unit and the switching power consumption go down, and the speed goes up. However, ICs with nanometer-scale devices are not without their problems, principal among which is leakage current (see subthreshold leakage for a discussion of this), although these problems are not insurmountable and will likely be solved or at least ameliorated by the introduction of high-k dielectrics. Since these speed and power consumption gains are apparent to the end user, there is fierce competition among the manufacturers to use finer geometries. This process, and the expected progress over the next few years, is well described by the International Technology Roadmap for Semiconductors (ITRS).Only a half century after their development was initiated, integrated circuits have become ubiquitous. Computers, cellular phones, and other digital appliances are now inextricable parts of the structure of modern societies. That is, modern computing, communications, manufacturing and transport systems, including the Internet, all depend on the existence of integrated circuits.Integrated circuits can be classified into analog, digital and mixed signal (both analog and digital on the same chip).Digital integrated circuits can contain anything from one to millions of logic gates, flip-flops, multiplexers, and other circuits in a few square millimeters. The small size of these circuits allows high speed, low power dissipation,and reduced manufacturing cost compared with board-level integration. These digital ICs, typically microprocessors, DSPs, and micro controllers work using binary mathematics to process "one" and "zero" signals.Analog ICs, such as sensors, power management circuits, and operational amplifiers, work by processing continuous signals. They perform functions like amplification, active filtering, demodulation, mixing, etc. ICs can also combine analog and digital circuits on a single chip to create functions such as A/D converters and D/A converters. Such circuits offer smaller size and lower cost, but must carefully account for signal interference.The semiconductors of the periodic table of the chemical elements were identified as the most likely materials for a solid state vacuum tube by researchers like William Shockley at Bell Laboratories starting in the 1930s. Starting with copper oxide, proceeding to germanium, then silicon, the materials were systematically studied in the 1940s and 1950s. Today, silicon monocrystals are the main substrate used forintegrated circuits (ICs) although some III-V compounds of the periodic table such as gallium arsenide are used for specialized applications like LEDs, lasers, solar cells and the highest-speed integrated circuits. It took decades to perfect methods of creating crystals without defects in the crystalline structure of the semiconducting material.Semiconductor ICs are fabricated in a layer process which includes these key process steps:ImagingDepositionEtchingThe main process steps are supplemented by doping and cleaning.Integrated circuits are composed of many overlapping layers, each defined by photolithography, and normally shown in different colors. Some layers mark where various dopants are diffused into the substrate (called diffusion layers), some define where additional ions are implanted (implant layers), some define the conductors (polysilicon or metal layers), and some define the connections between the conducting layers (via or contact layers). All components are constructed from a specific combination of these layers.In a self-aligned CMOS process, a transistor is formed wherever the gate layer (polysilicon or metal) crosses a diffusion layer.Since a CMOS device only draws current on the transition between logic states, CMOS devices consume much less current than bipolar devices.A random access memory is the most regular type of integrated circuit; the highest density devices are thus memories; but even a microprocessor will have memory on the chip. Although the structures are intricate –with widths which have been shrinking for decades – the layers remain much thinner than the device widths. The layers of material are fabricated much like a photographic process, although light waves in the visible spectrum cannot be used to "expose" a layer of material, as they would be too large for the features. Thus photons of higher frequencies (typically ultraviolet) are used to create the patterns for each layer. Because each feature is so small, electron microscopes are essential tools for a process engineer who might be debugging a fabrication process.The earliest integrated circuits were packaged in ceramic flat packs, which continued to be used by the military for their reliability and small size for many years.Commercial circuit packaging quickly moved to the dual in-line package (DIP), first in ceramic and later in plastic. In the 1980s pin counts of VLSI circuits exceeded the practical limit for DIP packaging, leading to pin grid array (PGA) and leadless chip carrier (LCC) packages. Surface mount packaging appeared in the early 1980s and became popular in the late 1980s, using finer lead pitch with leads formed as either gull-wing or J-lead, as exemplified by small-outline integrated circuit -- a carrier which occupies an area about 30 –50% less than an equivalent DIP, with a typical thickness that is 70% less. This package has "gull wing" leads protruding from the two long sides and a lead spacing of 0.050 inches.In the late 1990s, PQFP and TSOP packages became the most common for high pin count devices, though PGA packages are still often used for high-end microprocessors. Intel and AMD are currently transitioning from PGA packages on high-end microprocessors to land grid array (LGA) packages.Ball grid array (BGA) packages have existed since the 1970s. Flip-chip Ball Grid Array packages, which allow for much higher pin count than other package types, were developed in the 1990s.Most integrated circuits large enough to include identifying information include four common sections: the manufacturer's name or logo, the part number, a part production batch number and/or serial number, and a four-digit code that identifies when the chip was manufactured. Extremely small surface mount technology parts often bear only a number used in a manufacturer's lookup table to find the chip characteristics.The manufacturing date is commonly represented as a two-digit year followed by a two-digit week code, such that a part bearing the code 8341 was manufactured in week 41 of 1983, or approximately in October 1983.Structure and function of the MCS-51 seriesStructure and function of the MCS-51 series one-chip computer is a name of a piece of one-chip computer series which Intel Company produces. This company introduced 8 top-grade one-chip computers of MCS-51 series in 1980 after introducing 8 one-chip computers of MCS-48 series in 1976. It belong to a lot of kinds this line of one-chip computer the chips have,such as 8051, 8031, 8751, 80C51BH, 80C31BH,etc., their basic composition, basic performance and instruction system are all the same. 8051 daily representatives- 51 serial one-chip computers .An one-chip computer system is made up of several following parts: ( 1) One microprocessor of 8 (CPU). ( 2) At slice data memory RAM (128B/256B),it use notdepositting not can reading /data that write, such as result not middle of operation, final result and data wanted to show, etc. ( 3) Procedure memory ROM/EPROM (4KB/8KB ), is used to preserve the procedure , some initial data and form in slice. But does not take ROM/EPROM within some one-chip computers, such as 8031 , 8032, 80C ,etc.. ( 4) Four 8 run side by side I/O interface P0 four P3, each mouth can use as introduction , may use as exporting too. ( 5) Two timer / counter, each timer / counter may set up and count in the way, used to count to the external incident, can set up into a timing way too, and can according to count or result of timing realize the control of the computer. ( 6) Five cut off cutting off the control system of the source . ( 7) One all duplexing serial I/O mouth of UART (universal asynchronous receiver/transmitter (UART) ), is it realize one-chip computer or one-chip computer and serial communication of computer to use for. ( 8) Stretch oscillator and clock produce circuit, quartz crystal finely tune electric capacity need outer. Allow oscillation frequency as 12 megahertas now at most. Every the above-mentioned part was joined through the inside data bus .Among them, CPU is a core of the one-chip computer, it is the control of the computer and command centre, made up of such parts as arithmetic unit and controller , etc.. The arithmetic unit can carry on 8 persons of arithmetic operation and unit ALU of logic operation while including one, the 1 storing device temporarilies of 8, storing device 2 temporarily, 8's accumulation device ACC, register B and procedure state register PSW, etc. Person who accumulate ACC count by 2 input ends entered of checking etc. temporarily as one operation often, come from person who store 1 operation is it is it make operation to go on to count temporarily , operation result and loopback ACC with another one. In addition, ACC is often regarded as the transfer station of data transmission on 8051 inside . The same as general microprocessor, it is the busiest register. Help remembering that agreeing with A expresses in the order. The controller includes the procedure counter , the order is depositted, the order decipher, the oscillator and timing circuit, etc. The procedure counter is made up of counter of 8 for two, amounts to 16. It is a byte address counter of the procedure in fact, the content is the next IA that will carried out in PC. The content which changes it can change the direction that the procedure carries out . Shake the circuit in 8051 one-chip computers, only need outer quartz crystal and frequency to finely tune the electric capacity, its frequency range is its 12MHZ of 1.2MHZ. This pulse signal, as 8051 basic beats of working, namely the minimum unit of time. 8051 is the same as other computers, the work in harmonyunder the control of the basic beat, just like an orchestra according to the beat play that is commanded.。

Load-pull principle

S 22 =

b2 a2

a 1= 0

terminated)

S12 =

b2 a1

(reverse transmission coefficient with output properly a1 =0 terminated).

29

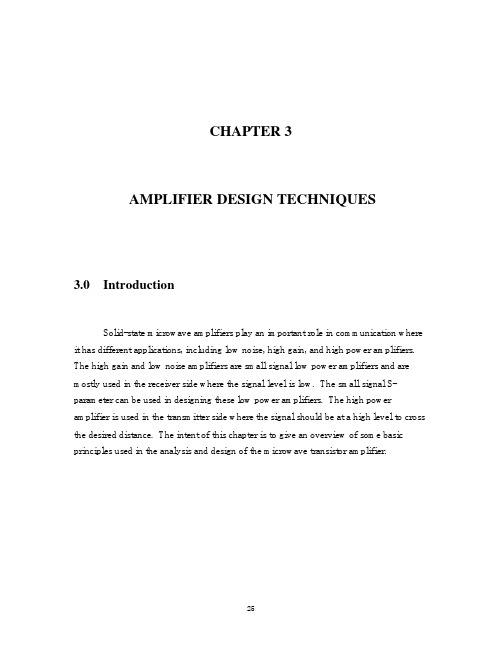

Figure 3.2 A transistor as two-port network.

15

20

Figure 3.1 Characteristics and recommended quiescent points for transistor amplifier

28

The S-parameters represent the transmission or reflection coefficients and can be obtained as follows:

b1 = S 11 ⋅ a1 + S12 ⋅ a2 b2 = S 21 ⋅ a1 + S 22 ⋅ a 2

where,

(3.1) (3.2)

ai and bi are the incident and reflected waves respectively at port i and can be defined in terms of the voltage wave, as shown in equations (3.3) and (3.4):

S11 =

b1 a1

(input reflection coefficient with output properly terminated) a

=0 2

S 21 =

b2 a1 a =0

2

(forward transmission coefficient with output properly terminated) (output reflection coefficient with output properly

【精品】电子信息工程专业英语课后答案

电子信息工程专业英语课后答案电子信息工程专业英语-教师用书Part 1第一课关于电子技术一、课文习题参考答案Ⅰ. (1) alternating current circuits (2) semiconductor diodes(3) passive component(4) the combinatory logic electric circuit(5) rectification(6) Laplace transform(7) inductor(8) Fourier series and Fourier transformⅡ.(1)控制理论(2)场效应管三极管(3)布尔代数(4)稳压(5)相关性和功率谱密度(6)滤波器类型(7)模/数转换器(8)时序逻辑电路的分析与综合Ⅲ.(1)Electronics is a part of the larger field of electricity. The basic principles of electricity are also common to electronics. Modern advances in the field of computer, control system, communications have a close relationship with electronics. The field of electronics includes the electron tube, transistor, integrated circuit and so on.(2) Direct current circuits & Alternating current circuits,Analog electronics,Digital electronics,signal and systems,Circuit theory and design, Control theory, Microcontrollersystems,Computer programming for engineering applications.(3) This curriculum mainly introduces the characteristics of semiconductor devices in linear application scope.The content involved in semiconductor diodes (PN junction diodes, special purpose diodes), transistors (field effects and bipolar transistors), signal amplifiers, practical amplifiers, biasing circuits, operationalamplifiers circuit and other circuits (rectification, regulation and DC power supplies).(4) This partial studies take the basicelectric circuit theory and the operational amplifier knowledge as the foundation. The main study goal is to enhance understanding of the electric circuit theory. Its main content includes the elementary theory in circuit theory (network functions, characteristic frequencies), types offilter (lowpass,bandpass), review of operational amplifiers (design of first and second order using operational amplifiers, cascade design), filter characteristics(Butterworth, Chebyshev, frequency transformations in design, sensitivity design of passive LC ladder filters and a brief introduction to switched capacitor filters).(5) Perfect.二、参考译文电子学的发展电子学是电学的一部分。

电子信息工程专业英语=文章翻译+课后解答

电子信息工程专业英语Part 1第一课关于电子技术一、课文习题参考答案Ⅰ. (1)alternating current circuits (2)semiconductor diodes(3)passive component(4)the combinatory logic electric circuit(5)rectification(6)Laplace transform(7)inductor(8)Fourier series and Fourier transformⅡ.(1)控制理论(2)场效应管三极管(3)布尔代数(4)稳压(5)相关性和功率谱密度(6)滤波器类型(7)模/数转换器(8)时序逻辑电路的分析与综合Ⅲ.(1)Electronics is a part of the larger field of electricity. The basic principles of electricity are also common to electronics. Modern advances in the field of computer, control system, communications have a close relationship with electronics. The field of electronics includes the electron tube, transistor, integrated circuit and so on.(2) Direct current circuits & Alternating current circuits,Analog electronics,Digital electronics,signal and systems,Circuit theory and design, Control theory, Microcontroller systems,Computer programming for engineering applications.(3) This curriculum mainly introduces the characteristics of semiconductor devices in linear application scope.The content involved in semiconductor diodes (PN junction diodes, special purpose diodes), transistors (field effects and bipolar transistors), signal amplifiers, practical amplifiers, biasing circuits, operational amplifiers circuit and other circuits (rectification, regulation and DC power supplies).(4) This partial studies take the basic electric circuit theory and the operational amplifier knowledge as the foundation. The main study goal is to enhance understanding of the electric circuit theory. Its main content includes the elementary theory in circuit theory (network functions, characteristic frequencies), types of filter (lowpass,bandpass), review of operational amplifiers (design of first and second order using operational amplifiers, cascade design), filter characteristics(Butterworth, Chebyshev, frequency transformations in design, sensitivity design of passive LC ladder filters and a brief introduction to switched capacitor filters).(5) Perfect.二、参考译文电子学的发展电子学是电学的一部分。

Operational amplifier

Operational amplifier1.IntroductionThe operational amplifier was first introduced in the early 1940s. Primary usage of these vacuum tube forerunners of the ideal gain block was in computational circuits. They were fed back in such a way as to accomplish addition, subtraction, and other mathematical functions.Expensive and extremely bulky, the operational amplifier found limited use until new technology brought about the integrated version, solving both size and cost drawbacks.Volumes upon volumes have been and could be written on the subject of op amps. In the interest of brevity, this application note will cover the basic op amp as it is defined, along with test methods and suggestive applications. Also, included is a basic coverage of the feedback theory from which all configurations can be analyzed.2.The perfect amplifierThe ideal operational amplifier possesses several unique characteristics. Since the device will be used as a gain block, the ideal amplifier should have infinite gain. By definition also, the gain block should have an infinite input impedance in order not to draw any power from the driving source. Additionally, the output impedance would be zero in order supply infinite current to the load being driven. These ideal definitions are illustrated by the ideal amplifier model of figure 4.2Further desirable attributes would include infinite bandwidth, zero offset voltage, and complete insensitivity to temperature, power supply variations, and common-mode input signals.Keeping these parameters in mind, further contemplation produces two very powerful analysis tools. Since the input impedance is infinite, there will be no current flowing at the amplifier input nodes. In addition, when feedback is employed, the different input voltage reduces to zero. These two statements are used universally as beginning points for any network analysis and will be explored in detail later on.3.The practical amplifierTremendous strides have been made by modern technology with respect to the ideal amplifier. Integrated circuits are coming closer and closer to the ideal gain block. In bipolar devices, for instance, input bias currents are in the pA range for FET input amplifiers while offset voltages have been reduced to less than 1mV in many cases.Any device has limitations however, and the integrated circuit is no exception. Modern op amps have both voltage and current limitations. Peak-to-peak output voltage, for instance, is generally limited to one or two base-emitter voltage drops below the supply voltage, while output current is internally limited to approximately 25mA. Other limitations such as bandwidth and slew rates are also present, although each generation of devices improves over the previous one.4.Definition of termsEarlier, the ideal operational amplifier was defined. No circuit is ideal, of course, so practical realizations contain some sources of error.Before the internal circuitry of the op amp is further explored, it would be beneficial to define those parameters commonly referenced.1)Input offset voltageIdeal amplifiers produce 0V out for 0V input. But, since the practical case is not perfect,a small DC voltage will appear at the output, even though no differential voltage is applied. This DC voltage is called the input offset voltage, with the majority of its magnitude being generated by the differential input stage pictured in figure 4.3.An operational amplifier’s performance is, in large part, dependent upon the first stage. It is the very high gain of the first stage that amplifiers small signal levels to drive remaining circuitry. Coincidentally, the input current, a function of beta, must be as small as possible. Collector current levels are thus made very low in the input stage in order to gain low bias currents. It is this input stage which also determines DC parameters such as offset voltage, since the amplified output of this stage is of sufficient voltage levels to eclipse most subsequent error terms added by the remaining circuitry. Under balance conditions, the collectors of Q1 and Q2 are perfectly matched, hence we may say:In practice, small differences in geometries of the base-emitter regions of Q1 and Q2 will cause E OS not to equal 0. Thus, for balance to be restored, a small DC voltage must be added to one V BE orWhere the V BE of the transistor is found byReference is made to the input when talking of offset voltage. Thus, the classic definition of input offset voltage is “that differential DC voltage required between inputs of an amplifier to force its output to zero volts.”Offset voltage becomes a very useful quantity for the designer because many other sources of error can be expressed in terms of V OS. For instance, the error contribution of input bias current can be expressed as offset voltages appearing across the input resistors.2)Input offset voltage driftAnother related parameter to offset voltage is V OS drift with temperature. Present-day amplifiers usually possess V OS drift levels in the range of 5V/C to 40V/C. The magnitude of V OS drift is directly related to the initial offset voltage at room temperature.Amplifiers exhibiting larger initial offset voltage will also possess higher drift rates with temperature. A rule of thumb often applied is that the drift per C will be 3.3V for each millivolt of initial offset. Thus, for tighter control of thermal drift, a low offset amplifier would be selected.3)Input bias currentReferring to figure 4.4, it is apparent that the input pins of this op amp are base inputs. They must, therefore, possess a DC current path to ground in order for the input to function. Input bias current, then, is the DC current required by the inputs of the amplifier to properly drive the first stage.The magnitude of I BIAS is calculated as the average of both currents flowing into the inputs and is calculated fromBias current requirements are made as small as possible by using high beta input transistors and very low collector currents in the first stage. The trade-off for bias current is lower stage gain due to low collector current levels and lower slew rates. The effect upon slew rate is covered in detail under the compensation section.4)Input offset currentThe ideal case of the differential amplifier and its associated bias current does not possess an input offset current. Circuit realizations always have a small difference in bias currents from one input to the other, however. This difference is called the input offsetcurrent.Actual magnitudes of offset current are usually at least an order of magnitude below the bias current. For many applications this offset may be ignored but very high gain, high input impedance amplifiers should possess as little I OS as possible because the difference in currents flowing across large impedance develops substantial offset voltage. Output voltage offset due to I OS can be calculated byHence, high gian and high input impedances magnify directly to the output, the error created by offset current. Circuits capable of nulling the input voltage and current errors are available and will be covered later in this chapter.5)Input offset current driftOf considerable importance is the temperature coefficient of input offset current. Even though the effects of offset are nulled at room temperature, the output will drift due to changes in offset current over temperature. Many popular models now include a typical specification for I OS drift with values ranging in the 0.5nA/C area.Obviously, those applications requiring low input offset currents also require low drift with temperature.6)Input impedanceDifferential and common-mode impedances looking into the input are often specified for integrated op amps. The differential impedance is the total resistance looking from one input to the other, while common-mode is the common impedance as measured to ground. Differential impedances are calculated by measuring the change of bias current caused by a change in the input voltage.7)Common-Mode rangeAll input structures have limitations as to the range of voltages over which they will operate properly. This range of voltages impressed upon both inputs which will not cause the output to misbehave is called the common-mode range. Most amplifiers possess common-mode ranges of 12V with supplies of 15V.8)Common-Mode rejection ratioThe ideal operational amplifier should have no gain for an input signal common to both inputs. Practical amplifiers do have some gain to common-mode signals. The classic definition for common-mode rejection ratio of an amplifier is the ratio of the differential signal gain to the common-mode signal gain expressed in dB as shown in the following equation.The measurement CMRR requires 2 sets of measurements. However, note that if e O is held constant, CMRR becomes:A new alternate definition of CMRR is the ratio of the change of input offset voltage to the input common-mode voltage change producing it.Figure 4.5 illustrates the application of the equivalent common-mode error generator to the voltage-follower circuit.。

FM-x14中英文操作手册10-6-26

Intended use计划使用

FM vehicles are suitable for the lifting and transporting of loads. They are designed for transport and storage applications such as stacking, entry into storage and retrieval. Due to the shift function of the mast, it is not necessary to provide a drive-under facility for the wheel spars. As a result, it is possible to approach a ledge and engage a load positioned on it, e.g. a ramp, in the same way as with a front lift truck.

P6,P8

The factory name plate工厂铭牌

The name plate is fitted in the area of the driving seat and contains the following details: 铭牌安装在驾驶员座椅的正前方的机身上(图中1位置), 包含以下内容: 1.CE symbol CE 符号

Caution 警告

The trucks described here must not be used: 叉车在以下情况下不可被使用 - in areas at risk from fire or explosions 有发生火灾或者爆炸的风险的区域中 - in areas with atmospheres conducive to corrosion 有腐蚀的气体的区域中 - in atmospheres containing large amounts of dust 有大量尘土的区域中 - in public traffic 在公众的交通中 - in refrigerated warehouses (see special equipment) 在中冷冻仓库(见特殊的设备) - in the open in the rain在户外冒雨作业。

英文翻译——采用红外传感器网络对移动目标的计数英文翻译