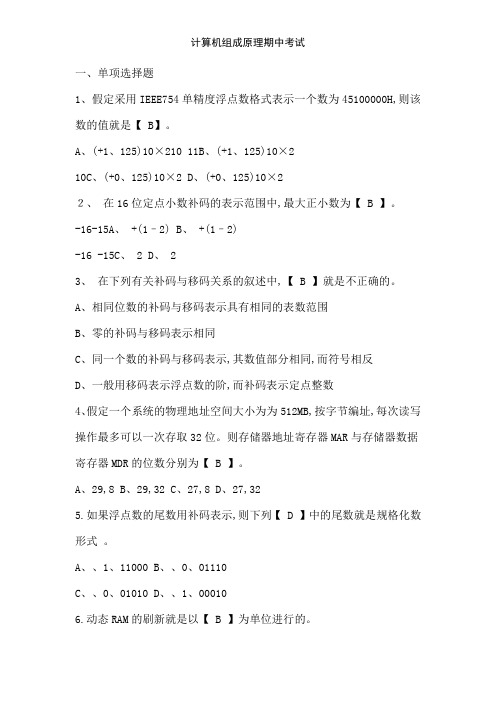

计算机组成原理-期中考试卷

计算机组成原理期中考试试卷

计算机组成原理期中考试试卷⼀、填空题(每空1 分,共30 分)1.计算机系统是由⼀个硬件和软件组成的多层次结构。

2. 随⼤规模集成电路技术的发展和软件硬化的趋势,现在已经可以将许多复杂、常⽤的程序制作成固件,从功能上说是软件,从形态上说是硬件。

3.在计算机系统中,数的真值变成机器代码时有原码表⽰法、表⽰法、补码表⽰法和移码表⽰法。

其中浮点数的阶码主要⽤采⽤移码表⽰,以利于⽐较两个指数的⼤⼩和对阶操作。

4.在计算机系统中,存储器通常采⽤由⾼速缓冲存储器、主存储器、外存储器构成的多级存储器体系结构,CPU能直接访问⾼速缓冲存储器、主存储器但不能直接访问外存储器。

5.机器字长是指计算机能直接处理的⼆进制数据的位数,它决定了计算机的运算精度。

6.形成指令地址的⽅式,称为A.___指令寻址___⽅式,有B. __顺序____寻址和C. ___跳跃___寻址。

7.⼀个较完善的指令系统应当包括数据处理、数据存储、数据传送、程序控制四⼤类指令。

8. 对存储器的要求是A. ___容量⼤___,B. _速度快_____,C. _成本低____。

为了解决这三⽅⾯的⽭盾,计算机采⽤多级存储体系结构。

9.⼀台计算机中所有机器指令的集合,称为这台计算机的指令系统,指令格式中通常由操作码字段和地址码字段字段组成。

其中__操作码____字段表征指令的特性与功能。

⼆、单项选择题(在每⼩题的四个备选答案中,选出⼀个正确答案,并将正确答案的序号填在题⼲的括号内)1.某计算机字长16位,它的存贮容量是64KB,若按字编址,那么它的寻址范围是( B )。

A. 64KB. 32KC. 64KBD. 32 KB2.. 双端⼝存储器在__B____情况下会发⽣读/写冲突。

A. 左端⼝与右端⼝的地址码不同B. 左端⼝与右端⼝的地址码相同C. 左端⼝与右端⼝的数据码不同D. 左端⼝与右端⼝的数据码相同3. 寄存器间接寻址⽅式中,操作数处在__B____。

计算机组成原理期中试卷及答案解析

计组期中考试考试说明考试说明:考察4.2章节之前的小题(其中3.6不考),难度接近真题。

满分100分,共20;对A.250us、400B.400us、250C.425us、235D.500us、2002.C【解析】100,000条指令总的执行周期数=1*45000+2*32000+15000*3+8000*2=170000个时钟周期,该处理器1秒钟的时钟周期数为400M,故执行时间为0.17M/400M=425us,该处理器的有效MIPS=1s/425us*100000≈235,故答案选C。

3.下面有关计算机语言的说法中,错误的是()。

Ⅰ. 机器语言是由0/1代码串构成的代码语言,而汇编语言是符号化的语言Ⅱ. 机器语言和汇编语言是面向机器的语言,因此,能够被计算机硬件直接执行Ⅲ. 高级语言需要编译成二进制机器指令后才能执行,而汇编语言因为与机器指令一一对应,所以不需要编译就可执行A.仅Ⅰ和ⅡB.仅Ⅰ和ⅢC.仅Ⅱ和ⅢD.Ⅰ、Ⅱ和Ⅲ3.C【解析】汇编语言是把机器语言的二进制代码对应成汇编的符号进行编程,因此汇编语言属于符号化的语言。

汇编语言的程序必须经过一个称为汇编程序的系统软件翻译,将其转换为计算机的机器语言程序之后,才能在计算机上执行。

4.以下有关使用GCC生成C语言程序的可执行文件的叙述中,错误的是()。

A. 第一步预处理,对#include、#define、#ifdef等预处理命令进行处理B. 第二步编译,将预处理结果编译转换为二进制形式的汇编语言程序代码C. 第三步汇编,将汇编语言代码汇编转换为机器指令表示的机器语言代码D. 第四步链接,将多个模块的机器语言代码链接生成可执行目标程序文件4.B【解析】编译是将预处理结果转换为汇编语言,汇编语言使用助记符,不是二进制形式,B错误。

5.假设sizeof (int) = 4 bytes,对于以下C语言代码:int cod=2;printf (“%d\n”,~cod); //~为按位取反操作上述程序段的输出结果为( )A.-3B. -2C.231-1D.231-25.A【解析】cod的补码表示为00 00 00 02H,则~cod为FF FF FF FDH,而FF FF FF FDH在计算机中是以补码的方式解析,其真值为-3,故选A。

计算机组成原理试题期中考试复习卷1

计算机组成原理试题一、选择题1、目前的计算机中,代码形式是()CA、指令以二进制的形式存放,数据以十进制的形式存放。

B、指令以十进制的形式存放,数据以二进制的形式存放。

C、指令和数据均以二进制的形式存放。

D、指令和数据均以十进制的形式存放。

2、目前普遍使用的微型计算机采用的电路是( )DA、电子管B、晶体管C、集成电路D、超大规模集电成路3、完整的计算机系统应包括()DA、运算器、存储器、控制器B、外部设备和主机C、主机和应用程序D、配套的硬件设备和软件系统4、计算机语言有许多种,其中与硬件直接相关的是( ) CA、网络语言B、操作系统C、机器语言D、高级语言5、在8421码表示的二—十进制数中,代码1001表示( ) CA、3B、6C、9D、16.代码10101逻辑右移一位后得( ) DA、10010B、10011C、01011D、010107、下列数中最小的数是()。

BA、(1010010)2B、(0101000)BCDC、(512)8D、(235)168、下列数中最大的数是()BA、(10010101)2B、(227)8C、(96)16D、(143)109、设寄存器的位数为8位,机器数采用补码形式(一位为符号位)对应于十进制为-27,寄存器内为()CA、(27)16B、(9B)16C、(E5)16D、(5A)1610、立即寻址是指() BA、指令中直接给出操作数地址B、指令中直接给出操作数C、指令中间接给出操作数D、指令中间接给出操作数地址11、输入输出指令的功能是() CA、进行算术运算和逻辑运算B、进行主存与CPU之间的数据传送C、进行CPU与I/O设备之间的数据传送D、改变程序执行的顺序12、在主存和CPU之间增加Cache的目的是()。

CA、扩大主存的容量B、增加CPU中通用寄存器的数量C、解决CPU和主存之间的速度匹配D、代替CPU中寄存器工作13、计算机系统的输入输出接口是()之间的交接界面。

计算机组成原理期中测试试卷一及答案

第一章微型计算机组成概述教学检测卷(本卷满分300分,考试时间120分钟)一、填空题(每空2分,45空,共90分)1.微型计算机从外观看主要由____________、显示器、键盘、鼠标、音箱等部件组成。

2.微型计算机中的核心部件是_____________,它是一块多层印制电路板,上面布满了各种插槽、接口和电子元件等。

3.决定微处理器性能指标主要有_____________和_____________。

4.目前的微型计算机的主板大多采用_____________(SIMM)结构,该结构的主板上提供与欧内存插槽及内存条。

5.微型计算机的各组成部件就是通过_____________相互连接而形成计算机系统的。

6.外存中的信息必须被调入_____________后才能为_____________使用。

7.VGA接口主要用于连接_____________。

8.CPU和主存、外围设备之间通过总线进行连接的逻辑部件称为_____________。

9.在大、中型机中的数据输入/输出传送控制方式一般为_____________方式。

10.当1/0设备的操作时间是固定不变时,CPU不需要测试设备状态,按规定时间直接访问设备的数据传送方式称为_____________。

11.在程序中断方式中,CPU每次执行中断服务程序前总要保护断点、保存现场,执行完中断服务程序返回现行程序之前又要_____________和_____________。

12.1/0接口中一般包括数据输入寄存器、_____________、控制寄存器、_____________和中断控制逻辑。

13.光盘按读/写方式分为____________光盘、一次写入型光盘和___________光盘三类。

14.大型计算机系统中的独立型通道一般分为字节多路通道、选择通道和_____________通道。

15.计算机的主机主要包括中央处理器和_____________。

计算机组成原理期中考试

2、 变址寻址与基址寻址的区别就是:在基址寻址中,基址寄存器提

供 , 指令提供 ; 而在变址寻址中,变址寄存器提供 ,指令提供 。

3、 影响流水线性能的因素主要反映在与

4、 设机器数字长为16位(含1位符号位)。若1次移位需10ns,一

A、、1、11000 B、、0、01110

C、、0、01010 D、、1、00010

6.动态RAM的刷新就是以【 B 】为单位进行的。

A.存储单元 B.存储矩阵行

B.存储矩阵列 D.存储芯片

7、 假定下列字符码中有奇偶校验位,但没有数据错误,采用偶校验的字符码就是【 D 】。

A.11001011 B.11010110

次加法需10ns,则补码除法需 时间,补码BOOTH算法最多需要 时间。

5、 CPU从主存取出一条指令并执行该指令的时间

叫 ,它通常包含若干个 ,而后者又包含若干个 。 组成多级时序系统。

二、名词解释(8分)

1、 微程序控制

2、 存储器带宽

3、 RISC

4、 中断隐指令及功能

三、简答(18分)

1、 完整的总线传输周期包括哪几个阶段?简要叙述每个阶段的工作。

4、 某机主存容量为4M×16位,且存储字长等于指令字长,若该机的指令系统具备120种操作。操作码位数固定,且具有直接、间接、立即、相对四种寻址方式。

(1)画出一地址指令格式并指出各字段的作用;

(2)该指令直接寻址的最大范围; (3)一次间址的寻址范围;

(4)相对寻址的寻址范围。

四、(6分)

9设阶码取3位,尾数取6位(均不包括符号位),按浮点补码运算规则 计算 [25

计算机组成原理-期中考试卷

计算机科学与技术系2013—2014学年第二学期期中考试《计算机组成原理》试题适用:计算机科学与技术命题人:****审核人:一、选择题(每小题2分,共20分)1、目前我们所说的个人台式商用机属于______。

A.巨型机B.中型机C.小型机D.微型机2、EPROM是指______。

A. 读写存储器B. 只读存储器C. 可编程的只读存储器D. 光擦除可编程的只读存储器3、信息只用一条传输线,且采用脉冲传输的方式称为______。

A.串行传输B.并行传输C.并串行传输D.分时传输4、下列______属于应用软件。

A. 操作系统B. 编译系统C. 连接程序D.文本处理5、计算机内存储器可以采用______。

A.RAM和ROMB.只有ROMC.只有RAMD.RAM和SAM6、一个256K×8的存储器,其地址线和数据线总和为______。

A.16B.18C.26D.207、存储单元是指______。

A.存放一个机器字的所有存储元B.存放一个二进制信息位的存储元C.存放一个字节的所有存储元的集合D.存放两个字节的所有存储元的集合8、当采用______对设备进行编址情况下,不需要专门的I/O指令组。

A.统一编址法B.单独编址法C.两者都是D.两者都不是9、下面有关“中断”的叙述,______是不正确的。

A. 一旦有中断请求出现,CPU立即停止当前指令的执行,转而去受理中断请求B. CPU响应中断时暂停运行当前程序,自动转移到中断服务程序C.中断方式一般适用于随机出现的服务D.为了保证中断服务程序执行完毕以后,能正确返回到被中断的断点继续执行程序,必须进行现场保护操作10、DMA方式中,周期窃取是窃取一个______。

A.存取周期B.指令周期C.CPU周期D.总线周期二、判断题(每小题2分,共10分)1、CPU只是计算机的控制器。

2、Cache是内存的一部分,它可由指令直接访问。

3、数据总线用来传输各种功能部件之间的数据信息,它是双向传输总线,其位数与机器字长有关。

计算机组成原理期中考试题整理

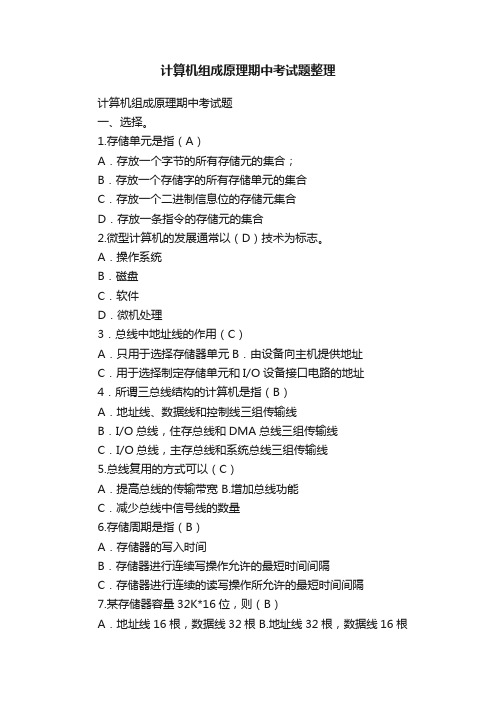

计算机组成原理期中考试题整理计算机组成原理期中考试题一、选择。

1.存储单元是指(A)A.存放一个字节的所有存储元的集合;B.存放一个存储字的所有存储单元的集合C.存放一个二进制信息位的存储元集合D.存放一条指令的存储元的集合2.微型计算机的发展通常以(D)技术为标志。

A.操作系统B.磁盘C.软件D.微机处理3.总线中地址线的作用(C)A.只用于选择存储器单元B.由设备向主机提供地址C.用于选择制定存储单元和I/O设备接口电路的地址4.所谓三总线结构的计算机是指(B)A.地址线、数据线和控制线三组传输线B.I/O总线,住存总线和DMA总线三组传输线C.I/O总线,主存总线和系统总线三组传输线5.总线复用的方式可以(C)A.提高总线的传输带宽 B.增加总线功能C.减少总线中信号线的数量6.存储周期是指(B)A.存储器的写入时间B.存储器进行连续写操作允许的最短时间间隔C.存储器进行连续的读写操作所允许的最短时间间隔7.某存储器容量32K*16位,则(B)A.地址线16根,数据线32根 B.地址线32根,数据线16根C.地址线15根,数据线16根8.一个四体并行低位交叉存储器,每个模块的容量是64K*32位,存储周期为200ns,在下列说法中(B)是正确的。

A.在200ns内,存储器能向CPU提供256位二进制信息B.在200ns内,存储器能向CPU提供128位二进制信息C.50ns内,每个模块能向CPU提供32位二进制信息9.下列器件中存取速度最快的是(C)A.Cache B.主存 C.寄存器10.设计器字长为64位,存储容量为128MB,若按字编址,它的寻址范围是(B)A.16MB B。

16M C。

32M11.在下列因素中,与Cache的命中率无关的是(C)A.Cache块的大小 B.Cache的容量 C.主存的存取时间12.磁盘的盘面上有很多半径不同的同心圆,这些同心圆称为(B)A.扇区 B.磁道 C.磁柱13.Cache的地址映像中,若主存中的任一块均可映射到Cache内任一块的位置上,称作(B)A.直接映射 B.全相联映射 C.组相联映射14.微型机系统中,主机和高速硬盘进行数据交换一般采用(C)方式。

13-14(1)计算机组成原理期中考试参考答案

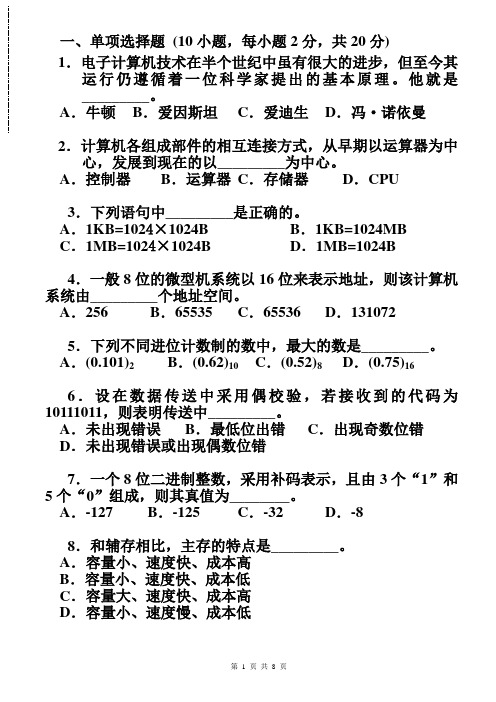

一、单项选择题(10小题,每小题2分,共20分)1.电子计算机技术在半个世纪中虽有很大的进步,但至今其运行仍遵循着一位科学家提出的基本原理。

他就是_________。

A.牛顿B.爱因斯坦C.爱迪生D.冯·诺依曼2.计算机各组成部件的相互连接方式,从早期以运算器为中心,发展到现在的以_________为中心。

A.控制器B.运算器C.存储器D.CPU3.下列语句中_________是正确的。

A.1KB=1024×1024B B.1KB=1024MBC.1MB=1024×1024B D.1MB=1024B4.一般8位的微型机系统以16位来表示地址,则该计算机系统由_________个地址空间。

A.256 B.65535 C.65536 D.1310725.下列不同进位计数制的数中,最大的数是_________。

A.(0.101)2 B.(0.62)10C.(0.52)8D.(0.75)166.设在数据传送中采用偶校验,若接收到的代码为10111011,则表明传送中_________。

A.未出现错误B.最低位出错C.出现奇数位错D.未出现错误或出现偶数位错7.一个8位二进制整数,采用补码表示,且由3个“1”和5个“0”组成,则其真值为________。

A.-127 B.-125 C.-32 D.-88.和辅存相比,主存的特点是_________。

A.容量小、速度快、成本高B.容量小、速度快、成本低C.容量大、速度快、成本高D.容量小、速度慢、成本低9.相联存储器与传统存储器的主要区别是前者又叫按_________寻址的存储器。

A.地址B.内容C.堆栈D.变址10.某计算机字长16位,它的存储容量是1MB,按字编址,它的寻址范围是_________。

A.512K B.1M C.512KB D.1MB二、判断题(10小题,每小题1分,共10分)√1.程序员编程所用的地址叫做逻辑地址。

计算机组成原理 期中测试卷

填空题:1.在三种集中式总线控制中,方式响应时间最快。

2.三种集中式总线控制中,方式对电路故障最敏感。

3.连接计算机与计算机之间的总线属于总线4.在计数器定时查询方式下,若每次计数从上一次计数的终止点开始,则设备的优先级5. 系统总线中的数据线、地址线和控制线是根据区分的。

6.CPU主要包括选择题1.计算机使用总线结构便于增减外设,同时---------- ()A.减少了信息传输量B.提高了信息的传输速度C*减少了信息传输线的条数2.总线中地址线的作用是A*只用于选择存储器单元B.由设备向主机提供地址C.用于选择指定存储器单元和I/0设备接口电路的地址3.在计数器定时查询方式下,若计数从0开始A.设备号小的优先级高B.每个设备使用总线的机会相等C.设备号大的优先级高总线4.在独立请求方式下,若有N个设备,则A.有一个总线请求信号和一个总线响应信号B.有N 个总线请求信号和N个总线响应信号C.有一个总线请求信号和N个总线响应信号5.在链式查询方式下,若有N个设备,则A.有N条总线请求线B.无法确定有几条总线请求线C.只有一条总线请求线6.总线通信中的同步控制是A.只适合于CPU控制的方式B.由统一时序控制的方式C.只适合于外围设备控制的方式7.在同步通信中,一个总线周期的传输过程是A先传送数据,再传输地址B.先传送地址,再传输数据C.只传输数据8.总线中数据传导和地址信号分别用A.串行传输B.并行传输C.复用传输来划分的。

9.总线复用方式可以A提高总线的传输带宽B.增加总线的功能C.减少总线中信号线的数量10.总线的异步通信方式。

A.不采用时钟信号,只采用握手信号这种总线传输方式是——传输B.既采用时钟信号,又采用握手信号C.既不采用时钟信号,又不采用握手信号1.什么是总线判优?为什么需要总线判优?2.什么是总线通信控制?为什么需要总线通信控制? 3.异步通信与同步通信的主要区别是什么,说明通信双方如何联络。

计算机组成原理期中考试试题

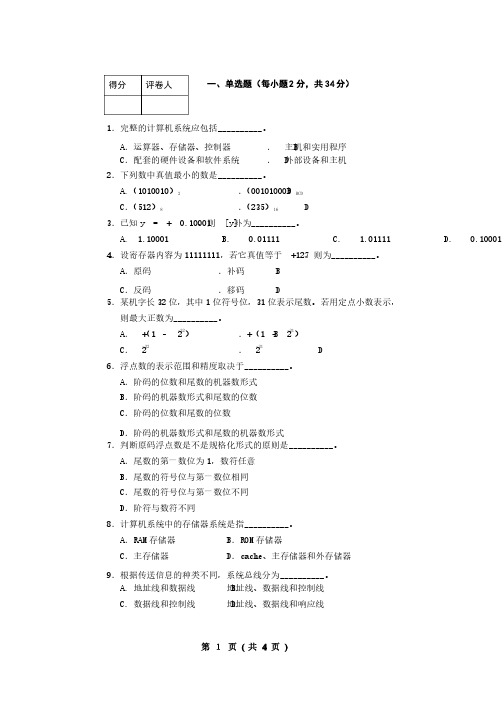

第 1 页 ( 共 4 页 )一、单选题(每小题2分,共34分)1.完整的计算机系统应包括.完整的计算机系统应包括______________________________。

A .运算器、存储器、控制器.运算器、存储器、控制器B B . 主机和实用程序主机和实用程序主机和实用程序C .配套的硬件设备和软件系统.配套的硬件设备和软件系统D D . 外部设备和主机外部设备和主机外部设备和主机2.下列数中真值最小的数是.下列数中真值最小的数是______________________________。

A.A.((10100101010010))2 B .(0010100000101000))BCDC .(512512))8D .(235235))163.已知y = + 0.10001,则,则 [y] [y]补为补为补为______________________________。

A. 1.10001B. 0.01111C. 1.01111D. 0.100014.设寄存器内容为1111111111111111,若它真值等于,若它真值等于,若它真值等于 +127 +127,则为,则为,则为______________________________。

A .原码.原码B B .补码.补码C .反码.反码D D .移码.移码5.某机字长32位,其中1位符号位,位符号位,3131位表示尾数。

若用定点小数表示,则最大正数为则最大正数为______________________________。

A . +(1 – 2-32)B .+(1 – 2-31)C . 2-32D . 2-316.浮点数的表示范围和精度取决于.浮点数的表示范围和精度取决于______________________________。

A .阶码的位数和尾数的机器数形式.阶码的位数和尾数的机器数形式B .阶码的机器数形式和尾数的位数.阶码的机器数形式和尾数的位数C .阶码的位数和尾数的位数.阶码的位数和尾数的位数D .阶码的机器数形式和尾数的机器数形式.阶码的机器数形式和尾数的机器数形式7.判断原码浮点数是不是规格化形式的原则是.判断原码浮点数是不是规格化形式的原则是______________________________。

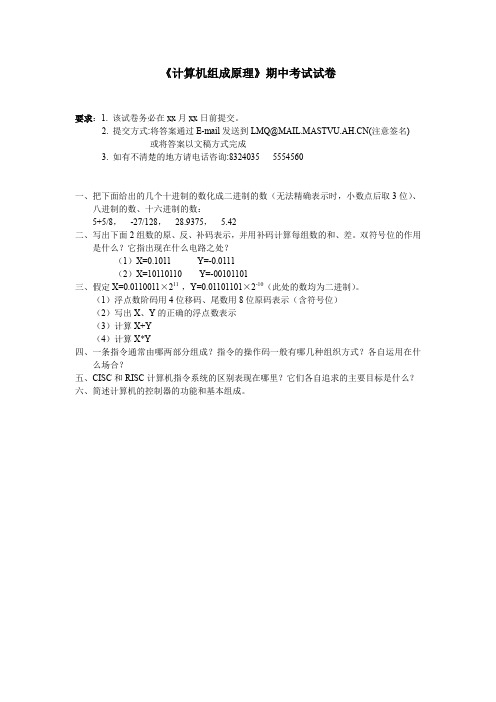

《计算机组成原理》期中考试试卷.

《计算机组成原理》期中考试试卷

要求:1. 该试卷务必在xx月xx日前提交。

2. 提交方式:将答案通过E-mail发送到LMQ@(注意签名)

或将答案以文稿方式完成

3. 如有不清楚的地方请电话咨询:8324035 5554560

一、把下面给出的几个十进制的数化成二进制的数(无法精确表示时,小数点后取3位)、

八进制的数、十六进制的数:

5+5/8,-27/128,28.9375, 5.42

二、写出下面2组数的原、反、补码表示,并用补码计算每组数的和、差。

双符号位的作用

是什么?它指出现在什么电路之处?

(1)X=0.1011 Y=-0.0111

(2)X=10110110 Y=-00101101

三、假定X=0.0110011×211 ,Y=0.01101101×2-10(此处的数均为二进制)。

(1)浮点数阶码用4位移码、尾数用8位原码表示(含符号位)

(2)写出X、Y的正确的浮点数表示

(3)计算X+Y

(4)计算X*Y

四、一条指令通常由哪两部分组成?指令的操作码一般有哪几种组织方式?各自运用在什

么场合?

五、CISC和RISC计算机指令系统的区别表现在哪里?它们各自追求的主要目标是什么?

六、简述计算机的控制器的功能和基本组成。

计算机组成原理期中考卷

A 32,8

B 15,8 C 16,8 D 8,8 。

二、填空题(本题共 8 小题,每空 1 分,共 25 分)

1. 直接使用西文键盘输入汉字,进行处理,并显示打印汉字,是一项重大成就。为此要解决汉字的(A )编码, 汉字(B ),( C )码等三种不同用途的编码。 2. 光盘是多媒体计算机不可缺少的外存设备。按读写性质分,光盘有(A ),(B ),( C )型三类光盘。 3. 存储器的读出时间通常称为( A ) ,它定义为( B ).为便于读写控制,存储器设计时写入时间和读出时间 相等,但事实上写入时间( C )读出时间。 4. 形成操作数地址的方式,称为( A )方式,操作数可放在( B )寄存器, ( C )寄存器,内存和指令中。 5. 层次化的存储器系统一般分为三级: ( A ) 、 ( B ) 、 ( C ) 。 6. cache 是一种( A )存储器,是为了解决 CPU 和主存之间( B )不匹配而采用的一项重要技术。它与主存 的替换算法有( C) 、 ( D ) 、 ( E ) 。 7. 指令操作码字段表征指令的( A ) ,而地址码字段指示( B ) 。 8. 移码表示法主要用于表示(A)数的阶码,以便于比较两个(B).的大小和(C)操作。

七、分析题一(本题 6 分)

某机字长 16 位,CPU 地址总线 18 位,数据总线 16 位,存储器按字编址。试问: (1) (1 分)该机可以配备的最大主存容量为多少? (2) (2 分)该机主存采用 64k×1 位的 DRAM 芯片(内部为 4 个 128×128 阵列)构成最大主存空间,则共需要多 少个芯片;若采用异步刷新方式,单元刷新间隔为 2ms,则刷新信号的周期为多少? (3) (3 分)若为该机配备 2K×16 位的 Cache,每块 8B,采用 2 路组相联映射方式,试写出对主存地址各个字段的 划分(标出各个字段的位数) ;若主存地址为 462EH,则该地址可映射到 Cache 的哪一个组?

计算机组成原理期中试题

计算机组成原理期中试题一、选择题(每题2分,共20分)1.在机器数___中,零的表示形式是唯一的。

A. 原码B.补码C. 补码和移码D. 原码和反码2.CRT的分辨率为1024×1024像素,像素的颜色数为256。

则刷新存储器的容量是___。

A. 512KB B.1MB C. 256KB D. 2MB3.某DRAM芯片,其存储容量为512K×8位,该芯片的地址线和数据线的数目是___。

A. 8, 512 B. 512, 8 C. 18, 8 D. 194. 计算机系统中的存贮器系统是指______。

A RAM存贮器B ROM存贮器C 主存贮器D cache、主存贮器和外存贮器5. 存储单元是指______。

A 存放一个二进制信息位的存贮元B 存放一个机器字的所有存贮元集合C 存放一个字节的所有存贮元集合D 存放两个字节的所有存贮元集合6. 计算机使用总线结构的主要优点是便于实现积木化,同时______。

A 减少了信息传输量B 提高了信息传输的速度C 减少了信息传输线的条数D 加重了CPU的工作量7. CPU响应中断的时间是___C__。

A 中断源提出请求B 取指周期结束C 执行周期结束D 间址周期结束8. 总线通信中的同步控制是__B____。

A.只适合于CPU控制的方式; B.由统一时序控制的方式;C.只适合于外围设备控制的方式; D.只适合于主存。

9. 某计算机字长是 16 位,它的存储容量是1MB,按字编址,它的寻址范围是___ __。

A.512K; B.1M; C.512KB; D.1MB。

10. 中断向量可提供_ ____。

A.被选中设备的地址; B.传送数据的起始地址;C.中断服务程序入口地址; D.主程序的断点地址。

二、填空题(每空2分,共20分)1. 直接使用西文键盘输入汉字,进行处理,并显示打印汉字,是一项重大成就。

为此要解决汉字的____①____编码,汉字___②____, __③__码等三种不同用途的编码2. 磁盘上常用的记录方式可分为归零制、不归零制,___④_____制,___⑤____制等多种类型。

期中试卷

《计算机组成原理》期中试卷 学号 姓名 分数一、填空题(本大题共10个空,每空2分,共20分)1、 计算机系统的软件可分为 软件和 软件,汇编程序属于前者。

2、 Plug and Play 的含义是 。

总线标准具有这种功能。

3、 总线 技术是指不同信号(如地址信号和数据信号)共用同一组物理线路,分时使用。

此时需要配置相应的电路。

4、 用1K ×4位的存储芯片组成容量为64K ×8位的存储器,共需 片,若将这些芯片分装在几块板上,设每块板的容量为16K ×8位,则该存储器所需要的地址码总位数是 ,其中 位用于选板。

5、 已知[]n 210x ...x .x x =补x ,则[]=-补x 。

6、 一个总线传输周期包括申请分配阶段、寻址阶段、 和结束阶段四个阶段。

二、选择题(本大题共10小题,每小题3分,共30分)1、电子计算机问世至今,新型机器不断推陈出新,不管怎么更新,依然保留“存储程序”的概念,最早提出这种概念的是______。

A .巴贝奇(Charles Babage )B .冯.诺依曼(Join von Neumann )C .帕斯卡(Blaise Pascal )D .贝尔(Bell )2、用以指定待执行指令所在地址是______。

A .指令寄存器 B .数据计数器C .程序计数器 D .累加器3、由0、1代码组成的语言称为______。

A .汇编语言B .人工语言C .机器语言D .高级语言 4、存储字长是指_______。

A .存放在一个存储单元中的二进制代码的组合B .存放在一个存储单元中的二进制代码的位数C .存储单元的个数D .机器指令的位数 5、设寄存器位数为8位,机器数采用补码形式(含一位符号位),对应于十进制数-27,寄存器内容为______。

A .27HB .9BHC .E5HD .7FH6、在小数定点机中,下述第____种说法正确。

A .只有补码能表示-1B .只有原码不能表示-1C .只有反码能表示-1D .三中机器数均不能表示-17、海明码具有以下第_____种能力。

计算机组成原理题期中试题

一、(10分)将数(-0.75)10转换成754标准的32位浮点数的二进制存储格式。

二、(10分)设有两个十进制数:x=-0.875×21,y=0.625×22,(1)将x,y的尾数转换为二进制补码形式。

(2)设阶码2位,阶符1位,数符1位,尾数3位,通过补码运算规则求出z=x–y 的二进制浮点规格化结果。

三、(10分)某加法器进位链小组信号为C4、C3、C2、C1,低位来的进位信号为C0,请分别按下述两种方式写出C4、C3、C2、C1、的逻辑表达式。

(1)串行进位方式(2)并行进位方式四、(10分)设存储器容量为4M字,字长32位,模块数m = 4,分别用顺序方式和交叉方式进行组织,存储周期T = 200ns,数据总线宽度32位,总线传送周期 = 50ns.问顺序存储器和交叉存储器带宽各是多少?五、(10分)CPU执行一段程序时,cache 完成存取的次数为1900次,主存完成存取的次数为100次,已知cache存取周期为50ns,主存存取周期为250ns.求:(1)cache/主存系统的效率。

(2)平均访问时间。

六、(10分)某机器中,配有一个ROM芯片,地址空间0000H—3FFFH。

现在再用几个16K×8的芯片构成一个32K×8的RAM 区域,使其地址空间为8000H—FFFFH。

假设此RAM芯片有CS和WE信号控制端。

CPU地址总线为A15—A0,数据总线为D7—D0,控制信号为RD(读),WR(写),MREQ(存储器请求),当且仅当MREQ和RD(或WR)同时有效时,CPU才能对有存储器进行读(或写),试画出此CPU与上述ROM芯片和RAM芯片的连接图。

七.(20分)一台处理机具有如下指令格式:2位6位3位3位格式表明有8个通用寄存器(长度16位),X指定寻址模式,主存实际容量为256K字。

(1)假设不用通用寄存器也能直接访问主存中的每一个单元,并假设操作码域OP=6位,请问地址码域应分配多少位?指令字长度应有多少位?(2)假设X=11时,指定的那个通用寄存器用做基址寄存器,请提出一个硬件设计规划,使得被指定的通用寄存器能访问1M主存空间中的每一个单元。

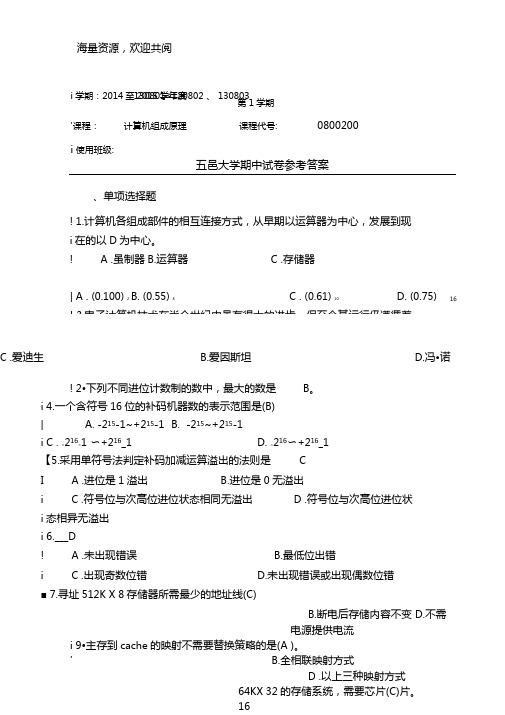

计算机组成原理-期中测试题参考答案,

海量资源,欢迎共阅i 学期:2014至2015学年度 第1学期 '课程:计算机组成原理课程代号:0800200i 使用班级:130801~120802 、 130803| A . (0.100) 2B . (0.55) 8C . (0.61)10D . (0.75)! 3.电子计算机技术在半个世纪中虽有很大的进步,但至今其运行仍遵循着B .爱因斯坦C .爱迪生 16D .冯•诺B .断电后存储内容不变 D .不需电源提供电流i 9•主存到cache 的映射不需要替换策略的是(A )。

' B.全相联映射方式D .以上三种映射方式64KX 32的存储系统,需要芯片(C )片。

16五邑大学期中试卷参考答案、单项选择题! 1.计算机各组成部件的相互连接方式,从早期以运算器为中心,发展到现 i 在的以D 为中心。

!A .虽制器B .运算器C .存储器! 2•下列不同进位计数制的数中,最大的数是 B 。

i 4.一个含符号16位的补码机器数的表示范围是(B ) |A. -215-1~+215-1B. -215~+215-1i C . -216-1 〜+216_1 D. -216〜+216_1【5.采用单符号法判定补码加减运算溢出的法则是CI A .进位是1溢出B .进位是0无溢出iC .符号位与次高位进位状态相同无溢出D .符号位与次高位进位状i 态相异无溢出 i 6.___D ! A .未出现错误 B .最低位出错iC .出现奇数位错D .未出现错误或出现偶数位错■ 7.寻址512K X 8存储器所需最少的地址线(C )! A. 9 B . 11i C . 19 D . 21| 8.静态RAM的特点是________ Ci A.工作时存储内容不变! C .不需刷新■ A .直接映射方式! C .组相联映射方式i 10.用8KX 8存储芯片组成一个! A. 8 B.i C. 32 D. 64i二、判断题I■ 1 .上由许多部件组成,其核心部分是算术逻辑运算单元(ALU )。

期中测试题答案

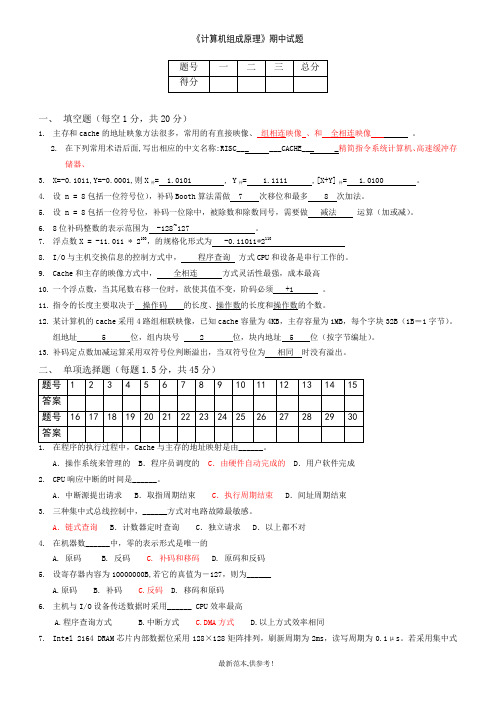

《计算机组成原理》期中试题一、填空题(每空1分,共20分)1.主存和cache的地址映象方法很多,常用的有直接映像、组相连映像、和全相连映像。

2.在下列常用术语后面,写出相应的中文名称:RISC___ ___CACHE___ _精简指令系统计算机、高速缓冲存储器、3.X=-0.1011,Y=-0.0001,则X补= 1.0101 , Y补= 1.1111 ,[X+Y]补= 1.0100 。

4.设 n = 8包括一位符号位),补码Booth算法需做 7 次移位和最多 8 次加法。

5.设 n = 8包括一位符号位,补码一位除中,被除数和除数同号,需要做减法运算(加或减)。

6.8位补码整数的表示范围为-128~127 。

7.浮点数X = -11.011 * 2100,的规格化形式为 -0.11011*21108.I/O与主机交换信息的控制方式中,程序查询方式CPU和设备是串行工作的。

9.Cache和主存的映像方式中,全相连方式灵活性最强,成本最高10.一个浮点数,当其尾数右移一位时,欲使其值不变,阶码必须 +1 。

11.指令的长度主要取决于操作码的长度、操作数的长度和操作数的个数。

12.某计算机的cache采用4路组相联映像,已知cache容量为4KB,主存容量为1MB,每个字块32B(1B=1字节)。

组地址 5 位,组内块号 2 位,块内地址 5 位(按字节编址)。

13.补码定点数加减运算采用双符号位判断溢出,当双符号位为相同时没有溢出。

二、单项选择题(每题1.5分,共45分)A.操作系统来管理的 B.程序员调度的 C.由硬件自动完成的 D.用户软件完成2.CPU响应中断的时间是______。

A.中断源提出请求 B.取指周期结束 C.执行周期结束 D.间址周期结束3.三种集中式总线控制中,______方式对电路故障最敏感。

A.链式查询 B.计数器定时查询 C.独立请求 D.以上都不对4.在机器数______中,零的表示形式是唯一的A. 原码B. 反码C. 补码和移码D. 原码和反码5.设寄存器内容为10000000B,若它的真值为-127,则为______A.原码B. 补码C.反码D. 移码和原码6.主机与I/O设备传送数据时采用______ CPU效率最高A.程序查询方式B.中断方式C.DMA方式D.以上方式效率相同7.Intel 2164 DRAM芯片内部数据位采用128×128矩阵排列,刷新周期为2ms,读写周期为0.1μs。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

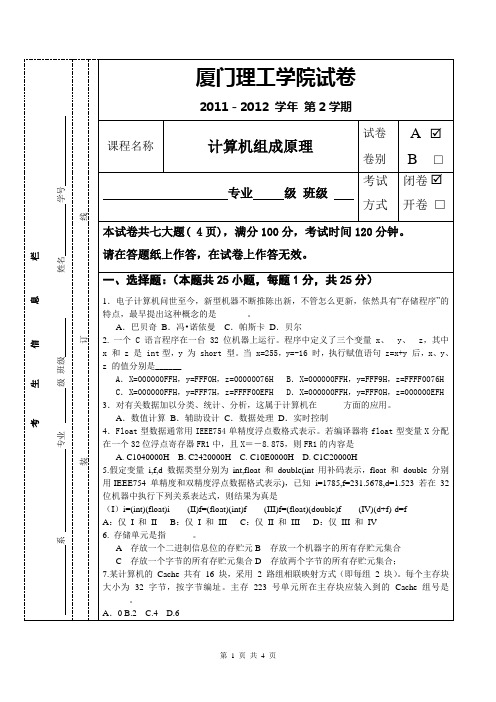

计算机科学与技术系

2013—2014学年第二学期期中考试

《计算机组成原理》试题

适用:计算机科学与技术命题人:****

审核人:

一、选择题(每小题2分,共20分)

1、目前我们所说的个人台式商用机属于______。

A.巨型机

B.中型机

C.小型机

D.微型机

2、EPROM是指______。

A. 读写存储器

B. 只读存储器

C. 可编程的只读存储器

D. 光擦除可编程的只读存储器

3、信息只用一条传输线,且采用脉冲传输的方式称为______。

A.串行传输

B.并行传输

C.并串行传输

D.分时传输

4、下列______属于应用软件。

A. 操作系统

B. 编译系统

C. 连接程序

D.文本处理

5、计算机内存储器可以采用______。

A.RAM和ROM

B.只有ROM

C.只有RAM

D.RAM和SAM

6、一个256K×8的存储器,其地址线和数据线总和为______。

A.16

B.18

C.26

D.20

7、存储单元是指______。

A.存放一个机器字的所有存储元

B.存放一个二进制信息位的存储元

C.存放一个字节的所有存储元的集合

D.存放两个字节的所有存储元的集合

8、当采用______对设备进行编址情况下,不需要专门的I/O指令组。

A.统一编址法

B.单独编址法

C.两者都是

D.两者都不是

9、下面有关“中断”的叙述,______是不正确的。

A. 一旦有中断请求出现,CPU立即停止当前指令的执行,转而去受理中断

请求

B. CPU响应中断时暂停运行当前程序,自动转移到中断服务程序

C.中断方式一般适用于随机出现的服务

D.为了保证中断服务程序执行完毕以后,能正确返回到被中断的断点继续执

行程序,必须进行现场保护操作

10、DMA方式中,周期窃取是窃取一个______。

A.存取周期

B.指令周期

C.CPU周期

D.总线周期

二、判断题(每小题2分,共10分)

1、CPU只是计算机的控制器。

2、Cache是内存的一部分,它可由指令直接访问。

3、数据总线用来传输各种功能部件之间的数据信息,它是双向传输总线,其

位数与机器字长有关。

4、指令寄存器IR用来存放下一条指令的地址。

5、在中断系统中,所谓“保护现场”就是保护程序计数器PC的内容。

三、填空题(每空1分,共10分)

1、数控机床是计算机在______方面的应用,邮局把信件自动分拣是在计算机

人工智能方面的应用。

2、主存储器的性能指标主要是______、______、存储周期和存储器带宽。

3、Cache与主存的地址映射主要有直接映射及______、______等几种映射方法。

4、一个中断服务程序流程可分为保护现场、______、______和______四个部

分。

5、异步通信的应答方式可分为______、______和全互锁三种类型。

四、 简答计算题(每小题6分,共30分)

1、设总线的时钟频率为8MHZ ,一个总线周期等于一个时钟周期。

如果一个总线周期中并行传送16位数据,试问总线的带宽是多少?

2、什么叫刷新?为什么要刷新?说明刷新有几种方法。

3、简述DMA 接口的功能。

4、在什么条件和什么时间,CPU 可以响应I/O 的中断请求?

5、假设某设备向CPU 传送信息的最高频率是40 000次/秒,而相应的中断处理程序其执行时间为40 s ,试问该外设是否可用程序中断方式与主机交换信息,为什么?

五、 设计题(每小题15分,共30分)

1、假设主存容量为512KB ,Cache 容量为4KB ,每个字块为16个字,每个字32位。

(1)Cache 地址有多少位?可容纳多少块?

(2)主存地址有多少位?可容纳多少块?

(3)在直接映射方式下,主存的第几块映射到Cache 中的第5块(设起始字块为第1块)?

(4)画出直接映射方式下主存地址字段中各段的位数。

2、设CPU 共有16根地址线,8根数据线,并用IO /M 作为访问存储器或I/O 的控制信号(高电平为访存,低电平为访I/O ),WR (低电平有效)为写命令,RD (低电平有效)为读命令。

设计一个容量为64KB 的采用低位交叉编址的8体并行结构存储器。

现有下图所示的存储器芯片和138译码器。

画出CPU 和存储器芯片(芯片容量自定)的连接图,并写出图中每个存储芯片的地址范围(用十六进制数表示)。

RAM OE WE CE ......Ai A0Dn D0 ┇ Y 7 G 1 G 2A G 2B C B A

74138译码器 Y 6 Y 0。