MC-428LFH641中文资料

MC2410 用户手册说明书

SinoMCU RF 2.4G射频传输专用芯片MC2410用户手册V1.0目录1产品概要 (3)2产品特性 (3)3模块框图 (4)4端口定义 (4)4.1引脚排列 (4)4.2端口说明 (5)5电气特性 (6)6典型应用 (8)7SPI接口 (9)7.1SPI默认格式 (9)7.2SPI时序要求 (10)8发送/接收流程 (11)8.1RF初始化 (11)8.2短包发送/接收流程 (11)8.3长包发送/接收流程 (12)8.4进入IDLE模式流程 (13)8.5进入SLEEP模式流程 (13)8.6SLEEP唤醒 (13)8.7扫描RSSI流程 (13)8.8250K传输数据率的附加流程 (13)9寄存器信息 (15)10数据包格式 (19)11电源要求 (19)12发射功率的调整 (20)13ESOP8封装功能说明 (20)13.1MCU通讯接口 (20)13.2射频性能 (20)14应用注意事项 (21)14.1IO电压 (21)14.2CE管脚 (21)14.3POR (21)14.4状态转换 (21)14.5同步字使用注意事项 (22)15封装尺寸 (23)15.1SOP16 (23)15.2ESOP8 (23)16修订记录 (24)1产品概要本产品是一款低成本,高集成度的2.4GHz的无线收发芯片,片上集成发射机、接收机、频率综合器和GFSK调制解调器,具有高灵敏度、低功耗以及抗干扰能力强的优点,可适用于无线遥控、无线键鼠、无线通讯以及工业控制等领域。

片上的发射接收FIFO寄存器可以和MCU进行通信,存储数据,然后以1Mbps或250Kbps数据率在空中传输。

内置了CRC、FEC、Auto ACK和自动重传机制,可以大大简化系统设计并优化性能。

同时外围电路简单,只需搭配MCU以及少数外围被动元件。

为了提高电池使用寿命,芯片在各个环节都降低功耗,芯片最低工作电压可以到1.9V,最低睡眠模式电流小于1μA。

MC-428LFF721中文资料

©1996MOS INTEGRATED CIRCUITMC-428LFF7213.3 V OPERATION 8M-WORD BY 72-BIT DYNAMIC RAM MODULEUNBUFFERED TYPE, EDODATA SHEETThe mark Z shows major revised points.Document No. M11912EJ3V0DS00 (3rd edition)Date Published October 1997 NS Printed in JapanThe information in this document is subject to change without notice.DescriptionThe MC-428LFF721 is a 8,388,608 words by 72 bits dynamic RAM module on which 9 pieces of 64M DRAM :µPD4264805 are assembled.This module provides high density and large quantities of memory in a small space without utilizing the surface-mounting technology on the printed circuit board.Decoupling capacitors are mounted on power supply line for noise reduction.Features• Unbuffered type • EDO (Hyper page mode)• 8,388,608 words by 72 bits organization • Fast access and cycle timeFamilyAccess time R/W cycle timeEDO (Hyper page mode)Power consumption (MAX.)(MAX.)(MIN.)cycle time (MIN.)Active Standby MC-428LFF721-A5050 ns 84 ns 20 ns 3.40 W 16.2 mW MC-428LFF721-A6060 ns104 ns25 ns3.08 W(CMOS level input)• Refresh cycleFamilyRefresh cycleRefreshMC-428LFF721-A508,192 cycles / 64 ms /RAS only refresh, Normal read / write MC-428LFF721-A604,096 cycles / 64 ms/CAS before /RAS refresh, Hidden refresh• 168-pin dual in-line memory module (Pin pitch = 1.27 mm)• Single +3.3 V ± 0.3 V power supply • Serial PD2Ordering InformationPart numberAccess time (MAX.)PackageMounted devicesMC-428LFF721FH-A5050 ns 168-pin Dual In-line Memory Module (Socket Type)9 pieces of µPD4264805G5(400 mil TSOP(II))MC-428LFF721FH-A6060 ns Edge connector : Gold plated[Single side]MC-428LFF721FB-A5050 ns 9 pieces of µPD4264805LE(400 mil SOJ)MC-428LFF721FB-A6060 ns[Single side]3Pin Configuration168-pin Dual In-line Memory Module Socket Type (Edge connector: Gold plated)[ MC-428LFF721FH, 428LFF721FB ]858687888990919293949596979899100101102103104105106107108109110111112113114115116117118119120121122123124125126127128129130131132133134135136137138139140141142143144145146147148149150151152153154155156157158159160161162163164165166167168GND DQ 32DQ 33DQ 34DQ 35Vcc DQ 36DQ 37DQ 38DQ 39DQ 40GND DQ 41DQ 42DQ 43DQ 44DQ 45Vcc DQ 46DQ 47CB4CB5GND NC NC Vcc NC /CAS4/CAS5NC NC GND A1A3A5A7A9A11NC Vcc NC NC GND NC NC /CAS6/CAS7NC Vcc NC NC CB6CB7GND DQ 48DQ 49DQ 50DQ 51Vcc DQ 52NC NC NC GND DQ 53DQ 54DQ 55GND DQ 56DQ 57DQ 58DQ 59Vcc DQ 60DQ 61DQ 62DQ 63GND NC NC SA0SA1SA2Vcc123456789101112131415161718192021222324252627282930313233343536373839404142434445464748495051525354555657585960616263646566676869707172737475767778798081828384GND DQ 0DQ 1DQ 2DQ 3Vcc DQ 4DQ 5DQ 6DQ 7DQ 8GND DQ 9DQ 10DQ 11DQ 12DQ 13Vcc DQ 14DQ 15CB0CB1GND NC NC Vcc /WE0/CAS0/CAS1/RAS0/OE0GND A0A2A4A6A8A10A12Vcc Vcc NC GND /OE2/RAS2/CAS2/CAS3/WE2Vcc NC NC CB2CB3GND DQ 16DQ 17DQ 18DQ 19Vcc DQ 20NC NC NC GND DQ 21DQ 22DQ 23GND DQ 24DQ 25DQ 26DQ 27Vcc DQ 28DQ 29DQ 30DQ 31GND NC NC NC SDA SCL VccA0 - A12: Address Inputs [ Row : A0 - A12, Column : A0 - A9 ]DQ0 - DQ63: Data Inputs / Outputs/RAS0, /RAS2: Row Address Strobe /CAS0 - /CAS7: Column Address Strobe /WE0, /WE2: Write Enable /OE0, /OE2: Output Enable SDA : Serial Data I/O for PD SCL : Clock Input for PD SA0 - SA2: Address Input for EEPROM CB0 - CB7: Check Bits V CC : Power Supply GND : Ground NC: No Connection/XXX indicates active low signal.4Block DiagramRemark D0 - D8 : µPD4264805 (8M words by 8 bits organization)/CAS0/WE0/OE0/RAS0/CAS4/WE2/OE2/RAS2/CAS D0/RAS/WE /OE DQ 1DQ 2DQ 3DQ 4DQ 5DQ 6DQ 7DQ 8D1DQ 0DQ 1DQ 2DQ 3DQ 4DQ 5DQ 6DQ 7D2DQ 16DQ 17DQ 18DQ 19DQ 20DQ 21DQ 22DQ 23D3DQ 24DQ 25DQ 26DQ 27DQ 28DQ 29DQ 30DQ 31D4D7DQ 56DQ 57DQ 58DQ 59DQ 60DQ 61DQ 62DQ 63D8D6DQ 48DQ 49DQ 50DQ 51DQ 52DQ 53DQ 54DQ 55D5DQ 40DQ 41DQ 42DQ 43DQ 44DQ 45DQ 46DQ 47CB 0CB 1CB 2CB 3CB 4CB 5CB 6CB 7DQ 32DQ 33DQ 34DQ 35DQ 36DQ 37DQ 38DQ 39A0 - A12A0 - A12 : D0 - D8V CC D0 - D8GNDD0 - D8SERIAL PDSCLSDAA0A1A2SA0SA1SA2/CAS1/CAS2/CAS3/CAS7/CAS6/CAS5DQ 8DQ 9DQ 10DQ 11DQ 12DQ 13DQ 14DQ 15DQ 0DQ 1DQ 2DQ 3DQ 4DQ 5DQ 6DQ 7DQ 0DQ 1DQ 2DQ 3DQ 4DQ 5DQ 6DQ 7DQ 0DQ 1DQ 2DQ 3DQ 4DQ 5DQ 6DQ 7DQ 0DQ 1DQ 2DQ 3DQ 4DQ 5DQ 6DQ 7DQ 0DQ 1DQ 2DQ 3DQ 4DQ 5DQ 6DQ 7DQ 0DQ 1DQ 2DQ 3DQ 4DQ 5DQ 6DQ 7DQ 0DQ 1DQ 2DQ 3DQ 4DQ 5DQ 6DQ 7/CAS/RAS/WE /OE /CAS/RAS/WE /OE /CAS/RAS/WE /OE /CAS/RAS/WE /OE/CAS/RAS/WE /OE /CAS/RAS/WE /OE /CAS/RAS/WE /OE/CAS/RAS/WE /OEDQ 0DQ 1DQ 2DQ 3DQ 4DQ 5DQ 6DQ 7Electrical Specifications• All voltages are referenced to GND.• After power up (V CC≥ V CC (MIN.)), wait more than 100 µs (/RAS, /CAS inactive) and then, execute eight /CAS before /RAS or /RAS only refresh cycles as dummy cycles to initialize internal circuit.Absolute Maximum RatingsParameter Symbol Condition Rating Unit Voltage on any pin relative to GND V T−0.5 to +4.6V Supply voltage V CC−0.5 to +4.6V Output current I O50mA Power dissipation P D9W Operating ambient temperature T A0 to +70°C Storage temperature T stg−55 to +125°C Caution Exposing the device to stress above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational section of this specification. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.Recommended Operating ConditionsParameter Symbol Condition MIN.TYP.MAX.Unit Supply voltage V CC 3.0 3.3 3.6V High level input voltage V IH 2.0V CC + 0.3VLow level input voltage V IL−0.3+0.8V Operating ambient temperature T A070°CCapacitance (T A = 25 °C, f = 1 MHz)Parameter Symbol Test condition MIN.TYP.MAX.Unit Input capacitance C I1A0 - A1290pFC I2/RAS0, /RAS250C I3/CAS0 - /CAS735C I4/WE0, /WE250C I5/OE0, /OE250Data input / output capacitance C I/O DQ0 - DQ63, CB0 - CB730pF5DC Characteristics (Recommended Operating Conditions unless otherwise noted)Parameter Symbol Test condition MIN.MAX.Unit Notes Operating current I CC1/RAS, /CAS cycling t RAC = 50 ns945mA1, 2, 3t RC = t RC (MIN.), I O = 0 mA t RAC = 60 ns855Standby current I CC2/RAS, /CAS ≥ V IH (MIN.), I O = 0 mA9.0mA/RAS, /CAS ≥ V CC−0.2 V, I O = 0 mA 4.5/RAS only refresh current I CC3/RAS cycling, /CAS ≥ V IH (MIN.)t RAC = 50 ns945mA1, 2, 3 ,4t RC = t RC (MIN.), I O = 0 mA t RAC = 60 ns855Operating current I CC4/RAS ≤ V IL (MAX.), /CAS cycling t RAC = 50 ns945mA1, 2, 5 (Hyper page mode (EDO))t HPC = t HPC (MIN.), I O = 0 mA t RAC = 60 ns855/CAS before /RAS I CC5/RAS cycling t RAC = 50 ns1,215mA1, 2 refresh current t RC = t RC (MIN.), I O = 0 mA t RAC = 60 ns1,035Input leakage current I I (L)V I = 0 to 3.6 V−5+5µAAll other pins not under test = 0 VOutput leakage current I O (L)V O = 0 to 3.6 V−5+5µAOutput is disabled (Hi−Z)High level output voltage V OH I O = −2.0 mA 2.4VLow level output voltage V OL I O = +2.0 mA0.4VNotes1. I CC1, I CC3, I CC4 and I CC5 depend on cycle rates (t RC and t HPC).2. Specified values are obtained with outputs unloaded.3. I CC1 and I CC3 are measured assuming that address can be changed once or less during /RAS≤V IL (MAX.) and/CAS ≥V IH (MIN.).4. I CC3 is measured assuming that all column address inputs are held at either high or low.5. I CC4 is measured assuming that all column address inputs are switched only once during each hyper page(EDO) cycle.67AC Characteristics (Recommended Operating Conditions unless otherwise noted)AC Characteristics Test Conditions(1) Input timing specification(2) Output timing specification(3) Output load conditionV IL (MAX.) = 0.8 VV IH (MIN.) = 2.0 V V OH (MIN.) = 2.0 V V OL (MAX.) = 0.8 Vt T = 2 ns t T = 2 nsI/O870100 pF 1,180V CC C LCommon to Read, Write, Read Modify Write CycleParameter Symbol t RAC = 50 ns t RAC = 60 ns Unit NotesMIN.MAX.MIN.MAX.Read / Write cycle time t RC84−104−ns/RAS precharge time t RP30−40−ns/CAS precharge time t CPN7−10−ns/RAS pulse width t RAS5010,0006010,000ns/CAS pulse width t CAS810,0001010,000ns/RAS hold time t RSH13−15−ns/CAS hold time t CSH38−40−ns/RAS to /CAS delay time t RCD11371445ns1/RAS to column address delay time t RAD9251230ns1/CAS to /RAS precharge time t CRP5−5−ns2 Row address setup time t ASR0−0−nsRow address hold time t RAH7−10−nsColumn address setup time t ASC0−0−nsColumn address hold time t CAH7−10−ns/OE lead time referenced to /RAS t OES0−0−ns/CAS to data setup time t CLZ0−0−ns/OE to data setup time t OLZ0−0−ns/OE to data delay time t OED10−13−nsTransition time (rise and fall)t T150150nsRefresh time t REF−64−64msNotes1.For read cycles, access time is defined as follows:Input conditions Access time Access time from /RASt RAD≤ t RAD (MAX.) and t RCD≤ t RCD (MAX.)t RAC (MAX.)t RAC (MAX.)t RAD > t RAD (MAX.) and t RCD≤ t RCD (MAX.)t AA (MAX.)t RAD + t AA (MAX.)t RCD > t RCD (MAX.)t CAC (MAX.)t RCD + t CAC (MAX.)t RAD (MAX.) and t RCD (MAX.) are specified as reference points only; they are not restrictive operating parameters.They are used to determine which access time (t RAC, t AA or t CAC) is to be used for finding out when output data will be available. Therefore, the input conditions t RAD≥t RAD (MAX.) and t RCD≥t RCD (MAX.) will not cause any operation problems.2.t CRP(MIN.) requirement is applied to /RAS, /CAS cycles.8Parameter Symbol t RAC = 50 ns t RAC = 60 ns Unit NotesMIN.MAX.MIN.MAX.Access time from /RAS t RAC−50−60ns 1 Access time from /CAS t CAC−13−15ns1 Access time from column address t AA−25−30ns1 Access time from /OE t OEA−13−15nsColumn address lead time referenced to /RAS t RAL25−30−nsRead command setup time t RCS0−0−nsRead command hold time referenced to /RAS t RRH0−0−ns2 Read command hold time referenced to /CAS t RCH0−0−ns2 Output buffer turn-off delay time from /OE t OEZ010013ns3/CAS hold time to /OE t CHO5−5−ns4 Notes1.For read cycles, access time is defined as follows:Input conditions Access time Access time from /RASt RAD≤ t RAD (MAX.) and t RCD≤ t RCD (MAX.)t RAC (MAX.)t RAC (MAX.)t RAD > t RAD (MAX.) and t RCD≤ t RCD (MAX.)t AA (MAX.)t RAD + t AA (MAX.)t RCD > t RCD (MAX.)t CAC (MAX.)t RCD + t CAC (MAX.)t RAD (MAX.) and t RCD (MAX.) are specified as reference points only; they are not restrictive operating parameters.They are used to determine which access time (t RAC, t AA or t CAC) is to be used for finding out when output data will be available. Therefore, the input conditions t RAD≥t RAD (MAX.) and t RCD≥t RCD (MAX.) will not cause any operation problems.2.Either t RCH (MIN.) or t RRH (MIN.) should be met in read cycles.3.t OEZ (MAX.) defines the time when the output achieves the condition of Hi-Z and is not referenced to V OH or V OL.4./WE : inactive (in read cycle)/CAS : inactive, /OE : active ...... t CHO is effective./RAS, /OE : active ...... t OCH is effective.9Parameter Symbol t RAC = 50 ns t RAC = 60 ns Unit NotesMIN.MAX.MIN.MAX./WE hold time referenced to /CAS t WCH7−10−ns1/WE pulse width t WP7−10−ns1/WE lead time referenced to /RAS t RWL13−15−ns/WE lead time referenced to /CAS t CWL7−10−ns/WE setup time t WCS0−0−ns2/OE hold time t OEH0−0−nsData-in setup time t DS0−0−ns3 Data-in hold time t DH7−10−ns3 Notes1.t WP(MIN.) is applied to late write cycles or read modify write cycles. In early write cycles, t WCH(MIN.) should be met.2.If t WCS≥t WCS(MIN.), the cycle is an early write cycle and the data out will remain Hi-Z through the entire cycle.3.t DS(MIN.) and t DH(MIN.) are referenced to the /CAS falling edge in early write cycles. In late write cycles andread modify write cycles, they are referenced to the /WE falling edge.Read Modify Write CycleParameter Symbol t RAC = 50 ns t RAC = 60 ns Unit NoteMIN.MAX.MIN.MAX.Read modify write cycle time t RWC107−133−ns/RAS to /WE delay time t RWD64−77−ns1/CAS to /WE delay time t CWD27−32−ns1 Column address to /WE delay time t AWD39−47−ns1 Note 1. If t WCS≥t WCS (MIN.), the cycle is an early write cycle and the data out will remain Hi-Z through the entire cycle.If t RWD≥t RWD(MIN.), t CWD≥t CWD(MIN.), t AWD≥t AWD(MIN.) and t CPWD≥t CPWD (MIN.), the cycle is a read modify write cycle and the data out will contain data read from the selected cell. If neither of the above conditions is met, the state of the data out is indeterminate.10Hyper Page Mode (EDO)Parameter Symbol t RAC = 50 ns t RAC = 60 ns Unit NotesMIN.MAX.MIN.MAX.Read / Write cycle time t HPC20−25−ns1/RAS pulse width t RASP50125,00060125,000ns/CAS pulse width t HCAS810,0001010,000ns/CAS precharge time t CP7−10−nsAccess time from /CAS precharge t ACP−30−35ns/CAS precharge to /WE delay time t CPWD41−52−ns2/RAS hold time from /CAS precharge t RHCP30−35−nsRead modify write cycle time t HPRWC52−66−nsData output hold time t DHC5−5−ns/OE to /CAS hold time t OCH5−5−ns3/OE precharge time t OEP5−5−nsOutput buffer turn-off delay from /WE t WEZ010013ns4,5/WE pulse width t WPZ7−10−ns5 Output buffer turn-off delay from /RAS t OFR010013ns4,5 Output buffer turn-off delay from /CAS t OFC010013ns4,5 Notes1.t HPC (MIN.) is applied to /CAS access.2.If t WCS≥t WCS (MIN.), the cycle is an early write cycle and the data out will remain Hi-Z through the entirecycle. If t RWD≥t RWD (MIN.), t CWD≥t CWD (MIN.), t AWD≥t AWD (MIN.) and t CPWD≥t CPWD (MIN.), the cycle is a read modify write cycle and the data out will contain data read from the selected cell. If neither of the above conditions is met, the state of the data out is indeterminate.3./WE : inactive (in read cycle)/CAS : inactive, /OE : active ...... t CHO is effective./CAS, /OE : active ...... t OCH is effective.4.t OFC (MAX.), t OFR (MAX.) and t WEZ (MAX.) define the time when the output achieves the conditions of Hi-Z and isnot referenced to V OH or V OL.5.To make DQs to Hi-Z in read cycle, it is necessary to control /RAS, /CAS, /WE, /OE as follows. The effectivespecification depends on state of each signal.(1)Both /RAS and /CAS are inactive (at the end of the read cycle)/WE : inactive, /OE : activet OFC is effective when /RAS is inactivated before /CAS is inactivated.t OFR is effective when /CAS is inactivated before /RAS is inactivated.The slower of t OFC and t OFR becomes effective.(2)Both /RAS and /CAS are active or either /RAS or /CAS is active (in read cycle)/WE, /OE : inactive ...... t OEZ is effective.Both /RAS and /CAS are inactive or /RAS is active and /CAS is inactive (at the end of read cycle)/WE, /OE : active and either t RRH or t RCH must be met ...... t WEZ and t WPZ are effective.The faster of t OEZ and t WEZ becomes effective.The faster of (1) and (2) becomes effective.11Refresh CycleParameter Symbol t RAC = 50 ns t RAC = 60 ns Unit NoteMIN.MAX.MIN.MAX./CAS setup time t CSR5−5−ns/CAS hold time (/CAS before /RAS refresh)t CHR10−10−ns/RAS precharge /CAS hold time t RPC5−5−ns/WE setup time t WSR10−10−ns/WE hold time t WHR15−15−ns12Byte No.Function Described Hex Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Notes 0Number of serial PD bytes5DH010******* bytes 1Serial memory08H00001000256 bytes 2Fundamental memory type02H00000010EDO3Number of rows0DH0000110113 rows 4Number of columns0AH0000101010 columns 5Number of banks01H00000001 1 bank 6Data width48H010******* bits 7Data width (continued)00H0000000008Voltage interface01H00000001LVTTL 9/RAS access time-A5032H0011001050 ns-A603CH0011110060 ns 10/CAS access time-A500DH0000110113 ns-A600FH0000111115 ns 11Error detection/correction02H00000010ECC12Refresh period00H00000000Normal 13DRAM width08H00001000×814Error checking DRAM width08H00001000×815 - 6100H00000000None62SPD revision01H00000001163Checksum for bytes 0 - 62-A501AH00011010-A6026H00100110 64Manufacture’s JEDEC ID code per10H00010000 JEP-106E65-7100H0000000072Manufacturing location73Part name34H0011010074Part name32H0011001075Part name38H0011100076Part name4CH0100110077Part name46H0100011078Part name46H0100011079Part name37H0011011180Part name32H0011001081Part name31H0011000182Part name46H0100011083Part name MC-428LFF721FB42H01000010MC-428LFF721FH48H01001000 84Part name2DH0010110185Part name41H0100000186Part name-A5035H00110101-A6036H00110110 87Part name30H0011000088Part name20H0010000089Part name20H0010000090Part name20H0010000091PCB revision code31H0011000192Blank20H00100000Remark 1 : High level (Serial data), 0 : Low level (Serial data)1314Data outHi - ZV IH V IL/CASV IH V IL/RASV IH V ILAddressV IH V IL/WEV OH V OLDQV IH V IL/OECRPt RCDt CSHt RASt RCt RSH t CASt RALt CAHt ASCt Col.RCSt OCH t OES t OEAt CLZt OLZt CACt AA t RAC t RPt CPNt RCHt RRHt WPZt CHOt WEZ t OFC t OEZ t OFRt Hi - ZASRt RAH t RADt Row15DSt CRPt RCDt WCHt WCSt ASRt RAH t RADt ASCt CAHt CASt RSH t CSHt RASt RPt RCt V IH V ILV IH V ILV IH V ILV IH V ILV IH V IL/RASAddress/WERowCol.Data inDHt CPNt /CASDQRemark /OE : Don’t care16/RASAddress/WERowCol.Data in/OEHi - ZRCt RPt RASt CRPt RCDt CASt RSH t CSHt CPNt ASRt RAH t RADt ASCt CAHt WPt RWLt CWL t RCSt OEHt OEDt DSt DHt V IH V ILV IH V ILV IH V ILV IH V ILV IH V ILV IH V IL/CASDQ17Read Modify Write Cycle/RAS/CASAddress/WEDQ/OEDQRowCol.Data inHi - ZData out Hi - ZV OH V OLV IH V ILV IH V ILV IH V ILV IH V ILV IH V ILV IH V ILRWCt RASt RPt CPN t RSH t CASt CSHt RCDt CRPt ASRt RAH t RADt CAHt ASCt RCSt OEAt OEHt DSt DHt OEDt AA t RAC t CACt CLZt OLZ t OEZ t CWL t RWL t WPt RWD t AWD t CWDt18Hyper Page Mode (EDO) Read Cycle/RAS/CASAddress/WE/OEDQt RASPt RPt CRPt RCDt HCASt CSHt CPt RHCPt RSH t HCASt CPNt HCASt HPCt CPt ASRt RAHt RADt CAH t ASCt CAH t ASCt CAH t RAL t RCSt RCH t RRHt WPZt WEZt OEZt ACP t AA t CACt ACP t AA t CACt DHC t DHC t OEA t OLZt RAC t AA t CAC t CLZRowCol.Col.Col.Data out Data out Data outHi - Zt OFR t OFCt OCHV IH V ILV OH V OLV IH V ILV IH V ILV IH V ILV IH V ILCHOt t ASCRemark In the hyper page mode (EDO), read, write and read modify write cycles are available for each of theconsecutive /CAS cycles within the same /RAS cycle./RAS/CAS Address/WE/OEt RASP t RPt CRP t RCD t HCASt CSHt RHCPt RSHt HCAS t CPNt HCASt ASR t RAHt RADt CAH t ASC t CAH t ASC t CAHt RALt RRHt WPZt OFRt OFCt OEZt AA t AAt CLZt CAC t CACt CLZt WEZ t WEZt OEAt OLZt RACt AAt CACt CLZRow Col.Col.Col.Data out Data out Data out Hi - ZDQt RCHt WPZt RCSt RCHt WPZt RCSt RCHHi - Z Hi - Zt WEZt OCHV IHV ILV OHV OLV IHV ILV IHV ILV IHV ILV IHV ILCHOtt ASCt RCSRemark In the hyper page mode (EDO), read, write and read modify write cycles are available for each of the consecutive /CAS cycles within the same /RAS cycle.1920Hi - ZHi - ZRowCol.ACol.B Col.C/RAS/CASAddress/OEDQData out AData out C/WEV IH V ILV OH V OLV IH V ILV IH V ILV IH V ILV IH V ILRASPt RPt RHCPt CPN t RSH t HCASt CPt HPC t HCASt CPt HCASt CSHt RCDt CRPt RADt RAHt ASRt ASCt CAHt CAH t ASCt CAH t RAL t OFRt OFC t RRH t RCHt OES t AA t CACt CACt AA t RAC t RCSt OEPt OCHt OEAt CHOt ACPt OCH t OEPt CHOt OEPt AAt CAC t ACP t OCHt CHOt OEZt OEA t OLZt OEZt OEA t OLZt OEZt CLZt OEZt CLZt OLZ t Data out BData out BASCt Remark In the hyper page mode (EDO), read, write and read modify write cycles are available for each of theconsecutive /CAS cycles within the same /RAS cycle.21Data in V IHV ILV IHV IL/WE V IHV ILAddress V IH V ILV IHV IL/RAS CRPt RADt ASRt RAHt ASCt CAHt ASCt CAH t WCH t WCSt WCH t DH t DS t DSt DH t Data in Data inDS t DHt WCHt RowCol.Col.Col.ASCt CAH t CPNt RPt RALt HCASt CPt HCASt HPCt RSH t RHCPt RASPt CPt HCASt RCDt CSHt WCS t WCSt /CASDQ Remarks 1./OE : Don’t care2.In the hyper page mode (EDO), read, write and read modify write cycles are available for each of theconsecutive /CAS cycles within the same /RAS cycle./RASAddress/WECol.Col.Col.RowHi-Z Hi-Z Hi-ZData inData in Data in/OERASPtRHCPtRPtCPNtRSHtHCAStHCAStHPCtCPtCPtCSHtHCAStRCDtCRPtASRt RAHtRADtCAHt CAHtASCtRALtCAHtWPtRWLtCWLtRCStWPtCWLtWPt RCStCWLtRCStOEHtOEHt OEHtOEDt DSt DHtOEDt DSt DHtOEDt DSt DHtV IHV ILV IHV ILV IHV ILV IHV ILV IHV ILV IHV ILASCtASCt/CASDQRemark In the hyper page mode (EDO), read, write and read modify write cycles are available for each of the consecutive /CAS cycles within the same /RAS cycle.2223t RCS/CASt CPNt CP t HCAS t HCAS t CP t HPRWCt HCAS t RCD /RASt RASPt RPt CRPAddresst ASRt RAHt RADt ASCt CAHt ASCt CAH t CAH t ASCRowCol.Col.Col.t RAL/WEt RWD t OLZt DH t DSt AWD t CWDt WP t RCSt CWLt ACPt CPWD t AWD t CWDt WPt CWLt ACPt CPWD t AWD t CWD t RCSt CWL t RWL t WP/OEDQoutt CLZ t OED t OEAt CACt AAt RAC int OEAt OEHt CAC t AAt OLZ t DH t DS outt OEZ t OED int OLZt DH t DS outt OEZ t CLZ t OED int OEHt AAt CAC t OEAt OEHHi-ZHi-ZHi-ZHi-ZDQV IH V ILV OH V OLV IH V ILV IH V ILV IH V ILV IH V ILV IH V ILt OEZ t CLZ Remark In the hyper page mode (EDO), read, write and read modify write cycles are available for each of theconsecutive /CAS cycles within the same /RAS cycle.24t RASPt RPt CRPt RCDt HCASt CSHt CPt RHCPt RSHt HCASt CPNt HCAS t HPCt CPt ASRt RAHt RADt CAH t ASCt CAH t ASCt CAHt RAL t RCSt RCHt ACP t AA t CACt WEZt DHCt OEA t RAC t AA t CAC t CLZRowCol.Col.Col.Data outData outHi - Zt WCS t WCHHi - Zt DH t DSData int OCH t OLZ CHOt /RASV IH V ILV IH V ILAddressV IH V IL/WEV IH V IL/OEV IH V ILV OH V OLV IH V ILt ASCt OEZ/CASDQDQRemark In the hyper page mode (EDO), read, write and read modify write cycles are available for each of theconsecutive /CAS cycles within the same /RAS cycle.25/CAS Before /RAS Refresh Cyclet t t t t t t t t t t t t t t t CSRCHRWSRWHR RCRPRPCCSRCHRRASRASRPRCRPCCPNCRPV IH V ILV IH V IL/WEV IH V ILt t WSR WHR/CAS/RASRemark Address, /OE : Don't care DQ : Hi-Z/RAS Only Refresh CycleRowRowt RCt RCt RASt RASt RPt RPt CRPt RPCt CPNt ASRt ASR t RAH t RAH t CRPV IH V IL/RASV IH V ILV IH V ILAddress/CASRemark /WE, /OE : Don't care DQ : Hi-Z26t t t t t t RowCol.Data outHi - ZHi - Zt t t t t t t t t t t t t t t t t t t t t t RC RC RASRASRPCRPt RCD RSH CHR CPNt ASRRADRAH RALCAHASCRCHWHRWPZWEZCHOOFC OFROEZRCSt OES t OEARAC AA CAC OLZ CLZ/RASV IH V ILV IH V ILAddress V IHVIL/WE V IHVIL/OEV IH V ILV OH V OLRPt /CASDQ27t t t t t t t t t t RowCol.t t t t t t t t Data inRC RASRPRCRASRCD RSH CHR CPNCAHASCRADRAHASRCRPWCSt WCHDSDH/RASV IH V ILV IH V ILAddressV IH V IL/WEV IH V ILV IH V ILRPt /CASDQt WHRt WSR Remark /OE : Don’t care28Package Drawings[ MC-428LFF721FH ]168 PIN DUAL IN-LINE MODULE (SOKET TYPE)ITEM MILLIMETERS INCHES A1A C 36.83 1.450U 4.00 MIN.0.157 MIN.B 11.430.450S T 1.27±0.10.050±0.004D1 6.350.250D2 2.00.079X 2.54±0.100.100±0.004133.355.250133.35±0.13 5.250±0.006G 6.350.250E 54.61 2.150H 1.27 (T.P.)0.050 (T.P.)I 8.890.3503.1250.123J L 17.780.700K 42.18 1.661M 31.75±0.13 1.250±0.006M111.970.47124.4950.964R 4.00±0.100.157+0.005–0.004Y 3.0 MIN.0.118 MIN.φM168S-50A57Z3.0 MIN.0.118 MIN.M219.780.779N 3.0 MAX.0.119 MAX.V 0.25 MAX.0.010 MAX.W 1.0±0.050.039+0.003–0.002D 3.00.118φP 1.00.039Q R2.0R0.079YRJHDQUTdetail of A partD2P XV A(OPTIONAL HOLES)SWNZBIGdetail of B partD1M1 (AREA B)M2 (AREA A)LEA (AREA B)CB KA1 (AREA A)M529[ MC-428LFF721FB ]NTUM168 PIN DUAL IN-LINE MODULE (SOCKET TYPE)P DITEM MILLIMETERS INCHES U 4.0 MIN.0.157 MIN.S T 1.27±0.10.05±0.004A B 11.43133.35±0.13 5.250±0.0060.450C D 6.3536.83 1.4500.250E G6.3554.61 2.1500.250H1.27 (T.P.)0.050 (T.P.)I 8.890.350J 24.4950.964K 42.18 1.661L 17.780.700M N R 4.0±0.10.157Q V 0.25 MAX.0.010 MAX.R2.0R0.079+0.005–0.0045.08 MAX.0.200 MAX.3.00.118P1.00.039Y 3.0 MIN.0.118 MIN.W X2.54 MIN.1.0±0.050.100±0.004Z3.0 MIN.0.118 MIN.0.039+0.003–0.002WGVXYRSLQ ZJH CBK GIBD EA(OPTIONAL HOLES)Adetail of partdetail ofpart 31.751.250UB3JS[MEMO] 30NOTES FOR CMOS DEVICES1PRECAUTION AGAINST ESD FOR SEMICONDUCTORSNote:Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps mustbe taken to stop generation of static electricity as much as possible, andquickly dissipate it once, when it has occurred. Environmental control mustbe adequate. When it is dry, humidifier should be used. It is recommendedto avoid using insulators that easily build static electricity. Semiconductordevices must be stored and transported in an anti-static container, staticshielding bag or conductive material. All test and measurement toolsincluding work bench and floor should be grounded. The operator shouldbe grounded using wrist strap. Semiconductor devices must not be touchedwith bare hands. Similar precautions need to be taken for PW boards withsemiconductor devices on it.2HANDLING OF UNUSED INPUT PINS FOR CMOSNote:No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal inputlevel may be generated due to noise, etc., hence causing malfunction. CMOSdevice behave differently than Bipolar or NMOS devices. Input levels ofCMOS devices must be fixed high or low by using a pull-up or pull-downcircuitry. Each unused pin should be connected to V DD or GND with aresistor, if it is considered to have a possibility of being an output pin. Allhandling related to the unused pins must be judged device by device andrelated specifications governing the devices.3STATUS BEFORE INITIALIZATION OF MOS DEVICESNote:Power-on does not necessarily define initial status of MOS device. Produc-tion process of MOS does not define the initial operation status of thedevice. Immediately after the power source is turned ON, the devices withreset function have not yet been initialized. Hence, power-on does notguarantee out-pin levels, I/O settings or contents of registers. Device is notinitialized until the reset signal is received. Reset operation must beexecuted imme-diately after power-on for devices having reset function.31。

北京四方-280系列数字式保护(测控)装置说明书(0SF.451.069)_V2.0

2.7

输出触点容量............................................................................................................................ 4

2.8

装置主要技术参数.................................................................................................................... 4

3.2

装置功能组件概述.............................ห้องสมุดไป่ตู้...................................................................................... 6

3.3

交流插件(AC) ...................................................................................................................... 7

2.5

热性能(过载能力)................................................................................................................ 4

2.6

功率消耗 ................................................................................................................................... 4

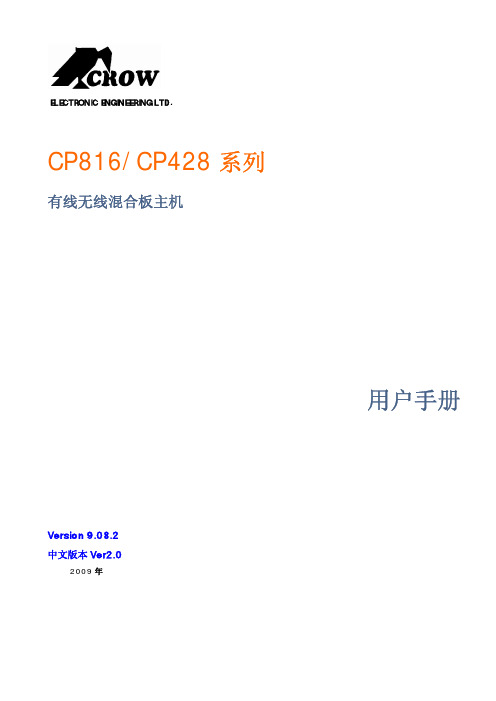

CP428系列主机安装手册

对有线防区编程

SEQ 1

Address P122E 1-16E Runner-4 1-8E

2

P121E 1-16E

Runner-4 1-8E

Remarks/Example

设定防区 1-16(对于 Runner-4 仅为 1~4 防 区)处于激活状态 开启选项 1 (防区激活).

设置防区 1-16(对于 Runner-4 仅为 1~4 防 区)分区属性.

用户码 ................................................................................................ 10 其它选项和时钟设置 ............................................................................. 14 输出 OUTPUTS ................................................................................. 16 分区 AREAS ...................................................................................... 18 键盘 KEYPADS.................................................................................. 21 夜间钥匙开关面板 KEYSWITCHES ........................................................ 27 防区 ZONES ...................................................................................... 28 定时时区 TIME ZONES ........................................................................ 37 拨号通讯器 DIALLER ......................................................................... 38

MC10H641FNR2G;MC10H641FNG;MC10H641FNR2;MC100H641FN;MC100H641FNG;中文规格书,Datasheet资料

MC10H641, MC100H641 Single Supply PECL to TTL 1:9 Clock Distribution ChipDescriptionThe MC10H/100H641 is a single supply, low skew translating 1:9 clock driver. Devices in the ON Semiconductor H641 translator series utilize the PLCC−28 for optimal power pinning, signal flow through and electrical performance.The device features a 24 mA TTL output stage, with AC performance specified into a 50 pF load capacitance. A latch is provided on−chip. When LEN is LOW (or left open, in which case it is pulled LOW by the internal pulldown) the latch is transparent. A HIGH on the enable pin (EN) forces all outputs LOW. Both the LEN and EN pins are positive ECL inputs.The V BB output is provided in case the user wants to drive the device with a single−ended input. For single−ended use, the V BB should be connected to the D input and bypassed with a 0.01 m F capacitor.The 10H version of the H641 is compatible with positiveMECL 10H™ logic levels. The 100H version is compatible with positive 100K levels.Features•PECL − TTL Version of Popular ECLinPS E111•Low Skew•Guaranteed Skew Spec•Latched Input•Differential ECL Internal Design•V BB Output for Single−Ended Use•Single +5.0 V Supply•Logic Enable•Extra Power and Ground Supplies•Separate ECL and TTL Supply Pins•Pb−Free Packages are Available**For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.MARKING DIAGRAM*xxx= 10 or 100A= Assembly LocationWL= Wafer LotYY= YearWW= Work WeekG=Pb−Free PackagePLCC−28FN SUFFIXCASE 776MCxxxH641GAWLYYWW1*For additional marking information, refer toApplication Note AND8002/D.See detailed ordering and shipping information in the package dimensions section on page 8 of this data sheet.ORDERING INFORMATIONV BB D D VE LEN GE EN1GT Q5VT Q4VT Q3GTGT Q6VT Q7VT Q8GT GTQ2VTQ1VTQ0GT5678910112524232221201926272823418171615141312Figure 1. Pinout: PLCC −28 (Top View)TTL OutputsQ0Q1Q2Q3Q4Q5Q6Q7Q8Figure 2. Logic DiagramTable 2. 10H PECL DC CHARACTERISTICSSymbol Characteristic Condition0°C25°C85°CUnit Min Max Min Max Min MaxI INH Input HIGH Current255175175m A I IL Input LOW Current0.50.50.5m A V IH Input HIGH Voltage V E = 5.0 V (Note 1) 3.83 4.16 3.87 4.19 3.94 4.28V V IL Input LOW Voltage V E = 5.0 V (Note 1) 3.05 3.52 3.05 3.52 3.05 3.55V V BB Output Reference Voltage V E = 5.0 V (Note 1) 3.62 3.73 3.65 3.75 3.69 3.81V NOTE:Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.1.PECL V IH, V IL, and V BB are referenced to VE and will vary 1:1 with the power supply. The levels shown are for VE = 5.0 V.Table 3. 100H PECL DC CHARACTERISTICSSymbol Characteristic Condition0°C25°C85°CUnit Min Max Min Max Min MaxI INH Input HIGH Current255175175m A I INL Input LOW Current0.50.50.5m A V IH Input HIGH Voltage V E = 5.0 V (Note 2) 3.835 4.120 3.835 4.120 3.835 4.120V V IL Input LOW Voltage V E = 5.0 V (Note 2) 3.190 3.525 3.190 3.525 3.190 3.525V V BB Output Reference Voltage V E = 5.0 V (Note 2) 3.62 3.74 3.62 3.74 3.62 3.74V NOTE:Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.2.PECL V IH, V IL, and V BB are referenced to VE and will vary 1:1 with the power supply. The levels shown are for VE = 5.0 V.Table 4. DC CHARACTERISTICS (V T = V E = 5.0 V ± 5%)Symbol CharacteristicT A = 0°C T A = + 25°C T A = + 85°CUnit Min Typ Max Min Typ Max Min Typ MaxI EE Power Supply CurrentPECL243024302430mA I CCH TTL243024302430mA I CCL273527352735mA NOTE:Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.Table 5. TTL DC CHARACTERISTICS (V T = V E = 5.0 V ± 5%)Symbol0°C25°C85°C Characteristic Condition Min Max Min Max Min Max UnitV OH Output HIGH Voltage I OH = −15 mA 2.5 2.5 2.5V V OL Output LOW Voltage I OL = 24 mA0.50.50.5V I OS Output Short Circuit Current V OUT = 0 V−100−225−100−225−100−225mA NOTE:Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.Table 6. AC CHARACTERISTICS (V T = V E = 5.0 V ± 5%)Characteristic T J = 0°C T J = + 25°C T J = + 85°CSymbol Condition Min Typ Max Min Typ Max Min Typ Max Unitt PLH t PHL Propagation DelayD to QCL = 50 pF (Note 3) 5.005.365.505.866.006.364.865.275.365.775.866.275.085.435.585.936.086.43nst skew Device SkewPart−to−PartSingle V CCOutput−to−Output CL = 50 pF (Note 4)CL = 50 pF (Note 5)CL = 50 pF (Note 6)100075035010007503501000750350pst PLH t PHL Propagation DelayLEN to QCL = 50 pF 4.9 6.9 4.9 6.9 5.07.0nst PLH t PHL Propagation DelayEN to QCL = 50 pF 5.07.0 4.9 6.9 5.07.0nst r t f Output Rise/Fall0.8 V to 2.0 VCL = 50 pF 1.71.61.71.61.71.6nsf MAX Max Input Frequency CL = 50 pF (Note 7)656565MHz t S Setup Time0.750.500.750.500.750.50ns t H Hold Time0.750.500.750.500.750.50ns NOTE:Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.3.Propagation delay measurement guaranteed for junction temperatures. Measurements performed at 50 MHz input frequency.4.Skew window guaranteed for a single temperature across a V CC = V T = V E of 4.75 V to5.25 V (See Application Note in this data sheet).5.Skew window guaranteed for a single temperature and single V CC = V T = V E6.Output−to−output skew is specified for identical transitions through the device.7.Frequency at which output levels will meet a 0.8 V to 2.0 V minimum swing.Determining Skew for a Specific ApplicationThe H641 has been designed to meet the needs of very low skew clock distribution applications. In order to optimize the device for this application special considerations are necessary in the determining of the part−to−part skew specification limits. Older standard logic devices are specified with relatively slack limits so that the device can be guaranteed over a wide range of potential environmental conditions. This range of conditions represented all of the potential applications in which the device could be used. The result was a specification limit that in the vast majority of cases was extremely conservative and thus did not allow for an optimum system design. For non−critical skew designs this practice is acceptable, however as the clock speeds of systems increase overly conservative specification limits can kill a design.The following will discuss how users can use the information provided in this data sheet to tailor a part−to−part skew specification limit to their application. The skew determination process may appear somewhat tedious and time consuming, however if the utmost in performance is required this procedure is necessary. For applications which do not require this level of skew performance a generic part−to−part skew limit of 2.5 ns can be used. This limit is good for the entire ambient temperature range, the guaranteed V CC (V T, V E) range and the guaranteed operating frequency range.Temperature DependenceA unique characteristic of the H641 data sheet is that the AC parameters are specified for a junction temperature rather than the usual ambient temperature. Because very few designs will actually utilize the entire commercial temperature range of a device a tighter propagation delay window can be established given the smaller temperature range. Because the junction temperature and not the ambient temperature is what affects the performance of the device the parameter limits are specified for junction temperature. In addition the relationship between the ambient and junction temperature will vary depending on the frequency, load and board environment of the application. Since these factors are all under the control of the user it is impossible to provide specification limits for every possible application. Therefore a baseline specification was established for specific junction temperatures and the information that follows will allow these to be tailored to specific applications.Since the junction temperature of a device is difficult to measure directly, the first requirement is to be able to “translate” from ambient to junction temperatures. The standard method of doing this is to use the power dissipation of the device and the thermal resistance of the package. For a TTL output device the power dissipation will be a function of the load capacitance and the frequency of the output. The total power dissipation of a device can be described by the following equation:P D (watts) = I CC (no load) * V CC +V S* V CC * f * C L * # Outputswhere:V S= Output V oltage Swing = 3.0 Vf = Output FrequencyC L = Load CapacitanceI CC = I EE + I CCHFigure 1 plots the I CC versus Frequency of the H641 with no load capacitance on the output. Using this graph and the information specific to the application a user can determine the power dissipation of the H641.Figure 1. I CC versus f (No Load)01020304050607080FREQUENCY (MHz)NORMALIZEDICC12345Figure 2 illustrates the thermal resistance (in °C/W) for the PLCC−28 under various air flow conditions. By reading the thermal resistance from the graph and multiplying by the power dissipation calculated above the junction temperature increase above ambient of the device can be calculated.02004006008001000AIRFLOW (LFPM)THERMALRESISTANCE(3040506070C/W)°Figure 2. j JA versus Air FlowFinally taking this value for junction temperature and applying it to Figure 3 allows the user to determine thepropagation delay for the device in question. A more common use would be to establish an ambient temperature range for the H641’s in the system and utilize the above methodology to determine the potential increased skew of the distribution network. Note that for this information if the T PD versus Temperature curve were linear the calculations would not be required. If the curve were linear over all temperatures a simple temperature coefficient could be provided.Figure 3. T PD versus Junction Temperature−30JUNCTION TEMPERATURE (P R O P A G A T I O N D E L A Y (n s )5.2−101030507090110130°C)5.45.65.86.06.26.4V CC DependenceTTL and CMOS devices show a significant propagationdelay dependence with V CC . Therefore the V CC variation in a system will have a direct impact on the total skew of the clock distribution network. When calculating the skew between two devices on a single board it is very likely an assumption of identical V CC ’s can be made. In this case the number provided in the data sheet for part −to −part skew would be overly conservative. By using Figure 4 the skew given in the data sheet can be reduced to represent a smaller or zero variation in V CC . The delay variation due to the specified V CC variation is ≈ 270 ps. Therefore, the 1 ns window on the data sheet can be reduced by 270 ps if the devices in question will always experience the same V CC .The distribution of the propagation delay ranges given in the data sheet is actually a composite of three distributions whose means are separated by the fixed difference inpropagation delay at the typical, minimum and maximum V CC .Figure 4. D T PD versus V CC4.75VCC (V)T −1404.85 4.955.05 5.15 5.25−100−60−202060100140ΔP D (p s )Capacitive Load DependenceAs with V CC the propagation delay of a TTL output is intimately tied to variation in the load capacitance. The skew specifications given in the data sheet, of course, assume equal loading on all of the outputs. However situations could arise where this is an impossibility and it may be necessary to estimate the skew added by asymmetric loading. In addition the propagation delay numbers are provided only for 50 pF loads, thus necessitating a method of determining the propagation delay for alternative loads.Figure 5 shows the relationship between the two propagation delays with respect to the capacitive load on the output. Utilizing this graph and the 50 pF limits the specification of the H641 can be mapped into a spec for either a different value load or asymmetric loads.Figure 5. T PD versus LoadCAPACITIVE LOAD (pF)M O R M A L I Z E D P R O P A G A T I O N D E L A Y (n s )0.751020304050607080901000.800.850.900.951.001.051.101.15Rise/Fall Skew DeterminationThe rise−to−fall skew is defined as simply the difference between the T PLH and the T PHL propagation delays. This skew for the H641 is dependent on the V CC applied to the device. Notice from Figure 4 the opposite relationship of T PD versus V CC between T PLH and T PHL. Because of this the rise−to−fall skew will vary depending on V CC. Since in all likelihood it will be impossible to establish the exact value for V CC, the expected variation range for V CC should be used. If this variation will be the ± 5% shown in the data sheet the rise−to−fall skew could be established by simply subtracting the fastest T PLH from the slowest T PHL; this exercise yields 1.41 ns. If a tighter V CC range can be realized Figure 4 can be used to establish the rise−to−fall skew. Specification Limit Determination ExampleThe situation pictured in Figure 6 will be analyzed as an example. The central clock is distributed to two different cards; on one card a single H641 is used to distribute the clock while on the second card two H641’s are required to supply the needed clocks. The data sheet as well as the graphical information of this section will be used to calculate the skew between H641a and H641b as well as the skew between all three of the devices. Only the T PLH will be analyzed, the T PHL numbers can be found using the same technique. The following assumptions will be used:−All outputs will be loaded with 50 pF−All outputs will toggle at 30 MHz−The V CC variation between the two boards is ± 3 %−The temperature variation between the threedevices is ± 15°C around an ambient of 45°C.−500 lfpm air flowThe first task is to calculate the junction temperature for the devices under these conditions. Using the power equation yields:P D=I CC (no load) * V CC +V CC * V S * f * C L * # outputs=4.3 * 48m A * 5.0 V + 5.0 V * 3.0 V * 30 MHz *50 pF * 9=432 mW + 203 mW = 635 mWUsing the thermal resistance graph of Figure 2 yields a thermal resistance of 41°C/W which yields a junction temperature of 71°C with a range of 56°C to 86°C. Using the T PD versus Temperature curve of Figure 3 yields a propagation delay of 5.42 ns and a variation of 0.19 ns. Since the design will not experience the full ± 5% V CC variation of the data sheet the 1.0 ns window provided will be unnecessarily conservative. Using the curve of Figure 4 shows a delay variation due to a ± 3% V CC variation of ± 0.075 ns. Therefore the 1.0 ns window can be reduced to 1.0 ns − (0.27 ns − 0.15 ns) = 0.88 ns. Since H641a and H641b are on the same board we will assume that they will always be at the same V CC; therefore the propagation delay window will only be 1 ns − 0.27 ns = 0.73 ns.Putting all of this information together leads to a skew between all devices of0.19 ns + 0.88 ns(temperature + supply, and inherent device),while the skew between devices A and B will be only 0.19 ns + 0.73 ns(temperature + inherent device only).In both cases, the propagation delays will be centered around 5.42 ns, resulting in the following t PLH windows: T PLH = 4.92 ns − 5.99 ns; 1.07 ns window(all devices)T PLH= 5.00 ns − 5.92 ns; 0.92 ns window(devices a & b)Of course the output−to−output skew will be as shown in the data sheet since all outputs are equally loaded.This process may seem cumbersome, however the delay windows, and thus skew, obtained are significantly better than the conservative worst case limits provided at the beginning of this note. For very high performance designs, this extra information and effort can mean the difference between going ahead with prototypes or spending valuableFigure 6. Example ApplicationORDERING INFORMATIONDevice Package Shipping†MC10H641FN PLCC−2837 Units / Rail37 Units / RailMC10H641FNG PLCC−28(Pb−Free)MC10H641FNR2PLCC−28500 / Tape & Reel500 / Tape & ReelMC10H641FNR2G PLCC−28(Pb−Free)MC100H641FN PLCC−2837 Units / Rail37 Units / RailMC100H641FNG PLCC−28(Pb−Free)MC100H641FNR2PLCC−28500 / Tape & Reel500 / Tape & ReelMC100H641FNR2G PLCC−28(Pb−Free)†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.Resource Reference of Application NotesAN1405/D−ECL Clock Distribution TechniquesAN1406/D−Designing with PECL (ECL at +5.0 V)AN1503/D−ECLinPS t I/O SPiCE Modeling KitAN1504/D−Metastability and the ECLinPS FamilyAN1568/D−Interfacing Between LVDS and ECLAN1672/D−The ECL Translator GuideAND8001/D−Odd Number Counters DesignAND8002/D−Marking and Date CodesAND8020/D−Termination of ECL Logic DevicesAND8066/D−Interfacing with ECLinPSAND8090/D−AC Characteristics of ECL DevicesPACKAGE DIMENSIONSPLCC −28FN SUFFIXPLASTIC PLCC PACKAGECASE 776−02ISSUE ESL−M S 0.010 (0.250) NST VIEW SNOTES:1.DATUMS −L−, −M−, AND −N− DETERMINED WHERE TOP OF LEAD SHOULDER EXITS PLASTIC BODY AT MOLD PARTING LINE.2.DIMENSION G1, TRUE POSITION TO BEMEASURED AT DATUM −T−, SEATING PLANE.3.DIMENSIONS R AND U DO NOT INCLUDE MOLD FLASH. ALLOWABLE MOLD FLASH IS 0.010 (0.250) PER SIDE.4.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.5.CONTROLLING DIMENSION: INCH.6.THE PACKAGE TOP MAY BE SMALLER THAN THE PACKAGE BOTTOM BY UP TO 0.012(0.300). DIMENSIONS R AND U ARE DETERMINED AT THE OUTERMOST EXTREMES OF THE PLASTIC BODY EXCLUSIVE OF MOLD FLASH, TIE BAR BURRS, GATE BURRS AND INTERLEAD FLASH, BUT INCLUDING ANY MISMATCH BETWEEN THE TOP AND BOTTOM OF THE PLASTIC BODY.7.DIMENSION H DOES NOT INCLUDE DAMBAR PROTRUSION OR INTRUSION. THE DAMBAR PROTRUSION(S) SHALL NOT CAUSE THE H DIMENSION TO BE GREATER THAN 0.037(0.940). THE DAMBAR INTRUSION(S) SHALL NOT CAUSE THE H DIMENSION TO BE SMALLER THAN 0.025 (0.635).DIM MIN MAX MIN MAX MILLIMETERSINCHES A 0.4850.49512.3212.57B 0.4850.49512.3212.57C 0.1650.180 4.20 4.57E 0.0900.110 2.29 2.79F 0.0130.0190.330.48G 0.050 BSC 1.27 BSC H 0.0260.0320.660.81J 0.020−−−0.51−−−K 0.025−−−0.64−−−R 0.4500.45611.4311.58U 0.4500.45611.4311.58V 0.0420.048 1.07 1.21W 0.0420.048 1.07 1.21X 0.0420.056 1.07 1.42Y −−−0.020−−−0.50Z 2 10 2 10 G10.4100.43010.4210.92K10.040−−− 1.02−−−____ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATIONECLinPS is a trademark of Semiconductor Components Industries, LLC (SCILLC).MECL 10H is a trademark of Motorola, Inc.分销商库存信息:ONSEMIMC10H641FNR2G MC10H641FNG MC10H641FNR2 MC100H641FN MC100H641FNG MC100H641FNR2 MC100H641FNR2G MC10H641FN。

MC-4系列说明书 (1)

• 使检测仪进入校准操作,按住 C,检测仪先完成OFF倒计时,继续按住C,显示屏暂时关闭,

然后出现CAL倒计时。CAL倒计时完成后放开C。

• 开启背景照明灯,按 C。 • 确认已锁定的报警,按 C。

5

GasAlertMicroClip 气体检测仪操作指南

校准

步骤

1. 在清洁空气环境下,按住C直至屏幕出 现OFF倒计时,检测仪暂时关闭后时继 续按住C。

H2S: 0至100 ppm (1 ppm 增量) CO: 0至500 ppm (1 ppm 增量) O2: 0至30.0% vol. (0.1% vol.增量) 可燃气体(LEL): 0至100% (1%增量) 传感器类型: H2S, CO, O2:单一插拔式电化学电池 可燃气体:插拔式催化珠 氧气检测原理:毛细管控制浓度传感器

2. 检测仪重新启动,屏幕显示CAL倒计 时,按住C直至倒计时结束并进入校准 状态。

3.

闪烁,此时检测仪开始将

所有传感器归零,并对氧气传感器进

行校准。如自动归零失败,则不能进

行跨度调整。自动归零完成后,屏幕

显示APPLY GAS(施加标气)。

显示

步骤

4. 接通标气气瓶且以250-500ml/min流

正常关机:

• 四次“ 嘟” 音和四次闪光 • 震动报警器暂时性启动

GasAlertMicroClip 报警

屏幕显示

注意 报警方式可设置成锁定模式或非锁定模式。进入GasAlertMicroClip菜单的警报锁定选项可确认设定。地方法规有可能要求检测仪须使 用锁定报警模式。 如果检测仪设置为静音模式,在报警条件出现时只有震动报警启动(听觉报警和视觉报警均被关闭);如检测仪设置为IR静音模式, 则视觉报警和震动报警启动(听觉报警关闭)。 背景灯在任何报警条件下均启动。

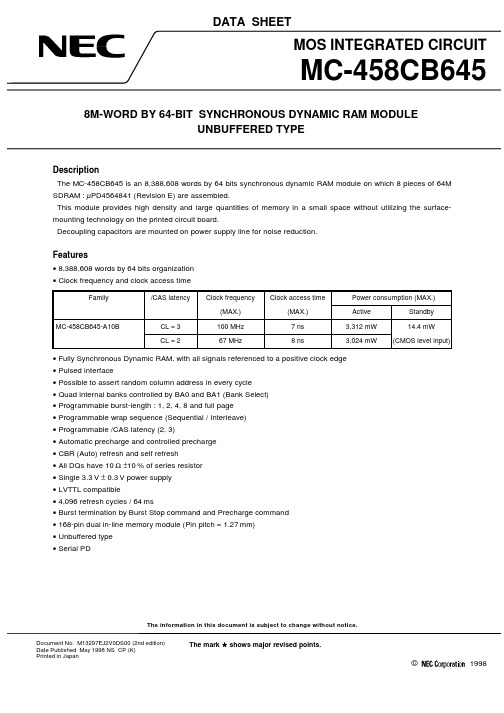

MC-458CB641ES-A10中文资料

©1999Document No. M14015EJ4V0DS00 (4th edition)Date Published February 2000 NS CP(K)Printed in JapanDATA SHEETThe mark • shows major revised points.The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version.Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.DescriptionThe MC-458CB641ES and MC-458CB641PS are 8,388,608 words by 64 bits synchronous dynamic RAM module (Small Outline DIMM) on which 4 pieces of 128M SDRAM: µPD45128163 are assembled.These modules provide high density and large quantities of memory in a small space without utilizing the surface-mounting technology on the printed circuit board.Decoupling capacitors are mounted on power supply line for noise reduction.Features• 8,388,608 words by 64 bits organization • Clock frequency and access time from CLKPart number/CAS latency Clock frequency (MAX.)Access time from CLK (MAX.)MC-458CB641ES-A80CL = 3125 MHz 6 ns CL = 2100 MHz 6 ns MC-458CB641ES-A10CL = 3100 MHz 6 ns CL = 277 MHz 7 ns MC-458CB641PS-A80CL = 3125 MHz 6 ns CL = 2100 MHz 6 ns MC-458CB641PS-A10CL = 3100 MHz 6 ns CL = 277 MHz7 ns• Fully Synchronous Dynamic RAM, with all signals referenced to a positive clock edge • Pulsed interface• Possible to assert random column address in every cycle • Quad internal banks controlled by BA0, BA1 (Bank Select)• Programmable burst-length: 1, 2, 4, 8 and Full Page • Programmable wrap sequence (Sequential / Interleave)• Programmable /CAS latency (2, 3)• Automatic precharge and controlled precharge • CBR (Auto) refresh and self refresh • Single 3.3 V ±0.3 V power supply • LVTTL compatible • 4,096 refresh cycles/64 ms• Burst termination by Burst Stop command and Precharge command • 144-pin small outline dual in-line memory module (Pin pitch = 0.8 mm)• Unbuffered type • Serial PD55Data Sheet M14015EJ4V0DS002Ordering InformationPart numberClock frequency MHz (MAX.)PackageMounted devicesMC-458CB641ES-A80125 MHz 144-pin Small Outline DIMM (Socket Type)4 pieces of µPD45128163G5 (Rev. E)(10.16mm (400) TSOP (II))MC-458CB641ES-A10100 MHz Edge connector: Gold plated 25.4 mm heightMC-458CB641PS-A80125 MHz 4 pieces of µPD45128163G5 (Rev. P)(10.16mm (400) TSOP (II))MC-458CB641PS-A10100 MHz55Data Sheet M14015EJ4V0DS003Pin Configuration144-pin Dual In-line Memory Module Socket Type (Edge connector: Gold plated)Vss DQ 0DQ 1DQ 2DQ 3DQ 4DQ 5DQ 6DQ 7Vss DQMB0DQMB1A0A1A2Vss DQ 8DQ 9DQ 10DQ 11DQ 12DQ 13DQ 14DQ 15Vss NC NCCLK0Vcc /RAS /WE /CS0NC NC Vss NC NC DQ 16DQ 17DQ 18DQ 19Vss DQ 20DQ 21DQ 22DQ 23Vcc A6A8Vss A9A10Vcc DQMB2DQMB3Vss DQ 24DQ 25DQ 26DQ 27DQ 28DQ 29DQ 30DQ 31Vss SDAVss DQ 32DQ 33DQ 34DQ 35Vcc DQ 36DQ 37DQ 38DQ 39Vss DQMB4DQMB5Vcc A3A4A5Vss DQ 40DQ 41DQ 42DQ 43Vcc DQ 44DQ 45DQ 46DQ 47Vss NC NCCKE0Vcc/CASNCNCNCCLK1VssNCNCVccDQ 48DQ 49DQ 50DQ 51VssDQ 52DQ 53DQ 54DQ 55VccA7BA0 (A13)VssBA1 (A12)A11VccDQMB6DQMB7VssDQ 56DQ 57DQ 58DQ 59VccDQ 60DQ 61DQ 62DQ 63Vss SCL Vcc CC V CC V CC V CC V CC V CC V /xxx indicates active low signal.A0 - A11:Address Inputs[Row: A0 - A11, Column: A0 - A8]BA0(A13),BA1(A12):SDRAM Bank Select DQ0 - DQ63:Data Inputs/Outputs CLK0, CLK1:Clock Input CKE0:Clock Enable Input /CS0:Chip Select Input /RAS :Row Address Strobe /CAS :Column Address Strobe /WE :Write Enable DQMB0 - DQMB7:DQ Mask EnableSDA :Serial Data I/O for PD SCL :Clock Input for PD V CC :Power Supply V SS :Ground NC:No ConnectionData Sheet M14015EJ4V0DS004Block Diagram/WE /CS0A0 - A11A0 - A11 : D0 - D3DQMB0DQMB1DQMB2DQMB3/RAS/RAS : D0 - D3/CAS /CAS : D0 - D3CKE0CKE : D0 - D3BA0A13 : D0 - D3BA1A12 : D0 - D3Remarks 1.D0 - D3: µPD45128163 (2M words x 16 bits x 4 banks)2.The value of all resistors is 10 Ω.Electrical Specifications• All voltages are referenced to V SS (GND).• After power up, wait more than 100 µs and then, execute power on sequence and CBR (Auto) refresh before proper device operation is achieved.Absolute Maximum RatingsParameter Symbol Condition Rating Unit Voltage on power supply pin relative to GND V CC–0.5 to +4.6V Voltage on input pin relative to GND V T–0.5 to +4.6V Short circuit output current I O50mA Power dissipation P D4W Operating ambient temperature T A0 to +70°C Storage temperature T stg–55 to +125°C Caution Exposing the device to stress above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limitsdescribed in the operational section of this specification. Exposure to Absolute Maximum Ratingconditions for extended periods may affect device reliability.Recommended Operating ConditionsParameter Symbol Condition MIN.TYP.MAX.Unit Supply voltage V CC 3.0 3.3 3.6V High level input voltage V IH 2.0V CC +0.3V Low level input voltage V IL–0.3+0.8V Operating ambient temperature T A070°CCapacitance (T A = 25°C, f = 1 MHz)Parameter Symbol Test condition MIN.TYP.MAX.Unit1530pF Input capacitance C I1A0 - A11, BA0(A13), BA1(A12),/RAS, /CAS, /WEC I2CLK02337C I3CKE01526C I4/CS01526C I5DQMB0 - DQMB7510Data input/output capacitance C I/O DQ0 - DQ63512pFData Sheet M14015EJ4V0DS005Data Sheet M14015EJ4V0DS006ParameterSymbol Test conditionMIN.MAX.Unit Notes Operating currentI CC1Burst length = 1, t RC ≥ t RC(MIN.)/CAS latency = 2-A80440mA1-A10440/CAS latency = 3-A80440-A10440Precharge standby current inI CC2P CKE ≤ V IL(MAX.), t CK = 15 ns 4mA power down modeI CC2PS CKE ≤ V IL(MAX.), t CK = ∞4Precharge standby current in non power down modeI CC2NCKE ≥ V IH(MIN.), t CK = 15 ns, /CS ≥ V IH(MIN.),Input signals are changed one time during 30 ns.80mA I CC2NSCKE ≥ V IH(MIN.), t CK = ∞, Input signals are stable.32Active standby current in I CC3P CKE ≤ V IL(MAX.), t CK = 15 ns 20mApower down mode I CC3PS CKE ≤ V IL(MAX.), t CK = ∞16Active standby current in non power down modeI CC3NCKE ≥ V IH(MIN.), t CK = 15 ns, /CS ≥ V IH(MIN.),Input signals are changed one time during 30 ns.120mA I CC3NSCKE ≥ V IH(MIN.), t CK = ∞, Input signals are stable.80Operating current I CC4t CK ≥ t CK(MIN.), I O = 0 mA/CAS latency = 2-A80580mA2(Burst mode)-A10440/CAS latency = 3-A80700-A10560CBR (Auto) refresh current I CC5t RC ≥ t RC(MIN.)/CAS latency = 2-A80920mA3-A10920/CAS latency = 3-A80920-A10920Self refresh current I CC6CKE ≤ 0.2 V8mA Input leakage current I I(L)V I = 0 to 3.6 V, All other pins not under test = 0 V – 4+4µA Output leakage current I O(L)D OUT is disabled, V O = 0 to 3.6 V –1.5+1.5µA High level output voltage V OH I O = – 4.0 mA 2.4V Low level output voltageV OLI O = + 4.0 mA0.4VNotes 1.I CC1 depends on output loading and cycle rates. Specified values are obtained with the output open. Inaddition to this, I CC1 is measured on condition that addresses are changed only one time during t CK(MIN.).2.I CC4 depends on output loading and cycle rates. Specified values are obtained with the output open. Inaddition to this, I CC4 is measured on condition that addresses are changed only one time during t CK(MIN.).3.I CC5 is measured on condition that addresses are changed only one time during t CK(MIN.).555Test ConditionsParameter Value Unit AC high level input voltage / low level input voltage 2.4 / 0.4V Input timing measurement reference level 1.4VTransition time (Input rise and fall time)1nsOutput timing measurement reference level 1.4V2.4 V1.4 V0.4 VCLK2.4 V1.4 V0.4 VInputOutput5Data Sheet M14015EJ4V0DS007Data Sheet M14015EJ4V0DS008MIN.MAX.MIN.MAX.Clock cycle time/CAS latency = 3t CK38(125 MHz)10(100 MHz)ns /CAS latency = 2t CK210(100 MHz)13(77 MHz)ns Access time from CLK/CAS latency = 3t AC366ns 1/CAS latency = 2t AC267ns 1CLK high level width t CH 33ns CLK low level width t CL33ns Data-out hold time/CAS latency = 3t OH333ns 1/CAS latency = 2t OH233ns 1Data-out low-impedance time t LZ00nsData-out high-impedance time/CAS latency = 3t HZ33636ns /CAS latency = 2t HZ23637ns Data-in setup time t DS 22ns Data-in hold time t DH 11ns Address setup time t AS 22ns Address hold time t AH 11ns CKE setup time t CKS 22ns CKE hold timet CKH 11ns CKE setup time (Power down exit)t CKSP 22ns Command (/CS0, /RAS, /CAS, /WE,DQMB0 - DQMB7) setup time t CMS 22ns Command (/CS0, /RAS, /CAS, /WE,DQMB0 - DQMB7) hold timet CMH11nsNote 1. Output loadOutput50 pFRemark These specifications are applied to the monolithic device.MIN.MAX.MIN.MAX.ACT to REF/ACT command period(Operation)t RC7070nsREF to REF/ACT command period(Refresh)t RC17078nsACT to PRE command period t RAS48120,00050120,000nsPRE to ACT command period t RP2020nsDelay time ACT to READ/WRITE command t RCD2020nsACT(one) to ACT(another) command period t RRD1620nsData-in to PRE command period/CAS latency = 3t DPL3810ns/CAS latency = 2t DPL2810nsData-in to ACT(REF) command/CAS latency = 3t DAL31CLK+201CLK+20nsperiod (Auto precharge)/CAS latency = 2t DAL21CLK+201CLK+20nsMode register set cycle time t RSC22CLKTransition time t T0.530130nsRefresh time (4,096 refresh cycles)t REF6464msData Sheet M14015EJ4V0DS009Serial PD(1/2) Byte No.Function Described Hex Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Notes80H10000000128 bytes 0Defines the number of bytes written intoserial PD memory1Total number of bytes of serial PD memory08H00001000256 bytes 2Fundamental memory type04H00000100SDRAM 3Number of rows0CH0000110012 rows 4Number of columns09H000010019 columns 5Number of banks01H00000001 1 bank 6Data width40H010******* bits 7Data width (continued)00H0000000008Voltage interface01H00000001LVTTL 9CL = 3 Cycle time-A8080H100000008 ns-A10A0H1010000010 ns 10CL =3 Access time-A8060H01100000 6 ns-A1060H01100000 6 ns 11DIMM configuration type00H00000000None 12Refresh rate/type80H10000000Normal 13SDRAM width10H00010000×16 14Error checking SDRAM width00H00000000None 15Minimum clock delay01H00000001 1 clock 16Burst length supported8FH100011111, 2, 4, 8, F 17Number of banks on each SDRAM04H00000100 4 banks 18/CAS latency supported06H000001102, 3 19/CS latency supported01H00000001020/WE latency supported01H00000001021SDRAM module attributes00H0000000022SDRAM device attributes : General0EH0000111023CL = 2 Cycle time-A80A0H1010000010 ns-A10D0H1101000013 ns 24CL = 2 Access time-A8060H01100000 6 ns-A1070H011100007 ns 25-2600H0000000027t RP(MIN.)-A8014H0001010020 ns-A1014H0001010020 ns 28t RRD(MIN.)-A8010H0001000016 ns-A1014H0001010020 ns 29t RCD(MIN.)-A8014H0001010020 ns-A1014H0001010020 ns 30t RAS(MIN.)-A8030H0011000048 ns-A1032H0011001050 ns 31Module bank density10H0001000064M bytes10Data Sheet M14015EJ4V0DS00(2/2) Byte No.Function Described Hex Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Notes 32Command and address-A8020H00100000 2 ns signal setup time-A1020H00100000 2 ns 33Command and address-A8010H00010000 1 ns signal hold time-A1010H00010000 1 ns 34Data signal input setup time-A8020H00100000 2 ns-A1020H00100000 2 ns 35Data signal input hold time-A8010H00010000 1 ns-A1010H00010000 1 ns 36-6100H0000000062SPD revision-A8012H00010010 1.2 A-A1012H00010010 1.2 A 63Checksum for bytes 0 - 62-A80E7H11100111-A104DH01001101 64-71Manufacture’s JEDEC ID code72Manufacturing location73-90Manufacture’s P/N91-92Revision code93-94Manufacturing date95-98Assembly serial number99-126Mfg specific126Intel specification frequency-A8064H01100100100 MHz-A1064H01100100100 MHz 127Intel specification /CAS-A8087H10000111 latency support-A1085H10000101Timing ChartRefer to the SYNCHRONOUS DRAM MODULE TIMING CHART Information (M13348E).Data Sheet M14015EJ4V0DS0011Data Sheet M14015EJ4V0DS0012Package Drawing144-PIN DUAL IN-LINE MODULE (SOCKET TYPE)X 2.55 MIN.M144S-80A15Y2.0 MIN.5Data Sheet M14015EJ4V0DS001314Data Sheet M14015EJ4V0DS00Data Sheet M14015EJ4V0DS0015CAUTION FOR HANDLING MEMORY MODULESWhen handling or inserting memory modules, be sure not to touch any components on the modules, such as the memory IC, chip capacitors and chip resistors. It is necessary to avoid undue mechanical stress on these components to prevent damaging them.When re-packing memory modules, be sure the modules are NOT touching each other. Modules in contact with other modules may cause excessive mechanical stress, which may damage the modules.• The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version.• No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.• NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual propertyrights of third parties by or arising from use of a device described herein or any other liability arising from useof such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.• Descriptions of circuits, software, and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits,software, and information in the design of the customer's equipment shall be done under the full responsibilityof the customer. NEC Corporation assumes no responsibility for any losses incurred by the customer or third parties arising from the use of these circuits, software, and information.• While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons orproperty arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.• NEC devices are classified into the following three quality grades:"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications ofa device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robotsSpecial: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disastersystems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)Specific: Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.M7 98. 8。

常用的数字电路和运算放大电路的型号

下面是电子制作网推荐的非常常用的数字电路和运算放大电路的型号和用途说明,这些是我们在设计电路中最基本的常常会使用的集成电路。

光电耦合电路-----------------LM 系列IC4N25 晶体管输出--------------LM24J 四运放(军用级)4N25MC 晶体管输出------------LM148J 通用四运放4N26 晶体管输出--------------LM1875T 无线电控制/接收器4N27 晶体管输出--------------LM224J 四运放(工业级)4N28 晶体管输出--------------LM258N 分离式双电源双运放4N29 达林顿输出--------------LM2901N 四电压比较器4N30 达林顿输出--------------LM2904N 四运放4N31 达林顿输出--------------LM301AN 通用运算放大器4N32 达林顿输出--------------LM308N 单比较器4N33 达林顿输出--------------LM311P 单比较器4N33MC 达林顿输出------------LM317L 可调三端稳压器/100mA4N35 达林顿输出--------------LM317T 可调三端稳压器/1.5A4N36 晶体管输出--------------LM317K 可调三端稳压器/3A4N37 晶体管输出--------------LM318 高速宽带运放4N38 晶体管输出--------------LM324K 通用四运放4N39 可控硅输出--------------LM331N V-F/F-V转换器6N135 高速光耦晶体管输出-----LM336-2.5V 基准电压电路6N136 高速光耦晶体管输出-----LM336 5V 基准电压电路6N137 高速光耦晶体管输出-----LM337T 基准电压电路1A6N138 达林顿输出-------------LM338K 可调三端稳压器5A6N139 达林顿输出-------------LM339N 四比较器MOC3020 可控硅光耦合驱动输出-------LM348N 四741运放MOC3021 可控硅光耦合驱动输出-------LM358N 低功耗双运放MOC3023 可控硅光耦合驱动输出-------LM361N 高速差动比较器MOC3030 可控硅光耦合驱动输出-------LM386N 声频功率放大器MOC3040 过零触发光耦合可控硅输出---LM3914N 十段点线显示驱动MOC3041 过零触发光耦合可控硅输出---LM393N 低功耗低失调双比较器MOC3061 过零触发光耦合可控硅输出---LM399H 精密基准源(6.9)MOC3081 过零触发光耦合可控硅输出---LM723CN 可调正式负稳压器TLP521-1 单光耦--------------------LM733CN 视频放大器TLP521-2 双光耦--------------------LM741J 单运放TLP521-4 四光耦--------------------LM741CN 双运放TLP621 四光耦TIL113 达林顿输出---------------------OP 系列ICTIL117 TLL逻辑输出--------------------OP07 低噪声运放PC814 单光耦--------------------------OP27 超低噪声精密运放PC817 单光耦--------------------------OP37 超低噪声精密运放H11A2 晶体管输出----------------------TL 系列ICH11D1 高压晶体管输出------------------TL062 低功耗JEFT输入双运放H11G2 电阻达林顿输出------------------TL072 低噪声JEFTLF 系列IC-----------------------------TL082 二运放LF347N 宽带JFET输入四运放 ------------TL084 四运放LF351N 宽带JFET输入运放---------------TL431 稳压LF353N JFET输入宽带运放---------------TL494 PWM解调调制器电源专用IC LF355N JFET输入运放 ------------------ULN 系列ICLF357N JFET宽带非全裣运放-------------ULN2003 周边七段驱动陈列LF398N 采样/保持电路------------------ULN2004 周边七段驱动陈列LF412N 低偏差飘移输入运放------------ULN2803 周边八段驱动陈列MC 系列IC-----------------------------ULN2804 周边八段驱动陈列MC1377 彩色电视编码器-----------------ICL 系列ICMC1403 精密电压基准源(2.5)------------ICL7106 3位ADC/驱动LCDMC1413 周边七段驱动阵列---------------ICL7107 3位半ADC/驱动LEDMC1416 周边七段驱动陈列---------------ICL7109 4位半ADC/驱动LEDMC14409 二进制脉冲拨号器--------------ICL7129 4位半ADC/LCD驱动MC14433 3位半A/D转换器----------------ICL7135 ADC/LCD驱动BCD输出MC14489 多字符LED显示驱动器-----------ICL7136 3位半CMOSADC/LCD驱动 MC145026 编码器-----------------------ICL7218 CMOS低功耗运算放大器VD5026 编码器-------------------------ICL7650 整零运放斩波MC145027 译码器-----------------------ICL7652 整零运放斩波VD5027 译码器-------------------------ICL7660 CMOS直流-直流转换器MC145028 译码器-----------------------ICL8038 函数信号发生器MC145030 编码译码器-------------------ICL8049 反对数放大器MC145106 频率合成器-------------------CA 系列ICMC145146 4位数据总线------------------CA3140 单BIMOS运行NE 系列IC----------------------------CA3240 单BIMOS运行NE521 高速双差分比较器----------------UC 系列ICNE5532 双运放-------------------------UC3842 WM电流型控制器电源专用IC NE5534 双运放-------------------------UC3845 PWM电流型控制器电源专用IC --------------------------------------UC3825 PWM电流型控制器电源专用ICNE555N 单运放 ------------------------DS 系列ICNE555J 时基电路军品极-----------------DS12887 非易失实时时钟芯片NE556 双级型双时基电路----------------L3845 中继接口电路NE564 锁相环--------------------------SG 系列ICNE565 锁相环--------------------------SG3524 PWM解调调制器电源专用ICNE567 音调译码器----------------------SG3525 PWM解调调制器电源专用IC NE592 视频放大器----------------------20106 前置放大器。

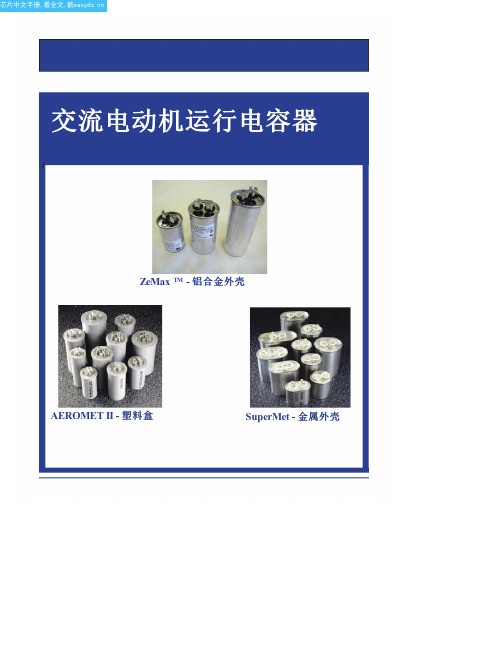

Z64S4440M中文资料(Aerovox)中文数据手册「EasyDatasheet - 矽搜」

交流电动机运行电容器

ZeMax TM - 铝合金外壳

AEROMET II - 塑料盒

SuperMet - 金属外壳

芯片中文手册,看全文,戳

目录

AEROMET II规格(系列M型).......................................... .................................... 3 SuperMet & ZeMax TM 规格(系列Z型)............................................ .................. 4 部分编号系统.............................................................................................................五 AEROMET II评分表(单台容量)系列M型....................................... ........... 6 AEROMET II评分表(双功能)系列型号M ....................................... ............. 8 SuperMet评分表(单台容量)系列Z型........................................ ............... 9 SuperMet评分表(双容量)系列Z型........................................ .............. 11 ZeMax TM 评分表(单台容量)系列Z型......................................... ........... 13 AEROMET II机械尺寸.............................................. .......................................... 15 SuperMet机械尺寸............................................... ........................................... 16 ZeMax TM 机械Dimensions............................................................................................17 附件 - 安装硬件.............................................. ............................................ 18

国电南自 PSL 641U线路保护测控装置技术说明书

10

9

8

7

6

5 4 3 2 1 序号

V1.24S V1.22 V1.10 V1.00 说明书版本号

增加计量功能 平台版本升级 改进版本 初始版本

修改摘要

PSL 641UV1.24S PSL 641UV1.22 PSL 641UV1.10 PSL 641UV1.00

软件版本号

2013.5 2011.3 2009.04 2007.04 修改日期

4 端子说明 ..............................................................................................................................................9 4.1 总端子图 .......................................................................................................................................9 4.2 交流模件端子 X1 定义...................................................................................................................9 4.3 CPU 模件端子 X2 定义 ...............................................................................................................10 4.4 计量模件端子 X3,X4 定义.........................................................................................................11 4.5 DI0 模件端子 X5 定义 .................................................................................................................12 4.6 DI0 模件端子 X6 定义 .................................................................................................................12 4.7 TRIP 模件端子 X7 定义...............................................................................................................13 4.8 TRIP 模件端子 X8 定义...............................................................................................................13

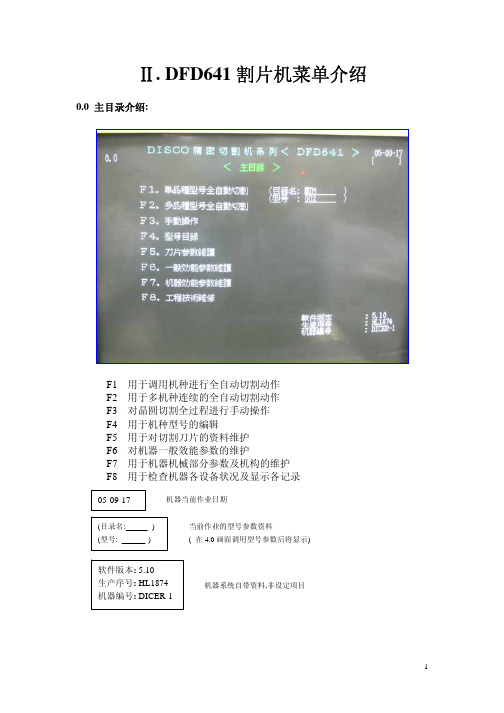

ⅡDFD641割片机菜单介绍

Ⅱ. DFD641割片机菜单介绍0.0主目录介绍:F1 用于调用机种进行全自动切割动作F2 用于多机种连续的全自动切割动作F3 对晶圆切割全过程进行手动操作F4 用于机种型号的编辑F5 用于对切割刀片的资料维护F6 对机器一般效能参数的维护F7 用于机器机械部分参数及机构的维护F8 用于检查机器各设备状况及显示各记录机器当前作业日期当前作业的型号参数资料( 在4.0画面调用型号参数后将显示)机器系统自带资料,非设定项目3.0 手动操作:对晶圆切割全过程进行手动操作F1 将晶圆从cassete内夹出并运送到工作盘上F2 收集晶圆图像资料,见3.2.1画面F3 同一片晶圆上有不同型号晶粒时使用F4 对晶圆进行自动切割动作(CH1和CH2连续切割)F5 对晶圆进行半自动切割动作,见3.5画面(既先切割CH1,手动θ调整即晶圆旋转90°后,影像教读,再切CH2) F6 将工作台面上的晶圆送到清洗盘上F7 对晶圆进行清洗动作F8 将清洗完的晶圆送入cassete内F9 对外型进行辨识F10 执行影像教读(3.2)后,做一次晶圆辩识载物箱内cassete的数量晶圆在cassete的第几格进料当前作业的型号参数资料( 在4.0画面调用型号参数后将显示)3.2.1 影像教读:收集晶圆图像资料F1 对晶圆进行重新辩识F4 视窗大小调节, 见视窗调节画面(先低倍用小窗对晶圆调,再高倍用大窗对晶粒CH1/CH2调)F5 调节晶圆的水平度;F6 自动对晶圆进行影像辩识F7 照明灯光亮度调节,见调光画面F8 调节图象的清晰度, 见对焦画面F9 自动对晶圆进行辩识F10 显微镜低倍率(LO) /高倍率(HI)切换视窗调节画面F1 视窗X方向尺寸减5 F6 视窗Y方向尺寸减5F2 视窗X方向尺寸减1 F7 视窗Y方向尺寸减1F3 视窗X方向尺寸加1 F8 视窗Y方向尺寸加1F4 视窗X方向尺寸加5 F9 视窗Y方向尺寸加5F10 以系统内部设定视窗大小为准θ角校正画面先在晶片上找一特定点按F5(θ角校正),再调节视窗位置使其在晶片的同一位置,再按F5(θ角校正)调整;反复几次操作后,直到视窗在各处晶片位置都一致且TV下方显示“完成θ角调整”调光画面F1 直射光强度数值减5 F6 斜射光强度数值减5F2 直射光强度数值减1 F7 斜射光强度数值减1F3 直射光强度数值加1 F8 斜射光强度数值加1F4 直射光强度数值加5 F9 斜射光强度数值加5F5 系统自动根据影像调节光源强度F10 以系统内部设定光源强度为准对焦画面F2 摄像头手动上升对焦F3 校准参数对焦F4 大行程对焦F5摄像头位置归零后在重新自动调焦F7 摄像头手动下降对焦F8 型号参数对焦F9 小行程对焦3.5 半自动切割画面F1 切割向Y+ 方向调节F6 切割向Y- 方向调节F2 对切割的深度进行调节F7 更改进刀速度F8 到“4.1.2型号参数”画面F4 手动对晶圆进行校准,见手动调焦画面F9 对晶圆进行预切动作F5 割刀向Y+ 方向切割F10 割刀向Y- 方向切割右边数据是切割时的作业参数手动调焦F7 对照明灯光进行调节F8 显微镜对晶圆进行调焦使图像清晰F4 将基准线宽度调窄F9 将基准线宽度调宽F5 对晶圆进行θ角校正F10 显微镜低倍率(LO) /高倍率(HI)切换4.0 型号目录画面F1 上页F6 下页F2 对型号资料进行拷贝F7 移动光标到所需要处F3 将型号参数移动到另一子目录F8 添加子目录F4 更改型号名称的参数号F9 删除子目录F5 删除该型号参数F10 直接选用光标所指的型号名称4.1.2型号参数画面(选择一项切割参数后,按ENTER键进入4.1.2画面)F1 对光标处的参数进行选择F6 至“4.1.6程序控制表”画面(用来进行单位互换) F7 预切割教程F3 至“4.1.3校准参数”画面F8 至“4.1.8刀痕检查参数”画面F4 至“4.1.4洗净搬送参数”画面F9 特殊仕样F5 多重尺寸F10 测量晶片大小(提示:只需要设定旋转轴转速、晶片厚度、进刀速度、圆形切割尺寸、晶粒尺寸,其他都是固定不变)4.1.3校准参数:设定校准参数,以利于“3.2 影像教读”注意事项①跳格检查Y方向:10晶粒容许值:0.001mm②粗调θ值50以上③CH1/CH2θ值80以上。

User Manual Transceiver Module TC 641说明书

HBC – Transceiver ModuleHBC-radiomatic GmbH • 74564 Crailsheim • Germany T C 641 (F C C )Manufactured by: HBC-radiomatic GmbHHaller Strasse 47 – 5374564 Crailsheim, GermanyTelephone: +49 ( 0 ) 79 51 – 3 93 – 0Fax: +49 ( 0 ) 79 51 – 3 93 – 50*******************E-mail:HBC-radiomatic GmbH is not liable for any misprints or errors! – All rights reserved.™ HBC-radiomatic is a registered German trademark.© 2007 – 06 , HBC-radiomatic GmbH , 74564 Crailsheim , GermanyNo part of any software or of the present document may be reproduced in any manner whatsoever without the expressedwritten permission of HBC-radiomatic GmbH.HBC-radiomatic GmbH • 74564 Crailsheim • GermanyTable of ContentsWarnings (4)Technical Data (5)HBC-radiomatic GmbH • 74564 Crailsheim • GermanyWarningsThis device complies with part 15 of the FCC rules and with RSS-210 of IndustryCanada. Operation is subject to the following two conditions: (1) This device may notcause harmful interference and (2) this device must accept any interference received,including interference that may cause undesired operation.Caution: Any changes or modifications by the user could void the user’s authority tooperate the equipment!NOTE: This equipment has been tested and found to comply with the limits for a Class Bdigital device, pursuant to part 15 of the FCC Rules. These limits are designed toprovide reasonable protection against harmful interference in a residential installation.This equipment generates, uses and can radiate frequency energy and, if not installedand used in accordance with the instructions, may cause harmful interference to radiocommunications. However, there is no guarantee that interference will not occur in aparticular installation. If this equipment does cause harmful interference to radio ortelevision reception, which can be determined by turning the equipment off and on, theuser is encouraged to try to correct the interference by one or more of the followingmeasures:•Reorient or relocate the receiving antenna.•Increase the separation between the equipment and receiver.•Connect the equipment into an outlet on a circuit different from that to which the receiver is connected.•Consult the dealer or an experienced radio/TV technician for help.IMPORTANT NOTE:FCC Radiation Exposure StatementThis equipment complies with FCC radiation exposure limits set forth for an uncontrolledenvironment. This equipment should be installed and operated with minimum distance of20 cm between the radiator and your body.This transmitter must not be co-located or operating in conjunction with any otherantenna or transmitter.HBC-radiomatic GmbH • 74564 Crailsheim • GermanyTechnical DataInterface:Type: SPI interfaceRequired input voltage: 3 VPPMaximum data rate: 250 kBit/sPort impedance: 100 kOhm // 220 pFAntenna terminal impedance: 50 OhmCommon (RX+TX):Frequency range:TC 64125 455,0 MHz – 465,0 MHzTC 64126 465,0 MHz – 470,0MHzFrequency accuracy: +/- 2,5 ppmOperating voltage: 3,3 ... 4,6 VChannel pattern: 12,5 kHzLF transmission bandwidth: 150 Hz ... 2,4 kHzModulation type: F2DOperating temperature range: -30 ... +70 °CTransmitter:Output power: +10 dBmFrequency deviation: +/- 2,5 kHzCurrent consumption (when transmitting): 100 mASwitch-over time (RX-TX): < 1 msReceiver:Sensitivity: -105 dBm (20dB S/N)First IF: 45 MHzSecond IF: 455 kHzCurrent consumption (when receiving): 70 mASwitch-over time (TX-RX): < 1 msLF output voltage: 65 mV RMS at +/-2,5 kHz deviation (internal test point only!)IP3: 0 dBmHBC-radiomatic GmbH • 74564 Crailsheim • Germany。

ALLDSP PLP428 处理器 产品说明书

PLP428处理器产品说明书前言感谢您购买PLP428处理器。

ALLDSP一直致力于在高端数字音频处理领域成为领军品牌。

在您熟悉PLP428处理器的功能和操作后,我们建议您通过使用PLP428的强大处理功能来为您的系统找到最高效的运行方式。

PLP428是一款功能强大的处理器。

有4个模拟输入,2个AES3输入,可选配的Dante输入,8个输出(12dBu),每路输入和输出都有10段PEQ,频率范围高达26kHz。

模拟输入部分可接受高达+23dBu的输入电压,因此匹配当前市场上所有的输入源,动态范围为118dB.开关电源的使用保证了无干扰的供电及极好的耐用性。

拥有64-bit数字处理系统及目前市场上最好的转换器。

PLP428处理器所处理的声音质量无论在专业还是家用领域都可以达到标杆性的水准。

本说明书描述了怎样在前面板上设置PLP428处理器,或者,也可以通过连接PC,MAC,iPad或iPhone来进行操作设置。

详情请在远程控制应用中参考Software User Manual.通过前面板或远程控制应用程序控制,DSP设置和系数在改变参数时实时计算。

频率设置可达1Hz精度,延迟可达15微秒精度,增益可达0.01dB精度。

当通过前面板编辑值时,有些值的精度间隔会被限制;比如:这种情况下,增益是通过0.25dB的步距设置的。

产品特点:-2个可选的DANTE输入-118dB动态范围(输入)/114dB动态范围(输出)-电子平衡输入-匹配阻抗输出-频率范围20Hz....26kHz-每路输入和输出都有10段PEQ-EQ可被设为Bell,High Shelf,Low Shelf,Notch,Allpass,Band Pass,High Pass,Low Pass-每路输入延迟2000ms,每路输出延迟2000ms-Butterworth,Bessel,Linkwitz-Riley滤波器高达24dB/oct.-真正的RMS压缩器-零启动峰值限幅器-延迟990微秒-通过连接PC,MAC,iPad或iPhone进行全面设置和实时监控-100组预设数据-64位多种模式数字处理-音箱库支持安全说明为了您的安全,请仔细阅读:仪器不要暴露在滴水或溅泼的液体中,任何装满液体的物体,如花瓶,都不应放置在机器上,只用干布清洁,不要堵住任何通风口。

AEMC 电流仪器磁通钳地质抗接电阻测试仪 Model 6418 英文用户手册说明书