LCD Controller

单片机lcd工作原理

单片机lcd工作原理单片机液晶显示器(LCD)是一种广泛应用于各种电子设备中的显示技术,它具有低功耗、低成本、高对比度和可见度良好等优点。

那么,单片机LCD的工作原理是怎样的呢?下面我将详细描述。

单片机LCD工作原理主要包含以下几个方面:1. 液晶显示原理:液晶显示的原理是利用液晶的光学特性。

液晶是一种特殊的有机化合物,具有电光效应和光电效应。

液晶分为向列、向行和像素点三类,其中像素点最小。

当液晶显示器处于不通电状态时,液晶分子遵循自然排列规律,液晶被光线穿过,显示器完全透明。

当液晶显示器通电时,电场会改变液晶分子的排列,使得液晶产生旋转,从而变成不透明的状态。

通过不同液晶分子的排列方式和控制电压的变化,可以实现液晶显示器的显示效果。

2. LCD驱动电路:液晶显示器需要驱动电路来提供适当的电压和电流,以控制液晶分子的旋转。

通常,主要使用2x7串行接口、并行接口或I2C接口等方式与单片机连接。

驱动电路中包含液晶显示控制器(LCD Controller)和液晶驱动器(LCD Driver)两部分。

2.1 液晶显示控制器(LCD Controller)是单片机内部的一个模块,通过与单片机的通信接口,控制和调整驱动电路工作状态。

其主要功能包括计算和产生液晶的驱动信号,实现各种显示模式的切换和刷新频率的设置。

2.2 液晶驱动器(LCD Driver)是一个对液晶进行驱动的组件。

主要通过产生驱动信号,控制和实现液晶的开关和偏置电压。

液晶驱动器通常由多个段驱动(Segment Driver)和多个位驱动(Common Driver)组成。

段驱动负责控制液晶的列选通,而位驱动则负责控制液晶的行选通。

3. 液晶显示模式:单片机LCD可以实现多种显示模式,常见的有字符模式和图形模式。

3.1 字符模式:字符模式是通过液晶驱动器和液晶显示控制器来显示字符。

在字符模式下,单片机将要显示的字符数据传给液晶驱动器,液晶驱动器将字符数据转换成液晶所需的控制信号,最终显示在液晶屏上。

创维液晶拼接控制器操作手册

现象,画质优异,超强色彩表现能力。 支持高清 支持高清电视 720p,1080i 输入和输出(某些型号)。 自由拼接 可随意调整图像位置, 设置图像的拼接。多级联调可以把几个拼接处理器联合成为 一个大规模的拼接处理器,并且各个处理器的输出都是同步的。 图像微调 对图像的亮度、对比度、饱和度、色度、平滑等全部参数的调整 。 信号组合 单路信号可设置多种显示方式组合。配合矩阵,可实现不同信号的显示组合并有矩 阵通道记忆功能,在调用模式的时候会重新记忆各个显示单元的图像通道。 模式自定 给用户提供丰富的模式定义功能,16 个内置自定义模式,大容量外模式自定义, 并支持中控的调用模式。 其它功能 LCD-CONTROLLER12(LCD-SKPJ MXN)系列产品可以实现窗口的漫游、叠加、缩 放、透视等操作。通过子窗口的自由拉伸功能可以轻松解决 16:9,4:3 不同的显示 比例的信号在拼接墙上的比例失真问题。 窗口可任意叠加, 关闭, 并支持跨屏幕的显示, 主次窗口互不干扰。窗口可以任意缩放,尺寸比例随意调整,大小随您任意调整,并能 在预设模式下保存。 透视功能 可以任意控制子窗口的透视度, 不管是文字内容,还是动感的高码流视频都实时流

9. 安全注意事项

9.1 设备内部有高压电,非专业维修人员不得打开机箱,以免发生危险; 9.2 严禁水滴或水溅,严禁在设备上放置任何装有液体的容器物品; 9.3 为预防火灾,禁止设备靠近火源; 9.4 为了充分通风,设备前后面板至少应保持20CM的空隙; 9.5 设备如发出怪异噪音、冒烟或怪味,应立即拔掉电源插头,由专业维修人员处理; 9.6 在有雷电或长期不用的情况下,请拔掉电源插头; 9.7 不要从本设备通风孔塞入任何物体,以免造成设备损坏或触电; 9.8 不宜将本设备放置于近水或其它潮湿的地方使用; 9.9 不宜将本设备放置于散热片附近或其它高温地方使用; 9.10 请妥善整理放置电源线,以防破损; 9.11 下列情况,应拔掉本设备电源插头,由专业维修人员处理: 1) 插头电源线损坏或磨损时; 2) 有液体溅入本设备时; 3) 本设备跌落或机箱损坏时; 4) 本设备出现明显功能异常或性能变化时。

lcd液晶驱动2

图4译码器LED模式仿真波形

Fig.4 Emulation wav@form of decoder in LED mode

[2]李维程,郭强.液晶显示应用技术[M].北京:电子工业出版 社,2000:339—344.

[3]刘润华,单亦先.电子设计自动化[M].东营:石油大学出版

社,2001:127一134.

的方波信号,其电压是脉冲信号的两倍,因而显示器显 示字形;而当A=0时,异或门输出脉冲信号C与其输 入信号B同频同相,从而使LCD显示器的两端电压为 0,显示器呈白色而不显示字形。

…时: ]n厂

n几

黑

公共电极

图1 液晶驱动电路及电极波形

Fig.1 LCD drive circuit and electrode waveforms

在数字系统的信息显示中,十进制数字的显示是 最基本的显示方式,通常对于LED和LCD显示器,应 采用不同的显示译码器,这样对于硬件电路已设计好 的系统其显示器就只能固定为一种,而使用CPLD/FP— GA所设计的通用显示译码器,无需改变电路硬件结 构即可实现LED或LCD的数码显示。

修改稿收到日期:2007—10—19。 作者邓翔宇,男,1974年生,2005年毕业于西安电子科技大学通信 工程学院,获硕士学位,讲师;主要从事电子与通信工程专业方面的研 究。

基于FPGA/CPLD的LED/LCD通用显示译码器设计邓翔宇

基于FPGA/CPLD的LED/LCD通用显示译码器设计

Design of Commonly Used LED/LCD Display Decoder Based OR FPG芦/CPLD

邓翔穹

(兰州工业高等专科学校电气工程系,甘肃兰州730050)

MIPI video mode 和 command mode 的区别

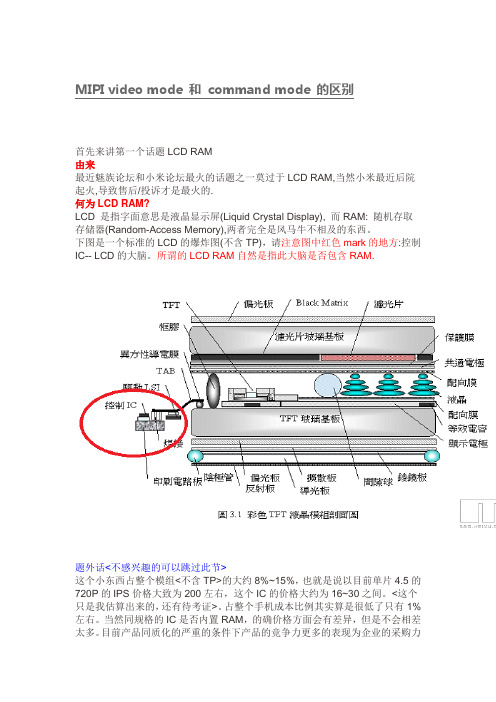

首先来讲第一个话题LCD RAM由来最近魅族论坛和小米论坛最火的话题之一莫过于LCD RAM,当然小米最近后院起火,导致售后/投诉才是最火的.何为LCD RAM?LCD 是指字面意思是液晶显示屏(Liquid Crystal Display), 而RAM: 随机存取存储器(Random-Access Memory),两者完全是风马牛不相及的东西。

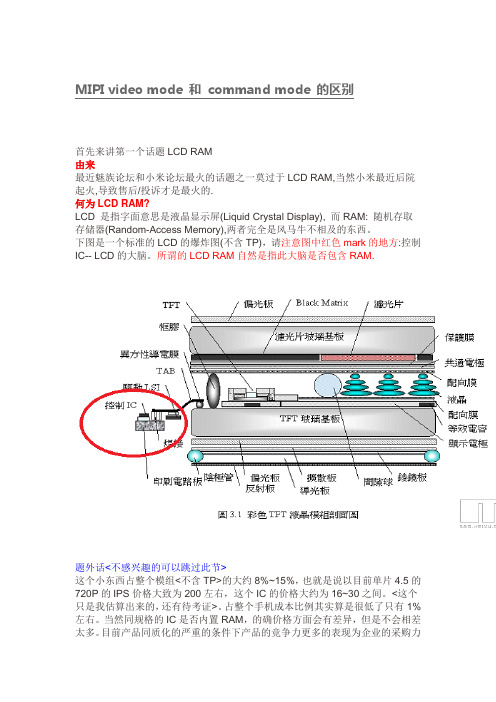

下图是一个标准的LCD的爆炸图(不含TP),请注意图中红色mark的地方:控制IC-- LCD的大脑。

所谓的LCD RAM自然是指此大脑是否包含RAM.题外话<不感兴趣的可以跳过此节>这个小东西占整个模组<不含TP>的大约8%~15%,也就是说以目前单片4.5的720P的IPS价格大致为200左右,这个IC的价格大约为16~30之间。

<这个只是我估算出来的,还有待考证>。

占整个手机成本比例其实算是很低了只有1%左右。

当然同规格的IC是否内置RAM,的确价格方面会有差异,但是不会相差太多。

目前产品同质化的严重的条件下产品的竞争力更多的表现为企业的采购力和成本控制能力。

apple就是一个好的例子,最好的东西,最低的价格,当然一定是最大的量,甚至很多企业不惜亏本也要接apple的案子,原因有二:一是苹果能帮助企业一起提升制程能力,另外一方面,需要借助apple提升自己的形象。

<不好意思扯的远了点>。

回到正题。

LCD是否需要RAM?既然说到这里,我不得不澄清,这个狗血剧情并非新话题,其实在N久以前非高速产品就一直存在此现象.这就好比N版的神雕侠侣,剧情不变,每一版的主演都在变.想当初一个年轻力壮的RGB和妖艳冻人貌美如花的如花:CPU一起当然要上演些狗血的激情.而现今廉颇老矣,尚能饭的自然只有MIPI.当然MIPI一人扮两角,搞2P是是万万不可的.因为这个主演的MIPI是一家之主,有N多小妾,其中两个一个被称为DSI和DCS。

MIPI video mode 和 command mode 的区别

首先来讲第一个话题LCD RAM由来最近魅族论坛和小米论坛最火的话题之一莫过于LCD RAM,当然小米最近后院起火,导致售后/投诉才是最火的.何为LCD RAM?LCD 是指字面意思是液晶显示屏(Liquid Crystal Display), 而RAM: 随机存取存储器(Random-Access Memory),两者完全是风马牛不相及的东西。

下图是一个标准的LCD的爆炸图(不含TP),请注意图中红色mark的地方:控制IC-- LCD的大脑。

所谓的LCD RAM自然是指此大脑是否包含RAM.题外话<不感兴趣的可以跳过此节>这个小东西占整个模组<不含TP>的大约8%~15%,也就是说以目前单片4.5的720P的IPS价格大致为200左右,这个IC的价格大约为16~30之间。

<这个只是我估算出来的,还有待考证>。

占整个手机成本比例其实算是很低了只有1%左右。

当然同规格的IC是否内置RAM,的确价格方面会有差异,但是不会相差太多。

目前产品同质化的严重的条件下产品的竞争力更多的表现为企业的采购力和成本控制能力。

apple就是一个好的例子,最好的东西,最低的价格,当然一定是最大的量,甚至很多企业不惜亏本也要接apple的案子,原因有二:一是苹果能帮助企业一起提升制程能力,另外一方面,需要借助apple提升自己的形象。

<不好意思扯的远了点>。

回到正题。

LCD是否需要RAM?既然说到这里,我不得不澄清,这个狗血剧情并非新话题,其实在N久以前非高速产品就一直存在此现象.这就好比N版的神雕侠侣,剧情不变,每一版的主演都在变.想当初一个年轻力壮的RGB和妖艳冻人貌美如花的如花:CPU一起当然要上演些狗血的激情.而现今廉颇老矣,尚能饭的自然只有MIPI.当然MIPI一人扮两角,搞2P是是万万不可的.因为这个主演的MIPI是一家之主,有N多小妾,其中两个一个被称为DSI和DCS。

Solomon Systech SSD1926 图形LCD控制器 PICtail Plus 示例板说

Japan - Yokohama - 81-45-471-6166

Korea - Daegu - 82-53-744-4301

Korea - Seoul - 82-2-554-7200

Malaysia - Kuala Lumpur - 60-3-6201-9857

Malaysia - Penang - 60-4-227-8870

China - Xian - 86-29-8833-7252

China - Zhuhai - 86-756-3210040

India - Bangalore - 91-80-4182-8400

India - New Delhi - 91-11-4160-8631

India - Pune - 91-20-2566-1512

DS51790A

Graphics LCD Controller PICtail™ Plus SSD1926 Board

Board Schematic (Rev. 2, Page 2 of 2)

.1 MF

.1 MF

.1 MF

.1 MF 47 MF

.1 MF 47 MF

.1 MF

47 MF

22 MF

DS51790A

Italy - Milan - 39-0331-742611

China - Qingdao - 86-532-8502-7355

Netherlands - Drunen - 31-416-690399

China - Shanghai - 86-21-5407-5533

Spain - Madrid - 34-91-708-08-90

Asia/Pacific

Europe

创维液晶拼接控制器操作手册

创维LCD—CONTROLLER12 (LCD-SKPJ MxN)系列液晶拼接控制软件操作手册感谢您使用创维LCD—CONTROLLER12(LCD—SKPJ MxN)系列液晶拼接控制器请在使用本产品前仔细阅读该用户操作指导书重要提示:—-控制软件随时升级,以实际提供的版本为准,产品配置不同,调试控制软件的细节略有差异;如有操作手册版本变动,恕不另行通知,请谅解。

—-如果不能正常运行本操控软件,需要安装windows系统插件Dotnetfx.exe。

——如果在使用中遇到疑问,请首先阅读本操作手册,本手册中有详细描述; 如仍有疑问,请联系我们,我们将尽快给您满意的答复。

安全说明1. 电源请使用带保护地的单相三线制交流220V电源,并确保整个工程系统使用同一保护地.不能使用无保护地的电源,电源线的接地脚不能破坏。

2。

断电需要进行设备移动或其他需要断电的工作时,要关断所有的电源,包括电源开关,拔掉电源插头等,以确保您和设备的安全.3。

线缆不能在电源线、信号线、通讯线等线缆上压放物品,应避免线缆被踩踏或挤压,以防止出现漏电或短路等危险。

4。

信号线连接从设备上插、拔信号线时,设备需要断电,以免损坏设备。

带电插拔造成的损坏不在保修范围.5。

散热孔设备外表面可能有散热用的开孔,不要堵塞这些开孔,以免热量积聚,损坏设备或造成火灾等危险.6。

设备安置应合理安置设备,如装入标准机架、机箱、机柜,或放置在稳固平整的工作台面上,防止设备跌落。

7。

环境设备工作的环境要注意防尘、防潮,尤其要防止液体浸泡和溅入设备内部.8。

维修所有的维修工作应由专业维修人员完成,未经培训不要尝试自己维修设备。

为防止电击危险,不要擅自打开机壳。

9. 安全注意事项9。

1 设备内部有高压电,非专业维修人员不得打开机箱,以免发生危险;9。

2 严禁水滴或水溅,严禁在设备上放置任何装有液体的容器物品;9.3 为预防火灾,禁止设备靠近火源;9.4 为了充分通风,设备前后面板至少应保持20CM的空隙;9。

Altera MAX II CPLD 上的 LCD 控制器应用说明说明书

Application Note 497LCD Controller Using MAX II CPLDs IntroductionThis document details the implementation of an LCD controller in an Altera ® MAX ® II CPLD. The example display uses an Optrex 16x 2 Dot Matrix LCD module, such as the popular SC1602D device. The controller receives its display signal from a microprocessor or a micro controller and translates it into commands that are understood by the LCD module. MAX II devices possess the industry’s only user flash memory (UFM), which is used by the controller to display a message upon power on. This eliminates the need for an external memory. Also, no external clock signal is required by the controller as it utilizes the CPLD’s internal UFM oscillator for its clocking needs. These unique features make the MAX II CPLD the perfect target device for such a controller.LCDsLiquid crystal displays (LCDs) are thin, flat display devices made up of any number of color or monochrome pixels arranged in front of a light source or reflector. These displays have become an indispensable part of most of electronic devices. Some features that have made LCDs popular are:■LCDs provide applications with a useful interface that allows debugging capabilities and provides the application with a more professional look ■LCDs use very small amounts of electric power; they are very suitable for battery powered devices ■LCDs are slim and use small amounts of space compared to other display types Most LCD modules are equipped with a generic interface, on-board controllers, and an on-board driver. Thus, using an LCD to enhance the visual appeal of any application has become a lot simpler. Some devices that use LCD displays are wrist watches, calculators, laptops, PDAs, cellular phones, home electronics, and toys.LCD ControllerYou can easily integrate this controller design into any application to provide a suitable display unit. It meets the timing constraints of the LCD by generating the necessary timing signals and simultaneously off loads the microprocessor and controller from the details of the LCD, thereby allowing the processor and the controller to carry out their other operations efficiently.December 2007, version 1.0Figure1 shows a block diagram for the LCD controller. The three mainmodules inside the LCD controller are the finite state machine (FSM), theuser flash memory (UFM), and the clock divider module. The interfacingsignals to the LCD module are E, RS, RW, and DB0-DB7. This designsuccessfully interfaces the processor and the LCD module through thecontroller. For more information on the signals, refer to Table1.Figure1.LCD ControllerInitializing the LCD Module and the Finite State MachineThe FSM is made of eight different states. It is used to initialize the LCD,display a message after initialization is complete, and to write to and readfrom the LCD. The initialization steps for the LCD module are shown inFigure2.Figure2.LCD Module Initialization Flow Chartf f To simplify initialization, a delay of 15ms is provided after each command is sent (instead of checking the status of the busy flag). However, while writing data into the LCD module, the status of the busy flag is checked after each data write. This makes the writing procedure faster.For more information about initializing the LCD module and the various commands supported by it, see the Optrex LCD Manual at the following link:http s:///User Flash MemoryThe UFM inside the MAX II CPLD is used to store the ASCII values of the characters to be displayed as soon as the controller is turned on. It is instantiated using the UFM megafunction. Parallel interface programs the UFM with the help of a hexadecimal (Intel_Format) file (.hex). For more information on creating a .hex file using the Quartus® II software, refer to the following link:/support/software/nativelink/quartus2/glossa ry/def_rif.htmlFor more information about instantiating the UFM using the MegaWizard® Plug-In Manager, refer to the Using User Flash Memory in MAX II Devices chapter in the MAX II Device Handbook.Clock DividerThe clock divider module reduces the frequency of the internal oscillator output so that the timing requirements of the LCD module are met and the controller performance is satisfactory. Table1 lists signal descriptions for the LCD controller (MAX II CPLD) block diagram shown in Figure1. Table1.Signal Descriptions for the LCD Controller (MAX II CPLD) (Part 1 of2)Signal DescriptionDB0-DB78-bit bi-directional bus that carries data andcommands to and from the LCD module.RW Read and write signal to distinguish between a readand a write operation.●RW = 0: Write Operation●RW = 1: Read OperationRS Register select signal. This is used to choose between the data and the command registers of the LCD module.●RS = 0: Command Register ●RS = 1: Data Register E Enable strobe signal. A negative edge on this signal latches the data on the bi-directional bus into the data or command register, and vice versa.DATA0-DATA78-bit bus coming from the processor and controller that carries the ASCII value of the character to be displayed on the LCD module.RST Reset signal. This signal is used to reset the controller and initialize the LCD module again.WE Write enable signal. This signal indicates the beginning of a write cycle. It should be set to low to enable writing to the LCD module.ACK Acknowledge signal. This signal indicates that the data has been successfully sent to the LCD module and is ready to receive the next data. Any data send before this signal goes low will be ignored by the controller.addr 9-bit address bus used to select a particular memory location of the UFM.nread Set this signal to 0 in order to read the contents of the memory location pointed to by the address bus.do Data output signal. An 8-bit data bus which holds the higher order 8-bits of the 16-bit memory location pointed to by the address bus.dv Data valid signal. Signal that indicates the data on the 8-bit data bus is valid and can be read.osc Output of the internal oscillator of the UFM block. Outputs a signal frequency of 5.5MHz.clk Output of the clock divider block. Reduces the frequency of the oscillator output signal to approximately 43kHz.Table 1.Signal Descriptions for the LCD Controller (MAX II CPLD) (Part 2 of 2)Signal DescriptionImplementationYou can implement this design with an EPM240G or any other MAX II CPLD and an Optrex SC1602D 16x 2 alphanumeric LCD module. Use this design source code and allocate the data bus and control lines (input and output) to the general purpose I/O (GPIO) lines of the MAX II CPLD. Use the internal user flash memory to store any default message you wish to display on the LCD module upon power on. Use the memory editor in the Quartus II software to create a memory initialization file to store the default message in the LCD module.The following details the implementation of this design on the MDN-B2 demo board. Table 2 lists the EPM240G pin assignments for this design example.1Unused pins are assigned as input tri-stated in the Quartus II software’s device and pin option settings prior to compilation.Design Notes To demonstrate this design on the MDN-B2 demo board, complete the following:1.Download the design on to the MAX II CPLD through the JTAG header JP5 and a conventional cable (ByteBlaster ™II, USB-Blaster ™). Programming requires the demo board to be switched on (slide switch SW1). After programming, turn off the power.Table 2.Design Implementation Using the MDN-B2 Demo Board EPM240G Pin Assignments Signal Pin Signal Pin DB[0] pin 53DB[4]pin 1DB[1] pin 98DB[5] pin 96DB[2] pin 52DB[6]pin 92DB[3] pin 97DB[7]pin 95data[0] pin 55data[4]pin 61data[1] pin 56data[5]pin 66data[2] pin 57data[6]pin 67data[3] pin 58data[7]pin 68E pin 99rst pin 77RS pin 100ack pin 69RW pin 54we pin 812.Ensure that the memory file lcd_new.hex (included with the sourcecode files) is placed in the Quartus II software’s project library.3.Connect the LCD module to the board using the suppliedinterconnect cable. Connect the 14-pin socket of the cable to CN1 on the LCD module (the red mark meets pin1 on CN1 of the demoboard) and connect the 20-pin socket to JP8 on demo board (the red mark on socket meets pin 1 on JP8 of the demo board).e the Optrex SC1602D LCD module (which is also supplied withAltera’s NIOS® II development kit 2C35N [Cyclone II version]).5.Supply the LCD module with the required 5V power supplythrough the DC socket on the interconnect cable. This DC socket has conventional polarity (the inner pin is positive). You can also use3xAA or AAA batteries to power up the LCD module.6.Connect the 5V power supply to the LCD module first. Thenconnect the interconnect cables as mentioned in step 4.7.Turn on the power supply to the MDN-B2 demo board using theslide switch SW1.8.Observe the default message on the LCD module. This message ispre-programmed in the UFM of the MAX II CPLDs using thelcd_new.hex file. The controller reads this message only once upon power-on.e the reset push button SW6 on the demo board to reset the LCDmodule. Note that after reset, the cursor on the LCD is in its firstcharacter position on the first row and is blinking.10.For the purpose of this exercise, you can enter any ASCII datacorresponding to a character you wish to display using the SW5switch (the 8-way dual in-line package (DIP) GPIO input switch on the demo board). The switch sets a logic 0 when ON, and a logic 1 when OFF. Switch #1 is the LSB on this ASCII data byte.11.Press button SW8 on the demo board to write enable the controller,which enables it to take in fresh data set by the SW5 switch. Thedemo board takes in new data as long as the SW8 button is pressed, and at a rate of approximately 4.25 kHz. It updates all characters on both rows almost immediately after pressing the SW8 button.1This design is made to work specifically with Optrex’s SC1602DLCD module. This LCD module has non-consecutive addresseson the last character of the first row and first character of thesecond row on the LCD. This design makes suitable alterationsto match this arrangement.Source Code This design has been implemented in Verilog and successful operationhas been demonstrated using the MDN-B2 demo board, as referenced inthe documentation. The source code, test bench, and complete Quartus IIproject are available at:/literature/an/an497_design_example.zipConclusion MAX II CPLDs are an excellent choice to implement LCD controllers.Their low power, easy power-on feature, and built-in user flash memorymake them ideal programmable logic devices to implement LCDcontroller designs.Referenced Documents This application note references the following documents:■/pdf/dmcman.pdf■/support/software/nativelink/quartus2/glos sary/def_rif.html■Using User Flash Memory in MAX II Devices chapter in the MAX II Device Handbook.Additional Resources The following are additional resources for this application note:■MAX II CPLD home page:/products/devices/cpld/max2/mx2-index.jsp■MAX II Device Literature page:http://www.altera.-com/literature/lit-max2.jsp■MAX II Power-Down Designs:/support/examples/max/exm-power-down.html■MAX II Application Notes:AN 428: MAX II CPLD Design GuidelinesAN 422: Power Management in Portable Systems Using MAX II CPLDs101 Innovation DriveSan Jose, CA 95134 Technical Support: /support Literature Services:*********************Copyright © 2007 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their re-spective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make chang-es to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service describedherein except as expressly agreed to in writing by Altera Corporation. Altera customersare advised to obtain the latest version of device specifications before relying on any pub-lished information and before placing orders for products or services.Application Note 497: LCD Controller Using MAX II CPLDsDocumentRevision HistoryTable3 shows the revision history for this application note.Table3.Document Revision HistoryDate and DocumentVersionChanges Made Summary of ChangesDecember 2007,v1.0Initial release.—。

最常用的LCD驱动IC

SPLC502A •132 x 65 •Vdd=1.8 – 3.6 •VLCD=12V •COG/TCP

MP

Developing

2004/1Q

2004/2Q

2004/3Q 2004/4Q

SPLC502A

•132x176 •Vdd=1.8 – 3.6 •Hi-FAS •4096/65k color •COG/TCP

2004/4Q

2005/1Q

2005/2Q

MP

Developing Planning

3. Graphic LCD Driver Roadmap

channels

320 240 160 80

長龍鑫國際有限公司

GOLD LINK DRAGON INTERNATIONAL CO. LIMITED

LCD産品介紹

網址: E-mail:sales@

业务联系:阙泉德 13826597610

長龍鑫國際有限公司 简介

GOLD LINK DRAGON INTERNATIONAL CO. LIMITED

2. Color LCD Controller Roadmap

Resolution

SPLC552A

•132x132 •Vdd=1.6 – 3.6 •VLCD=4.5-18V •4096/ 65k color •COG/TCP

SPLC552B

•128x128 •Vdd=1.6 – 3.6 •VLCD=4.5-18V •4096/ 65k color •COG/TCP

MP

0 240

TCP

SPLC563A 320 0

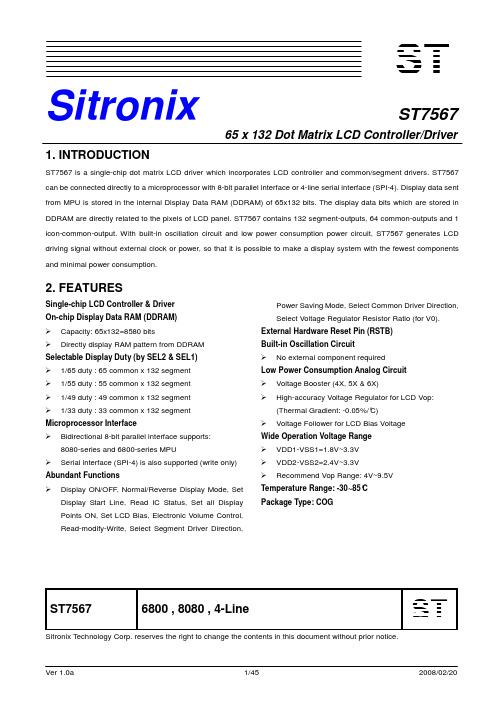

ST7567 lcd控制器

ST7567

6800 , 8080 , 4-Line

Sitronix Technology Corp. reserves the right to change the contents in this document without prior notice.

Ver 1.0a

1/45

2008/02/20

ST7567

3-1. ST7567 COG OUTLINE

12 27

10 35

Pass No: ST7567-G4

Chip Size: 4840 X 660 (+/- 15)

Chip Thickness: 300

Bump Height: 15

Unit: um

Bump Size

PAD No.

Hale Waihona Puke SizeY -74.25 -227.75 -74.25 -227.75 -74.25 -227.75 -74.25 -227.75 -74.25 -227.75 -74.25 -227.75 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50

Y -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -274.50 -74.25 -227.75 -74.25 -227.75 -74.25

STM32L4液晶控制模块(LCD)介绍

• During the other phases, the signal amplitude is 1/4 VLCD or 3/4 VLCD in case of 1/4 bias or 1/3 VLCD or 2/3 VLCD in case of 1/3 Bias and 1/2 VLCD in case of 1/2 Bias.

• Buffers prevent the LCD capacitive load from loading the resistor bridge unacceptably and interfering with its voltage generation

• The first frame generated is the odd one followed by an even one

• Five Duty ratios can be selected: Static Duty, 1/2 Duty, 1/3 Duty, 1/4 Duty or 1/8 Duty

=

fLCD

=

fLCDCLK 2PS(16+ DIV)

ck_div

• The frame frequency is obtained from the LCD frequency by dividing it by the number of active common terminals

fFrame = fLCD * duty

COM0

V LCD

LCDV整合芯片详细介绍

LCD TV整合芯片详细介绍2006-11-16LCD TV领域的整合晶片有几个笼统的称呼,有些人延用显示器时代的习惯,称为控制IC (Controller),或者因為它具有处理器功能,又称為视讯处理器(Video Processor),国外大厂技术领先,整合进许多功能,通常就以SOC整合晶片称之;它是指控制板(Controller Board)上的视讯解码器(Video Decoder)、去交错扫描器(De-interlacer)和缩放控制器(Scaler)為核心晶片的一颗整合性IC,并且因应LCD的动态画面缺点等等,加入许多影像处理技术以改善画质。

过去在显示器时代,台湾厂商以Scaler技术為长,随著市场方向逐渐从显示器移往LCD电视,大部分业者也都强化视讯技术,以整合De-interlacer和VideoDecoder的技术;不过比较起国际大厂都已经将这些技术整合进单晶片,台湾厂商还在紧紧追赶中。

整合为单晶片是趋势如果以大尺寸(32吋以上)的LCD电视来看,台湾厂商目前还是多以Video Decoder加上一颗整合晶片為主,这颗整合晶片就整合了ADC、De-interlacer、Scaler等功能,De-interlacer除了本身功能以外,又整合了RGB、DVI、HDMI等介面。

主要是Video Decoder 中的视讯技术或影像压缩MPEG技术,厂商都还在精进阶段,可能现在出了一版,很快又有新版出现,若整合进整颗晶片,要修改整颗晶片恐怕太费成本,因此其他技术较成熟的功能先行整合,所以现在TV常用2颗晶片。

不过32吋以下的LCD TV,整合趋势就相当明显,像脚步较快的晨星,和DVD晶片起家,原本MPEG技术就领先的联发科,都已经有整合型单晶片,其他许多厂商也都在开发中。

厂商表示,价格压力之下,整合型晶片是必然的趋势;控制IC的成本从原本的120∼130美元,降到现在的80几美元,未来往50美元降下去是可以预见的趋势。

LCD控制器 (1)

A[31]A[30]…A[1]A[0]B[31]B[30]…B[1]B[0]C[31]C[30]…C[1]C[0]…

4位或8位单扫描数据显示

0000 0004

0008

┇ …

1000

1004

┇ …

A[31: 0] B[31: 0] C[31: 0]

┇┇ L[3…1: 0] M[31: 0]

┇ …

A[31]A[30]…A[1]A[0]B[31]B[30]…B[1]B[0]C[31]C[30]…C[1]C[0]… L[31]L[30]…L[1]L[0]M[31]M[30]…M[1]M[0]

数据传送速率=水平尺寸×垂直尺寸×帧速率×模式值

• 帧速率的计算公式为

VCLK=MCLK/(VCLKVAL×2) 帧速率 ={[(1/VCLK)×(HOZVAL+1)+(1/MCLK)×(WLH+WDLY+LINEBLANK)]× (LINEVAL+1)}

• VCLK还可以使用下式计算:

VCLK=(HOZVAL+1)/{[1/(帧速率×(LlNEVAL+1))]- [(WLH+WDLY+LINEBLANK) /MCLK]}

液晶类型和扫描模式 单色液晶 4级灰度屏 16级灰度屏 彩色液晶

4位单扫描 1/4 1/4 1/4 3/4

液晶扫描模式值

8位单扫描或4位双扫描 1/8 1/8 1/8 3/8

(3)设置数据帧显示控制 • LCDBASEU:设置显示扫描方式中的开始地址(单扫描方

式)或高位缓存地址(双扫描方式)。 • LCDBASEL:设置双扫描方式的低位缓存开始地址。可以使

1 个像素

4位单扫描

LCD控制器ILI9320中文

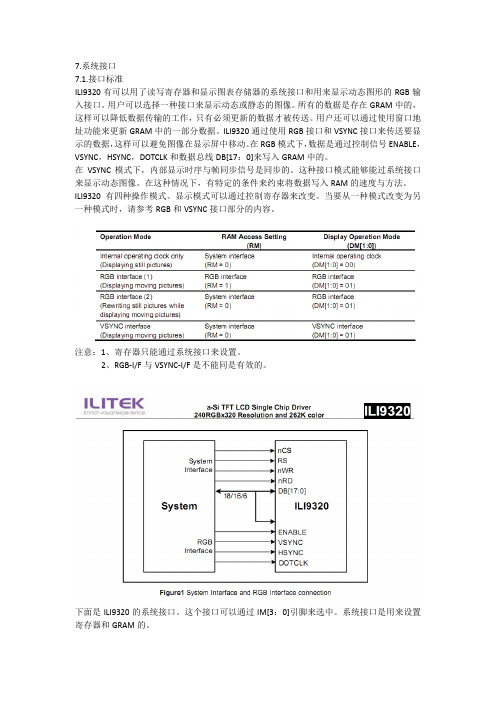

7.系统接口7.1.接口标准ILI9320有可以用了读写寄存器和显示图表存储器的系统接口和用来显示动态图形的RGB输入接口。

用户可以选择一种接口来显示动态或静态的图像。

所有的数据是存在GRAM中的,这样可以降低数据传输的工作,只有必须更新的数据才被传送。

用户还可以通过使用窗口地址功能来更新GRAM中的一部分数据。

ILI9320通过使用RGB接口和VSYNC接口来传送要显示的数据,这样可以避免图像在显示屏中移动。

在RGB模式下,数据是通过控制信号ENABLE,VSYNC,HSYNC,DOTCLK和数据总线DB[17:0]来写入GRAM中的。

在VSYNC模式下,内部显示时序与帧同步信号是同步的。

这种接口模式能够能过系统接口来显示动态图像。

在这种情况下,有特定的条件来约束将数据写入RAM的速度与方法。

ILI9320有四种操作模式。

显示模式可以通过控制寄存器来改变。

当要从一种模式改变为另一种模式时,请参考RGB和VSYNC接口部分的内容。

注意:1、寄存器只能通过系统接口来设置。

2、RGB-I/F与VSYNC-I/F是不能同是有效的。

下面是ILI9320的系统接口。

这个接口可以通过IM[3:0]引脚来选中。

系统接口是用来设置寄存器和GRAM的。

7.2.1.i80-system接口i80-system接口是通过设置IM[3:0]为“1010”电平选中。

8、寄存器描述8.1、ILI9320采用的是18位总路线接口结构的高性能微处理器。

ILI9320所有的功能模块在收到由外部微处理器以18-、16-、9-、8-位接口方式发的正确命令后才能起作用。

索引寄存器(IR)储存着可以写入指令与显示数据寄存器的地址。

寄存器选择信号(RS),读写信号(nRD/nWR)和数据总路线(D17-0)是用来读写指令和数据的。

ILI9320寄存器分为以后几类:索引寄存器用来指定寄存器的地址或将要写入RAM的地址。

状态寄存器表明了当前ILI9320内部的状态。

LCD用时序控制器(TCON)技术与特征研究

第10期2021年5月No.10May,20210 引言时序控制器是指能够令被控制对象按照一定的时间、秩序完成对应功能的一种逻辑控制方式,主要由电源控制基变换、机械式拨码定时、数字触发器等共计6个单元电路组成。

随着消费者需求的提升,应用于LCD 液晶显示屏的时序控制器必须具备引导高压驱动器芯片移动的功能,并提高黑白色背光的过滤强度,使显示屏的对比度提高至新的阶段,避免像素响应时间过长。

1 LCD用时序控制器的接口功能LCD 用时序控制器主要用于引导高压驱动芯片,完成对彩色滤光片的移动。

作为一个电路元器件,时序控制器经常被直接安装在玻璃显示屏之下,电路板的最下方位置。

与LCD 液晶显示屏连接后,时序控制器接收来自计算机中央处理器发出的命令,完成对液晶显示屏亮度及色彩的调整。

若要实现上述过程,必须明确时序控制器主要接口的功能。

(1)GPU 接口。

GPU 接口主要用于与常见的N 卡、A 卡(均为显卡,即Nvidia ,AMD ,Intel 等)进行连接,通过eDP 嵌入的方式,完成信号的发出与接收。

(2)eDP 接口。

eDP 接口为eDP 与时序控制器接口系统的一般性连接装置。

实现“Transmitter (图像信号处理发射机)”与“ML receiver (液晶显示屏信号接收器)”的连接。

当图像处理调整信号成功发送并被液晶显示器的接收器接收之后,经过Pixel Formatter (像素格式化程序)的处理,经由LCD interface (液晶显示接口)传输至LCD Display (液晶显示器)的Row Drivers (横排像素驱动程序,一个显示器由多排组成)和Column Drivers (纵列像素驱动程序,同样拥有多列)。

(3)AUX Ch interface (辅助接口)。

AUX Ch interface (辅助接口)与计算机图像处理系统中的eDP Transmitter 可互相发射并接收信号。

液晶显示器的驱动芯片 整理版

题目:学习心得报告編碼:Page:1/3使用于液晶显示器的驱动芯片主要分为两类,分别为gate driver与source driver。

Gate driver的主要功用是将液晶面板上一行一行的薄膜晶体管(TFT,thin film transistor)依序打开,好让source driver将位于液晶面板上的液晶电容(Clc,capacitor on liquid crystal)与储存电容(Cs,storage capacitor),充电到所需要的电压。

Gate driver名称的由来,是因为接到TFT的gate端,所以才称作gate driver。

此外,由于它是依序将一行一行的TFT打开,所以也称之为scan driver。

而就面板的坐标来说,连接到gate driver的走线,是位于Y轴上,所以也称为row driver。

同理source driver也有许多不同的称呼,而source driver的名称来由是因为这个驱动芯片是连接到TFT的source端,所以才叫做source driver。

此外当gate driver 将一行行的TFT打开时,source driver会将相对应的显示数据转换成电压,把液晶面板的电容充放电到相对应灰阶的电压,因此source driver也叫做data driver。

再者就整块面板的坐标来说,连接到source driver的走线是位于X轴上,因此也叫做column driver。

LCD source river/ate driver的工作频率1.VGA为例,起荧幕的分辨率为800*600,画面的更新频率为60Hz,因此每秒需要显示的画面资料量为800*600*60=28.8M,所以pixel clock需要为28.8MHz。

不过这只是所必须的最小工作频率而已,实际上SVGA的全部分辨率为1056*628,只不过一些分辨率并不是拿来显示画面之用的,实际上显示出来的画面只有800*600而已,这真正作为显示画面的部分称之为active field,而不显示的部分则称之为blanking。

LCD显示控制器原理

754

658

图3 行同步状态机状态转移图

Timing implementation

场同步状态机有v_video,v_front,v_sync, v_back四 种状态,它根据场行数计数器的计数值来进行状态翻转。

494

492

图5 场同步状态机状态转移图

Frame memory module

帧存控制模块原理如图5所示。

--- 翁开胜

content

1 LCD introduction 2 Controller principle 3 Controller module 4 Experiment

LCD introduction

LCD (Liquid Crystal Display) ,即液晶显示器。 可分为被动矩阵式及主动矩阵式两种不同的控制方 式。主动矩阵式也称TFT(Thin Film Transistor)。

帧存控制模块实现2个显存的“乒乓”切换,当DSP向其 中一个显存写显示信息时,由FPGA构成的帧存控制模块将 另一个显存的控制权交给LCD显示控制器图像处理模块,反 之亦然。

DSP访问显存的地址总线与FPGA 内LCD 显示控制器 图像处理模块的地址总线之间的切换通过多路选择器MUX 实现, DSP的数据总线与LCD显示控制器图像处理模块的数 据总线通过三态门挂在显存SRAM的数据总线上, 2路数据 总线的切换由切换信号SEL控制。

图2 VGA(640X480,60Hz)图像格式信号时序图

Timing implementation

VGA时序信号模块包括行点数计数器h_cnt、场行数计数器 v_cnt、行同步产生状态机h_state和场同步产生状态机v_state 等。行同步状态机有 h_video,h_front,h_sync,h_back四 种状态。

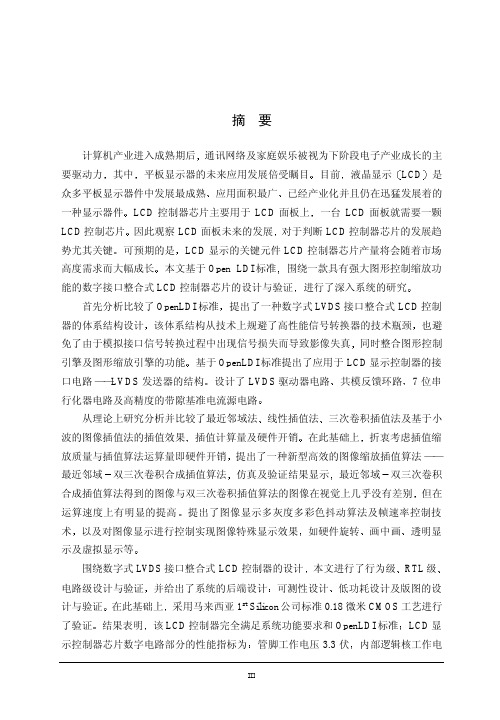

基于OpenLDI标准CMOSLCD控制器设计与验证

摘要计算机产业进入成熟期后其中目前LCDÓ¦ÓÃÃæ»ý×î¹ãLCD控制器芯片主要用于LCD面板上因此观察LCD面板未来的发展可预期的是本文基于Open LDI标准进行了深入系统的研究提出了一种数字式LVDS接口整合式LCD控制器的体系结构设计也避免了由于模拟接口信号转换过程中出现信号损失而导致影像失真基于OpenLDI标准提出了应用于LCD显示控制器的接口电路——LVDS发送器的结构共模反馈环路从理论上研究分析并比较了最近邻域法三次卷积插值法及基于小波的图像插值法的插值效果在此基础上提出了一种新型高效的图像缩放插值算法——最近邻域仿真及验证结果显示双三次卷积合成插值算法得到的图像与双三次卷积插值算法的图像在视觉上几乎没有差别提出了图像显示多灰度多彩色抖动算法及帧速率控制技术如硬件旋转透明显示及虚拟显示等本文进行了行为级电路级设计与验证可测性设计在此基础上结果表明LCD显示控制器芯片数字电路部分的性能指标为内部逻辑核工作电压1.8伏功耗为12.2mW液晶显示器低压差分信号帧速率控制可测性设计ABSTRACTAfter the PC industry has come into autumn, communication, network and household entertainment are regarded as main stimulus in the next period of electronic industry development. Thereinto, the application of the flat panel display in the future will be paid more attention. At the present time, LCD is the maturest and widest on application among all display devices. It has been put into industrialization and still has rapid development. So the development of LCD panel is the key to estimate the developing trend of the LCD controller chip. It is expected that the output of LCD controller chip will be greatly increased with the market mass requirement. This thesis concentrates on the design and verification of an integrated LCD controller with LVDS transmitter based on OpenLDI Standard.First OpenLDI Standard is analyzed and compared, the architecture of an integrated LCD controller with LVDS transmitter is introduced, which escapes the technical bottleneck of the high performance signal converter, and turn away image signal loss on the process of signal conversion at the analog interface. In addition, it realizes both image display controlling and image display scaling. The LVDS transmitter used as LCD controller interface is presented based on the OpenLDI Standard. LVDS driver, CMFB, 7 bits serializer and high precision bandgap-current reference are designed in the thesis.Theoretically, nearest neighbor, linear, cubic convolution and image interpolation based on wavelet are analyzed and compared on interpolation effect, computational complexity and hardware cost. Based on good image interpolation quality with low hardware cost, a new efficient algorithm of interpolation synthesizing nearest neighbor and bi-cubic convolution is proposed. The simulation results show that it has almost the same image interpolation quality and lower hardware cost as bi-cubic convolution. The dynamic dithering algorithm and FRC(Frame Rate Control) technique presented in this thesis provide an improved method for displaying image on LCD panel to greatly increase the number of grey shades or colors. Furthermore, some special effects such as hardware rotation, PIP, Ink-layer transparency and virtual display are realized through controlling image display data.Around the design of the integrated LCD controller with LVDS transmitter, this thesis process behavior, RTL, circuit level verifications, and system back-end design, including DFT, low power design and layout design and verification. The LCD controller has been taped out with standard 0.18ìm 1P4M CMOS technology in the 1st Silicon. The resultsshow that the LCD controller can fully satisfy system function requirements and OpenLDI Standard. The digital part of LCD controller work on 3.3V voltage, but the internal digital core work on 1.8V voltage, area is 11.8mm2, and power consumption is 12.2mW.Keywords: LCD, Controller, LVDS, Dithering, FRC, Scaling Algorithm, DFT1 绪论1.1 研究背景进入20世纪以来工业交通航空航天显示产业已经成为电子信息工业的一大支柱产业显示技术及相关产业的产品占信息产业总产值的45随着人们对大屏幕阴极射线管CRT色彩丰富响应速度快价廉等优点耗能大有X射线等致命弱点阻碍了它的发展Flat Panel Display以其体积小总量轻无辐射抗振性能好有效显示面积大逐渐引起众多显示器厂商及广大用户的关注应用领域覆盖了大小显示器应用的方方面面异彩纷呈发光型FPD Array按工作原理的不同可分为等离子体显示器包括ELD或LED场致发光显示器VFDÊܹâÐÍFPD按工作原理的不同可分为液晶显示器ECD电泳显示器PLZTÆäÖÐÒº¾§ÏÔʾLCD图1.1 LCD显示器产销量比较图人们预言信息化要求更多的大容量便携式的平板显示器件LCDÓ¦ÓÃÃæ»ý×î¹ã根据台湾省工研院经资中心研究报告预计到2005年LCD显示器件市场占有率将超过CRT显示器如图1.1所示通讯网络及家庭娱乐被视为下阶段电子产业成长的主要驱动力平板显示器的未来应用发展倍受瞩目液晶显示是众多平板显示器件中发展最成熟已经产业化并且仍在迅猛发展着的一种显示器件一台LCD面板就需要一颗LCD控制芯片对于判断LCD控制器芯片的发展趋势至为关键LCD显示的关键元件LCD控制器IC产量将会随着市场高度需求而大幅成长如图1.2所示2004年则可高达2.42亿美元LCDModule图1.3 LCD显示面板结构图现有LCD显示面板主流结构主要由LCD控制板及LCD模块两部分所组成所示一般包括有模拟式接口ADC/PLL能将PC主机或视频设备如DVD Player等输出的模拟在信号处理方面MCU及存储器等多灰度多彩色及特效显示处理等步骤由于LCD控制器市场竞争激烈产品技术的先进性及成本因素成为产品被市场接受与否的关键技术上来看相应的优点是功耗同时IC整合方式的发展趋势是从模拟式接口ADC/PLL与LCD控制器/OSD作整合(模拟接口模式)Ï൱¶àµÄ¹«Ë¾Ò²½«Êý×Öʽ½Ó¿Ú¼ÓÒÔÕûºÏ¹ú¼ÊÖøÃûÉè¼Æ¹«Ë¾½üÆÚÓÖÍƳöÁËÁùºÏÒ»µÄÖÇÄÜÃæ°åÔ¤¼ÆÏÂÒ»½×¶Î¿ÉÕûºÏµÄÔª¼þ½«ÊÇÂß¼-Ôª¼þ΢¿ØÖÆÆ÷及存储元件如SDRAM/EEPROM/ROM等主要技术瓶颈来自整合高频模拟元件模数转换器模数转换器工作频率为100-110MHzµ±Æ½°åÏÔʾÆ÷ÏòS XGA分辨率(1280x1024)的17-18吋产品发展时而应用于20吋以上产品时才能使UXGA分辨率(1600x1200)产品显示出最佳状况仅有一家国际领导设计公司Genesis宣称成功整合165MHz模数转换器(ADC)Òò´ËÈÔÒÔÔ-ÓзÖÁ¢Ê½½â¾ö·½°¸ÎªÖ÷Êý×ÖʽʽԪ¼þLVDS/Controller/OSD/TCON单独整合提供ADC/PLL整合晶片给从事数字式元LVDS/Controller/OSD/TCON整合晶片的LCD控制器IC公司依美国市场研究机构Display Search及台湾省工研院经资中心的市场资料显示占有60%的市场而2002年数字式接口及双模模式接口产品合并市场占有率已超过50%´ïµ½36%Ô¤¼Æ½ñÄêÊý×Öʽ½Ó¿Ú²úÆ·Êг¡Õ¼ÓÐÂʽ«³¬¹ý˫ģģʽ½Ó¿Ú²úÆ·ÓÉ´Ë¿´À´ADC²ÉÈ¡Êý×Ö½Ó¿ÚÕûºÏʽLCD控制器方案综上所述也引起国外及台湾省众多IC设计公司相继跨入此领域的研究往高端产品低成本的解決方案是现有业界寻求发展并脱颖而出的方向有必要对LCD图象彩色增强并尽早自主设计开发具有强大图形控制功能的数字接口整合式LCD控制器芯片LCDÆäÖ÷Òª×÷ÓÃÊÇΪµç×ÓÐÅÏ¢É豸ËùʹÓõÄÒº¾§ÏÔʾÆ÷¼þÌṩʱÐòÐźÅÓëÏÔʾÊý¾ÝÊÇMCU与液晶显示系统之间的接口又可以脱机独立控制并驱动液晶显示[7]ʹµÃÒº¾§ÏÔʾÆ÷¼þ¸ü¼ÓÈÝÒ×Ó¦ÓÃÓÚÖÇÄÜ»¯ÏµÍ³ÖÐÔÚÍê³ÉͼÏñËõ·Å´¦ÀíµÄͬʱ¶¶É«ÊÇƽ°åÏÔʾ±Ø²»¿ÉÉÙµÄÒ»¸ö²¿·ÖÀûÓöÔÖ÷°åÊä³öµÄͼÏñ·Ö±æÂʽøÐÐÉèÖò¢±£³ÖͼÏñÏÔʾµÄÇåÎúºÍÎȶ¨ÔÚLCD中采用模拟或数字接口一般而言模拟视频常用于视频信号传输距离比较远的台式机采用数字接口而现在台式机也大量采用LCD显示器但是在医学超声和X射线等医学图像处理对灰度有严格要求的应用中表1.1直观地表现出了LCD显示器模拟接口与数字接口性能的对比[8-9]表1.1 LCD 显示器模拟接口与数字接口性能的对比表数字接口模拟接口优点12ÏòÁ¿µÄµ÷Õû价格便宜12缺点1LVDS 和TMDS21. 为避免像素闪烁的出现向量与模拟信号的完全一致3. 显示器内部要加入负责模数转换的电路1.2.1 模拟接口LCD 控制器模拟接口LCD 控制器将图形引擎处理好的数字视频信号经数模转换器而转换成模拟信号再在LCD 显示器模块中经模数转换器将模拟视频信号转换成数字视频信号来驱动LCD 显示器的相应的显示单元信号传输形式上并且在很长的电缆上都有效LCD控制器图1.4 模拟接口LCD 显示器图像信号流程图1.2.2 数字接口LCD控制器LCD显示器从本质上来说是数字产品而如图1.4所示的图像信号转换引入了信号失真源是完全没有必要的LCD显示器不能精确地还原像素的位置尽管大多数模拟接口地LCD显示器有相位和时钟控制电路来调节显示器模块电路但显然不可能完全消除所有干扰因此目前高端LCD控制器与其相应地LCD显示模块直接支持数字接口就不再需要调节相位和时钟了而且在慢刷新速率时LCD显示器也不会出现图像抖动可以将LCD控制器的刷新速率设置得更慢并加速图像处理的速度A/D和D/A传到LCD显示器的数据几乎没有信号损失黑色像素仍然显示为黑色而不是暗灰色使图像看起来更好同时如色彩这样做不仅可以节省信号转换用的数模有助于降低成本同时在用户使用上如大尺寸的计算机LCD显示器如个人数字助理PDA为用户提供了极大的方便设计数字接口LCD控制器及数字接口LCD显示模块但是在数字接口方面OpenLDI是由美国国家半导体所主推的LCD数字接口标准DVI是由Intel, Compaq, Silicon Image等公司所主推的LCD数字接口该接口标准Transition Minimized Differential Signaling因此有可能成为数字接口标准的最有竞争力的接口技术包括传输最小差分信号(TMDS)Ä£ÄâµÄÊÓƵÕóÁÐ接口是一种老化的技术主要是因为要使这些系统适应模拟接口需要附加费用然后在驱动带有模拟连接的LCD显示器之前1996年开始对视频监视器OpenLDI标准是由美国国家半导体所主推这些公司涉及半导体计算机体系它为显示源和显示设备的数字化连接提供了一种开放式标准也不需加入任何组织成为会员即可使用该标准的目的是为了在显示源和显示设备传输数据显示图像失真的可能还可以减少电磁干扰在OpenLDI标准中严格定义了低压差分信号(LVDS)的接口的信号格式电器特性同时低压差分信号(LVDS)在IEEE P1596.3¼°ANSI/EIA/EIA-644Á½±ê×¼ÖÐÒ²Óж¨ÒåËüÖ÷ÒªÃæÏò¿ÉÀ©Õ¹Ò»ÖÂÐÔ½Ó¿ÚSCI(Scalable Coherent Interface)»¹¶¨ÒåÁËSCI协议中包交换时的编码格式低压差分信号LVDS是一种低摆幅的差分信号技术通过其低压幅度和低电流驱动输出实现了低噪声和低功耗现在它工作电压低并且由于发送的是差分信号它产生的噪音最小低压差分信号LVDS数字接口是一种理想的接口方案1.2.2.2 基于DVI标准TMDS接口1998年9月DeveloperDigital Display Working Group使得数字显示接口标准化工作加快了进程Digital Video Interface数字视频接口DVI标准规定了用于计算设备与显示器件之间的数字接口使系统开发者们能添加一些零部件以适合他们的特殊应用为了反映工业界众多的要求并易于向数字化过渡DVI标准规定了两种机械特性完全相同地连接器VIDVI标准采用转换最小化差分信号TMDS将LCD控制器的图形数据传送到LCD显示器包括Image Link公司制定的转换最小化差分信号TMDS协议的详细说明连接器的机械规格和信号引脚的配置该标准还涵盖了高速率数据的信号质量特性TMDS作为标准数字接口放映机及视频卡上的LCD控制器上VESA P&D DFP ͬʱҲµÃµ½Intel Compaq Dell IBM转换最小化差分信号TMDS与与低压差分信号LVDS类似和差分信号传送转换最小化(Differential)叙述的是利用一对互补信号来传输信号的方法实现了直流平衡XORXNOR减少了由高到低和由低到高信号转换的次数时钟边界独立性(clock-dege independence)和易测量性TMDS采用双股铜线电缆能使数据可靠地传输好几米对于在宽范围电缆长度和媒介上提供稳定而可靠的高速数据传输来说图1.6 TMDS数字接口在LCD显示系统中的连接图TMDS数字接口在LCD显示系统中的连接图如图1.6所示绿接口可传输的数据Array速率达到1.65 Gbit/Sec分辨率可从VGA4801920与QXGA15361.2.2.3 LVDS数字接口与TMDS数字接口的比较OpenLDI标准与DVI标准最有可能成为LCD显示系统数字接口的最有竞争力的标准现从以下几个方面进行比较输出驱动器的差别LVDS是推挽式的电流驱动器从另一端流回电流大小相等这种设计可以用来驱动双绞线产生的电磁干扰(EMI)较小但是电流在两端之间流动因此要注意电源线与地线靠近所以一般建议在双轴电缆的每对线上使用屏蔽层来屏蔽EMIÆÁ±Î²ãÔö¼ÓÁ˵çÀµijɱ¾绞线对数和屏蔽方式对于每个像素6位的应用中而用TMDS数字接口也需要3对数据线加上一条时钟线采用LVDS数字接口需要4对数据线和一条时钟线在8位双像素的应用中而采用TMDS数字接口只要6对数据线加时钟信号TMDS数字接口和LVDS数字接口用相同的电缆线对数或前者比后者少1到2对线的结构以及屏蔽层数量都直接影响成本由于双轴电缆每一对线都需要一个屏蔽层3Ôò±íʾÊý¾Ýλ¿íÔ½¿íÒÔ¼°¸ü´óµÄµçѹºÍζÈÈÝÏÞÐźÅƵÂʵ͹¦ºÄҲСÔÚ162MHz的时钟频率下而TMDS数字接口数据位宽为625ps·Ö±ðΪ446ps 与312ps´«Ê䶶¶¯ÓÉÓÚ´æÔÚÕâЩÒòËØÕâÁ½ÖÖʱÐòÈçͼ1.7所示代码带宽在直流均衡模式下而TMDS数字接口只有80% 160MHz双像素TMDS数字接口应用中5´«ÊäËÙÂʵÍÔÚ¿ÕÏÐÆڼ䳡ͬ²½ÐźÅVSYNC和HSYNC以及DE)×¢Òâµ½Õâ¶ùÿ֡ÖнöÓÐÁ½´ÎʱÖÓÐźÅÑØÖÐת»»ÔÚ¿ÕÏÐʱ¼äÄÚTMDS数字接口传输的位串最大化转换次数在空闲时间内每对线达到最大的8次转换对某些状态的研究表明将空闲时间计算在内LVDS数字接口具有较低的数据转换速率因此功耗较低在提高集成度的同时并没有增加功耗LCD显示用的控制器IC将由多颗分立式转变为整合式的单颗产品1.3.1 集成式LCD控制器将取代分立式LCD控制器一般IC产品在开发初期大多为均为分立式的产品而且如果在设计上有错误(Bug)的情形发生时而在产品技术趋于成熟之后也会走向整合之路由于分立式LCD控制器IC的发展严重受制于A/D转换器的高性能1.3.2 LCD控制器数字式接口将取代模拟式接口LCD控制器中的图形控制引擎及图形缩放引擎內部所做的图形处理时均属于数字信号的处理显示控制器的輸出均为模拟RGB信号随着数字接口标准制定工作的开展期间由于在数字RGB信号的发展了历程中出现了低压差分信号LVDS与转换最小化差分信号TMDS的标准的混战于是模拟接口式LCD控制器遂成了过渡时期的产品必须先由D/A 转换器将数字信号转换成模拟信号这两次信号的转换不但毫无意义而且也会造成了信号失真如画面波纹等所以在不久的将来数字接口将取代传统的模拟接口Smart PanelʹµÃÔ-±¾Î»ÓÚLCD屏模块的时序控制器TCON (Timing Controller)亦有整合进入LCD控制器IC的趋势因此未来当时序控制器TCON亦整合进LCD控制器IC之后这种LCD显示器的结构即称为智能屏Smart PanelÊ¡µôÊý×Ö½Ó¿ÚоƬÒÔ¼°DC/DC变压芯片Electro Magnetic Interference而且节省了封装以及TFT显示模块的成本和功耗但目前仍未普及因为智能屏Smart Panel的规格兴起将会侵蚀LCD显示器厂商的附加价值拥有智能屏Smart Panel的趋势将只是时间早晚的问题该标准将LVDS的性能特点应用到平板显示器的列驱动电路与TCON的芯片的连接上由于这种接口具有降低EMI及省功耗的功能相信在不久之后相关产品可望陆续出现噪声等方面有进一步改善1.4 本文研究内容及章节安排本文围绕华中科技大学电子科学与技术系集成电路设计中心与武汉亚芯微电子有限公司合作课题由上面分析可知但在显示性能上明显存在不足本文希望基于Open LDI标准规避了高性能信号转换器的技术瓶颈本文基于上述目的该体系结构同时整合了图形控制引擎芯片及图形缩放引擎芯片缩小芯片面积后封装成本及材料成本等都随之降低第一章概述本文的研究背景引出本文的研究内容第二章分析Open LDI标准在一块芯片上同时整合图形控制引擎及图形缩放引擎的功能基于OpenLDI标准提出应用于LCD控制器的接口电路——LVDS发送器的结构共模反馈环路7位串行化器第四章从理论上研究分析并比较最近邻域法三次卷积插值法及基于小波的图像插值法的插值效果在此基础上提出一种新型高效的图像缩放插值算法——最近邻域并给出仿真及验证结果以及对图像显示进行控制实现图像特殊显示效果画中画第五章给出LCD显示控制器芯片的后端设计低功耗设计及系统芯片版图设计与验证2 基于Open LDI标准LCD控制器体系结构设计2.1 引言作为主要人机接口设备之一的显示器是电子信息众多领域中不可或缺的重要组成部分低功耗易集成和轻巧便携等特点占据了其中很大份额一套完整的液晶显示系统主要由五部分组成LCD控制器LCD驱动器和液晶显示器LCD控制器的主要作用是为电子信息设备所使用的液晶显示器提供时序信号与显示数据是MCU与液晶显示屏之间的接口又可以脱机独立控制并驱动液晶显示使得液晶显示器件更加容易应用于智能化系统中LCD显示控制器同时具有管理显示存储器的能力MCU通过对液晶显示控制器的指令来操作显示输出结果模拟接口式LCD控制器芯片采用两块集成电路来实现其中一块是带D/A转换器的图形控制引擎如显示效果增强画中画及透明显示等实现图形缩放模拟接口式LCD控制器芯片在将LCD屏显示数据传送给LCD显示屏模块时在LCD显示器模块中再通过A/D转换器转回数字信号导致LCD显示器显示效果不佳同时分立多芯片解决方案封装成本及材料成本都明显较高本文基于OpenLDI标准提出了数字接口整合式LCD控制器的体系结构设计该体系结构规避了高性能信号转换器的技术瓶颈同时整合图形控制引擎芯片及图形缩放引擎芯片缩小芯片面积后封装成本及材料成本等都随之降低提出了一种基于OpenLDI标准的LCD图像控制芯片的体系结构仿真结果显示该体系结构完全符合系统设计的要求开放式LVDS 显示接口Open LVDS Display InterfaceNational Semiconductor CompanyÁªºÏ¶à¼ÒÉæ¼°°ëµ¼Ìå¼ÆËã»úϵͳ¸øÏÔʾԴ¼°ÏÔʾÉ豸µÄÊý×Ö»¯Á¬½ÓÌṩÁËÒ»ÖÖ¿ª·Åʽ±ê×¼Ò²ÎÞÐèʹÓÃÕß¼ÓÈëÈκÎ×éÖ¯³ÉΪ»áÔ±±ã¿ÉʹÓÃÒÔOpenLDI为标准起草的其他标准被视频电子标准协会和美国国家标准局广泛应用BlueHsynVsynPclkDE图2.2 OpenLDI结构图随着数字显示设备的发展OpenLDI标准描述了一个从显示源到显示设备的纯数字化接口OpenLDI标准逻辑接口规范部分描述一种即插即用的接口形式同步信号及控制信号转换为串行的位数据流并在LCD显示模块中又重新将串行的位数据流恢复为并行像素数据图2.2所示为OpenLDI结构图采用最少的导线同步信号及控制信号包括机械接口和电缆连接18位单像素18位双像素及24位双像素格式OpenLDI标准描述了并行像素数据流在显示源和显示设备之间串行传输A0及两条时钟线18位单像素格式使用A0到A2三条串行数据线18位双像素格式A0到A224位双像素格式将使用A0到A7八条串行数据线只有被使用的串行数据线才使能OpenLDI标准有两种工作模式任何一种模式都可以用来传输单像素及双像素格式下面图示中R B分别表示单像素格式中的红蓝分量GU绿而RL BL分别代表双像素中低像素红蓝分量Vsyn垂直同步控制信号和数据使能信号用来执行特殊操作的附加信号CntlE 和CntlF也可能一起被发送所以DC直流平衡工作模式在本文中不作详细分析每根信号线除了传送像素和控制信息外该位就是DC平衡位通过选择性地发送原始的或转化的像素数据来实现只有像素和控制信息从显示源发送到显示设备图2.3所示为18位单像素非平衡模式下输出信号线A3到A7不用并保持为固定值输入的RGB和控制信号传输方式图RES为预留位可取任意值输入的RGB和控制信号传输方式图A7不用并保持为固定值图2.6所示为24位双像素非平衡模式下 RES为预留位可取任意值图2.5 18位双像素非平衡模式数据传输方式图图2.6 24位双像素非平衡模式数据传输方式图2.2.2 OpenLDI标准电气接口规范OpenLDI标准规定用于发送LVDS信号的必须满足如表 2.1所示的ANSI/EIA/TIA-644的要求即最大像素时钟频率为160MHz表2.1 ANSI/EIA/EIA-644标准参数定义最小值最大值单位VOD 差分输出电压247 454 mVVOS 共模电压 1.125 1.375 VVOS 共模电压漂移50 mVI SA,I SB短路电流24 MA上升时间/下降时间nS200Mhz 0.26 0.3 Bit timeIin输入电流20100 mV V in输入电压范围0 2.4 V 同时一般在LVDS信号线上采用预加重Array技术图中描绘了样板信号粗黑线图2.7 预加重模板图2.2.3 OpenLDI标准物理接口规范OpenLDI电缆集线器必须有一根两端都含有OpenLDI插头或一端有OpenLDI插头一端永久固定于显示设备的电缆电缆的最大长度是10米LVDS电缆达到最大长度时电缆中各导线必须相互绝缘2.3 基于Open LDI 标准的LCD 控制芯片的体系结构设计根据以上分析提出一种基于Open LDI 标准的整合式数字LCD图像控制芯片的体系结构框图如图2.8所示图形显示控制图中所示的系统锁相环模块在本论文中不作研究[17-20]CLKI图2.8 基于Open LDI 标准的数字LCD 图像控制芯片的体系结构框图2.3.1 MPU 接口通过系统总线接收MCU 的命令和数据MPU 接口模块提供了LCD 控制器和MCU 之间的通信通道LCD 控制器也可以通过接口模块向MCU 反馈所需的状态信息从而产生不同的显示效果可以直接支持多达八大类型的MCU 总线形式使用握手信号线coldfireGeneric #2通用MCU 接口主要应用包括NEC VR4102/4111/4181AIntel StrongARM SA-1110Generic 8-bit processorHitachi SH3/SH4针对Hitachi采用SuperH结构CPU的接口主要应用包括Motorola MC68K1/MC68K2针对Motorola 采用 68000 结构CPU的接口主要应用包括68K1系列的MC68HC000MC68EC000等Motorola Dragonball针对Motorola采用68000结构CPU的接口主要应用包括Dragonball系列的MC68EZ328MC68VZ328ÎÞÎÕÊÖÐźÅÏßÕâЩ×ÜÏßʱÐò´¦Àíµ¥ÔªÍ¨¹ýоƬÅäÖÃÒý½ÅCNF4和CNF[2:0]的设置来选择cs_panel interface主要针对不同显示模式在读取显存数据时进行取址运算画中画及虚拟显示等特效显示效果在Ink Layer透明显示模式下存储前景和背景两幅图像可以是前景图像的空白区象素值如果相等则输出背景图像这时输出图像的视觉效果就是前景图像覆盖在背景图像上由于嵌入式缓存需要存储两幅图像图形显示控制模块主要由四个部分组成图2.10 图形显示控制模块电路结构图地址产生器主要完成对地址的计算以读取到相应的数据如旋转Picture In Picture实际上都是通过对功能寄存器的设置之后读取出正确的数据而完成的快速的数据存储和读取单元用来存储从Memory Interface传送过来的SRAM中图象数据输出到屏上的数据是不能停顿的图形显示控制模块输出的图象数据是不能为空的Memory Interface除了读取相应的数据给图形显示控制模块之外因而并不能保证每一次FIFO提出的读数据请求都能够马上相应这里采用了双指针的FIFO±È½ÏÕâÁ½¸öÖ¸ÕëµÄλÖõ±FIFO中数据将要读完时要求立刻读取数据Ink Layer 透明显示比较器也就是将两幅图象的数据与预先设定的一个参考值进行象素点的比较这是输出的图象就会将其中的一幅图象作为背景需要注意的是故在使用这种功能时时序链路V sny和H sny2.3.3 图形缩放控制为了在不同的显示模式下取得良好的视觉效果以匹配显示器设定的显示分辨率同时也可以是图像尺寸的改变图形缩小即图像数据量的减少的过程叫做图像数据抽样图形放大即图像数据量增加的过程称为图像数据插值所以通常将图像缩放的过程就简称为图像插值[21,22]Ò²¾ÍÊÇÔö¼ÓͼÏñµÄ·Ö±æÂÊËüÓ¦¸Ã¼ÈÄܱ£Ö¤Í¼Ïñ±ßÑصĹ⻬ÐÔÒ²¾ÍÊÇÓ¦¸Ã¾¡¿ÉÄܵı£³ÖÔ-ͼÏñµÄ»ù±¾ÌØÕ÷²»±ä图2.11 数字图像缩放的整个过程图数字图像缩放地基本原理是函数或算法离散模型求得连续模型参数进而得到缩放图像[23]ͼÖÐS 为图像缩放倍率先将数字图像),(n m f d 恢复为模拟图像),(y x f a µÃµ½Ëõ·ÅºóµØÊý×ÖͼÏñ),(l k S d输出至显示终端新的采样周期T比原采样周期T小SS时<图像便被放大当1则在相等的时间内采样到的离散象素少显然图像的尺寸保持不变故大大的提高了传输速度LVDS因为以差分形式传输信号低电磁干扰等优点[24,25]»ùÓÚOpenLDI标准LVDS驱动器用来发送串行LVDS数据以及LVDS传输时钟CMOS串行化器是用来将并行CMOS数据按一定的时钟速率转换成串行数据图2.12所示为 OpenLDI标准规定的24位单像素非平衡模式LVDS 发送器系统图电荷泵锁相环及带隙基准源是为各驱动器公用电荷泵锁相环产生系统时钟的7倍频时钟每个通道并串转换电路接收并行的7位数据然后数据信号及像素时钟信号经过驱动器缓冲模块。

液晶显示器的程序设计

液晶显示器的程序设计概述液晶显示器(Liquid Crystal Display,简称LCD)是一种常见的显示设备,广泛应用于计算机、电视、方式等电子设备中。

液晶显示器的程序设计是为了控制和管理液晶显示器的工作,包括显示图像、显示文字、调节亮度和对比度等功能。

LCD控制器液晶显示器的控制是通过液晶显示器控制器(LCD Controller)进行的。

LCD控制器是一种专门设计的芯片,用于控制液晶显示器的各个参数和功能。

LCD控制器的主要任务是将输入的图像数据转换为适合液晶显示器显示的信号,并发送给液晶显示器。

显示图像在液晶显示器的程序设计中,显示图像是最基本的功能之一。

通常,液晶显示器的图像数据是以像素(Pixel)的形式存储和传输的。

程序设计需要将要显示的图像数据转换为液晶显示器可识别的信号,并设置显示的坐标和尺寸。

程序还需要处理图像的刷新和更新,以保持显示的连续性和流畅性。

显示文字液晶显示器还可以显示文字信息。

在程序设计中,显示文字需要使用字符编码和字库来实现。

字符编码是将字符映射为相应的二进制代码的过程,而字库是存储和管理字符的集合。

程序设计需要将要显示的文字信息转换为相应的字符编码,并从字库中获取对应的字符数据。

然后,将字符数据转换为液晶显示器可识别的信号,并设置显示的位置和样式。

调节亮度和对比度液晶显示器的亮度和对比度是可以调节的。

在程序设计中,调节亮度和对比度需要通过设置LCD控制器的参数来实现。

可以通过增加或减少LCD控制器的驱动电流、PWM调光等方式来调节液晶显示器的亮度。

对比度的调节则可以通过调整LCD控制器的电压差或电压偏置等来实现。

动态效果液晶显示器的程序设计还可以实现一些动态效果,如渐变、闪烁、滚动等。

这些动态效果可以通过在程序中控制图像和文字的显示位置、透明度、曝光时间等来实现。

程序设计需要根据实际需求,对液晶显示器的参数进行精确控制,以实现所需的动态效果。

液晶显示器的程序设计包括显示图像、显示文字、调节亮度和对比度等功能,以及实现一些动态效果。

LCD Driver(液晶驱动器)

LCD Driver(液晶驅動器)在單片機的應用中,人機界面佔據相當重要的地位。

人機界面主要包括事件輸入和結果指示,事件輸入包括鍵盤輸入,通訊介面,事件中斷等,結果指示包括LED/LCD顯示、通訊介面、週邊設備操作等。

而在這些人機界面當中,LCD 顯示技術由於其具有介面友好,成本較低等特點而在很多應用場合得以廣泛應用。

我們在第一章SH6xxx單片機分類中就介紹過,LCD類單片機是SH6xxx單片機產品線的一個重要類別。

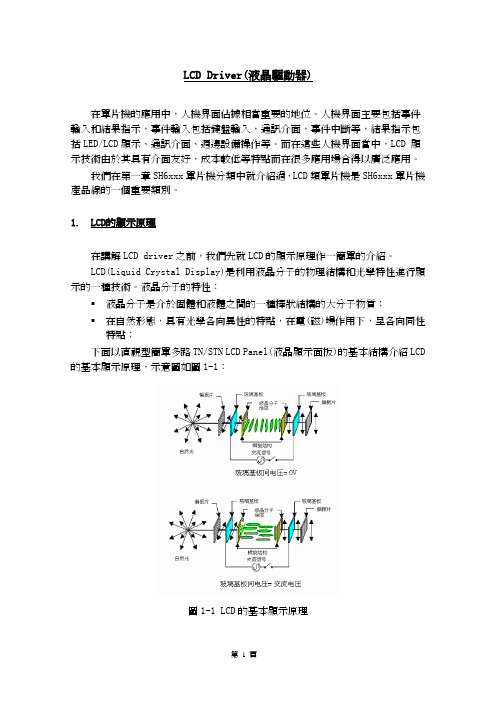

1.LCD的顯示原理在講解LCD driver之前,我們先就LCD的顯示原理作一簡單的介紹。

LCD(Liquid Crystal Display)是利用液晶分子的物理結構和光學特性進行顯示的一種技術。

液晶分子的特性:液晶分子是介於固體和液體之間的一種棒狀結構的大分子物質;在自然形態,具有光學各向異性的特點,在電(磁)場作用下,呈各向同性特點;下面以直視型簡單多路TN/STN LCD Panel(液晶顯示面板)的基本結構介紹LCD 的基本顯示原理,示意圖如圖1-1:圖1-1 LCD的基本顯示原理整個LCD Panel 由上下玻璃基板和偏振片組成,在上下玻璃之間,按照螺旋結構將液晶分子有規律的進行塗層。

液晶面板的電極是通過一種ITO 的金屬化合物蝕刻在上下玻璃基板上。

如圖所示,液晶分子的排列為螺旋結構,對光線具有旋旋光性,上下偏振片的偏振角度相互垂直。

在上下基板間的電壓為0時,自然光通過偏振片後,只有與偏振片方向相同的光線得以進入液晶分子的螺旋結構的塗層中,由於螺旋結構的的旋旋光性,將入射光線的方向旋轉90度後照射到另一端的偏振片上,由於上下偏振片的偏振角度相互垂直,這樣入射光線通過另一端的偏振片完全的射出,光線完全進入觀察者的眼中,看到的效果就為白色。

而在上下基板間的電壓為一交流電壓時,液晶分子的螺旋結構在電(磁)場的作用下,變成了同向排列結構,對光線的方向沒有作任何旋轉,而上下偏振片的偏振角度相互垂直,這樣入射光線就無法通過另一端的偏振片射出,光線無法進入觀察者的眼中,看到的效果就為黑色。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Design Objectives

• Use the Liquid Crystal Display (LCD) on the Altera SOPC board to display information • Implement a design on the APEX 20KE452-1X that interfaces to the Hitachi LCD controller

rs= 1 rw= 1 e= 0 wr_done= 0

Idle

Write1 Write3

rs= write_rs rw= 0 e= 0 wr_done= 1

Write2

rs= write_rs rw= 0 e= 1 wr_done= 0

rs= write_rs rw= 0 e= 0 wr_done= 0

LCD Controller

Example Design Review Dr. Gruenbacher AprilHale Waihona Puke 12, 2004Topics

• • • • • • • Objectives Block Diagram Model Interface Definition Design Description Design and Test Plan Current Status Issues

S tart_Mode

write_data = 8'h06; write_rs = 1'b0; begin_write = 1'b1;

~ wr_done

Wait_D

write_data = 8'h44; write_rs = 1'b0; begin_write = 1'b0;

Wait_H

write_data = 8'h48; write_rs = 1'b0; begin_write = 1'b0;

Wait_Clear

write_data = 8'h01; write_rs = 1'b0; begin_write = 1'b0;

wr_done

Wait_Display

write_data = 8'h0f; write_rs = 1'b0; begin_write = 1'b0;

wr_done ~ wr_done ~ wr_done ~ wr_done wr_done

• DB7 indicates a busy flag during reads • Intermediate SN74LVT245BDW controlled by the RW line

Design Description

• Clock divider

– // Generate slower FSM clock by dividing clk_fast by 2^14

• Synthesis using Synopsys Design Compiler

– final target will be APEX20K400

• Final place and route using Altera QuartusII • Test and verification on APEX SOPC board

Bus state machine

~ busy begin_write ~ begin_write rs= 1 rw= 1 e= 0 wr_done= 0 rs= 1 rw= 1 e= 0 wr_done= 0 busy

Read1

Read2

rs= 1 rw= 1 e= 1 wr_done= 0

R ead3

begin_write is asserted by the data state machine busy is the value of bit DB7during a read wr_done is used to indicate the main state machine that a write transaction has finished (used by data state machine)

always @(negedge ar or posedge clk_fast) if(~ar) clkdiv_cntr <= 4'b0; else clkdiv_cntr <= clkdiv_cntr + 1; assign fsm_clk = clkdiv_cntr[13];

• Bus state machine • Data state machine

Design and Test Plan

• All designs and test benches written in Verilog • Behavioral compile and simulation using Synopsys VCS

– Test bench will allow verification of intended bus protocol, but will (cannot) verify Hitachi LCD operation

Bus code

• Three state (bidirectional) implementation:

assign lcd_db = ~lcd_rw ? write_data_reg : 8'bzzzzzzzz;

Data is registered (clocked) to prevent glitches:

write_data = 8'h01; write_rs = 1'b0; begin_write = 1'b1;

S tart_Display

write_data = 8'h0f; write_rs = 1'b0; begin_write = 1'b1;

~ wr_done

Reset

write_data = 8'h00; write_rs = 1'b0; begin_write = 1'b0;

Wait_Mode

write_data = 8'h06; write_rs = 1'b0; begin_write = 1'b0;

D

write_data = 8'h44; write_rs = 1'b0; begin_write = 1'b1;

wr_done

H

write_data = 8'h48; write_rs = 1'b0; begin_write = 1'b1;

• Reading the busy flag caused a space to be inserted between each character • Removing/bypassing the read cycles has temporarily avoided this problem

Summary Info.

• Blah, blah, blah….. • Other information you may provide in your presentation:

– Individual assignments/responsibilities – Design Hierarchy (how you are breaking the design into separate modules) – ???

wr_done

Data state machine code (Ex.)

always @(negedge ar or posedge fsm_clk) if(~ar) cs = Reset; else cs = ns; always @(cs or wr_done) begin case(cs) D: begin

• Test bench

– 100% written

• 100% verified in VCS

Issues

• Resolved

– Maximum bus speed to LCD Controller

• Runs well with 8 kHz fsm_clk

• Outstanding

– Busy flag read from LCD Controller

– Visual confirmation of the characters displayed on LCD

Current Status

• Design

– 100% code written – 100% synthesized in Design Compiler – 100% place and route in Quartus

// Write the letter D write_data <= 8'h44; write_rs <= 1'b1; begin_write <= 1'b1; ns <= Wait_D;

end Wait_D : begin write_data <= 8'h44; write_rs <= 1'b1; begin_write <= 1'b0; // Don't allow another write to begin if(wr_done) ns <= L; else ns <= Wait_D; end …

External Interfaces

• Asynchronous Reset (ar, active low) • Clock : 66 MHz

– Divide by 2^(13) for internal clock rate