16550说明

CMS1650 用户手册说明书

CMS1650用户手册LED驱动控制/键盘扫描专用集成电路V1.0请注意以下有关CMS知识产权政策*中微半导体公司已申请了专利,享有绝对的合法权益。

与中微半导体公司MCU或其他产品有关的专利权并未被同意授权使用,任何经由不当手段侵害中微半导体公司专利权的公司、组织或个人,中微半导体公司将采取一切可能的法律行动,遏止侵权者不当的侵权行为,并追讨中微半导体公司因侵权行为所受的损失、或侵权者所得的不法利益。

*中微半导体公司的名称和标识都是中微半导体公司的注册商标。

*中微半导体公司保留对规格书中产品在可靠性、功能和设计方面的改进作进一步说明的权利。

然而中微半导体公司对于规格内容的使用不负责任。

文中提到的应用其目的仅仅是用来做说明,中微半导体公司不保证和不表示这些应用没有更深入的修改就能适用,也不推荐它的产品使用在会由于故障或其它原因可能会对人身造成危害的地方。

中微半导体公司的产品不授权适用于救生、维生器件或系统中作为关键器件。

中微半导体公司拥有不事先通知而修改产品的权利,对于最新的信息,请参考我们的网站目录1.产品概述 (1)1.1功能特性 (1)1.2特性说明 (1)1.3适用领域 (1)1.4内部结构框图 (1)1.5管脚分布 (2)2.通讯协议 (3)3.键盘扫描码 (5)4.控制命令 (5)5.显存地址 (6)5.1一个完整的写显示时序 (7)6.应用电路 (8)7.电气参数 (9)7.1绝对最大额定值范围 (9)7.2推荐工作条件范围 (9)7.3电气特性 (10)7.4内部时序参数 (10)7.5接口时序参数 (11)8.封装 (12)8.1SOP16 (12)8.2DIP16 (13)9.版本修订说明 (14)1. 产品概述1.1MCU输1.2⚫⚫⚫⚫⚫⚫⚫⚫⚫1.31.4A/KI1B/KI2C/KI3D/KI4E/KI5F/KI6G/KI7DP/KP1.5 管脚分布2. 通讯协议CMS1650采用2线串行传输协议通讯。

uart16550IP核的设计与FPGA的实现

图2.1UART16550基本结构图

下面将介绍整个UART工作原理。

CPU通过CPU接口模块设定整个UART初始状态,如是奇校验还是偶校验、波特率数值和停止位的位数。波特率发生器分频出设定好的波特率并以设定的波特率控制发送和接收模块以达到发送和接收的同步。发送数据时CPU将待发送的并行数据输入发送FIFO,在发送FIFO中有16字节的缓存以减少发送数据时CPU中断次数。发送模块将并行数据转化为串行数据并在数据位前加上起始位后面加上奇偶校验位和停止位,通过串行发送方式发送给外设。接收模块会时刻监视串行输入端口,一旦检测到电平转换(即起始位)接收模块会马上进行状态判断并接收数据,通过奇偶校验和启停位检测有效的排除掉错误数据,然后将启停位和校验位去除,剩余的数据位发送到发送FIFO,并通知CPU在CPU接口模块接收的数据,最后数据就被传输至中央处理区。

3.4波特率发生模块

波特率发生器主要功能就是从输入时钟转换出需要的波特率clk。波特率发生器实际就是一个分频器,通过设计一个计数器,使工作频率很高的系统时钟分频为所需的波特率时钟。之所以需要设定这样一个时钟是因为收发设备间的时钟会积累导致接收数据不正确。而波特率发生器就是专门产生一个远远高于波特率的本地时钟信号对输入RXD不断采样以保证接收器和发送器保持同步。

16550初始化流程

16550初始化流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!1. 设置波特率:16550 支持多种波特率,通过设置除数锁存器(Divisor Latch)来选择。

uart 16550手册

uart 16550手册

UART 16550是一种通用异步收发传输器(UART),常用于计算

机系统中与外部设备进行串行通信。

它通常被集成在计算机的主板

或外部扩展卡中,用于连接调制解调器、打印机、鼠标、键盘等外

部设备。

UART 16550手册包含了该设备的技术规格、功能描述、寄存器

配置、时序图、工作模式、电气特性等详细信息。

在手册中,你可

以找到关于UART 16550芯片的物理特性、数据传输速率、中断控制、流控制、接口电路等方面的详细说明。

手册通常会包括以下内容:

1. 技术规格,这部分会详细描述UART 16550的功能特性,如

数据格式、传输速率、数据缓冲区大小、中断控制等。

2. 寄存器配置,手册会列出UART 16550的各个寄存器及其功能、地址和访问方式,包括接收缓冲寄存器、发送保持寄存器、中

断使能寄存器等。

3. 时序图,通过时序图,你可以清晰地了解数据的传输时序和时钟信号的关系,有助于理解UART 16550的工作原理。

4. 工作模式,手册会介绍UART 16550的工作模式,包括异步模式和同步模式,以及如何配置和切换这些模式。

5. 电气特性,这部分描述了UART 16550的电气特性,如电压范围、功耗、输入输出阻抗等。

通过阅读UART 16550手册,你可以全面了解该设备的技术细节和工作原理,有助于在设计电路或编写驱动程序时更好地理解和应用UART 16550。

希望这些信息能够帮助你更好地理解UART 16550的相关知识。

EPSON ET-16500SP 产品说明书

French controlpanel stickersink bottles that are designed forproduct setup and 4 additional full-size bottles for refilling. TheseNote: This product requires careful handling of ink. Wear disposablegloves and place a sheet of paper or plastic under the ink tank whenyou fill or refill the ink tanks, as ink may splatter. If ink spills, wipe it offimmediately with a damp towel to avoid permanent stains. If ink gets onyour clothes or belongings, it may not come off.Warning: Keep the ink bottles out of the reach of children and do notdrink the ink.1 O2 U3 S nap the bottle tip off, then remove the bottle cap.Carefully remove the protective seal (avoid touching the inkunderneath the seal), then close the bottle cap tightly.C4 FNote: Refer to the color-coded sticker above the ink tank unit toidentify the color of each tank.Caution: Be sure to fill each tank with the correct color.5 C arefully seal the bottle using the reverse side of the bottletip for proper disposal.12 P ress one of the Start buttons to start charging the ink.Ink charging takes approximately 20 minutes. Ink chargingis complete when thepower light stops flashing.20 minutesNote: After some ink is used for charging, the rest is available forprinting.Caution: Do not turn off the product, raise the scanner unit, orload paper while the product is charging or you’ll waste ink.1 M ake sure the product is not charging, and then pull out apaper cassette.2 L ift and remove the paper cassette cover from the papercassette. Set the paper cassette cover aside.3 S lide the side edge guides all the way out and set thefront edge guide to the paper size you are using.4 Insert paper with the glossy or printable side down.Note: Make sure the paper is loaded against the front edge guide and not sticking out from the end of the cassette..Note: If your computer does not have a CD/DVD drive or you areusing a Mac, an Internet connection is required to obtain the product software.To print from a Chromebook™, go to /support/gcp (U.S.) or www.epson.ca/support/gcp (Canada) for instructions.1 M ake sure the product is NOT CONNECTED to yourcomputer.W indows ®: If you see a Found New Hardware screen, clickCancel and disconnect the USB cable.2 I nsert the product CD or download and run your product’ssoftware package:/support/et16500downloads (U.S.)www.epson.ca/support/et16500downloads (Canada)3 F ollow the instructions on the screen to run the setupprogram.Mac: Make sure you install Software Updater to receive firmware and software updates for your product.4 W hen you see the Select Your Connection screen, selectone of the following:• Wireless connectionIn most cases, the software installer automatically attempts to set up your wireless connection. If setup is unsuccessful, you may need to enter your network name (SSID) and password.• Direct USB connectionM ake sure you have a USB cable (not included).• Wired network connectionM ake sure you have an Ethernet cable (not included).Mobile printingConnect wirelessly from your smartphone, tablet, or computer.Print documents and photos from across the room or around the world:• Use Epson Print Enabler (free from Google Play™) with Android™ devices (v4.4 or later). Then connect your printer and device to the same network and tap the menu icon to print.• Print remotely with Epson Connect™ and Google CloudPrint™. See your online User’s Guide for instructions or learn more at .5 S lide the side edge guides against the paper, but nottoo tightly.6 P ut the paper cassette cover back onto the papercassette.7 Keep the cassette flat as you insert it all the way.8 S elect the paper settings on the product’s control panel.9 Pull out the output tray.1 C onnect a phone cord to a telephone wall jack and tothe LINE port on your product. See the online User’sGuidefor more information.2 P ress Start on the product’s control panel to set up thefax, or press Closeto set it up later.Technical supportVisit /support (U.S.) or www.epson.ca/support (Canada) and search for your product to download drivers, view manuals, get FAQs, or contact Epson.Call (562) 276-4382 (U.S.) or (905) 709-3839 (Canada), 6 am to 8 pm , Pacific Time, Monday through Friday, and 7 am to 4 pm , Pacific Time, Saturday. Days and hours of support are subjectresults with Genuine Epson Ink and specialty papers, engineeredspecifically for Epson ® printers. Find Genuine Epson Ink and specialty papers at (U.S. sales) or www.epson.ca (Canadian sales) and at Epson authorized resellers. Call 800-GO-EPSON (800-463-7766).ET -16500 refill inksEPSON is a registered trademark, Epson Connect is a trademark, and EPSON Exceed Your Vision is a registered logomark of Seiko Epson Corporation. Designed for Excellence is a trademark of Epson America, Inc.Mac is a trademark of Apple Inc., registered in the U.S. and other countries.Android, Google Cloud Print, Chromebook, and Google Play are trademarks of Google Inc.General Notice: Other product names used herein are for identification purposes only and may be trademarks of their respective owners. Epson disclaims any and all rights in those marks.This information is subject to change without notice.© 2016 Epson America, Inc., 10/16Printed in XXXXXXCPD-51568R2。

可编程串行通信接口芯片16550与8250

D1

△DSR

D0

△CTS

△表示变化的状态

△允许发送(CTS) △ 数据装置就绪(DSR) △ 响铃指示 △ 数据载波检测(DCD)

2023年5月4日星期四

7.中断允许寄存器IER

反映了接收器和发送器以及Modem是否允许中 断的情况,通过设置可以指定其中的某些部件 允许中断。它是一个可读可写的寄存器。

其它引脚

1. 电源及时钟VCC,GND,XTLA1,XTLA2 2. 数据线:D7~D0 3. 片选信号:CS0,CS1和/CS2(输入) 4. 选通信号:

地址输入选通: /ADS 数据输入选通:DISTR和/DISTR(接/IOR) 数据输出选通:DOSTR和/DOSTR(接/IOW) 5. 主复位:MR 6. 接收时钟: =接收波特率的16倍 7. 清除发送: /CTS 8. 数据装置(MODEM)准备好: /DSR 9. 接收线路信号检测: /RLSD(有效时表示Modem检测数据载波 10.振铃指示:/RI 有效表示Modem已经接收到一个电话振铃信号

读/写操作 OUT (写) IN (读) IN(读)或 OUT(写) IN(读)或 OUT(写) IN(读)或 OUT(写) IN (读) IN(读)或 OUT(写) IN(读)或 OUT(写) IN(读) IN(读)

2023年5月4日星期四

2.串行接口初始化

串行接口初始化的任务: (1)设置波特率 (2)确定通信的具体格式 (3)设置操作方式 (4)设定是否使用中断、是否自测试操作等

D7 D6 D5 D4

IEE 0 0

0

0

1 允许中断 0 禁止中断 1 允许中断 0 禁止中断

Modem状态中断 接收字符代码错 或接收中止状态中断

TLC16550C芯片的介绍(R232串行口通讯)

2 Tlc16c550引脚

Tlc16c550是TI公司的异步通 信芯片,他具有以下特点:管 脚与TLc16c750兼容;最高可 达1M的波特率,且波特率发 生器可编程设定;由软件设 定的FIFO以减少CPU中断;有 可编程的串行数据发送格式: 数据位长度为5、6、7、8; 具有奇偶校验或无校验方式; 停止位长度为1、1.5、2;采 用44脚PLCC封装。其引脚如 右 图 所 示 。

0010 0000

3 4

THR空 Modem状态

读IIR或写 THR

检测到数据载波,检测到振铃,读MSR modem状态变化等

5.3.3FIFO控制寄存器

FIFO的操作是通过FCR来设置,其字段定义如下文所描述。当使用FIFO 时,UART中最多可存放16字节数据;反之则只能存放一个数据,即相 当于只有一个字节大小。 位6和7:接收FIFO的跟踪级别,确定产生FIFO中断的数据数目。00:一 和 字节;01:4字节;10:8字节;11:14字节。 位4,5:保留。 , : 位3:DMA模式,当FCR0=1时,控制RXRDY和TXRDY(从0到1)。 : 位2:发送FIFO复位。写1时会清除发送FIFO,并自动清0。 : 位1:接收FIFO复位。写1时会清除接收FIFO,并自动清0。 : 位0:FIFO使能。写1时使能接收和发送FIFO,清0时会清除接收和发送 : FIFO。 当使能FIFO后,其工作方式有两种:中断方式和查询方式。 首先分析中断方式。当接收FIFO使能,且接收线路状态中断和接收 数据就绪中断使能(即FCR0=1,IER0=1,IER2=1),接收中断产生的 过程如下:当FIFO中数据的数目达到跟踪级别,UART产生中断并且IIR 中出现接收数据就绪的标志。当FIFO中数据的数目低于跟踪级别后,中 断信号返回无效状态,接收数据就绪的标志也自动清除。当一个字符从 RSR送入接收FIFO时,LSR中的数据就绪位(LSR0)将置起;当FIFO 变空,该位会自动清除。

16550芯片课程介绍

美国国家半导体公司(National Semiconductor)的PC 16550D是一个通用的异步接收器/发送器UART芯片,它与IBM早期推出的个人计算机IBM PC/XT所使用的UART芯片INS 8250 兼容,但最高波特率提高到1.5Mb/s,且具有接收器和发送器FIFO(first-in first-out 先进先出)缓冲区,每个FIFO缓冲区长度均为16个字节。

目前16550在PC机的外围芯片组中得到了广泛的应用,本节以16550为例来说明UART芯片的功能、特点和用法。

12.3.1 16550的功能描述16550作为一个通用的异步通信接口芯片,与大多数UART芯片一样,其内部结构可分为发送器、接收器和控制器三大部分,分别承担各自的功能。

其中接收器和发送器两个部分完全相互独立,使得16550可以工作在单工、半双工或全双工方式下。

1.发送器:由发送保持寄存器、发送移位寄存器和发送同步控制三部分组成。

数据发送时,接收CPU送来的并行数据,再添加上起始位、校验位和停止位以后,由SOUT引脚依次串行发送出去。

2.接收器:由接收移位寄存器、接收缓冲寄存器和接收同步控制器三部分组成。

它将由SIN 引脚输入的串行数据逐位移入,去掉起始位、停止位和校验位后转换成并行数据,且进行奇/偶然校验后,提供给CPU。

3.控制器:16550的内部控制器完成对芯片自身工作状况的控制,分为以下几个部分电路。

(1)波特率发生器控制电路:由波特率发生器、分频系数(亦称除数)寄存器组成,用于产生串行通信时所需要的波特率时钟信号。

若16550是以18.432MHZ外部时钟源作为基准时钟,则16位二进制的分频系数与所要求的波特率的关系可由下式表示:分频系数=18432000÷(波特率×16) (12.1)式(12.1)中除以16是因为接收或发送的时钟频率为相应波持率的16倍。

(2)通信线控制寄存器和通信线状态寄存器:这里的控制寄存器用来接收CPU写入的控制字,并依此控制字来控制串行通信的数据格式;状态寄存器则是反映16550在数据发送和接收时的状态,供CPU读取。

RS232串口使用说明

串口通讯--接口电路

能够完成上述“串<- ->并”转换功能的电路,通常称为“通用异步收 发器” (UART:Universal Asynchronous Receiver and Transmitter), 典型的芯片有:Intel 8250/8251,16550。

波特率

波特率 (bps) 110 300 1200 2400 4800 9600 1 号电缆传输距离(英尺) 5000 5000 3000 1000 1000 250 2 号电缆传输距离(英尺) 3000 3000 3000 500 250 250

RS-232C的接口信号 RTS CTS

• 请求发送(Request to send-RTS)——用来表示DTE请求 DCE发送数据,即当终端要发送数据时,使该信号有效 (ON状态),向MODEM请求发送。它用来控制 MODEM是否要进入发送状态。

• 允许发送(Clear to send-CTS)——用来表示DCE准备 好接收DTE发来的数据,是对请求发送信号RTS的响应 信号。当MODEM已准备好接收终端传来的数据,并向 前发送时,使该信号有效,通知终端开始沿发送数据 线TxD发送数据。

数据位与停止位

• 数据位:1位、2位

• 停止位:1位、1.5位、2位

流控制

.流控制在串行通讯中的作用 解决丢失数据的问题 .硬件流控制 硬件流控制常用的有RTS/CTS(请求发送/清除发送) 流控制和DTR/DSR(数据终端就绪/数据设置就绪)流 控制 .软件流控制

一般通过XON/XOFF来实现软件流控制。

• 在RTS、CTS、DSR、DTR和DCD等控制线上: • 信号有效(接通,ON状态,正电压)=+3V~+15V

品牌CRD 型号58, 65, 66和105 产品说明书

⏹ Compact and robust design for mechanicalengineering and industrial plant applications⏹ With PROFIBUS-DP interface(process field bus - decentral periphery )⏹ DP-slave class 2 functionality in according to Profibus-Profile for Encoders, No. 3.062⏹ Transmission speed: 12 MBaud max.⏹ Output code: natural binary⏹ Resolution: max. 8192 positions per revolu-tion (13 Bits)⏹ Measuring range: max. 4096 revolutions ⏹ Total number of positions: 225 (25 Bits)⏹ Variant “L ” with RS 25 round connector ⏹ Variant “Z” with connecting cap: T -couplerfunctionality with integrated addressing facility as well as bus-termination resistors ⏹ Diagnosis LED's for Supply voltage, SRD, Class and Error⏹ Protection grade IP 65 or IP 66⏹ Option: flange, housing and connecting cap in stainless steel (model series SRD)ConstructionFlange and housing of aluminium (model se-ries SRD: stainless steel) - shaft of stainless steel -12 mm ball-bearings with Nilos ring seal or radial packing ring seal - code disk of glass or of deformation resistant plastic - GaAlAs diodes - photo-transistor array with comparator and trigger circuits for long-term stabilization of the sensor systems gate array - SMD technology.General features and modes of connectionThe CRD encoders are designed for connecting directly to PROFIBUS-DP buses as slave stations. T he interface is realized with the SPC3 Siemens PROFIBUS controller. The encoders can be operated with transmission speeds of up to 12 MBaud. The protocol is executed in accordance with DP-slave class 2 functionality as laid down in Profibus-Profile for Encoders, No. 3.062 and is described in detail in the user manual TZY 10617.T wo different modes of electrical connection are provided as standard variants (Line driver in acc. with RS 485):Variant L with RS 25 round connector:☐ The encoder is connected to the bus with a cable (connec-tor arrangement in accordance with profile description for encoders).☐ The default address is changed via the service for changingthe station address of a DP slave, namely DDLM_Set_Sla-ve_Add. The bus-termination resistors have to be installed externally.Certificate Certificate Z00358 Z00359Variant Z with connecting cap (standard)(T -coupler functionality with integrated addressing)This variant is designed for the following connection cables and provides the following functions:☐ 1 cable for the supply voltage(+ V S = 24 VDC, - V S = 0 VDC), PG 7 cable gland☐ 1 cable for Bus In ( A, B ), PG 9 cable gland ☐ 1 cable for Bus Out (A', B'), PG 9 cable gland☐ The station address and bus-termination resistors are setwith DIP switches in the connecting cap.Parameters which can be programmed (via DDLM_Set_Prm / DDLM_Data_Exchange / DDLM_Set_Slave_Add)Bus data⏹ Specification:PROFIBUS-DP , Slave stations SPC3 Siemens PROFIBUS controller⏹ Data transmission rate: 9.6 kBaud to 12 MBaud ⏹ Manufacturer code: 1962H ⏹Station address: 1 to 126, default value: 123; withvariant Z the station address is set with DIP switches; with variant L the station address can be changed with the DDLM_Set_Slave_Add service⏹ G SD File: in acc. with DIN 19245-3,PROFIBUS-DP⏹Diagnosis LEDs *: UB S (green) - V S Supply voltageSRD (green) - SRD C (green) - ClassErr (red) - Error ⏹ Freeze mode: being supported ⏹ Sync. mode: being supported ⏹Automatic baud ratesearch: being supported ⏹Diagnosis bytes Class 2: 63 Diagnosis bytesClass 1: 16 Diagnosis bytes ⏹User-Parameter bytes: Class 2: 22 bytesClass 1: 2 bytes ⏹Configuration options:D0 (1 Word Input, consistent) - Class1 D1 (2 Word Input, consistent) - Class1F0 (1 Word Input / Output, consistent) - Class2F1 (2 Word Input / Output, consistent) - Class2* At max. shaft load and working temperature between - 20 °C and+ 60 °C. Higher values are permissible with lower loads.*True table according connector arrangement supplied with each item.Electrical data⏹ Sensor system: G aAlAs diodes, photo-transistorarray⏹ Resolution: 8192 positions revolution, max. ⏹ Measuring range: 4096 revolutions⏹ T otal number ofpositions: 225 (25 Bits)⏹ Graduation code: Gray⏹ Max. position variance: ≤ 2' 38" at 4096 positions/rev.≤ ±1'59 at 8192 positions/rev.⏹ Output code: Natural binary or Gray ⏹ Code sense: CW or CCW; (programmable)⏹ Supply voltage range: + 13,5 VDC to + 30 VDC ⏹ Power consumption: PD ≤ 3,5 W (Inrush current ≤ 300 mA)⏹ Interface: Line driver in acc. with RS 485; gal-vanic separation is achieved withan opto-coupler. Supply voltage galvanic separation is achieved with DC/DC-converter⏹ Electromagnetic compatibility (EMC): EN 61000-4-2 (ESD), EN 61000-4-4 (Burst), EN 61000-6-4 (Emis-sion)Mechanical data⏹ Operating speed:3000 rpm max. (continuous)4000 rpm max. (short period)⏹ Angular acceleration: 105 rad/s² max.⏹ Moment of inertia (rotor): 45 gcm²⏹Operating torque: ≤ 5 Ncm (8 Ncm - CRD 66)(at 1000 rpm)⏹ Starting torque: ≤ 1 Ncm (4 Ncm - CRD 66)⏹ Permissible shaft load: 250 N max. (axial and radial)⏹ Bearing life expectancy: 109 revolutions * ⏹Mass: ca. 0.5 kg with round connectorca. 0.7 kg with connecting capValue rangeDescription of parameterCode sense CW, CCW Direction of rotation when looking towards the shaft: CW (clockwise), CCW (counter clockwise)Class 2 functionality enable / disable Enable for class 2 functionality Diagnosis routine yes / no Diagnosis routine for the encoderScaling function enable / disable Enable for programming the parameters Resolution and Total number of positionsResolution:positions per revolution 1 to 8192 positions per revolution Resolution (number of positions per revolution)Total number of positions 1 to 33.554.432Total number of positions"Reference value(DDLM-Data_Exchange)"0 to (Total number of positions -1)Value displayed at the reference point Station address1 to 126Identification of the station within the bus network (can only be programmed with variant L via RS 25 connector)Number of PG unions Connecting cap for variant “Z” encoderConnecting cap for model CRD Notes:⏹ Mounting accessories and securing clips can be supplied;see data sheet MZ 10111.⏹ The model No. 105 encoders have a 105 mm ø housingand can be supplied on request with a mounting bracket and heating.⏹ Copies of Profibus-Profile for Encoders, No. 3.062 can beobtained from: PROFIBUS Nutzerorganisation e.V ., Haid und Neu Str. 7, D-76131 Karlsruhe.Electrical and/ormechanical variants * CRD 58 - 4096 R 4096 C2 Z 01C2 = Device Class 2(Profile No. 3062)Max. number of revolutions able to be acquired Output codeR = natural binary G = gray Model No.58, 65, 66 or 105Positions per revolution Model series CRD - abso-lute encoder with PROFI-BUS-DP interfaceZ D - P 3 L 4 - 01Number of LEDs P = PG union Electrical and/ormechanical variants * ⏹ The TWK user manual TZY 10617 as well as the GSDfile and example programmes for the integration of the encoder in a Profibus network with Siemens S7 control-ers are available for download on www.twk.de or can be order on CD.Electrical connection Z = via connecting cap L = with RS 25 round con-nectorOrder code format for connecting capOrder code format for encoderEnvironmental data⏹ Operating temperaturerange: - 20 °C to + 60 °C ☐ optional- 40 °C to + 85 °C⏹ Storage temperature range: - 20 °C to + 70 °C ☐ optional- 40 °C to + 95 °C⏹ Permissible rel. humidity: 85 % without condensation ⏹ Resistance to shock:200 m/s²; 11 ms (DIN IEC 68)⏹Resistance to vibration: 5 Hz to 1000 Hz; 100 m/s²(DIN IEC 68)⏹Protection grade (DIN 40 050) CRD 58 and 65: IP 65 (Nilos ring) CRD 66: IP 66 (radial packing ring)CRD 105: IP65⏹Connecting cap: IP 00 (when not mounted)Electrical connections (alternatives)⏹ Connecting cap:T -coupler with 3 PG cable(variant Z)glands; integrated address-ing facility and bus-termina-tion resistors ⏹ Round connector RS 25:12 pin(variant L)*The basic versions in accordance with the data sheet bear the code number 01. Variations from the basic version are indicated with a consecutive number and are documented in our works.*The basic versions in accordance with the data sheet bear the code number 01. Variations from the basic version are indicated with a consecutive number and are documented in our works.Order code for the stainless steel version:e.g. SRD 66 - 8192 R 4096 C2 Z01ZD - P3L0 - 11Dimensions in mm+1.5Model No. 58 with synchro-flangeModel No. 65 with synchro-flangeModel No. 66 with clamping flange and shaft with flatVariant …L“ with RS connector (12 pin)The mating plugs STR 12 G P07 do not form part of the scope of deliveryVariant …Z“ with connecting cap ZDModel No. 58 with synchro-flangeModel No. 65 with synchro-flange Model No. 66 with clamping flange and shaft with flatConnecting cap ZD-P3L4-01The cap is listed as a separate item for ordering and deliv-ery. The cap can be separated from the encoder for setting purposes by removing two screws.Design form 105 with heating (option)+0.2Mating connector GGCK105HZG,4 pin, female(u。

巴马格纺丝控制系统软件说明书

概要回运建议如果有必要运回部件,比如说要维修,我们要求返运下面地址:北京巴马格机械有限公司电气部北京市朝阳区甜水园东街18号邮编:100026并保证部件的完整性且保管好附带元件(包括装箱单)信息为了防止在运输意外损坏,请仔细安全地包装部件。

如果可能的话,请用Barmag原包装包装备件。

.小心•机械震动和摆动•湿度•静电放电(ESD)包括损坏电子装配和设备的危险通常在维修时不能发现这些损坏,因为在某段时间内这些元件还能继续工作.然而,在归还后,在短时间后这些零件就失效.电子装配及设备必须用ESD(防静电)保护袋包裹或用波状板包装.(也参考电子零件和配件处理守则).然后这些零件放到有衬垫的盒子运输。

避免聚苯乙烯,泡沫塑料和塑料薄膜对电子元件有任何接触。

为了保证这些工作顺利进行,我们建议你在运回前联系BBM(北京巴马格机械有限公司)。

北京巴马格机械有限公司电气部传真: (010) 65019014电话: (010) 65019014用户建议如果用户对本系统有任何建议,请另附文档说明。

技术改造如果提供了技术文件后有技术改造的,BBM将提供更新文件来解决这几个问题,并转交给现场工程师,以便于设备尽可能正常操作。

1. 操作/设定摘要1.1 概要1.1.1 用途巴马格纺丝控制系统的PC输入设备是用来统计、操作和工艺参数修改的个人点脑,并能监控控制系统的运行过程。

每一个PC输入设备针对每一条生产线,由于每条生产线的系统配置可能不同,请严格按照编号匹配,否则将不能正常使用,请参考发货信息及PC机上的编号。

1.1.2 PC–组成巴马格纺丝控制系统软件的交货范围是PC机和Windows2000系统恢复盘。

在个人电脑的后面有交货的提示,它包括连续序列号和界面名。

供应部分巴马格纺丝控制系统软件所使用的个人电脑是作为完整的装配交付的,并由BBM安装软件。

信息!如果想要一台功能更强大的PC,可以与BBM商议并决定可行方案后是能够实现的。

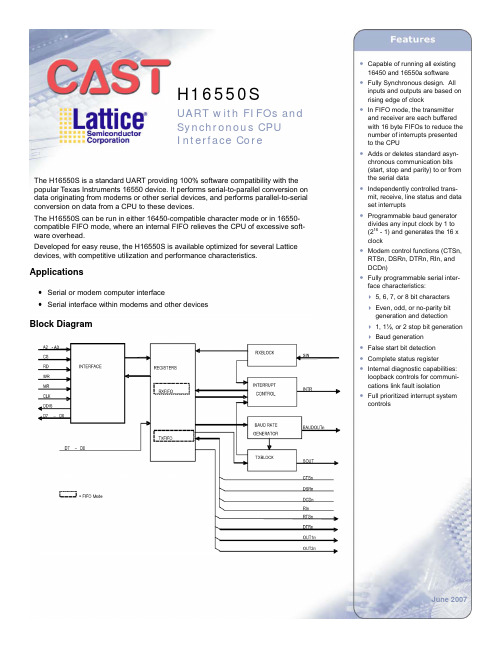

H16550S中文资料

Capable of running all existing16450 and 16550a softwareFully Synchronous design. Allinputs and outputs are based on rising edge of clockIn FIFO mode, the transmitterand receiver are each buffered with 16 byte FIFOs to reduce the number of interrupts presented to the CPUAdds or deletes standard asyn-chronous communication bits (start, stop and parity) to or from the serial dataIndependently controlled trans-mit, receive, line status and data set interruptsProgrammable baud generatordivides any input clock by 1 to (216- 1) and generates the 16 x clockModem control functions (CTSn,RTSn, DSRn, DTRn, RIn, and DCDn)Fully programmable serial inter-face characteristics: 5, 6, 7, or 8 bit characters Even, odd, or no-parity bit generation and detection 1, 1½, or 2 stop bit generation Baud generationFalse start bit detection Complete status register Internal diagnostic capabilities:loopback controls for communi-cations link fault isolationFull prioritized interrupt systemcontrolsH16550SUART with FIFOs and Synchronous CPU Interface CoreThe H16550S is a standard UART providing 100% software compatibility with the popular Texas Instruments 16550 device. It performs serial-to-parallel conversion on data originating from modems or other serial devices, and performs parallel-to-serial conversion on data from a CPU to these devices.The H16550S can be run in either 16450-compatible character mode or in 16550-compatible FIFO mode, where an internal FIFO relieves the CPU of excessive soft-ware overhead.Developed for easy reuse, the H16550S is available optimized for several Lattice devices, with competitive utilization and performance characteristics.Applications• Serial or modem computer interface• Serial interface within modems and other devicesBlock DiagramJune 2007CAST, Inc. 11 Stonewall CourtWoodcliff Lake, NJ 07677 USAtel 201-391-8300 fax 201-391-8694Copyright © CAST, Inc. 2007, All Rights Reserved. Contents subject to change without notice.Functional DescriptionAs shown above and explained below, the H16550S includes six major blocks: Interface, Registers, RXBlock, Interrupt Con-trol, Baud Rate Generator, and TXBlock. All inputs and outputs for the H16550S are fully synchronous to the rising edge of the CLK input.InterfaceThe Interface block is responsible for handling the communica-tions with the processor (or parallel) side of the system. All writing and reading of internal registers is accomplished through this block.RegistersThe Registers block holds all of the device’s internal registers. See the Register Description table for details on existing regis-ters and their addresses. Some information comes from the other blocks, but this is all gathered together in the Registers block and made available to all blocks.RXBlockThis is the receiver block. It handles the receiving of the incom-ing serial word. It is programmable to recognize data widths such as 5, 6, 7 or 8 bits, various parity settings such as even, odd or no parity and different stop bits of 1, 1½ and 2 bits. It checks for errors in the input data stream such as overrun er-rors, frame errors, parity errors and break errors. If the incoming word has no problems it is placed either in the Re-ceiver Holding register or in the Receiver FIFO depending on the mode programmed.Interrupt ControlThe Interrupt Control block sends an interrupt signal back to the processor depending on the state of the FIFO and its re-ceived and transmitted data. There are various levels of interrupt which can be read from the Interrupt Identification reg-ister, which gives the level of interrupt. Interrupts are sent in the condition of empty transmission or receiving buffers (or FIFOs), an error in the receiving of a character, or other conditions re-quiring the attention of the processor.Baud Rate GeneratorThis block takes the input clock, CLK, and divides it by a pro-grammed value (from 1 to 216 – 1). This divided clock is then divided by 16 to create the transmission clock called the Bau-dout clock.TXBlockThe Transmit block handles the transmission of data written to the Transmission Holding register (or transmit FIFO). It adds required start, parity and stop bits to the data being transmitted so that the receiving device can do the proper error handling and receiving. Implementation ResultsThe following are typical performance and utilization results us-ing several Lattice devices.Lattice DeviceLUT-4sRegis-tersPFUsSysMEMEBRsExternalI/OsSpeed(f max, MHz)LFX1200B-4 765462224 2 39 55 LFX125EB-3 619315217 2 39 57 LFEC6E-3 4812332332 39 61Regis-ters RAM512sOR4E02-3 776251116 2 39 51Slices BlockRAMsLFXP3-3 4233192512 39 65 LFSC3GA25-7 568 332 251 - 39 198LFE2-50-7 688451272 2 39 156 LFXP2-17E-7 587 442 267 2 39 82 Options and ModificationsThe H16550S core can be customized to include:• Removing or changing the size of the FIFO• Removing various control interface signalsPlease contact CAST for any required modifications.SupportThe core as delivered is warranted against defects for one year from purchase. Thirty days of phone and email technical sup-port are included, starting with the first interaction. Additional maintenance and support options are available.VerificationThe core has been verified through extensive simulation and rigorous code coverage measurements. It has also been suc-cessfully implemented in commercial and prototype systems. DeliverablesThe core includes everything required for successful implemen-tation:• Post-synthesis EDIF netlist (firm core) optimized for a spe-cific Lattice device (HDL RTL source code (soft core) isalso available)• Sample wrapper for Texas Instruments 16550 pin-compatible replacement• Testbenches (self-checking)• Simulation script, vectors, and expected results• Synthesis (soft) or place and route (firm) script• Comprehensive user documentation。

1650 操作与维护手册说明书

LIFT CORP.11921 Slauson Avenue.Santa Fe Springs, CA. 90670(800) 227-4116MM-1650OPERATION &MAINTENANCEMANUALCMAXON Lift Corp. 2000M-00-34APRIL 2000LIFT CORP .11921 Slauson Ave.Santa Fe Springs, CA. 90670CUSTOMER SERVICE:(562) 464-0099(800) 227-4116FAX: (888) 771-7713TECHNICAL SERVICE:(800) 8-MAXTEK (862-9835)WARRANTY POLICY & PROCEDURENEW LIFTGATE WARRANTYTerm of Warranty: 2 Years from Date of In-ServiceType of Warranty: Full Parts and LaborMAXON agrees to replace any components which are found to be defective during the first2 years of service, and will reimburse for labor based on MAXON’s Liftgate Warranty Flat Rate Labor Schedule. (Call MAXON Customer Service for a copy).All claims for warranty must be received within 30 Days of the repair date, and include thefollowing information:1. Liftgate Model Number2. Liftgate Serial Number3. Description of Problem4. Corrective Action Taken, and Date of Repair.5. Parts used for Repair, Including MAXON Part Number(s).6. MAXON R.G.A. # and/or Authorization # if applicable (see below).7. Person contacted at MAXON if applicable.PURCHASE PART WARRANTYTerm of Warranty: 1 Year from Date of Purchase Type of Warranty: Part Replacement and Replacement Labor.MAXON will guarantee all returned genuine replacement parts upon receipt, and inspectionof parts and invoice. All Warranty repairs must be performed by an authorized MAXON warranty station.For major repairs, MAXON’s Warranty Department must be notified, and an “AuthorizationNumber” received. Major repairs would generally be considered repairs made to the structural assembly of the liftgate and/or repairs not outlined in the MAXON Liftgate Waranty Flat Rate Schedule.Major components (i.e. hydraulic pumps, cylinders, valves, or failed structural parts) mustbe returned, freight pre-paid, prior to the claim being processed. To ensure timely processing of these warranty claims, an R.G.A. (Returned Goods Authorization) number must be obtained from MAXON’s Warranty Department prior to the return of any defective part. Defective Parts must be returned within 60 days of the claim date for consideration to:Warranty Dapartment, MAXON Lift Corp.5920 Alameda St., Huntington Park, CA. 90255MAXON’s warranty policy does not include the reimbursement for travel time; towing;vehicle rental; service calls; fabrication of parts which are available from MAXON; oil; defects due to misuse or abuse; loss of income due to downtime.MAXON’s Flat Rate Labor Schedule times takes into consideration time required fordiagnosis of problem.Warranty and Technical Information is available by calling MAXON’s Customer ServiceDepartment.NOTE: Check with Customer Service Department for updated versions of Manuals on an annual basis.Table of ContentsWARNING...................................................................................................................PAGE 4 OPERATION SECTION...........................................................PAGE 5 DECALS AND DECAL PLACEMENT........................................................................PAGE 6 LIFTGATE TERMINOLOGY.........................................................................................PAGE 8 OPERATING INSTRUCTIONS.....................................................................................PAGE 9 POSITION OF LOAD.................................................................................................PAGE 10 MAINTENANCE SECTION....................................................PAGE 11 SPECIFICATIONS....................................................................................................PAGE 12 PERIODIC MAINTENANCE CHECKLIST.................................................................PAGE 13 PARTS BREAKDOWN DRAWINGS.....................................PAGE 14 PARTS DRAWINGS (PAGE 1)..................................................................................PAGE 15 PARTS DRAWINGS (PAGE 2)..................................................................................PAGE 16 PARTS DRAWINGS (PAGE 3)..................................................................................PAGE 18 HYD. COMPONENTS, GRAVITY DOWN...................................................................PAGE 20 ELECTRICAL COMPONENTS.................................................................................PAGE 21 ELECTRICAL AND HYDRAULIC SCHEMATIC.........................................................PAGE 2211921 Slauson Ave. Santa Fe Springs, CA. 90670 (800) 227-4116 FAX (888) 771-7713PAGE 41.Read the Maintenance Manual and understand it thoroughly before any maintenance of this unit is done.2.Read the YELLOW urgent warning decal on the side of the vehicle close to the unit before operating.3.If decals are dirty, clean them. If decals are defaced or missing, replace them. Free replace-ments are available from the manufacturer. See information at the end of the Warnings 4.Be aware that the safety and location of other people or objects should be considered before operation of this unit. Stand to one side of platform while operating this unit.5.Do not stand under, or have any foreign object under the Platform when lowering. Be sure that the lowering of the Platform and/or Flipover will miss your feet!6.Keep fingers, hands, arms, legs, and feet clear of moving parts when operating this unit.7.If during your maintenance procedure, it becomes necessary to ride the platform, keep your feet and any foreign objects clear of the rear edge of the platform. Otherwise your feet or the foreign objects could become trapped between the edge of the platform and the vehicle bed.8.Inspect all Roll Pins monthly, to insure that they are not broken. Replace if broken.9.Inspect all hydraulic hoses and fittings annually. Check for cracks and deterioration, and replace if necessary.10.Disconnect battery when replacing parts or servicing.11.Do not allow children to ride, play with, or operate this unit.12.In the event of an emergency while operating the unit, release the toggle switch and the unit will stop immediately.13.A properly installed Lift should operate smoothly and the only noise during the operation of this unit should be from the Pump Unit during the raising of the Platform. Any scraping,grating or audible indications of rough operation will need investigating. The cause will need resolving before any further deterioration of performance occurs.14.Use only Maxon Authorized Parts for replacement. Replacement parts should be ordered from:MAXON LIFT CORP . Parts Department11921 Slauson Ave., Santa Fe Springs, Ca. 90670Phone: (800) 227-4116WARNING11921 S l a u s o n A v e . S a n t a F e S p r i n g s , C A . 90670 (800) 227-4116 F A X (888) 771-7713PAGE 5OPERATION SECTION11921 Slauson Ave. Santa Fe Springs, CA. 90670 (800) 227-4116 FAX (888) 771-7713PAGE 6DECALS AND DECAL PLACEMENTThe Maxon liftgate must have all warning and caution decals attached in readable condition. If decals are defaced or missing, replace them. Freereplacements are available from Maxon. Contact:DecalDecal “C”“D”DecalDecal Maxon Lift Corp., Parts Department11921 Slauson Ave., Santa Fe Springs, Ca.90670Phone: (800) 227-4116FAX: (888) 771-7713Decal Decal “C”Decal11921S la u s o n Av e .S a n t a F e Sp r i n g s , C A . 9067(800) 227-4116 F A X (888) 771-7713PAGE 7DECALS AND DECAL PLACEMENTWARNINGSTAND CLEAR WHENRELEASING PLATFORM STORAGE LATCHESP/N 263188WARNINGKEEP CLEAR OF THIS AREAP/N 263187Decal “A” P/N 264081Decal “B” P/N 280005Decal “C” P/N 263187Decal “E” P/N 263184Decal “D” P/N 280006Decal “F” P/N 26318811921 Slauson Ave. Santa Fe Springs, CA. 90670 (800) 227-4116 FAX (888) 771-7713PAGE 8LIFTGATE TERMINOLOGY1. Toggle Switch2. Main Frame3. Arm, Lower4. Link Support Assembly5. Lock Handle6. Platform7. Pin Mount Assembly8. Hydraulic Cylinder Assembly 9. Main Frame Cover68911921 S l a u s o n A v e . S a n t a F e S p r i n g s , CA . 90670 (800) 227-4116 F A X (888) 771-7713PAGE 9OPERATING INSTRUCTIONSFully read and understand this manual and all decals prior to the operation of the liftgate.1. Release lock by rotatinghandle to horizontal position.Manually unfold the platform to the horizontal position.2. To lower platform: Press down on the toggle switch. The plat-form may be stopped at any height by releasing the toggle switch.3. To raise platform: Lift up on the toggle switch until platform is level with the bed, then release the switch. Continuing to run the motor after reaching bed height can cause motor failure.4. To store the liftgate: Raise the platform until it is level with truck bed. Lift the platform to the vertical, closed position.Engage the right Lock Handle with the right Lock Plate.LOCK PLATES11921 Slauson Ave. Santa Fe Springs, CA. 90670 (800) 227-4116 FAX (888) 771-7713PAGE 10POSITION OF LOADAll loads must be placed as close to the edge of the Platform nearest to the vehicle floor as possible, with the heaviest part of the load toward the vehicle. No part of any load should be allowed to extend over the edges of the Platform. Do not place unstable loads on the Plat-form. Do not allow any load to exceed the rated capacity for the unit. If standing on the Platform, do not allow your feet to protrude beyond the edges.LOAD11921 S l a u s o n A v e . S a n t a F e S p r i n g s , C A . 90670 (800) 227-4116 F A X (888) 771-7713MAINTENANCE SECTIONGENERAL SPECIFICATIONS AND CAPACITIES Overall Bed Height.......................................................................................50”Overall Width:Model -01............................................................................85.75”Model -02............................................................................91.25”Rated Load Capacity..........................................................................1650 lbs.Hydraulic Cylinder Size......................................2-1/2” Dia Bore x 18.25” Stroke Pump/Motor Reservoir Capacity...............................................................228 in.3 Pump Operating Pressure...........................................................1250 psi max.Electrical System.................................12 volt, 180 amp max draw @ 1250 psiSPECIFICATIONS11921 Slauson Ave. Santa Fe Springs, CA. 90670 (800) 227-4116 FAX (888) 771-771311921 S l a u s o n A v e . S a n t a F e S p r i n g s , C A . 90670 (800) 227-4116 F A X (888) 771-7713* COLD WEATHER OPERATION OIL SPECIFICATIONS:Grade ISO-(32)Gravity, API - 29.5 Degrees Pour Point, F- (-54 Degrees)VISCOSITY:@ 40 Degrees C - 31.2 cSt @100 Degrees C - 6.2 cSt VISCOSITY INDEX - 154 VI Flash Point, F - 325 DegreesVisually check the complete unit for excessive wear, worn parts or broken welds. Check all Hinge Pins for excessive wear or broken welds. For parts replacement, see the Assembly Breakdown Drawings.PERIODIC MAINTENANCE CHECKLISTCheck the oil in the Pump Reservoir. The oil should be Grade ISO-(32) Hydraulic Fluid.*See below for Cold Weather operation.Check Hoses and Fittings for scuffing and leaks. Replace if necessary.Check the electrical wiring for worn insulation, and the terminals for corrosion and secure fit.Check all bolts for tightness.Check that all Warning Decals are in place and readable.Check that all roll pins are properly installed. Replace if necessary.AnnuallyQuarterlySix MonthsVisually check the Platform Hinge Pins for excessive wear or broken welds. For parts replacement, see the Assembly Breakdown Drawings.11921 Slauson Ave. Santa Fe Springs, CA. 90670 (800) 227-4116 FAX (888) 771-7713PARTS BREAKDOWN DRAWINGS11921 S l a u s o n A v e . S a n t a F e S p r i n g s , C A . 90670 (800) 227-4116 F A X (888) 771-7713PARTS DRAWINGS (PAGE 1)SEE PARTS DRAWINGS SEE PARTS DRAWINGS (PAGE 3)3456ITEM QTY .PART NO.DESCRIPTION110900004-2CAP SCREW, 1/4-20 x 3/4" LG .22264348FLAT BAR BRACE 32264347WEAR STRIP 48901011-1NUT, 1/4-20 UNC 513904005-1RIVET , 3/16"61050175MAXON PLATE 76905138-11E-RING , 7/8"82263574PIN, LOWER ARM11921 Slauson Ave. Santa Fe Springs, CA. 90670 (800) 227-4116 FAX (888) 771-7713PARTS DRAWINGS (PAGE 2)119017111516131407121222654S E E H Y D . C O M P O N E N T S ,G R A V I T Y D O W N17, 272811921 S l a u s o n A v e . S a n t a F e S p r i n g s , C A . 90670 (800) 227-4116 F A X (888) 771-7713ITEM QTY .PART NO.DESCRIPTION91263700-01MAINFRAME ASSEMBLY 91" WIDE 263700-02MAINFRAME ASSEMBLY 80" WIDE 108905138-13E-RING , 1"112263580PIN, UPPER CYLINDER121264343-01COVER CENTRAL HOUSING , 91" WIDE 264343-02COVER CENTRAL HOUSING , 80" WIDE 132264442CYLINDER ASSEMBLY142263559UPPER PARALLEL ARM ASSEMBLY 152263578PIN, UPPER PARALLEL ARM 163203216RUBBER GROMMET, 1-3/4"175901011-5NUT, 3/8-16182900014-6CAP SCREW, 3/8-16 x 1.5 LG . ZINC 194905146-01FIBERGLIDE THRUST BEARING 202264351PIN, CYLINDER BOTTOM214900014-4CAP SCREW, 3/8-16 x 1" LG . ZINC 221263695-01HOLDER, TRUCK REAR LIGHTS 263695-02HOLDER, TRUCK REAR LIGHTS 231226598PLATE, RECESSED SWITCH241264443ELECTRICAL CABLE & SWITCH ASSEMBLY 251250876BOOT, RUBBER SEAL SWITCH 261050178PLATE, MAXON SERIAL 273902011-4LOCK WASHER 3/8"282901018U-NUTPARTS DRAWINGS (PAGE 2)11921 Slauson Ave. Santa Fe Springs, CA. 90670 (800) 227-4116 FAX (888) 771-7713PARTS DRAWINGS (PAGE 3)20332333333872394111921 S l a u s o n A v e . S a n t a F e S p r i n g s , C A . 90670 (800) 227-4116 F A X (888) 771-7713PARTS DRAWINGS (PAGE 3)ITEM QTY .PART NO.DESCRIPTION291263565-01PLATFORM WELDMENT 304901001NUT, NYLON 5/16-18 ZINC 314902011-3LOCK WASHER 5/16" ZINC 324253516RUBBER BUMPER 2"334900001-3BUTTON SCREW, 5/16-18 x 1" ALLOY 342263560LINK ASSEMBLY351264339-01TORSION BAR WELDMENT 362905138-08E-RING , 5/8"372263579PIN, UPPER LINK 381263571-01PIN MOUNT ASSEMBLY 391902001-1WASHER 3/8"402901002NUT, NYLON 3/8-16 ZINC 411264340PIN WELDMENT11921 Slauson Ave. Santa Fe Springs, CA. 90670 (800) 227-4116 FAX (888) 771-7713HYD. COMPONENTS, GRAVITY DOWN2S E E P U M P C O M P O N E N T S95RETURN LINELH CYLINDERLH LIFTING HOSERETURN LINERH CYLINDERRH LIFTING HOSE11921 S l a u s o n A v e . S a n t a F e S p r i n g s , C A . 90670 (800) 227-4116 F A X (888) 771-7713PAGE 21ITEM QTY .PART NO.DESCRIPTION11224370-11HOSE, 87" LG .21224370-13HOSE , 75" LG 32264349ELBOW, 90º, 1/4" NPT 42264440HOSE, LIFTING 52264442CYLINDER ASSEMBLY61905193TEE BRANCH NUT, SWIVEL,SAE 37º, 3/8" MF 71905188TEE BRANCH, 1/8" NPT, 1/4" HOSE 83900014-04CAP SCREW, 3/8-16 x 1" LG . ZINC 92902011-4LOCK WASHER, 3/8"HYD. COMPONENTS, GRAVITY DOWNELECTRICAL COMPONENTS1ITEM QTY .PART NO.DESCRIPTION11264443ELECTRICAL CABLE & SWITCH ASSEMBLY 21263551-02CABLE ASSEMBLY 4 GA, 29 FT11921 Slauson Ave. Santa Fe Springs, CA. 90670 (800) 227-4116 FAX (888) 771-7713PAGE 22PUMP COMPONENTS84537101111921 S l a u s o n A v e . S a n t a F e S p r i n g s , C A . 90670 (800) 227-4116 F A X (888) 771-7713PAGE 23PUMP COMPONENTSITEM QTY .PART NO.DESCRIPTION11280178ADJUSTABLE RELIEF VALVE 21280177BUSHING 31280452PLUG 41280171STRAP51280172STARTER SOLENOID 61280170MOTOR 71280165PUMP 81280175PLUG 91280176RESERVOIR 101280173FILTER ASSEMBLY 111280168FILTER121280167VALVE ASSEMBLY11921 Slauson Ave. Santa Fe Springs, CA. 90670 (800) 227-4116 FAX (888) 771-7713PAGE 24ELECTRICAL AND HYDRAULIC SCHEMATICG r o u n d t o T r u c k F r a m eT r u c k B a t t e r y12 V#4 C a b l eF l u s h 30A M P1323 P o s i t i o n T o g g l e S w i t c hW i t e B l a c kG r e e n S o l e n o i dG r o u n d t o P u m p /M o t o r A s s e m b l y G r o u n dF i l t e rP U M PV a l v e sV a l v e sC y l i n d e rP r e s s u r e F l o w C o n t r o l V a l v e R .V . 1500 P S IG r o u n d t o P u m p /M o t o r A s s e m b l yF i l t e rC y l i n d e rP r e s s u r e F l o w C o n t r o l V a l v eLIQUID SEALANT APPLICATIONClean all threads with a soft brush and a suitable cleaning solvent.Dry threads thoroughly with compressed air or shop towel.Apply the Liquid Sealant (Compound PLS 2), to the external threads of the Male Connector.Assemble the fitting and torque it to the prescribed value.Check for leakage. If leakage exists, remove the fitting and return to Step # 1.If fitting is loosened or removed, return to Step # 1.1.2.3.4.5. 6.P/N 260798-02。

16550寄存器的使用

80H

19200

00H

06H

600

00H

C0H

38400

00H

03H

2400

00H

30H

57600

00H

02H

4800

00H

18H

115200

00H

01H

中断允许寄存器IER格式

D7

D6

D5

D4

D3

D2

D1

D0

0

0

0

0

I0E

I3E

I1E

I2E

类型0中断

MODEM状态改变

1—允许

0—屏蔽

类型3中断

接收出错

1—允许

0—屏蔽

类型1中断

发送保持器空

1—允许

0—屏蔽

类型2中断

接收缓冲区满

1—允许

0—屏蔽

中断标识寄存器IIR(表示有无待处理的中断发生及其类型)

MODEM控制寄存器(MCR)控制芯片的4个管脚的输出和芯片的环路检测。

MCR格式

D7

D6

D5

D4

D3

D2

D1

D0

0

0

0

环路检测

输出2

输出1

请求发送

D0

TSRE

THRE

BI

FE

PE

OE

DR

FIFO中接收数据错误

发送移位寄存器空

发送保持寄存器空

中止识别指示

接收帧错误

接收奇错

接收溢出错

接受缓冲器满

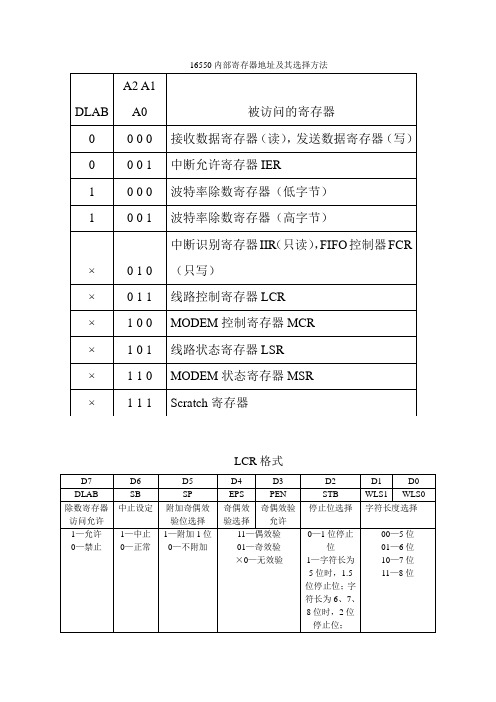

DLAB

A2 A1 A0

被访问的寄存器

0

0 0 0

接收数据寄存器(读),发送数据寄存器(写)

uart16550 xilinx UART串口

© Copyright 2010–2012 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein aretrademarks of Xilinx in the United States and other countries. AMBA and ARM are trademarks of ARM in the EU and other countries. All other trademarks are the property of their respective owners.IntroductionThe AXI Universal Asynchronous Receiver Transmitter (UART) 16550 connects to the AMBA ® (Advance Microcontroller Bus Architecture) AXI (Advanced eXtensible Interface) and provides the controller interface for asynchronous serial data transfer. This soft IP core is designed to connect through an AXI4-Lite interface.The AXI UART 16550 described in this document incorporates features described in the National Semiconductor PC16550D UART with FIFOs Data Sheet .The National Semiconductor PC16550D data sheet is referenced throughout this document and should be used as the authoritative specification. Differences between the National Semiconductor PC16550D and the AXI UART 16550 data sheet are highlighted in the Specification Exceptions section.Features•AXI interface is based on AXI4-Lite specification •Hardware and software register compatible with all standard 16450 and 16550 UARTs•Supports default core configuration for 9600 baud, 8 bits data length, 1 stop bit and no parity •Implements all standard serial interface protocols •5, 6, 7 or 8 bits per character•Odd, Even or no parity detection and generation•1, 1.5 or 2 stop bit detection and generation •Internal baud rate generator and separate receiver clock input •Modem control functions•Prioritized transmit, receive, line status and modem control interrupts•False start bit detection and recover •Line break detection and generation •Internal loopback diagnostic functionality •16 character transmit and receive FIFOsLogiCORE IP AXI UART 16550(v1.01a)DS748 July 25, 2012Product SpecificationLogiCORE IP Facts TableCore SpecificsSupportedDevice Family (1) Zynq ™-7000(2), Virtex ®-7, Kintex ™-7,Artix ™-7,Virtex-6, Spartan ®-6Supported User Interfaces AXI4-LiteResourcesSee T able 18, T able 19, T able 20, T able 21,T able 22Provided with CoreDesign Files VHDLExample Design Not Provided Test Bench Not Provided Constraints File Not ProvidedSimulation ModelN/AS upportedS/W Driver (3)Standalone and LinuxTested Design Flows (4)Design Entry Xilinx Platform Studio (XPS)Vivado™ Design Suite (5)Simulation Mentor Graphics ModelSimSynthesisXilinx Synthesis T echnology (XST)Vivado Synthesis SupportProvided by Xilinx @ /support1.For a complete list of supported derivative devices, see the Embedded Edition Derivative Device Support .2.Supported in ISE Design Suite implementations only.3.Standalone driver details can be found in the EDK or SDK directory(<install_directory>/doc/usenglish/xilinx_drivers.htm). Linux OS and driver support information is available from // .4.For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide5.Supports only 7 series devices.Functional DescriptionThe AXI UART 16550 implements the hardware and software functionality of the National Semiconductor 16550 UART, which works in both the 16450 and 16550 UART modes. For complete details, see the National Semiconductor data sheet.The AXI UART 16550 performs parallel to serial conversion on characters received from the AXI master and serial to parallel conversion on characters received from a modem or serial peripheral.The AXI UART 16550 is capable of transmitting and receiving 8, 7, 6, or 5 bit characters, with 2, 1.5 or 1 stop bits and odd, even or no parity. The AXI UART 16550 can transmit and receive independently.The device can be configured and its status monitored by the internal register set. The AXI UART 16550 is capable of signaling receiver, transmitter and modem control interrupts. These interrupts can be masked, are prioritized and can be identified by reading an internal register.The device contains a 16-bit, programmable, baud rate generator, and independent 16 character length transmit and receive FIFOs. The FIFOs can be enabled or disabled through software control.The top-level block diagram for the AXI UART 16550 is shown in Figure1.Figure 1:Top-level DiagramThe top level modules of the AXI UART 16550 are:•AXI Interface Module•IPIC_IF•UART16550The detailed block diagram for the AXI UART 16550 is shown in Figure2.Figure 2:Top-level DiagramThe AXI UART 16550 modules are described in these sections:AXI Interface Module: The AXI Interface Module provides the interface to the AXI and implements AXI protocol logic. The AXI Interface Module is a bidirectional interface between a user IP core and the AXI interface standard. To simplify the process of attaching the AXI UART 16550 to the AXI, the core makes use of a portable, pre-designed AXI interface called AXI4-Lite IPIF that manages the AXI interface signals.IPIC_IF: The IPIC_IF Module provide interface between the AXI interface Module and the UART16550 register interface. This module has the logic for generation of acknowledgment signals for read and write transactions to UART. The AXI4-Lite IPIF specification is listed in Reference Documents.UART16550: The UART16550 Module consists of register interface, Receiver, Transmitter, programmable Baud Generator and Modem logic modules. The UART16550 module of AXI UART 16550 can be configured for 16450 or 16550 mode of operation. This is accomplished by the usage of generic C_IS_A_16550.The AXI UART 16550 core provides separate interrupt enable and interrupt identification registers. If interrupts are enabled, a level sensitive interrupt is generated for these conditions:•Receiver line status•Received data available•Character Timeout•Transmitter holding register empty•Modem statusReceiver line statusThe Receiver Line Status Interrupt is generated for these conditions:•Overrun error - An interrupt is generated when Receive buffer is not read by the master and the next character is transferred to the Receive buffer register. In FIFO mode; an overrun interrupt is generated only when FIFO is full and the next character is completely received in the shift register.•Parity Error - This interrupt is generated when the receive character has an invalid parity bit.•Framing Error - This interrupt is generated if the received character has an invalid stop bit.•Line Break - This interrupt is generated when the Receiver detects logic 0 for longer than a full word transmission time.•The Receiver Line Status Interrupt is cleared by reading the LSR register.Received data availableThe Received data available interrupt is generated when the Receiver FIFO trigger level is reached. This interrupt is cleared when the Receiver FIFO drops below the trigger level.Character TimeoutThe Character Timeout interrupt is generated when no character has been removed from, or input to, the receiver FIFO during the last 4 character time and there is at least one character in the FIFO during this time. The character time considered for timeout (Start + 8 bit data + Parity + 2 Stop bit) is constant for all configurations. This interrupt is cleared by reading Receiver Buffer Register.Transmitter holding register emptyThe Transmitter holding register empty interrupt is generated when the character is transferred from the Transmitter holding register to the Transmitter shift register. In the FIFO mode, this interrupt is generated when Transmitter FIFO becomes empty. This interrupt is cleared by reading the IIR or writing into the Transmitter holding register.Modem StatusThis interrupt is generated for these modem status conditions:•Clear to send•Data Set Ready•Ring Indicator•Data Carrier DetectThis interrupt is cleared by reading the Modem Status Register.The I/O signals are listed and described in Table1.Table 1: I/O SignalsPort Signal Name Interface I/O InitialState DescriptionSystem SignalsP1S_AXI_ACLK System I-AXI ClockP2S_AXI_ARESETN System I-AXI Reset signal, active-LowP3IP2INTC_Irpt System O0Device interrupt output to microprocessor interrupt input or system interrupt controller (active-High)P4Freeze System I-Freezes UART for software debug (active-High)AXI Write Address Channel SignalsP5S_AXI_AWADDR[C_S_AXI_ADDR_WIDTH-1:0]AXI I-AXI Write address. The write address bus gives theaddress of the write transaction.P6S_AXI_AWVALID AXI I-Write address valid. This signal indicates that valid write address is available.P7S_AXI_AWREADY AXI O0Write address ready. This signal indicates that the slave is ready to accept an address.AXI Write Channel SignalsP8S_AXI_WDA TA[C_S_AXI_DA T A_WIDTH - 1: 0]AXI I-Write dataP9S_AXI_WSTB[C_S_AXI_DA T A_WIDTH/8-1:0] (1)AXI I-Write strobes. This signal indicates which byte lanes toupdate in memory.P10S_AXI_WVALID AXI I-Write valid. This signal indicates that valid write data and strobes are available.P11S_AXI_WREADY AXI O0Write ready. This signal indicates that the slave can accept the write data.AXI Write Response Channel SignalsP12S_AXI_BRESP[1:0](2)AXI O0Write response. This signal indicates the status of the write transaction.“00“ - OKAY“10“ - SLVERRP13S_AXI_BVALID AXI O0Write response valid. This signal indicates that a valid write response is available.P14S_AXI_BREADY AXI I-Response ready. This signal indicates that the master can accept the response information.AXI Read Address Channel SignalsP15S_AXI_ARADDR[C_S_AXI_ADDR_WIDTH -1:0]AXI I-Read address. The read address bus gives the addressof a read transaction.P16S_AXI_ARVALID AXI I-Read address valid. When High, this signal indicates that the read address is valid and remains stable until the address acknowledgement signal, S_AXI_ARREADY, is High.P17S_AXI_ARREADY AXI O1Read address ready. This signal indicates that the slave is ready to accept an address.AXI Read Data Channel SignalsP18S_AXI_RDA T A[C_S_AXI_DA T A_WIDTH -1:0]AXIORead dataP19S_AXI_RRESP[1:0](2)AXI O 0Read response. This signal indicates the status of the read transfer.“00“ - OKAY “10“ - SLVERRP20S_AXI_RVALID AXI O 0Read valid. This signal indicates that the required read data is available and the read transfer can complete P21S_AXI_RREADYAXII-Read ready. This signal indicates that the master can accept the read data and response informationUART Interface SignalsP22BaudoutN Serial O 116 x clock signal from the transmitter section of the UART P23Rclk Serial I -Receiver 16x clock (Optional, can be driven externally under control of the C_HAS_EXTERNAL_RCLK parameter)P24Sin Serial I -Serial data input P25Sout Serial O 1Serial data outputP26XinSerialI-Baud rate generator reference clock (Optional, can be driven externally under control of the C_HAS_EXTERNAL_XIN parameter)P27Xout Serial O 0If C_HAS_EXTERNAL_XIN = 0, Xout is 0, ifC_HAS_EXTERNAL_XIN = 1 Xout can be used as reference feedback clock for Baud rate generator P28CtsN Modem I -Clear to send (active-Low).When Low, this indicates that the MODEM or data set is ready to exchange data.P29DcdN Modem I -Data carrier detect (active-Low).When Low, indicates that the data carrier has been detected by the MODEM or data set.P30DsrN Modem I -Data set ready (active-Low).When Low, this indicates that the MODEM or data set is ready to establish the communication link with the UART.P31DtrN Modem O 1Data terminal ready (active-Low).When Low, this informs the MODEM or data set that the UART is ready to establish a communication link.P32RiN Modem I -Ring indicator (active-Low).When Low, this indicates that a telephone ringing signal has been received by the MODEM or data set.P33RtsN Modem O 1Request to send (active-Low).When Low, this informs the MODEM or data set that the UART is ready to exchange data.P34Ddis User O 1Driver disable. This goes Low when CPU is reading data from UART.P35Out1N User O 1User controlled output P36Our2NUserO1User controlled outputPort Signal NameInterfaceI/OInitialState DescriptionDesign ParametersTo allow the user to create an AXI UART 16550 that is uniquely tailored for the user’s system, certain features are parameterizable in the AXI UART 16550 design. This allows the user to have a design that utilizes only the resources required by the system and runs at the highest possible performance. The parameterizable features in the AXI UART 16550 core are as shown in Table 2.In addition to the parameters listed in this table, there are also parameters that are inferred for each AXI interface in the EDK tools. Through the design, these EDK-inferred parameters control the behavior of the AXI Interconnect.For a complete list of the interconnect settings related to the AXI interface, see DS768, AXI Interconnect IP Data Sheet . P37RxrdyN User O 1DMA control signal P38TxrdyNUserODMA control signalNotes:1.This signal is not used. The AXI UART 16550 assumes that all byte lanes are active.2.For these signals, the IP core does not generate the Decode Error (“11”) response. Other responses such as “00” (OKAY) and “10” (SLVERR) are generated by the core based on certain conditions.Table 2:Design Parameters Generic Parameter DescriptionParameter NameAllowable Values Default Value VHDLTypeSystem ParametersG1Target FPGA familyC_FAMIL Yvirtex7, kintex7, artix7, zynq, virtex6,spartan6virtex6stringG2System clock frequency (inHz) driving the 16550 UART peripheralC_S_AXI_ACLK_FREQ_HZ integer(ex.100000000)100_000_000integerAXI ParametersG3AXI address bus width C_S_AXI_ADDR_WIDTH 1313integer G4AXI data bus widthC_S_AXI_DA TA_WIDTH3232integer16550 UART InterfaceG5External xin clock C_HAS_EXTERNAL_XIN 0: xin is open (1)(2)1: xin is externally driven0integerG6External Receiver clock C_HAS_EXTERNAL_RCLK 0 : rclk is open1 : rclk is externally driven0integerG7Select 16450/16550 UART C_IS_A_165500 : 16450 mode 1 : 16550 mode1integerPort Signal NameInterfaceI/OInitialState DescriptionParameter - Port DependenciesThe dependencies between the AXI UART 16550 core design parameters and I/O signals are described in Table 3.In addition, when certain features are parameterized out of the design, the related logic is no longer a part of the design. The unused input signals and related output signals are set to a specified value.G8External xin clock frequency in Hz.C_EXTERNAL_XIN_CLK_HZ (3)Valid xin clock frequency in Hz.25000000integerNotes:1.When C_HAS_EXTERNAL_XIN=0, this core uses S_AXI_ACLK as a reference clock for the baud calculation. User must use S_AXI_ACLK frequency to calculate baud divisor value for DLL and DLM register configuration.2.The external xin input clock must be less than half of S_AXI_ACLK.3.External xin clock frequency. User must configure this parameter when external xin is used. (C_HAS_EXTERNAL_XIN is ‘1’).Table 3:Parameter-Port Dependencies Generic or PortName Affects Depends Relationship DescriptionDesign ParametersG3C_S_AXI_ADDR_WIDTH P5, P15-Defines the width of the ports G4C_S_AXI_DA T A_WIDTHP8, P9, P18-Defines the width of the portsI/O SignalsP5S_AXI_AWADDR[C_S_AXI_ADDR_WIDTH-1:0]-G3Port width depends on the generic C_S_AXI_ADDR_WIDTHP8S_AXI_WDA T A[C_S_AXI_DA TA_WIDTH-1:0]-G4Port width depends on the generic C_S_AXI_DA TA_WIDTHP9S_AXI_WSTB[C_S_AXI_DA TA_WIDTH/8-1:0]-G4Port width depends on the generic C_S_AXI_DA TA_WIDTHP15S_AXI_ARADDR[C_S_AXI_ADDR_WIDTH -1:0]-G3Port width depends on the generic C_S_AXI_ADDR_WIDTHP18S_AXI_RDATA[C_S_AXI_DATA_WIDTH -1:0]-G4Port width depends on the generic C_S_AXI_DA TA_WIDTHP23Rclk-G6If C_HAS_EXTERNAL_RCLK = 0 baudoutN is used as 16x receiver clock,C_HAS_EXTERNAL_RCLK = 1, rclk is used as 16x receiver clock.P26Xin -G5When C_HAS_EXTERNAL_XIN = 0, xin isunconnected, C_HAS_EXTERNAL_XIN = 1, xin is driven externally.Table 2:Design Parameters (Cont’d)Generic Parameter DescriptionParameter NameAllowable Values Default Value VHDLTypeRegister DescriptionsAXI 16550 InterfaceThe internal registers of the AXI UART 16550 are offset from the base address C_BASEADDR. Additionally, some of the internal registers are accessible only when bit 7 of the Line Control Register (LCR) is set. The AXI UART 16550 internal register set is described in Table4.Table 4: RegistersRegister Name LCR(7) + Address Access Receiver Buffer Register (RBR)0 + 0x1000Read Transmitter Holding Register (THR)0 + 0x1000WriteInterrupt Enable Register (IER)0 + 0x1004Read/Write Interrupt Identification Register (IIR)0 + 0x1008ReadFIFO Control Register (FCR)(3)X + 0x1008WriteFIFO Control Register(2)(3) 1 +0x1008ReadLine Control Register (LCR)X(1) + 0x100C Read/Write Modem Control Register (MCR)X(1) + 0x1010Read/WriteLine Status Register (LSR)X(1) + 0x1014Read/Write Modem Status Register (MSR)X(1) + 0x1018Read/Write Scratch Register (SCR)X(1) + 0x101C Read/Write Divisor Latch (Least Significant Byte) Register (DLL) 1 + 0x1000Read/Write Divisor Latch (Most Significant Byte) Register (DLM) 1 + 0x1004Read/Write Notes:1.X denotes a ‘don’t care’2.FIFO Control Register is write-only in the National PC16550D3.16450 UART mode implementation does not include this registerRegister LogicThis section tabulates the internal AXI UART 16550 registers, including their reset values (if any). See the National Semiconductor PC16550D UART with FIFOs data sheet (June, 1995) for a more detailed description of the register behavior.Receiver Buffer RegisterThis 32-bit read register is shown in Figure 3. The Receiver Buffer Register contains the last received character. The bit definitions for the register are shown in Table 5. The offset and accessibility of this register value is as shown in Table 4.Transmitter Holding RegisterThis 32-bit write register is shown in Figure 4. The Transmitter H olding Register contains the character to be transmitted next. The bit definitions for the register are shown in Table 6. The offset and accessibility of this register is shown in Table 4.Figure 3:Receiver Buffer Register (RBR)Table 5:Receiver Buffer Register Bit Definitions BitNameAccessReset ValueDescription31-8Reserved N/A N/A Reserved7-0RBRRead"00000000"Last received characterFigure 4:Transmitter Holding Register (THR)Table 6:Transmitter Holding Register Bit Definitions BitNameAccessReset ValueDescription31-8Reserved N/A N/A Reserved7-0THRWrite"11111111"Holds the character to be transmitted nextInterrupt Enable RegisterThis 32-bit read/write register is shown in Figure 5. The Interrupt Enable Register contains the bits which enable interrupts. The bit definitions for the register are shown in Table 7. The offset and accessibility of this register value is shown in Table 4.Figure 5:Interrupt Enable Register (IER)Table 7:Interrupt Enable Register Bit Definitions BitNameAccessReset ValueDescription31-8Reserved N/A N/A Reserved7-4N/A Read/Write "0000"(1)Always returns "0000"3EDSSIRead/Write’0’Enable Modem Status Interrupt’0’ = Disables Modem Status Interrupts.’1’ = Enables Modem Status Interrupts.2ELSI Read/Write ’0’Enable Receiver Line Status Interrupt’0’ = Disables Receiver Line Status Interrupts.’1’ = Enables Receiver Line Status Interrupts.1ETBEIRead/Write ’0’Enable Transmitter Holding Register Empty Interrupt ’0’ = Disables Transmitter Holding Register Empty Interrupts.’1’ = Enables Transmitter Holding Register Interrupts.0ERBFI Read/Write ’0’Enable Received Data Available Interrupt’0’ = Disables Received Data Available Interrupts ’1’ = Enables Received Data Available Interrupts1.Reading these bits always returns "0000"Interrupt Identification RegisterThis 32-bit read register is shown in Figure6. The Interrupt Identification Register contains the priority interrupt identification. The bit definitions for the register are shown in Table8. The offset and accessibility of this register value is shown in Table4.Figure 6:Interrupt Identification Register (IIR)Table 8:Interrupt Identification Register Bit DefinitionsBit Name Access Reset Value Description31-8Reserved N/A N/A Reserved7-6FIFOEN(1)Read"00"FIFOs Enabled. Always zero if not in FIFO mode.5-4N/A Read"00"(2)Always returns "00"3-1INTID2Read"000"Interrupt ID"011" = Receiver Line Status (Highest)(4) "010" = Received Data Available (Second) "110" = Character Timeout (Second)"001" = T ransmitter Holding Register Empty (Third) "000" = Modem Status (Fourth)0INTPEND(3)Read’1’0 - Interrupt is pending1- No interrupt is pendingNotes:1.Bits are always zero in 16450 UART mode2.Reading these bits always return "00"3.If INTPEND = ’0’, interrupt is pending. See National Semiconductor PC16550D data sheet for more details4.Line status interrupt is generated for framing, parity, overrun error and break condition.This is 32-bit write/read register is shown in Figure7. The FIFO Control Register contains the FIFO configuration bits. The bit definitions for the register are shown in Table9. The offset and accessibility of this register value is shown in Table4. The DMA mode signalling information is given in Table10.Figure 7:FIFO Control Register (FCR)Table 9:FIFO Control Register Bit Definitions (1)Bit Name Access Reset Value Description31-8Reserved N/A N/A Reserved7-6RCVR FIFO Trigger Level Read/Write"00"RCVR FIFO T rigger Level. "00" = 1 byte"01" = 4 bytes"10" = 8 bytes"11" = 14 bytes5-4Reserved Read/Write N/A Reserved3DMA Mode Select Read/Write’0’DMA Mode Select ’0’ = Mode 0’1’ = Mode 12XMIT FIFO Reset Read/Write’0’T ransmitter FIFO Reset ’1’ = Resets XMIT FIFO.1RCVR FIFO Reset Read/Write’0’Receiver FIFO Reset’1’ = Resets RCVR FIFO.0FIFOEN Read/Write’0’FIFO Enable’1’ = Enables FIFOs.Notes:1.FCR is not included in 16450 UART modeTable 10:DMA Modes signallingDMA Mode TXRDYn RXRDYnMODE 0In the 16450 mode or in mode 0, when there are nocharacters in the THR or Transmitter FIFO, thissignal is Low. This signal goes High again after thefirst character is loaded into the THR or FIFO.In the 16450 mode or in mode 0, when there is at leastone character in the Receiver FIFO or Receiverholding register, this signal is Low. This signal goesHigh again when there are no characters in FIFO orreceiver holding register.MODE 1When there are no characters in the TransmitterFIFO, this signal goes Low. This signal goes Highagain if the FIFO is completely full.When the trigger level or the timeout has beenreached, this signal goes Low. This signal goes Highagain when there are no characters in the FIFO orreceiver holding register.This 32-bit write/read register is shown in Figure8. The Line Control Register contains the serial communication configuration bits. The bit definitions for the register are shown in Table11. The offset and accessibility of this register value is shown in Table4.Figure 8:Line Control Register (LCR)Table 11:Line Control Register Bit DefinitionsBit Name Access ResetValue Description31-8Reserved N/A N/A Reserved7DLAB Read/Write’0’Divisor Latch Access Bit.’1’ = Allows access to the Divisor Latch Registers and reading of the FIFO Control Register.’0’ = Allows access to RBR, THR, IER and IIR registers.6Set Break Read/Write’0’Set Break’1’ = Enables break condition. Sets SOUT to ’0’ and cause break condition.’0’ = Disables break condition.5Stick Parity Read/Write’0’Stick Parity’1’ = When bits 3, 4 are logic1 the Parity bit is transmitted and checked as a logic 0. If bit 4 is a logic 0 and bit 3 is logic 1 then the Parity bit is transmitted and checked as a logic 1.’0’ = Stick Parity is disabled.4EPS Read/Write’0’Even Parity Select’1’ = Selects Even parity.’0’ = Selects Odd parity.3PEN Read/Write’0’Parity Enable’1’ = Enables parity.’0’ = Disables parity.2STB Read/Write’0’Number of Stop Bits’0’ = 1 Stop bit’1’ = 2 Stop bits or 1.5, if 5 bits/character selected.The receiver checks for 1 stop bit only regardless of the number of stop bits selected.1-0WLS Read/Write"11"Word Length Select "00" = 5 bits/character "01" = 6 bits/character "10" = 7 bits/character "11" = 8 bits/characterModem Control RegisterThis 32-bit write/read register is shown in Figure 9. The Modem Control Register contains the modem signalling configuration bits. The bit definitions for the register are shown in Table 12. The offset and accessibility of this register value is shown in Table 4.Figure 9:Modem Control Register (MCR)Table 12:Modem Control Register Bit Definitions BitNameAccessReset ValueDescription31-8Reserved N/A N/A Reserved 7-5N/A Read/Write "000"(1)Always "000"4LoopRead/Write’0’Loop Back’1’ = Enables loop back.3Out2Read/Write ’0’User Output 2’1’ = Drives OUT2N Low.’0’ = Drives OUT2N High.2Out1Read/Write ’0’User Output 1’1’ = Drives OUT1N Low.’0’ = Drives OUT1N High.1RTS Read/Write’0’Request T o Send’1’ = Drives RTSN Low.’0’ = Drives RTSN High.0DTR Read/Write ’0’Data Terminal Ready ’1’ = Drives DTRN Low.’0’ = Drives DTRN High.Notes:1.Reading these bits always returns "000".Line Status RegisterThis 32-bit write/read register as shown in Figure10. The Line Status Register contains the current status of receiver and transmitter. The bit definitions for the register are shown in Table13. The offset and accessibility of this register value is shown in Table4.Table 13:Line Status Register Bit DefinitionsBit Name Access Reset Value Description31-8Reserved N/A N/A Reserved7Error inRCVR FIFORead/Write’0’Error in RCVR FIFO(1): RCVR FIFO contains at least onereceiver error (Parity, Framing, Break condition).6TEMT Read/Write’1’ T ransmitter Empty:0 - THR or Transmitter shift register contains data.1 - THR and T ransmitter shift register empty. In FIFO mode, Transmitter FIFO and shift register are both empty.5THRE Read/Write’1’Transmitter Holding Register Empty0 - THR or Transmitter FIFO has data to transmit.1 - THR is empty. In FIFO mode, Transmitter FIFO is empty.4BI Read/Write’0’Break InterruptSet when SIN is held Low for an entire character time. (Start + data bits + Parity + Stop bits). In FIFO mode, this error is associated with a particular character in FIFO. The next character transfer is enabled if the Sin goes to marking state and receives the next valid start bit.3FE Read/Write’0’Framing ErrorCharacter missing a stop bit. In framing error, the UART attempts to re-synchronize by assuming that the framing error was due to next character start bit, so it samples start bit twice and then takes in following data. In FIFO mode, this error is associated with a particular character in the FIFO.2PE Read/Write’0’Parity ErrorIndicates that the received data character does not have correct even or odd parity as selected by the Even parity select bit. In FIFO mode, this error is associated with a particular character in the FIFO.1OE Read/Write’0’Overrun ErrorRBR not read before next character is received, thereby destroying the previous character. In FIFO mode, data continues to fill the FIFO beyond the trigger level, an overrun error occurs only after the FIFO is full and the next character has been completely received in the shift register. The character in the shift register is overwritten but it is not transferred to the FIFO.。

AXIS Q1656-BLE光标像素相机数据手册说明书