8051 instruction set summary

8051微控制器硬件手册及应用注释说明书

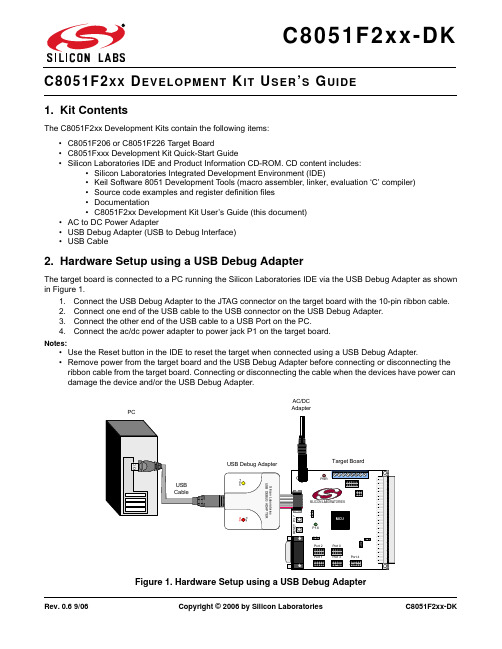

1API Program ExamplesReferences•Atmel 8051 Microcontrollers Hardware Manual1. IntroductionThis Application Note provides to customers C program examples for Api usages.24365A–80C51–07/0434365A–80C51–07/042. API for Standard C512.1 flash_eeprom_api.c/*C************************************************************************ NAME: flash_eeprom_api.c*-------------------------------------------------------------------------* Copyright (c) 2004 Atmel.*-------------------------------------------------------------------------* RELEASE:* REVISION: 1.0*-------------------------------------------------------------------------* PURPOSE:* Read/Write flash* CAUTTION : add #define ONCHIP_EEPROM for on-chip eeprom products* (defined by default in the standard delivery)**************************************************************************//*_____ I N C L U D E - F I L E S _______________________________________*/#include "reg_C51.h"/*_____ D E C L A R A T I O N ___________________________________________*/#define ONCHIP_EEPROM //define it only for on-chip eeprom products/*---- API for FLASH access --------------------------------------------*//*************************************************************************/#define __api_rd_code_byte(address) (*((unsigned char code*) (address)))unsigned char__api_wr_code_byte(int , unsigned char)small;unsigned char__api_wr_code_page(int , int, unsigned char)small;/*---- API for EEPROM access -------------------------------------------*//*************************************************************************/#ifdef ONCHIP_EEPROMvoid __api_wr_eeprom_byte(unsigned int adr, unsigned char value);unsigned char __api_rd_eeprom_byte(unsigned int adr);#endif/*_____ G L O B A L S ___________________________________________________*/sfr16 DPTR = 0x82;/*_____ L O C A L S _____________________________________________________*/#define MSK_AUXR1_ENBOOT0x20#define MSK_AUXR_M00x20#define MAP_BOOT AUXR1 |= MSK_AUXR1_ENBOOT;#define UNMAP_BOOTAUXR1 &= ~MSK_AUXR1_ENBOOT;/*_____ EXTERNAL - F U N C T I O N S - D E C L A R A T I O N ____________*/extern void ASM_MOV_R1_A(void);extern void __API_FLASH_ENTRY_POINT(void);/*F************************************************************************ NAME: __api_wr_code_byte*-------------------------------------------------------------------------* PARAMS:* int address : address to program* unsigned char value : data to write* unsigned char return :* return = 0x00 -> pass* return != 0x00 -> fail*-------------------------------------------------------------------------* PURPOSE:* Program data byte in Flash memory**************************************************************************/unsigned char __api_wr_code_byte (int address, unsigned char value) small{bit ea_save;ea_save = EA;EA = 0;DPTR = address;ACC = 0x02;ASM_MOV_R1_A();ACC = value;MAP_BOOT;__API_FLASH_ENTRY_POINT();UNMAP_BOOT;EA = ea_save; // restore interrupt statereturn (ACC);}/*F************************************************************************ NAME: __api_wr_code_page*-------------------------------------------------------------------------* PARAMS:* int add_flash : address of the first byte to program in the Flash* int add_xram : address in XRAM of the first data to program* unsigned char nb_data : number of bytes to program*unsigned char return :* return = 0x00 -> pass* return != 0x00 -> fail*-------------------------------------------------------------------------* PURPOSE:* Program until 128 Datas in Flash memory.* Number of bytes to program is limited such as the Flash write remains in a* single 128 bytes page.**************************************************************************/unsigned char __api_wr_code_page (int add_flash, int add_xram, unsigned charnb_data) small{unsigned char save_auxr1;bit ea_save;44365A–80C51–07/0454365A–80C51–07/04ea_save = EA;EA = 0;save_auxr1 = AUXR1;AUXR1 &= ~0x01; // Set DPTR=DPTR0DPTR = add_flash;AUXR1++; // DPTR = DPTR1DPTR = add_xram;ACC = 0x09;ASM_MOV_R1_A();ACC = nb_data;AUXR1 &= ~0x01; // Set DPTR = DPTR0MAP_BOOT__API_FLASH_ENTRY_POINT();UNMAP_BOOT;AUXR1 = save_auxr1;EA = ea_save; // restore interrupt statereturn (ACC);}/*F************************************************************************ NAME: __api_rd_eeprom_byte*-------------------------------------------------------------------------* PARAMS:* unsigned int adr: The EEDATA memory location to read* return: value*-------------------------------------------------------------------------* PURPOSE:* This function reads one byte in the on-chip EEPROM data.*-------------------------------------------------------------------------* EXAMPLE:* val=__api_rd_eeprom_byte(128);*-------------------------------------------------------------------------* NOTE:*-------------------------------------------------------------------------* REQUIREMENTS:**************************************************************************/unsigned char __api_rd_eeprom_byte(unsigned int adr){unsigned char val;bit ea_save;while (EECON&1);//Eeprom_busy()ea_save=EA;EA=0;EECON |= 0x02;//Enable eeprom data;val=*(unsigned char xdata*)adr;EECON &= ~0x02;//Disable eeprom data;EA=ea_save;return val;}/*F************************************************************************ NAME: __api_wr_eeprom_byte*-------------------------------------------------------------------------* PARAMS:* unsigned int adr: The EEDATA memory location to read* unsigned char value: The data byte to write* return: none*-------------------------------------------------------------------------* PURPOSE:* This function writes one byte in the on-chip EEPROM data.*-------------------------------------------------------------------------* EXAMPLE:*-------------------------------------------------------------------------* NOTE:*-------------------------------------------------------------------------* REQUIREMENTS:**************************************************************************/void __api_wr_eeprom_byte(unsigned int adr, unsigned char value){bit ea_save;while(EECON & 0x01);// wait bit busyea_save=EA;EA=0;EECON |= 0x02;//Enable eeprom data*(unsigned char xdata*)adr=value;EECON &= ~0x02;//Disable eeprom dataEA=ea_save;}64365A–80C51–07/0474365A–80C51–07/042.2 flash_lib.a51NAME FLASH_LIB;;*A51********************************************************************; FILE_NAME : FLASH_LIB.a51 ;------------------------------------------------------------------------ ;------------------------------------------------------------------------; FILE_PURPOSE: low level function for API;************************************************************************USING 0PUBLIC ASM_MOV_R1_APUBLIC __API_FLASH_ENTRY_POINTAUXR1 EQU0A2hSTART SEGMENT CODERSEG START;************************************************************************; FUNCTION_NAME: ASM_MOV_A_R1;************************************************************************ASM_MOV_R1_A:Mov R1, ARet;************************************************************************; FUNCTION_NAME: __API_FLASH_ENTRY_POINT;************************************************************************__API_FLASH_ENTRY_POINT:PUSHAR2PUSHAR4PUSHAR6LCALL 0FFF0hPOPAR6POPAR4POPAR2RetEND3. API for USB products3.1 flash_eeprom_api.c/*C************************************************************************ NAME: flash_eeprom_api.c*-------------------------------------------------------------------------* Copyright (c) 2004 Atmel.*-------------------------------------------------------------------------* RELEASE:* REVISION:*-------------------------------------------------------------------------* PURPOSE:* This file contains whole of functions to access AT89C5131 Flash and* EEPROM and AT89C51SND1.* CAUTTION : add #define ONCHIP_EEPROM for on-chip eeprom products* (defined by default in the standard delivery)**************************************************************************//*_____ I N C L U D E S _________________________________________________*/#include "reg_C51.h"/*_____ D E F I N I T I O N _____________________________________________*/#define ONCHIP_EEPROM //define it only for build-in eeprom chipsunsigned char data api_command _at_ 0x1C;unsigned char data api_value _at_ 0x1D;#define MSK_AUXR1_ENBOOT 0x20#define MAP_BOOT AUXR1 |= MSK_AUXR1_ENBOOT;#define UNMAP_BOOT AUXR1 &= ~MSK_AUXR1_ENBOOT;#define __API_FLASH_ENTRY_POINT (*((const void(code*)(void)) 0xFFC0 ))/*_____ D E C L A R A T I O N ___________________________________________*//*---- API for FLASH access --------------------------------------------*//*************************************************************************/unsigned char __api_rd_code_byte (unsigned char code * pt_address);unsigned char __api_wr_code_byte (unsigned char xdata* , unsigned char);unsigned char __api_wr_code_page (unsigned char xdata* pt_code,unsigned char xdata* pt_xram,unsigned char nb_data);/*---- API for EEPROM access -------------------------------------------*//*************************************************************************/#ifdef ONCHIP_EEPROMunsigned char __api_rd_eeprom_byte(unsigned char xdata *);unsigned char __api_wr_eeprom_byte(unsigned char xdata *, unsigned char);#endif84365A–80C51–07/0494365A–80C51–07/04/*F************************************************************************ NAME: __api_rd_code_byte*-------------------------------------------------------------------------* PARAMS:* unsigned int address : address in flash memory to read* return:* unsigned char device : read value*-------------------------------------------------------------------------* PURPOSE:* This function allows to read a flash memory byte.*-------------------------------------------------------------------------* EXAMPLE:*-------------------------------------------------------------------------* NOTE:*-------------------------------------------------------------------------* REQUIREMENTS:**************************************************************************/unsigned char __api_rd_code_byte (unsigned char code * pt_address){return(*pt_address);}/*F************************************************************************ NAME: __api_wr_code_byte*-------------------------------------------------------------------------* PARAMS:* unsigned int address : address to program* unsigned char value : data to write* return:* unsigned char return :* return = 0x00 -> pass* return != 0x00 -> fail*-------------------------------------------------------------------------* PURPOSE:* This function allows to program data byte in Flash memory.*-------------------------------------------------------------------------* EXAMPLE:*-------------------------------------------------------------------------* NOTE:*-------------------------------------------------------------------------* REQUIREMENTS:**************************************************************************/unsigned char __api_wr_code_byte (unsigned char xdata * pt_address, unsigned char value){bit ea_save;ea_save = EA;EA = 0;api_command = 0x0D; //_COMMAND_WR_CODE_BYTE;FCON = 0x08;*pt_address = value;MAP_BOOT;__API_FLASH_ENTRY_POINT();UNMAP_BOOT;EA = ea_save; // restore interrupt statereturn(api_value);}/*F************************************************************************ NAME: __api_wr_code_page*-------------------------------------------------------------------------* PARAMS:* unsigned int add_flash : address of the first byte to program* in the Flash* unsigned int add_xram : address in XRAM of the first data to program* unsigned char nb_data : number of bytes to program* return:* unsigned char return :* return = 0x00 -> pass* return != 0x00 -> fail*-------------------------------------------------------------------------* PURPOSE:* This function allows to program until 128 Datas in Flash memory.* Number of bytes to program is limited such as the Flash write remains* in a single 128 bytes page.*-------------------------------------------------------------------------* EXAMPLE:*-------------------------------------------------------------------------* NOTE:* This function used Dual Data Pointer DPTR0&1. At the end of this* function.* DPTR = DPTR0.*-------------------------------------------------------------------------* REQUIREMENTS:**************************************************************************/unsigned char __api_wr_code_page (unsigned char xdata * pt_code,unsigned char xdata * pt_xram,unsigned char nb_data){unsigned char data i, temp, temp_nb_data;bit ea_save;unsigned int data add_pt_code, add_pt_xram;add_pt_xram = pt_xram;add_pt_code = pt_code;temp_nb_data = nb_data;104365A–80C51–07/04114365A–80C51–07/04ea_save = EA;EA = 0;api_command = 0x0D;for (i=0 ; i< temp_nb_data; i++,add_pt_xram++,add_pt_code++){temp = *(unsigned char xdata *)add_pt_xram;FCON = 0x08;*(unsigned char xdata *)add_pt_code = temp;FCON = 0x00;}MAP_BOOT;__API_FLASH_ENTRY_POINT();UNMAP_BOOT;EA = ea_save; // restore interrupt statereturn(api_value);}#ifdef ONCHIP_EEPROM/*F************************************************************************ NAME: api_rd_eeprom*-------------------------------------------------------------------------* PARAMS:* unsigned char xdata *address : address to read* return:*-------------------------------------------------------------------------* PURPOSE:* This function allows to read a byte in Eeprom.*-------------------------------------------------------------------------* EXAMPLE:*-------------------------------------------------------------------------* NOTE:*-------------------------------------------------------------------------* REQUIREMENTS: The EEPROM mustn't be busy to perform the read access.* eeprom status :(EECON & 0x01)=1 busy, =0 free**************************************************************************/unsigned char __api_rd_eeprom_byte(unsigned char xdata *address){unsigned char val;bit ea_save;ea_save = EA;EA = 0;EECON = 0x02;val = *address;EECON = 0x00;EA = ea_save;return (val);}/*F************************************************************************ NAME: api_wr_eeprom_byte*-------------------------------------------------------------------------* PARAMS:* unsigned char xdata* address : address to read* unsigned char value : data to write* return:*-------------------------------------------------------------------------* PURPOSE:* This function allows to program a byte in Eeprom.*-------------------------------------------------------------------------* EXAMPLE:*-------------------------------------------------------------------------* NOTE:*-------------------------------------------------------------------------* REQUIREMENTS: The EEPROM mustn't be busy to perform the read access.* eeprom status :(EECON & 0x01)=1 busy, =0 free**************************************************************************/unsigned char __api_wr_eeprom_byte (unsigned char xdata *address,unsigned char value){bit ea_save;while(EECON & 0x01);// wait bit busyea_save = EA;EA = 0;EECON = 0x02;*address = value;/* addr is a pointer to external data mem */EECON = 0x50;EECON = 0xA0;EA = ea_save;return (1);}#endif124365A–80C51–07/04134365A–80C51–07/044. Example4.1 test_api.c/*C*********************************************************************** NAME: test_api.c*------------------------------------------------------------------------* Copyright (c) 2004 Atmel.*------------------------------------------------------------------------* RELEASE:* REVISION: 1.0*------------------------------------------------------------------------* PURPOSE: usage example of flash_eeprom_api.c*************************************************************************//*_____ I N C L U D E S ________________________________________________*/#include "flash_eeprom_api.c"/*F************************************************************************ NAME: main*-------------------------------------------------------------------------* PARAMS:*-------------------------------------------------------------------------* PURPOSE: usage example of flash_eeprom_api.c*-------------------------------------------------------------------------* EXAMPLE:*-------------------------------------------------------------------------* NOTE:*-------------------------------------------------------------------------* REQUIREMENTS:*************************************************************************/void main (void){int adress;char i=0;char data_tmp;/* write code page example */for(adress=0x0000;adress<0x007F;adress++){/* write 0x55 between 0x0000 and 0x007F of xram */*((unsigned char xdata*) adress)=0x55;}/* copy xram page to flash at 0x1100 */__api_wr_code_page(0x1100,0x0000,0x7F);/* write code byte example */i=0;for(adress=0x1000;adress<0x1006;adress++){/* write "ABCDEF" at 0x1000 */__api_wr_code_byte(adress,0x41+i++);}/* read and write code byte example */for(adress=0x1000;adress<0x1006;adress++){/* copy 0x1000-0x1006 to 0x1010-0x1016 in flash memory */data_tmp = __api_rd_code_byte(adress);__api_wr_code_byte(adress+0x0010,data_tmp);}#ifdef ONCHIP_EEPROM/* write eeprom byte example */i=0;for (adress=0x000;adress<0x400;adress++) /* write 1Ko of eeprom */{/* write a byte, write time = 10ms to 20ms */__api_wr_eeprom_byte(adress,i++);}/* read eeprom byte example */for (adress=0x000;adress<0x400;adress++){/* copy previous writed data from eeprom to flash at 0x1200 */data_tmp=__api_rd_eeprom_byte(adress);__api_wr_code_byte(0x1200+adress,data_tmp);}#endifwhile(1); /* endless */}144365A–80C51–07/04154365A–80C51–07/044.2 SFR Register Definition/*H**************************************************************************** NAME: AT89C51XD2.h*----------------------------------------------------------------------------* PURPOSE: SFR Description file for AT89C51xD2 products* ON KEIL compiler*****************************************************************************/#define Sfr(x, y) sfr x = y#define Sbit(x, y, z) sbit x = y^z#define Sfr16(x,y) sfr16 x = y/*----------------------------------------*//* Include file for 8051 SFR Definitions *//*----------------------------------------*//* BYTE Register */Sfr (P0 , 0x80);Sbit (P0_7 , 0x80, 7);Sbit (P0_6 , 0x80, 6);Sbit (P0_5 , 0x80, 5);Sbit (P0_4 , 0x80, 4);Sbit (P0_3 , 0x80, 3);Sbit (P0_2 , 0x80, 2);Sbit (P0_1 , 0x80, 1);Sbit (P0_0 , 0x80, 0);Sfr (P1 , 0x90);Sbit (P1_7 , 0x90, 7);Sbit (P1_6 , 0x90, 6);Sbit (P1_5 , 0x90, 5);Sbit (P1_4 , 0x90, 4);Sbit (P1_3 , 0x90, 3);Sbit (P1_2 , 0x90, 2);Sbit (P1_1 , 0x90, 1);Sbit (P1_0 , 0x90, 0);Sfr (P2 , 0xA0);Sbit (P2_7 , 0xA0, 7);Sbit (P2_6 , 0xA0, 6);Sbit (P2_5 , 0xA0, 5);Sbit (P2_4 , 0xA0, 4);Sbit (P2_3 , 0xA0, 3);Sbit (P2_1 , 0xA0, 1);Sbit (P2_0 , 0xA0, 0);Sfr (P3 , 0xB0);Sbit (P3_7 , 0xB0, 7);Sbit (P3_6 , 0xB0, 6);Sbit (P3_5 , 0xB0, 5);Sbit (P3_4 , 0xB0, 4);Sbit (P3_3 , 0xB0, 3);Sbit (P3_2 , 0xB0, 2);Sbit (P3_1 , 0xB0, 1);Sbit (P3_0 , 0xB0, 0);Sbit (RD , 0xB0, 7);Sbit (WR , 0xB0, 6);Sbit (T1 , 0xB0, 5);Sbit (T0 , 0xB0, 4);Sbit (INT1 , 0xB0, 3);Sbit (INT0 , 0xB0, 2);Sbit (TXD , 0xB0, 1);Sbit (RXD , 0xB0, 0);Sfr (P4 , 0xC0);Sbit (P4_7 , 0xC0, 7);Sbit (P4_6 , 0xC0, 6);Sbit (P4_5 , 0xC0, 5);Sbit (P4_4 , 0xC0, 4);Sbit (P4_3 , 0xC0, 3);Sbit (P4_2 , 0xC0, 2);Sbit (P4_1 , 0xC0, 1);Sbit (P4_0 , 0xC0, 0);Sfr (P5 , 0xE8);Sbit (P5_7 , 0xE8, 7);Sbit (P5_6 , 0xE8, 6);Sbit (P5_5 , 0xE8, 5);Sbit (P5_4 , 0xE8, 4);Sbit (P5_3 , 0xE8, 3);Sbit (P5_2 , 0xE8, 2);Sbit (P5_1 , 0xE8, 1);Sbit (P5_0 , 0xE8, 0);Sfr (PSW , 0xD0);Sbit (CY , 0xD0 , 7);Sbit (AC , 0xD0 , 6);164365A–80C51–07/04174365A–80C51–07/04Sbit (RS1 , 0xD0 , 4);Sbit (RS0 , 0xD0 , 3);Sbit (OV , 0xD0 , 2);Sbit (UD , 0xD0 , 1);Sbit (P , 0xD0 , 0);Sfr (ACC , 0xE0);Sfr (B , 0xF0);Sfr (SP , 0x81);Sfr (DPL , 0x82);Sfr (DPH , 0x83);Sfr (PCON , 0x87);Sfr (CKCON0 , 0x8F);Sfr (CKCON1 , 0xAF);/*------------------ TIMERS registers ---------------------*/Sfr (TCON , 0x88);Sbit (TF1 , 0x88, 7);Sbit (TR1 , 0x88, 6);Sbit (TF0 , 0x88, 5);Sbit (TR0 , 0x88, 4);Sbit (IE1 , 0x88, 3);Sbit (IT1 , 0x88, 2);Sbit (IE0 , 0x88, 1);Sbit (IT0 , 0x88, 0);Sfr (TMOD , 0x89);Sfr (T2CON , 0xC8);Sbit (TF2 , 0xC8, 7);Sbit (EXF2 , 0xC8, 6);Sbit (RCLK , 0xC8, 5);Sbit (TCLK , 0xC8, 4);Sbit (EXEN2 , 0xC8, 3);Sbit (TR2 , 0xC8, 2);Sbit (C_T2 , 0xC8, 1);Sbit (CP_RL2, 0xC8, 0);Sfr (T2MOD , 0xC9);Sfr (TL0 , 0x8A);Sfr (TL1 , 0x8B);Sfr (TL2 , 0xCC);Sfr (TH0 , 0x8C);Sfr (TH1 , 0x8D);Sfr (TH2 , 0xCD);Sfr (RCAP2L , 0xCA);Sfr (RCAP2H , 0xCB);Sfr (WDTRST , 0xA6);/*------------------- UART registers ------------------------*/Sfr (SCON , 0x98);Sbit (SM0 , 0x98, 7);Sbit (FE , 0x98, 7);Sbit (SM1 , 0x98, 6);Sbit (SM2 , 0x98, 5);Sbit (REN , 0x98, 4);Sbit (TB8 , 0x98, 3);Sbit (RB8 , 0x98, 2);Sbit (TI , 0x98, 1);Sbit (RI , 0x98, 0);Sfr (SBUF , 0x99);Sfr (SADEN , 0xB9);Sfr (SADDR , 0xA9);/*-------------------- Internal Baud Rate Generator --------*/Sfr (BRL , 0x9A);Sfr (BDRCON , 0x9B);/*-------------------- IT registers -----------------------*/Sfr (IEN0 , 0xA8);Sfr (IEN1 , 0xB1);Sfr (IPH0 , 0xB7);Sfr (IPH1 , 0xB3);Sfr (IPL0 , 0xB8);Sfr (IPL1 , 0xB2);/* IEN0 */Sbit (EA , 0xA8, 7);Sbit (EC , 0xA8, 6);Sbit (ET2 , 0xA8, 5);Sbit (ES , 0xA8, 4);Sbit (ET1 , 0xA8, 3);Sbit (EX1 , 0xA8, 2);Sbit (ET0 , 0xA8, 1);Sbit (EX0 , 0xA8, 0);/*--------------------- PCA registers -----------------------------*/Sfr (CCON , 0xD8);Sfr (CMOD , 0xD9);Sfr (CH , 0xF9);184365A–80C51–07/04194365A–80C51–07/04Sfr (CCAP0H , 0xFA);Sfr (CCAP0L , 0xEA);Sfr (CCAPM0 , 0xDA);Sfr (CCAP1H , 0xFB);Sfr (CCAP1L , 0xEB);Sfr (CCAPM1 , 0xDB);Sfr (CCAP2H , 0xFC);Sfr (CCAP2L , 0xEC);Sfr (CCAPM2 , 0xDC);Sfr (CCAP3H , 0xFD);Sfr (CCAP3L , 0xED);Sfr (CCAPM3 , 0xDD);Sfr (CCAP4H , 0xFE);Sfr (CCAP4L , 0xEE);Sfr (CCAPM4 , 0xDE);/* CCON */Sbit (CF , 0xD8, 7);Sbit (CR , 0xD8, 6);Sbit (CCF4 , 0xD8, 4);Sbit (CCF3 , 0xD8, 3);Sbit (CCF2 , 0xD8, 2);Sbit (CCF1 , 0xD8, 1);Sbit (CCF0 , 0xD8, 0);/*------------------ T W I registers ------------------------------*/Sfr ( SSCON , 0x93);Sfr ( SSCS , 0x94);Sfr ( SSDAT , 0x95);Sfr ( SSADR , 0x96);Sfr ( PI2, 0xF8);Sbit (PI2_1 , 0xF8, 1);Sbit (PI2_0 , 0xF8, 0);/*-------------------- OSC control registers ----------------------*/Sfr ( CKSEL , 0x85 );Sfr ( OSCCON , 0x86 );Sfr ( CKRL , 0x97 );/*-------------------- Keyboard control registers -----------------*/Sfr ( KBLS , 0x9C );Sfr ( KBE , 0x9D );Sfr ( KBF , 0x9E );/*-------------------- SPI ---------------------- -----------------*/Sfr ( SPCON, 0xC3 );Sfr ( SPSTA, 0xC4 );Sfr ( SPDAT, 0xC5 );/*------ Misc ----------------------------------------------------*/Sfr( AUXR , 0x8E);Sfr ( AUXR1, 0xA2);Sfr ( FCON, 0xD1);/*------ E data --------------------------------------------------*/Sfr ( EECON, 0xD2 );204365A–80C51–07/04Disclaimer: Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company’s standard warranty which is detailed in Atmel’s Terms and Conditions located on the Company’s web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel’s products are not authorized for use as critical components in life support devices or systems.Atmel CorporationAtmel Operations2325 Orchard Parkway San Jose, CA 95131Tel: 1(408) 441-0311Fax: 1(408) 487-2600Regional HeadquartersEuropeAtmel SarlRoute des Arsenaux 41Case Postale 80CH-1705 Fribourg SwitzerlandTel: (41) 26-426-5555Fax: (41) 26-426-5500AsiaRoom 1219Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong KongTel: (852) 2721-9778Fax: (852) 2722-1369Japan9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTel: (81) 3-3523-3551Fax: (81) 3-3523-7581Memory2325 Orchard Parkway San Jose, CA 95131Tel: 1(408) 441-0311Fax: 1(408) 436-4314Microcontrollers2325 Orchard Parkway San Jose, CA 95131Tel: 1(408) 441-0311Fax: 1(408) 436-4314La Chantrerie BP 7060244306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18Fax: (33) 2-40-18-19-60ASIC/ASSP/Smart CardsZone Industrielle13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00Fax: (33) 4-42-53-60-011150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906Tel: 1(719) 576-3300Fax: 1(719) 540-1759Scottish Enterprise Technology Park Maxwell BuildingEast Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000Fax: (44) 1355-242-743RF/AutomotiveTheresienstrasse 2Postfach 353574025 Heilbronn, Germany Tel: (49) 71-31-67-0Fax: (49) 71-31-67-23401150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906Tel: 1(719) 576-3300Fax: 1(719) 540-1759Biometrics/Imaging/Hi-Rel MPU/High Speed Converters/RF DatacomAvenue de Rochepleine BP 12338521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00Fax: (33) 4-76-58-34-80e-mail********************Web Site4365A–80C51–07/04/xM©Atmel Corporation 2004. All rights reserved. Atmel, the Atmel logo, andcombinations thereof are registered trademarks of Atmel Corporation or its subsidiaries. Windows ® Windows 98™, Windows XP ™, and Windows 2000™ are trademarks and/ore registered trademark of Microsoft Corporation. Other terms and product names in this document may be the trademarks of others.。

8051单片机实验报告

8051单片机实验报告练习题一1-1修改例程一的源程序:(1)将A寄存器的初值改为80H(正逻辑,数据位为1表示发光二极管点亮),再对源程序进行简单修改,使程序运行后发光二极管点亮情况与修改前相同。

(2)将LED向左循环移位点亮改为向右循环移位点亮。

(3)加快LED循环移位点亮的速度。

(1)在源程序MOV A,#080H后加CPL A(对A取反,80H取反后为7FH)。

(2)将RR A改为RL A。

(3)删除几个CALL DELAY。

1-2将例程二0-F的循环显示改为0-9的循环显示。

将源程序中CJNE A,#10H,MAIN改为CJNE A,#0AH,MAIN.练习题二2-1通过对例程5的程序进行修改和上机调试,改变原程序的功能。

(1)将KEY2,KEY4的功能对调。

(2)每次停下再启动后,更改发光二极管点亮的循环方向。

(1)将ORG 0003H改为0013H,将ORG 0013H改为0003H;将MOV IP,#01H改为MOV IP,#04H;将SETB EX1改为SETB EX0,将SETB EX0改为SETB EX1,将CLR EX0改为CLR EX1;将CLR IE1改为CLR IE0,将CLR IE0改为CLR IE1;(2)程序如下,主要利用两个循环分别进行左移与右移。

$include (C8051F020.inc)ORG 0000HLJMP INITIALORG 0013HLJMP STARORG 0003HLJMP STOPORG 0100HINITIAL: LCALL Init_DeviceMOV R4,#0FHMOV P3,#0FFHMOV A,#0FFHMOV DPTR,#7F80HMOVX @DPTR,AMOV A,#0FEHMOV R1,#1HMOV IP,#04HMOV TCON,#05HSETB EX0SETB EALOOP1: CLR EACJNE R4,#0FH,LOOP2RL ACJNE R4,#0FH,LOOP2MOV P3,ACJNE R4,#0FH,LOOP2INC R1CJNE R4,#0FH,LOOP2SETB EALCALL DELAY1LCALL DELAY1LCALL DELAY1LCALL DELAY1CJNE R1,#8,LOOP1MOV R1,#0HSJMP LOOP1LOOP2: CLR EACJNE R4,#0F0H,LOOP1RR ACJNE R4,#0F0H,LOOP1MOV P3,ACJNE R4,#0F0H,LOOP1DEC R1SETB EALCALL DELAY1LCALL DELAY1LCALL DELAY1LCALL DELAY1CJNE R1,#0,LOOP2MOV R1,#8SJMP LOOP2STOP: PUSH ACCMOV A,R1MOV DPTR,#TABMOVC A,@A+DPTRMOV DPTR,#7F80HMOVX @DPTR,ASETB EX1JNZ $MOV A,#0FFHMOVX @DPTR,ACLR EX1POP ACCCLR IE0RETISTAR: MOV A,#00HCLR IE1PUSH ACCMOV A,R4CPL AMOV R4,APOP ACCRETITAB: DB 0C0H,0F9H,0A4H,0B0H,099HDB 092H,082H,0F8H,080H DELAY1: MOV R6,#0D1: MOV R7,#0DJNZ R7,$DJNZ R6,D1RET$include (Init_Device.inc) ;END2-2修改例程6,将计数范围由0-F扩展至00-FF(使用定时器/计时器0),并在2位数码管上用10进制数显示计数结果(00-99)。

温度监测中英文翻译

土壤温度测量的设计1.简介温度是土壤的一个十分重要的环境因素,它直接影响微生物的活跃性及有机物的分解,影响植物的根吸收水分与矿物质,同时它在植物生长率及根的范围上发挥着重要作用。

据统计,植物的根一般在地下50厘米范围内,因此测量这一范围内不同深度的土壤温度变得十分有意义。

目前,土壤温度测量仪器可分为三类。

第一种,是利用热敏电阻与土壤温度之间的关系测量实际温度。

在使用这类仪器前,系统参数需要校正,同时当解决系统遇到的问题时,十分不便。

第二种是非接触式的土壤测温仪器,它通过红外线测量温度,这种设备价格昂贵。

第三种,通过数字温度计测量温度。

目前,这类仪器不仅可测量一点的土壤温度,还可将数据进行存储与传输。

总之,上述设备因为价格过于昂贵或功能过于简单,而得不到广泛应用。

因此,一种价格更廉价,更能更强大的仪器需要去开发设计。

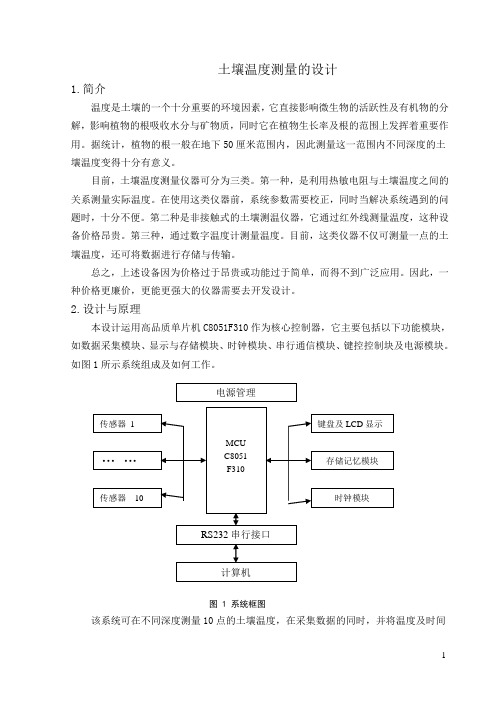

2.设计与原理本设计运用高品质单片机C8051F310作为核心控制器,它主要包括以下功能模块,如数据采集模块、显示与存储模块、时钟模块、串行通信模块、键控控制块及电源模块。

如图1所示系统组成及如何工作。

图 1 系统框图该系统可在不同深度测量10点的土壤温度,在采集数据的同时,并将温度及时间数据予以显示之后,系统通过串行通信接口将数据传送到计算机。

用户可以通过按键设置系统参数及运行系统。

经过试验,这种效率高成本低的便携式的仪器能平稳工作且运行良好。

2.1硬件设计在硬件设计中,系统可利用的部分包括C8051F310单片机、DS18B20数字温度传感器、ISL6292可编程锂电池充电管理芯片、NCP500电压管理芯片以及DS1302时钟芯片,它们通过相应的外围电路连接在一起,同时这几部分是系统的核心结构。

下面就介绍这些核心部分及其外围电路。

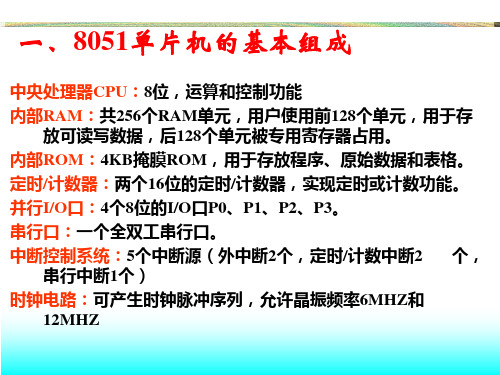

2.1.1高质量C8051F310单片机C8051F310是一款兼容8051指令集的完全集成的混合信号ISP型MCU芯片。

C8051F310主要由CIP-51内核、外围模拟电路、数字I/O口及电源模块组成。

汇编指令大全

ORG 0000HNOP ;空操作指令AJMP L0003 ;绝对转移指令L0003: LJMP L0006 ;长调用指令L0006: RR A ;累加器A内容右移(先置A为88H)INC A ; 累加器A 内容加1INC 01H ;直接地址(字节01H)内容加1INC @R0 ; R0的内容(为地址) 的内容即间接RAM加1;(设R0=02H,02H=03H,单步执行后02H=04H)INC @R1 ; R1的内容(为地址) 的内容即间接RAM加1;(设R1=02H,02H=03H,单步执行后02H=04H)INC R0 ; R0的内容加1 (设R0为00H,单步执行后查R0内容为多少) INC R1 ; R1的内容加1(设R1为01H,单步执行后查R1内容为多少) INC R2 ; R2的内容加1 (设R2为02H,单步执行后查R2内容为多少) INC R3 ; R3的内容加1(设R3为03H,单步执行后查R3内容为多少) INC R4 ; R4的内容加1(设R4为04H,单步执行后查R4内容为多少) INC R5 ; R5的内容加1(设R5为05H,单步执行后查R5内容为多少) INC R6 ; R6的内容加1(设R6为06H,单步执行后查R6内容为多少) INC R7 ; R7的内容加1(设R7为07H,单步执行后查R7内容为多少) JBC 20H,L0017; 如果位(如20H,即24H的0位)为1,则转移并清0该位L0017: ACALL S0019 ;绝对调用S0019: LCALL S001C ;长调用S001C: RRC A ;累加器A的内容带进位位右移(设A=11H,C=0;单步执行后查A和C内容为多少)DEC A ;A的内容减1DEC 01H ;直接地址(01H)内容减1DEC @R0 ;R0间址减1,即R0的内容为地址,该地址的内容减1 DEC @R1 ; R1间址减1DEC R0 ; R0内容减1DEC R1 ; R1内容减1DEC R2 ; R2内容减1DEC R3 ; R3内容减1DEC R4 ; R4内容减1DEC R5 ; R5内容减1DEC R6 ; R6内容减1DEC R7 ; R7内容减1JB 20H,L002D;如果位(20H,即24H的0位)为1则转移L002D: AJMP L0017 ;绝对转移RET ;子程序返回指令RL A ;A左移ADD A,#01H ;A的内容与立即数(01H)相加ADD A,01H ; A的内容与直接地址(01H内容)相加ADD A,@R0 ; A的内容与寄存器R0的间址内容相加ADD A,@R1 ; A的内容与寄存器R1的间址内容相加ADD A,R0 ; A的内容与寄存器R0的内容相加ADD A,R1 ; A的内容与寄存器R1的内容相加ADD A,R2 ; A的内容与寄存器R2的内容相加ADD A,R3 ; A的内容与寄存器R3的内容相加ADD A,R4 ; A的内容与寄存器R4的内容相加ADD A,R5 ; A的内容与寄存器R5的内容相加ADD A,R6 ; A的内容与寄存器R6的内容相加ADD A,R7 ; A的内容与寄存器R7的内容相加JNB 30H,L0041 ;直接位(30H)为0相对转移L0041: ACALL S0100 ;绝对调用RETI ;中断返回指令RLC A ;带进位位左移ADDC A,#02H ;A带进位位与立即数(#02H)相加ADDC A,02H ; A带进位位与直接地扯(02H内容)相加ADDC A,@R0 ; A带进位位与R0间扯内容相加ADDC A,@R1 ; A带进位位与R1间扯内容相加ADDC A,R0 ; A带进位位与R0内容相加ADDC A,R1 ; A带进位位与R1内容相加ADDC A,R2 ; A带进位位与R2内容相加ADDC A,R3 ; A带进位位与R3内容相加ADDC A,R4 ; A带进位位与R4内容相加ADDC A,R5 ; A带进位位与R5内容相加ADDC A,R6 ; A带进位位与R6内容相加ADDC A,R7 ; A带进位位与R7内容相加JC L0095 ;进位为1转移NOPAJMP L0017 ;绝对转移ORL 02H,A ;直接地址内容与A或ORL 02H,#02H ; 直接地址内容与立即数或ORL A,#44H ;A与立即数或ORL A,02H ; A与直接地址内容或ORL A,@R0 ; A与R0间址内容或ORL A,@R1 ; A与R1间址内容或ORL A,R0 ; A与R0内容或ORL A,R1 ; A与R1内容或ORL A,R2 ; A与R2内容或ORL A,R3 ; A与R3内容或ORL A,R4 ; A与R4内容或ORL A,R5 ; A与R5内容或ORL A,R6 ; A与R6内容或ORL A,R7 ; A与R7内容或JNC L0017 ;进位为0转移ACALL L0017 ;绝对调用ANL 02H,A ; 直接地址与A与ANL 02H,#02H ; 立即数与直接地址与ANL A,#02H ; A与立即数与ANL A,02H ;A与直接地址与ANL A,@R0 ; A与R0间址与ANL A,@R1 ; A与R1间址与ANL A,R0 ; A与R0与ANL A,R1 ; A与R1与ANL A,R2 ; A与R2与ANL A,R3 ; A与R3与ANL A,R4 ; A与R4与ANL A,R5 ; A与R5与ANL A,R6 ; A与R6与ANL A,R7 ; A与R7与JZ L0084 ;A为零转移L0084: AJMP L0017 ;绝对转移XRL 01H,A ;直接地址与A异或XRL 02H,#01H ; 直接地址与立即数异或XRL A,#01H ;A与立即数异或XRL A,01H ; A与直接地址异或XRL A,@R0 ; A与R0间址址异或XRL A,@R1 ; A与R1间址址异或XRL A,R0 ; A与R0异或XRL A,R1 ; A与R1异或XRL A,R2 ; A与R2异或XRL A,R3 ; A与R3异或XRL A,R4 ; A与R4异或L0095: XRL A,R5 ; A与R5异或XRL A,R6 ; A与R6异或XRL A,R7 ; A与R7异或JNZ L0084 ;A不为零转L009A: ACALL L0084 ;绝对调用ORL C,01H ;直接位或到进位JMP @A+DPTR;相对于DPTR间接转MOV A,#01H ;立即数送AMOV 01H,#02H ;立即数送直接地址MOV @R0,#01H ;立即数送间址R0 MOV @R1,#02H ; 立即数送间址R1 MOV R0,#01H ; 立即数送R0MOV R1,#01H ; 立即数送R1MOV R2,#01H ; 立即数送R2MOV R3,#01H ; 立即数送R3MOV R4,#01H ; 立即数送R4MOV R5,#01H ; 立即数送R5MOV R6,#01H ; 立即数送R6MOV R7,#01H ; 立即数送R7SJMP L00BA ;短转移L00BA: AJMP L0095 ;绝对转移ANL C,02H ;直接地址与进位与ORG 00C0H ;MOV 02H,01H ;直接地址送直接地址MOV 01H,@R0;间址R0送直接地址MOV 01H,@R1; 间址R1送直接地址MOV 01H,R0 ; R0送直接地址MOV 01H,R1 ; R1送直接地址MOV 01H,R2 ; R2送直接地址MOV 01H,R3 ; R3送直接地址MOV 01H,R4 ; R4送直接地址MOV 01H,R5 ; R5送直接地址MOV 01H,R6 ; R6送直接地址MOV 01H,R7 ; R7送直接地址NOPMOV DPTR,#1234H;建立数据指针地址为1234HACALL L00BA ;绝对调用MOV 03H,C ;进位送03H位(即20H的03位)MOVC A,@A+DPTR ;由A+DPTR寻扯的程序存贮器字节送A SUBB A,#01H ;A减去立即数和进位位SUBB A,02H ; A减去直接地址内容和进位位SUBB A,@R0 ; A减去R0间接RAM和进位位SUBB A,@R1 ; A减去R1间接RAM和进位位SUBB A,R0 ; A减去R0和进位位SUBB A,R1 ; A减去R1和进位位SUBB A,R2 ; A减去R2和进位位SUBB A,R3 ; A减去R3和进位位SUBB A,R4 ; A减去R4和进位位SUBB A,R5 ; A减去R5和进位位SUBB A,R6 ; A减去R6和进位位SUBB A,R7 ; A减去R7和进位位ORL C,/00H ;直接位的反或到进位AJMP L0084 ;绝对转移MOV C,03H ;直接位数送进位INC DPTR ;数据指针加1MUL AB ;A乘以BNOP ;A5H为二字节空操作指令NOPMOV @R0,05H ;直接字芯送R0间接RAMMOV @R1,05H ; 直接字芯送R1间接RAMMOV R0,05H ; 直接字芯送R0MOV R1,05H ; 直接字芯送R1S0100: MOV R2,05H ; 直接字芯送R2MOV R3,05H ; 直接字芯送R3MOV R4,05H ; 直接字芯送R4MOV R5,05H ; 直接字芯送R5MOV R6,05H ; 直接字芯送R6MOV R7,05H ; 直接字芯送R7ANL C,/04H ; 直接位的反与到进位ACALL S0100 ;绝对调用CPL 04H ;直接位取反CPL C ;进位取反CJNE A,#01H,L0139 ;立即数与A比较,不相等则转移CJNE A,01H,L0139 ; 直接字节与A比较,不相等则转移CJNE @R0,#01H,L0139 ; 立即数与R0间接RAM比较,不相等则转移CJNE @R1,#01H,L0139 ; 立即数与R1间接RAM比较,不相等则转移CJNE R0,#01H,L0139 ; 立即数与R0比较,不相等则转移CJNE R1,#01H,L0139 ; 立即数与R1比较,不相等则转移CJNE R2,#01H,L0139 ; 立即数与R2比较,不相等则转移CJNE R3,#01H,L0139 ; 立即数与R3比较,不相等则转移CJNE R4,#01H,L0139 ; 立即数与R4比较,不相等则转移CJNE R5,#01H,L0139 ; 立即数与R5比较,不相等则转移CJNE R6,#01H,L0139 ; 立即数与R6比较,不相等则转移CJNE R7,#01H,L0139 ; 立即数与R7比较,不相等则转移PUSH 00H ;直接字节进栈,SP加1L0139: AJMP L0084 ;绝对转移CLR 04H ;直接位清零CLR C ;清零进位SWAP A ;A左环移四位(A的二个半字节交换)XCH A,05H ;交换A和直接字节XCH A,@R0 ; 交换A和R0间接RAMXCH A,@R1 ; 交换A和R1间接RAMXCH A,R0 ; 交换A和R0XCH A,R1 ; 交换A和R1XCH A,R2 ; 交换A和R2XCH A,R3 ; 交换A和R3XCH A,R4 ; 交换A和R4XCH A,R5 ; 交换A和R5XCH A,R6 ; 交换A和R6XCH A,R7 ; 交换A和R7POP 00H ;直接字节出栈,SP减1ACALL L0139 ;绝对调用SETB 03H ;置位直接位SETB C ;置位进位DA A ;A的十进制加法调熊DJNZ 01H,L0139 ;直接字节减1,不为零则转移XCHD A,@R0 ;交换A和R0间接RAM的低4位XCHD A,@R1 ; 交换A和R1间接RAM的低4位L0158: DJNZ R0,L0139 ; R0减1,不为零则转移DJNZ R1,L0158 ; R1减1,不为零则转移DJNZ R2,L0158 ; R2减1,不为零则转移DJNZ R3,L0158 ; R3减1,不为零则转移DJNZ R4,L0158 ; R4减1,不为零则转移DJNZ R5,L0158 ; R5减1,不为零则转移DJNZ R6,L0158 ; R6减1,不为零则转移DJNZ R7,L0158 ; R7减1,不为零则转移MOVX A,@DPTR ;外部数据(16位地址)送AL0169: NOPAJMP L0139 ;绝对转移MOVX A,@R0 ;R0间址即外部数据(8位地址)送A MOVX A,@R1 ; R1间址即外部数据(8位地址)送A CLR A ;清零AMOV A,05H ;直接字节送AMOV A,@R0 ;R0间接RAM送AMOV A,@R1 ; R1间接RAM送AMOV A,R0 ; R0送AMOV A,R1 ; R1送AMOV A,R2 ; R2送AMOV A,R3 ; R3送AMOV A,R4 ; R4送AMOV A,R5 ; R5送AMOV A,R6 ; R6送AMOV A,R7 ; R7送AMOVX @DPTR,A ;A送外部数据(16位地址)NOPACALL L0169 ;绝对调用MOVX @R0,A ;A送R0间址即外部数据(8位地址) MOVX @R1,A ; A送R1间址即外部数据(8位地址) CPL A ;A取反MOV 05H,A ;A送直接字节MOV @R0,A ; A送R0间址即间接RAMMOV @R1,A ; A送R1间址即间接RAMMOV R0,A ; A送R0MOV R1,A ; A送R1MOV R2,A ; A送R2MOV R3,A ; A送R3MOV R4,A ; A送R4MOV R5,A ; A送R5MOV R6,A ; A送R6MOV R7,A ; A送R7END51的汇编控制指令详细列表8051 INSTRUCTION SET1.Arithmetic operations:Mnemonic Byte CycADD A,@Ri 1 1ADD A,Rn 1 1ADD A,direct 2 1ADD A,#data 2 1ADDC A,@Ri 1 1ADDC A,Rn 1 1ADDC A,direct 2 1ADDC A,#data 2 1SUBB A,@Ri 1 1SUBB A,Rn 1 1SUBB A,direct 2 1SUBB A,#data 2 1INC A 1 1INC @Ri 1 1INC Rn 1 1INC DPTR 1 1INC direct 2 1INC direct 2 1DEC A 1 1DEC @Ri 1 1DEC Rn 1 1DEC direct 2 1MUL AB 1 4DIV AB 1 4DA A 1 18051的汇编控制指令,占用字节,执行周期列表3.Data transfer:Mnemonic Byte CycMOV A,@Ri 1 1MOV DPTR,#data16 3 2MOV A,Rn 1 1MOVC A,@A+DPTR 1 2MOV A,direct 2 1MOVC A,@A+PC 1 2MOV A,#data 2 1MOVX A,@Ri 1 2 8051的汇编控制指令,占用字节,执行周期列表2. Logical opreations:ANL A,@Ri 1 1XRL A,@Ri 1 1ANL A,Rn 1 1XRL A,Rn 1 1ANL A,direct 2 1XRL A,direct 2 1ANL A,#data 2 1XRL A,#data 2 1ANL direct,A 2 1XRL direct,A 2 1ANL direct,#data 3 2XRL direct,#data 3 2ORL A,@Ri 1 1CLR A 1 1ORL A,Rn 1 1CPL A 1 1ORL A,direct 2 1RL A 1 1ORL A,#data 2 1RLC A 1 1ORL direct,A 2 1RR A 1 1ORL direct,#data 3 2RRC A 1 1SWAP A 1 18051的汇编控制指令,占用字节,执行周期列表4.Boolean variable manipulation:Mnemonic Byte CycCLR C 1 1ANL C,bit 2 2SETB C 1 1ANL C,/bit 2 2CPL C 1 1ORL C,bit 2 2CLR bit 2 1ORL C,/bit 2 2SETB bit 2 1MOV C,bit 2 1CPL bit 2 1MOV bit,C 2 2MOV @Ri,A 1 1MOVX A,@DPTR 1 2 MOV @Ri,direct 2 2 MOVX @Ri,A 1 2 MOV @Ri,#data 2 1 MOVX @DPTR,A 1 2 MOV Rn,A 1 1 PUSH direct 2 2 MOV Rn,direct 2 2 POP direct 2 2MOV Rn,#data 2 1 XCH A,@Ri 1 1 MOV direct,A 2 1 XCH A,Rn 1 1MOV direct,@Ri 2 2 XCH A,direct 2 1 MOV direct,Rn 2 2 XCHD A,@Ri 1 1 MOV direct,direct 3 2 MOV direct,#data 3 2 8051的汇编控制指令,占用字节,执行周期列表5.Program and machine control:Mnemonic Byte CycNOP 1 1JZ rel 2 2RET 1 2JNZ rel 2 2RETI 1 2JC rel 2 2ACALL addr11 2 2JNC rel 2 2AJMP addr11 2 2JB bit,rel 3 2LCALL addr16 3 2JNB bit,rel 3 2LJMP addr16 3 2JBC bit,rel 3 2SJMP rel 2 2CJNE A,direct,rel 3 2JMP @A+DPTR 1 2CJNE A,#data,rel 3 2DJNZ Rn,rel 2 2CJNE @Ri,#data,rel 3 2DJNZ direct,rel 3 2CJNE Rn,#data,rel 3 2。

8051兼容安全微控制器DS2252T数据表说明书

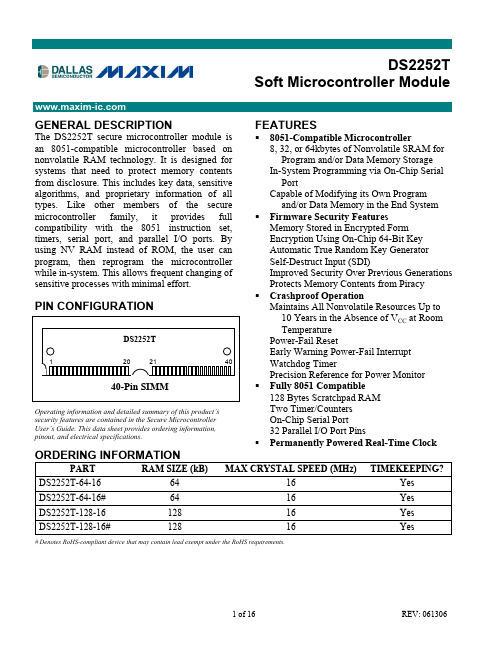

GENERAL DESCRIPTIONThe DS2252T secure microcontroller module is an 8051-compatible microcontroller based on nonvolatile RAM technology. It is designed for systems that need to protect memory contents from disclosure. This includes key data, sensitive algorithms, and proprietary information of all types. Like other members of the secure microcontroller family, it provides full compatibility with the 8051 instruction set, timers, serial port, and parallel I/O ports. By using NV RAM instead of ROM, the user can program, then reprogram the microcontroller while in-system. This allows frequent changing of sensitive processes with minimal effort. PIN CONFIGURATIONOperating information and detailed summary of this product’ssecurity features are contained in the Secure Microcontroller User’s Guide. This data sheet provides ordering information,pinout, and electrical specifications.FEATURES8051-Compatible Microcontroller 8, 32, or 64kbytes of Nonvolatile SRAM for Program and/or Data Memory Storage In-System Programming via On-Chip Serial Port Capable of Modifying its Own Program and/or Data Memory in the End System Firmware Security Features Memory Stored in Encrypted Form Encryption Using On-Chip 64-Bit Key Automatic True Random Key Generator Self-Destruct Input (SDI) Improved Security Over Previous Generations Protects Memory Contents from PiracyCrashproof OperationMaintains All Nonvolatile Resources Up to 10 Years in the Absence of V CC at Room Temperature Power-Fail Reset Early Warning Power-Fail Interrupt Watchdog Timer Precision Reference for Power Monitor Fully 8051 Compatible 128 Bytes Scratchpad RAM Two Timer/Counters On-Chip Serial Port 32 Parallel I/O Port Pins Permanently Powered Real-Time ClockORDERING INFORMATIONPARTRAM SIZE (kB)MAX CRYSTAL SPEED (MHz)TIMEKEEPING?DS2252T-64-16 64 16 Yes DS2252T-64-16# 64 16 Yes DS2252T-128-16 128 16 Yes DS2252T-128-16# 12816Yes# Denotes RoHS-compliant device that may contain lead exempt under the RoHS requirements.DS2252TSoft Microcontroller ModuleDETAILED DESCRIPTIONThe DS2252T provides an array of mechanisms to prevent an attacker from examining the memory. It is designed to resist all levels of threat including observation, analysis, and physical attack. As a result, a massive effort would be required to obtain any information about memory contents. Furthermore, the “Soft” nature of the DS2252T allows frequent modification of secure information. This minimizes that value of any information that is obtained.Using a security system based on the DS5002FP, the DS2252T protects the memory contents from disclosure. It loads program memory via its serial port and encrypts it in real time prior to storing it in SRAM. Once encrypted, the RAM contents and the program flow are unintelligible. The real data exists only inside the processor chip after being decrypted. Any attempt to discover the on-chip data, encryption keys, etc., results in its destruction. Extensive use of nonvolatile lithium-backed technology creates a microcontroller that retains data for over 10 years at room temperature, but which can be erased instantly if tampered with. The DS2252T even interfaces directly to external tamper protection hardware.The DS2252T provides a permanently powered real time lock with interrupts for time stamp and date. It keeps time to one hundredth of a second using its onboard 32 kHz crystal.Like other Secure Microcontrollers in the family, the DS2252T provides crashproof operation in portable systems or systems with unreliable power. These features include the ability to save the operating state, Power-fail Reset, Power-fail Interrupt, and Watchdog Timer. All nonvolatile memory and resources are maintained for over 10 years at room temperature in the absence of power.A user loads programs into the DS2252T via its on-chip Serial Bootstrap Loader. This function supervises the loading of software into NV RAM, validates it, then becomes transparent to the user. It also manages the loading of new encryption keys automatically. Software is stored in onboard CMOS SRAM. Using its internal Partitioning, the DS2252T can divide a common RAM into user selectable program and data segments. This Partition can be selected at program loading time, but can be modified anytime later. The microcontroller will decode memory access to the SRAM, access memory via its Byte-wide bus and write-protect the memory portion designated as program (ROM).DS2252T BLOCK DIAGRAM Figure 1PIN ASSIGNMENTPIN NAME PIN NAME1 P1.0 11 P1.52 V CC12 P0.4 3 P1.1 13 P1.6 4 P0.0 14 P0.55 P1.215 P1.76 P0.1 16 P0.67 P1.3 17 RST8 P0.2 18 P0.79 P1.4 19 P3.0/RXD 10 P0.3 20 SDIINSTRUCTION SETThe DS2252T executes an instruction set that is object code-compatible with the industry standard 8051 microcontroller. As a result, software development packages such as assemblers and compilers that have been written for the 8051 are compatible with the DS2252T. A complete description of the instruction set and operation are provided in the Secure Microcontroller User’s Guide.MEMORY ORGANIZATIONFigure 2 illustrates the memory map accessed by the DS2252T. The entire 64k of program and 64k of data are available to the Byte-wide bus. This preserves the I/O ports for application use. An alternate configuration allows dynamic Partitioning of a 64k space as shown in Figure 3. Any data area not mapped into the NV RAM is reached via the Expanded bus on Ports 0 and 2. Off-board program memory is not available for security reasons. Selecting PES = 1 provides access to the real-time clock as shown in Figure 4. These selections are made using Special Function Registers. The memory map and its controls are covered in detail in the Secure Microcontroller User’s Guide.DS2252T MEMORY MAP IN NON-PARTITIONABLE MODE (PM = 1) Figure 2DS2252T MEMORY MAP IN PARTITIONABLE (PM = 0) Figure 3NV RAM PROGRAM NV RAM DATAPROGRAM MEMORY DATA MEMORY (MOVX)FFFFh --0000h ---- 64KNV RAM PROGRAMNV RAM DATAPROGRAM MEMORYDATA MEMORY (MOVX)FFFFh --0000h --PARTITIONNOTE: PARTITIONABLE MODE IS NOT SUPPORTED ON THE 128KB VERSION OF THE DS2252T.LEGEND:=NV RAM MEMORY= EXPANDED BUS (PORTS 0 AND 2)=NOT AVAILABLEDS2252T MEMORY MAP WITH (PES = 1) Figure 4POWER MANAGEMENTThe DS2252T monitors V CC to provide power-fail reset, early warning power-fail interrupt, and switchover to lithium backup. It uses an internal band-gap reference in determining the switch points. These are called V PFW , V CCMIN , and V LI respectively. When V CC drops below V PFW , the DS2252T will perform an interrupt vector to location 2Bh if the power-fail warning is enabled. Full processor operation continues regardless. When power falls further to V CCMIN , the DS2252T invokes a reset state. No further code execution will be performed unless power rises back above V CCMIN . All decoded chip enables and the R/W signal go to an inactive (logic 1) state. V CC is still the power source at this time. When V CC drops further to below V LI , internal circuitry will switch to the built-in lithium cell for power. The majority of internal circuits will be disabled and the remaining nonvolatile states will be retained. The Secure Microcontroller User’s Guide has more information on this topic. The trip points V CCMIN and V PFW are listed in the electrical specifications.NV RAM PROGRAMPROGRAM MEMORY DATA MEMORY (MOVX)FFFFh --0000h --PARTITION=NOT ACCESSIBLEREAL-TIME CLOCKC000h --B000h --4000h ---- 64K-- 16KABSOLUTE MAXIMUM RATINGSVoltage Range on Any Pin Relative to Ground……………………………………...-0.3V to (V CC + 0.5V) Voltage Range on V CC Relative to Ground…………………………………………………-0.3V to +6.0V Operating Temperature Range……………………………………………………………...-40°C to +85°C Storage Temperature (Note 1)…………………………………………………………….-55°C to +125°C Soldering Temperature………………………………………………………………+260°C for 10 seconds This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.Note 1: Storage temperature is defined as the temperature of the device when V CC = 0V and V LI = 0V. In this state the contents of SRAM are not battery-backed and are undefined.DC CHARACTERISTICSDC CHARACTERISTICS (continued)(V CC = 5V ±10%, T A = 0°C to +70°C.)PARAMETER SYMBOL MIN TYP MAX UNITS NOTESWith BAT = 3.0V 4.0 4.25Reset Trip Point in StopMode With BAT =3.3V4.4 4.65V 1SDI Input High Voltage V IHS 2.0 V CC V 1,2 SDI Input High Voltage V IHS 2.0 3.5 V 1,2 SDI Pulldown Resistor R SDI 25 60 kΩAC CHARACTERISTICS(V CC = 0V to 5V, T A = 0°C to +70°C.)PARAMETER SYMBOL MIN TYP MAX UNITS NOTES(4.5V < V CC < 5.5V) t SPR 2SDI Pulse Reject(V CC = 0V, V BAT = 2.9V) 4µs 10(4.5V < V CC < 5.5V) t SPA 10 SDI PulseAccept (VCC = 0V,V BAT = 2.9V) 50µs 10AC CHARACTERISTICS—EXPANDED BUS MODE TIMING SPECIFICATIONSEXPANDED DATA MEMORY READ CYCLEEXPANDED DATA MEMORY WRITE CYCLEAC CHARACTERISTICS—EXTERNAL CLOCK DRIVE (V CC = 5V ±10%, T A = 0°C to +70°C.)# PARAMETER SYMBOL MIN MAX UNITS At 12MHz 20 28 External Clock High Time At 16MHz t CLKHPW 15 nsAt 12MHz 2029 External Clock Low Time At 16MHz t CLKLPW 15 nsAt 12MHz 2030 External Clock Rise Time At 16MHz t CLKR 15 nsAt 12MHz20 31 External Clock Fall Time At 16MHzt CLKF15nsEXTERNAL CLOCK TIMINGAC CHARACTERISTICS—POWER CYCLE TIMING(V CC = 5V ±10%, T A = 0°C to +70°C.)# PARAMETER SYMBOL MIN MAX UNITS 32 Slew Rate from V CCMIN to 3.3V t F 130µs8)33 Crystal Startup Time t CSU (Note34 Power-On Reset Delay t POR 21,504t CLK POWER CYCLE TIMINGAC CHARACTERISTICS—SERIAL PORT TIMING: MODE 0(V CC = 5V ±10%, T A = 0°C to +70°C.)# PARAMETER SYMBOL MIN MAX UNITS35 Serial Port Clock Cycle Time t SPCLK 12t CLK µs36 Output Data Setup to Rising Clock Edge t DOCH 10t CLK - 133 ns37 Output Data Hold after Rising Clock Edge t CHDO 2t CLK - 117 ns38 Clock Rising Edge to Input Data Valid t CHDV 10t CLK - 133 nsns 39 Input Data Hold after Rising Clock Edge t CHDIV 0SERIAL PORT TIMING: MODE 0NOTES:1. All voltage referenced to ground.2. SDI should be taken to a logic high when V CC = +5V, and to approximately 3V when V CC < 3V.3. SDI is deglitched to prevent accidental destruction. The pulse must be longer than t SPR to pass thedeglitcher, but SDI is not guaranteed unless it is longer than t SPA.4. Maximum operating I CC is measured with all output pins disconnected; XTAL1 driven with t CLKR,t CLKF=10 ns, V IL = 0.5V; XTAL2 disconnected; RST = PORT0 = V CC.5. Idle mode I IDLE is measured with all output pins disconnected; XTAL1 driven with t CLKR, t CLKF = 10ns, V IL = 0.5V; XTAL2 disconnected; PORT0 = V CC, RST = V SS.6. Stop mode I STOP is measured with all output pins disconnected; PORT0 = V CC; XTAL2 notconnected; RST = XTAL1 = V SS.7. Pin capacitance is measured with a test frequency—1 MHz, T A = +25°C.8. Crystal startup time is the time required to get the mass of the crystal into vibrational motion from thetime that power is first applied to the circuit until the first clock pulse is produced by the on-chiposcillator. The user should check with the crystal vendor for a worst-case specification on this time.PACKAGE DRAWINGDIM MIN MAXA 2.645 2.655B 2.379 2.389C 0.995 1.005D 0.395 0.405E 0.245 0.255F 0.050 BSCG 0.075 0.085H 0.245 0.255I 0.950 BSCJ 0.120 0.130K 1.320 1.330L 1.445 1.455M 0.057 0.067N - 0.300O - 0.165P 0.047 0.054DATA SHEET REVISION SUMMARYThe following represent the key differences between 12/13/95 and 08/16/96 version of the DS2252T data sheet. Please review this summary carefully.1. Change V CC slew rate specification to reference 3.3V instead of V LI.2. Add minimum value to PCB thickness.The following represent the key differences between 08/16/96 and 05/28/97 version of the DS2252T data sheet. Please review this summary carefully.1. AC characteristics for battery-backed SDI pulse specification added.The following represent the key differences between 05/28/97 and 11/08/99 version of the DS2252T data sheet. Please review this summary carefully. (PCN I80903)1. Correct Absolute Maximum Ratings to reflect changes to DS5002FP microprocessor.2. Add note clarifying that SRAM contents are not defined under storage temperature conditions. The following represent the key differences between 11/08/99 and 01/18/00 version of the DS2252T data sheet. Please review this summary carefully.1. Data sheet conversion from Interleaf to Word.The following represent the key differences between 01/18/00 and 06/13/06 version of the DS2252T data sheet. Please review this summary carefully.1. Updated reference in Features (Crashproof Operation) to 10-year NV RAM data life to includeroom temperature caveat.2. Added RoHS-compliant packages to Ordering Information table.3. Replaced references to “Secure Microcontroller Data Book” with “Secure MicrocontrollerUser’s Guide.”16 of 16Maxim/Dallas Semiconductor cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim/Dallas Semiconductor product. No circuit patent licenses are implied. Maxim/Dallas Semiconductor reserves the right to change the circuitry and specifications without notice at any time.。

8051_assembler

8051 CROSS ASSEMBLER.USER'S MANUALCopyright (c) 1984, 1985, 1986, 1987, 1988, 1989, 1990 MetaLink Corp.1. 8051 OVERVIEW1.1. IntroductionThe 8051 series of microcontrollers are highly integrated single chip microcomputers with an 8-bit C PU, memory, interrupt controller, timers, serial I/O and digital I/O on a single piece of silicon. The current members of the 8051 family of components include:80C152JA/JB/JC/JD, 83C152JA/JC, 80C15780C154, 83C154, 85C1548044, 8344, 874480C451, 83C451, 87C45180C452, 83C452, 87C4528051, 8031, 8751, 80C51, 80C31, 87C5180512, 8053280515, 80535, 80C535, 80C51580C517, 80C53780C51FA, 83C51FA, 87C51FA, 83C51FB, 87C51FB, 83C51FC, 87C51FC 8052, 8032, 875280C321, 80C521, 87C521, 80C541, 87C5418053, 9761, 875380C552, 83C552, 87C55280C652, 83C652, 87C65283C654, 87C65483C751, 87C75183C752, 87C75280C851, 83C851All members of the 8051 series of microcontrollers share a common architecture. They all have the same instruction set, addressing modes, addressing range and memory spaces. The primary differences between different 8051 based products are the amount of memory on chip, the amount and types of I/O and peripheral functions, and the component's technology (see Table 1-1).In the brief summary of the 8051 architecture that follows, the term 8051 is used to mean collectively all available members of the 8051 family. Please refer to reference (1) for a complete description of the 8051 architecture and the specifications for all the currently available 8051 based products.1.2. 8051 ArchitectureThe 8051 is an 8-bit machine. Its memory is organized in bytes and practically all its instruction deal with byte quantities. It uses an Accumulator as the primary register for instruction results. Other operands can be accessed using one of the four different addressing modes available: register implicit, direct,indirect or immediate. Operands reside in one of the five memory spaces of the 8051.The five memory spaces of the 8051 are: Program Memory, External Data Memory, Internal Data Memory, Special Function Registers and Bit Memory.The Program Memory space contains all the instructions, immediate data and constant tables and strings. It is principally addressed by the 16-bit Program C ounter (PC), but it can also be accessed by a few instructions using the 16-bit Data Pointer (DPTR). The maximum size of the Program Memory space is 64Kbytes. Several 8051 family members integrate on-chip some amount of either masked programmed ROM or EPROM as part of this memory space (refer to Table 1-1).The External Data Memory space contains all the variables, buffers and data structures that can't fit on-chip. It is principally addressed by the 16-bit Data Pointer (DPTR), although the first two general purpose register (R0,R1) of the currently selected register bank can access a 256-byte bank of External Data Memory. The maximum size of the External Data Memory space is 64Kbytes. External data memory can only be accessed using the indirect addressing mode with the DPTR, R0 or R1.The Internal Data Memory space is functionally the most important data memory space. In it resides up to four banks of general purpose registers, the program stack, 128 bits of the 256-bit memory, and all the variables and data structures that are operated on directly by the program. The maximum size of the Internal Data Memory space is 256-bytes. However, different 8051 family members integrate different amounts of this memory space on chip (see Amnt of RAM in Table 1-1). The register implicit, indirect and direct addressing modes can be used in different parts of the Internal Data Memory space.The Special Function Register space contains all the on-chip peripheral I/O registers as well as particular registers that need program access. These registers include the Stack Pointer, the PSW and the Accumulator. The maximum number of SpecialFunction Registers (SFRs) is 128, though the actual number on a particular 8051 family member depends on the number and type of peripheral functions integrated on-chip (see Table 1-1). The SFRs all have addresses greater than 127 and overlap the address space of the upper 128 bytes of the Internal Data Memory space. The two memory spaces are differentiated by addressing mode. The SFRs can only be accessed using the Direct addressing mode while the upper 128 bytes of the Internal Data Memory (if integrated on-chip) can only be accessed using the Indirect addressing mode.The Bit Memory space is used for storing bit variables and flags. There are specific instructions in the 8051 that operate only in the Bit Memory space. The maximum size of the Bit Memory space is 256-bits. 128 of the bits overlap with 16-bytes of the Internal Data Memory space and 128 of the bits overlap with 16 Special Function Registers. Bits can only be accessed using the bit instructions and the Direct addressing mode.The 8051 has a fairly complete set of arithmetic and logical instructions. It includes an 8X8multiply and an 8/8 divide. The 8051 is particularly good at processing bits (sometimes called Boolean Processing). Using the Carry Flag in the PSW as a single bit accumulator, the 8051 can move and do logical operations between the Bit Memory space and the Carry Flag. Bits in the Bit Memory space can also be used as general purpose flags for the test bit and jump instructions.Except for the MOVE instruction, the 8051 instructions can only operate on either the Internal Data Memory space or the Special Function Registers. The MOVE instruction operates in all memory spaces, including the External Memory space and Program Memory space.Program control instructions include the usual unconditional calls and jumps as well as conditional relative jumps based on the C arry Flag, the Accumulator's zero state, and the state of any bit in the Bit Memory space. Also available is a Compare and Jump if Not Equal instruction and a Decrement C ounter and Jump if Not Zero loop instruction. See C hapter 4 for a description of the complete 8051 instruction set.1.3. Summary of the 8051 Family of ComponentsComponent Technology ROM Type of ROM RAM No. of SFRs Serial I/O Type 8031HMOS0-128 b21Start/Stop Async 8051HMOS 4 Kb Masked128 b21Start/Stop Async 8751HMOS 4 Kb EPROM128 b21Start/Stop Async 8053HMOS8 Kb Masked128 b21Start/Stop Async 9761HMOS8 Kb EPROM128 b21Start/Stop Async 8751HMOS8 Kb EPROM128 b21Start/Stop Async 80C31CMOS0-128 b21Start/Stop Async 80C51CMOS 4 Kb Masked128 b21Start/Stop Async 87C51CMOS 4 Kb EPROM128 b21Start/Stop Async 8032HMOS0-256 b26Start/Stop Async 8052HMOS8 Kb Masked256 b26Start/Stop Async 8752HMOS8 Kb EPROM256 b26Start/Stop Async 80C32CMOS0-256 b26Start/Stop Async 80C52CMOS8 Kb Masked256 b26Start/Stop Async 87C52CMOS8 Kb EPROM256 b26Start/Stop Async 8044HMOS 4 Kb Masked192 b34HDLC/SDLC 8344HMOS0-192 b34HDLC/SDLC 8744HMOS 4 Kb EPROM192 b34HDLC/SDLC 80535HMOS0-256 b41Start/Stop Async 80515HMOS8 Kb Masked256 b41Start/Stop Async 80C535CHMOS0-256 b41Start/Stop Async 80C515CHMOS8 Kb Masked256 b41Start/Stop Async 80532HMOS0-128 b28Start/Stop Async 80512HMOS 4 Kb Masked128 b28Start/Stop Async 80C152CHMOS0-256 b56CSMA/CD83C152CHMOS8 Kb Masked256 b56CSMA/CD80C154CMOS0-256 b27Start/Stop Async 83C154CMOS16 Kb Masked256 b27Start/Stop Async 85C154CMOS16 Kb EPROM256 b27Start/Stop Async 80C51FA CHMOS0-256 b47Start/Stop Async 83C51FA CHMOS8 Kb Masked256 b47Start/Stop Async 87C51FA CHMOS8 Kb EPROM256 b47Start/Stop Async 83C51FB CHMOS16 Kb Masked256 b47Start/Stop Async 87C51FB CHMOS16 Kb EPROM256 b47Start/Stop Async 83C51FC CHMOS32 Kb Masked256 b47Start/Stop Async 87C51FC CHMOS32 Kb EPROM256 b47Start/Stop Async 80C537CHMOS0-256 b41Start/Stop Async 80C517CHMOS8 Kb Masked256 b82Start/Stop Async 80C451CMOS0-128 b24Parallel I/F 83C451CMOS 4 Kb Masked128 b24Parallel I/F 87C451CMOS 4 Kb EPROM128 b24Parallel I/F 80C452CHMOS0-256 b55U.P.I.83C452CHMOS8 Kb-256 b55U.P.I.87C452CHMOS8 Kb-256 b55U.P.I.80C552CMOS0-256 b54Start/Stop Async 83C552CMOS8 Kb Masked256 b54Start/Stop Async 87C552CMOS8 Kb EPROM256 b54Start/Stop Async 80C652CMOS0-256 b24Start/Stop Async 83C652CMOS8 Kb Masked256 b24Start/Stop Async 87C652CMOS8 Kb EPROM256 b24Start/Stop Async 83C654CMOS16 Kb Masked256 b24Start/Stop Async 87C654CMOS16 Kb EPROM256 b24Start/Stop Async 83C752CMOS 2 Kb Masked64 b25I2C87C752CMOS 2 Kb EPROM64 b25I2C83C751CMOS 2 Kb Masked64 b20I2C87C751CMOS 2 Kb EPROM64 b20I2C80C521CMOS0-256 b26Start/Stop Async 80C321CMOS8 Kb Masked256 b26Start/Stop Async 87C521CMOS8 Kb EPROM256 b26Start/Stop Async 80C541CMOS16 Kb Masked256 b26Start/Stop Async 87C541CMOS16 kb EPROM256 b26Start/Stop Async 80C851CMOS0-128 b21Start/Stop Async 83C851CMOS 4 Kb Masked128 b21Start/Stop Async Table 1-1: 8051 Family of Components1.4. References1) Intel Corp., 8-Bit Embedded Controllers, 1990.2) Siemens Corp., Microcontroller Component 80515, 1985.3) AMD Corp., Eight-Bit 80C51 Embedded Processors, 1990.4) Signetics Corp., Microcontroller Users' Guide, 1989.2. 8051 CROSS ASSEMBLER OVERVIEW2.1. IntroductionThe 8051C ross Assembler takes anassembly language source file created with a text editor and translates it into a machine language object file. This translation process is done in two passes over the source file. During the first pass, the C ross Assembler builds a symbol table from the symbols and labels used in the source file. It's during the second pass that the C ross Assembler actually translates the source file into the machine language object file. It is also during the second pass that the listing is generated.The following is a discussion of the syntax required by the C ross Assembler to generate error free assemblies.2.2. SymbolsSymbols are alphanumeric representations of numeric constants, addresses, macros, etc. The legal character set for symbols is the set of letters, both upper and lower case (A..Z,a..z), the set of decimal numbers (0..9) and the special characters, question mark (?) and underscore (_). To ensure that the CrossAssembler can distinguish between a symbol and a number, all symbols must start with either a letter or special character (? or _). The following are examples of legal symbols:PISerial_Port_BufferLOC_4096?_?_?In using a symbol, the C ross Assembler converts all letters to upper case. As a result, the Cross Assembler makes no distinction between upper and lower case letters. For example, the following two symbols would be seen as the same symbol by the Cross Assembler:Serial_Port_BufferSERIAL_PORT_BUFFERSymbols can be defined only once. Symbols can be up to 255 characters in length, though only the first 32 are significant. Therefore, for symbols to be unique, they must have a unique character pattern within the first 32 characters. In the following example, the first two symbols would be seen by the Cross Assembler as duplicate symbols, while the third and fourth symbols are unique.BEGINNING_ADDRESS_OF_CONSTANT_TABLE_1BEGINNING_ADDRESS_OF_CONSTANT_TABLE_2CONSTANT_TABLE_1_BEGINNING_ADDRESSCONSTANT_TABLE_2_BEGINNING_ADDRESSThere are certain symbols that are reserved and can't be defined by the user. These reserved symbols are listed in Appendix C and include the assembler directives, the 8051 instruction mnemonics, implicit operand symbols, and the following assembly time operators that have alphanumeric symbols: EQ, NE, GT, GE, LT, LE, HIGH, LOW, MOD, SHR, SHL, NOT, AND, OR and XOR.The reserved implicit operands include the symbols A, AB, C, DPTR, PC, R0, R1, R2, R3, R4, R5, R6, R7, AR0, AR1, AR2, AR3, AR4, AR5, AR6 and AR7. These symbols are used primarily as instruction operands. Except for AB, C, DPTR or PC, these symbols can also be used to define other symbols (see EQU directive inChapter 5).The following are examples of illegal symbols with an explanation of why they are illegal: 1ST_VARIABLE (Symbols can not start with a number.)ALPHA# (Illegal character "#" in symbol.)MOV (8051 instruction mnemonic)LOW (Assembly operator)DATA (Assembly directive)2.3. LabelsLabels are special cases of symbols. Labels are used only before statements that have physical addresses associated with them. Examples of such statements are assembly language instructions, data storage directives (DB and DW), and data reservation directives (DS and DBIT). Labels must follow all the rules of symbol creation with the additional requirement that they be followed by a colon. The following are legal examples of label uses:TABLE_OF_CONTROL_CONSTANTS:DB 0,1,2,3,4,5 (Data storage)MESSAGE: DB 'HELP' (Data storage)START: MOV A,#23 (Assembly language instruction)2.4. Assembler ControlsAssembler controls are used to control where the Cross Assembler gets its input source file, where it puts the object file, and how it formats the listing file.Table 2-1 summarizes the assembler controls available. Refer to C hapter 6 for a detailed explanation of the controls.$DATE(date) Places date in page header $EJECT Places a form feed in listing $INCLUDE(file) Inserts file in source program $LIST Allows listing to be output $NOLIST Stops outputting the listing $MOD51 Uses 8051 predefined symbols $MOD52 Uses 8052 predefined symbols $MOD44 Uses 8044 predefined symbols $NOMOD No predefined symbols used $OBJECT(file) Places object output in file $NOOBJECT No object file is generated $PAGING Break output listing into pages $NOPAGING Print listing w/o page breaks $PAGELENGTH(n) No. of lines on a listing page $PAGEWIDTH(n) No. of columns on a listing page $PRINT(file) Places listing output in file $NOPRINT Listing will not be output $SYMBOLS Append symbol table to listing $NOSYMBOLS Symbol table will not be output $TITLE(string) Places string in page header Table 2-1: Summary of Cross Assembler ControlsAs can be seen in Table 2-1, all assembler controls are prefaced with a dollar sign ($). No spaces or tabs are allowed between the dollar sign and the body of the control. Also, only one control per line is permitted. However, comments can be on the same line as a control. The following are examples of assembler controls:$TITLE(8051 Program Ver. 1.0)$LIST$PAGEWIDTH(132)2.5. Assembler DirectivesAssembler directives are used to define symbols, reserve memory space, store values in program memory and switch between different memory spaces. There are also directives that set the location counter for the active segment and identify the end of the source file. Table 2-2 summarizes the assembler directivesavailable. These directives are fully explained in Chapter 5.EQU Define symbolDATA Define internal memory symbolIDATA Define indirectly addressed internal XDATA Define external memory symbolBIT Define internal bit memory symbol CODE Define program memory symbolDS Reserve bytes of data memoryDBIT Reserve bits of bit memoryDB Store byte values in program memory DW Store word values in program memory ORG Set segment location counterEND End of assembly language source file CSEG Select program memory spaceDSEG Select internal memory data space XSEG Select external memory data spaceISEG Select indirectly addressed internal BSEG Select bit addressable memory space USING Select register bankIF Begin conditional assembly blockELSE Alternative conditional assembly block ENDIF End conditional assembly blockTable 2-2: Summary of Cross Assembler DirectivesOnly one directive per line is allowed, however comments may be included. The following are examples of assembler directives:TEN EQU 10 RESET CODE 0 ORG 40962.6. 8051 Instruction MnemonicsThe standard 8051 Assembly Language Instruction mnemonics plus the generic C ALL and JMP instructions are recognized by the C ross Assembler and are summarized in Table 2-3. See hapter 4 for the operation of the individual instructions.ACALL Absolute callADD AddADDC Add with carryAJMP Absolute jumpANL Logical andCJNE Compare & jump if not equal CLR ClearCPL ComplementDA Decimal adjustDEC DecrementDIV DivideDJNZ Decrement&jump if not zero INC IncrementJB Jump if bit setJBC Jump & clear bit if bit set JC Jump if carry setJMP JumpJNB Jump if bit not setJNC Jump if carry not setJNZ Jump if accum. not zeroJZ Jump if accumulator zero LCALL Long callLJMP Long jump MOV MoveMOVC Move codeMOVX Move externalMUL MultiplyNOP No operationORL Inclusive orPOP Pop stackPUSH Push stackRET ReturnRETI Return from interrupt RL Rotate leftRLC Rotate left thru carry RR Rotate rightRRC Rotate right thru carry SETB Set bitSJMP Short jumpSUBB Subtract with borrow SWAP Swap nibblesXCH Exchange bytesXCHD Exchange digitsXRL Exclusive orCALL Generic callTable 2-3: 8051 Instructions and MnemonicsWhen the C ross Assembler sees a generic C ALL or JMP instruction, it will try to translate the instruction into its most byte efficient form. The Cross Assembler will translate a C ALL into one of two instructions (AC ALL or LC ALL) and it will translate a generic JMP into one of three instructions (SJMP, AJMP or LJMP). The choice of instructions is based on which one is most byte efficient. The generic CALL or JMP instructions saves the programmer the trouble of determining which form is best.However, generic C ALLs and JMPs do have their limitations. While the byte efficiency algorithm works well for previously defined locations, when the target location of the C ALL or JMP is a forward location (a location later on in the program), the assembler has no way of determining the best form of the instruction. In this case the C ross Assembler simply puts in the long version (LC ALL or LJMP) of the instruction, which may not be the most byte efficient. NOTE that the generic C ALLs and JMPs must not be used for the 751/752 device as LC ALL and LJMP are not legal instructions for those devices. Instead use ACALL and AJMP explicitly.For instructions that have operands, the operands must be separated from the mnemonic by at least one space or tab. For instructions that have multiple operands, each operand must be separated from the others by a comma.Two addressing modes require the operands to be preceded by special symbols to designate the addressing mode. The AT sign (@) is used to designate the indirect addressing mode. It is used primarily with Register 0 and Register 1 (R0, R1), but is can also be used with the DPTR in the MOVX and the Accumulator in MOVC and JMP @A+DPTR instructions. The POUND sign (#) is used to designate an immediate operand. It can be used to preface either a number or a symbol representing a number.A third symbol used with the operands actually specifies an operation. The SLASH (/) is used to specify that the contents of a particular bit address is to be complemented before the instruction operation. This is used with the ANL and ORL bit instructions.Only one assembly language instruction is allowed per line. Comments are allowed on the same line as an instruction, but only after all operands have been specified. The following are examples of instruction statements:START: LJMP INITMOV @R0,Serial_Port_BufferCJNE R0 , #TEN, INC_TENANL C,/START_FLAGCALL GET_BYTERET2.7. Bit AddressingThe period (.) has special meaning to the Cross Assembler when used in a symbol. It is used to explicitly specify a bit in a bit-addressable symbol. For example, it you wanted to specify the most significant bit in the Accumulator, you could write AC C.7, where AC C was previously defined as the Accumulator address. The same bit can also be selected using the physical address of the byte it's in.For example, the Accumulator's physical address is 224. The most significant bit of the Accumulator can be selected by specifying 224.7. If the symbol ONwas defined to be equal to the value 7, you could also specify the same bit by either ACC.ON or 224.ON.2.8. ASCII LiteralsPrintable characters from the ASCII characterset can be used directly as an immediate operand, or they can used to define symbols or store ASCII bytes in Program Memory. Such use of the ASCII character set is called ASCII literals. ASCII literals are identifiedby the apostrophe (') delimiter. The apostrophe itself can be used as an ASCII literal. In this case, use two apostrophes in a row. Below are examples of using ASCII literals.MOV A,#'m' ;Load A with 06DH (ASCII m)QUOTE EQU '''' ;QUOTE defined as 27H (ASCII single quote)DB '8051' ;Store in Program Memory2.9. CommentsComments are user defined character stringsthat are not processed by the C ross Assembler. A comment begins with a semicolon ( ; ) and ends at the carriage return/line feed pair that terminates theline. A comment can appear anywhere in a line, but it has to be the last field. The following are examples of comment lines:; Begin initialization routine here$TITLE(8051 Program Vers. 1.0) ;Place version number here TEN EQU 10 ;Constant2.10. The Location CounterThe C ross Assembler keeps a locationcounter for each of the five segments (code, internal data, external data, indirect internal data and bit data). Each location counter is initialized to zero and can be modified using Assembler Directives described in Chapter 5.The dollar sign ($) can be used to specify thecurrent value of the location counter of the active segment. The following are examples of how this can be used:JNB FLAG,$ ;Jump on self until flag is reset CPYRGHT: DB 'Copyright, 1983'CPYRGHT_LENGTH EQU $-CPYRGHT-1 ;Calculate length of copyright message2.11. Syntax SummarySince the Cross Assembler essentiallytranslates the source file on a line by line basis,certain rules must be followed to ensure the translation process is done correctly. First of all,since the C ross Assembler's line buffer is 256characters deep, there must always be a carriage return/line feed pair within the first 256 columns of the line.A legal source file line must begin with either acontrol, a symbol, a label, an instruction mnemonic, a directive, a comment or it can be null (just thecarriage return/line feed pair). Any other beginning to a line will be flagged as an error.While a legal source file line must begin withone of the above items, the item doesn't have to begin in the first column of the line. It only must be the first field of the line. Any number (including zero)of spaces or tabs, up to the maximum line size, may precede it.C omments can be placed anywhere, but theymust be the last field in any line.2.12. Numbers and OperatorsThe Cross Assembler accepts numbers in anyone of four radices: binary, octal, decimal and hexadecimal. To specify a number in a specific radix,the number must use the correct digits for the particular radix and immediately following the number with its radix designator. Decimal is the default radixand the use of its designator is optional. An hexadecimal number that would begin with a letter digit must be preceded by a 0 (zero) to distinguish it from a symbol. The internal representation of numbers is 16-bits, which limits the maximum number possible. Table 2-4 summarizes the radices available.Radix DesignatorLegal DigitsMax. Legal Number Binary B 0,11111111111111111BOctal O, Q0,1,2,3,4,5177777Q Decimal D, (default)0,1,2,3,4,5,6,7,8,965535D Hexadecimal H 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F 0FFFFHTable 2-4: Cross Assembler RadicesNo spaces or tabs are allowed between thenumber and the radix designator. The letter digits and radix designators can be in upper or lower case.The following examples list the decimal number 2957in each of the available radices:101110001101B (Binary)5615o or 5615Q (Octal)2957 or 2957D (Decimal)0B8DH, 0b8dh (Hexadecimal)When using radices with explicit bit symbols,the radix designator follows the byte portion of the address as shown in the following examples:0E0H.7 Bit seven of hexadecimal address 0E0200Q.ON Bit ON of octal address 200The C ross Assembler also allows assemblytime evaluation of arithmetic expressions up to thirty-two levels of embedded parentheses. All calculationsuse integer numbers and are done in sixteen bit precision.+ Addition Unary positive- Subtraction Unary negation (2's complement)* Multiplication/ Integer division (no remainder)MOD Modulus (remainder of integer division)SHR Shift right SHL Shift leftNOT Logical negation (1's complement)AND Logical and OR Inclusive or XOR Exclusive orLOW Low order 8-bits HIGH High order 8-bits EQ, = Relational equalNE, <> Relational not equal GT, > Relational greater thanGE, >= Relational greater than or equal LT, < Relational less thanLE, <= Relational less than or equal ( ) Parenthetical statementTable 2-5: Assembly Time OperationsThe relational operators test the specifiedvalues and return either a True or False. False is represented by a zero value, True is represented by a non zero value (the True condition actually returns a 16-bit value with every bit set; i.e., 0FFFFH). The relational operators are used primarily with theC onditional Assembly capability of the Cross Assembler.Table 2-5 lists the operations available whileTable 2-6 lists the operations precedence in descending order. Operations with higher precedence are done first. Operations with equal precedence are evaluated from left to right.(,)HIGH,LOW*,/,MOD,SHR,SHL +,-EQ,LT,GT,LE,GE,NE,=,<,>,<=,>=,<>NOT AND OR,XORTable 2-6: Operators Precedence2.13. Source File ListingThe source file listing displays the results of the C ross Assembler translation. Every line of the listing includes a copy of the original source line as well as a line number and the C ross Assembler translation. For example, in translating the following line taken from the middle of a source file:TRANS: MOV R7,#32 ;Set up pointer 002F 7920 152 TRANS: MOV R1,#32 ;Set up pointerThe '002F' is the current value of the location counter in hexadecimal. The '7920' is the translated instruction, also in hexadecimal. The '152' is the decimal line number of the current assembly. After the line number is a copy of the source file line that was translated.Another example of a line in the listing file is as follows:015B 13 =1 267 +2 RRC AHere we see two additional fields. The '=1' before the line number gives the current nesting of include files. The '+2' after the line number gives the current macro nesting. This line essentially says that this line comes from a second level nesting of a macro that is part of an include file.Another line format that is used in the listing is that of symbol definition. In this case the location counter value and translated instruction fields described above are replaced with the definition of the symbol. The following are examples of this:00FF 67 MAX_NUM EQU 255 REG 68 COUNTER EQU R7The '00FF' is the hexadecimal value of the symbol MAX_NUM. Again, '67'is the decimal line number of the source file and the remainder of the first line is a copy of the source file. In the second line above, the 'REG' shows that the symbol C OUNTER was defined to be a general purpose register.Optionally, a listing can have a page header that includes the name of the file being assembled, title of program, date and page number. The header and its fields are controlled by specific Assembler Controls (see Chapter 6).The default case is for a listing to be output as a file on the default drive with the same name as the entered source file and an extension of .LST. For example, if the source file name was PROGRAM.ASM, the listing file would be called PROGRAM.LST. Or if the source file was called MODULE1, the listing file would be stored as MODULE1.LST. The default can be changed using the $NOPRINT and $PRINT() Assembler C ontrols (see Chapter 6).2.14. Object FileThe 8051 C ross Assembler also creates a machine language object file. The format of the object file is standard Intel Hexadecimal. This Hexadecimal file can be used to either program EPROM’s using standard PROM Programmers for prototyping, or used to pattern masked ROMs for production.The default case is for the object file to be output on the default drive with the same name as the first source file and an extension of .HEX. For example, if the source file name was PROGRAM.ASM, the object file would be called PROGRAM.HEX. Or if the source file was called MODULE1, the object file would be stored as MODULE1.HEX. The default can be changed using the $NOOBJECT and $OBJECT() Assembler Controls (see Chapter 6).。

8051 Microcontroller Instruction Set