CMP体系结构上非包含高速缓存的设计及性能分析

CMP体系结构上非包含高速缓存的设计及性能分析

1.1 实 验 模 型 本文采用的实验模型如图 3 所示 (图 (a)(b)(c) 为片外集成

L3 cache 的情况,图(d)(f)(g)为片上集成 L3 cache 的情况,图(e) 为仅有两级 cache 的情况。另外,L3_normal_offchip/onchip 表 示三级 cache 均为 inclusive cache;L2_NI、L3_NI 分别表示 L2 cache、L3 cache 为 non-inclusive cache; L2_NI_only 表示仅有两级 cache,且 L2 cache 为 non-inclusive; L3_NI_share、L3_NI_private 分别表示 L2 cache 为共享和私有且 L3 cache 为 non-inclusive)。 由于大量实验数据表明 L1 cache 可满足指令及数据的绝大多 数请求 ([4] 注 2:对 Splash2 测试程序集,在 16k 4 路组相联的配 置下,L1 cache 的平均缺失率为 5%;对 SPEC2000 程序测试集,

Memory Channel

图 1 4 路 Dancehall CMP 共享 L2 cache 结构

CPU L1

L2 non-inclusive

MEM

图 2 Non-inclusive L2 cache

换(图 2①); (2) 由于设置了 L1 cache 与下级主存间的独立数据通路,

当 L1 cache 缺失并在 non-inclusive L2 cache 中继续缺失后,处 理器会继续访问主存(图 2②),并将找到的数据直接从主存读 入 L1 cache(图 2③)不必经过 non-inclusive L2 cache。同时将 L1 cache 被换出的 cache 行写入 non-inclusive L2 cache 中(图 2①), L2 cache 被换出的 cache 行被写回主存(图 2②)。

超级计算机的体系结构和性能分析

超级计算机的体系结构和性能分析超级计算机是目前世界上最为强大的计算机之一,能够处理巨大的数据和运算任务,是现代科学和技术发展的重要基础设施。

但是想要深入了解超级计算机的性能和体系结构,需要具备一些相关的专业知识和技能。

本文将从计算机结构、处理器、内存等方面进行分析,帮助读者更好地了解超级计算机的体系结构和性能。

一、计算机结构超级计算机的结构与普通计算机基本一致,主要包括CPU、内存、输入输出设备等部件,但是其规模和性能要远远超过普通计算机。

超级计算机通常采用并行计算的方式,即将大的任务分解成若干个小任务,由多个处理器并行处理,最终将结果整合起来。

这种方法可以大大提高计算效率,缩短计算时间。

二、处理器超级计算机的处理器通常采用多核心和超线程技术。

多核心技术指处理器内部集成了多个独立的CPU核心,可以同时处理多个任务。

超线程技术是在单一核心内部模拟多个逻辑核心,可以实现单一核心同时处理多个线程。

这些技术的使用可以有效提高计算机的运算速度和效率。

三、内存超级计算机的内存通常采用高性能存储技术,如延迟高带宽内存(HBM)、高速缓存(Cache)等。

这些技术可以实现内存数据的快速读取和存储,为计算机的高速运算提供了保障。

此外,超级计算机的内存容量通常需要大于普通计算机,以应对大规模的数据处理需求。

四、高速网络超级计算机的高速网络是其性能优异的重要保障。

高速网络可以实现处理器之间和计算节点之间的高速数据传输,提高数据处理效率和运算速度。

此外,高速网络还可以支持异构计算,即不同种类的处理器在同一系统中协同工作,共同完成计算任务。

总之,超级计算机是目前科学技术发展中不可或缺的重要设备。

了解其体系结构和性能分析对于深入理解超级计算机的运行原理和应用场景非常重要。

通过对计算机结构、处理器、内存等方面的分析,我们可以更好地了解超级计算机的优势和限制,从而更好地利用其为科学技术发展做出贡献。

cmp膜 交联结构沉淀-概述说明以及解释

cmp膜交联结构沉淀-概述说明以及解释1.引言1.1 概述概述部分的内容可以从CMP膜的定义和作用入手,以简洁明了的语言概括介绍CMP膜及其交联结构在材料科学领域中的重要性和广泛应用。

以下是可能的一种写法:概述CMP膜(Chemical Mechanical Polishing Membrane),是一种具有交联结构的薄膜材料,其在材料科学领域中起着重要作用。

CMP膜的交联结构是指在材料制备过程中通过化学和机械的双重作用形成的一种材料结构。

相比于传统薄膜材料,CMP膜的交联结构给予了它独特的物理和化学性质,使其在各种应用领域具有显著的优势。

CMP膜在半导体、光电子、材料加工和微电子设备等领域具有广泛的应用。

它被广泛用于制备半导体器件、光电子元件和微观结构的加工过程中,并在提高器件性能和可靠性方面发挥着重要作用。

CMP膜的交联结构能够增强膜的机械强度和热稳定性,提高其耐磨性和抗化学腐蚀性能。

此外,由于其优异的电学性质和独特的表面特性,CMP 膜还可用于制备高性能的光电子材料和微电子器件。

本文旨在探讨CMP膜交联结构的优势及其在各个领域的可能应用。

在接下来的章节中,我们将详细介绍CMP膜的基本原理以及交联结构在材料科学中的重要性。

通过深入了解CMP膜的交联结构,我们将更好地理解其在各种应用领域中的潜力和发展前景。

1.2文章结构文章结构是指整篇文章的组织框架和内容安排。

一个良好的文章结构能够使读者更好地理解文章的主题和内容,并能够有条理地阐述作者的观点和论证。

在这篇文章中,我们将会按照以下方式组织和安排内容:1. 引言:在引言部分,我们将会概述本文的主题和目的,以及CMP 膜和交联结构的基本概念和重要性。

同时,我们还会简要介绍文章的结构和内容安排。

2. 正文:正文部分将会详细介绍CMP膜的基本原理和交联结构的重要性。

在2.1节,我们将会深入探讨CMP膜的基本原理,包括其组成成分和制备方法。

同时,我们还会介绍CMP膜在半导体制造和光学领域的应用情况。

CMP

2.1 CeO2抛光浆料稀土氧化物CeO2具有很好的抛光性能,其特点是抛光速率高,对材料的去除率高,被抛光表面粗糙度和表面微观波纹度较小,颗粒硬度低,对被抛光表面损伤较弱;其缺点是勃度大,易划伤且高低选择性不好,沉淀在介质膜_L吸附严重,为后续清洗带来困难. CeO2抛光浆料广泛应用于玻璃精密抛光、超大规模集成电路Sio2介质层抛光和单晶硅片抛光等,而现在国内外有很多研究也致力于CeO2抛光浆料对半导体衬底材料(如GaAs晶片)的抛光。

首先纳米CeO2粒子通过化学吸附与抛光表面上的Sio2之间形成Ce-O-Si键,CeO2粒子将表面部分Sio2撕裂下来,进入溶液中;经过扩散,Sio2粒子又从CeO2粒子的表面脱落。

Ce-O-Si键的形成与S-O-Si键的断裂影响着抛光速率.化学吸附作用和机械撕裂作用同时影响着Si-O-Si键的断裂。

CeO2抛光浆料区别于传统抛光活性强的抛光浆料都是强酸,它在碱性抛光环境下是两性的,能同时吸附阳离子和阴离子,故有更好的抛光性能。

乡屯度、硬度、粒度、粒度分布、悬浮性、表面电性、表面活性和密度等都是影响其抛光性能的主要因素.粒度大的适合高速抛光,粒度小的适用于低速抛光圈.具有高抛光性能的纳米CeO2目前的合成方法主要有:液相反应法、固相反应法、机械化学法。

液相反应法包括:溶胶一凝胶法、液相沉淀法、电化学法、水热法、微乳液法、喷雾热分解法等。

张鹏珍等采用溶胶一凝胶法制备了平均晶粒度在13.3 nm且粒度分布均匀的纳米CeO2粉体,经此CeO2抛光浆料抛光后的玻璃幕片表面粗糙度(Ra)可降到0.6nm左右,显示了良好的抛光性能。

Ming等(2a)也采用此法在常压下制备纳米CeO2,原料为硝酸饰钱、尿素和去离子水,通过加热得到的Ce O2粒径为8 nm,具有立方体结构。

电化学法制得的CeO2优点是粒子粒度很小,分散性也较好,工艺也相对简单,但是产率较低。

水热法的优点是不需要进行高温灼烧处理,避免了硬团聚。

多核处理器中多级缓存替换策略的设计

摘要高速缓存是高性能处理器中提高访存速度的重要技术,其对处理器性能的影响至关重要。

本论文主要针对基于包容式高速缓存结构的多核处理器中,多核共享的最下级缓存不清楚其上层缓存的使用情况而导致下级缓存将上级的常用数据无效掉的问题,提出一种感应上级的最近最少使用(LRU, Least Recently Used)替换策略,将上级高速缓存(Cache)的局部性信息发送给下级Cache,下级Cache在数据替换的时候,结合上级Cache和本级Cache综合的局部性信息进行替换,避免上述错误的无效掉上级Cache常用数据的情况。

从而提高处理器执行效率和整体性能。

在上述理论基础上,以GEM5处理器模拟器为设计与测试平台,修改缓存模型中最外层高速缓存(LLC, Last Level Cache)的替换策略的代码。

具体方法主要为,在共享的LLC上加入upperAccess 标志位,以upperAccess标志位的状态为上级Cache数据使用情况的判断依据,在LLC需要做出替换决定时优化LLC高速缓存行(Cacheline)的替换顺序,尽量避免上层缓存的常用数据被替换掉,从而完成感应上级的LRU替换策略的加入,并以此减少二级缓存(L2 Cache)和更上级Cache出现包含式受害者(Inlusuve Victim)现象的次数。

在加入感应上级的LRU替换策略的模拟器模型中运行SPEC CPU2006测试集进行验证。

以L2和L3 Cache的每千条指令的未命中数据(MPKI, Miss per Kilo Instruction)和每周期指令数(IPC, Instruc-tions per cycle)数据为切入点,对比优化前后的缓存替换策略对系统整体性能的影响。

对比多个测试项目的结果,优化后单核测试下的IPC平均提升1.35%,L2 Cache 的MPKI平均降低1.5%。

优化后多核测试的IPC数据平均提升3.83%,L3 cache的MPKI平均降低5.0%。

cmp的技术要求-概述说明以及解释

cmp的技术要求-概述说明以及解释1.引言1.1 概述CMP (Content Management Platform) 是一种基于互联网技术的内容管理平台,旨在帮助企业、组织和个人更加高效地管理和发布内容。

它通过提供一套完备的技术要求,使得用户可以轻松创建、编辑、组织和发布各种类型的内容,如文档、图片、视频、音频等。

随着互联网的快速发展和信息爆炸式增长,如何高效地管理和发布内容成为了一个亟待解决的问题。

CMP通过将传统的内容管理方式与先进的技术手段相结合,为用户提供了一种全新的解决方案。

它包括了一系列的技术要求,涵盖了内容创建、编辑、版本控制、权限管理、发布等方面,可以帮助用户在多渠道、多平台上统一管理和发布内容。

CMP的技术要求可以分为以下几个方面:1. 内容创建和编辑:CMP需要提供一个用户友好的界面,使得用户可以方便地创建和编辑各种类型的内容。

这些内容可以包括文字、图片、视频、音频等,用户可以通过富文本编辑器或其他工具进行编辑和格式化。

2. 版本控制:CMP需要支持对内容的版本控制,使得用户可以随时查看和恢复之前的版本。

这对于团队协作和内容审查非常重要,可以避免人为错误或不必要的修改带来的影响。

3. 权限管理:CMP需要提供一个严密的权限管理系统,以确保只有授权人员能够进行内容的创建、编辑和发布。

这可以有效地防止非法操作和信息泄露,并确保内容的安全性和可靠性。

4. 多渠道发布:CMP需要支持多渠道的内容发布,包括网站、移动应用、社交媒体等。

用户可以通过统一的平台,将内容发布到不同的渠道,以提高内容的传播效果和覆盖范围。

5. 数据分析和统计:CMP需要提供强大的数据分析和统计功能,以帮助用户了解内容的表现和效果。

通过对各种指标和数据的分析,用户可以根据实际情况进行调整和优化,提升内容的质量和效益。

综上所述,CMP的技术要求涵盖了内容创建、编辑、版本控制、权限管理、多渠道发布、数据分析和统计等方面。

CMP操作系统技术

运“芯”帷幄—CMP的操作系统技术单芯片多处理器(CMP),特别是在一个芯片上集成了多个相同通用处理器的单芯片对称多处理器(同构CMP)的发展,是上世纪90年代以来集成电路制造工艺的进步与微处理器体系结构的发展所带来的必然发展方向。

和目前在服务器领域广泛采用的对称多处理器(Symmetric Multi-Processor, SMP)结构类似,在CMP系统中,位于同一个芯片内部所有处理器内核以平等的身份参与任务调度和中断处理,共享内存和外部设备,而且也可以共享片内的(部分或全部)高速缓存。

CMP的结构相对简单,可以直接使用现有的处理器内核,因此开发周期与成本相对较低,结构简单带来的另一个好处是更易获得高的主频。

由于多个处理器集成在一块芯片上,且共享cache,微处理器之间的通信延迟会明显降低,有利于提高系统的整体性能。

因此,CMP 具有良好的发展前景和广泛的应用空间,众多著名大学、科研机构和商业公司都展开了广泛而积极的研究。

而要想真正发挥CMP的优势,软件,特别是操作系统和编译工具等系统软件的支持至关重要,没有这些软件,CMP将处于“空转”状态。

因此,每一个CMP系统都需要为其量身打造的系统软件。

CMP对操作系统提出的挑战系统软件对于CMP广泛、深入的应用有重要的意义,这里我们讨论操作系统。

操作系统是计算机系统的基本系统软件,在整个计算机系统中处于核心地位,负责控制、管理计算机的所有软件、硬件资源,是惟一直接和硬件系统打交道的软件,是整个软件系统的基础部分,同时还为计算机用户提供良好的界面。

对于普通用户而言,操作系统是一个资源管理者,通过它提供的系统命令和界面操作等工具,以某种易于理解的方式完成系统管理功能,有效地控制各种硬件资源,组织自己的数据,完成自己的工作并和其他人共享资源。

对于程序员来讲,操作系统提供了一个与计算机硬件等价的扩展或虚拟的计算平台。

操作系统提供给程序员的工具除了系统命令、界面操作之外,还有系统调用,系统调用抽象了许多硬件细节,程序可以以某种统一的方式进行数据处理,程序员可以避开许多具体的硬件细节,提高程序开发效率,改善程序移植特性。

多核处理器体系结构分析

多核技术的优势

多核处理器体系结构分析

多核的并行运行

多核处理器体系结构分析

在每个核中,线程是并发的

多核处理器体系结构分析

多核与多处理器的比较

多处理器:两个或两个以上的CPU及主板上 的多个CPU插槽

多核处理器:一颗CPU搭载两个核芯,即1 die 2 cores ,即在一个单晶硅上集成了多个 核芯

多核处理器体系结构分析

多核与多处理器的比两个较处理器

• 两个分开的芯片通过外在系统总 线连接

• 需要外在软件支持 • 更多的热量消耗

双核

■ 两个核在一个芯片内直接连接 ■ 多线程和多进程自动并行处理 ■ 热量消耗增加的很少 ■ 封装成本降低

多核处理器体系结构分析

多核与超线程的比较

超线程:Hyper-Threading Technology HT是Intel对SMT的实现,在最近的P4和Xeon处

多核处理器体系结构分析

AMD双核

多核处理器体系结构分析

AMD四核酷龙

Large shared L3 cache shares data between cores efficiently while helping reduce latency to main memory

Dedicated L1 and L2 cache per core helps performance of virtualized environments and large databases by reducing cache pollution associated with a shared L2 cache

但近年来,通过这些技术并未获得更好的性能 能量和存储延时问题,已经成为提高单线程性能的障

多核cache亲和性

多核cache亲和性综述概述利用亲和性这种特性可以降低进程转移带来的性能损失,提高cache命中率,同时利用该特性可以充分利用片上所有的cache来加速串行程序的执行。

但要利用该特性需要操作系统调度程序的支持,同时要求有一定的硬件的支持。

经过研究,cache亲和性对单核多处理器的性能提升不大,但对于多核多处理器能带来很大的性能提升。

该文主要介绍了亲和性的定义,亲和性对性能的影响,最后怎样利用操作系统及硬件支持来充分利用该特性。

引言芯片多处理器(CMP)的已成为当今高性能的多处理器主要形式之一。

对影响性能的关键因素之一便是高速缓存的利用率。

传统的对于高速缓存,每个核心是有自己的私有L1高速缓存,并在同一芯片上所有核心共享的较大二级缓存。

为了提高缓存利用率,我们需要考虑在缓存中的数据重用,在所有核心上共享缓存缓存访问的争夺,和私有缓存间的连贯性缺失率。

亲和性定义:亲和性指进程在给定的cpu或cpu核上运行尽量长的时间而不被转移到别的处理器的倾向性。

在Linux里,内核进程调度器天生就具有软亲和性(soft affinity)的特性,这意味着进程通常不会在处理器或者内核之间频繁迁移。

这种情况是我们希望的,因为进程迁移的频率低意味着产生的负载小,具有更好的性能表现。

在对称多处理(SMP)上,操作系统的进程调度程序必须决定每个CPU上要运行哪些进程。

这带来两项挑战:调度程序必须充分利用所有处理器,避免当一个进程已就绪等待运行,却有一个CPU核心闲置一旁,这显然会降低效率。

然而一个进程一旦被安排在某个CPU核心上运行,进程调度程序也会将它安排在相同的CPU核心上运行。

这会使性能更好,因为将一个进程从一个处理器迁移到另一个处理器是要付出性能代价的。

一般进程会在相同的核或CPU上运行,只会在负载极不均衡的情况下从一个核移往另一个核。

这样可以最小化缓存区迁移效应,同时保证系统中处理器负载均衡。

亲和性程序性能的影响多核处理器的处理器与处理器之间的cache亲和力是通过观察缓存方面积累了一定的进程的状态,即数据或指令后才进行考察的。

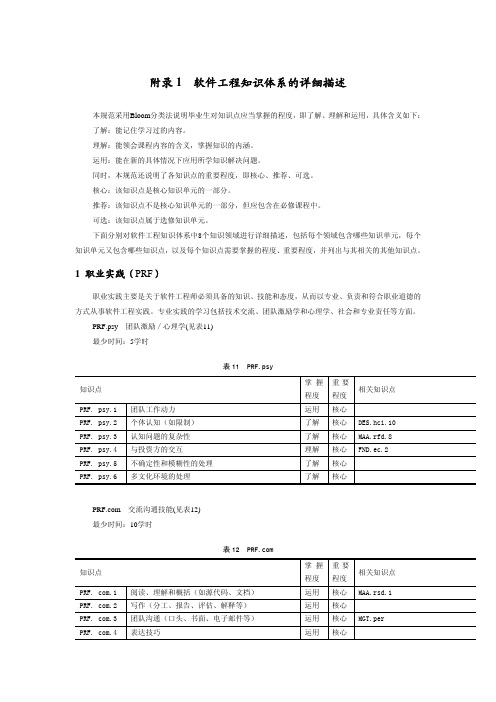

18142621-%b8%bd%c2%bc1%a1%a1%c8%ed%bc%fe%b9%a4%b3%cc%d6%aa%ca%b6%cc%e5%cf%b5%b5%c4%cf%ea%cf%b8%c3%e8

职业实践主要是关于软件工程师必须具备的知识、技能和态度,从而以专业、负责和符合职业道德的 方式从事软件工程实践。专业实践的学习包括技术交流、团队激励学和心理学、社会和专业责任等方面。

PRF.psy 团队激励/心理学(见表11) 最少时间:5学时

表 11 PRF.psy

知识点

PRF. psy.1 PRF. psy.2 PRF. psy.3 PRF. psy.4 PRF. psy.5 PRF. psy.6

MAA. tm.8 MAA. tm.9

表 15 MAA.tm

掌握

程度

信息建模(例如实体—关系模型、类图等)

运用

行为建模(例如结构化分析、状态图、用例分析、交互 运用

图、失效模式和影响分析、故障树分析等)

结构建模(例如体系结构等)

理解

领域建模(例如领域工程方法等)

了解

功能建模(例如构件图等)

理解

企业建模(例如业务流程、组织结构、目标等)

质量(非功能性)需求分析(如安全性、保密性、 运用

易用性、性能、根本原因分析等)

优先级确定、折衷分析、风险分析和效果分析 可追踪性 形式化分析

理解 理解 了解

重要 程度 核心 核心 核心

核心 核心 核心

相关知识点

FND.ef.4 , QUA.pda , DES.con.6 , VAV.fnd.4,VAV.tst.9,VAV.hct, EVO.ac.4 FND.ec.3,FND.ec.4,QUA.pda.4 DES.ar.4,EVO.pro.2 CMP.fm

掌 握 重要 相关知识点

程度 程度

理解 了解 了解

核心 核心 核心 推荐 推荐 推荐

CacheCoherence文献综述

Cache Coherence文献综述文献阅读背景如何选择高速缓存一致性的解决方案一直以来都是设计共享存储器体系结构的关键问题。

相对于维护高速缓存一致性而言,数据的传输也显得简单了。

高速缓存一致性协议致力于保证每个处理器的数据一致性。

一致性通常是在高速缓存总线或者网线上得到保证。

高速缓存的缺失可以从内存中得到数据,除非有些系统(处理器或者输入输出控制器)设备修改了高速缓存总线。

为了进行写操作,该处理器必须进行状态的转换,通常是转换为独占的状态,而总线上其他的系统设备都必须将他们的数据无效化,目前该数据块的拥有者就成为了数据来源。

因此,当其他设备提出需要此数据块时,该数据块的拥有者,而不是内存,就必须提供数据。

只有当该数据块的拥有者必须腾出空间用以存放其他的数据时,才将最新的数据重新写回内存中。

当然,在这方面,各种协议也有区别,上文所诉只是最基本的一些解决方案1。

并且,协议也包括基于硬件的以及基于软件的协议两个种类。

也有写无效和写更新的区别。

下面概述性地介绍下体系结构中所采用的两种主要的一致性方案:监听式(也称广播式)协议:所有的地址都送往所有的系统设备中。

每个设备在本地缓存中检查(监听)高速缓存总线的状态,系统在几个时钟周期后决定了全局的监听结果。

广播式协议提供了最低的可能延迟,尤其当缓存之间的传输是基本的传输方式。

监听式协议传输数据的带宽也是有一定限制的,通常被限制在:带宽=缓存总线带宽×总线时钟周期/每次监听的时钟周期数。

这将在下文中详细提到。

目录式(也称点对点式)协议:每个地址都被送往系统设备中对缓存数据感兴趣的那些设备。

物理存储器的共享状态放在一个地点,称之为目录。

目录式一致性的开销更大,尤其在延时等方面,因为协议本身的复杂性。

但是整体的带宽可以比监听式协议高很多,往往应用于比较大型的系统,最主要的应用是分布式系统。

这将在下文详细提到。

缓存一致性涉及的体系结构主要有如下几种:第一种类型是集中式存储体系结构,也称作为对称(共享存储器)多处理器系统(SMPs),这种体系结构也称为均匀存储器访问(UMA),这是因为所有的处理器访问存储器都有相同的时延。

电芯材料cmp

电芯材料cmp

电芯材料 CMP(Cell Materials CMP)是一种用于制造锂离子电池电芯的材料。

CMP 是“Cell Materials Compound”的缩写,意思是电芯材料混合物。

锂离子电池是一种可充电电池,广泛应用于移动设备、电动汽车和储能系统等领域。

电芯是锂离子电池的核心组成部分,它由正负极、隔膜和电解液等部分组成。

电芯材料 CMP 是指将正负极材料、隔膜和电解液等电芯组件混合在一起形成的材料。

这种材料通常以浆料的形式供应给电池制造商,然后通过涂布、碾压等工艺制成电芯。

电芯材料 CMP 的性能对锂离子电池的性能和寿命有着重要的影响。

因此,电池制造商通常会对 CMP 材料的性能进行严格的测试和筛选,以确保其符合电池设计的要求。

总的来说,电芯材料 CMP 是锂离子电池制造过程中不可或缺的一部分,它的质量和性能直接影响着电池的性能和寿命。

cmp保持环 测试要求

cmp保持环测试要求1.引言1.1 概述概述部分的内容可以是关于CMP保持环测试要求的简要介绍。

可以包括以下内容:CMP保持环测试是一种针对CMP(Content Management Platform)系统的测试方法,用于验证CMP系统在处理大量并发请求时是否能够保持稳定的性能和可靠的功能。

在现代的互联网应用中,CMP系统扮演了至关重要的角色,负责处理和管理各种类型的内容,如文本、图片、视频等。

由于CMP系统需要处理大量的数据和请求,因此对其进行性能和稳定性的测试十分重要。

CMP保持环测试要求主要包括以下几个方面:1. 高并发测试要求:CMP系统需要能够处理大量并发请求,因此在测试过程中要模拟多个用户同时访问系统,以验证系统在高并发情况下的性能表现。

2. 长时间测试要求:CMP系统需要能够保持稳定的性能和功能,因此在测试过程中需要进行长时间的测试,以验证系统在持续工作的情况下是否能够正常运行。

3. 异常情况测试要求:CMP系统需要能够正确处理各种异常情况,如网络故障、服务器宕机等,因此在测试过程中需要模拟各种异常情况,以验证系统的容错能力和恢复能力。

4. 安全性测试要求:CMP系统涉及到用户的隐私数据和敏感信息,因此在测试过程中需要进行安全性测试,以验证系统的安全性和防护能力,确保用户数据的安全和隐私不被泄露。

5. 可扩展性测试要求:CMP系统需要具备良好的可扩展性,能够随着业务的增长而进行扩展和升级,因此在测试过程中需要验证系统的可扩展性,以确保系统能够适应不断增长的业务需求。

通过对CMP保持环测试要求的严格执行,可以有效评估CMP系统的性能、稳定性、安全性和可扩展性,为系统的上线和运维提供重要的参考依据,从而确保系统能够稳定可靠地运行。

文章结构部分的内容可以按照以下方式撰写:1.2 文章结构本文将按照以下结构进行讲述:引言、正文、结论。

引言部分将提供对该测试的概述,阐明文章的目的。

正文部分包含两个要点,分别是第一个要点和第二个要点。

高速缓存设备应用及其性能分析

高速缓存设备应用及其性能分析

王石;董琰;杨贵福;李向龙

【期刊名称】《中国教育网络》

【年(卷),期】2014(000)004

【摘要】高速缓存设备(Cache)可以缓存互联网资源,缩短用户对内容的访问距离,

将互联网内容本地化,大大提升用户用网体验,因而逐渐成为网络应用热点. 校园网

用户的与日俱增,校园网面临的压力越来越大.体现为带宽曰趋紧张,尤其B丁、P2P 下载、在线视频、音乐、网络游戏等网络应用占用大量带宽,严重影响教学、科研、办公活动,导致用户用网体验下降.

【总页数】2页(P76-77)

【作者】王石;董琰;杨贵福;李向龙

【作者单位】东北师范大学;东北师范大学;东北师范大学;东北师范大学

【正文语种】中文

【相关文献】

1.航空钣金成形设备应用调查报告航空钣金成形设备应用调查报告

2.CMP体系结

构上非包含高速缓存的设计及性能分析3.结合流行度选择的集群网络高速缓存优

化仿真4.浅议企业成本与新技术、新设备应用之关系──兼谈铁路平面无线调车设

备应用5.外部高速缓存与非易失内存结合的混合内存体系结构特性评测

因版权原因,仅展示原文概要,查看原文内容请购买。

一种基于容量复用的异构CMP Cache

一种基于容量复用的异构CMP Cache高翔;章隆兵;胡伟武【期刊名称】《计算机研究与发展》【年(卷),期】2008(45)5【摘要】多核环境下的Cache设计技术受到线延时和应用等多方面因素影响,私有和共享方案都存在各自的不足.提出了一种异构的CMP Cache结构,采用两类具有不同Cache层次的结点组成多核芯片,设计了基于间接索引的Cache容量复用等技术,提供了容量有效且访问迅速的片上存储层次.在全系统环境下对SPECCPU2000,SPLASH2等程序的评测结果表明,异构CMP Cache结构能够适应各类应用的需要,对单进程和多线程应用平均性能提高分别可达16%和9%.异构CMP Cache同时具有硬件设计简单的特点,具有较好的工程可实现性,其设计思想将应用在未来的龙芯多核处理器设计中.【总页数】9页(P877-885)【作者】高翔;章隆兵;胡伟武【作者单位】中国科学院计算技术研究所系统结构重点实验室,北京,100190;中国科学技术大学计算机科学与技术系,合肥,230027;中国科学技术大学计算机科学与技术系,合肥,230027;中国科学院计算技术研究所系统结构重点实验室,北京,100190【正文语种】中文【中图分类】TP302【相关文献】1.一种面向CMP的可变相联度混合Cache结构 [J], 晏沛湘;杨先炬;张民选2.一种基于超大容量Cache的VOD系统 [J], 杨金岗;戎蒙恬3.CMP中Cache私有方式下副本容量的动态控制 [J], 文敏华4.CMP 中基于目录的协作Cache 设计方案 [J], 赵小雨;吴俊敏;隋秀峰;王庆波;唐轶轩Sim:基于Pin的CMPCache访问模拟器 [J], 郑启龙;栾俊;房明;吴晓伟因版权原因,仅展示原文概要,查看原文内容请购买。

面向CMP体系结构的二级CACHE替换算法设计

面向CMP体系结构的二级CACHE替换算法设计张骏;樊晓桠;刘松鹤【期刊名称】《小型微型计算机系统》【年(卷),期】2007(28)12【摘要】片上多处理器体系结构(CMP)能够有效地挖掘程序线程级和指令级的并行性.典型的CMP体系结构中二级CACHE被多个处理器内核共享,这提高了二级CACHE利用率并且能避免复制存储器硬件资源.但内核的分支误预测导致错误路径上的LOAD缺失向共享的二级 CACHE中写入无用数据,造成二级CACHE的污染.这降低了其他内核对二级CACHE空间的占用率,增加了二级CACHE缺失率,引起了存储资源在线程间分配的不均衡,甚至导致线程饥饿,影响处理器的整体性能.本文提出一种适用于CMP处理器的轻污染二级CACHE替换算法,优先将这些错误路径上的数据替换出去,缓解了二级CACHE污染对性能造成的影响.【总页数】5页(P2277-2281)【作者】张骏;樊晓桠;刘松鹤【作者单位】西北工业大学,计算机学院,陕西,西安,710072;西北工业大学,计算机学院,陕西,西安,710072;长安大学,信息工程学院,陕西,西安,710064【正文语种】中文【中图分类】TP303【相关文献】1.一种面向CMP的可变相联度混合Cache结构 [J], 晏沛湘;杨先炬;张民选2.基于OPT Cache替换Profiling的Cache提示生成 [J], 田兴彦;黄春;陈火旺3.面向虚拟机环境的Cache动态划分算法设计与实现 [J], 李家文;沈立4.可交换数据Cache结构的CMP:EDCA-CMP [J], 陈建党;郭松柳;王海霞;汪东升5.面向替换延迟隐藏的Cache空间预约技术 [J], 张骏; 田泽; 韩立敏; 牛少平; 裴希杰因版权原因,仅展示原文概要,查看原文内容请购买。

CMP 中基于目录的协作Cache 设计方案

CMP 中基于目录的协作Cache 设计方案赵小雨;吴俊敏;隋秀峰;王庆波;唐轶轩【期刊名称】《计算机工程》【年(卷),期】2010(036)021【摘要】片上多处理器中二级Cache 的设计和管理是影响其性能的关键因素之一.在私有二级Cache 的基础上,提出一种基于集中式一致性目录的协作Cache 设计方案,通过有效地管理片上存储资源来优化处理器的性能,从而使该协作Cache 具有平均访存延迟小、Cache 缺失率低、可扩展性好等优点.实验结果显示,与共享二级Cache 设计相比,协作Cache 可以将4 核处理器的吞吐量平均提高13.5%,而其硬件开销约为8.1%.【总页数】3页(P283-285)【作者】赵小雨;吴俊敏;隋秀峰;王庆波;唐轶轩【作者单位】中国科学技术大学计算机科学与技术学院合肥230027;中国科学技术大学苏州研究院江苏苏州215123;中国科学技术大学计算机科学与技术学院合肥230027;中国科学技术大学苏州研究院江苏苏州215123;中国科学技术大学计算机科学与技术学院合肥230027;中国科学技术大学苏州研究院江苏苏州215123;IBM 中国研究院北京100094;中国科学技术大学计算机科学与技术学院合肥230027;中国科学技术大学苏州研究院江苏苏州215123【正文语种】中文【中图分类】TP302【相关文献】1.基于区域协作的Cache压缩 [J], 曾露;李鹏;王焕东2.CMP中Cache一致性协议的验证 [J], 李崇民;王海;李兆麟3.一种基于容量复用的异构CMP Cache [J], 高翔;章隆兵;胡伟武4.CMP中Cache私有方式下副本容量的动态控制 [J], 文敏华Sim:基于Pin的CMPCache访问模拟器 [J], 郑启龙;栾俊;房明;吴晓伟因版权原因,仅展示原文概要,查看原文内容请购买。

cmp 芯片

cmp 芯片CMP (Complementary Metal Oxide Semiconductor)芯片是一种用于集成电路的制造技术和设计方法。

它采用了双极性硅材料(P型和N型) 来构成互补对。

这种设计使得芯片在电源电压较低的情况下能够实现高速和低功耗的操作。

CMP技术在电子行业中具有重要的地位。

它被广泛应用于微处理器、存储器、逻辑电路等各种芯片的制造和设计过程中。

CMP芯片有很多优势,下面将详细介绍。

首先,CMP芯片具有高度集成的特点。

其制造技术可以实现在一块硅片上同时集成上亿个晶体管。

这种高度集成的特点使得芯片在体积上非常小,因而可以应用于手机、计算机等各种小型设备中。

其次,CMP芯片具有高速的性能。

因为采用了双极性硅材料的互补对设计,CMP芯片能够实现低电平时的高速运算。

这对于需要高速计算的应用非常重要,比如数据中心、人工智能等领域。

第三,CMP芯片拥有低功耗的特性。

双极性硅的互补对设计使得CMP芯片在低电压下能够正常工作。

因此,CMP芯片在运行时可以有效降低功耗,延长电池寿命,在便携设备上得到广泛应用。

此外,CMP芯片还具有良好的可靠性。

由于互补对设计,芯片在工作过程中能够互相平衡电荷和电压,减少噪声和干扰。

这种设计使得芯片在高速运算和复杂电路的情况下更加稳定可靠。

然而,CMP芯片也存在一些挑战。

首先,CMP芯片的制造过程相对复杂,需要精密的工艺和设备。

此外,由于集成度的提高,芯片的设计也变得更加复杂,需要考虑更多的因素,如功耗管理、散热等。

另外,CMP芯片的制造成本也较高,这对于一些小型企业来说可能是一个挑战。

总之,CMP芯片是一种重要的集成电路制造技术和设计方法。

它具有高度集成、高速、低功耗和可靠性等优势。

虽然存在一些挑战,但CMP芯片在电子行业中得到广泛应用,推动了技术的不断发展。

随着科技的进步,CMP芯片在未来将继续发挥重要作用,为人们带来更多便利和创新。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2 Istto o p t gT cn lg, C iee ae yo i cs eig10 8 ,C ia . ntue f m ui eh oo y hn s Acd m f c ne,B in 0 0 0 hn) i C n Se j

Ab t a t Ass m io d co c n l g e eo s i i p s i l a k b l o so a sso so i g e d e Ho t t ie s c sr c : e c n u t rt h o o y d v l p , t s o sb e t p c i i n f r n it r n a s l i . e o l t n w ou i z u h a l

冯 昊 , 吴承 勇 。 。

(.中国科 学 院研 究生 院 ,北京 104 ;2 1 009 .中国科 学 院计算技 术研 究所 ,北 京 108) 000

摘 要 : 半导 体技 术 的发 展使 得在 芯片上 集成 数十 亿 个晶体 管成 为可 能 。目前 工业 界和 学术界 倾 向 于采 用 片上 多处理 器体 系结构 (MP , 于此 类 结构 , 片性 能 受片 外访存 影 响较 大 ,因此 如何 组 织 片上 高速 缓存 层次 结构是 一 个 关键 。针对 此 c )对 芯 问题 , 出采用 非 包含 高速 缓存 组 织 片上 最后 一级 高速 缓存 , 提 以降低 片 外访存 次 数 。并通 过对 S l h 部 分测 试程 序 的详 pa 2 s 细模 拟 ,对 C MP 上 高速 缓存 层 次 结构 的 不 同组 织 方式做 了比较 。数 据显 示非 包含 高速 缓存 最 多可使 平 均访存 时 间降低 83 -%。 同时 , 出非 包含 高速缓 存 有助 于 节省 片上 资 源的 特性 , 指 并给 出片上 集成三 级 高速缓 存后 C MP上 高速 缓存 层 次结

构 的设 计 建 议 。

关键词 : 高速 缓存 ;非 包含 高速缓存 ; 片上 多处理 器; 高速缓 存层 次结构 ; 工作 集 中图法 分类号 : P 0 T 33 文 献标识 码 : A 文章编 号 :0 07 2 2 0 ) 719 —5 1 0—0 4(0 8 0 —5 50

De i n a dp ro ma c n l sso o — cu i ec c eo P sg n e f r n ea ay i f n i l sv a h nCM n n

r g a d eerh rjcs d rs c imut rcsos( MP d s n i s rsac poeta des hp lpo esr C ) ei .Mayds o t n o o o rai c e i acybfr n n i g n ei pi s nh wt ognz c h he h eoe n g o ea r r

h t n mo y wa l or iet ep r o ma c f i i gme r l t s e f r n eo CM P a c ie t r ep e e td a dn n i cu i e a h n f o e Afe v l ai g t a h r h t cu ea r s n e o — l sv c ei o eo t s . r n n c s h t e au t r n s v r l i e e t r a iai n f a h ir c y o e e a f r n g z t so c eh e a h n CM P wi a t l p a h e c ma k , t er s l s o a o — cu i ec c e d o n o c r t p ri l s 2 b h aS n h r s h e u t h wst t n i l sv a h h n n C e e e t f8 3 i r v me t v r g aa a c s i o r d cn f-h p a c s . n a g t n f so .% mp o e n a e a ed t c e st b i n i me f m e u i go c i c e s r Asn n ic u i ec c eC lo s v o — l s a h a as a e n v n o —h p r s u c s i i p o o e n c i e o e , t s r p s dt i r v r o mp o e CM P S e f r a c y o g ii g t e ls n fd f n e o a h ir c y wi o — — ’ p ro m n eb r a z a tl e o e e s fc c e h ea h t n n i n n h i r h n cu i e c c eb f r o n f-h p l s a h e o e g i go c i . v Ke r s c c e n n i cu i ec c e CM P c c eh e a c y wo k n e y wo d : a h ; o — l sv a h ; n ; a h ir h ; r ri gst

维普资讯 http://www.cqv第 2 卷 第 7 9 期

Vo . 9 12 NO 7 .

计 算 机 工程 与设 计

Co p trEn i e rn n sg m u e gn ei ga dDei n

20 年 4 08 月

Apr 0 .2 08

C MP体系结构上非包含高速缓存的设计及性能分析

l r e e o r e u g t f ce t a e n o — on o e r . Th r la v d n eo e d t a o ea dm o ec mm ec a fe a g s u c sb d e f in l h sb e n g i g f r a s r ei y y e ei ce e i e c f he n t r r o s r t t r h m n ril r— o

F N G o E Ha . W U e g y n 。 Ch n — o g

(. rd a nv r t 1 G aut U i sy hn s ae f c ne,B in 0 0 9 hn ; e e i ,C iee Acdmyo i cs e ig10 4 ,C ia Se j