汇编教程控制寄存器和系统地址寄存器

《汇编语言》寄存器物理地址(第二章第二节)

DS ES SS CS 地 址 加 法 IP 器 地 址 总 线 AB

本课件由汇编网()制作提供

物理地址PA = 段地址 + 偏移地址 = ( 段寄存器 ) × 10H + 偏移地址 或段寄存器的内容左移4位,加上偏移地址

例:某内存单元的段地址由DS、偏移地址由BX给出。

2.5 16位结构的CPU

概括的讲,16位结构描述了一个CPU具有 以下几个方面特征:

1、运算器一次最多可以处理16位的数据。 2、寄存器的最大宽度为16位。 3、寄存器和运算器之间的通路是16位的。

2.6 8086CPU给出物理地址的方法

8086有20位地址总线,可传送20 位地址,寻址能力为1M。 8086内部为16位结构,它只能传送 16位的地址,表现出的寻址能力却 只有64K。

2.7 “段地址×16+偏移地址=物理地址” 的本质含义

两个比喻说明:

说明“基础地址+偏移地址 = 物理地址” 的思想:第一个比喻 说明“段地址×16+偏移地址=物理地址” 的思想:第二个比喻 8086CPU就是这样一个只能提供两张3位 数据纸条的CPU。

2.8 段的概念

错误认识:

内存被划分成了一个一个的段,每一个 段有一个段地址。

通用寄存器

数据寄存器(AX,BX,CX,DX) 地址指针寄存器(SP,BP) 变址寄存器(SI,DI)

5

2.1 通用寄存器

8086CPU所有的寄存器都是16位的, 可以存放两个字节。 AX、BX、CX、DX 通常用来存放一般 性数据被称为通用寄存器。 下面以AX为例,我们看一下寄存器的 逻辑结构。

汇编语言入门汇编指令及寄存器详解教程

汇编语⾔⼊门汇编指令及寄存器详解教程⽬录前⾔什么是汇编语⾔汇编语⾔产⽣的原因汇编与⼆进制的关系寄存器寄存器作⽤存取速度⽐较寄存器分类常⽤寄存器⽤途寄存器EAX、AX、AH、AL的关系汇编语⾔指令数据传送指令算术运算指令逻辑运算指令循环控制指令转移指令linux 和 windows 下汇编的区别总结前⾔我们⼤都是被⾼级语⾔惯坏了的⼀代,源源不断的新特性正在逐步添加到各类⾼级语⾔之中,汇编作为最接近机器指令的低级语⾔,已经很少被直接拿来写程序了,不过我还真的遇到了⼀个,那是之前的⼀个同事,因为在写代码时遇到了成员函数权限及可见性的问题,导致他⽆法正确调⽤想执⾏的函数,结果他就开始在C++代码⾥嵌⼊汇编了,绕过了种种限制终于如愿以偿,但是读代码的我们傻眼了…因为项⽬是跨平台的,代码推送的 Linux 上编译的时候他才发现,汇编代码的语法在 Linux 和 Windows 上居然是不⼀样的,结果他⼜⽤⼀个判断平台的宏定义“完美”的解决了,最终这些代码肯定是重写了啊,因为可读性太差了,最近在学习左值、右值、左引⽤和右引⽤的时候,总是有⼈⽤程序编译⽣成的中间汇编代码来解释问题,看得我迷迷糊糊,所以决定熟悉⼀下简单的汇编指令,边学习边记录,⽅便今后忘记了可以直接拿来复习。

什么是汇编语⾔汇编语⾔是最接近机器语⾔的编程语⾔,引⽤百科中的⼀段话解释为:汇编语⾔(assembly language)是⼀种⽤于电⼦计算机、微处理器、微控制器或其他可编程器件的低级语⾔,亦称为符号语⾔。

在汇编语⾔中,⽤助记符代替机器指令的操作码,⽤地址符号或标号代替指令或操作数的地址。

汇编语⾔⼜被称为第⼆代计算机语⾔。

汇编语⾔产⽣的原因对于绝⼤多数⼈来说,⼆进制程序是不可读的,当然有能⼈可以读,⽐如第⼀代程序员,但这类⼈快灭绝了,直接看⼆进制不容易看出来究竟做了什么事情,⽐如最简单的加法指令⼆进制表⽰为00000011,如果它混在⼀⼤串01字符串中就很难把它找出来,所以汇编语⾔主要就是为了解决⼆进制编码的可读性问题。

汇编语言之寄存器(CPU工作原理)

汇编语言之寄存器(CPU工作原理)1、介绍一个典型的CPU,由运算器、控制器、寄存器等器件组成,对于游戏修改者来说,重点学习寄存器,其它不必管。

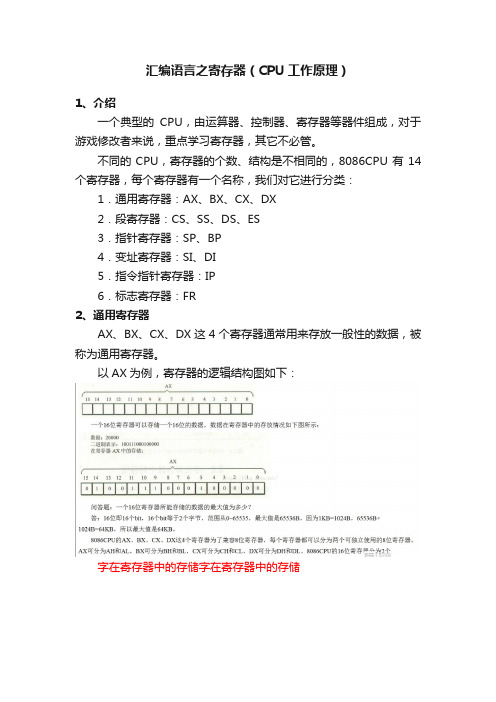

不同的CPU,寄存器的个数、结构是不相同的,8086CPU有14个寄存器,每个寄存器有一个名称,我们对它进行分类:1.通用寄存器:AX、BX、CX、DX2.段寄存器:CS、SS、DS、ES3.指针寄存器:SP、BP4.变址寄存器:SI、DI5.指令指针寄存器:IP6.标志寄存器:FR2、通用寄存器AX、BX、CX、DX这4个寄存器通常用来存放一般性的数据,被称为通用寄存器。

以AX为例,寄存器的逻辑结构图如下:字在寄存器中的存储字在寄存器中的存储3 字在寄存器中的存储4、物理地址存储单元又叫内存单元,以后我们多数用内存单元这一名称。

所有的内存单元构成的存储空间是一个一维的线性空间,每一个内存单元在这个空间中都有唯一的地址,我们将这个唯一的地址称为物理地址。

CPU通过地址总线送入内存的,必须是一个内存单元的物理地址,在CPU向地址总线上发出物理地址之前,必须要在内部先形成这个物理地址,不同的CPU可以有不同的形成物理地址的方式,我们现在讨论8086CPU是如何在内部形成内存单元的物理地址的。

5、 8086CPU给出物理地址的方法8086CPU有20位地址总线,可以传送20位地址,而8086CPU 内部结构是16位的,一次性只能传送16位的地址,怎么解决20位地址与16位地址不一致的问题呢?8086CPU采用一种在内部用2个16位地址合成的方法来形成一个20位的物理地址。

当8086CPU要读写内存时,怎样在CPU内部形成物理地址的呢?1:CPU中的相关部件提供2个16位的地址,一个称为段地址,另一个称为偏移地址。

2:段地址和偏移地址通过内部总线送入一个称为地址加法器的部件。

3:地址加法器将这两个16位地址合成为1个20位的物理地址。

地址加法器采用“段地址×16+偏移地址”的方法合成物理地址。

寄存器、汇编命令详解

寄存器、汇编命令详解汇编命令详解32位CPU所含有的寄存器有:4个数据寄存器(EAX、EBX、ECX和EDX)2个变址和指针寄存器(ESI和EDI) 2个指针寄存器(ESP和EBP) 6个段寄存器(ES、CS、SS、DS、FS和GS)1个指令指针寄存器(EIP) 1个标志寄存器(EFlags)1、数据寄存器数据寄存器主要用来保存操作数和运算结果等信息,从而节省读取操作数所需占用总线和访问存储器的时间。

32位CPU有4个32位的通用寄存器EAX、EBX、ECX和EDX。

对低16位数据的存取,不会影响高16位的数据。

这些低16位寄存器分别命名为:AX、BX、CX和DX,它和先前的CPU中的寄存器相一致。

4个16位寄存器又可分割成8个独立的8位寄存器(AX:AH-AL、BX:BH-BL、CX:CH-CL、DX:DH-DL),每个寄存器都有自己的名称,可独立存取。

程序员可利用数据寄存器的这种“可分可合”的特性,灵活地处理字/字节的信息。

寄存器EAX通常称为累加器(Accumulator),用累加器进行的操作可能需要更少时间。

可用于乘、除、输入/输出等操作,使用频率很高;寄存器EBX称为基地址寄存器(Base Register)。

它可作为存储器指针来使用;寄存器ECX称为计数寄存器(Count Register)。

在循环和字符串操作时,要用它来控制循环次数;在位操作中,当移多位时,要用CL来指明移位的位数;寄存器EDX称为数据寄存器(Data Register)。

在进行乘、除运算时,它可作为默认的操作数参与运算,也可用于存放I/O的端口地址。

在16位CPU中,AX、BX、CX和DX不能作为基址和变址寄存器来存放存储单元的地址,在32位CPU中,其32位寄存器EAX、EBX、ECX和EDX不仅可传送数据、暂存数据保存算术逻辑运算结果,而且也可作为指针寄存器,所以,这些32位寄存器更具有通用性。

2、变址寄存器32位CPU有2个32位通用寄存器ESI和EDI。

汇编语言—寄存器

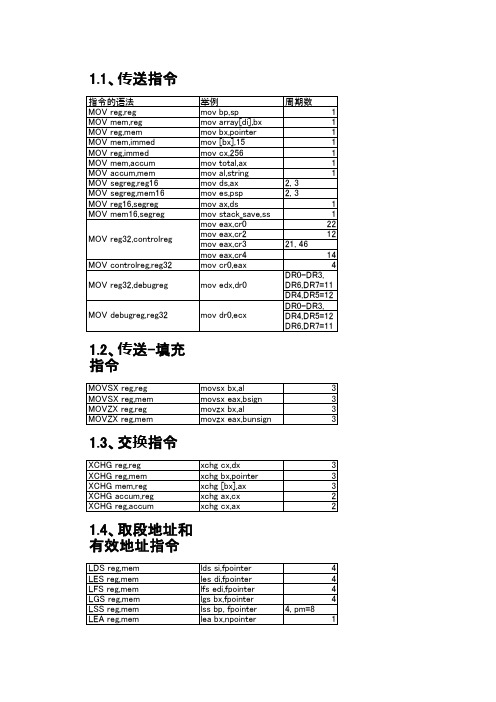

1.1、传送指令

指令的语法 MOV reg,reg MOV mem,reg MOV reg,mem MOV mem,immed MOV reg,immed MOV mem,accum MOV accum,mem MOV segreg,reg16 MOV segreg,mem16 MOV reg16,segreg MOV mem16,segreg MOV reg32,controlreg MOV controlreg,reg32 MOV reg32,debugreg MOV debugreg,reg32 举例 mov bp,sp mov array[di],bx mov bx,pointer mov [bx],15 mov cx,256 mov total,ax mov al,string mov ds,ax mov es,psp mov ax,ds mov stack_save,ss mov eax,cr0 mov eax,cr2 mov eax,cr3 mov eax,cr4 mov cr0,eax mov edx,dr0 mov dr0,ecx 周期数 1 1 1 1 1 1 1 2, 3 2, 3 1 1 22 12 21, 46 14 4 DR0-DR3, DR6,DR7=11 DR4,DR5=12 DR0-DR3, DR4,DR5=12 DR6,DR7=11

1.6、出栈指令

POP reg POP mem POP segreg POPA POPAD POPF POPFD pop cx pop param pop es popa popad popf popfd 1 3 3 5 5 6, pm=4 6, pm=4

汇编语言手册

寄存器与存储器1. 寄存器功能. 寄存器的一般用途和专用用途. CS:IP 控制程序执行流程. SS:SP 提供堆栈栈顶单元地址. DS:BX(SI,DI) 提供数据段内单元地址. SS:BP 提供堆栈内单元地址. ES:BX(SI,DI) 提供附加段内单元地址. AX,CX,BX和CX寄存器多用于运算和暂存中间计算结果,但又专用于某些指令(查阅指令表)。

. PSW程序状态字寄存器只能通过专用指令(LAHF, SAHF)和堆栈(PUSHF,POPF)进行存取。

2. 存储器分段管理. 解决了16位寄存器构成20位地址的问题. 便于程序重定位. 20位物理地址=段地址* 16 + 偏移地址. 程序分段组织: 一般由代码段,堆栈段,数据段和附加段组成,不设置堆栈段时则使用系统内部的堆栈。

3. 堆栈. 堆栈是一种先进后出的数据结构, 数据的存取在栈顶进行, 数据入栈使堆栈向地址减小的方向扩展。

. 堆栈常用于保存子程序调用和中断响应时的断点以及暂存数据或中间计算结果。

.堆栈总是以字为单位存取指令系统与寻址方式1. 指令系统. 计算机提供给用户使用的机器指令集称为指令系统,大多数指令为双操作数指令。

执行指令后,一般源操作数不变,目的操作数被计算结果替代。

. 机器指令由CPU执行,完成某种运算或操作,8086/8088指令系统中的指令分为6类: 数据传送,算术运算,逻辑运算,串操作,控制转移和处理机控制。

2. 寻址方式. 寻址方式确定执行指令时获得操作数地址的方法. 分为与数据有关的寻址方式(7种)和与转移地址有关的寻址方式(4)种。

. 与数据有关的寻址方式的一般用途:(1) 立即数寻址方式--将常量赋给寄存器或存储单元(2) 直接寻址方式--存取单个变量(3) 寄存器寻址方式--访问寄存器的速度快于访问存储单元的速度(4) 寄存器间接寻址方式--访问数组元素(5) 变址寻址方式(6) 基址变址寻址方式(7) 相对基址变址寻址方式(5),(6),(7)都便于处理数组元素. 与数据有关的寻址方式中,提供地址的寄存器只能是BX,SI,DI或BP. 与转移地址有关的寻址方式的一般用途:(1) 段内直接寻址--段内直接转移或子程序调用(2) 段内间接寻址--段内间接转移或子程序调用(3) 段间直接寻址--段间直接转移或子程序调用(4) 段间间接寻址--段间间接转移或子程序调用汇编程序和汇编语言1. 汇编程序. 汇编程序是将汇编语言源程序翻译成二进制代码程序的语言处理程序,翻译的过程称为汇编。

汇编教程汇编指令详解

汇编教程汇编指令详解

汇编语言可以说是机器语言的一种直观形式,是与硬件直接相关的低

级程序设计语言。

它是一种以简洁的汇编指令来表达操作码机器指令的程

序设计语言,汇编语言的指令代码一般比机器语言的指令代码要短,是编

写高效、可移植的机器级程序的理想语言。

汇编语言的基本构成:

(1)指令集:汇编语言的指令集是机器的最基本和最重要的组成部分,也是机器的指令集,描述了机器所做的操作。

(2)操作数:汇编语言的指令集中涉及到的操作数有多种,比如寄

存器操作数、立即数、内存操作数等。

(3)运算和转移指令:汇编语言中的运算和转移指令包括算术运算

指令、比较指令、逻辑运算指令、移位指令等,它们是机器执行的基本操作。

(4)转移指令:汇编语言中的转移指令可以改变机器指令的执行顺序,并实现分支程序设计。

(5)I/O指令:汇编语言中的I/O指令可以实现与外部设备的通信,获取外部设备提供的数据。

(6)汇编指令:汇编指令用于移植各种汇编程序到不同的处理器上,从而实现程序的机器无关性。

一、MOV指令:

MOV指令用于把操作数的值赋给另一个操作数。

汇编指令大全

汇编指令大全1. 引言汇编语言是一种基于计算机硬件体系结构的低级语言。

它用于编写与硬件交互的程序,并且具有直接访问计算机底层硬件的能力。

汇编指令是汇编语言中的基本操作指令,用于执行各种计算机操作,如数据传输、算术运算和逻辑运算等。

本文将为您介绍一些常见的汇编指令。

2. 数据传输指令数据传输指令用于在寄存器之间或内存和寄存器之间传输数据。

2.1 MOV - 数据传送指令mov是最常见的数据传送指令之一。

它用于将数据从一个源操作数传送到一个目的操作数。

mov destination, source其中,destination是目的操作数,source是源操作数。

这两个操作数可以是寄存器、内存地址或立即数。

2.2 LEA - 加载有效地址指令lea指令用于加载一个有效地址到一个目的操作数。

lea destination, source其中,destination是目的操作数,通常为一个寄存器,source是一个内存地址。

3. 算术运算指令算术运算指令用于执行加法、减法、乘法和除法等算术运算。

3.1 ADD - 加法指令add指令用于将两个操作数相加,并将结果存储在目的操作数中。

add destination, source其中,destination是目的操作数,source是源操作数。

这两个操作数可以是寄存器或内存地址。

3.2 SUB - 减法指令sub指令用于将第二个操作数从第一个操作数中减去,并将结果存储在目的操作数中。

sub destination, source其中,destination是目的操作数,source是源操作数。

这两个操作数可以是寄存器或内存地址。

3.3 MUL - 乘法指令mul指令用于将两个操作数相乘,并将结果存储在目的操作数中。

其中,destination是目的操作数,source是源操作数。

这两个操作数可以是寄存器或内存地址。

3.4 DIV - 除法指令div指令用于将目的操作数除以源操作数,并将商存储在目的操作数中,余数存储在另一个寄存器中。

[整理]寄存器详细讲解

![[整理]寄存器详细讲解](https://img.taocdn.com/s3/m/2562f8711fb91a37f111f18583d049649b660e6f.png)

[整理]寄存器详细讲解-------------寄存器32位CPU的寄存器结构寄存器是中央处理器内的组成部分。

寄存器是有限存贮容量的高速存贮部件,它们可用来暂存指令、数据和位址。

在中央处理器的控制部件中,包含的寄存器有指令寄存器(IR)和程序计数器(PC)。

在中央处理器的算术及逻辑部件中,包含的寄存器有累加器(ACC)。

目录编辑本段寄存器英文名称:Register寄存器寄存器是内存阶层中的最顶端,也是系统获得操作资料的最快速途径。

寄存器通常都是以他们可以保存的位元数量来估量,举例来说,一个“8 位元寄存器”或“32 位元寄存器”。

寄存器现在都以寄存器档案的方式来实作,但是他们也可能使用单独的正反器、高速的核心内存、薄膜内存以及在数种机器上的其他方式来实作出来。

寄存器通常都用来意指由一个指令之输出或输入可以直接索引到的暂存器群组。

更适当的是称他们为“架构寄存器”。

例如,x86 指令集定义八个32 位元寄存器的集合,但一个实作x86 指令集的CPU 可以包含比八个更多的寄存器。

寄存器是CPU内部的元件,寄存器拥有非常高的读写速度,所以在寄存器之间的数据传送非常快。

编辑本段分类数据寄存器- 用来储存整数数字(参考以下的浮点寄存器)。

在某些简单/旧的CPU,特别的数据寄存寄存器器是累加器,作为数学计算之用。

地址寄存器- 持有存储器地址,以及用来访问存储器。

在某些简单/旧的CPU里,特别的地址寄存器是索引寄存器(可能出现一个或多个)。

通用目的寄存器(GPRs)- 可以保存数据或地址两者,也就是说他们是结合数据/地址寄存器的功用。

浮点寄存器(FPRs) - 用来储存浮点数字。

常数寄存器- 用来持有只读的数值(例如0、1、圆周率等等)。

向量寄存器- 用来储存由向量处理器运行SIMD(Single Instruction, Multiple Data)指令所得到的数据。

特殊目的寄存器- 储存CPU内部的数据,像是程序计数器(或称为指令指针),堆栈寄存器,以及状态寄存器(或称微处理器状态字组)。

汇编语言程序设计知识

汇编语言程序设计知识汇编语言是一种低级语言,用于向计算机提供指令和数据。

掌握汇编语言程序设计知识,对于深入理解计算机体系结构和系统底层原理非常重要。

本文将为你介绍汇编语言程序设计的基本知识,并探讨其在实际应用中的应用。

一、汇编语言概述汇编语言是一种与机器语言直接对应的语言,每一条指令都可以直接被计算机硬件执行。

相比高级语言,汇编语言更加接近计算机底层,因此执行效率更高。

汇编语言通常包括指令集、寄存器和内存等概念。

1. 指令集汇编语言的指令集是由一系列指令组成的,这些指令可以直接被计算机执行。

指令集通常包括算术指令、逻辑指令、数据传输指令等,每个指令具有特定的功能和操作码。

2. 寄存器寄存器是计算机内部用于存储数据和执行操作的存储器。

在汇编语言中,寄存器用于进行数据传输、算术运算和逻辑操作等。

常见的寄存器包括通用寄存器、特殊寄存器和段寄存器等。

3. 内存内存是计算机用于存储指令和数据的地方。

在汇编语言中,程序员可以直接操作内存地址,进行数据的读取和存储。

通过合理地利用内存,可以提高程序的执行效率。

二、基本语法和数据表示在汇编语言中,程序员需要掌握基本的语法和数据表示方法,以编写正确的程序。

1. 语法汇编语言的语法是由指令、操作数和注释组成的。

指令是计算机执行的命令,操作数是指令所涉及的数据或寄存器。

注释用于解释程序的功能和作用。

2. 数据表示在汇编语言中,数据可以表示为二进制、十进制、十六进制等形式。

程序员需要根据实际需求选择适当的表示方式,并了解不同进制之间的转换方法。

三、程序设计实例为了更好地理解和应用汇编语言程序设计知识,我们将通过一个实例来演示程序设计的过程。

假设我们需要编写一个汇编程序,实现两个数相加的功能。

下面是程序的伪代码表示:```1. 将第一个数存储到寄存器A2. 将第二个数存储到寄存器B3. 将寄存器A和寄存器B的值相加,结果存储到寄存器C4. 将寄存器C的值存储到内存中```根据上述伪代码,我们可以编写如下的汇编程序:```MOV AX, num1 ; 将第一个数存储到寄存器AXMOV BX, num2 ; 将第二个数存储到寄存器BXADD AX, BX ; 将寄存器AX和寄存器BX的值相加MOV result, AX ; 将寄存器AX的值存储到result内存地址中```通过上述程序,我们实现了两个数相加的功能,并将结果保存在result变量中。

汇编入门 精髓(转)寄存器和寻址方式

一汇编入门精髓(转)寄存器和寻址方式2010-03-20 13:01寄存器和寻址方式寄存器,在8086/8088里,有三组共13个16位寄存器.寄存器,从名字上看,可以知道,它就象书店的行包寄存处,寄存器的名字就象寄存处发给用户取回自已物件的标志牌子,表示物件的存放地址.寄存器的内部给构都相同,只不过是一个二字节或一字节的存储空间,别看他们小,作用可大了,所有电脑的运算,都要从他们过关,因为他们的处理速度快嘛.为了区分和准确运用,就要给他们进行科学的分组和起名.第一组,数据寄存器,AX,BX,CX,DX.其中,X表示一个未知数,那么这些寄存器都可以用来存放数据,ABCD,虽说都可以理解为一个顺序号,但是,A还是加法ADD的简称,所以AX叫累加器,B是基地址的简称,所以BX可以叫基地址寄存器,C是计数器的简称,所以CX可以叫做计数器.D是数据DATA的简称,所以DX可以叫数据寄存器.这四个寄存都可以按高八位和低八位分成两个寄存器:AH,AL,BH,BL,CH,CL,DH,DL.第二组,地址指示和变址寄存器,SI,DI,BP,SP.它们用来表示一个地址偏移,或用来表示一个地址的变化状况.SI,DI都可以表示变址,在串操作中,SI和DI表示源和目的操作数的指示器,快速记忆方法:SI联想饮水思源的思(谐音SI),DI联想目的(谐音DI).BP,SP的P表示堆栈专用,BP表示基地址专用,SP则是堆栈顶指示器.其中,BP,SI,DI还可以兼作数据寄存器.SP则只能和堆栈绑定.第三组,段寄存器,CS,SS,DS,ES.它们用来存放CPU可以直接访问的四个当前段的段首地址.CS代码段,SS堆栈段,DS数据段,ES附加段.其中,在表示地址时,CS和指令指示器IP绑定使用,SS 和BP绑定.DS为SI,DI,BX共用.第四组,指令指示器,IP,这是CPU自动引用的,表示下一次要从主存取出的指令的偏移.寻址方式寻址方式分为六种,(这是教材里讲的).1,立即寻址, 数据的本身在代码段.用于赋初值.2,直接寻址, 数据的偏移在代码段,用于变量名.3,寄存器寻址, 数据的本身在寄存器.用寄存器名表示.4,寄存器相对寻址, 数据的偏移在寄存器.注意:BP和SS绑定.DS为SI,DI,BX 共用.5,变址寻址, 数据的偏移在一个寄存器里,并要加上一个偏移量.注意:BP和SS绑定.DS为SI,DI,BX共用.6,基址加变址寻址, 数据的偏移放在两个寄存器中,并要加上一个偏移量.注意:BP和SS绑定.DS为SI,DI,BX共用.BX为DS段的基址专用.寻址方式是汇编语言的重点和难点。

x86汇编 讲解

x86汇编讲解摘要:1.x86 汇编简介2.x86 汇编的基本语法3.x86 汇编的寄存器和内存4.x86 汇编的指令集5.x86 汇编的应用场景正文:【x86 汇编简介】x86 汇编是一种用于编写计算机程序的低级编程语言。

它是x86 架构处理器的指令集体系结构(ISA) 的助记符表示形式。

x86 汇编语言可以用于编写操作系统、驱动程序和嵌入式系统等底层应用程序。

由于其底层特性,x86 汇编语言能够直接访问计算机硬件,并实现高性能的计算。

【x86 汇编的基本语法】x86 汇编语言的基本语法包括以下几个部分:1.指令:x86 汇编指令是用于完成特定任务的命令。

每个指令都有一个操作码,它表示指令要执行的操作。

操作码后面通常跟有一些操作数,用于指定操作的对象。

2.寄存器:x86 汇编中的寄存器是一组高速存储单元,用于存储数据和地址。

常用的寄存器包括通用寄存器(EAX、EBX、ECX、EDX)、指针寄存器(ESP、EBP)和索引寄存器(ESI、EDI)等。

3.内存:x86 汇编中的内存是指计算机中的主存储器,用于存储程序和数据。

内存地址通常用基址(Base Address)加偏移量(Displacement)的方式表示。

4.常用指令:x86 汇编中有很多常用指令,包括数据传输指令(如MOV)、算术指令(如ADD、SUB)、逻辑指令(如AND、OR)、跳转指令(如JMP、JZ、JNZ)等。

【x86 汇编的寄存器和内存】x86 汇编中的寄存器和内存扮演着非常重要的角色。

它们可以存储程序中的数据和地址,并在程序运行过程中进行高速读写。

以下是一些常用的寄存器和内存操作指令:1.寄存器指令:MOV 寄存器,数值将数值移动到指定的寄存器中。

2.内存指令:MOV 内存地址,寄存器将寄存器的值移动到指定的内存地址。

3.加载/存储指令:LOAD/STORE 寄存器,内存地址在内存和寄存器之间传输数据。

【x86 汇编的指令集】x86 汇编指令集非常丰富,可以完成各种复杂的操作。

汇编教程,汇编指令详解

A 0 0 1 1

B 0 1 0 1

AvB 0 1 1 1

21

1.4.3 “非”运算(NOT) 如变量为A,则它的“非”运算的结果用 A来 表示。“非”运算规则可用下表说明: A A 0 1 1 0

22

1.4.4 “异或”运算(XOR Exclusive—OR)

“异或”运算可用符号 来表示。 运算规则:即当两个变量的取值相异时,它们 的“异或” 结果为1。

13

用补码表示数时的符号扩展问题

符号扩展:将一个数从位数较少扩展到 位数较多。正数的符号扩展:高位补0, 负数的符号扩展:高位补1。

汇编语言程序设计教程(第二版)习题参考答案

汇编语言程序设计教程(第二版)习题参考答案第1章计算机基础知识1.计算机的应用分哪几个方面,请举例说明书中未提到的领域的计算机应用。

科学计算、数据处理、计算机控制、计算机辅助设计、人工智能、企业管理、家用电器、网络应用。

书中未提及的如:远程教育、住宅小区控制、飞行系统控制与管理等。

2.简述计算机的发展过程,请查阅相关资料,列出微机的发展过程。

电子管、晶体管、集成电路、大规模集成电路以IBM为例,微机的发展:4004、8008、8080、8086/8088、80286、80386、80486、Pentium 系列3.计算机的字长是怎么定义的,试举例说明。

计算机能同时处理二进制信息的位宽定义为计算机的字长。

如8086能同时进行16位二进制数据的运算、存储和传输等操作,该机器的字长为16位。

4.汇编语言中的基本数据类型有哪些?数值型数据和非数值型数据。

非数值数据如字符、字符串、逻辑值等。

(1)7BCH=011110111100B=1980D(2)562Q=101110010B=370D(3)90D=01011010B=5AH(4)1110100.111B=164.7Q=74.EH30H~39H 41H~5AH 61H~7AH9.在汇编语言中,如何表示二进制、八进制、十进制和十六进制的数值?用相应进制的数值加上进制标记即可。

二进制用B,如10101010B八进制用Q,如437Q。

十进制用D或不用,如54D,或54。

十六进制用H,如27A8H10.完成下列二进制数的加减运算。

(1)10101010 + 11110000 (2)11001100 + 01010100=110011010 =100100000(3)11011010 - 01010010 (4)11101110 - 01001101=10001000 =1010000111.完成下列十六进制数的加减运算。

(1)0FEA9 - 8888=7621H (2)0FFFF - 1234=EDCBH(3)0EAC0 + 0028=EAE8H (4)3ABC + 1678=5134H12.完成下列BCD码的运算。

汇编语言重点知识总结

汇编语言重点知识总结汇编速查手册汇编语言总结概要寄存器与存储器1. 寄存器功能. 寄存器的一般用途和专用用途. CS:IP 控制程序执行流程. SS:SP 提供堆栈栈顶单元地址. DS:BX(SI,DI) 提供数据段内单元地址. SS:BP 提供堆栈内单元地址. ES:BX(SI,DI) 提供附加段内单元地址. AX,CX,BX 和CX 寄存器多用于运算和暂存中间计算结果,但又专用于某些指令( 查阅指令表)。

. PSW 程序状态字寄存器只能通过专用指令( LAHF, SAHF) 和堆栈(PUSHF,POPF) 进行存取。

2. 存储器分段管理. 解决了16 位寄存器构成20 位地址的问题. 便于程序重定位. 20 位物理地址= 段地址* 16 + 偏移地址. 程序分段组织: 一般由代码段, 堆栈段,数据段和附加段组成, 不设置堆栈段时则使用系统内部的堆栈。

3. 堆栈. 堆栈是一种先进后出的数据结构, 数据的存取在栈顶进行, 数据入栈使堆栈向地址减小的方向扩展。

. 堆栈常用于保存子程序调用和中断响应时的断点以及暂存数据或中间计算结果。

. 堆栈总是以字为单位存取指令系统与寻址方式1. 指令系统. 计算机提供给用户使用的机器指令集称为指令系统, 大多数指令为双操作数指令。

执行指令后,一般源操作数不变,目的操作数被计算结果替代。

. 机器指令由CPU 执行,完成某种运算或操作,8086/8088 指令系统中的指令分为6 类: 数据传送,算术运算,逻辑运算,串操作,控制转移和处理机控制。

2. 寻址方式. 寻址方式确定执行指令时获得操作数地址的方法. 分为与数据有关的寻址方式(7 种) 和与转移地址有关的寻址方式(4)种。

. 与数据有关的寻址方式的一般用途:(1) 立即数寻址方式--将常量赋给寄存器或存储单元(2) 直接寻址方式-- 存取单个变量(3) 寄存器寻址方式--访问寄存器的速度快于访问存储单元的速度(4) 寄存器间接寻址方式--访问数组元素(5) 变址寻址方式(6) 基址变址寻址方式(7) 相对基址变址寻址方式(5),(6),(7) 都便于处理数组元素. 与数据有关的寻址方式中,提供地址的寄存器只能是BX,SI,DI 或BP . 与转移地址有关的寻址方式的一般用途:(1) 段内直接寻址-- 段内直接转移或子程序调用(2) 段内间接寻址-- 段内间接转移或子程序调用(3) 段间直接寻址-- 段间直接转移或子程序调用(4) 段间间接寻址-- 段间间接转移或子程序调用汇编程序和汇编语言1. 汇编程序. 汇编程序是将汇编语言源程序翻译成二进制代码程序的语言处理程序, 翻译的过程称为汇编。

汇编的内容

汇编的内容

汇编语言(Assembly Language)是一种用于计算机编程的低级语言,它直接与计算机硬件交互,提供了对计算机体系结构的底层控制。

汇编语言的主要内容包括以下几个方面:

1. 指令集:汇编语言使用特定计算机的指令集来描述程序的操作。

每个指令对应着计算机可以执行的一个基本操作,例如加载数据、存储数据、进行算术运算等。

2. 寄存器:寄存器是计算机内部用于存储数据和操作结果的高速存储单元。

在汇编语言中,通过引用寄存器来操作和传递数据。

3. 寻址方式:寻址方式用于指定操作数的位置,可以是立即数、寄存器、内存中的数据等。

汇编语言支持多种寻址方式,例如直接寻址、间接寻址、寄存器间接寻址等。

4. 伪指令:伪指令是汇编语言中用于指导编译器

进行相关操作的特殊指令,它们不直接对应计算机的硬件操作。

例如,伪指令可以用于定义数据段、分配内存空间、声明变量等。

5. 程序结构:汇编语言程序通常由多个模块组成,包括数据段、代码段和堆栈段等。

程序结构的组织和管理对于程序的可维护性和可读性非常重要。

6. 调试和调试工具:汇编语言编程需要使用专门的调试工具来帮助程序员检查程序的执行情况、查看寄存器和内存的内容等。

汇编的8种寻址方式,以及2个默认段寄存器

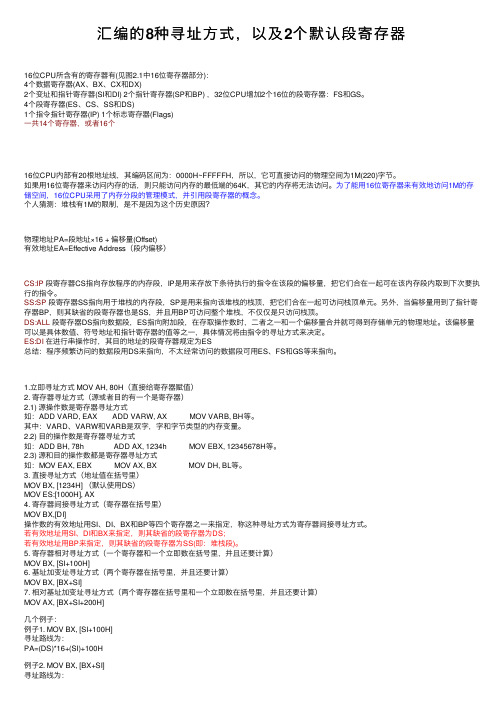

汇编的8种寻址⽅式,以及2个默认段寄存器16位CPU所含有的寄存器有(见图2.1中16位寄存器部分):4个数据寄存器(AX、BX、CX和DX)2个变址和指针寄存器(SI和DI) 2个指针寄存器(SP和BP) ,32位CPU增加2个16位的段寄存器:FS和GS。

4个段寄存器(ES、CS、SS和DS)1个指令指针寄存器(IP) 1个标志寄存器(Flags)⼀共14个寄存器,或者16个16位CPU内部有20根地址线,其编码区间为:0000H~FFFFFH,所以,它可直接访问的物理空间为1M(220)字节。

如果⽤16位寄存器来访问内存的话,则只能访问内存的最低端的64K,其它的内存将⽆法访问。

为了能⽤16位寄存器来有效地访问1M的存储空间,16位CPU采⽤了内存分段的管理模式,并引⽤段寄存器的概念。

个⼈猜测:堆栈有1M的限制,是不是因为这个历史原因?物理地址PA=段地址×16 + 偏移量(Offset)有效地址EA=Effective Address(段内偏移)CS:IP段寄存器CS指向存放程序的内存段,IP是⽤来存放下条待执⾏的指令在该段的偏移量,把它们合在⼀起可在该内存段内取到下次要执⾏的指令。

SS:SP段寄存器SS指向⽤于堆栈的内存段,SP是⽤来指向该堆栈的栈顶,把它们合在⼀起可访问栈顶单元。

另外,当偏移量⽤到了指针寄存器BP,则其缺省的段寄存器也是SS,并且⽤BP可访问整个堆栈,不仅仅是只访问栈顶。

DS:ALL段寄存器DS指向数据段,ES指向附加段,在存取操作数时,⼆者之⼀和⼀个偏移量合并就可得到存储单元的物理地址。

该偏移量可以是具体数值、符号地址和指针寄存器的值等之⼀,具体情况将由指令的寻址⽅式来决定。

ES:DI在进⾏串操作时,其⽬的地址的段寄存器规定为ES总结:程序频繁访问的数据段⽤DS来指向,不太经常访问的数据段可⽤ES、FS和GS等来指向。

1.⽴即寻址⽅式 MOV AH, 80H(直接给寄存器赋值)2. 寄存器寻址⽅式(源或者⽬的有⼀个是寄存器)2.1) 源操作数是寄存器寻址⽅式如:ADD VARD, EAX ADD VARW, AX MOV VARB, BH等。

汇编语言——寄存器

汇编语⾔——寄存器⼀、栈的基本概念栈有两个基本的操作:⼊栈和出栈。

⼊栈:将⼀个新的元素放到栈顶;出栈:从栈顶取出⼀个元素。

栈顶的元素总是最后⼊栈,需要出栈时,⼜最先被从栈中取出。

栈的操作规则:后进先出8086CPU提供的栈机制8086CPU提供⼊栈和出栈指令:(最基本的)PUSH(⼊栈)POP (出栈)push ax:将寄存器ax中的数据送⼊栈中;pop ax :从栈顶取出数据送⼊ax。

push和pop指令也可以在内存和寄存器传输数据(以栈的形式)8086CPU的⼊栈和出栈操作都是以字为单位进⾏的。

⽰例:1 2 3 4 5 6 7 8 9 10 11假设将10000H~1000FH这段内存当作栈来使⽤(其实CPU并不知道这段是代码段,数据段还是栈段,都是⼈为设定的)下⾯⼀段指令的执⾏过程:mov ax,0123H# AX=0123Hpush ax # 将AX的值推⼊栈中mov bx,2266H# BX=2266Hpush bx # 将BX的值推⼊栈中mov cx,1122H# CX=1122Hpush cx # 将CX的值推⼊栈中pop ax # 将栈顶的2个内存单元取出放到AX寄存器中,AX=1122Hpop bx # 将栈顶的2个内存单元取出放到BX寄存器中,BX=2266Hpop cx # 将栈顶的2个内存单元取出放到CX寄存器中,CX=0123H那么问题来了,在执⾏push和pop的时候,如何知道哪个单元是栈顶单元?8086CPU中,有两个寄存器:段寄存器SS 存放栈顶的段地址寄存器SP 存放栈顶的偏移地址任意时刻,SS:SP指向栈顶元素。

⼆、push和pop指令push 指令的执⾏过程在执⾏push ax指令时,主要做了⼀下2件事(1)先将SP=SP–2(2)将ax中的内容送⼊SS:SP指向的内存单元处,SS:SP此时指向新栈顶。

pop 指令的执⾏过程在执⾏pop ax指令时,主要做了⼀下2件事(1)先将SS:SP指向的内存单元处的数据送⼊ax中;(2)SP = SP+2,SS:SP指向当前栈顶下⾯的单元,以当前栈顶下⾯的单元为新的栈顶。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

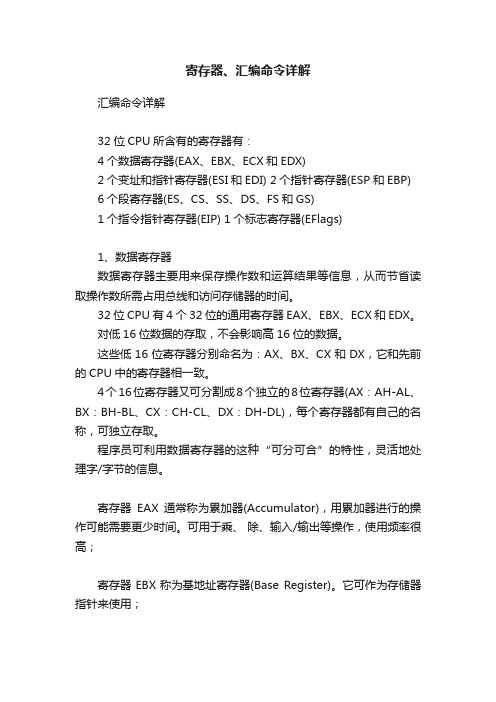

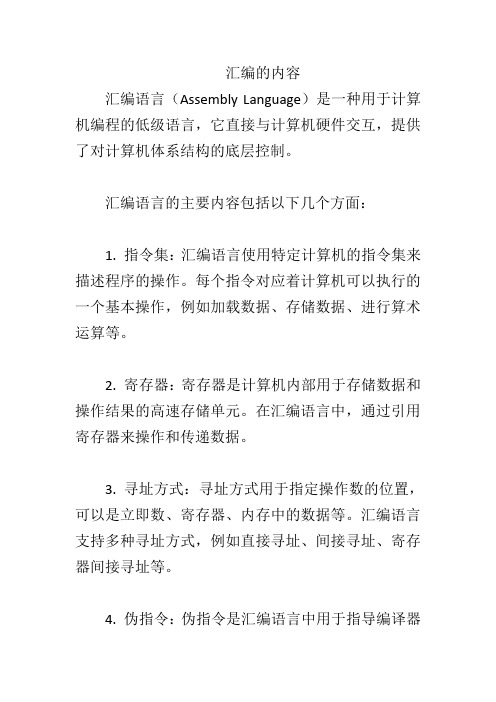

80386控制寄存器和系统地址寄存器如下表所示。

它们用于控制工作方式,控制分段管理机制及分页管理机制的实施。

控制寄存器CRx BIT31 BIT30—BIT12 BIT11—BIT5 BIT4 BIT3 BIT2 BIT1 BIT0 CR0 PG 0000000000000000 ET TS EM MP PE CR1 保留

CR2 页故障线性地址

CR3 页目录表物理页码000000000000

BIT47—BIT16 BIT15—BIT

全局描述符表寄存器GDTR 基地址界限中断描述符表寄存器IDTR 基地址界限

BIT15—BIT0

局部描述符表寄存器LDTR 选择子任务状态段寄存器TR 选择子BIT31—BIT0 BIT31—BIT0 BIT11—BIT0 基地址界限属性

基地址界限属性

<一>控制寄存器

从上表可见,80386有四个32位的控制寄存器,分别命名位CR0、CR1、CR2和CR3。

但CR1被保留,供今后开发的处理器使用,在80386中不能使用CR1,否则会引起无效指令操作异常。

CR0包括指示处理器工作方式的控制位,包含启用和禁止分页管理机制的控制位,包含控制浮点协处理器操作的控制位。

CR2及CR3由分页管理机制使用。

CR0中的位5—位3 0及CR3中的位0至位11是保留位,这些位不能是随意值,必须为0。

控制寄存器CR0的低16位等同于80286的机器状态字MSW。

1.保护控制位

控制寄存器CR0中的位0用PE标记,位31用PG标记,这两个位控制分段和分页管理机制的操作,所以把它们称为保护控制位。

PE控制分段管理机制。

PE=0,处理器运行于实模式;PE=1,处理器运行于保护方式。

PG控制分页管理机制。

PG=0,禁用分页管理机制,此时分段管理机制产生的线性地址直接作为物理地址使用;PG=1,启用分页管理机制,此时线性地址经分页管理机制转换位物理地址。

关于分页管理机制的具体介绍在后面的文章中进行。

下表列出了通过使用PE和PG位选择的处理器工作方式。

由于只有在保护方式下才可启用分页机制,所以尽管两个位分别为0和1共可以有四种组合,但只有三种组合方式有效。

PE=0且PG=1是无效组合,因此,用PG 为1且PE 为0的值装入CR0寄存器将引起通用保护异常。

需要注意的是,PG 位的改变将使系统启用或禁用分页机制,因而只有当所执行的程序的代码和至少有一部分数据在线性地址空间和物理地址空间具有相同的地址的情况下,才能改变PG 位。

PG 和PE 位与处 理器工 作模式

PG P E 处理器工作方式

0 0 实模式 0 1 保护模式,禁用分页机制 1 0 非法组合 1 1 保护方式,启用分页机制

2.协处理器控制位

控制寄存器CR0中的位1—位4分别标记为MP(算术存在位)、EM(模拟位)、TS(任务切换位) 和ET(扩展类型位),它们控制浮点协处理器的操作。

当处理器复位时,ET 位被初始化,以指示系统中数字协处理器的类型。

如果系统中存在 80387协处理器,那么ET 位置1;如果系统中存在80287协处理器或者不存在协处理器,那么ET 位清0。

EM 位控制浮点指令的执行是用软件模拟,还是由硬件执行。

EM=0时,硬件控制浮点指令传送到协处理器;EM=1时,浮点指令由软件模拟。

TS 位用于加快任务的切换,通过在必要时才进行协处理器切换的方法实现这一目的。

每当进行任务切换时,处理器把TS 置1。

TS=1时,浮点指令将产生设备不可用(DNA)异常。

MP 位控制WAIT 指令在TS=1时,是否产生DNA 异常。

MP=1和TS=1时,WAIT 产生异常;MP =0时,WAIT 指令忽略TS 条件,不产生异常。

3.CR2和CR3

控制寄存器CR2和CR3由分页管理机制使用。

CR2用于发生页异常时报告出错信息。

当发生页异常时,处理器把引起页异常的线性地址保存在CR2中。

操作系统中的页异常处理程序可以检查CR2的内容,从而查出线性地址空间中的哪一页引起本次异常。

CR3用于保存页目录表的其始物理地址。

由于目录是页对齐的,所以仅高20位有效,低12 位保留未用。

向CR3中装入一个新值时,低12位必须为0;但从CR3中取值时,低12位被忽略。

每当用MOV 指令重置CR3的值时,会导致分页机制高速缓冲区的内容无效,用此方法,可以在启用分页机制之前,即把PG 位置1之前,预先刷新分页机制的高速缓存。

C R3寄存器即使在CR0寄存器的PG 位或PE 位为0时也可装入,如在实模式下也可设置CR3,以便进行分页机制的初始化。

在任务切换时,CR3要被改变,但是如果新任务中CR3的值与

原任务中CR3的值相同,那么处理器不刷新分页高速缓存,以便当任务共享也表时有较快的执行速度。

<二>系统地址寄存器

全局描述符表GDT、局部描述符表LDT和中断描述符表IDT等都是保护方式下非常重要的特殊段,它们包含有为段机制所用的重要表格。

为了方便快速地定位这些段,处理器采用一些特殊的寄存器保存这些段的基地址和段界限。

我们把这些特殊的寄存器称为系统地址寄存器。

1.全局描述符表寄存器GDTR

如本文开始处的表格所示,GDTR长48位,其中高32位为基地址,低16位为界限。

由于GDT 不能有GDT本身之内的描述符进行描述定义,所以处理器采用GDTR为GDT这一特殊的系统段提供一个伪描述符。

GDTR给定了GDT,如下图所示。

GDTR中的段界限以字节为单位。

由于段选择子中只有13位作为描述符索引,而每个描述符长8个字节,所以用16位的界限足够。

通常,对于含有N个描述符的描述符表的段界限设为8*N-1。

利用结构类型可定义伪描述符如下:

PDESC STRUC LIMIT DW 0 BASE DD 0 PDESC ENDS 2.局部描述符表寄存器LDTR

局部描述符表寄存器LDTR规定当前任务使用的局部描述符表LDT。

如本文开始处的表格所示,LDTR类似于段寄存器,由程序员可见的16位的寄存器和程序员不可见的高速缓冲寄存器组成。

实际上,每个任务的局部描述符表LDT作为系统的一个特殊段,由一个描述符描述。

而用于描述符LDT的描述符存放在GDT中。

在初始化或任务切换过程中,把描述符对应任务LDT的描述符的选择子装入LDTR,处理器根据装入LDTR可见部分的选择子,从GDT 中取出对应的描述符,并把LDT的基地址、界限和属性等信息保存到LDTR的不可见的高速缓冲寄存器中。

随后对LDT的访问,就可根据保存在高速缓冲寄存器中的有关信息进行合法性检查。

LDTR寄存器包含当前任务的LDT的选择子。

所以,装入到LDTR的选择子必须确定一个位于GDT中的类型为LDT的系统段描述符,也即选择子中的TI位必须是0,而且描述符中的类型字段所表示的类型必须为LDT。

可以用一个空选择子装入LDTR,这表示当前任务没有LDT。

在这种情况下,所有装入到段寄存器的选择子都必须指示GDT中的描述符,也即当前任务涉及的段均由GDT中的描述符来描述。

如果再把一个TI位为1的选择子装入到段寄存器,将引起异常。

3.中断描述符表寄存器IDTR

中断描述符表寄存器IDTR指向中断描述符表IDT。

如本文开始处的表格所示,IDTR长48 位,其中32位的基地址规定IDT的基地址,16位的界限规定IDT的段界限。

由于8038 6只支持256个中断/异常,所以IDT表最大长度是2K,以字节位单位的段界限为7FFH。

ID TR 指示IDT的方式与GDTR指示GDT的方式相同。

4.任务状态段寄存器TR

任务状态段寄存器TR包含指示描述当前任务的任务状态段的描述符选择子,从而规定了当前任务的状态段。

任务状态段的格式在后面的文章中介绍。

如本文开始处的表格所示,TR也有程序员可见和不可见两部分。

当把任务状态段的选择子装入到TR可见部分时,处理器自动把选择子所索引的描述符中的段基地址等信息保存到不可见的高速缓冲寄存器中。

在此之后,对当前任务状态段的访问可快速方便地进行。

装入到TR的选择子不能为空,必须索引位于GDT中的描述符,且描述符的类型必须是TSS。