基于LowK介质QFN55nm铜线键合ILD断层的分析

55 nm金属沟槽通孔一体化刻蚀关键尺寸偏差与图形相关性研究

1 引言

电 常数 材 料 已经 得 到 广 泛 应 用 ,金 属 硬 掩 模 一 体 化

在 集 成 电路 制 造 工 艺 里 , 随 着 器 件 关 键 尺 寸 刻 蚀 (Metal Mard Mask All—in.One Etch)因 为更 好 的

(Critical Dimension,CD )的缩 小 ,金 属铜 和低 介 CD 控制 和 更少 的介 质损 伤 ,成 为 后端 金 属 沟槽 /通 孔

products to make corresponding adjustment in advance.

Key words: lC manufactu ring,metaI hard m ask,AlO ETCH,criticaI dim ension bias. transm ission ratio,trench perim eter

m etal and via etch technology.which solved the traditionaI process inherent In Iow dielectric

layer at the top of the sleek,lOW groove between the dielectric layer thickness thinning and the problem s such as sidew alI Angle sm aller.But the introduction of m etal barrier layer and

Bias and graph strUCtureC0rreIati0nanaIVzed base on production data,the innovative positive c0rreIatiOnc0ncIusiOn proved.w hich will can help US to effectively predict key size of the new

Low-K介质与Cu互连技术在新型布线系统中的应用前景

Low-K介质与Cu互连技术在新型布线系统中的应用前景摘要:集成电路(IC)的快速发展对ULSI布线系统提出了更高的要求。

本文通过对ULSI互连布线系统的分析,在介绍了ULSI新型布线系统的同时,尝试预测互连技术的趋势走向,同时展望Low-K 介质与Cu互连技术在新型布线系统中的应用前景。

关键词:ULSI Low-K介质Cu互连Abstract:The rapid development of IC technology has led to a search for the ULSI routing system.This paper discussed for ULSI interconnect routing system,designed to introduce ULSI interconnect routing system and the trend of interconnect technologies,the future application of the Low-k and Cu interconnect technology are also prospected.Key Words:ULSI Low-K medium Cu interconnect如今,半导体工业飞速发展,人们对于电子产品的功能和体积也提出了进一步的要求,因而,提高集成电路的集成度、应用新式材料和新型布线系统以缩小产品体积、提高产品稳定性势在必行。

根据Moore定律,IC上可容纳的晶体管数目,约每隔18个月便会增加一倍,性能也将提升一倍。

日益减小的导线宽度和间距与日益提升的晶体管密度促使越来越多的人把目光投向了低介电常数材料在ULSI中的应用。

另一方面,金属铝(Al)是芯片中电路互连导线的主要材料,然而,由表1可知,金属铜(Cu)的电阻率比金属铝(Al)低40%左右,且应用Al会产生更明显的互联寄生效应。

电子封装互连无铅钎料及其界面问题研究

电子封装互连无铅钎料及其界面问题研究1. 本文概述随着电子科技的飞速发展,电子封装互连技术在现代电子产品中发挥着至关重要的作用。

钎料作为实现电子器件之间以及器件与基板之间连接的关键材料,其性能直接影响到电子产品的质量和可靠性。

传统的钎料中往往含有铅元素,铅是一种有毒物质,对环境和人体健康造成了严重威胁。

研究和开发无铅钎料已成为电子封装领域的重要课题。

本文旨在探讨无铅钎料在电子封装互连中的应用及其界面问题。

我们将对无铅钎料的发展历程和现状进行概述,分析无铅钎料的主要类型和特点。

我们将深入探讨无铅钎料与电子器件、基板之间的界面问题,包括界面结构、界面反应、界面性能等方面。

本文还将对无铅钎料在电子封装中的可靠性进行评估,以便为实际应用提供指导。

2. 无铅钎料的基本性质无铅钎料是电子封装互连中的关键材料,随着环境保护法规的日益严格和对人类健康的关注,无铅钎料逐渐取代含铅钎料成为行业标准。

无铅钎料的基本性质主要包括以下几个方面:熔点:无铅钎料的熔点通常高于含铅钎料,这意味着在焊接过程中需要更高的温度。

熔点的提高可能会对电子组件的热敏感性造成挑战。

润湿性:润湿性是指钎料在固体基底上的铺展能力,它是评价钎料性能的重要指标。

无铅钎料的润湿性通常不如含铅钎料,这可能会影响焊接质量和可靠性。

机械性能:无铅钎料的机械性能,包括抗拉强度和延展性,通常较含铅钎料有所下降。

这要求在设计和制造过程中对材料选择和工艺参数进行优化。

热稳定性:无铅钎料需要具备良好的热稳定性,以保证在电子设备的使用过程中不会因温度变化而发生性能退化。

热稳定性的提高有助于延长产品的使用寿命。

化学稳定性:无铅钎料在使用过程中应不易发生化学变化,以避免导致焊接接头的腐蚀或断裂。

化学稳定性是确保电子封装长期可靠性的重要因素。

环境适应性:无铅钎料应具有良好的环境适应性,能够在不同的环境条件下保持性能稳定,包括湿度、温度变化和机械振动等。

3. 电子封装互连技术概述电子封装互连技术是电子工程领域中的一个关键环节,它涉及到芯片、元器件、电路板和系统之间的电气连接和物理固定。

Ku、Ka波段高频头PCB用低介电常数、低损耗覆铜板

Key wor ds

Hi g h Fr e qu en c y ; Mi c r o wav e; L o w No i s e Bl oc k ; Cop pe r Cl ad La mi n a t e; T e s t Co mpar i s o n

.

.

2 3. .

基 板材 料

B a s e Ma t e r i a l

印制 电 路 信 息 2 0 1 7 N o . 3

十 多年时 间 ,此类 产 品逐渐 从 国外生 产加 工转 向

对使用 生益科 技高频 基材后 的产 品指标 性能与使 用原来 进 口材 料 的性能指标 对 比数据进 行说 明, 从而 为高频 头产 品设计 工程 师 、P C B 材 料认证 工 程师提供 基材方 面的指 引。

U 刖 舌

卫星 天线 又称 “ 高 频 头 ”,属于 通讯 产 品中 的无线类 产 品,主要 运用 于C 波段 、Ku 波 段 、K a

伴 随着 中 国通 讯行 业 的整体 蓬勃 发展 ,许 多

通 讯 行 业 细 分 的 领 域 也 在 从 以前 能 够 做 出 产 品 的

波 段 卫 星 信 号 接 收 ,主 要 作 用 是 接 受 高 频 信 号 , 将 其 进 行 放 大 ,对 部 分 不 稳 定 的 信 号 进 行 处 理 。

度控 制等 等多 个环 节 都再做 到精 益求精 ,并且做 出的产 品与 国 际上的知 名企业 可 以并 驾齐驱 。生

益 科技 也一直 在努 力将 高频 、高速 类 市场领域 产 品P C B 用基材做到更好 。

芯片半导体制造工艺-第十三章 金属化

多层金属化

层间介质

亚0.25µm CMOS 剖面

金属互连结构

复合金属互连

具有钨塞的通孔互连结构

局部互连(钨) 初始金属接触 在硅中扩散 的有源区

Figure 12.1

• 层间介质(ILD)是绝缘材料,它分离了金属 之间的电连接。ILD一旦被淀积,便被光刻成 图形、刻蚀以便为各金属层之间形成通路。用 金属(通常是钨 W)填充通孔,形成通孔填充 薄膜。在一个芯片上有许多通孔,据估计,一 个300mm2单层芯片上的通孔数达到一千亿个 。在一层ILD中制造通孔的工艺,在芯片上的 每一层都被重复。

金属化对不同金属连接有专门的术语名称。互 连(interconnect)意指由导电材料(铝、多晶硅或 铜)制成的连线将信号传输到芯片的不同部分。互 连也被用做芯片上器件和整个封装之间普通的金属 连接。接触(contact)意指硅芯片内的器件与第一 层金属之间在硅表面的连接。通孔(via)是穿过 各种介质层从某一金属层到毗邻的另一金属层之间 形成电通路的开口。“填充薄膜”是指用金属薄膜 填充通孔,以便在两金属层之间形成电连接。

半导体制造技术

第十三章

金属化

概述

金属化是芯片制造过程中在绝缘介质薄膜上 淀积金属薄膜,通过光刻形成互连金属线和集成 电路的孔填充塞的过程。金属线被夹在两个绝缘 介质层中间形成电整体。高性能的微处理器用金 属线在一个芯片上连接几千万个器件,随着互连 复查性的相应增加,预计将来每个芯片上晶体管 的密度将达到10亿个。

1. 导电率: 要求高导电率,能够传道高电流密度。 2. 黏附性:能够黏附下层衬底,容易与外电路实现电连接 3. 淀积:易于淀积经相对低温处理后具有均匀的结构和组分 4. 刻印图形/平坦化:提供高分辨率的光刻图形 5. 可靠性:经受温度循环变化,相对柔软且有好的延展性 6. 抗腐蚀性:很好的抗腐蚀性,层与层以及下层器件区有最

Low K芯片引线键合工艺计算机仿真与参数优化

参数优化 的有 限元分析 。因此 , 本文 阐述 的用数 值仿

真方法X L wK芯片引线键合日期 : 0 80 —2 2 0 - 10

引线键合通常包 括连续 的两个阶段 :冲击 阶段与

超声波键合 阶段 。 冲击 阶段 , 在 瓷嘴引导金球 以初速度

c ( o s n eo i 1 c n t tv lct , a y)打压在芯片 铝垫上 。之后 即

进入超声波键合 阶段 , 时超声波能量与键合力( o d 此 b n fre 同时作用于瓷嘴并持续 一段 时问使金球与铝垫 oc ) 充分键合 。 超声波键合 阶段较为复杂 , 其中掺 杂了众多 的物理与化学过程 ( 如相变与金属 间化合物的形成 ) ,

合是一个复杂 的机器控制过程 , 不少研究 者已对此作 了研究n , 中包括X C / w- 其  ̄ ul K芯片的引线键合的 o 数值仿 真研究 【 , 1 卜 但还未见 报道针对 引线 键合工 艺

因此对这个过程作准确的数值模拟是不可能的。 对引线

键合 的冲击阶段而言, 以用数值仿真方法准确地加 以 可 研究 , 因为这个 阶段可认为是单一 的机械响应过程。 本 研究首先推导冲击阶段的近似数学模型 , 再对冲击阶段 作有限元分析 , 通过 冲击阶段的形变贡献 比例得 到优化

Co p tt n l o ei ga dP o e s a a ee t iai nf r ieBo dn m ua i a d l n r c s r m trOp i z t r n i g o M n P m o o W

Te hn l g n Lo K W a e s c o o yo w- fr

维普资讯

第 8卷, 2期 第

Vol 8, N o 2

半导体器件中的low-k技术

半导体集成电路中的low-k技术摘要:随着芯片集成度的不断提高,RC时延、串扰噪声和功耗等越来越成为严重的问题。

low-k(低介电常数)技术在这样的背景下产生并逐渐应用到集成电路工艺中。

low-k材料代替SiO2能够进一步提高芯片的速度,但在low-k材料带来巨大技术优势的同时,也带来了一些技术性难题。

研究新型low-k材料并提升其相应的性能,将极大的促进集成电路的发展。

关键词: 集成电路 low-k技术低介电常数多孔材料1 前言随着超大规模集成电路(VeryLarge Scale Integration,VLSI)的高速发展,芯片的集成度不断提高,特征尺寸不断减小。

金属互连的多层布线导致金属导线的电阻、线间电容和层间电容增大,从而使RC延迟时间、串扰噪声和功耗等增加,这些问题成为集成电路进一步发展的制约因素[1,2]。

为了解决上述问题,提高芯片的速度,一方面用采用Cu金属互连线代替Al金属,减少电阻(Cu电阻率为1.75 ×10-8Ω·m,Al电阻率2.83 ×10-8Ω·m)。

另一方面用low-k电介质(k<3)代替SiO2(k=3.9~4.2),降低金属互连层间绝缘层的介电常数k[3,4]。

90 nm工艺要求k = 3.0~2.9;65 nm 工艺要求k = 2.8~2.7;45 nm 工艺要求k = 2.6~2.5[3];32nm及以下工艺要求k值在2.4之下[5]。

因此,low-k 技术已经成为集成电路领域的重点研究内容之一。

2 low-k技术的优势图1 分布电容示意图low-k技术就是就是寻找介电常数(k)较小的材料作为芯片内部电路层之间的绝缘介质ILD(Inter Layer Dielectrics,层间电介质),防止各层电路的相互干扰,以提升芯片的稳定性和工作频率。

集成电路的速度由晶体管的栅延时和信号的传播延时共同决定,使用high-k材料可以有效地降低栅延时。

【2017年整理】什么是低k材料

什么是低k材料low-k是一种“绝缘材料”。

所有材料从导电特性上可分为导体和绝缘体两种类型,导电性能良好的材料称为电的良导体或直接称为导体,不导电的材料称为电的不良导体或者称作绝缘体。

导体中含有许多可以自由移动的电子,而绝缘体中电子被束缚在自身所属的原子核周围,这些电子可以相互交换位置,但是不能到处移动。

绝缘体不能导电,但电场可以在其中存在,并且在电学中起着重要的作用。

因此从电场的角度来看,绝缘体也被称为电介质(dielectric)。

正如导体一样,电介质在电子工程领域有着广泛应用,电容器内的储电材料以及芯片内的绝缘材料等都是电介质。

为了定量分析电介质的电气特性,用介电常数k(permittivity或dielectric constant)来描述电介质的储电能力。

电容C定义为储存的电量Q与电压E的比值,在相同电压下,储存的电量越多,则说明电容器的容量越大。

电容的容量与电容器的结构尺寸及电介质的k值有关(图1),其中作为储电材料的电介质的k 值对电容容量的大小起着关键性作用,制造大容量的电容器时通常是通过选择高k 值的电介质来实现的。

不同电介质的介电常数k 相差很大,真空的k 值为1,在所有材料中最低;空气的k 值为1.0006;橡胶的k值为2.5~3.5;纯净水的k值为81。

工程上根据k值的不同,把电介质分为高k(high-k)电介质和低k(low-k)电介质两类。

介电常数k >3.9 时,判定为high-k;而k≤3.9时则为low-k。

IBM将low-k标准规定为k≤2.8,目前业界大多以2.8作为low-k电介质的k 值上限。

[编辑本段]二、low-k有什么作用?在集成电路内部,由于ILD(Inter Layer Dielectrics,层间电介质)的存在,导线之间就不可避免地存在分布电容,或者称之为寄生电容(图2)。

分布电容不仅影响芯片的速度,也对工作可靠性构成严重威胁。

从电容器容量计算公式中我们可以看出,在结构不变的情况下,减少电介质的k值,可以减小电容的容量。

铜接触片断裂分析计划

铜接触片断裂分析计划下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by the editor. I hope that after you download them, they can help yousolve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you!In addition, our shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts,other materials and so on, want to know different data formats and writing methods, please pay attention!铜接触片在机电设备中扮演着至关重要的角色,其质量问题直接关系到设备的正常运转和安全性。

铜表面钨涂层对激光焊接焊缝裂纹的影响研究

管理及其他M anagement and other 铜表面钨涂层对激光焊接焊缝裂纹的影响研究李 安摘要:在传统焊接检测方法中,并未考虑铜表面钨涂层对电磁超声信号传递效果的差异,导致焊接缺陷的检测结果存在较大误差,为此,提出铜表面钨涂层焊接中的接焊缝裂纹检测技术研究。

分别沿0°方向和90°方向对待检测焊接部位进行超声扫描,并结合焊接母材的声阻抗系数,对电磁超声信号激发频率与波数进行适应性设置,在对采集到的信号数据进行处理时,根据超声波在非均匀介质中的衍射效应,首先利用回波衍射法计算得到缺陷的深度,再结合扫描点位与信号峰值之间的关系,计算得到缺陷的位置信息。

测试结果表明,设计的接焊缝裂纹检测技术可以实现对铜表面钨涂层焊接缺陷的准确检测,相对误差稳定在0.06mm以内,可为激光焊接质量检测工作的开展提供有效帮助。

关键词:铜表面钨涂层焊接;接焊缝裂纹检测技术;超声扫描;激发频率;衍射效应;信号峰值随着近年来接焊缝裂纹检测技术的不断发展,其凭借超声波在试件中的传播特性,实现了利用超声波检测仪的声源对试件内部具体情况进行探测的目的。

在具体的实施过程中,只需要按特定方式将超声波发射至目标检测位置,借助声波在介质传播过程表现出的变化,即可实现通过表征信息判断试件内部状态的效果。

但是值得注意的是,在不连续声阻抗介质交界面上,声波会出现不同程度的反射,此时的信号即为超声回波信号,只有完整获取超声回波信号,才能够切实保障后续超声换能器的处理结构能够真实反映构件的实际情况。

无论是信号的衰减系数、传播速度、声强,还是信号的频率,都在一定程度上反馈着构件的内部状态信息。

由于在铜表面钨涂层焊接过程中,裂纹、未熔合等质量缺陷,采用抽检的方式无法得到检验目的,因此,接焊缝裂纹检测技术也开始在该领域得到进一步应用。

为了确保检测结果的可靠性,本文针对铜表面钨涂层焊接进行了接焊缝裂纹检测技术研究,并实现了对焊接件中缺陷的位置、大小、形状和发展程度的准确检测。

55nm铜互连工艺电迁移性能的优化的开题报告

55nm铜互连工艺电迁移性能的优化的开题报告一、选题的背景和意义随着电子技术的不断发展,电子器件的制作工艺也在不断更新。

近年来,55nm铜互连工艺越来越普遍地被应用于集成电路芯片的制造过程中。

但是,这种工艺在使用过程中存在电迁移现象。

电迁移是指电子在金属导线内不断移动,由于电子激活了钝化层,导致导线长度短路或断路,从而导致器件的性能下降或故障。

因此,研究优化55nm铜互连工艺的电迁移性能,对于提高集成电路芯片的稳定性和可靠性具有重要的意义。

二、前沿性和研究现状目前,有许多研究工作致力于优化铜互连工艺的电迁移性能。

在工艺方面,有研究将基板温度降低可以有效地降低铜互连中的电迁移现象。

在材料方面,有研究表明,使用添加剂的铜电极可以有效地提高电线的可靠性。

此外,使用高硬度的介电材料可降低应力并延长器件寿命,同时用改进的电联接方法可降低电线压力。

三、研究方法和技术路线本研究将采用实验室制作的55nm铜互连工艺试片,通过电学测试和扫描电子显微镜技术来分析电迁移现象,并研究优化该工艺的电迁移性能。

实验中将使用不同的电流密度进行测试,来研究电流密度对电迁移的影响,在此基础上,将研究各种方法来降低电迁移现象,例如控制基板温度、添加剂的铜电极等。

四、预期成果和意义通过本研究,我们预期获得以下的成果:1.了解55nm铜互连工艺的电迁移现象及其机理。

2.研究不同电流密度条件下的电迁移现象和影响因素,分析结构参数和过程参数对电迁移的影响。

3.通过实验探索不同的方法来优化55nm铜互连工艺的电迁移性能。

最终的目标是探讨一系列可行的优化方案,并为55nm铜互连工艺的电迁移性能提供一定的理论和实践依据。

该工作对于提高芯片的性能和可靠性,降低器件的制造成本具有重要的意义。

基于蛋清栅介质的超低压双电层薄膜晶体管

基于蛋清栅介质的超低压双电层薄膜晶体管佚名【摘要】新一代环保、生物兼容性电子功能器件受到了广泛关注.本文采用具有高质子导电特性的天然鸡蛋清作为耦合电解质膜制备双电层薄膜晶体管,该薄膜晶体管以氧化铟锡导电玻璃为衬底和底电极,以旋涂法制备的鸡蛋清为栅介质,以磁控溅射沉积的氧化铟锌为沟道和源漏电极.实验结果表明,这种基于鸡蛋清的栅介质具有良好的绝缘性,并能在其与沟道界面处形成巨大的双电层电容,从而使得该类晶体管具有超低工作电压(1.5 V)、低亚阈值(164 mV/dec)、大电流开关比(2.4×106)和较高的饱和区场效应迁移率(38.01 cm2/(V·s)).这种以天然鸡蛋清为栅介质的超低压双电层TFTs有望应用于新型生物电子器件及低能耗便携式电子产品.【期刊名称】《物理学报》【年(卷),期】2018(067)023【总页数】6页(P206-211)【关键词】鸡蛋清;双电层;薄膜晶体管;生物材料【正文语种】中文1 引言信息时代,电子产品高速更新换代所产生的大量电子废弃物,已经严重污染环境并将制约社会的可持续发展,因此在电子器件领域,需要更进一步的研究来解决这类问题[1,2].近年来,新一代环保、生物兼容性电子功能器件受到了广泛的关注[3−6].其中利用可降解的生物材料制备电子器件,对于可穿戴及一次性的电子产品来说是极具应用前景的[7,8].Hu等[9]采用海藻酸钠(SA)作为电解制膜制备了双面内栅结构的AI-Zn-O神经型晶体管.Wu和Lin[10]利用芦苇膜作为嵌入ZnO纳米晶体管的间隔层,制备了一种柔性紫外探测器.Wang等[11]利用微胶囊制备了高灵敏度的电子皮肤传感器.Jin等[12]利用甲壳素自组装形成了透明纸,并论述了其作为柔性有机发光二极管基板的应用.本文采用天然鸡蛋清作为栅介质制备薄膜晶体管(thin-f i lm transistors,TFTs).TFTs是一类重要的场效应晶体管,已在平板显示、新型传感器、非易失性存储器等领域得到了广泛的应用[13−15].而天然鸡蛋清可以从鸡蛋中提取,方法简单且成本廉价,其介电常数为5.3—6.1[16],远大于传统的有机介电层(如聚甲基丙烯酸甲酯、聚苯乙烯).因此,以鸡蛋清为栅介质的TFTs将具有良好的电流驱动能力.另外,与传统的场效应晶体管静电耦合机理不同,具有双电层效应的晶体管主要依靠电解质中的离子迁移和极化实现耦合效应,具有丰富的电化学过程,因此非常适合于神经仿生等领域.Xie等[17]利用聚乙烯醇作为栅极制备了双电层MoS2晶体管,并成功模拟了视觉神经元的基本形态行为.本文以旋涂法制备的鸡蛋清为栅介质,然后利用磁控溅射方法,在栅介质上通过硬掩模板同时沉积氧化铟锌(IZO)源、漏电极和沟道,其中IZO沟道层是在沉积源、漏电极的同时由于绕射作用而在两电极之间形成的.结果表明,栅介质层与沟道层界面处能够形成巨大的双电层电容,以鸡蛋清为栅介质的TFTs具有超低工作电压(1.5 V)、低亚阈值(164 mV/dec)和较高饱和区场效应迁移率(38.01 cm2/(V·s)).2 实验如图1所示,该器件以氧化铟锡(ITO)导电玻璃为衬底和底电极,将方阻为15 Ω/?的ITO玻璃切割成2.5 cm×2.5 cm的方形片.将鸡蛋打到图2(a)碗中,用不锈钢网对蛋黄进行分离,把鸡蛋清提取出来不做任何处理地装入图2(b)玻璃瓶里.首先,用丙酮、乙醇、甲醇、去离子水对ITO玻璃表面进行逐次清洗,用高纯氮气干燥,然后将厚度为1.0µm的鸡蛋清在3000 r/min的ITO玻璃基片上旋转,并在空气中干燥形成固体膜.然后,在压强为0.5 Pa的Ar气体环境下,在室温中采用磁控溅射方法,在栅介质上通过硬掩模板同时沉积了30 nm厚IZO沟道和100 nm厚IZO 源、漏电极,其中IZO沟道层是在沉积源、漏电极的同时由于绕射作用而在两电极之间形成的,如图2(c)所示.TFTs的沟道长度(L)和沟道宽度(W)分别为80µm和1 mm.为了测量漏电流密度和电化学阻抗谱(EIS),还制备了电极尺寸为100µm×100µm的ITO/蛋白质/IZO三明治结构.实验射频电源功率、AR流量控制分别为100 W,30 sccm.最后,在室温常压下,利用Solartron1260 A阻抗分析仪对三明治结构(ITO/蛋白质/IZO)的EIS进行了表征,同时利用Keithley2612B/2636B源表系统测量了其电学特性.图1 以鸡蛋清为栅介质的TFTs的器件结构示意图Fig.1 .Structure diagram of the chicken albumengated TFTs.图2 (a)将鸡蛋打破至碗中;(b)将鸡蛋清分离;(c)IZO沉积示意流程图Fig.2 .(a)Break an egg into a bowl;(b)separate the chicken albumen;(c)IZO deposition f l owchart.3 结果与讨论鸡蛋清中的鸡蛋白由90%水和10%蛋白质(主要包括白蛋白和少量的黏蛋白和球蛋白)组成.鸡蛋白中含有多种亲水官能团,如—COOH,—NH2,—SH和—OH21等,因此具有良好的水溶性、乳化性和离子导电性;同时根据Darvishi等[18]的证明,鸡蛋白的离子导电性也与其所含的水有着密切的关系,水的存在促进了质子的运动.当蛋白质加热到80◦C以上时,蛋白质内氨基酸结构会发生不可逆反应,蛋白质分子就从原来有序的卷曲紧密结构变为无序的松散伸展状结构,即变性,这将使得蛋白质的离子导电性和靠近栅极的等效电容大大降低[19,20].而在本文实验中,良好的TFTs必须保持一定的亲水性和离子导电性,因此旋涂的鸡蛋清只在空气中干燥,不经过任何加热处理.图3 不同交流电位下鸡蛋清薄膜的(a)电容与频率和(b)相角与频率的关系Fig.3 .(a)Capacitance-frequency curves and(b)phase angle-frequency curves of the chicken albumen f i lm under dif f erent AC potentials.图3(a)为鸡蛋清薄膜的电容-频率曲线,从图中可以看出,当交流电位从0.2 V变化到2 V,频率为160 Hz以上时,曲线几乎重合,这主要是因为在高频率,质子没有足够的时间迁移到界面聚集.单位面积电容随着频率的减小而增加,在频率为1.0 Hz时达到最大值(>1.0µF/cm2),这主要是因为在低频区域,质子迁移形成巨大的双电层电容.为了解释大电容形成的原因,我们从化学层面进一步探究,鸡蛋白中的蛋白质绝大部分(约75%)是解离常数(pKa)值大于4.7的白蛋白[21].H2O可以与白蛋白中的氨基酸残基相互作用,因此可以在水合蛋白中产生移动离子.氨基酸与水分子相互作用的同时解离生成带负电的(CH2)2—COO−侧链和H+(H3O+)离子[22],因此蛋清膜中的离子导电现象主要原因是质子的迁移,换句话说,这里的蛋清膜是质子传导膜.在此需要说明的是,吸水也会产生大量的质子传导氢键链,这可以作为质子迁移的质子线,质子遵循Grotthum机制沿着氢键网络移动[23],在蛋清膜中,大量的移动质子是高质子导电特性的主要原因.当给栅极外加正向偏压时,H+通过间隙向栅介质和沟道层界面移动,在沟道层内产生大量的相反电荷,形成双电层,从而获得大电容.当给定电压从0.2 V增至2 V,单位面积电容也从1.07µF/cm2增至2.52µF/cm2,这是因为在更高的电压下,更多的质子将迁移到界面区域,从而形成更大的界面电容.为了进一步阐述以鸡蛋清为栅介质在不同频率区间对晶体管的影响,本文以相角-频率来表示(图3(b)),相角是频率的函数.当相位角为−90◦时,是理想的电容器;当相位角为0◦时,是理想的电阻器[24].因此,从图3(b)可以看出,当频率大于300 kHz(θ> −45◦)时,表现出更多的电阻特性,这是因为在高频情况下,质子没有足够的响应时间迁移到界面区域,不能对界面电容做出贡献,主要的极化机理为形成离子弛豫.当频率低于300 kHz(θ<−45◦)时,表现出更多的电容特性,这是因为在低频状态下,质子有足够的响应时间迁移到界面上,从而导致了界面大电容的形成,主要的极化机理为双电层的形成.当给定更高的交流电压时(>2.0 V),自由移动的质子穿过蛋白质/IZO表面,发生可逆电化学过程,表面氢化过程导致IZO电导增加,也会表现出更多的电阻特性.当频率小于160 Hz时,曲线开始出现分支,出现分支的原因可以归结于界面超大双电层电容的形成.图4(a)为该晶体管的输出特性曲线(Ids-Vds).Vds由0 V扫描至1.5 V,同时栅压Vgs由0 V扫描至1.0 V,每次增加0.2 V.由图4(a)可知,在Vds较高的时,该器件显示出了良好的电流饱和特性;而在Vds较低时,Ids也具有很好的线性特性,器件具有良好的欧姆接触.当给定 Vds=1.5 V和Vgs=1.0 V下具有较高的饱和电流 (约600µA).以鸡蛋清为栅介质和沟道界面处的双电层效应,形成了较大电容,因此本器件显示出了超低的工作电压(1.5 V).图4(b)为该晶体管的转移特性曲线(Ids-Vgs)及漏电流曲线.在Vds为1 V,栅压Vgs由−1.5 V扫描至1.5 V.在1.5 V偏压下,漏电流大小约为3 nA,低于离子液体和聚合物电解质[25,26],这表明基于鸡蛋清的栅介质具有较好的绝缘特性,能够保证TFTs的正常工作.由图4(b)可知,器件的回滞较小,具有较高的电流开关比(2.4×106),亚阈值斜率可由公式S=dVgs/d(lgIds)计算得到,S=164 mV/dec,器件的阈值电压Vth可以通过-Vgs曲线的切线在横轴的截距得到,由图4(b)可知Vth为−0.2 V,因而饱和区(Vds>Vgs−Vth)场效应迁移率可以根据(1)式获得:式中L=80µm;W=1 mm;Ci为栅介质单位面积电容;计算得到饱和区场效应迁移率µFE ≈ 38.01 cm2/(V·s).图5(a)为该晶体管的脉冲响应曲线,在Vds外加电压1.5 V,Vgs外加−1.5 V和1.5 V的脉冲测试信号下,器件维持了稳定的电流开关比(>106),并且没有明显的电流损失,表明了基于鸡蛋清的栅介质和IZO沟道层之间没有发生明显的电化学现象.图5(b)为该器件转移曲线随时间的变化趋势,测试过程中器件一直暴露在空气中.由图5(b)可以看出,经过1 d后,器件的开启电压、开关比等电学特性只发生了较小的变化.未来通过封装,该器件的环境稳定性还能得到进一步的提升.图4 (a)晶体管的Ids-Vds输出特性曲线;(b)晶体管的Ids-Vgs转移特性以及漏电流曲线Fig.4 .(a)Output characteristic curves of transistor;(b)transfer characteristic curves and leakage current curves of transistor.图5 (a)以鸡蛋清为栅介质的TFTs脉冲响应曲线;(b)器件转移曲线随时间的变化趋势Fig.5 .(a)Pulse response curve of the chicken albumen-gatedTFTs;(b)evolution of transfer characteristics as a function of time.4 结论本文以天然鸡蛋清为栅介质,制备出超低压双电层TFTs.鸡蛋清薄膜中有着大量的可自由移动的质子,因此在正向偏压下,部分质子将迁移到栅介质和沟道的界面区域,形成双电层效应,产生巨大的界面电容.基于双电层电容耦合,该器件具有超低的工作电压(1.5 V)、低亚阈值(164 mV/dec)、较高的饱和区场效应迁移率(38.01cm2/(V·s))以及高电流开关比(2.4×106).天然鸡蛋清具有环保、易于降解等优点,因此以鸡蛋清为栅介质的TFTs在新一代的环保、生物兼容性电子器件领域将具有广泛的应用前景.参考文献【相关文献】[1]Siegel A C,Phillips S T,Wiley B J,Whitesides G M 2009 Lab Chip 9 2775[2]Martins R,Barquinha P,Pereira L,Correia N,Goncalo G,Ferreira I,Fortunato E 2008 Appl.Phys.Lett.93 203501[3]Ordinario D D,Phan L,Walkup W G,Jocson J M,Karshalev E,Hüsken N,Gorodetsky A A 2014 Nat.Chem.6 596[4]Ratner B D,Bryant S J 2004 Annu.Rev.Biomed.Eng.6 41[5]Willner I 2002 Science 298 2407[6]Yu X,Shou W,Mahajan B K,Huang X,Pan H 2018 Adv.Mater.30 28[7]Irimia-Vladu M,Sariciftci N S,Bauer S 2011 J.Mater.Chem.21 1350[8]Kim D H,Kim Y S,Amsden J,Panilaitis B,Kaplan D L,Omenetto F G,Zakin M R,Rogers J A 2009 Appl.Phys.Lett.95 133701[9]Hu W,Jiang J,Xie D D,Wang S T,Bi K,Duan H,Yang J,He J 2018 Nanoscale 10 14893[10]Wu J,Lin L Y 2015 Adv.Opt.Mater.3 1530[11]Wang L,Jackman J A,Tan E L,Park J H,Potroz M G,Hwang E T,Cho N J 2017 Nano Energy 36 38[12]Jin J,Lee D,Im H G,Han Y C,Jeong E G,Rolandi M,Choi K C,Bae B S 2016 Adv.Mater.28 5169[13]Street R A 2009 Adv.Mater.21 2007[14]Fortunato E M C,Barquinha P M C,Pimentel A C M B G,Gonc A M F,Marques A JS,Pereira L M N,Martins R F P 2005 Adv.Mater.17 590[15]Zhao K S,Xuan R J,Han X,Zhang G M 2012 Acta Phys.Sin.61 197201(in Chinese)[赵孔胜,轩瑞杰,韩笑,张耕铭2012物理学报61 197201][16]Lu Y J,Fujii M,Kanai H 1998 Int.J.Food Sci.Technol.33 393[17]Xie D D,Jiang J,Hu W N,He Y L,Yang J L,He J,Gao Y L,Wan Q 2018 ACSAppl.Mater.Interfaces 10 25943[18]Darvishi H,Khoshtaghaza M,Zarein M,Azadbakht M 2012 Agric.Eng.Int.:CIGR Journal 14 224[19]Sela M,Lifson S 1959 Biochim.Biophys.Acta 36 471[20]Chang J W,Wang C G,Huang C Y,Tsai T D,Guo T F,Wen T C 2011 Adv.Mater.23 4077[21]Mine Y 1995 Trends Food Sci.Tech.6 225[22]Ma C,Holme J 1982 J.Food Sci.47 1454[23]Zhong C,Deng Y,Roudsari A F,Kapetanovic A,Anantram M P,Rolandi M 2011mun.2 476[24]Jiang J,Sun J,Lu A,Wan Q 2011 IEEE Electron Device Lett.58 547[25]Cho J H,Lee J,Xia Y,Kim B,He Y,Renn M J,Lodge T P,Frisbie C D 2008 Nat.Mater.7 900[26]Lee J,Panzer M J,He Y,Lodge T P,Frisbie C D 2007 J.Am.Chem.Soc.129 4532。

Low-K芯片的激光开槽工艺质量稳定性控制

Low-K芯片的激光开槽工艺质量稳定性控制

李曼;彭川;冯晨;侯煜;宋琦;石海燕;王秋明;张紫辰

【期刊名称】《电子产品可靠性与环境试验》

【年(卷),期】2022(40)4

【摘要】基于低介电常数(Low-K)材料覆盖的晶圆加工需求和激光开槽工艺质量控制特点,开展Low-K材料激光开槽工艺技术质量稳定性研究。

以开槽宽度、槽壁夹角、开槽深度和底部波动距离表征槽型形貌特征,定义了激光开槽工艺质量评价准则。

针对扫描速度、激光频率、单脉冲能量、扫描次数和脉宽5个因素以正交试验法开展Low-K芯片激光开槽槽型质量波动分析,得出影响槽型质量波动的主次顺序依次为激光频率>单脉冲能量>扫描速度>扫描次数>脉宽。

提出了一套评定系统用于识别工艺质量最优参数,建立激光开槽工艺质量稳定性控制策略模型。

经实例验证控制策略模型具备可行性,对Low-K材料激光开槽设备在工艺实施过程中的质量稳定性控制提供了有效的技术途径。

【总页数】7页(P17-23)

【作者】李曼;彭川;冯晨;侯煜;宋琦;石海燕;王秋明;张紫辰

【作者单位】中国科学院微电子研究所;空军装备部驻芜湖地区军事代表室;中国电子技术标准化研究院

【正文语种】中文

【中图分类】TN305.1

【相关文献】

1.结合工程实例谈玻璃钢夹砂管开槽埋管施工工艺与质量控制要点

2.6DM3灰铸铁缸体材料质量稳定性的控制工艺

3.红花注射液质量稳定性的生产工艺控制研究

4.无源RFID标签芯片贴装工艺分析和质量控制

因版权原因,仅展示原文概要,查看原文内容请购买。

K模断层检定

铝合金含渣量测定——K模断口检查法

断口检查法是用肉眼或低倍放大镜检查铝硅合金锭断口上有无夹杂物。

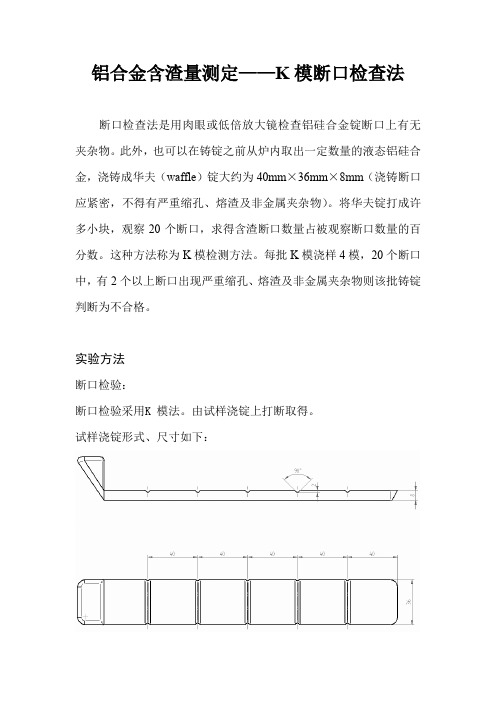

此外,也可以在铸锭之前从炉内取出一定数量的液态铝硅合金,浇铸成华夫(waffle)锭大约为40mm×36mm×8mm(浇铸断口应紧密,不得有严重缩孔、熔渣及非金属夹杂物)。

将华夫锭打成许多小块,观察20个断口,求得含渣断口数量占被观察断口数量的百分数。

这种方法称为K模检测方法。

每批K模浇样4模,20个断口中,有2个以上断口出现严重缩孔、熔渣及非金属夹杂物则该批铸锭判断为不合格。

实验方法

断口检验:

断口检验采用K 模法。

由试样浇锭上打断取得。

试样浇锭形式、尺寸如下:

断口组织用肉眼进行检查。

试样浇锭断口应致密,不得有严重缩孔、熔渣及非金属夹杂物。

每批铸锭,K 模浇样,查20 个断口中,超过2 个

以上断口出现严重缩孔、熔渣及非金属夹杂物则该批铸锭判定为不合格

检验规则

检验方法:目测

断口检验:每炉一次。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2 0 1 3 年4 月

光 电技 术应 用

E L ECTRO— OP I C T ECHNOL0GY AP P L I CATI ON

V01 . 2 8. NO. 2

Ap r i l , 2 01 3

・Байду номын сангаас

光 电器 件 与材 料 ・

基于 L o w K介 质 QF N 5 5 n m铜 线键 合 I L D断层 的分 析

差的层 间粘附性 , 加上 c u比 A u 具有 更高 的机 械强度 和硬度 , 并且 需要 使用更 严谨 的引线 键合 的参数 ( 例

如较 高 的力 , 更 高 的 功率 , 较 高 的温 度 ) 。加 上 电子

打火后 的铜 焊球 表面容 易氧 化 , 更 加增强 了其 硬度 , 在 以上 因素的共 同作用 下 , 焊盘容 易形成 成坑 , 对于

s t a n t ( L o w K) a r e i n t r o d u c e d . Du in r g c o p p e r wi r e b o n d i n g , I LD c r a c k l a y e r o f t h e d i e l e c t i r c wi t h l o w K a n d o p t i mi —

z a t i o n p r o c e s s re a a n a l y z e d.Co ns i d e in r g t e c h n i q u e s s t a bi l i t y ,o p t i mi z a t i o n b o n d i n g p a r a me t e r s re a a d o pt e d t o i m— p r o v e t h e d e s i g n s ho r t c o mi n gs o f c hi ps d u ing r o p t i mi z a t i o n p r o c e s s . Af t e r a s e r i e s o f t e c h n i q u e s o p t i mi z a t i o n a n d pl e n t y o f e x pe im e r n t d e s i g n s , t h e i n m i mu m r a t i o o f I LD c r a c k l a y e r h a s b e e n a c h i e v e d .

中 图分 类 号: T N 4 9 5 文献 标 识码 : A 文章 编 号 : 1 6 7 3 — 1 2 5 5 ( 2 0 1 3 ) 一 0 2 — 0 0 4 4 — 0 7

A n a l y s i s o f I L D C r a c k L a y e r o f QF N 5 5 a m C o p p e r Wi r e

张金 辉 , 程 秀 兰

( 上海交通大学微 电子学院, 上海 2 0 1 4 0 6 )

摘

要: 主要介绍了低 介电常数介质芯片层间介质层 的分类 , 特别是对铜线键合过程中低介 电常数介质层间介质 断层方面

的分析 , 以及铜线键合过程中如何优化工艺。在工 艺优化过程中主要采用 了键合参数的优化来 改善芯片本身存在 的设计缺陷, 这主要是从工艺稳定性方面考虑。通过一系列工艺的优化 , 通过大量实验设计 , 获得了尽可能少的层间介质断层缺 陷。 关键词: 低介电常数 ; 层间介质; 铜线键合 ; 实验设计

Ke y wo r d s : l o w d i e l e c t r i c c o n s t a n t ( L o w K) ; i n n e r l a y e r d i e l e c t r i c( I L D) ; c o p p e r wi r e b o n d i n g ; e x p e ime r n t d e —

s i g n

近几 年来 许多 国 内外 论文 研究 C u 和P d C u 键合 的优点 , 和金 线键 合 的 比较 , 最具 明显 的意义 在于 它 的低 成 本 , 更好 的 电性 能 、 热 电学效 应 、 可 靠性 。从 9 0 n m以下集 成 电路 制 造工 艺 开始 层 间结 构都 采 用 L o w K介质 和铜 金属层 , 并在介 电和铜之 间添加氮 化

Bo ndi ng Ba s e d o n Lo w K Di e l e c t r i c

Z HANG J i n - h u i , C HENG Xi u — l a n f S c h o o l o f Mi c r o e l e c t r o n i c s , S h a n g h a i J i a o t o n g U n i v e r s i t y , S h a n g h a i 2 0 1 4 0 6 , C h i n a J

Ab s t r a c t : Th e c l a s s i f i c a t i o n s o f i n n e r l a y e r d i e l e c t r i c( I L D)l a y e r s o f d i e l e c t ic r c h i p s wi t h l o w d i e l e c t r i c c o n —