STUB08C中文资料

74ls08

74LS08介绍74LS08 是一种逻辑门芯片,属于 TTL(Transistor-Transistor Logic)系列。

它由四个 2 输入 AND 门组成,是一种四输入 AND 门。

特点74LS08 具有以下特点:•输入端电压范围:0V 到 5V•输出端电压范围:0V 到 5V•输入端的阻抗为10kΩ•输出能力为 8mA•工作温度范围为 -55°C 到 125°C•供电电压为 5V引脚说明74LS08 具有 14 个引脚,它们的功能如下:•Pin 1: 输入 A1•Pin 2: 输入 B1•Pin 3: 输出 Y1•Pin 4: 输入 A2•Pin 5: 输入 B2•Pin 6: 输出 Y2•Pin 7: GND(地)•Pin 8: 输入 A3•Pin 9: 输入 B3•Pin 10: 输出 Y3•Pin 11: 输入 A4•Pin 12: 输入 B4•Pin 13: 输出 Y4•Pin 14: VCC(电源)使用示例以下是一个使用 74LS08 的简单逻辑电路示例,它通过将两个 AND 门的输出连接到第三个 AND 门的输入上,实现了一个 4 个逻辑输入的 AND 逻辑。

+---|B1| +---|B3|| +---|B2| |+-|-+--+ 74LS08| |+-|-+--+ 74LS08| |+---|A1| +---|A3|| +---|B4| |+-|-+--+ 74LS08| |+-|-+--+| |+---|A4| +---|A2|+-|-+–+ 74LS08 | | +—|Y1 | +—|Y3| +—|Y2```•输入 A1、A2、A3、A4 分别连接到逻辑电路的四个逻辑输入•输入 B1、B2、B3、B4 分别连接到逻辑电路的四个逻辑输入•输出 Y1、Y2、Y3、Y4 分别作为逻辑电路的输出以上逻辑电路即为一个 4 个输入的 AND 逻辑电路,只有当所有输入均为高电平(5V)时,输出才会为高电平(5V),否则输出为低电平(0V)。

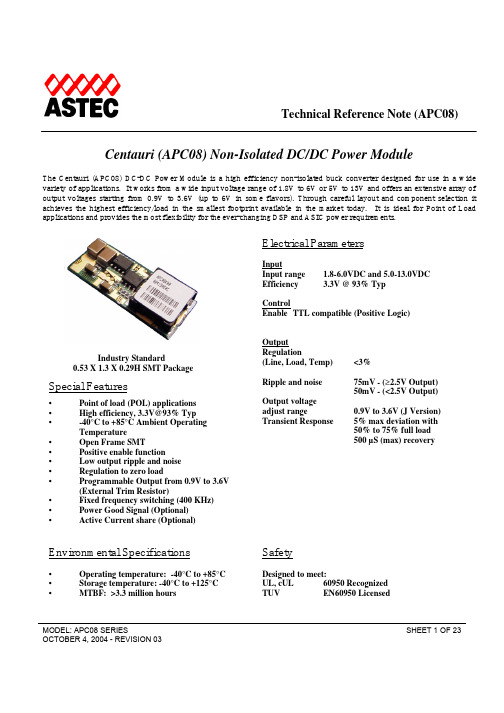

APC08K08-W中文资料

Options (suffix): "-9" = Trim "-9MA" = Trim with Power Good and Active Current Share "-J" = Jedec tray-type packaging “W” = Improved Loop Bandwidth / Transient Response (only for APC08x03 series)

MODEL: APC08 SERIES OCTOBER 4, 2004 - REVISION 03 SHEET 3 OF 23

元器件交易网

ቤተ መጻሕፍቲ ባይዱ

Technical Reference Note (APC08)

Electrical Specifications (continued)

MODEL: APC08 SERIES OCTOBER 4, 2004 - REVISION 03

SHEET 2 OF 23

元器件交易网

Technical Reference Note (APC08)

Electrical Specifications

STANDARD TEST CONDITION on a single unit, unless otherwise specified. T A: 25°C (Ambient Air) Vin (P1): APC08x03 +1.8V to +6.0V APC08x08 +5.0V to +13V Enable (P5): Open Vo (P2): Connect to load Gnd (P3): Return for Vin and Vo Trim (P4): Open PGood (P6): Open P (P7): Open ABSOLUTE MAXIMUM RATINGS Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. Functional operation of the device is not implied at these or in any other conditions in excess of those given in the operational sections of the specs. Exposure to absolute maximum ratings for extended periods can adversely affect device reliability. Parameter Input Voltage Continuous Transient (100ms) Continuous Transient (100ms) Operating Temperature Storage Temperature Operating Humidity Device 03 03 08 08 All All All Symbol VIN VIN,trans VIN VIN,trans TA TSTG Min 1.8 5.0 -40 -40 Typ Max 6.0 7.0 13.0 14.0 85 125 85 Unit Vdc Vdc Vdc Vdc ºC ºC %

MT5C1008C-20中文资料

MARKING

-12 (contact factory) -15 -20 -25 -35 -45 -55* -70*

• Package(s)• Ceramic DIP (400 mil) Ceramic DIP (600 mil) Ceramic LCC Ceramic LCC Ceramic Flatpack Ceramic SOJ Ceramic SOJ

Input High (Logic 1) Voltage

VIH

2.2 VCC+0.5

V

1

Input Low (Logic 0) Voltage

VIL

-0.5

0.8

V

1, 2

Input Leakage Current Output Leakage Current

0V<VIN<VCC

ILI

-10

10

µA

32-Pin Flat Pack (F)

32-Pin LCC (EC) 32-Pin SOJ (DCJ)

NC

1

A16

2

A14

3

A12

4

A7

5

A6

6

A5

7

A4

8

A3

9

A2

10

A1

11

A0

12

DQ1

13

DQ2

14

DQ3

15

VSS

16

32

VCC

31

A15

30

CE2

29

WE\

28

A13

27

A8

26

A9

25

A11

*Stresses at or greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods will affect reliability. Refer to page 17 of this datasheet for a technical note on this subject. ** Junction temperature depends upon package type, cycle time, loading, ambient temperature and airflow, and humidity.

第2章 Freescale HC(S)08系列单片机概述

第2章Freescale HC08/S08/RS08 MCU概述Freescale的08系列单片机由于其稳定性高、开发周期短、成本低、型号多种多样、兼容性好而被广泛应用。

本章概要介绍08系列单片机的类型、基本结构,并从总体上阐述其性能特点。

主要内容有:在介绍08系列单片机的命名规则和资源状况的基础上,分别以MC908GP32、MC9S08GB60及MC9RS08KA2为例讲述HC08系列、HCS08系列及RS08系列单片机的基本结构和特点。

了解这些基本知识,不仅可以为实际开发应用中的单片机选型提供参考,也对后续章节的学习有很大的帮助。

本书以GP32为主要芯片阐述嵌入式系统基本硬件与软件原理,2.2节讨论的GP32引脚功能、硬件最小系统及GP32的存储器框图是重点掌握的内容。

硬件最小系统是芯片运行的基本条件,应该对此有清晰的理解。

对于GP32不具备的功能,本书将使用其他芯片进行阐述,但编程语言体系是相同的。

2.1 08系列单片机简介目前,Freescale的08系列单片机主要有HC08、HCS08和RS08三种类型。

HC08是1999年开始推出的产品,种类也比较多,针对不同场合的应用都可以选到合适的型号。

HCS08是2004年左右推出的8位MCU,资源丰富,功耗低,性价比很高,是08系列单片机的发展趋势。

HC08与HCS08的最大区别是调试方法不同与最高频率的变化。

RS08是HCS08架构的简化版本,于2006年推出,其内核体积比传统的内核小30%,带有精简指令集,满足用户对体积更小、更加经济高效的解决方案的需求。

RAM及Flash 空间大小差异、封装形式不同、温度范围不同、频率不同、I/O资源差异等形成了不同型号,为嵌入式应用产品的开发提供了丰富的选型。

2.1.1 Freescale单片机的命名规则Freescale单片机的型号庞大,但同一系列的CPU是相同的,也就是说具有相同的指令系统,多种型号只是为了适用于不同的场合。

SA8000-2008(CN)

SA 8000:2008中文版SA8000系社会责任国际之注册商标关于本标准这是SA8000的第三版.SA8000是供第三方认证体系所用的统一,可供核查的标准.它制定了雇主在工作场所方面须符合的自愿性要求,包括工人权利,工作环境以及管理体系.该标准的规范性原则基于国家法律,国际人权以及ILO国际劳工组织的规定.SA8000标准可以和SA8000指导文件一起用于评审一个工作场所是否符合这些标准.SA8000的指导文件用于SA8000标准及其实施,并提供检验符合方法的示例.核查人员以及欲获认证的公司可将其当作手册使用.指导文件可以从SAI花很少的费用获得.SAI社会责任国际15West 44th Street6th FloorNew York, NY 10036USA电话: +1-212-684-1414传真: +1-212-684-1515电邮: info@网址: @ SAI 2008未经SAI书面认可不得翻印.目录I.目的与范围II. 规范性原则及其解释III. 定义1.公司定义2.员工定义3.工人定义4.供应商/分包商定义5.下级供应商定义6.纠正和预防行动定义7.利益相关方定义8.儿童定义9.青少年定义10.童工定义11.强迫和强制劳动12.非法雇用定义13.救济儿童定义14.家庭工人定义15.SA8000工人代表定义16.管理代表定义17.工人组织定义18.集体谈判定义IV.社会责任要求1.童工2.强迫和强制性劳动3.健康与安全4.结社自由及集体谈判权利5.歧视6.惩戒性措施7.工作时间8.报酬9.管理系统社会责任国际标准(SA8000)I.目的与范围本标准目的在于提供一个基于国际人权/惯例和国家法律的标准,保护和授权所有在公司控制和影响范围内的生产或服务人员,包括公司自己及其供应商或分包方雇用的员工和家庭工人。

SA8000通过证据为基础的过程进行验证,本标准各项规定具有普遍适用性,不受地域、产业类别和公司规模限制。

STUB536中文资料

MAXIMUM RATINGS

Rating at 25 °C ambient temperature unless otherwise specified.

Ratiபைடு நூலகம்g

Peak Power Dissipation at Ta = 25 °C, Tp=1ms (Note1) Steady State Power Dissipation at TL = 75 °C

TYPE

VBR (V) Min. Max. STUB06I STUB56I STUB07F STUB57F STUB08C STUB58C STUB09B STUB59B STUB010 STUB510 STUB011 STUB511 STUB012 STUB512 STUB013 STUB513 STUB015 STUB515 STUB016 STUB516 STUB018 STUB518 STUB020 STUB520 STUB022 STUB522 STUB024 STUB524 STUB027 STUB527 STUB030 STUB530 STUB033 STUB533 STUB036 STUB536 STUB039 STUB539 STUB043 STUB543 STUB047 STUB547 STUB051 STUB551 STUB056 STUB556 STUB062 6.45 6.45 7.13 7.13 7.79 7.79 8.65 8.65 9.50 9.50 10.5 10.5 11.4 11.4 12.4 12.4 14.3 14.3 15.2 15.2 17.1 17.1 19.0 19.0 20.9 20.9 22.8 22.8 25.7 25.7 28.5 28.5 31.4 31.4 34.2 34.2 37.1 37.1 40.9 40.9 44.7 44.7 48.5 48.5 53.2 53.2 58.9 7.48 7.14 8.25 7.88 9.02 8.61 10.0 9.55 11.0 10.5 12.1 11.6 13.2 12.6 14.3 13.7 16.5 15.8 17.6 16.8 19.8 18.9 22.0 21.0 24.2 23.1 26.4 25.2 29.7 28.4 33.0 31.5 36.3 34.7 39.6 37.8 42.9 41.0 47.3 45.2 51.7 49.4 56.1 53.6 61.6 58.8 68.2 It (mA) 10 10 10 10 10 10 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0

C&C08简介(32模)

C&C08B 交换机简介1.2 C&C08交换机的特点1.2.1 满足新国标及补充规定要求,确保网络的先进性C&C08 己于1998年9月率先通过新国标测试,并在同年12月通过网上实际验证。

C&C08 顺从新国标1998年、1999年的补充规定,还通过了2000年时钟过渡问题测试。

1.2.2 容量大、结构先进、处理能力强C&C08 系统容量可从256用户平滑扩充到80万用户线或18万中继线,C&C08 采用话务分散控制结构,交换模块内部采用分级分散群机控制技术,模块内部通信采用内存映射技术,加上大量使用大容量内存和高性能CPU,使C&C08 系统的BHCA值达6000K。

1.2.3 组网灵活,支持FTTB、FTTC组网思想可根据用户容量及接口类型利用C&C08提供的多种远端模块及SDH,实现多级模块组网。

可组成环形、链形、树形、星形等网络拓扑结构,快速提供业务。

1.2.4 处于领先地位的业务提供能力C&C08可提供完整的PSTN业务、ISDN业务,丰富的Centrex业务和智能网业务。

1.2.5 信令系统结构先进、容量大,升级容易,兼容性好支持中国一号和七号信令,同一局向中国一号可与七号信令并存。

MFC 板与七号信令板槽位兼容,一号信令可方便地升级为七号信令。

七号信令处理分散在各交换模块中,可靠性高,处理能力强。

内置七号信令监视仪,方便局方维护。

1.2.6 硬件通用性强,单板种类少,功耗小充分考虑了硬件通用性,减少单板种类,降低维护开销,提高系统可靠性。

C&C08大量采用了华为公司自行研制的0.35-0.5微米芯片,集成度高,系统功耗小。

每万门功耗闲时3065W,忙时5240W。

1.2.7 先进的软件设计,软件升级简单采用C语言和SDL设计方法,并采用稳定性、可靠性及可扩展性好的实时操作系统。

软件的更改和升级管理采用了软件工程的配置管理方法,保证升级版本的一致性和测试的规范性,通过软件加载方式实现软件升级。

4V210-08参数、功能、尺寸、型号解读与用法

4V210-08 RDPC荣大电磁阀、4V210-08RDPC电磁阀4V210-08电磁阀、荣大4V210-08以上信息由宁波RDPC荣大气动元件厂提供!产品型号:3V1-M5|3V1-06|3V110-M5|3V120-M5|3V110-063V120-06|3V210-063|V220-06|3V210-08|3V220-08|3V310-08|3V320-08|3V310-10|3V320-10|4M110-M5|4M120-M5|4M110-06|4M120-06|4M210-06|4M220-06|4M210-08|4M220-08|4M310-08|4M320-08|4M310-10|4M320-10|4M410-15|4V110-M5|4V120-M5|4V130C-M5|4V130E-M5|4V130P-M5|4V110-06|4V120-06|4V130C-06|4V130E-06|4V130P-06|4V210-06|4V220-06|4V230C-06|4V230E-06|4V230P-06|4V210-08|4V220-08|4V230C-08|4V230E-08|4V230P-08|4V310-08|4V320-08|4V330C-08|4V330E-08|4V330P-08|4V310-10|4V320-10|4V330C-10|4V330E-10|4V330P-10|4V410-15|4V420-15|4V430C-15|4V430E-15|4V430P-15|5SV210-06|5SV220-06|5SV230C-06|5SV230E-06|5SV230P-06|5SV210-08|5SV220-08|5SV230C-08|5SV230E-08|5SV230P-08|5SV310-08|5SV320-08|5SV330C-08|5SV330E-08|5SV330P-08|5SV310-10|5SV320-10|5SV330C-10|5SV330E-10|5SV330P-10|5SV410-15|5SV420-15|5SV430C-15|5SV430E-15|5SV430P-15|二:产品特性:1、先导方式:外部与内部可选;2、滑柱式结构,密封性好,反应灵敏;3、三位置电磁阀有三种中央功能可供选择;4、双头二位置电磁阀具有记忆功能;5、内孔采用特殊工艺加工,磨擦阻力小,启动气压低,使用寿命长;6、无需加油润滑;7、可与底座集成阀组,节省安装空间;8、附设手动装置,利于安装调试;9、有多种标准电压等级可供选用。

BTA08-600C中文资料

BTA08-600C中⽂资料1/10BTA/BTB08 and T8 SeriesSNUBBERLESS ?, LOGIC LEVEL & STANDARD8A TRIAC SApril 2002 - Ed: 5AMAIN FEATURES:DESCRIPTIONAvailable either in through-hole or surface-mount packages, the BTA/BTB08 and T8 triac series is suitable for general purpose AC switching. They can be used as an ON/OFF function in applications such as static relays, heating regulation, induction motor starting circuits... or for phase control operation in light dimmers, motor speed controllers,...The snubberless versions (BTA/BTB...W and T8series) are specially recommended for use on inductive loads, thanks to their high commutation performances. By using an internal ceramic pad,the BTA series provides voltage insulated tab (rated at 2500V RMS) complying with UL standards (File ref.: E81734)Symbol Value Unit I T(RMS)8A V DRM /V RRM 600 and 800V I GT (Q 1)5 to 50mAABSOLUTE MAXIMUM RATINGSSymbol ParameterValueUnitI T(RMS)RMS on-state current (full sine wave)DP AK / D 2PAK IPAK / TO-220AB Tc = 110°C 8A TO-220AB Ins.Tc = 100°C I TSM Non repetitive surge peak on-state current (full cycle, Tj initial = 25°C) F = 50 Hz t = 20 ms 80AF = 60 Hzt = 16.7 ms84I 2t I 2t Value for fusingtp = 10 ms36A 2s dI/dt Critical rate of rise of on-state current I G = 2 x I GT , tr ≤ 100 ns F = 120 Hz Tj = 125°C 50A/µs I GM Peak gate currenttp = 20 µsTj = 125°C 4A P G(AV)Average gate power dissipation Tj = 125°C1W T stg T jStorage junction temperature range Operating junction temperature range- 40 to + 150- 40 to + 125°CBTA/BTB08 and T8 Series2/10ELECTRICAL CHARACTERISTICS (Tj = 25°C, unless otherwise specified)sSNUBBERLESS? and LOGIC LEVEL (3 Quadrants)sSTANDARD (4 Quadrants)STATIC CHARACTERISTICSNote 1: minimum IGT is guaranted at 5% of IGT max.Note 2: for both polarities of A2 referenced to A1 Symbol Test ConditionsQuadrantT8BTA/BTB08UnitT810T835TW SW CW BW I GT (1)V D = 12 V R L = 30 ?I - II - III MAX.10355103550mA V GT I - II - III MAX. 1.3V V GD V D = V DRM R L = 3.3 k ?Tj = 125°C I - II - IIIMIN.0.2V I H (2)I T = 100 mA MAX.153510153550mA I L I G = 1.2 I GTI - III MAX.255010255070mA II306015306080dV/dt (2)V D = 67 %V DRM gate open Tj = 125°CMIN.4040020404001000V/µs (dI/dt)c (2)(dV/dt)c = 0.1 V/µs Tj = 125°C MIN.5.4- 3.5 5.4--A/ms(dV/dt)c = 10 V/µs Tj = 125°C 2.8- 1.5 2.8--Without snubber Tj = 125°C- 4.5-- 4.57Symbol Test ConditionsQuadrant BTA/BTB08UnitCB I GT (1)V D = 12 V R L = 30 ?I - II - III IV MAX.255050100mA V GT ALL MAX. 1.3V V GD V D = V DRM R L = 3.3 k ?Tj = 125°C ALLMIN.0.2V I H (2)I T = 500 mA MAX.2550mA I L I G = 1.2 I GTI - III - IVMAX.4050mA II80100dV/dt (2)V D = 67 %V DRM gate open Tj = 125°CMIN.200400V/µs (dV/dt)c (2)(dI/dt)c = 3.5 A/ms Tj = 125°CMIN.510V/µsSymbol Test ConditionsValue Unit V TM (2)I TM = 11 A tp = 380 µs Tj = 25°C MAX. 1.55V V to (2)Threshold voltage Tj = 125°C MAX.0.85V R d (2)Dynamic resistance Tj = 125°C MAX.50m ?I DRM I RRMV DRM = V RRMTj = 25°C MAX.5µA Tj = 125°C1mABTA/BTB08 and T8 Series3/10THERMAL RESISTANCESS = Copper surface under tabPRODUCT SELECTORBTB: non insulated TO-220AB packageSymbol ParameterValue Unit R th(j-c)Junction to case (AC)DPAK / D 2PAK IPAK / TO-220AB 1.6°C/WTO-220AB Insulated2.5R th(j-a)Junction to ambientS = 1 cm 2D 2PAK 45°C/WS = 0.5 cm 2DPAK70TO-220ABTO-220AB Insulated60IPAK100Part NumberVoltage (xxx)Sensitivity Type Package 600 V 800 V BTA/BTB08-xxxB X X 50 mA Standard TO-220AB BTA/BTB108-xxxBW X X 50 mA Snubberless TO-220AB BTA/BTB08-xxxC X X 25 mA Standard TO-220AB BTA/BTB08-xxxCW X X 35 mA Snubberless TO-220AB BTA/BTB08-xxxSW X X 10 mA Logic level TO-220AB BTA/BTB08-xxxTW X X 5 mA Logic level TO-220AB T810-xxxB X X 10 mA Logic level DP AK T810-xxxH X X 10 mA Logic level IP AK T835-xxxB X X 35mA Snubberless DP AK T835-xxxG X X 35 mA Snubberless D 2PAK T835-xxxHXX35 mASnubberlessIP AKBTA/BTB08 and T8 Series4/10ORDERING INFORMATIONOTHER INFORMATIONNote: xxx = voltage, yy = sensitivity, z = typePart NumberMarkingWeight Base quantity Packing mode BTA/BTB08-xxxyz BTA/BTB08xxxyz 2.3 g 250Bulk BTA/BTB08-xxxyzRG BTA/BTB08-xxxyz 2.3 g 50Tube T8yy-xxxB T8yyxxx 0.3 g 75Tube T8yy-xxxB-TR T8yyxxx 0.3 g 2500Tape & reel T8yy-xxxH T8yyxxx 0.4 g 75Tube T8yy-xxxG T8yyxxx 1.5 g 50Tube T8yy-xxxG-TRT8yyxxx1.5 g1000Tape & reelBTA/BTB08 and T8 Series5/10Fig. 1: Maximum power dissipation versus RMS on-state current (full cycle).Fig. 2-1: RMS on-state current versus case temperature (full cycle).Fig. 2-2: RMS on-state current versus ambient temperature (printed circuit board FR4, copper thickness: 35µm),full cycle. Fig. 3: Relative variation of thermal impedance versus pulse duration.Fig. 4: On-state characteristics (maximum values).Fig. 5: Surge peak on-state current versus number of cycles. BTA/BTB08 and T8 Series6/10Fig. 6: Non-repetitive surge peak on-state current for a sinusoidal pulse with width tp <10ms, and corresponding value of I2t. Fig. 7: Relative variation of gate trigger current,holding current and latching current versus junction temperature (typical values).Fig. 8-1: Relative variation of critical rate of decrease of main current versus (dV/dt)c (typical values). Snubberless & Logic Level TypesFig. 8-2: Relative variation of critical rate of decrease of main current versus (dV/dt)c (typical values). Standard Types Fig. 9: Relative variation of critical rate of decrease of main current versus junction temperature.Fig. 10: DP AK and D 2PAK Thermal resistance junction to ambient versus copper surface under tab (printed circuit board FR4, copper thickness:35µm).BTA/BTB08 and T8 Series PACKAGE MECHANICAL DATAFOOTPRINT DIMENSIONS (in millimeters)7/10BTA/BTB08 and T8 Series PACKAGE MECHANICAL DATAFOOTPRINT DIMENSIONS (in millimeters)8/10BTA/BTB08 and T8 Series PACKAGE MECHANICAL DATA9/10BTA/BTB08 and T8 SeriesPACKAGE MECHANICAL DATAInformation furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.The ST logo is a registered trademark of STMicroelectronics2002 STMicroelectronics - Printed in Italy - All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia - Brazil - Canada - China - Finland - France - GermanyHong Kong - India - Isreal - Italy - Japan - Malaysia - Malta - Morocco - Singapore Spain - Sweden - Switzerland - United Kingdom - United States./doc/9577c19bdaef5ef7ba0d3c89.html10/10。

adc0808中文资料

11.2.4 典型的集成ADC芯片为了满足多种需要,目前国内外各半导体器件生产厂家设计并生产出了多种多样的ADC芯片。

仅美国AD公司的ADC产品就有几十个系列、近百种型号之多。

从性能上讲,它们有的精度高、速度快,有的则价格低廉。

从功能上讲,有的不仅具有A/D转换的基本功能,还包括内部放大器和三态输出锁存器;有的甚至还包括多路开关、采样保持器等,已发展为一个单片的小型数据采集系统。

尽管ADC芯片的品种、型号很多,其内部功能强弱、转换速度快慢、转换精度高低有很大差别,但从用户最关心的外特性看,无论哪种芯片,都必不可少地要包括以下四种基本信号引脚端:模拟信号输入端(单极性或双极性);数字量输出端(并行或串行);转换启动信号输入端;转换结束信号输出端。

除此之外,各种不同型号的芯片可能还会有一些其他各不相同的控制信号端。

选用ADC芯片时,除了必须考虑各种技术要求外,通常还需了解芯片以下两方面的特性。

(1)数字输出的方式是否有可控三态输出。

有可控三态输出的ADC芯片允许输出线与微机系统的数据总线直接相连,并在转换结束后利用读数信号RD选通三态门,将转换结果送上总线。

没有可控三态输出(包括内部根本没有输出三态门和虽有三态门、但外部不可控两种情况)的ADC芯片则不允许数据输出线与系统的数据总线直接相连,而必须通过I/O接口与MPU交换信息。

(2)启动转换的控制方式是脉冲控制式还是电平控制式。

对脉冲启动转换的ADC芯片,只要在其启动转换引脚上施加一个宽度符合芯片要求的脉冲信号,就能启动转换并自动完成。

一般能和MPU配套使用的芯片,MPU的I/O写脉冲都能满足ADC芯片对启动脉冲的要求。

对电平启动转换的ADC芯片,在转换过程中启动信号必须保持规定的电平不变,否则,如中途撤消规定的电平,就会停止转换而可能得到错误的结果。

为此,必须用D 触发器或可编程并行I/O 接口芯片的某一位来锁存这个电平,或用单稳等电路来对启动信号进行定时变换。

ADC0808中文资料_数据手册_参数

Operating Conditions (1)(2)

Temperature Range Range of VCC

TMIN≤TA≤TMAX −40°C≤TA≤+85°C ቤተ መጻሕፍቲ ባይዱ.5 VDC to 6.0 VDC

(1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating the device beyond its specified operating conditions.

KEY SPECIFICATIONS

• Resolution: 8 Bits • Total Unadjusted Error: ±½ LSB and ±1 LSB • Single Supply: 5 VDC • Low Power: 15 mW • Conversion Time: 100 μs

Figure 2. PLCC

See Package N0028E

Package

See Package FN0028A

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

CC08程控交换机

超经典 HPUX AIX cisco 华为毕业论文学习资料/ccy7758华为C&C08数字程控交换机产品介绍1.C&C08交换机的系统功能和特点 (3)1.1 C&C08交换机特点 (3)1.2 C&C08交换机系统硬件结构 (7)1.3 C&C08交换机系统软件结构 (10)2.C&C08交换机系统提供的业务 (11)2.1 对PSTN用户提供的业务 (11)2.2 对ISDN用户提供的业务 (11)2.3 Centrex业务 (13)2.4 酒店功能接口 (16)3.C&C08机的信令与接口 (19)3.1 C&C08信令系统特点 (19)3.2 接口种类 (20)3.3 时钟与同步 (21)3.4 C&C08操作维护中心 (22)3.4.1 C&C08维护测试 (22)3.4.2 C&C08话务统计 (23)3.4.3 C&C08网管 (25)3.4.4 C&C08告警系统 (26)4.设备机电参数及环境要求 (27)4.1设备机电参数 (27)4.2对环境温湿度的要求 (28)4.3对防尘和有害气体的防护要求 (29)4.4对电源和接地的要求 (29)4.4.1设备耗电量 (29)4.4.2电源 (30)4.4.3接地 (31)1. C&C08交换机的系统功能和特点1.1 C&C08交换机特点满足新国标及补充规定要求,确保网络的先进性C&C08数字程控交换系统,符合ITU-T和新国标--《邮电部电话交换设备总技术规范书》的要求,提供符合ITU-T标准的ISDN接口, 提供与分组网互连的PHI 接口及多种无线接入方式,提供ITU-T标准的V5接口协议,具有完整的随路信令和先进的CCS7信令系统。

目前提供的新业务和新功能达100多种。

提供的业务及性能符合以下技术规范:《邮电部电话交换设备总技术规范书》(YDN 065-1997)《中国电信交换机99版内容说明》《中国电信互联互通点交换设备技术要求》《开放呼叫前转,语音邮箱,电话卡等业务的技术要求》(GF009-94)《中国电话网随路信号方式技术规范》《中国国内电话网NO.7信号方式技术规范》(GF001-9001)《中国国内电话网NO.7信令方式综合数字业务网用户部分(ISUP)技术规范》(YDN-038-1997)《ISDN用户--网络接口基本呼叫控制技术规范》《ISDN用户--网络接口数据链路层技术规范》《ISDN用户--网络接口补充业务技术规范及一致性测试》《本地交换机和接入网V5.1接口技术规范》《本地交换机和接入网V5.2接口技术规范》《国内NO.7信令方式技术规范――信令连接控制部分(SCCP)》(GF-010-95) 《国内NO.7信令方式技术规范――事物处理能力部分(TC)》(GF-010-95)《中国智能网应用规范----INAP》《中国智能网业务交换点(SSP)设备技术规范》《被叫集中付费业务、记帐卡呼叫业务和虚拟专用网业务的业务含义和流程》(暂行规定) 中华人民共和国邮电部一九九八年三月《通用个人通信(UPT)、广域集中用户交换机(WAC)、电话投票(VOT)和大众呼叫(MAS)的业务含义合流程(报批稿)》中华人民共和国邮电部容量大、结构先进、处理能力强C&C08 系统容量可从256用户平滑扩充21万用户,并可进一步扩容到80万用户线或18万中继线,C&C08 采用话务分散控制结构,交换模块内部采用分级分散群机控制技术,模块内部通信采用内存映射技术,加上大量使用大容量内存和高性能CPU,使C&C08 系统的BHCA值达6000K。

C183-2008中文版

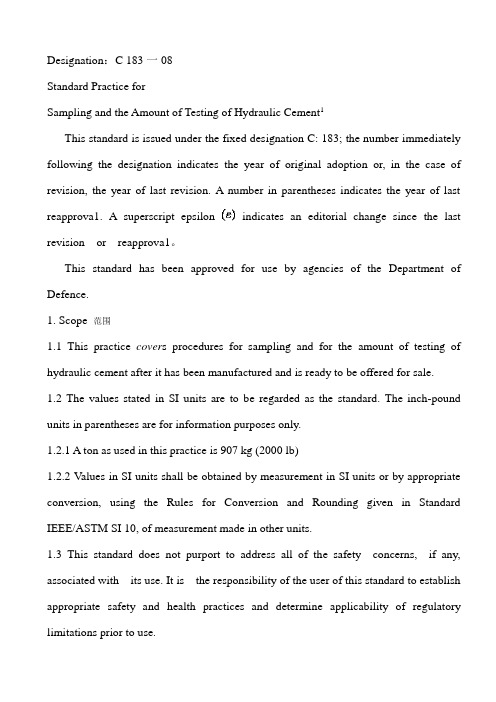

Designation:C 183一08Standard Practice forSampling and the Amount of Testing of Hydraulic Cement1This standard is issued under the fixed designation C: 183; the number immediately following the designation indicates the year of original adoption or, in the case of revision, the year of last revision. A number in parentheses indicates the year of lastreapprova1. A superscript epsilon indicates an editorial change since the last revision or reapprova1。

This standard has been approved for use by agencies of the Department of Defence.1. Scope 范围1.1 This practice cover s procedures for sampling and for the amount of testing of hydraulic cement after it has been manufactured and is ready to be offered for sale.1.2 The values stated in SI units are to be regarded as the standard. The inch-pound units in parentheses are for information purposes only.1.2.1 A ton as used in this practice is 907 kg (2000 lb)1.2.2 Values in SI units shall be obtained by measurement in SI units or by appropriate conversion, using the Rules for Conversion and Rounding given in Standard IEEE/ASTM SI 10, of measurement made in other units.1.3 This standard does not purport to address all of the safety concerns, if any, associated with its use. It is the responsibility of the user of this standard to establish appropriate safety and health practices and determine applicability of regulatory limitations prior to use.2 Referenced Document 参考文献2.1 ASTM Standards2ASTM标准C 91 Specification for Masonry CementC109/C109M Test Method for Compressive Strength of Hydraulic Cement Mortars (Using 2-in. or [50-mm] Cube Specimens)C 114 Test Methods for Chemical Analysis of Hydraulic CementC115 Test Method for Fineness of Portland Cement by the TurbidimeterC 150 Specification for Portland CementC151Test Method for Autoclave Expansion of Hydraulic CementC 157/C157M Test Method for Length Change of Hardened Hydraulic-Cement Mortar and ConcreteC 185 Test Method for Air Content of Hydraulic Cement Mortar 水泥风干的测定方法C 186 Test Method for Heat of Hydration of Hydraulic CementC 191 Test Methods for Time of Setting of Hydraulic Cement by Vicat NeedleC 2l4 Test Methods for Fineness of Hydraulic Cement by Air-Permeability ApparatusC 227 Test Method for Potential Alkali Reactivity of Cement-Aggregate Combinations (Mortar-Bar Method)C265 Test Method for Water-Extractable Sulfate in Hydrated Hydraulic Cement MortarC266 Test Method for Tune of Setting of Hydraulic-Cement Paste by Gillmore NeedlesC451 Test Method for Early Stiffening of Hydraulic Cement (Paste Method)C452 Test Method for Potential Expansion of Portland Cement Mortars Exposedto SulfateC563 Test Method for Approximation of Optimum SO3 Hydraulic Cement Using Compressive Strength.C 535 Specification for Blended Hydraulic CementsC 845 Specification for expansive Hydraulic CementC 1012 Test Method for Length Change of Hydraulic Cement Mortars Exposed to a Sulfate SolutionC1157 Performance Specification for Hydraulic CementC 1328 Specification for Plastic (Stucco) CementC 1329 Specification for Mortar Cement E 11 Specification for wire cloth and sieves for testing purposes IEEE/ASTM SI 10 Standard for Use of the International system of units (SI):The modern metric system2.2 ACI Standard.225.1 R Guide to the Selection and Use of Hydraulic Cement3水泥使用指南3. Terminology 术语3.1.1Definitions of Terms Specific to This Standard:本标准引用特殊条款的定义3.1.1 A lot (of cement)--specific quantity offered cement inspection at any one time. A lot may be one or more storage bins filled consecutively. A lot may also be the contents of one or more transport units representing cement drawn from the same storage bin. 3.1.2 reduced testing rate-test program that provides for the testing of only two samples from. any given lot of samples obtained and prepared for testing at the normal rate as described herein- The program utilizes probability factors and is so designed that whenresults from the two samples fulfill the requirements of the program it may be said with 95% confidence that less than 5% of the sample would be outside the specification limits.1 This practice is under the jurisdiction of ASTM committee C01 on Cement and is the direct responsibility of subcommittee C01.95 on coordination of standards.Current edition approved Dec.15,2008. Published January 2009. Originally approved in 1944. Last previous edition approved in 2002 as C183-02.2For referenced ASTM standard s, visit the ASTM website, , or contact ASTM Customer Service at service@. For Annual book of ASTM standards volume information, refer to the standard’s Document Summary page on the ASTM website.3Detailed requirement for this sieve are given in Specification E11.4. Significance and Use4.1 The sampling procedures described are intended for use in the procurement of samples of hydraulic cement after it has been manufactured and is ready to be offered for sale. They are not intended as sampling procedures for quality control purposes during manufacturing. The testing procedures outlined cover the amount of testing to be done and provide guidance for reporting on conformance or non-conformance of cements with requirements of purchase specifications.4.2 This practice is referenced as the procedure for sampling masonry cement (Specification C91), Portland cement specification C150), blended hydraulic cement (Specification C595), expansive hydraulic cement (Specification C845), plastic stucco cement (Specification C1328), mortar cement (Specification C1329), and hydrauliccement based on a performance specification (specification C1157).4.3 Most building codes and construction specifications require that hydraulic cement to be used in the work meet the applicable requirements of the relevant purchase specifications, such as Specifications C91, C150, C595, C1157, C1328, C1329, or C845. If the code or specification requires sampling of the manufactured cement, the provisions given in 4.4 are applicable. Not much cement is sold on the basis of such sampling and testing. A useful discussion of sampling and testing cement is contained in ACI 225.1R.4.4 The procedures covered in the practices should be done by or for purchasers of hydraulic or specification who are using a code or specification that requires sampling and testing to determine if the samples conform to the relevant acceptance specification. The testing is done using specified methods to determine whether the samples yield test results that conform to the specification, and the tests serve as a basis for acceptance or rejection of the lot of material sampled.4.5 It is neither intended nor required that all cements be tested using all the test methods referenced in Section 2.5. Kinds and Size of Samples and by Whom Taken5.1 A cement sample secured from a conveyor, from bulk storage, or from a bulk shipment in one operation, shall be termed a "grab sample." A sample obtained during 10-min interval using an automatic sampling device that continuously samples a cement stream may also be termed a grab sample. Grab samples taken at prescribed intervals aver a period of time may be combined to form a "composite sample" representative of the cement produced during that period of time.5.2 All samples, whether grab or composite, shall have a mass of at least 5 kg (10 .1D).5.3 The purchaser may designate a representative to supervise the sampling, packing, and shipping of samples when it is so specified in the purchase contract.5.4 Package the samples in moisture-proof, airtight containers numbered consecutively in the order in which the samples are taken. The purchase contract shall state who will pay for the costs of sampling, packaging, shipping and testing the samples.Note1-Polyvinyl chloride sample containers, upon occasion, have been found to affect the air-entraining potential of a cement sample. The same problem might be experienced with containers made from other plastics.6. Testing-Time Requirements for the Completion of Tests6.1. When tests of hydraulic cement are made at a laboratory other than that of the cement manufacturer, the cement sampling schedule, sample transportation lime, and sample testing schedule must be coordinated among the purchaser, the manufacturer, and the testing laboratory so that the tests results will be available when required.6.2 The manufacturer of the cement shall make the cement available to be sampled for testing early enough before the time the test results are needed so that at least the applicable time intervals listed in 6.3 exist.6.3 When this has been done, the testing laboratory shall provide test results not later than the indicated number of days after sampling:Test Methods Time Intetval,daysC 109/C 109M(1-day results), G 114, C115, C151 8C 185,C 191, C 204, C 451, C 265, C 286, C 563C 109/C 109M (3-day results) 10C 109/C 109M and C 186 (7-day results} 14C 227, C 452, and C 1012 (14-day results) 21C 109 /C 109M and C 186 (28-day results) 35C 1571C 157M (34-day results) 41G 227 (56-day results} 63C 227 (91-day results) 987. Sampling7.1 The cement may be sampled by any of the applicable methods described in this section.7.1.1 From the Conveyor Delivering to Bulk Storage-Take one grab sample, having a mass of at least 5 kg (10 1b), at approximately 6-h intervals.7.1.2 Transfer Sampling-Sample cement in storage while the cement is being transferred from one bin to another. Take one grab sample From the transfer stream for each 360Mg (400tans) of cement, or fraction thereof, but take no less than two grab samples and combine them to produce a composite sample.7.1.3 Other Sampling methods-When neither of the above sampling methods is applicable, samples may, when authorized by the purchaser, he taken by one of the following methods:7.1.3.1 From Bulk storage at Points of Discharge Withdraw cement from the discharge openings in a steady stream until sampling is completed. Estimate the quantity ofcement in Mg to be withdrawn from one discharge opening as 0.055 d3×0.2, whereis the depth in metres of cement above the discharge opening. If a high circular silo is being sampled, take all samples from one opening. If the quantity of the cement in the bin exceeds 1100Mg (1200 tons) when low rectangular bins are being sampled, discharge openings employed in the sampling shall be such that for no opening shall the number of samples represent more than 1800Mg (2000 tons).In sampling bulk storage at points of discharge, while the cement is flowing through the openings, take samples atsuch intervals so that at least two grab samples shall be Secured for each 360Mg (400 tons) in the bin or silo.7.1.3.2 From Bulk Storage and Bulk Shipment by Means of a Slotted Tube Sampler When the depth of the cement to be sampled does not exceed 2.1m (7 ft), obtain samples using a slotted tube sampler similar to that shown in fig 1,It shall be between1.5 anal 1.8 m (5 and 6 ft) long and approximately 35mm ( )in outside diameter and consist of two polished brass telescopic tubes with registering slots that are opened or closed by rotation of the inner tube, the outer tube being provided with a sharp point to facilitate penetration. Take samples from well-distributed points and various depths of the cement so that the samples taken will represent the cement involved.7.1.3.3 From Packaged Cement by means of Tube Sample—Insert the Sampler, shown in Fig.2, diagonally into the valve of the bag and place the thumb over the air hole. Then withdraw the sampler. Take one sample from a bag in each 4.5Mg (5tons) or fraction thereof.7.1.3.4 From Bulk Shipment of Car or truck:(a)(a) Single Shipment-If only one Car or truck is being loaded and the loading is continuous and all from the same source, take a 5-kg (10-1b) sample ,if not continuous or unknown ,combine five or more portions from different points in the load to form the test sample.(b) (b) Multiple Shipments-When the shipment consists of several cars or trucks loaded from the same source and on the same day, sample the shipment at the rate of one sample for each 90Mg (100 tons) of cement or fraction thereof, but take not less thantwo samples. Consider cement represented by such samples as a lot, and test the samples in accordance with the procedure outlined in the section on Amount of Testing.7.2 Protection of Samples-As samples are taken, place them directly in moisture-proof airtight containers to avoid moisture absorption and aeration of the sample. If the samples are placed in cans, fill the can completely and immediately seal. Use moisture-proof multiple-wall paper bags or plastic bags if they are strong enough to avoid breakage, and if they can be sealed immediately after filling in such a manner as to eliminate excess air in the sample and avoid moisture absorption and aeration of the sample. Samples shall be treated as described in the section on Preparation of sample. 8. Preparation of sample8.1 Before testing ,pass each sample through an 850-um(No. 20) sieve6, or any other sieve having approximately the Same size openings, in order to mix the sample, break up lumps, and remove foreign material. Discard the foreign materials and hardened lumps that do not break up on sieving or brushing. Store the cement in airtight moisture-proof containers to prevent aeration or absorption of moisture prior to test.9. Amount of Testing9.I General-When required, the purchaser shall specify the amount of testing for heat of hydration ( test Method C186), alkali reactivity (Test Method C227), and sulfate resistance (Test Method C1012). Make all other tests on individual grab or composite samples chosen as specified herein under Selection of Samples for Testing. Do only those tests required by the applicable specification.9.2 Normal Testing一Determine the number of samples to be tested in accordance with Table 1.The normal testing rate shall be used under the following conditions:9.2.1 Before the quality history has been established,9.2.2 When no samples from a particular mill have been test within a year,9.2.3When the quality history is based entirely on data more than two years old, and 9.2.4 When it is deemed necessary to recalculate limit because of indicated lack of control as shown by the control chart of the range.Note 2-Random garb samples taken at inappropriate times, such as immediately following the repair or adjustment of manufacturing equipment, or from inappropriate places, such as from the top surface of the material in a car, will not suitably reflect the properties of a cement, and therefore should not be used as the basis for acceptance or rejection of a lot of cement.9.3 Reduced Testing---After the quality history has been established, test at the reduced testing rate. If the results of these tests are within the critical range, make additional tests (total equal to the number of tests at the normal rate as shown in Table 1).Note 3-When the quality history indicates that the results for a given requirement will probably be within the critical range, and substantial delay in completion of the tests would result from making additional tests (for example, compressive strength), it may be desirable to make the tests at the normal rate, rather than the reduced testing rate.9.4 Selection of Samples for Testing-Take samples to be tested from each lot by some random method. The following method is suggested: Place a group of consecutively numbered markers equal to the number of samples in a container and mix, then draw one maker at a time from the container until the number drawn is equal to the number of samples to be tested at the normal rate. If the testing is to be done at the reduced rate, mix the drawn markers and draw two to select the numbers of the samples to be tested.9.5 Establishing a Quality History and Control Charts:9.5.1 Quality History-The quality history shall represent cement from the same sourceas the cement to be tested, and shall be based on data not more than 2 years old. There shall be available test results for not less than 40 test samples representing not Less than 7 lots of cement. The test samples shall conform to the applicable provisions of this practice. A pair shall be two test samples from the same lot, in numerical sequence. several pairs from the same lot may be used where available. The number of paired samples representing a large lot may be reduced as follows: From the consecutively numbered group of tested samples representing the entire lot, select a subgroup by some random method. List the numbers identifying the subgroup in numerical sequence, and pair in the order of listing. Compute the range (difference between the test results of a pair) for each pair of test results. Total the ranges and divide their sum by the totalnumber of ranges used to obtain the average range, Compute the average range, for each included physical and chemical property limited by specification requirements.9.5.2 Critical Limit-Calculate the critical limit, C, for each included physical and chemical property limited by a specification requirement. First, multiply the averagerange, , by the probability factor, 2.49, this will yield a number that for convenience is called d. If the requirement has a maximum Specification limit, obtain C by subtracting d from the specification limit and, if a minimum, add d to the specification limit. Maintain quality history charts.Note 4-lrnproved estimates of the range, and consequently of C, will result if the test results are not rounded. For example, the test result of 21.78% for Si02 is preferred to the rounded value of 21.8%.For the fineness, the calculated value of 3243 is preferred to the rounded value of 3240.9.5.3 Control Chart of the Range-Maintain a control chart of the range to indicatewhen the critical limit needs to be recomputed. Multiply the average range., asobtained in 9.5.2,by the probability factor 3.267 to obtain the upper control limit for the range between each consecutive pair of test results. The horizontal scale of the chart will be successive groups of two, and the vertical scale will be the range. Where the range chart indicates lack of control (points beyond the upper control limit), the critical limit, C, may need to be recalculated. Consider the occurrence of two consecutive paints beyond the upper control limit for the range, or the occurrence of three points beyond the upper control limit in any series of five consecutive points cause to recalculate the critical limit. Where it becomes necessary to recalculate the critical limit, discontinue reduced testing until a new quality history has been established.Note 5-Examples of the calculation of , d, and quality history and control charts are shown in Table 2 and Fig. 3 and Fig. 4. The specification limits used in these examples are Hypothetical.9.5.4 When the hydraulic cement sampled is to conform to Specification C 150, and the manufacturer has chosen the optimized cement SO3; option as described in Specification C150 Table 1 footnote D, the critical limit described in paragraph 9.5.2 using the specification limit for SO3is not applicable. Paragraphs 9.5.2 and 9.5.3 dealing with the calculation of critical limit are not required for SO3 in this case.9.5.5 When the hydraulic cement sampled is to conform to Specification C595, and the manufacturer has chosen the optimized cement SO3; content option as described in Specification C595 Table l footnote A, the critical limit described in paragraph 9.5.2 using the specification limit for SO3 is not applicable. Paragraphs 9.5.2 and 9.5.3 dealing with the calculation of critical limit are not required for SO3 in this case.9.6 Reporting for Normal Testing-When the testing is done at the normal testing rate, report the cement as complying with the specification if it meets the specification requirements, and report it as failing to meet the specification requirements if it does notmeet each of the requirements as specified.9.7 Reporting for reduced Testing-When the testing is done at the reduced testing rate, report the cement as complying with the specification if the average of the test results is further from the specified limit than the critical limit. If the average of the results for one or more requirements are between the critical limit and the specification limit, test additional samples (total equal to the number of tests at the normal rate) for that requirement, and if on completion of the additional tests, all of the results meet the specified requirement report the cement as complying with the specification. Report the cement as failing to meet the specification requirement if any test result does not conform to the respective requirements.9.8 When a cement is reported as failing to meet the specification requirements, state in the report which requirement the cement failed and the applicable limit.10. Noncompliance and Retest10.1 If any test result fails to meet the specification requirement, the lot of cement shall not be reported as not complying with the specification unless noncompliance is confirmed by retest as described in 10.2 .10.2 A retest is considered to be an additional test of a certain property that is made when the initial test of that property produces a result not complying with the specification requirements. A retest may consist of either a single determination or a set of replicate determinations.10.3 Retests shall be conducted in accordance with the provisions, if given, of the applicable specification. If no provisions are given, the following procedure shall be used:10.3.1 Make the retest on a portion of the same sample as was used for the initial test. Use referee methods whenever they are provided for determination of the property requiring retest and in such case use only the results obtained by referee methods. The retest shall Consist of the same number of determinations required for the initial test, or, if a within laboratory precision statement is given which is based on a specified number of replicates (that is, duplicate or triplicate determinations), the number of replicates used as the basis of such precision statement. If two or more determinations are required, the value reported shall be the average of all results that are within the limits of precision of the method at the 95% confidence level, as stated in the applicable specification or as generally recognized.11. Keywords11.1 hydraulic cement; sampling; testingSUMMARY OF CHANGESCommittee C01 has identified the location of selected changes to this practice since the last issue, C 183一02, that may impact the use of this practice. (Approved December 15, 2008)(1) Added new 9.5.4 and 9.5.5.ASTM International takes no position respecting the validity of any patent rights asserted in connection with any item mentioned in this standard. Users of this standard are expressly advised that determination of the validity of any such patent rights, and the risk of infringement of such rights, are entirely their own responsibility .This standard is subject to revision at any time by the responsible technicalcommittee and must be reviewed every five years and if not revised, either reapprovedor withdrawn. Your comments are invited either for revision of this standard or for additional standards and should be addressed to ASTM International Headquarters. Your comments will receive careful consideration at a meeting of the responsible technical committee, which you may attend. If you feel that your comments have not received a fair hearing you should make your views known to the ASTM Committee on Standards, at the address shown below.This standard is copyrighted by ASTM International, 100 Barr Harbor Drive, PO BoxC700,West Conshohocken, PA 19428-2959,United States. Individual reprints(single or multiple copies)of this standard may be obtained by contacting ASTM at the above address or at 610-832-9585(phone), 610-832-9555(fax),or service@(e-mail); or through the ASTM website ()。

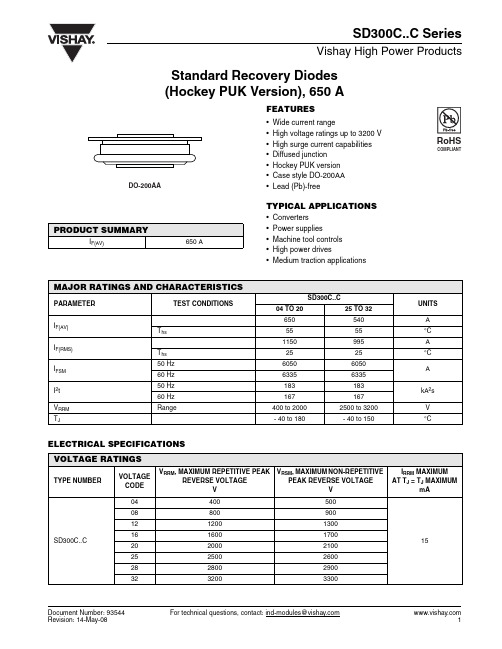

SD300C08C资料

Document Number: 93544For technical questions, contact: ind-modules@Standard Recovery Diodes(Hockey PUK Version), 650 ASD300C..C SeriesVishay High Power ProductsFEATURES•Wide current range•High voltage ratings up to 3200 V •High surge current capabilities •Diffused junction •Hockey PUK version •Case style DO-200AA •Lead (Pb)-freeTYPICAL APPLICATIONS•Converters •Power supplies•Machine tool controls •High power drives•Medium traction applicationsELECTRICAL SPECIFICATIONS PRODUCT SUMMARYI F(AV)650 AMAJOR RATINGS AND CHARACTERISTICSPARAMETER TEST CONDITIONS SD300C..CUNITS 04 TO 2025 TO 32I F(AV)650540A T hs 5555°C I F(RMS)1150995A T hs 2525°C I FSM 50 Hz 60506050A 60 Hz 63356335I 2t 50 Hz 183183kA 2s 60 Hz 167167V RRM Range400 to 20002500 to 3200V T J- 40 to 180- 40 to 150°CVOLTAGE RATINGSTYPE NUMBERVOLTAGECODEV RRM , MAXIMUM REPETITIVE PEAK REVERSE VOLTAGE V V RSM , MAXIMUM NON-REPETITIVEPEAK REVERSE VOLTAGEVI RRM MAXIMUM AT T J = T J MAXIMUMmASD300C..C044005001508800900121200130016160017002020002100252500260028280029003232003300元器件交易网 For technical questions, contact: ind-modules@Document Number: 93544SD300C..C SeriesVishay High Power Products Standard Recovery Diodes(Hockey PUK Version), 650 ANote•The table above shows the increment of thermal resistance R thJ-hs when devices operate at different conduction angles than DCFORWARD CONDUCTIONPARAMETERSYMBOL TEST CONDITIONSSD300C..C UNITS 04 TO 2025 TO 32Maximum average forward current at heatsink temperature I F(AV)180° conduction, half sine wave Double side (single side) cooled650 (380)540 (250)A 55 (85)55 (85)°CMaximum RMS forward currentI F(RMS)25 °C heatsink temperature double side cooled 1150995AMaximum peak, one-cycle forward, non-repetitive surge currentI FSMt = 10 ms No voltage reapplied Sinusoidal half wave,initial T J = T J maximum6050t = 8.3 ms 6335t = 10 ms 100 % V RRM reapplied 5090t = 8.3 ms 5330Maximum I 2t for fusing I 2t t = 10 ms No voltage reapplied 183kA 2st = 8.3 ms 167t = 10 ms 100 % V RRM reapplied129t = 8.3 ms118Maximum I 2√t for fusingI 2√t t = 0.1 to 10 ms, no voltage reapplied1830 kA 2√s Low level value of threshold voltage V F(TO)1(16.7 % x π x I F(AV) < I < π x I F(AV)), T J = T J maximum 0.95VHigh level value of threshold voltage V F(TO)2(I > π x I F(AV)), T J = T J maximum1.00Low level values of forward slope resistancer f1(16.7 % x π x I F(AV) < I < π x I F(AV)), T J = T J maximum 0.75m ΩHigh level values of forward slope resistancer f2(I > π x I F(AV)), T J = T J maximum 0.72Maximum forward voltage dropV FMI pk = 1500 A, T J = T J maximum; t p = 10 ms sinusoidal wave2.08VTHERMAL AND MECHANICAL SPECIFICATIONSPARAMETER SYMBOL TEST CONDITIONSSD300C..CUNITS04 TO 2025 TO 32Maximum operating temperature range T J - 40 to 180- 40 to 150°CMaximum storage temperature range T Stg - 55 to 200Maximum thermal resistance,junction to heatsink R thJ-hsDC operation single side cooled 0.163K/W DC operation double side cooled0.073Mounting force, ± 10 %4900 (500)N (kg)Approximate weight 70gCase styleSee dimensions - link at the end of datasheetDO-200AAΔR thJ-hs CONDUCTIONCONDUCTION ANGLESINUSOIDAL CONDUCTION RECTANGULAR CONDUCTION TEST CONDITIONSUNITSSINGLE SIDEDOUBLE SIDESINGLE SIDEDOUBLE SIDE180°0.0170.0170.0110.012T J = T J maximumK/W120°0.0200.0200.0200.02090°0.0250.0250.0270.02760°0.0360.0360.0380.03830°0.0640.0620.0650.062元器件交易网SD300C..C Series Standard Recovery Diodes(Hockey PUK Version), 650 AVishay High Power ProductsFig. 1 - Current Ratings Characteristics Fig. 2 - Current Ratings Characteristics Fig. 3 - Current Ratings Characteristics Fig. 4 - Current Ratings Characteristics Fig. 5 - Current Ratings Characteristics Fig. 6 - Current Ratings Characteristics元器件交易网Document Number: 93544For technical questions, contact: ind-modules@ SD300C..C SeriesVishay High Power Products Standard Recovery Diodes(Hockey PUK Version), 650 AFig. 7 - Current Ratings Characteristics Fig. 8 - Current Ratings Characteristics Fig. 9 - Forward Power Loss CharacteristicsFig. 10 - Forward Power Loss Characteristics Fig. 11 - Maximum Non-Repetitive Surge Current Single and Double Side CooledFig. 12 - Maximum Non-Repetitive Surge Current Single and Double Side Cooled元器件交易网 For technical questions, contact: ind-modules@ Document Number: 93544Document Number: 93544For technical questions, contact: ind-modules@SD300C..C SeriesStandard Recovery Diodes (Hockey PUK Version), 650 AVishay High Power ProductsFig. 13 - Forward Voltage Drop CharacteristicsFig. 14 - Thermal Impedance Z thJC CharacteristicsORDERING INFORMATION TABLELINKS TO RELATED DOCUMENTSDimensions/doc?95248元器件交易网Disclaimer Legal Disclaimer NoticeVishayAll product specifications and data are subject to change without notice.Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, “Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay’s terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.Product names and markings noted herein may be trademarks of their respective owners.元器件交易网Document Number: 。

08机硬件介绍

交换模块(SM)

• 交换模块(SM)具有独立交换功能,主要 用于实现模块内用户的呼叫及接续的全部 功能,并配合AM/CM完成模块间的交换功 能,提供分散数据库管理、呼叫处理、维 护操作等各种功能。 • SM在功能上独立于AM/CM,对外提供各种 接口,如用户线接口、中继线接口等,是 C&C08数字程控交换系统的核心部件之一。

交换模块(SM)的容量示意图

交换模块(SM)的其他特点1

• SM的控制结构采用二级分散控制的方法,一级控 制使用总线方式,由主处理机负责执行;二级控 制使用主从节点邮箱通讯方式,由各节点处理机 负责执行,主处理机还采用双机热备份的方法, 因此,大大提高了设备的可靠性和稳定性。 • 处理能力强 • SM可支持多种主处理机板(MPU),例如CB04 型MPU板,其CPU主频运行于200MHz,普通呼 叫BHCA值达200k。MPU板的内存标准配置为 64MB,可扩充至256MB,新业务新功能对用户 的开放比例达100%。

C&C08交换机机柜

• 机柜的主要作用是放置设备(包括单板、机框、 服务器等),并起到屏蔽、防护、防尘等作用。 C&C08的机柜从用途上来分主要有交换设备机柜、 BAM机柜和直流配电柜三种。 • (1) 交换设备机柜主要用于固定单板、机框、风扇、 工控机等设备。 • (2) BAM机柜中主要用于放置BAM服务器组件, 如服务器、逆变器等。 • (3) 直流配电柜主要用于-48V直流电源的分配和地 线的汇接,提供电源输入母排、电源输出端子以 及地线汇接母排等。

C&C08单板、机框、机柜的简要描述

• 本小节将对C&C08所使用的单板、机框、 机柜作简要的描述。

C&C08交换机单板

• 单板的功能特点 • C&C08的单板具有如下共同特点: • 大量采用ASIC、EPLD、FPGA等先进的集成电路, 单板的集成度高、工艺性好、可靠性高。 • 严格按照统一的硬件设计规范进行设计,大量继 承原有的成熟电路设计经验,单板升级简单。 • 支持热拔插功能。 • 单板内部自带WATCH DOG,在单板出现严重问 题时,能自动复位单板。 • 提供串口打印功能和复位开关。

海湾8302c模块接线及工作原理

海湾8302c模块接线及工作原理嗨,朋友!今天咱们来唠唠海湾8302c模块,这可是个很有趣又很实用的小玩意儿呢!先来说说它的接线吧。

这接线就像是给模块搭积木一样,每一根线都有它自己的小窝。

一般来说,它有好几类线要接。

电源输入线那可是相当重要的,就像人的一日三餐,给模块提供能量。

这两根线就稳稳地接到电源的正负极上,可别接反了哦,不然模块会闹小脾气,不工作的。

就像你把鞋子穿反了,走路肯定不舒服呀。

然后就是信号线啦。

信号线就像是模块的小耳朵,接收来自外界的各种消息。

它要和它对应的设备连好,比如和火灾报警设备相连的时候,那根信号线就像一条秘密通道,把火灾报警设备的“呼喊”准确无误地传给8302c模块。

这个接线的时候可得细心,就像绣花一样,稍微一马虎,信号可能就传不好了。

我有一次就差点接错,还好及时发现,不然就麻烦大啦。

还有输出线呢。

输出线是模块用来对外“说话”的线。

比如说它要控制一些设备的启动或者停止,就靠这输出线啦。

如果把模块比作一个小管家,输出线就是小管家的手,去操作那些需要被控制的东西。

这线要接到对应的设备端子上,而且要保证连接牢固,不然就像你握手的时候没握紧,信息传达不到位呢。

再来说说这海湾8302c模块的工作原理吧。

这模块就像是一个超级智能的小助手。

它一直在那静静地等着信号的到来。

当它的信号线接收到火灾报警设备传来的信号时,就像耳朵听到了紧急呼叫一样,它马上就开始处理这个信息。

它内部的小芯片就像一个超级大脑,迅速判断这个信号是不是真的有危险情况。

如果确定是有情况了,它就通过自己的电路系统,把这个信息转化成一种指令,然后通过输出线把这个指令发送出去。

比如说要启动一个排烟风机,它就会给排烟风机的控制电路发送一个“启动”的指令,就像你对小伙伴喊一声“快跑”一样干脆利落。

而且呀,这个模块还很聪明呢。

它会对信号进行一些过滤和判断,不会一有风吹草动就乱发指令。

就像你不会因为一点小动静就大喊大叫一样。

它会判断这个信号是不是符合火灾报警的特征,如果只是一些小干扰,它就会忽略掉,不会造成不必要的麻烦。

COP8SGC040D3资料

COP8SG Family8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory,Two Comparators and USARTGeneral DescriptionThe COP8SG Family ROM and OTP based microcontrollers are highly integrated COP8™Feature core devices with 8k to 32k memory and advanced features including Analog comparators,and zero external components.These single-chip CMOS devices are suited for more complex applica-tions requiring a full featured controller with larger memory,low EMI,two comparators,and a full-duplex USART.COP8SGx7devices are 100%form-fit-function compatible OTP (One Time Programmable)versions for use in produc-tion or development of the COP8SGx5ROM.Erasable windowed versions (Q3)are available for use with a range of COP8software and hardware development tools.Family features include an 8-bit memory mapped architec-ture,15MHz CKI with 0.67µs instruction cycle,14inter-rupts,three multi-function 16-bit timer/counters with PWM,full duplex USART,MICROWIRE/PLUS ™,two analog com-parators,two power saving HALT/IDLE modes,MIWU,idle timer,on-chip R/C oscillator,high current outputs,user se-lectable options (WATCHDOG ™,4clock/oscillator modes,power-on-reset),2.7V to 5.5V operation,program code se-curity,and 28/40/44pin packages.Devices included in this datasheet are:Device Memory (bytes)RAM (bytes)I/O Pins Packages Temperature COP8SGE58k ROM 25624/36/4028DIP/SOIC,40DIP ,44PLCC/QFP/CSP -40to +85˚C,-40to +125˚C COP8SGG516k ROM 51224/36/4028DIP/SOIC,40DIP ,44PLCC/QFP/CSP -40to +85˚C,-40to +125˚C COP8SGH520k ROM 51224/36/4028DIP/SOIC,40DIP ,44PLCC/QFP/CSP -40to +85˚C,-40to +125˚C COP8SGK524k ROM 51224/36/4028DIP/SOIC,40DIP ,44PLCC/QFP/CSP -40to +85˚C,-40to +125˚C COP8SGR532k ROM 51224/36/4028DIP/SOIC,40DIP ,44PLCC/QFP/CSP -40to +85˚C,-40to +125˚C COP8SGE78k OTP EPROM 25624/36/4028DIP/SOIC,40DIP ,44PLCC/QFP/CSP -40to +85˚C,-40to +125˚C COP8SGR732k OTP EPROM 51224/36/4028DIP/SOIC,40DIP ,44PLCC/QFP/CSP -40to +85˚C,-40to +125˚C COP8SGR7-Q332k EPROM51224/36/4028DIP ,40DIP ,44PLCCRoom Temp.Key Featuresn Low cost 8-bit microcontrollern Quiet Design (low radiated emissions)n Multi-Input Wakeup pins with optional interrupts (8pins)nMask selectable clock options —Crystal oscillator—Crystal oscillator option with on-chip bias resistor —External oscillator —Internal R/C oscillatorn Internal Power-On-Reset —user selectablen WATCHDOG and Clock Monitor Logic —user selectable n Eight high current outputsn 256or 512bytes on-board RAMn8k to 32k ROM or OTP EPROM with security featureCPU Featuresn Versatile easy to use instruction set n 0.67µs instruction cycle timen Fourteen multi-source vectored interrupts servicing —External interrupt /Timers T0—T3—MICROWIRE/PLUS Serial Interface —Multi-Input Wake Up —Software Trap—USART (2;1receive and 1transmit)—Default VIS (default interrupt)n 8-bit Stack Pointer SP (stack in RAM)n Two 8-bit Register Indirect Data Memory Pointers n True bit manipulationn BCD arithmetic instructionsPeripheral Featuresn Multi-Input Wakeup Logicn Three 16-bit timers (T1—T3),each with two 16-bit registers supporting:—Processor Independent PWM mode —External Event Counter mode —Input Capture modeCOP8™is a trademark of National Semiconductor Corporation.October 2001COP8SG Family,8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory,Two Comparators and USART©2001National Semiconductor Corporation Peripheral Features(Continued)n Idle Timer (T0)n MICROWIRE/PLUS Serial Interface (SPI Compatible)n Full Duplex USARTnTwo Analog ComparatorsI/O Featuresn Software selectable I/O options (TRI-STATE ®Output,Push-Pull Output,Weak Pull-Up Input,and High Impedance Input)n Schmitt trigger inputs on ports G and L n Eight high current outputsn Packages:28SO with 24I/O pins,40DIP with 36I/O pins,44PLCC,PQFP and CSP with 40I/O pinsFully Static CMOS Designn Low current drain (typically <4µA)n Two power saving modes:HALT and IDLETemperature Rangen −40˚C to +85˚C,−40˚C to +125˚CDevelopment Supportn Windowed packages for DIP and PLCCn Real time emulation and debug tools availableBlock Diagram10131744FIGURE 1.COP8SGx Block DiagramC O P 8S G F a m i l y 21.0Device Description1.1ARCHITECTUREThe COP8family is based on a modified Harvard architec-ture,which allows data tables to be accessed directly from program memory.This is very important with modern microcontroller-based applications,since program memory is usually ROM or EPROM,while data memory is usually RAM.Consequently data tables need to be contained in non-volatile memory,so they are not lost when the micro-controller is powered down.In a modified Harvard architec-ture,instruction fetch and memory data transfers can be overlapped with a two stage pipeline,which allows the next instruction to be fetched from program memory while the current instruction is being executed using data memory. This is not possible with a Von Neumann single-address bus architecture.The COP8family supports a software stack scheme that allows the user to incorporate many subroutine calls.This capability is important when using High Level Languages. With a hardware stack,the user is limited to a small fixed number of stack levels.1.2INSTRUCTION SETIn today’s8-bit microcontroller application arena cost/ performance,flexibility and time to market are several of the key issues that system designers face in attempting to build well-engineered products that compete in the marketplace. Many of these issues can be addressed through the manner in which a microcontroller’s instruction set handles process-ing tasks.And that’s why COP8family offers a unique and code-efficient instruction set—one that provides the flexibil-ity,functionality,reduced costs and faster time to market that today’s microcontroller based products require.Code efficiency is important because it enables designers to pack more on-chip functionality into less program memory space.Selecting a microcontroller with less program memory size translates into lower system costs,and the added security of knowing that more code can be packed into the available program memory space.1.2.1Key Instruction Set FeaturesThe COP8family incorporates a unique combination of in-struction set features,which provide designers with optimum code efficiency and program memory utilization.Single Byte/Single Cycle Code ExecutionThe efficiency is due to the fact that the majority of instruc-tions are of the single byte variety,resulting in minimum program space.Because compact code does not occupy a substantial amount of program memory space,designers can integrate additional features and functionality into the microcontroller program memory space.Also,the majority instructions executed by the device are single cycle,result-ing in minimum program execution time.In fact,77%of the instructions are single byte single cycle,providing greater code and I/O efficiency,and faster code execution.1.2.2Many Single-Byte,Multifunction InstructionsThe COP8instruction set utilizes many single-byte,multi-function instructions.This enables a single instruction to accomplish multiple functions,such as DRSZ,DCOR,JID, LD(Load)and X(Exchange)instructions with post-incrementing and post-decrementing,to name just a fewexamples.In many cases,the instruction set can simulta-neously execute as many as three functions with the samesingle-byte instruction.JID:(Jump Indirect);Single byte instruction;decodes exter-nal events and jumps to corresponding service routines(analogous to“DO CASE”statements in higher level lan-guages).LAID:(Load Accumulator-Indirect);Single byte look up tableinstruction provides efficient data path from the programmemory to the CPU.This instruction can be used for tablelookup and to read the entire program memory for checksumcalculations.RETSK:(Return Skip);Single byte instruction allows returnfrom subroutine and skips next instruction.Decision tobranch can be made in the subroutine itself,saving code.AUTOINC/DEC:(Auto-Increment/Auto-Decrement);Theseinstructions use the two memory pointers B and X to effi-ciently process a block of data(analogous to“FOR NEXT”inhigher level languages).1.2.3Bit-Level ControlBit-level control over many of the microcontroller’s I/O portsprovides a flexible means to ease layout concerns and saveboard space.All members of the COP8family provide theability to set,reset and test any individual bit in the datamemory address space,including memory-mapped I/O portsand associated registers.1.2.4Register SetThree memory-mapped pointers handle register indirect ad-dressing and software stack pointer functions.The memorydata pointers allow the option of post-incrementing or post-decrementing with the data movement instructions(LOAD/EXCHANGE).And15memory-maped registers allow de-signers to optimize the precise implementation of certainspecific instructions.1.3EMI REDUCTIONThe COP8SGx5family of devices incorporates circuitry thatguards against electromagnetic interference—an increasingproblem in today’s microcontroller board designs.National’spatented EMI reduction technology offers low EMI clockcircuitry,gradual turn-on output drivers(GTOs)and internalICCsmoothing filters,to help circumvent many of the EMI issues influencing embedded control designs.National hasachieved15dB–20dB reduction in EMI transmissions whendesigns have incorporated its patented EMI reducing cir-cuitry.1.4PACKAGING/PIN EFFICIENCYReal estate and board configuration considerations demandmaximum space and pin efficiency,particularly given today’shigh integration and small product form factors.Microcon-troller users try to avoid using large packages to get the I/Orge packages take valuable board space andincreases device cost,two trade-offs that microcontrollerdesigns can ill afford.The COP8family offers a wide range of packages and do notwaste pins:up to90.9%(or40pins in the44-pin package)are devoted to useful I/O.COP8SGFamily3Connection Diagrams10131704Top ViewOrder Number COP8SGXY28M8See NS Package Number M28B Order Number COP8SGXY28N8See NS Package Number N28B Order Number COP8SGR728Q3See NS Package Number D28JQ10131753Top ViewOrder Number COP8SGR7HLQ8See NS Package Number LQA44A10131705Top ViewOrder Number COP8SGXY40N8See NS Package Number N40A Order Number COP8SGR5740Q3See NS Package Number D40KQ10131706Top ViewOrder Number COP8SGXY44V8See NS Package Number V44A Order Number COP8SGR744J3See NS Package Number EL44C10131743Top ViewOrder Number COP8SGXYVEJ8See NS Package Number VEJ44ANote 1:X =E for 8k,G for 16k,H for 20k,K for 24k,R for 32k Y =5for ROM,7for OTPC O P 8S G F a m i l y 4Pinouts for28-,40-and44-Pin PackagesPort Type Alt.Fun 28-PinSO40-Pin DIP44-PinPLCC44-Pin PQFP44-Pin CSPL0I/O MIWU1117171112 L1I/O MIWU or CKX1218181213 L2I/O MIWU or TDX1319191314 L3I/O MIWU or RDX1420201415 L4I/O MIWU or T2A1521251920 L5I/O MIWU or T2B1622262021 L6I/O MIWU or T3A1723272122 L7I/O MIWU or T3B1824282223 G0I/O INT2535393334 G1I/O WDOUT*2636403435 G2I/O T1B2737413536 G3I/O T1A2838423637 G4I/O SO1334142 G5I/O SK2444243 G6I SI3554344 G7I CKO466441 D0O1925292324 D1O2026302425 D2O2127312526 D3O2228322627 D4O29332728 D5O30342829 D6O31352930 D7O32363031 F0I/O79934 F1I/O COMP1IN−8101045 F2I/O COMP1IN+9111156 F3I/O COMP1OUT10121267 F4I/O COMP2IN−131378 F5I/O COMP2IN+141489 F6I/O COMP2OUT1515910 F7I/O16161011 C0I/O39433738 C1I/O40443839 C2I/O113940 C3I/O224041 C4I/O211516 C5I/O221617 C6I/O231718 C7I/O241819 VCC68823 GND2333373132 CKI I57712 RESET I2434383233 *G1operation as WDOUT is controlled by ECON bit2.COP8SG Family 52.1Ordering Information10131708FIGURE 2.Part Numbering SchemeC O P 8S G F a m i l y 63.0Electrical CharacteristicsAbsolute Maximum Ratings(Note2) If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.Supply Voltage(V CC)7VVoltage at Any Pin−0.3V to V CC+0.3VTotal Current into V CCPin(Source)100mATotal Current out ofGND Pin(Sink)110mAStorage TemperatureRange−65˚C to+140˚CESD Protection Level2kV(Human BodyModel) Note2:Absolute maximum ratings indicate limits beyond which damage to the device may occur.DC and AC electrical specifications are not ensured when operating the device at absolute maximum ratings.DC Electrical Characteristics−40˚C≤T A≤+85˚C unless otherwise specified.Parameter Conditions Min Typ Max Units Operating Voltage 2.7 5.5V Power Supply Rise Time1050x106ns V CC Start Voltage to Guarantee POR00.25V Power Supply Ripple(Note4)Peak-to-Peak0.1V cc V Supply Current(Note5)CKI=15MHz V CC=5.5V,t C=0.67µs9.0mA CKI=10MHz V CC=5.5V,t C=1µs 6.0mA CKI=4MHz V CC=4.5V,t C=2.5µs 2.1mA HALT Current(Note6)V CC=5.5V,CKI=0MHz<410µA IDLE Current(Note5)CKI=15MHz V CC=5.5V,t C=0.67µs 2.25mA CKI=10MHz V CC=5.5V,t C=1µs 1.5mA CKI=4MHz V CC=4.5V,t C=2.5µs0.8mA Input Levels(V IH,V IL)RESETLogic High0.8V cc V Logic Low0.2V cc V CKI,All Other InputsLogic High0.7V cc V Logic Low0.2V cc V Internal Bias Resistor for theCrystal/Resonator Oscillator0.512MΩCKI Resistance to V CC or GND when R/COscillator is selectedV CC=5.5V5811kΩHi-Z Input Leakage V CC=5.5V−2+2µA Input Pullup Current V CC=5.5V,V IN=0V−40−250µA G and L Port Input Hysteresis V CC=5.5V0.25V cc V COP8SG Family 7DC Electrical Characteristics(Continued)−40˚C ≤T A ≤+85˚C unless otherwise specified.ParameterConditionsMinTypMaxUnitsOutput Current Levels D Outputs Source V CC =4.5V,V OH =3.3V −0.4mA V CC =2.7V,V OH =1.8V -0.2mA Sink V CC =4.5V,V OL =1.0V 10mA V CC =2.7V,V OL =0.4V 2mA All OthersSource (Weak Pull-Up Mode)V CC =4.5V,V OH =2.7V −10.0−110µA V CC =2.7V,V OH =1.8V -2.5-33µA Source (Push-Pull Mode)V CC =4.5V,V OH =3.3V −0.4mA V CC =2.7V,V OH =1.8V -0.2mA Sink (Push-Pull Mode)V CC =4.5V,V OL =0.4V V CC =2.7V,V OL =0.4V 1.60.7mA mA TRI-STATE LeakageV CC =5.5V−2+2µA Allowable Sink Current per Pin (Note 9)D Outputs and L0to L315mA All Others3mA Maximum Input Current without Latchup (Note 7)Room Temp.±200mA RAM Retention Voltage,Vr 2.0V V CC Rise Time from a V CC ≥2.0V (Note 10)12µsEPROM Data Retenton (Note 8),(Note 9)T A =55˚C >29years Input Capacitance (Note 9)7pF Load Capacitance on D2(Note 9)1000pFAC Electrical Characteristics−40˚C ≤T A ≤+85˚C unless otherwise specified.ParameterConditionsMin Typ Max Units Instruction Cycle Time (t C )Crystal/Resonator,External 4.5V ≤V CC ≤5.5V 0.67µs 2.7V ≤V CC ≤4.5V 2µsR/C Oscillator (Internal) 4.5V ≤V CC ≤5.5V 2µs Frequency Variation (Note 9) 4.5V ≤V CC ≤5.5V ±35%External CKI Clock Duty Cycle (Note 9)fr =Max4555%Rise Time (Note 9)fr =10MHz Ext Clock 8ns Fall Time (Note 9)fr =10MHz Ext Clock5ns MICROWIRE Setup Time (t UWS )(Note 11)20ns MICROWIRE Hold Time (t UWH )(Note 11)56nsMICROWIRE Output Propagation Delay (t UPD )(Note 11)220nsInput Pulse Width (Note 9)Interrupt Input High Time 1t C Interrupt Input Low Time 1t C Timer 1,2,3,Input High Time 1t C Timer 12,3,Input Low Time 1t C Reset Pulse Width1µsNote 3:t C =Instruction cycle time.C O P 8S G F a m i l y 8AC Electrical Characteristics(Continued)Note4:Maximum rate of voltage change must be<0.5V/ms.Note5:Supply and IDLE currents are measured with CKI driven with a square wave Oscillator,External Oscillator,inputs connected to V CC and outputs driven low but not connected to a load.Note6:The HALT mode will stop CKI from oscillating in the R/C and the Crystal configurations.In the R/C configuration,CKI is forced high internally.In the crystal or external configuration,CKI is TRI-STATE.Measurement of I DD HALT is done with device neither sourcing nor sinking current;with L.F,C,G0,and G2–G5 programmed as low outputs and not driving a load;all outputs programmed low and not driving a load;all inputs tied to V CC;clock monitor disabled.Parameter refers to HALT mode entered via setting bit7of the G Port data register.Note7:Pins G6and RESET are designed with a high voltage input network.These pins allow input voltages>V CC and the pins will have sink current to V CC when biased at voltages>V CC(the pins do not have source current when biased at a voltage below V CC).The effective resistance to V CC is750Ω(typical).These two pins will not latch up.The voltage at the pins must be limited to<14V.WARNING:Voltages in excess of14V will cause damage to the pins.This warning excludes ESD transients.Note8:National Semiconductor uses the High Temperature Storage Life(HTSL)test to evaluate the data retention capabilities of the EPROM memory cells used in our OTP microcontrollers.Qualification devices have been stressed at150˚C for1000hours.Under these conditions,our EPROM cells exhibit data retention capabilities in excess of29years.This is based on an activation energy of0.7eV derated to55˚C.Note9:Parameter characterized but not tested.Note10:Rise times faster than the minimum specification may trigger an internal power-on-reset.Note11:MICROWIRE Setup and Hold Times and Propagation Delays are referenced to the appropriate edge of the MICROWIRE clock.See and the MICROWIRE operation description.Comparators AC and DC CharacteristicsV CC=5V,−40˚C≤T A≤+85˚C.Parameter Conditions Min Typ Max Units Input Offset Voltage(Note12)0.4V≤V IN≤V CC−1.5V±5±15mV Input Common Mode Voltage Range0.4V CC−1.5V Voltage Gain100dB Low Level Output Current V OL=0.4V−1.6mA High Level Output Current V OH=V CC−0.4V 1.6mA DC Supply Current per Comparator(When Enabled)150µAResponse Time(Note13)200mV step input100mV Overdrive,100pF Load600nsComparator Enable Time(Note14)600ns Note12:The comparator inputs are high impedance port inputs and,as such,input current is limited to port input leakage current.Note13:Response time is measured from a step input to a valid logic level at the comparator output.software response time is dependent of instruction execution. Note14:Comparator enable time is that delay time required between the end of the instruction cycle that enables the comparator and using the output of the comparator,either by hardware or by software.10131709FIGURE3.MICROWIRE/PLUS Timing COP8SG Family 9Absolute Maximum Ratings(Note 2)If Military/Aerospace specified devices are required,please contact the National Semiconductor Sales Office/Distributors for availability and specifications.Supply Voltage (V CC )7VVoltage at Any Pin −0.3V to V CC +0.3VTotal Current into V CC Pin (Source)100mA Total Current out of GND Pin (Sink)110mAStorage Temperature Range−65˚C to +140˚C ESD Protection Level2kV (Human BodyModel)Note 15:Absolute maximum ratings indicate limits beyond which damage to the device may occur.DC and AC electrical specifications are not ensured when operating the device at absolute maximum ratings.DC Electrical Characteristics−40˚C ≤T A ≤+125˚C unless otherwise specified.ParameterConditionsMin TypMax Units Operating Voltage 4.5 5.5V Power Supply Rise Time1050x 106ns V CC Start Voltage to Guarantee POR 00.25V Power Supply Ripple (Note 4)Peak-to-Peak0.1V ccVSupply Current (Note 5)CKI =10MHz V CC =5.5V,t C =1µs 6.0mA CKI =4MHz V CC =4.5V,t C =2.5µs 2.1mA HALT Current (Note 6)V CC =5.5V,CKI =0MHz<410µAIDLE Current (Note 5)CKI =10MHz V CC =5.5V,t C =1µs 1.5mA CKI =4MHz V CC =4.5V,t C =2.5µs0.8mAInput Levels (V IH ,V IL )RESET Logic High 0.8V ccV Logic Low 0.2V ccVCKI,All Other Inputs Logic High 0.7V ccV Logic Low0.2V ccV Internal Bias Resistor for the Crystal/Resonator Oscillator0.512M ΩCKI Resistance to V CC or GND when R/C Oscillator is selected V CC =5.5V 5811k ΩHi-Z Input Leakage V CC =5.5V−5+5µA Input Pullup CurrentV CC =5.5V,V IN =0V −35−400µA G and L Port Input Hysteresis V CC =5.5V0.25V ccVOutput Current Levels D Outputs Source V CC =4.5V,V OH =3.3V −0.4mA Sink V CC =4.5V,V OL =1.0V9mAAll OthersSource (Weak Pull-Up Mode)V CC =4.5V,V OH =2.7V −9−140µA Source (Push-Pull Mode)V CC =4.5V,V OH =3.3V −0.4mA Sink (Push-Pull Mode)V CC =4.5V,V OL =0.4V 1.4mA TRI-STATE LeakageV CC =5.5V−5+5µAAllowable Sink Current per Pin (Note 9)D Outputs and L0to L31515mA All Others33mAC O P 8S G F a m i l y 10DC Electrical Characteristics(Continued)−40˚C≤T A≤+125˚C unless otherwise specified.Parameter Conditions Min Typ Max UnitsMaximum Input Current without Latchup (Note7)Room Temp.±200mARAM Retention Voltage,Vr 2.0V V CC Rise Time from a V CC≥2.0V(Note10)12µs EPROM Data Retenton(Note8),(Note9)T A=55˚C>29years Input Capacitance(Note9)7pF Load Capacitance on D2(Note9)1000pF COP8SG FamilyAC Electrical Characteristics−40˚C ≤T A ≤+125˚C unless otherwise specified.ParameterConditionsMinTypMaxUnitsInstruction Cycle Time (t C )Crystal/Resonator,External 4.5V ≤V CC ≤5.5V 1µs R/C Oscillator (Internal) 4.5V ≤V CC ≤5.5V 2µs Frequency Variation (Note 9) 4.5V ≤V CC ≤5.5V ±35%External CKI Clock Duty Cycle (Note 9)fr =Max4555%Rise Time (Note 9)fr =10MHz Ext Clock 12ns Fall Time (Note 9)fr =10MHz Ext Clock8ns MICROWIRE Setup Time (t UWS )(Note 11)20ns MICROWIRE Hold Time (t UWH )(Note 11)56ns MICROWIRE Output Propagation Delay (t UPD )(Note 11)220nsInput Pulse Width (Note 9)Interrupt Input High Time 1t C Interrupt Input Low Time 1t C Timer 1,2,3,Input High Time 1t C Timer 12,3,Input Low Time 1t C Reset Pulse Width1µsComparators AC and DC CharacteristicsV CC =5V,−40˚C ≤T A ≤+125˚C.ParameterConditionsMinTypMaxUnits Input Offset Voltage (Note 12)0.4V ≤V IN ≤V CC −1.5V±5±25mV Input Common Mode Voltage Range 0.4V CC −1.5V Voltage Gain100dB Low Level Output Current V OL =0.4V −1.6mA High Level Output CurrentV OH =V CC −0.4V1.6mA DC Supply Current per Comparator (When Enabled)150µAResponse Time (Note 13)200mV step input 100mV Overdrive,600ns Comparator Enable Time600nsC O P 8S G F a m i l yTypical Performance Characteristics TA=25˚C(unless otherwise specified)10131749101317501013175110131752COP8SG Family4.0Pin DescriptionsThe COP8SGx I/O structure enables designers to reconfig-ure the microcontroller’s I/O functions with a single instruc-tion.Each individual I/O pin can be independently configured as output pin low,output high,input with high impedance or input with weak pull-up device.A typical example is the use of I/O pins as the keyboard matrix input lines.The input lines can be programmed with internal weak pull-ups so that the input lines read logic high when the keys are all open.With a key closure,the corresponding input line will read a logic zero since the weak pull-up can easily be overdriven.When the key is released,the internal weak pull-up will pull the input line back to logic high.This eliminates the need for external pull-up resistors.The high current options are avail-able for driving LEDs,motors and speakers.This flexibility helps to ensure a cleaner design,with less external compo-nents and lower costs.Below is the general description of all available pins.V CC and GND are the power supply pins.All V CC and GND pins must be connected.CKI is the clock input.This can come from the Internal R/C oscillator,external,or a crystal oscillator (in conjunction with CKO).See Oscillator Description section.RESET is the master reset input.See Reset description section.Each device contains four bidirectional 8-bit I/O ports (C,G,L and F),where each individual bit may be independently configured as an input (Schmitt trigger inputs on ports L and G),output or TRI-STATE under program control.Three data memory address locations are allocated for each of these I/O ports.Each I/O port has two associated 8-bit memory mapped registers,the CONFIGURATION register and the output DATA register.A memory mapped address is also reserved for the input pins of each I/O port.(See the memory map for the various addresses associated with the I/O ports.)Figure 4shows the I/O port configurations.The DATA and CONFIGURATION registers allow for each port bit to be individually configured under software control as shown be-low:CONFIGURATIONRegisterDATA RegisterPort Set-Up00Hi-Z Input(TRI-STATE Output)01Input with Weak Pull-Up 10Push-Pull Zero Output 11Push-Pull One OutputPort L is an 8-bit I/O port.All L-pins have Schmitt triggers on the inputs.Port L supports the Multi-Input Wake Up feature on all eight pins.Port L has the following alternate pin functions:L7Multi-input Wakeup or T3B (Timer T3B Input)L6Multi-input Wakeup or T3A (Timer T3A Input)L5Multi-input Wakeup or T2B (Timer T2B Input)L4Multi-input Wakeup or T2A (Timer T2A Input)L3Multi-input Wakeup and/or RDX (USART Receive)L2Multi-input Wakeup or TDX (USART Transmit)L1Multi-input Wakeup and/or CKX (USART Clock)L0Multi-input WakeupPort G is an 8-bit port.Pin G0,G2–G5are bi-directional I/O ports.Pin G6is always a general purpose Hi-Z input.All pins have Schmitt Triggers on their inputs.Pin G1serves as thededicated WATCHDOG output with weak pullup if WATCHDOG feature is selected by the Mask Option reg-ister.The pin is a general purpose I/O if WATCHDOG feature is not selected.If WATCHDOG feature is selected,bit 1of the Port G configuration and data register does not have any effect on Pin G1setup.Pin G7is either input or output depending on the oscillator option selected.With the crystal oscillator option selected,G7serves as the dedicated output pin for the CKO clock output.With the internal R/C or the external oscillator option selected,G7serves as a gen-eral purpose Hi-Z input pin and is also used to bring the device out of HALT mode with a low to high transition on G7.Since G6is an input only pin and G7is the dedicated CKO clock output pin (crystal clock option)or general purpose input (R/C or external clock option),the associated bits in the data and configuration registers for G6and G7are used for special purpose functions as outlined below.Reading the G6and G7data bits will return zeroes.Each device will be placed in the HALT mode by writing a “1”to bit 7of the Port G Data Register.Similarly the device will be placed in the IDLE mode by writing a “1”to bit 6of the Port G Data Register.Writing a “1”to bit 6of the Port G Configuration Register enables the MICROWIRE/PLUS to operate with the alter-nate phase of the SK clock.The G7configuration bit,if set high,enables the clock start up delay after HALT when the R/C clock configuration is used.Config.Reg.Data Reg.G7CLKDLY HALT G6Alternate SKIDLEPort G has the following alternate features:G7CKO Oscillator dedicated output or general purposeinputG6SI (MICROWIRE Serial Data Input)G5SK (MICROWIRE Serial Clock)G4SO (MICROWIRE Serial Data Output)G3T1A (Timer T1I/O)G2T1B (Timer T1Capture Input)G1WDOUT WATCHDOG and/or CLock Monitor if WATCH-DOG enabled,otherwise it is a general purpose I/O G0INTR (External Interrupt Input)Port C is an 8-bit I/O port.The 40-pin device does not have a full complement of Port C pins.The unavailable pins are not terminated.A read operation on these unterminated pins will return unpredictable values.The 28pin device do not offer Port C.On this device,the associated Port C Data and Configuration registers should not be used.Port F is an 8-bit I/O port.The 28--pin device does not have a full complement of Port F pins.The unavailable pins are not terminated.A read operation on these unterminated pins will return unpredictable values.Port F1–F3are used for Comparator 1.Port F4–F6are used for Comparator 2.The Port F has the following alternate features:F6COMP2OUT (Comparator 2Output)F5COMP2+IN (Comparator 2Positive Input)F4COMP2-IN (Comparator 2Negative Input)F3COMP1OUT (Comparator 1Output)F2COMP1+IN (Comparator 1Positive Input)F1COMP1-IN (Comparator 1Negative Input)C O P 8S G F a m i l y。

AT88SC0808CA-MP资料