第2讲 第2章 F2812结构与最小系统 2013-3-4

F2812教材

使用PC、通用的C代码编译器例如实现 代码实例:

#include <stdio.h> int data[4]={1,2,3,4}; int coeff[4]={8,6,4,2}; int main(void) { int i; int result =0; for (i=0;i<4;i++) result += data[i]*coeff[i]; printf("%i",result); return 0; }

Data Bus

32 16 32

操作数1

XT (32) or T/TL

MULTIPLIER 32 x 32 or Dual 16 x 16 P (32) or PH/PL

32

32

16/32 8/16/32

Shift R/L (0-16)

32

操作码

8/16 32

Shift R/L (0-16)

乘法器结果

使用DSP硬件平台以及Ti的C编译器来实现 代码实例:

int data[4]={1,2,3,4}; int coeff[4]={8,6,4,2}; int main(void) { int i; int result =0; for (i=0;i<4;i++) result += data[i]*coeff[i]; printf("%i",result); return 0; }

03 C2 89 45 F8 EB D2

mov

add mov jmp

eax,dword ptr [ult]

eax,edx dword ptr [result],eax main+19h (411969h)

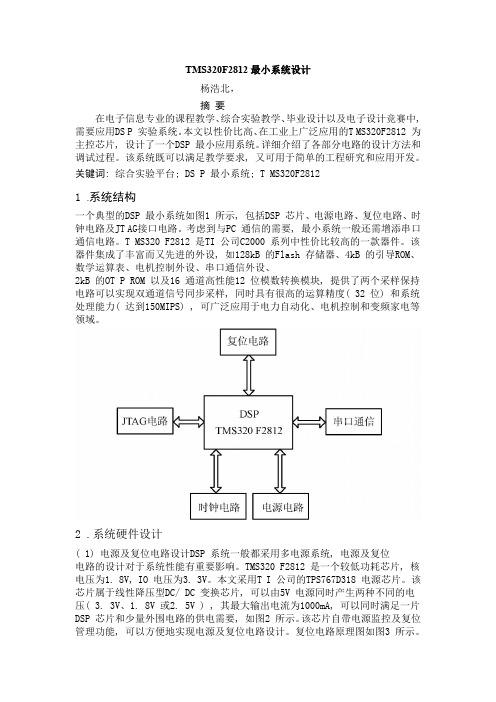

TMS320F2812最小系统设计

TMS320F2812最小系统设计杨浩北,摘要在电子信息专业的课程教学、综合实验教学、毕业设计以及电子设计竞赛中, 需要应用DS P 实验系统。

本文以性价比高、在工业上广泛应用的T MS320F2812 为主控芯片, 设计了一个DSP 最小应用系统。

详细介绍了各部分电路的设计方法和调试过程。

该系统既可以满足教学要求, 又可用于简单的工程研究和应用开发。

关键词: 综合实验平台; DS P 最小系统; T MS320F28121 .系统结构一个典型的DSP 最小系统如图1 所示, 包括DSP 芯片、电源电路、复位电路、时钟电路及JT AG接口电路。

考虑到与PC 通信的需要, 最小系统一般还需增添串口通信电路。

T MS320 F2812 是TI 公司C2000 系列中性价比较高的一款器件。

该器件集成了丰富而又先进的外设, 如128kB 的Flash 存储器、4kB 的引导ROM、数学运算表、电机控制外设、串口通信外设、2kB 的OT P ROM 以及16 通道高性能12 位模数转换模块, 提供了两个采样保持电路可以实现双通道信号同步采样, 同时具有很高的运算精度( 32 位) 和系统处理能力( 达到150MIPS) , 可广泛应用于电力自动化、电机控制和变频家电等领域。

2 .系统硬件设计( 1) 电源及复位电路设计DSP 系统一般都采用多电源系统, 电源及复位电路的设计对于系统性能有重要影响。

TMS320 F2812 是一个较低功耗芯片, 核电压为1. 8V, IO 电压为3. 3V。

本文采用T I 公司的TPS767D318 电源芯片。

该芯片属于线性降压型DC/ DC 变换芯片, 可以由5V 电源同时产生两种不同的电压( 3. 3V、1. 8V 或2. 5V ) , 其最大输出电流为1000mA, 可以同时满足一片DSP 芯片和少量外围电路的供电需要, 如图2 所示。

该芯片自带电源监控及复位管理功能, 可以方便地实现电源及复位电路设计。

基于TMS320F2812的DSP最小系统设计毕业设计论文

题目:基于TMS320F2812的DSP最小系统设计要求:TMS320F2812的DSP最小系统设计包括两个模块,即硬件设计模块和软件检测模块。

硬件设计模块包括电源设计、复位电路设计、时钟电路设计、存储器设计、JTAC接口设计等。

软件检测模块需要编写测试程序。

用Protel软件绘制原理图和PCB图。

从理论上分析,设计的系统要满足基本的信号处理要求。

DSP主要应用在数字信号处理中,目的是为了能够满足实时信号处理的要求,因此需要将数字信号处理中的常用运算执行的尽可能快。

这就决定了DSP的特点和关键技术。

适合数字信号处理的技术:DSP包涵乘法器,累加器,特殊地址发生器,领开销循环等;提高处理速度的技术:流水线技术,并行处理技术,超常指令等。

DSP对元件值的容限不敏感,受温度、环境等外部参与影响小;容易实现集成;VLSI 可以时分复用,共享处理器;方便调整处理器的系数实现自适应滤波;可实现模拟处理不能实现的功能:线性相位、多抽样率处理、级联、易于存储等;可用于频率非常低的信号。

关键词: TMS320F2812,CCS3.3,Protel99SE软件目录第1章绪论第2章系统设计2.1系统方案介绍2.2 系统结构设计第3章硬件电路设计3.1 TMS320F2812芯片介绍3.2电源及复位电路设计3.3 时钟电路设计3.4 DSP与JTAG接口设计3.5 DSP的串行接口设计3.6 通用扩展口设计3.7 总体电路原理图设计第4章软件设计4.1 程序设计4.2 仿真调试总结参考文献附录1:总体电路图附录2:程序代码第1章绪论数字化已成为电子、通信和信息技术的发展趋势与潮流。

在这种趋势与潮流的推动下,数字信号处理的理论与实现手段获得了快速的发展,已成为当代发展最快的学科之一。

而DSP芯片作为数字信号处理,尤其是实时数字信号处理的主要方法和手段,自20世纪70年代末、80年代初诞生以来,无论在性能上还是在价格上,都取得了突破性的迅猛发展。

第2课 F2812系统结构

BGA封装的F2812

179引脚GHH球形网格阵列BGA(Ball Grid Array)

11

BGA封装的机械尺寸

12

贴片封装的F2812

176引脚LQFP封装顶视图

128引脚PBK封装顶视图

13

贴片封装的机械尺寸

14

F2812电源

2812采用了高性能的静态CMOS技术,时钟 频率可达150MHZ(6.67ns),其核心电压 为1.8V,I/O口电压3.3V,Flash编程电压也 为3.3V。 在设计2812电源部分的时候,需要将常用 的5V电压转换成1.8V和3.3V的电压之后, 才能供给2812。

8

TMS320F2812的主要特点

4) 片上存储器 --有多达128K×16的FLASH存储器 (4个8K×16和 6个16K×16) --有多达128K×16的ROM 5)外部存储器接口 --有多达1MB的寻址空间 --三个独立的片选端 6)时钟与系统控制 --支持动态的改变锁相环(PLL)的频率 --片上振荡器 7)三个外部中断 8)外部中断扩展(PIE)模块,支持45外部中 断

MUX

Data Memory

XAR31-16

XAR15-0

=AR7-0

28

C28x Pipeline

A F1 F2 D1 D2 R1 R2 B C D E F G H

F1: 取指令地址 F2: 取指令内容 D1: 32/16判断边界 D2: 取指译码 R1: 操作数地址 R2: 取操作数 E: 指令执行 W: 写内容回存储单元

Program Bus

32-bit 定点DSP

32 x 32 bit MAC

2次单周期16 x 16 MAC (DMAC) 快速中断响应机制 单周期读、写、修改指令

TMS320F2812中文手册

TMS320F2812中文手册第1章芯片结构及性能概述TMS320C2000系列是美国TI公司推出的最佳测控应用的定点DSP芯片,其主流产品分为四个系列:C20x、C24x、C27x和C28x。

C20x可用于通信设备、数字相机、嵌入式家电设备等;C24x主要用于数字马达控制、电机控制、工业自动化、电力转换系统等。

近年来,TI公司又推出了具有更高性能的改进型C27x和C28x系列芯片,进一步增强了芯片的接口能力和嵌入功能,从而拓宽了数字信号处理器的应用领域。

TMS320C28x系列是TI公司最新推出的DSP芯片,是目前国际市场上最先进、功能最强大的32位定点DSP芯片。

它既具有数字信号处理能力,又具有强大的事件管理能力和嵌入式控制功能,特别适用于有大批量数据处理的测控场合,如工业自动化控制、电力电子技术应用、智能化仪器仪表及电机、马达伺服控制系统等。

本章将介绍TMS320C28x系列芯片的结构、性能及特点,并给出该系列芯片的引脚分布及引脚功能。

1.1 TMS320C28x 系列芯片的结构及性能C28x系列的主要片种为TMS320F2810和TMS320F2812。

两种芯片的差别是:F2812内含128K×16位的片内Flash存储器,有外部存储器接口,而F2810仅有64K×16位的片内Flash存储器,且无外部存储器接口。

其硬件特征如表1-1所示。

表1-1 硬件特征特征 F2810 F2812 指令周期(150MHz) 6.67ns 6.67ns SRAM(16位/字)18K 18K 3.3V片内Flash(16位/字) 64K 128K 片内Flash/SRAM的密钥有有有有 Boot ROM掩膜ROM 有有外部存储器接口无有事件管理器A和B(EVA和EVB)EVA、EVB EVA、EVB*通用定时器 4 4*比较寄存器/脉宽调制 16 16*捕获/正交解码脉冲电路 6/2 6/2 看门狗定时器有有 12位的ADC 有有*通道数 16 16TMS320C28x系列DSP的CPU与外设(上) ?2?续表特征 F2810 F2812 32位的CPU定时器 3 3 串行外围接口有有串行通信接口(SCI)A和B SCIA、SCIB SCIA、SCIB 控制器局域网络有有多通道缓冲串行接口有有数字输入/输出引脚(共享)有有外部中断源 3 3 核心电压1.8V 核心电压1.8V 供电电压 I/O电压3.3V I/O电压3.3V 封装128针PBK 179针GHH,176针PGF 温度选择‡ A:-40? ~ +85? PGF和GHH PBK S:-40? ~ +125? 仅适用于TMS 仅适用于TMS 产品状况‡‡产品预览(PP) AI AI 高级信息(AI)(TMP)‡‡‡ (TMP)‡‡‡ 产品数据(PD)注:‡ “S”是温度选择(-40? ~ +125?)的特征化数据,仅对TMS是适用的。

F2812中文手册

第1章芯片结构及性能概述TMS320C2000系列是美国TI公司推出的最佳测控应用的定点DSP芯片,其主流产品分为四个系列:C20x、C24x、C27x和C28x。

C20x可用于通信设备、数字相机、嵌入式家电设备等;C24x主要用于数字马达控制、电机控制、工业自动化、电力转换系统等。

近年来,TI公司又推出了具有更高性能的改进型C27x和C28x系列芯片,进一步增强了芯片的接口能力和嵌入功能,从而拓宽了数字信号处理器的应用领域。

TMS320C28x系列是TI公司最新推出的DSP芯片,是目前国际市场上最先进、功能最强大的32位定点DSP芯片。

它既具有数字信号处理能力,又具有强大的事件管理能力和嵌入式控制功能,特别适用于有大批量数据处理的测控场合,如工业自动化控制、电力电子技术应用、智能化仪器仪表及电机、马达伺服控制系统等。

本章将介绍TMS320C28x 系列芯片的结构、性能及特点,并给出该系列芯片的引脚分布及引脚功能。

1.1 TMS320C28x系列芯片的结构及性能C28x系列的主要片种为TMS320F2810和TMS320F2812。

两种芯片的差别是:F2812内含128K×16位的片内Flash存储器,有外部存储器接口,而F2810仅有64K×16位的片内Flash存储器,且无外部存储器接口。

其硬件特征如表1-1所示。

表1-1 硬件特征注:‡“S”是温度选择(-40℃~ +125℃)的特征化数据,仅对TMS是适用的。

‡‡产品预览(PP):在开发阶段的形成和设计中与产品有关的信息,特征数据和其他规格是设计的目标。

TI保留了正确的东西,更换或者终止了一些没有注意到的产品。

高级信息(AI):在开发阶段的取样和试制中与新产品有关的信息,特征数据和其他规格用以改变那些没有注意到的东西。

产品数据(PD):是当前公布的数据信息,产品遵守TI的每项标准保修规格,但产品加工不包括对所有参数的测试。

DSP2系统与实验教程_2812初识

第二章TMS320F2812的结构、资源、性能尽管TI公司将其DSP家族沿着2000、5000、6000的道路进行发展,但在TI家族,将其放到了MCU范畴里,处于高性能MCU的低端产品,再往上走就是ARM芯片了。

是因为2000系列对于纯数字信号处理方面工作较弱,但芯片集成了大量用于自动化的模块,定时器、PWM、捕获、中断、SCI、SPI、CAN模块等等,更接近于MCU,但2000系列不断地发展,从定点到浮点,双核DSP(PICCOLO系列的28035中的CLA核就是),功能更集中、管脚的复用率更大、工作频率更高,软件的硬件化更强大,芯片价格更加便宜……【PiccoloF2802x/3x/5x/6x/7x、Delfino F2833x/F2837x 】今天我就给大家介绍一下28系列的经典芯片2812。

作为2000系列大家族中的一员,我们不得不提一下2000系列的DSP第一节时钟、复位及JTAG引脚1.1 时钟2812是32位的定点DSP,它采用高性能的CMOS技术,他能达到150Mhz的频率,因此他的指令周期(机器周期)为6.67ns。

我们怎么得到150Mhz主频?通常常采用外部接入30Mhz 的晶振,配上2个24Pf的电容,接入X1/XCLKIN引脚。

在经过DSP内部的PLL倍频之后达到150Mhz的主频sysclkout。

这个频率一方面通过XCLKOUT引脚输出,另一方面作为系统内其他外设的频率输入。

The XCLKOUT signal is active when reset is active. Since XCLKOUT should reflect SYSCLKOUT/4 when reset is low, you can monitor this signal to detect if the device is being properly clocked during debug.There is no internal pullup or pulldown on the XCLKOUT pin. 1.2 电源2812采用功耗的设计模式,其内部有三类电压:内核电压:1.8vIO口电压:3.3vFlash编程电压:3.3v现在我们讨论一下IO口电压:如果我们对IO口输入的电压超过3.3v,那么就会烧坏DSP。

第2讲 F2812结构(xkj201611)4

合肥工业大学电气与自动化工程学院DSP实验室

2016-11-

C28x CPU

MCU/DSP balancing code density & execution time.

Program Bus

Supports 32-bit instructions for improved execution time;

VDDAIO VSSAIO

VDDA1 VDDA2 VSSA1 VSSA2

VDD1 VSS1

VDD2 VDD3 VDD4 VDD5 VDD6 VDD7 VDD8 VDD9 VDD10

VDDIO5 VDDIO4 VDDIO3 VDDIO2 VDDIO1

ADCREFP ADCREFM ADCRESEXT AVSSREFBG AVDDREFBG ADCLO ADCBGREFIN

160 77 76 119 18 43 80 85 103 108 111 118 121 125 130 132 138 141 144 148 152 156 158 21 24 27 30 33 36 39 54 65 68 73 74 96 97 139 147 44 88 133 84 42 51 161 17 159 82

CAN

EX中断

TEST2 TEST1 TESTSEL 6IOF9-MCLKRA GPIOF10-MFSXA GPIOF11-MFSRA GPIOF12-MDXA GPIOF13-MDRA

GPIOF6-CANTXA GPIOF7-CANRXA

149 151 150

ADC

电源

时钟 复位 外 部 地 址 总 线 外 部 数 据 总 线 外部总 线控制

GPIO

F2812中文手册

第1章芯片结构及性能概述TMS320C2000系列是美国TI公司推出的最佳测控应用的定点DSP芯片,其主流产品分为四个系列:C20x、C24x、C27x和C28x。

C20x可用于通信设备、数字相机、嵌入式家电设备等;C24x主要用于数字马达控制、电机控制、工业自动化、电力转换系统等。

近年来,TI公司又推出了具有更高性能的改进型C27x和C28x系列芯片,进一步增强了芯片的接口能力和嵌入功能,从而拓宽了数字信号处理器的应用领域。

TMS320C28x系列是TI公司最新推出的DSP芯片,是目前国际市场上最先进、功能最强大的32位定点DSP芯片。

它既具有数字信号处理能力,又具有强大的事件管理能力和嵌入式控制功能,特别适用于有大批量数据处理的测控场合,如工业自动化控制、电力电子技术应用、智能化仪器仪表及电机、马达伺服控制系统等。

本章将介绍TMS320C28x 系列芯片的结构、性能及特点,并给出该系列芯片的引脚分布及引脚功能。

1.1 TMS320C28x系列芯片的结构及性能C28x系列的主要片种为TMS320F2810和TMS320F2812。

两种芯片的差别是:F2812内含128K×16位的片内Flash存储器,有外部存储器接口,而F2810仅有64K×16位的片内Flash存储器,且无外部存储器接口。

其硬件特征如表1-1所示。

表1-1 硬件特征注:‡“S”是温度选择(-40℃~ +125℃)的特征化数据,仅对TMS是适用的。

‡‡产品预览(PP):在开发阶段的形成和设计中与产品有关的信息,特征数据和其他规格是设计的目标。

TI保留了正确的东西,更换或者终止了一些没有注意到的产品。

高级信息(AI):在开发阶段的取样和试制中与新产品有关的信息,特征数据和其他规格用以改变那些没有注意到的东西。

产品数据(PD):是当前公布的数据信息,产品遵守TI的每项标准保修规格,但产品加工不包括对所有参数的测试。

第2章TMS320F2812DSP内部结构

该产品的主要特点是:

1.运算速度 单周期指令执行时间为50、35或25ns; 即运算能力为20、28.5或40MIPS。

4

2. 兼容性

源代码与TMS320C1X/C2X全部产品兼容; 产品与TMS320C5X产品向上兼容;

5

3. 片内存储器

内部配置数量不同的RAM和ROM存 储器,有的芯片还配有闪速存储器Flash。 利用闪速存储器存储程序,不仅能降 低成本,减小体积,而且系统升级也比较 方便。

27

2.1.1 TMS320F2812CPU内部结构

除以上几个主要部分外,该控制器还包 含如指令队列、指令译码逻辑、中断处理 逻辑等控制单元。

28

2.1.1 TMS320F2812CPU内部结构

F2812 CPU的主要寄存器 • 累加器(ACC,AH、AL) • 辅助寄存器(XAR0-XAR7,AR0-AR7) • 状态寄存器(ST0) • 状态寄存器(ST1)

32 32

16/32 8/16/32

Shift R/L (0-16)

32

8/16 32

程序存储 区

Shift R/L (0-16)

数据存储区

32

ALU (32)

32 ACC (32) AH (16) AL (16)

AL.LSB AH.MSB AH.LSB AL.MSB

操作数2 来自于寄存器

• 32

Shift R/L (0-16)

1 1 1 1 2 1 1 1 1 1 1

1 1 1 1 1 1 1 1 1 1 1

8

表 1.2 TMS320C24X 内部资源配置

设备 RAM ROM FLASH BOOT 通用 看门 PWM SPI (16 位) (16 位) (16 位) ROM 定时器 狗 通道 _ _ _ _ _ 32K 16K 6K 8K _ _ 4K _ 32K 32K 16K 8K 8K _ _ _ _ 8K 8K _ 16K 256 256 256 256 256 _ _ _ _ _ _ _ _ 4 4 2 2 2 4 4 2 2 2 2 2 3 Y Y Y Y Y Y Y Y Y Y Y Y Y 16 16 8 8 7 16 16 8 7 8 8 8 12 Y Y Y _ _ Y Y _ _ Y Y _ Y SCI CAN Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y _ _ Y _ _ _ Y Y _ _ A/D 通道 16ch 16ch 8ch 8ch 5ch 16ch 16ch 8ch 5ch 8ch 8ch 8ch 16ch I/O 引脚 41 41 21 21 13 41 41 21 32 26 26 26 28 电压 3.3 3.3 3.3 3.3 3.3 3.3 3.3 3.3 3.3 5 5 5 5 MIPS 40 40 40 40 40 40 40 40 40 20 20 20 20

TMS320F2812最小系统设计(word文档良心出品)

TMS320F2812最小系统设计杨浩北,摘要在电子信息专业的课程教学、综合实验教学、毕业设计以及电子设计竞赛中, 需要应用DS P 实验系统。

本文以性价比高、在工业上广泛应用的T MS320F2812 为主控芯片, 设计了一个DSP 最小应用系统。

详细介绍了各部分电路的设计方法和调试过程。

该系统既可以满足教学要求, 又可用于简单的工程研究和应用开发。

关键词: 综合实验平台; DS P 最小系统; T MS320F28121 .系统结构一个典型的DSP 最小系统如图1 所示, 包括DSP 芯片、电源电路、复位电路、时钟电路及JT AG接口电路。

考虑到与PC 通信的需要, 最小系统一般还需增添串口通信电路。

T MS320 F2812 是TI 公司C2000 系列中性价比较高的一款器件。

该器件集成了丰富而又先进的外设, 如128kB 的Flash 存储器、4kB 的引导ROM、数学运算表、电机控制外设、串口通信外设、2kB 的OT P ROM 以及16 通道高性能12 位模数转换模块, 提供了两个采样保持电路可以实现双通道信号同步采样, 同时具有很高的运算精度( 32 位) 和系统处理能力( 达到150MIPS) , 可广泛应用于电力自动化、电机控制和变频家电等领域。

2 .系统硬件设计( 1) 电源及复位电路设计DSP 系统一般都采用多电源系统, 电源及复位电路的设计对于系统性能有重要影响。

TMS320 F2812 是一个较低功耗芯片, 核电压为1. 8V, IO 电压为3. 3V。

本文采用T I 公司的TPS767D318 电源芯片。

该芯片属于线性降压型DC/ DC 变换芯片, 可以由5V 电源同时产生两种不同的电压( 3. 3V、1. 8V 或2. 5V ) , 其最大输出电流为1000mA, 可以同时满足一片DSP 芯片和少量外围电路的供电需要, 如图2 所示。

该芯片自带电源监控及复位管理功能, 可以方便地实现电源及复位电路设计。

第2章 F2812最小系统

38 6 41 17 0.1uF 40 39

+3.3V

/RESET

33Ω

4 3

2 OSC30MHz TMS TDI 0.1uF

1

JTAG

TMS TDI GND VCC EMU1 GND TCK GND GND /TRST EMU0

14 EMU1 EMU0

/TRST

TCK

TDO 7

TCKREF TDO 8

RS

8K×16

X1/XCLKIN X2

XF _ XPLLDIS

第2章TMS320F2812的硬件结构学习要点

第2章 TMS320F2812的硬件结构【本章要点】了解TMS320F2812内部的功能结构了解TMS320F2812中央处理器的结构了解TMS320F2812的总线结构了解主要的CPU寄存器了解TMS320F2812的存储器管理1.TI DSP处理器TMS320F2812是采用改进型哈佛结构的32位定点DSP处理器,CPU内核架构为C28x内核。

2.哈佛结构:程序存储和数据存储空间相互独立,并设置了专用的程序总线和地址总线分别访问程序空间和数据空间,这样CPU就可以同时访问程序和数据了,从而极大地提高了处理速度。

3.改进的哈佛结构:允许数据存放在程序存储器中,并可以被算术指令直接使用;高速缓存存储指令;改进存储器块结构,允许在一个周期内同时读取一条指令和两个操作数。

4.芯片内部主要的功能部件:中央处理单元(CPU)、存储器、片内外设。

5.芯片的核心:中央处理单元(CPU)、相应的指令集及片内总线。

6.TMS320F2812芯片内部主要的功能部件有中央处理单元(CPU)、存储器、片内外设(与通用输入输接口GPIO复用)、全局定时器、外围设备中断管理单元PIE、模数转换器ADC、JTAG接口、外部扩展存储接口及系统控制单元等。

中央处理单元通过存储器总线、外设总线与其它功能部件相连接。

7.CPU与外围模块连接的信号线有四类:(1)存储器接口信号线。

(2)时钟和控制信号线。

(3)复位和中断信号线。

(4)仿真信号线。

8.C28x系列CPU的内核架构及数据通道:(1)内核的运算单元。

(2)CPU寄存器。

(3)地址寄存器算术单元(ARAU)。

(4)操作数总线。

(5)结果总线。

(6)程序地址总线(PAB)。

(7)数据读地址总线(DRAB)。

(8)数据写地址总线(DWAB)。

(9)程序读数据总线(PRDB)。

(10)数据读数据总线(DRDB)。

(11)数据写数据总线(DWDB)。

9.CPU的寄存器图 TMS320F2812 CPU的核心寄存器图 TMS320F2812 CPU的状态寄存器图 TMS320F2812 CPU的PSEUDO寄存器10.TMS320F2812处理器的存储器包括片上存储器和外部存储器接口两部分,所有的存储空间采用统一编址、统一映射到程序空间和数据空间。

第2讲 第2章 F2812结构与最小系统 2013-3-4

____________

18

TMS320F2812 DSP控制器原理及应用

2812 XINTF signals(多存储区Zone)

____________

19

TMS320F2812 DSP控制器原理及应用

____________

20

TMS320F2812 DSP控制器原理及应用

扩展存储器的最小系统需要的控制总线CB

INT13

M0 SARAM

1K×16

NMI

M1 SARAM

1K×16

GPIO Pins

L0 SARAM

4K×16

C28x CPU L1 SARAM

4K×16

Flash EVA/EVB

128K×16(F2812) 64 K×16(F2810)

OTP

16 Channels

12位 ADC

2K×16

XRS

H0 SARAM 系统控制 (晶振、PLL、 外设时钟、低功耗模 式、看门狗)

思考题2-7 : 输出变高阻 在什么情况下发生?高阻 有何用?

____________

21

TMS320F2812 DSP控制器原理及应用

扩展存储器的最小系统需要的控制总线CB XWE引脚(写控制信号,输出/高阻) Write Enable. Active-low write strobe. The write strobe waveform is specified, per zone basis, by the Lead, Active, and Trail periods in the XTIMINGx registers.

F2812工作模式(微处理器/微计算机模式) 配置引脚

第2课 CCS F2812一个完整工程的构成(完整版)

2.

根据前面一个完整工程的组成情况的分析,我们首先来准备头文件。由于头文件多数情况下是不

需改动的,也就是说大家用的头文件都是一样的,因为是定义 2812 的内部资源,所以可以将 newproject

文件夹内的头文件全部复制到 hellodsp 文件夹。& `6 Q! [% H A' \% |

3.

将 newproject 文件夹内的.lib 文件和.cmd 文件同样复制到 hellodsp 文件夹。, n2 o+ |6 X, K+ t, V8 F7 Q# M

6 P/ k* e, E+ X1 y

CCS 的安装和普通应用软件的安装没有多大区别,在这里就不赘述了。建议大家默认安装路径就行了,如 果需要修改安装路径,请确保将 CCS 安装到不含中文字符的路径。/ T6 N6 h# A3 s. u

CCS 安装完成之后,桌面上会出现两个图标,一个是 CCS,另外一个是 CCS Setup。在使用 CCS 之前,需 要对 CCS 进行一些配置操作,以保证 CCS 支持我们所要开发的 DSP,在这里就是 2812 了。

DSP28_Ev.C——外设 EV 的初始化函数,与外设 EV 相关。

DSP28_GlobalVariableDefs.C——全局变量的定义,这个文件也很重要,定义了 2812 的寄存器,中断向量

表等内容。

DSP28_Gpio.C——GPIO 的初始化函数,只和 GPIO 相关。

DSP28_InitPeripherals.C——所有外设的初始化函数,函数的内容是调用了 2812 各个外设的初始化函数。

* @5 A1 I( c. _, o4 E9 M2 A: }% \

OK,将 gpio 文件夹放好了吗?放好之后,我们打开 CCS,添加工程。添加工程的方法有两种,一种是点 击菜单栏的 Project—>Open,另一种方法是左侧 Files 窗口内,点击“Projects”然后右键,点击“Open Project”。

F2812DSP的最小系统设计

题目: F2812DSP的最小系统设计

院 系: 航天学院 学 科: 控制科学与工程

姓 名:

尚 伟

学 号 : 10S004022 日 期: 2011/6/12

F2812DSP的最小系统设计

尚伟 学号:10S004022 E-mail:capsw@ 摘要:本文主要介绍了基于TI公司生产的TMS320F2812DSP最小系统设 计。该最小系统主要包括电源、时钟、复位、外扩SRAM以及JTAG接 口的设计,为实现基本的程序演示,还增加了外部中断,基本输入输 出、以及异步串行通信模块。 关键词:TMS320F2812;DSP;最小系统;串行通信

图6 RS-232硬件设计电路图

2.6 示。

GPIO(流水灯)设计 为测试通用输入输出,本文设计了典型的流水灯电路,如图7所

Image

图7 流水灯设计电路图

外部中断设计 为测试外部中断,本文设计了按键形式的外部中断源,使用F2812 XINT1中断引脚,如图6所示。 2.7

图8 外部中断

在程序测试部分本文实现这样的功能,将上位机与F2812通过串口 相连,上位机可以利用串口调试助手发送数据给F2812,当F2812接收到 的数据为‘a’时,开启流水灯;每按一次按键,F2812向上位机发送一个 数据‘b’,利用串口调试助手可以看到接收的数据,并且关闭流水灯。 3.1 系统设置总程序 /*------------------------------------------------------------** ** 文 件 名:MinSys.c ** ** 处 理 器:DSP281x ** ** 版本: DSP281x C/C++ Header Files V1.20 ** ** Boot 配置:boot to Zone2 ** ** 功能描述:F2812最小系统测试 ** ** 修订日期:2011-06-12 ** ** 备 注:外部中断、定时、GPIO、SCI ** **------------------------------------------------------------*/ #include "DSP281x_Device.h" // DSP281x头文件

f2812最小系统原理图

LED

4K7 R11 2K2 R8

ADCLO ADCINA0 ADCINA1 ADCINA2 ADCINA3 ADCINA4 ADCINA5 ADCINA6 ADCINA7

LED

AGND

LED

D3 D4

4K7 R12 2K2 R9 4K7 R13 2K2 R10

AGND AGND

D 23 37 56 75 100 112 128 143 154 31 64 81 114 145 69

C9 104 XA15 XA14 XA13 XA12 XA11 XA10 XA9 XA8 XA7 XA6 XA5 XA4 XA3 XA2 XA1 XA0 0 R23

PG

47uF R26 18K2

LED1 LED0 MDXA WDI

19 32 38 52 58 70 78 86 99 105 113 120 129 142 153

C5 VDD5 104 C7 104 TXDA RXDA C

5 XSCITXDA 11 10 XSCIRXDA 12 9 15

GND

T1CTRIP_PDPINTA T2CTRIP/EVASOC T3CTRIP_PDPINTB T4CTRIP/EVBSOC XINT1_XBIO XINT2_ADCSOC XNMI_XINT13 SPISIMOA SPISOMIA SPICLKA SPISTEA SCITXDA SCIRXDA CANTXA CANRXA MCLKXA MCLKRA MFSXA MFSRA MDXA MDRA XF_XPLLDIS X1/XCLKIN X2 XCLKOUT TESTSEL XRS TEST1 TEST2 TRST TCK TMS TDI TDO EMU0 EMU1 SCITXDB SCIRXDB

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

思考题2-9 :无外设占 用总线请求时,该引脚 设应何处理?

____________

26

TMS320F2812 DSP控制器原理及应用

扩展存储器的最小系统需要的控制总线CB XZCS0AND1(外存储器扩展接口 块0/块1 片选信号) XINTF Zone 0 and Zone 1 Chip Select. XZCS0AND1 is active (low) when an access to the XINTF Zone 0 or Zone 1 is performed.

23

____________

TMS320F2812 DSP控制器原理及应用

扩展存储器的最小系统需要的控制总线CB

XREADY引脚(外设准备好,输入) Ready Signal. Indicates peripheral is ready to complete the access when asserted to 1. XREADY can be configured to be a synchronous or an asynchronous input. See the timing diagrams for more details.

Control

TINT2

TINT1

INT14

PIE (96个中断)

外部扩展接口 (XINTF)

Address(19) Data(16)

INT[12 : 1]

XINT13 外设中断控制 (XINT1/2/13,XNMI) XNMI G P I O M U X SCIA/SCIB SPI McBSP eCAN FIFO FIFO FIFO

TMS320F2812 DSP控制器原理及应用

DSP控制器原理与应用

第2章 F2812总体结构、最小系统 程序开发流程

TMS320F2812 DSP控制器原理及应用

DSP F2812的总体结构框图 14级CPU中断输入

内存总线 CPU定时器0 CPU定时器1 CPU定时器2

TINT0

实时 JTAG

思考题2-7 : 输出变高阻 在什么情况下发生?高阻 有何用?

____________

21

TMS320F2812 DSP控制器原理及应用

扩展存储器的最小系统需要的控制总线CB XWE引脚(写控制信号,输出/高阻) Write Enable. Active-low write strobe. The write strobe is specified, per zone basis, by the Lead, Active, and Trail periods in the XTIMINGx registers.

F2812工作模式(微处理器/微计算机模式) 配置引脚

XMP/MC=”1“,配置成微处理器模式, 外存储器寻址空间Zone 7 片选信号XZCS7有 效, 将Zone 7作为程序仿真RAM,初始化启动! XMP/MC=”0“,配置成微计算机模式, XZCS7 无效,DSP从片内FLASH 上电复位初始化启动!

____________

5

TMS320F2812 DSP控制器原理及应用

176引脚 LQFP封装TMS320F2812芯片

____________

6

AB=19根地址线 寻址空间多少?

TMS320F2812 DSP控制器原理及应用

TMS320F2812 外地址总线引脚

地址 最高位 XA[18]

____________

____________

16

TMS320F2812 DSP控制器原理及应用

F2812的5个存储器区寻址空间

Zone 0: 8K×16 Zone 1: 8K×16 Zone 2: 512K×16 Zone 6: 512K×16 Zone 7: 16K×16 (mapped here if MP/MC = 1)

INT13

M0 SARAM

1K×16

NMI

M1 SARAM

1K×16

GPIO Pins

L0 SARAM

4K×16

C28x CPU L1 SARAM

4K×16

Flash EVA/EVB

128K×16(F2812) 64 K×16(F2810)

OTP

16 Channels

12位 ADC

2K×16

XRS

H0 SARAM 系统控制 (晶振、PLL、 外设时钟、低功耗模 式、看门狗)

外存储器接口(External Interface, XINTF)

The external interface is a non-multiplexed (非多路的)asynchronous(异步) bus, similar to the C240x external interface. The external interface on the 2812 is mapped into five fixed zones (5个存储区 块:Zone 0, Zone 1, Zone 2, Zone 6, Zone 7).

F2812外存储器接口(XINTF)读写信号

____________

13

TMS320F2812 DSP控制器原理及应用

F2812外存储器接口(XINTF)片选信号

____________

14

TMS320F2812 DSP控制器原理及应用

F2812的工作模式设置信号

____________

15

TMS320F2812 DSP控制器原理及应用

____________

24

TMS320F2812 DSP控制器原理及应用

扩展存储器的最小系统需要的控制总线CB

XHOLD(外设占用请求,输入) External Hold Request. XHOLD, when active (low), requests the XINTF to release the external bus and place all buses and strobes into a high-impedance state. The XINTF will release the bus when any current access is complete and there are no pending accesses on the XINTF.

____________

4

TMS320F2812 DSP控制器原理及应用

DSP F2812总体结构

(10)模数转换器(A/D):12位单极性A/D转换器, 集成两个8通道模拟多路开关和采样保持器。 思考题2-4:设A/D转换器模拟电源输入设定为3.3V, 则数据D与输入电压V之间的转换表达式是什么? (11)串口外设:包括2个异步串口(SCI-A,SCI-B) 和1个同步串口(SPI),一个CAN总线接口,一个多 通道缓冲串行接口(McBSP)。 思考题2-5:异步/同步串口在异/同上差别是什么? (12)通用输入/输出口(GPIO):56根I/O引脚,可 编程配置成特定外设专用引脚。 (13)仿真逻辑单元:JTAG(Jiont Test Action Group,联合测试行动组,一个国际标准化组织)接口, 要接专用DSP仿真器才能调试。

RS

8K×16

X1/XCLKIN X2

XF_ XPLLDIS

CLKIN Boot ROM 内存总线 外设总线

4K×16

____________

2

TMS320F2812 DSP控制器原理及应用

TMS320F2812(DSP)总体结构

(1)CPU:32位字长 (2)存储器映像:片内18K SARAM,32KFlash,2K OTP,外设寄存器帧(外设帧,相当于存储器映像外 设寄存器) (3)引导ROM:每片2812出厂时均在引导ROM固化有一 段启动引导程序和常用数学函数如sin的查找表。 (4)片外存储器接口(XINTF):可编程外存储器接 口的时序参数,实现与各种异步存储器芯片的无缝 连接。 思考题2-1:什么叫无缝接口与有缝接口? (5)时钟与系统控制单元:时钟模块产生CPU所需的 工作频率。系统控制单元包括看门狗和低功耗模式 控制。

____________

18

TMS320F2812 DSP控制器原理及应用

2812 XINTF signals(多存储区Zone)

____________

19

TMS320F2812 DSP控制器原理及应用

____________

20

TMS320F2812 DSP控制器原理及应用

扩展存储器的最小系统需要的控制总线CB

7

TMS320F2812 DSP控制器原理及应用

TMS320F2812 外数据总线引脚

数据最 高位 XD[15]

____________

8

TMS320F2812 DSP控制器原理及应用

F2812外存储器接口(XINTF)读写引脚

写信号 XWE

读信号 XRD

____________

9

TMS320F2812 DSP控制器原理及应用

5个存储器区总容量超过地址 总线可寻址的范围时,如何实 现一个地址总线寻址多个存 储器区?请上网查阅资料解答!

思考题2-6 : 外寻址空间1M用多少根地址线?32 位地址值表示1M地址范围的数值表达式是什么?

____________

17

TMS320F2812 DSP控制器原理及应用

Memory Map

思考题2-8 :无外设 占用总线请求时,该 引脚设应何处理?

____________

25

TMS320F2812 DSP控制器原理及应用