K8D1716UTC-PI08中文资料

数据手册_HR6P71_Datasheet_C V2.1

HR

6P

No.

X

X

X

X

版本号:A(默认,不写) 封装:R—SSOP10; D—DIP18; S2—SOP18; D2—DIP20; S2—SOP20; R2—SSOP20 ROM容量:8—4K X 15位(8K字节) ROM类型:F—FLASH ROM 71:MCU型号 6P:8位 MCU指令集类型

2/95

上海海尔集成电路有限公司

HR6P71 数据手册

产品订购信息

型号 HR6P71F8R HR6P71F8D HR6P71F8S2 HR6P71F8D2 HR6P71F8S HR6P71F8R2 FLASH:4K×15 位 SRAM:224×8 位 程序存储器 数据存储器 封装 SSOP10 DIP18 SOP18 DIP20 SOP20 SSOP20

关于芯片的 ESD 防护措施

海尔 MCU 芯片具有满足工业级 ESD 标准保护电路。 建议用户根据芯片存储/应用的环境采取适当静电防护 措施。应注意应用环境的湿度;建议避免使用容易产生静电的绝缘体;存放和运输应在抗静电容器、抗静 电屏蔽袋或导电材料容器中;包括工作台在内的所有测试和测量工具必须保证接地;操作者应该佩戴静电 消除手腕环手套,不能用手直接接触芯片等。

上海海尔集成电路有限公司

HR6P71 数据手册

8 位 MCU HR6P71

数 据 手 册

产品简介 数据手册 产品规格

上海海尔集成电路有限公司 2011 年 5 月 5 日

V2.1 版权所有©上海海尔集成电路有限公司

1/95

上海海尔集成电路有限公司

上海海尔集成电路有限公司

HR6P71 数据手册

修订历史

版本 V1.0 V2.0 修改日期 2008-04-15 2010-09-28 初版 模板及命名修订 加强描述:3.2.1,3.2.3,5.1.4,附录 1.2 V2.1 2011-04-22 错误修正:2.1,2.2,4.3,5.1.1.1,5.1.1.2,5.1.2.1, 5.1.2.2,5.1.4.4,5.1.5,6.5.1,附录 1.2 更改概要

TEA1716中文资料免费版

TEA1716T中文资料免费版1. General descriptionTEA1716T集成了功率因数校正器(PFC)控制器和半桥谐振变换器的控制器(HBC)multi-chip IC。

它提供了离散MOSFET的驱动功能在一个上升变换器和两个离散功率场效应管谐振半桥配置。

高效PFC操作是通过实现准谐振软开关技术(QR)操作功能在高功率水平与QR操作谷跳跃在低功率水平。

过电流保护(OCP)、过电压保护装置(OVP)和退磁传感在所有条件下确保安全运行。

HBC模块是一个高压零开关LLC谐振变换器的控制器。

它包含一个高压电平转变电路和保护电路包括OCP,开环保护,电容模式保护和通用门锁保护输入。

高压芯片制作用的是专用高压Bipolar-CMOS-DMOS功率逻辑处理能够有效的从电源电压直接启动。

低压绝缘硅片(SOI)芯片用于准确、高速的保护功能和控制。

TEA1716T控制PFC电路和谐振转换器是非常灵活的。

它可以用于广泛的应用在一个宽的电源电压范围。

PFC和HBC控制器结合在一个单一的电源控制IC 使TEA1716T理想在液晶和等离子电视。

使用TEA1716T提供高效、可靠的电力供应从90 W到500 W可以轻松地使用TEA1716T设计,用最少的外部组件。

TEA1716T的集成突发模态和电源管理功能使共振的应用程序满足能源使用产品指令(EuP)很多6(< 0.5 W在待机模式)。

2.1 General features集成PFC和HBC控制器通用电源运行从70V-276V (AC)高水平的集成导致较低的外部组件数量和成本效益的设计集成突发模式感应符合能源使用产品指令(EuP)6使能输入只允许使能PFC或者PFC和HBC控制器芯片上的高压启动源独立运行或从DC源供应2.2 PFC controller features及时控制边界模式操作谷底和零电压开关以致最小损耗频率限制来减少开关损耗精确的增压调节用软启动和软停止的突发模式开关2.3 HBC controller features集成高压电平位移器可调节最大和最小频率半桥开关频率最大可达500KHz合适的非重叠时间突发模式开关2.4 Protection features安全系统故障条件下重启模式通用门锁保护输入对输出过电压保护或外部温度保护保护定时器超时并重启过温保护对两个控制器软启动欠电压保护给电源(断电),增压,IC供应和输出电压对两个控制器进行过流保护和调节对增高电压精确的过压保护对HBC控制器容性模式保护3. ApplicationsLCD电视等离子电视笔记本适配器台式机6.2 Pin descriptionCOMPPFC 1 PFC控制器频率补偿,外部链接到过滤器SNSMAINS 2 电源电压输入感应;外部连接分压电阻电源电压SNSAUXPFC 3 PFC消磁时间感应输入;外部连接到PFC的辅助绕组SNSCURPFC 4 PFC控制器为瞬时电流和软启动检测输入;外部连接到电流检测电阻和软启动过滤器SNSOUT 5 检测输入监测HBC输出电压;外部连接到辅助绕组SUPIC 6 SUPIC低压输入和输出的内部高压启动源;外部连接到辅助绕组HBC 或外部直流供电GATEPFC 7 PFC MOSFET 门极驱动输出PGND 8 电源地,HBC和PFC参考地SUPREG 9 管理SUPREG IC供应;内部调节器输出,输入驱动;外部连接到SUPREG缓冲电容器GATELS 10 HBC 低边MOSFET 门驱动输出n.c. 11 不连接SUPHV 12 内部高压启动源供应源高压输入;外部连接来提高电压GATEHS 13 HBC 高边MOSFET门驱动输出SUPHS 14 高端的驱动提供输入;外部连接到自举电容(CSUPHS)HB 15 参考高端驱动和半桥斜坡输入检测;外部连接到半桥节点HB的HBC mosfet之间(参见图17)n.c. 16 不连接SNSCURHBC 17 瞬时HBC检测输入;外部连接到谐振电流检测电阻SGND 18 信号地和IC参考地CFMIN 19 HBC最低频率设置;外部连接的电容器SNSBURST 20 突然停止激活检测输入;外部连接分压电阻SNSFB电压SNSFB 21 输出电压调节反馈检测输入;外部连接到光耦合器和上拉电阻SSHBC/EN 22 HBC软启动t时间和IC使能输入;使能PFC或PFC只或PFC和HBC控制器;外部连接到s软启动电容器,使下拉的信号RCPROT 23 保护定时器设置超时并重启;外部连接的电阻器和电容器SNSBOOST 24 检测输入增加电压调整;外部连接分压电阻提高电压7. Functional descriptionTEA1716T可以组合的功能如下:电源模块:IC供应管理。

ks0108中文资料

电子发烧友 电子技术论坛点阵图形液晶显示模块HD61202控制器使用手册目录注意事项----------------------------------------------------------------------------------------------------------------------------2第一章、关于HD61202 及其兼容控制驱动器的一般介绍----------------------------------4一、HD61202 及其兼容控制驱动器的特点-------------------------------------------------------------------------4二、HD61202 及其兼容控制驱动器的引脚功能-------------------------------------------------------------------4三、HD61202 及其兼容控制驱动器的时序-------------------------------------------------------------------------6四、HD61202 及其兼容控制驱动器显示RAM 的地址结构-----------------------------------------------------7五、HD61202 及其兼容控制驱动器的指令系统-------------------------------------------------------------------7第二章:内藏HD61202 及其兼容控制驱动器图形液晶显示模块的电路结构特点-------------------------------------------------------------------------------------9第三章:内藏HD61202 及其兼容控制驱动器图形液晶显示模块的应用用----------------------------------------------------------------11注意事项十分感谢您购买我公司的产品。

NORTE北电中文手册

LD 10PBX 电话机管理提示和响应-LD 10标号提示响应注释1 REQ 请求CHG 修改现有的数据块CPY n 从指定的分机数据块自动拷贝或生成1至32个新的分机数据块对Option 11各模式无效,版本12和其后的软件。

END 退出覆盖程序MOV 将数据块从一个TN移到另一个。

对Option 11各模式无效。

NEW X 增加新的数据块NEW后是一个1-255的数值,以生成此数目的接连的电话机数据块OUT X 取消数据块OUT后是一个1-255的数值,以取消此数目的接连的电话机数据块2 TYPE 数据块类型500500/2500电话机数据块500 M7Option 11的500/2500模式电话机数据块CARD 自动话机移位(ASR)的500/2500卡板块CARDSLT 单线电话机用户线卡板(版本19和其后的软件)OOSSLT20停止运行单线终端单元3 MODL71-127 模式号码,对Option 11模式话机提示。

4 CFTN 1 s c u 从TN拷贝,在REQ=CPY时提示。

c u7用于Option11,用这个TN作为新话机的样板。

5 SFMT 对拷贝命令选用以下一种格式,在CLS=AGTA时,提示POS。

D N输入项可长达4位,配备DNXP软件包150则长达7位TNDN 人工选择TN,DN和ACD电话机的ACD座席IDTN,DN和POS提示-n-次,如在CPY命令中所规定。

TN l s c u 新话机的TNDN xxxx 新话机的DNPOS xxxx ACD座席IDTN 新DN和ACD电话机的ACD座席ID是由系统提供的,对您提示要求开始的DN,ACD座席ID和每一个TN。

TN提示n次,如在CPY命令中所规定。

DN xxxx 新话机的DNPOS xxxx ACD座席IDTN l s c u 新话机的TNDN 新TN都是由系统提供的,对您提示要求开始的TN和每一个DN以及ACD电话机的ACD座席ID。

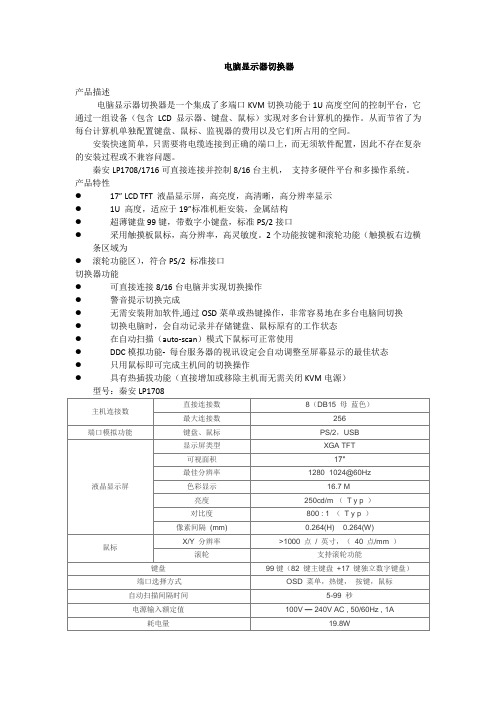

电脑显示器切换器

电脑显示器切换器

产品描述

电脑显示器切换器是一个集成了多端口KVM切换功能于1U高度空间的控制平台,它通过一组设备(包含LCD显示器、键盘、鼠标)实现对多台计算机的操作。

从而节省了为每台计算机单独配置键盘、鼠标、监视器的费用以及它们所占用的空间。

安装快速简单,只需要将电缆连接到正确的端口上,而无须软件配置,因此不存在复杂的安装过程或不兼容问题。

秦安LP1708/1716可直接连接并控制8/16台主机,支持多硬件平台和多操作系统。

产品特性

● 17” LCD TFT 液晶显示屏,高亮度,高清晰,高分辨率显示

● 1U 高度,适应于19”标准机柜安装,金属结构

● 超薄键盘99键,带数字小键盘,标准PS/2接口

● 采用触摸板鼠标,高分辨率,高灵敏度。

2个功能按键和滚轮功能(触摸板右边横

条区域为

●滚轮功能区),符合PS/2 标准接口

切换器功能

● 可直接连接8/16台电脑并实现切换操作

● 警音提示切换完成

● 无需安装附加软件,通过OSD菜单或热键操作,非常容易地在多台电脑间切换

● 切换电脑时,会自动记录并存储键盘、鼠标原有的工作状态

● 在自动扫描(auto-scan)模式下鼠标可正常使用

● DDC模拟功能- 每台服务器的视讯设定会自动调整至屏幕显示的最佳状态

● 只用鼠标即可完成主机间的切换操作

● 具有热插拔功能(直接增加或移除主机而无需关闭KVM电源)

型号:秦安LP1708。

EZ-LINK K16 IP 16口数字KVM控制器中文资料

台湾EZ-LINK K8/16 IP 8/16口数字KVM控制器产品资料

产品特点:

• 1数字用户、1本地用户控制8/16台服务器

•从任意地点远程访问KVM,控制电脑和服务器

•以色列MINICOM公司IP模块

• 支持BIOS基本输出输入

• 高品质画面以及鼠标实时同步功能

• 安全性, 128位SSL数据加密系统

• 远程串口控制电源切换器,路由器,以及其他设备

•支持多平台:PS/2或USB

• 1U机架式设计,方便安装

产品功能:

本地或远程访问服务器

IP K8/16可以帮助系统管理者在安全状态下,对8/16台服务器进行本地或远程的BIOS等级访问。

创新的,机架式,1U高。

BL专用KVM线缆避免机柜中出现线材杂乱现象,可以IP K16直接控制机柜中每台服务器,服务器与KVM切换器之间最远距离可以达到10m。

从独立的机柜到全球分散式数据中心

对于大型应用机房,比如全球分散式数据中心或机房,IP K8/16 可以在Minicom' 集中系统下管理所有设备-不但可以满足当今市场对多功能,高品质KVM切换器的要求,而且是未来集中式机房管理的发展趋势。

工业安全标准

支持工业最高安全加密,128-bit SSL协议,保证你公司的数据远离各类网络安全漏洞和黑客袭击。

BIOS等级,多平台访问

作为一个优秀的解决方案,IP K8/16可以让您通过BIOS直接访问,并控制多平台服务器,包括PS/2 和USB设备。

系统拓扑图

规格表。

电视机解锁大全

电视机解锁大全现介绍几种品牌彩电的解锁万能码。

1.海信东芝TB1238机心万能密码是2175或1238;2.乐华100Hz机心万能密码是987;3.乐华三菱+飞利浦机心万能密码是2442;4.夏华E系列三洋单片机万能密码是4321;5.康佳T5435彩电的解锁方法是:同时按面板上的“频道+”和“频道-”键;6.长虹A6机心的解锁方法是同时按遥控器上的“静音”键和“显示”键;7.长虹CN-12机心的解锁方法是同时按遥控器上的“F”键和“静音”键,或“F”键和“返回”键。

海尔电视解童锁海尔童锁功能有如下几种解锁方式:1.用菜单键解锁:按“MENU”键(或“FUNC”键),选择功能显示菜单(系统设定菜单),在子菜单里有童锁一项,按P+/-来移动光标移动到“童锁”字样处,按V+/-键将童锁设置为“关”,即将童锁功能关闭;2.按屏显键解锁:此类机器童锁后屏幕上无锁定标志,但是按屏显键节目号是红色:此类机器的解锁方法很简单:按遥控器上的“DISPLAY”键(频道号显示键),持续3秒钟(或5秒钟)以上,屏幕显示的节目号由红色变成绿色即可解锁。

3.密码解锁:按“LOCK”键或童锁键然后输入4位您设定的密码按P+/-来移动光标移动到“童锁”字样处,按V+/-键将童锁设置为“关”,即将童锁功能关闭。

工厂的初始密码为0000。

4.组合锁解锁同时按下遥控器的静音键和屏显键,屏幕显示的锁头(电视童锁功能)就可以解开,当电视的童锁功能打开后,电视的本机键与遥控器单键都被锁定,关机后再次开机仍保持童锁状态。

5.1269万能码解锁如:CPU:LC863320A,小信号是LA76810的机型,用户输入密码锁后又把密码忘了,或用户先输入定时关机后再按密码锁,这时就可输入1269万能码即可解决.不同的电视机型号、不同的电路设计有不同的解锁方式长虹21K32解除童锁方法同时按遥控器上的“F”和“静音”键长虹G2136k解除童锁方法先按住F键不放,再按静音键就OK了长虹B2116童锁1 同时按下屏幕键和消音键,电视显示童锁符号,电视进入童锁状态。

KVM-1716AC使用说明书

2

目录

目录................................................................................................................................................................................................3 章节一 基本介绍.......................................................................................................................................................................... 3 1.1 包装内容........................................................................................................................................................................ 3 1.2 后面板............................................................................................................................................................................ 5 1.3 可用套件.................................................

Tel act8 中文說明書

Telact8中文說明書

TELCLEANTRACKACT8

型号:A810WCWD-IF

对于200毫米晶圆

单块配置

晶圆流程:从左到右

运载站(CRA)1x4型,带拾取级,包括6个密理博智能泵

具有高速传送机构的处理块

a)通过MilliporeIntelligen泵(数量2)进行3次分配的光刻胶涂布机单元

b)显影单元,通过H型喷嘴分配1份溶液(数量2)

c)为1台开发设备(数量1)分配额外的显影剂

d)LHP,低温热板(数量10)

e)CPL,冷却板(数量4)

f)ADH,附着力促进剂单元(数量1)

g)TCP,传输冷却板(数量1)

h)用于涂布机的可编程转鼓清洗系统(数量1)

I)可编程PTI排气控制器(数量4)

用于佳能FPA-3000i5步进机的接口单元(IRA),包括一个多缓冲单元和晶片边缘曝光(WEE)

化学柜1

a)HMDS的加压罐

b)稀释剂缓冲罐,3升(数量2)

c)显影剂缓冲罐,3升(数量2)

化学柜2

a)显影剂脱气模块(数量2)

b)稀释剂脱气模块

温度控制架

a)冷却板的热电偶模块(数量4)

b)水循环装置(数量4)

涂布机温度和湿度控制装置

软件包

a)TELGEM在线软件

b)级联晶片流软件

c)系统登录软件

二氧化碳灭火系统准备就绪(管道和线路) 紫外线/红外线火灾探测器(数量3)

额外的5加仑不锈钢罐(数量5)。

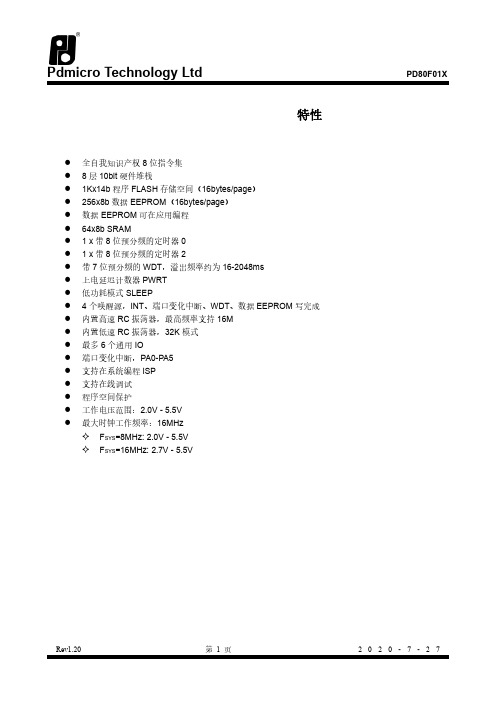

PD80F01x系列_中文资料_数据手册

Rev1.20

第1页

2020-7-27

Pdmicro Technology Ltd

PD80F01X

目录

特性..................................................................................................................................................................................1

2.1. 地址映射................................................................................................................................................................. 9 2.1.1. SFR,BANK0................................................................................................................................................. 9 2.1.2. SFR,BANK1............................................................................................................................................... 10 2.1.3. TMR0,地址 0x01........

W78E58中文

W78E58B规格书8位微控制器目录:1.概述 (3)2.特性 (3)3.管脚配置 (4)4.管脚描述 (5)5.方块图 (7)6.功能描述 (8)6.1 RAM (8)6.2 定时器0,1,2 (8)6.3 时钟 (9)6.4 晶体振荡器 (9)6.5 外部时钟 (9)6.6 电源管理 (9)6.7 减少EMI辐射 (9)6.8 复位 (9)6.9 I/O口4 (11)6.10 INT2/INT3 (12)6.11 P4口基地址寄存器 (14)6.12 在线编程(ISP)模式 (15)6.13 在线编程控制寄存器(CHPCON) (17)6.14 F04KBOOT 模式(从LDROM启动) (18)7.保密位 (22)7.1 锁止位 (22)禁止 (22)7.2 MOVC7.3 加密 (22)8.电气特性 (23)8.1 绝对最大额定值 (23)8.2 DC特性 (23)出版日期: December 22, 20048.3 AC特性 (25)8.3.1时钟输入波形 (25)8.3.2程序读取周期 (26)8.3.3数据读取周期 (26)8.3.4数据写周期 (27)8.3.5端口访问周期 (27)9.时序波形图 (28)9.1 程序读取周期 (28)9.2 数据读周期 (28)9.3 数据写周期 (29)9.4 端口访问周期 (29)10.典型应用电路 (30)10.1 扩展的外部程序存储器和石英晶体 (30)10.2 扩展的外部程序存储器和振荡器 (31)11.封装尺寸 (32)11.1 DIP40 (32)11.2 44 管脚PLCC (33)11.3 44 管脚PQFP (34)12.应用指南 (35)12.1 ISP 软件编程示例: (35)13.文件版本描述 (42)1. 概述W78E58B是具有带ISP功能的Flash EPROM的低功耗8位微控制器;ISP功能的Flash EPROM可用于固件升级。

PCI-1716 1716L 快速说明书

PCI-1716/1716L快速安装使用手册PCI-1716/1716L快速安装使用手册 (1)第一章 产品介绍 (2)1.1 概述 (2)1.1.1 即插即用功能 (2)1.1.2 自动通道/增益/SD*/BU*扫描 (2)1.1.3 卡上FIFO(先入先出)存储器 (2)1.1.4 卡上可编程计数器 (2)1.1.5 16路数字输入和16路数字输出 (3)1.1.6 自动校准功能 (3)1.1.7 板卡ID (3)1.2 特点: (3)第二章 安装与测试 (3)2.1 初始检查 (3)2.2 Windows2K/XP/9X下板卡的安装 (4)2.2.1 软件的安装: (4)2.2.2 硬件的安装: (6)2.3 测试 (11)2.3.1 模拟输入功能测试 (11)2.3.2 模拟输出功能测试 (12)2.3.3 数字量输入功能测试 (13)2.3.4 数字量输出功能测试 (14)2.4.5 计数器功能测试 (15)第三章 信号连接 (16)3.1 模拟信号输入连接: (18)3.1.1 单端模拟输入连接 (18)3.1.2 差分式模拟输入连接 (18)3.2模拟信号输出连接 (20)3.3触发源连接 (20)3.3.1 内部触发源连接 (20)3.3.2 外部触发源连接 (21)第四章 例程使用详解 (21)4.1板卡支持例程列表4.2 常用例子使用说明 (21)4.2.1 ADSOFT/ADTRIG(软件触发方式例程) (21)4.2.2 ADint(中断方式进行数据采集的例程) (22)4.2.3 DIGOUT(数字量输出): (24)4.2.4 COUNTER(计数程序) (26)4.2.5 Digin (数字量输入例程) (27)第五章 遇到问题,如何解决? (23)第一章产品介绍1.1 概述PCI-1716/1716L是一款功能强大的高分辨率多功能PCI数据采集卡。

它带有一个250KS/s16位A/D转换器,1K用于A/D的采样FIFO缓冲器。

常用开关电源芯片大全

常用开关电源芯片大全第1 章DC-DC 电源转换器/ 基准电压源1.1 DC-DC 电源转换器1. 低噪声电荷泵DC-DC 电源转换器AAT3113/AAT31142. 低功耗开关型DC-DC 电源转换器ADP30003. 高效3A 开关稳压器AP15014. 高效率无电感DC-DC 电源转换器FAN56605. 小功率极性反转电源转换器ICL76606. 高效率DC-DC 电源转换控制器IRU30377. 高性能降压式DC-DC 电源转换器ISL64208. 单片降压式开关稳压器L49609. 大功率开关稳压器L4970A10.1.5A 降压式开关稳压器L497111.2A 高效率单片开关稳压器L497812.1A 高效率升压/降压式DC-DC 电源转换器L597013.1.5A 降压式DC-DC 电源转换器LM157214. 高效率1A 降压单片开关稳压器LM1575/LM2575/LM2575HV15.3A 降压单片开关稳压器LM2576/LM2576HV16. 可调升压开关稳压器LM257717.3A 降压开关稳压器LM259618. 高效率5A 开关稳压器LM267819. 升压式DC-DC 电源转换器LM2703/LM270420. 电流模式升压式电源转换器LM273321. 低噪声升压式电源转换器LM275022. 小型75V 降压式稳压器LM500723. 低功耗升/降压式DC-DC 电源转换器LT107324. 升压式DC-DC 电源转换器LT161525. 隔离式开关稳压器LT172526. 低功耗升压电荷泵LT175127. 大电流高频降压式DC-DC 电源转换器LT176528. 大电流升压转换器LT193529. 高效升压式电荷泵LT193730. 高压输入降压式电源转换器LT195631.1.5A 升压式电源转换器LT196132. 高压升/降压式电源转换器LT343333. 单片3A 升压式DC-DC 电源转换器LT343634. 通用升压式DC-DC 电源转换器LT346035. 高效率低功耗升压式电源转换器LT346436.1.1A 升压式DC-DC 电源转换器LT346737. 大电流高效率升压式DC-DC 电源转换器LT378238. 微型低功耗电源转换器LTC175439.1.5A 单片同步降压式稳压器LTC187540. 低噪声高效率降压式电荷泵LTC191141. 低噪声电荷泵LTC3200/LTC3200-542. 无电感的降压式DC-DC 电源转换器LTC325143. 双输出/低噪声/降压式电荷泵LTC325244. 同步整流/升压式DC-DC 电源转换器LTC340145. 低功耗同步整流升压式DC-DC 电源转换器LTC340246. 同步整流降压式DC-DC 电源转换器LTC340547. 双路同步降压式DC-DC 电源转换器LTC340748. 高效率同步降压式DC-DC 电源转换器LTC341649. 微型2A 升压式DC-DC 电源转换器LTC342650.2A 两相电流升压式DC-DC 电源转换器LTC342851. 单电感升/降压式DC-DC 电源转换器LTC344052. 大电流升/降压式DC-DC 电源转换器LTC344253.1.4A 同步升压式DC-DC 电源转换器LTC345854. 直流同步降压式DC-DC 电源转换器LTC370355. 双输出降压式同步DC-DC 电源转换控制器LTC373656. 降压式同步DC-DC 电源转换控制器LTC377057. 双2相DC-DC 电源同步控制器LTC380258. 高性能升压式DC-DC 电源转换器MAX1513/MAX151459. 精简型升压式DC-DC 电源转换器MAX1522/MAX1523/MAX152460. 高效率40V 升压式DC-DC 电源转换器MAX1553/MAX155461. 高效率升压式LED 电压调节器MAX1561/MAX159962. 高效率5路输出DC-DC 电源转换器MAX156563. 双输出升压式DC-DC 电源转换器MAX1582/MAX1582Y64. 驱动白光LED 的升压式DC-DC 电源转换器MAX158365. 高效率升压式DC-DC 电源转换器MAX1642/MAX164366.2A 降压式开关稳压器67. 高效率升压式DC-DC MAX1644电源转换器MAX1674/MAX1675/MAX167668. 高效率双输出DC-DC 电源转换器MAX167769. 低噪声1A 降压式DC-DC 电源转换器MAX1684/MAX168570. 高效率升压式DC-DC 电源转换器MAX169871. 高效率双输出降压式DC-DC 电源转换器MAX171572. 小体积升压式DC-DC 电源转换器MAX1722/MAX1723/MAX172473. 输出电流为50mA 的降压式电荷泵MAX173074. 升/降压式电荷泵MAX175975. 高效率多路输出DC-DC 电源转换器MAX180076.3A 同步整流降压式稳压型MAX1830/MAX183177. 双输出开关式LCD 电源控制器MAX187878. 电流模式升压式DC-DC 电源转换器MAX189679. 具有复位功能的升压式DC-DC 电源转换器MAX194780. 高效率PWM 降压式稳压器MAX1992/MAX199381. 大电流输出升压式DC-DC 电源转换器MAX61882. 低功耗升压或降压式DC-DC 电源转换器MAX62983.PWM 升压式DC-DC 电源转换器MAX668/MAX66984. 大电流PWM 降压式开关稳压器MAX724/MAX72685. 高效率升压式DC-DC 电源转换器MAX756/MAX75786. 高效率大电流DC-DC 电源转换器MAX761/MAX76287. 隔离式DC-DC 电源转换器MAX8515/MAX8515A88. 高性能24V 升压式DC-DC 电源转换器MAX872789. 升/降压式DC-DC 电源转换器MC33063A/MC34063A90.5A 升压/降压/反向DC-DC 电源转换器MC33167/MC3416791. 低噪声无电感电荷泵MCP1252/MCP125392. 高频脉宽调制降压稳压器MIC220393. 大功率DC-DC 升压电源转换器MIC229594. 单片微型高压开关稳压器NCP1030/NCP103195. 低功耗升压式DC-DC 电源转换器NCP1400A96. 高压DC-DC 电源转换器NCP140397. 单片微功率高频升压式DC-DC 电源转换器NCP141098. 同步整流PFM 步进式DC-DC 电源转换器NCP142199. 高效率大电流开关电压调整器NCP1442/NCP1443/NCP1444/NCP1445 100. 新型双模式开关稳压器NCP1501101. 高效率大电流输出DC-DC 电源转换器NCP1550102. 同步降压式DC-DC 电源转换器NCP1570103. 高效率升压式DC-DC 电源转换器NCP5008/NCP5009104. 大电流高速稳压器RT9173/RT9173A105. 高效率升压式DC-DC 电源转换器RT9262/RT9262A106. 升压式DC-DC 电源转换器SP6644/SP6645107. 低功耗升压式DC-DC 电源转换器SP6691108. 新型高效率DC-DC 电源转换器TPS54350109. 无电感降压式电荷泵TPS6050x110. 高效率升压式电源转换器TPS6101x111.28V 恒流白色LED 驱动器TPS61042112. 具有LDO 输出的升压式DC-DC 电源转换器TPS6112x113. 低噪声同步降压式DC-DC 电源转换器TPS6200x114. 三路高效率大功率DC-DC 电源转换器TPS75003115. 高效率DC-DC 电源转换器UCC39421/UCC39422116. P WM 控制升压式DC-DC 电源转换器XC6371117. 白光LED 驱动专用DC-DC 电源转换器XC9116118.500mA 同步整流降压式DC-DC 电源转换器XC9215/XC9216/XC9217 119. 稳压输出电荷泵XC9801/XC9802120. 高效率升压式电源转换器ZXLB16001.2线性/ 低压差稳压器121. 具有可关断功能的多端稳压器BAXXX122. 高压线性稳压器HIP5600123. 多路输出稳压器KA7630/KA7631124. 三端低压差稳压器LM2937125. 可调输出低压差稳压器LM2991126. 三端可调稳压器LM117/LM317127. 低压降CMOS500mA 线性稳压器LP38691/LP38693 128. 输入电压从12V 到450V 的可调线性稳压器LR8 129.300mA 非常低压降稳压器(VLDO )LTC3025 130. 大电流低压差线性稳压器LX8610131.200mA 负输出低压差线性稳压器MAX1735132.150mA 低压差线性稳压器MAX8875133. 带开关控制的低压差稳压器MC33375134. 带有线性调节器的稳压器MC33998135.1.0A 低压差固定及可调正稳压器NCP1117136. 低静态电流低压差稳压器NCP562/NCP563137. 具有使能控制功能的多端稳压器PQxx138. 五端可调稳压器SI-3025B/SI-3157B139.400mA 低压差线性稳压器SPX2975140. 五端线性稳压器STR20xx141. 五端线性稳压器STR90xx142. 具有复位信号输出的双路输出稳压器TDA8133143. 具有复位信号输出的双路输出稳压器TDA8138/TDA8138A 144. 带线性稳压器的升压式电源转换器TPS6110x145. 低功耗50mA 低压降线性稳压器TPS760xx146. 高输入电压低压差线性稳压器XC6202147. 高速低压差线性稳压器XC6204148. 高速低压差线性稳压器XC6209F149. 双路高速低压差线性稳压器XC64011.3基准电压源150. 新型XFET 基准电压源ADR290/ADR291/ADR292/ADR293 151. 低功耗低压差大输出电流基准电压源MAX610x152. 低功耗1.2V 基准电压源MAX6120153.2.5V 精密基准电压源MC1403154.2.5V/4.096V 基准电压源MCP1525/MCP1541155. 低功耗精密低压降基准电压源REF30xx/REF31xx156. 精密基准电压源TL431/KA431/TLV431A第2章AC-DC 转换器及控制器1. 厚膜开关电源控制器DP104C2. 厚膜开关电源控制器DP308P3. D PA-Switch 系列高电压功率转换控制器DPA423/DPA424/DPA425/DPA4264. 电流型开关电源控制器FA13842/FA13843/FA13844/FA138455. 开关电源控制器FA5310/FA53116. P WM 开关电源控制器FAN75567. 绿色环保的PWM 开关电源控制器FAN76018. F PS 型开关电源控制器FS6M07652R9. 开关电源功率转换器FS6Sxx10. 降压型单片AC-DC 转换器HV-2405E11. 新型反激准谐振变换控制器ICE1QS0112. P WM 电源功率转换器KA1M088013. 开关电源功率转换器KA2S0680/KA2S088014. 电流型开关电源控制器KA38xx15.FPS 型开关电源功率转换器KA5H0165R16.FPS 型开关电源功率转换器KA5Qxx17.FPS 型开关电源功率转换器KA5Sxx18. 电流型高速PWM 控制器L499019. 具有待机功能的PWM 初级控制器L599120. 低功耗离线式开关电源控制器L659021. L INK SWITCH TN 系列电源功率转换器LNK304/LNK305/LNK30622. L INK SWITCH 系列电源功率转换器LNK500/LNK501/LNK52023. 离线式开关电源控制器M51995A24. P WM 电源控制器M62281P/M62281FP25. 高频率电流模式PWM 控制器MAX5021/MAX502226. 新型PWM 开关电源控制器MC4460427. 电流模式开关电源控制器MC4460528. 低功耗开关电源控制器MC4460829. 具有PFC 功能的PWM 电源控制器ML482430. 液晶显示器背光灯电源控制器ML487631. 离线式电流模式控制器NCP120032. 电流模式脉宽调制控制器NCP120533. 准谐振式PWM 控制器NCP120734. 低成本离线式开关电源控制电路NCP121535. 低待机能耗开关电源PWM 控制器NCP123036. S TR 系列自动电压切换控制开关STR8xxxx37. 大功率厚膜开关电源功率转换器STR-F665438. 大功率厚膜开关电源功率转换器STR-G865639. 开关电源功率转换器STR-M6511/STR-M652940. 离线式开关电源功率转换器STR-S5703/STR-S5707/STR-S570841. 离线式开关电源功率转换器STR-S6401/STR-S6401F/STR-S6411/STR-S6411F 442. 开关电源功率转换器STR-S651343. 离线式开关电源功率转换器TC33369 ~TC3337444. 高性能PFC 与PWM 组合控制集成电路TDA16846/TDA1684745. 新型开关电源控制器TDA1685046. “绿色”电源控制器TEA150447. 第二代“绿色”电源控制器TEA150748. 新型低功耗“绿色”电源控制器TEA153349. 开关电源控制器TL494/KA7500/MB375950.Tiny Switch Ⅰ系列功率转换器TNY253 、TNY254 、TNY25551.Tiny Switch Ⅱ系列功率转换器TNY264P ~TNY268G52.TOP Switch (Ⅱ)系列离线式功率转换器TOP209 ~TOP22753.TOP Switch-FX 系列功率转换器TOP232/TOP233/TOP23454.TOP Switch-GX 系列功率转换器TOP242 ~T OP25055.开关电源控制器UCX84X56.离线式开关电源功率转换器VIPer12AS/VIPer12ADIP57.新一代高度集成离线式开关电源功率转换器VIPer53 第3章功率因数校正控制/节能灯电源控制器1. 电子镇流器专用驱动电路BL83012. 零电压开关功率因数控制器FAN48223. 功率因数校正控制器FAN75274. 高电压型EL 背光驱动器HV8265. E L 场致发光背光驱动器IMP525/IMP5606. 高电压型EL 背光驱动器/反相器IMP8037. 电子镇流器自振荡半桥驱动器IR21568. 单片荧光灯镇流器IR21579. 调光电子镇流器自振荡半桥驱动器IR215910. 卤素灯电子变压器智能控制电路IR216111. 具有功率因数校正电路的镇流器电路IR216612. 单片荧光灯镇流器IR216713. 自适应电子镇流器控制器IR252014. 电子镇流器专用控制器KA754115. 功率因数校正控制器L656116. 过渡模式功率因数校正控制器L656217. 集成背景光控制器MAX8709/MAX8709A18. 功率因数校正控制器MC33262/MC3426219. 固定频率电流模式功率因数校正控制器NCP165320. E L 场致发光灯高压驱动器SP440321. 功率因数校正控制器TDA4862/TDA486322. 有源功率因数校正控制器UC385423. 高频自振荡节能灯驱动器电路VK05CFL24. 大功率高频自振荡节能灯驱动器电路VK06TL第4章充电控制器1. 多功能锂电池线性充电控制器AAT36802. 可编程快速电池充电控制器BQ20003. 可进行充电速率补偿的锂电池充电管理器BQ20574. 锂电池充电管理电路BQ2400x5. 单片锂电池线性充电控制器BQ2401x6. U SB 接口单节锂电池充电控制器BQ2402x7.2A 同步开关模式锂电池充电控制器BQ241008. 集成PWM 开关控制器的快速充电管理器BQ29549. 具有电池电量计量功能的充电控制器DS277010. 锂电池充电控制器FAN7563/FAN756411.2A 线性锂/锂聚合物电池充电控制器ISL629212. 锂电池充电控制器LA5621M/LA5621V13.1.5A 通用充电控制器LT157114.2A 恒流/恒压电池充电控制器LT176915. 线性锂电池充电控制器LTC173216. 带热调节功能的1A 线性锂电池充电控制器LTC173317. 线性锂电池充电控制器LTC173418. 新型开关电源充电控制器LTC198019. 开关模式锂电池充电控制器LTC400220.4A 锂电池充电器LTC400621. 多用途恒压/恒流充电控制器LTC400822.4.2V 锂离子/锂聚合物电池充电控制器LTC405223. 可由USB 端口供电的锂电池充电控制器LTC405324. 小型150mA 锂电池充电控制器LTC405425. 线性锂电池充电控制器LTC405826. 单节锂电池线性充电控制器LTC405927. 独立线性锂电池充电控制器LTC406128. 镍镉/ 镍氢电池充电控制器M62256FP29. 大电流锂/镍镉/镍氢电池充电控制器MAX150130. 锂电池线性充电控制器MAX150731. 双输入单节锂电池充电控制器MAX1551/MAX155532. 单节锂电池充电控制器MAX167933. 小体积锂电池充电控制器MAX173634. U SB 接口单节锂电池充电控制器MAX181135. 多节锂电池充电控制器MAX187336. 双路输入锂电池充电控制器MAX187437. 单节锂电池线性充电控制器MAX189838. 低成本/多种电池充电控制器MAX190839. 开关模式单节锂电池充电控制器MAX1925/MAX192640. 快速镍镉/镍氢充电控制器MAX2003A/MAX200341. 可编程快速充电控制器MAX712/MAX71342. 开关式锂电池充电控制器MAX74543. 多功能低成本充电控制器MAX846A44. 具有温度调节功能的单节锂电池充电控制器MAX8600/MAX860145. 锂电池充电控制器MCP73826/MCP73827/MCP7382846. 高精度恒压/ 恒流充电器控制器MCP73841/MCP73842/MCP73843/MCP73844 647. 锂电池充电控制器MCP73861/MCP7386248. 单节锂电池充电控制器MIC7905049. 单节锂电池充电控制器NCP180050. 高精度线性锂电池充电控制器VM7205Welcome To Download !!!欢迎您的下载,资料仅供参考!。

北京大华无线电仪器厂 DH-1716型直流稳压稳流电源 说明书

DH1716型直流稳压稳流电源技术说明书(DH系列电源产品通过2000版ISO9000认证)北京大华无线电仪器厂2010-01-081、概况2、技术特性3、工作原理4、使用操作说明5、维护修理6、成套型7、质量保证检测指标无论电源从前面板还是后面板端口输出,检测恒压指标时,请将检测线联接后面板+S,-S接线端子(见SJ2811,2-87标准)。

注意:本产品采用智能风机,温度低于设定值时风机不转。

1、概述DH1716型是具有恒压(CV)、恒流(CC)自动切换工作模式的中功率单路稳压稳流直流电源。

为提高电源的可靠性,应用了相位控制电路,输出端设计有过压保护电路,机内有过温保护继电器、智能风机。

本电源具有主从串联、并联、电压遥控、电压信号回读、电流信号回读、外控通断等功能。

是一种理想的直流稳压电源。

本产品可广泛用于实验室及工业控制等多种场合。

外形图(图一)2、技术特性2.1 产品规格:DH1716-2D DH1716-3D DH1716-4D DH1716-5D 输出电压调节范围0~20.5V 0~20.5V 0~36V 0~62V输出电压控制范围0~20V 0~20V 0~35V 0~60V 输出电流调节范围0~50.5A 0~30.5A 0~20.5A 0~12.2A 输出电流控制范围0~50A 0~30A 0~20A 0~12ADH1716-6DDH1716-7A输出电压调节范围0~103V 0~36V输出电压控制范围0~100V 0~35V输出电流调节范围0~7.2A 0~30.5A输出电流控制范围0~7A 0~30A2.2 性能指标:(按额定值计算)2.2.1 恒压工作时:源效应:0.005%+1mV 负载效应:0.005%+2mV周期与随机偏移电压(PARD):1mV(rms);DH1716—6型:2mV(rms)。

2.2.2 恒流工作时:源效应:0.005%+10mA 负载效应:0.005%+10mA周期与随机偏移电流(PARD):20mA(rms)2.2.3允许两台同类产品串联使用2.2.4允许两台同类产品并联使用2.2.5保证负载端电压准确度的使用方式。

捷波 智尊系列主板 Odin K8F7 K8F7P K8F7G 静音版 说明书

捷波®智尊系列主板Odin K8F7/K8F7P/K8F7G静音版用户手册AMD Socket 754处理器主板NVIDIA nForce4版本 1.0发布日期:2005年11月版权通告本手册的版权属于制造厂商。

本手册的任何部分,包括产品,软件的描述未经制造厂的书面授权都不能以任何方式或任何手段复制,传播或翻译成任何语言文字。

本手册包含了正常使用该主板所需的一切信息并且我们确信本手册可以适合用户的需求,本公司有权对使用手册的内容进行修改,但是本手册与产品在任何时间的修正与更改不会另行通告,使用手册中的内容如有错误,恳请谅解。

制造厂商提供的使用手册不应当被视作为任何种类,形式的担保。

并且也不会为任何间接的,特殊的,偶然的或相应而生的损害(包括利益损失的伤害,丢失交易、用户数据,交易的中断或与之类似的)负责。

手册版本信息版本 手册版本历史 发布日期1.0版 第一次发布 2005年11月包装项目列表5主机板5IDE/Floppy数据线5串行ATA IDE端口数据线□USB端口3/4扩展线(可选)5主板说明书5主板驱动工具光盘5智尊主板特色技术软件光盘散热方案AMD K8 处理器系列由于科技的日新月异,中央处理器 (CPU) 亦持续往更快速、更高的效能发展。

因此在建置计算机系统时,散热的处理变得越来越重要了,一个适当的散热环境,是让系统更加稳定及长期操作时的关键。

提供适当散热环境的最终目的,则在于维持中央处理器之温度,能低于计算机机壳之最大特定温度。

一个好的风扇,除了要有较高的转速外,适当的散热片面积亦是相当重要的因素。

它可透过其表面之散热片区域的范围,集中来自中央处理器的高热,并透过附加的风扇让热气流传导出去。

除此之外,散热膏亦能有效的将高热由中央处理器传输到散热片。

为了达到散热传导的最佳效果,AMD建议您使用散热膏,并以固定夹将风扇附加在处理器上。

当您为系统选择适当的风扇时,请参考以下网址中AMD所推荐与AMD处理器一起使用之风扇。

ATEN CS1708i CS1716i 说明书

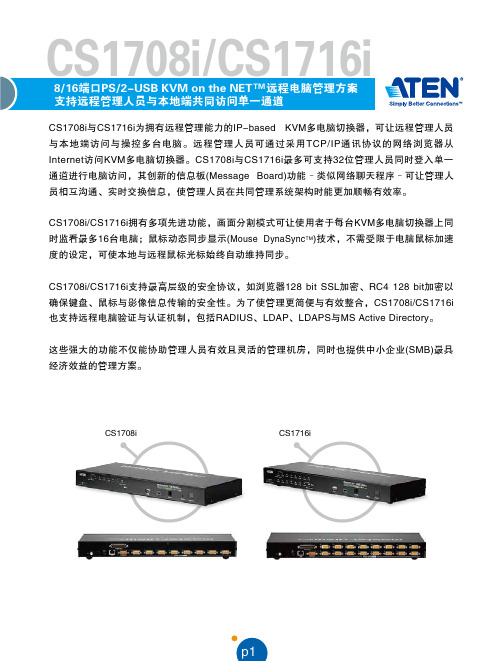

p1CS1708i 与CS1716i 为拥有远程管理能力的IP-based KVM多电脑切换器,可让远程管理人员与本地端访问与操控多台电脑。

远程管理人员可通过采用TCP/IP通讯协议的网络浏览器从Intern e t访问KVM多电脑切换器。

CS1708i 与CS1716i最多可支持32位管理人员同时登入单一通道进行电脑访问,其创新的信息板(M essage Boa r d )功能–类似网络聊天程序–可让管理人员相互沟通、实时交换信息,使管理人员在共同管理系统架构时能更加顺畅有效率。

CS1708i/CS1716i 拥有多项先进功能,画面分割模式可让使用者于每台KVM 多电脑切换器上同时监看最多16台电脑;鼠标动态同步显示(Mouse Dy na Sy n c T M )技术,不需受限于电脑鼠标加速度的设定,可使本地与远程鼠标光标始终自动维持同步。

CS1708i/CS1716i 支持最高层级的安全协议,如浏览器128 bi t SSL 加密、RC4 128 bi t加密以确保键盘、鼠标与影像信息传输的安全性。

为了使管理更简便与有效整合,CS1708i/CS1716i 也支持远程电脑验证与认证机制,包括RAD I U S、LD AP、LD APS与MS Act ive Di r e ct o ry。

这些强大的功能不仅能协助管理人员有效且灵活的管理机房,同时也提供中小企业(SM B )最具经济效益的管理方案。

p2管理可通过前端面板按键、热键与支持多国语言的OS D屏幕选单进行电脑选择与切换 允许32位使用者同时登入多国语言的web使用者接口,可支持本地端与远程OS D以树状架构显示所连接的电脑 可调整影像质量以弹性适应不同的网络环境 自动扫描功能可监看使用者所选择的电脑状态支持广播模式,可同时于所有选择的电脑上进行指令操作(如安装软件、系统关闭…等) 支持固件更新支持备份与复原组态设定,以及使用者账号设定 事件日志功能开启/关闭浏览器访问功能简易使用的接口本地控制端的浏览器与AP 图形化使用者接口(GUI)搭配OS D屏幕选单,可提供强大、直觉式、人性化与多国语言的接口,以减少使用者学习时间并提高产能 支持多平台的客户端系统 (W indow s, Mac OS X, Linux, Sun) 支持多种浏览器接口 (IE, Mozilla, Fir e fox, Safari, Op e ra, N e tscap e ) 当设备顺序改变时,可自动重新配置连接端口名称画面分割模式可让使用者从单一屏幕同时监看不同的电脑状态–每个所选的 电脑影像输出可显示在一个分割的屏幕上–使用者可轻松选择欲检视的画面数目 支持W indow s clie nt 与Jav a clie nt 软件;Jav a clie nt 可在所有的操作系统下运作先进的安全机制通过RC 4 128 b it 加密技术以确保键盘、鼠标、屏幕信号传输的安全性 128 b it SS L浏览器访问 双层密码保护机制–最多可允许64位使用者账号拥有各自的数据设定 支持外部(远程)认证机制–R ADIUS 、L DAP 、L DAPS 、MS Act ive Dir e ctory 支持IP/MA C过滤功能 本地端与远程登入及验证机制虚拟远程桌面窗口信息板功能可让已登入的使用者相互沟通,并可允许其中一位使用者单独控管KVM 功能支持鼠标动态同步显示(Mous e DynaSyncTM )技术 支持多国语言屏幕(on-scr ee n)键盘 BIOS 层级访问硬件8/16端口支持远程访问的KVM 多电脑切换器–可通过单一KVM 控制端监控多达8/16台电脑 可菊链串接额外15台KVM 多电脑切换器–单一控制端可控管多达128台(C S1708i)或256(C S 1716i)台电脑*在菊链串接的架构下,可自动侦测装置机台位置并显示于前端面板的LE D指示灯上,无须手动进行DIP 设定 支持热插拔–毋须关闭电源即可直接增加或移除电脑支持IP v6NEW可通过前端面板按键、热键与支持多国语言的OS D屏幕选单进行电脑选择与切换 允许32位使用者同时登入 多国语言的web使用者接口,可支持本地端与远程OS D以树状架构显示所连接的电脑 可调整影像质量以弹性适应不同的网络环境 自动扫描功能可监看使用者所选择的电脑状态 支持广播模式,可同时于所有选择的电脑上进行指令操作(如安装软件、系统关闭…等) 支持固件更新 支持备份与复原组态设定,以及使用者账号设定 事件日志功能 开启/关闭浏览器访问功能简易使用的接口 本地控制端的浏览器与AP 图形化使用者接口(GUI)搭配OS D屏幕选单,可提供强大、直觉式、人性化与多国语言的接口,以减少使用者学习时间并提高产能 支持多平台的客户端系统 (W indow s, Mac OS X, Linux, Sun) 支持多种浏览器接口 (IE, Mozilla, Fir e fox, Safari, Op e ra, N e tscap e ) 当设备顺序改变时,可自动重新配置连接端口名称 画面分割模式可让使用者从单一屏幕同时监看不同的电脑状态–每个所选的 电脑影像输出可显示在一个分割的屏幕上–使用者可轻松选择欲检视的画面数目 支持W indow s clie nt 与Jav a clie nt 软件;Jav a clie nt 可在所有的操作系统下运作先进的安全机制 通过RC 4 128 b it 加密技术以确保键盘、鼠标、屏幕信号传输的安全性 128 b it SS L浏览器访问 双层密码保护机制–最多可允许64位使用者账号拥有各自的数据设定 支持外部(远程)认证机制–R ADIUS 、L DAP 、L DAPS 、MS Act ive Dir e ctory 支持IP/MA C过滤功能 本地端与远程登入及验证机制虚拟远程桌面窗口 信息板功能可让已登入的使用者相互沟通,并可允许其中一位使用者单独控管KVM 功能 支持鼠标动态同步显示(Mous e DynaSync TM )技术 支持多国语言屏幕(on-scr ee n)键盘 BIOS 层级访问硬件 8/16端口支持远程访问的KVM 多电脑切换器–可通过单一KVM 控制端监控多达8/16台电脑 可菊链串接额外15台KVM 多电脑切换器–单一控制端可控管多达128台(C S1708i)或256(C S 1716i)台电脑* 在菊链串接的架构下,可自动侦测装置机台位置并显示于前端面板的LE D指示灯上,无须手动进行DIP 设定 支持热插拔–毋须关闭电源即可直接增加或移除电脑p3简易使用的接口虚拟远程桌面优异的视频质量分割画面模式信息板功能鼠标动态同步显示Mouse DynaSyncT M 前端面板的USB Hub可供连接的电脑进行外围设备分享 双接口–具备自动侦测接口的功能,可支持配备PS/2或USB键盘及鼠标的电脑 USB / PS/2键盘与鼠标仿真功能–即使控制端在不同电脑之间切换,仍可确保电脑正常开机运作 支持多媒体USB键盘(PC、Mac与Sun) 高视频分辨率–本地端支持2048 x 1536,DDC2B;远程支持1600 x1200@60Hz / 24位色深屏幕动态显示技术(Video DynaSync T M )–储存控制端屏幕E DID(延伸显示辨识码),保持最佳屏幕显示分辨率可安装于19寸(1U)机架空间*兼容的KVM多电脑切换器:AC S1208A、A C S 1216A、CS1708、CS1716、CS 1708A 、CS 1716A 、K H1508、KH1516浅显易懂的图形化使用者接口使访问、组态设定与操作更轻松简易。

K8D1716UBC-TI09资料

FLASH MEMORY K8D1716UTC / K8D1716UBCDocument Title16M Bit (2M x8/1M x16) Dual Bank NOR Flash MemoryRevision HistoryRevision No.0.00.10.21.0RemarkAdvancePreliminaryPreliminary HistoryInitial DraftSupport 48TSOP1 Lead Free PackageSupport 48FBGA Leaded/Lead Free PackageSpecification finalizedDraft DateJuly 25, 2004Sep 16, 2004Nov 29, 2004Dec 16, 2004FLASH MEMORYK8D1716UTC / K8D1716UBC16M Bit (2M x8/1M x16) Dual Bank NOR Flash MemoryThe K8D1716U featuring single 3.0V power supply, is a 16Mbit NOR-type Flash Memory organized as 2Mx8 or 1M x16. The memory architecture of the device is designed to divide its memory arrays into 39 blocks to be protected by the block group. This block architecture provides highly flexible erase and program capability. The K8D1716U NOR Flash consists of two banks. This device is capable of reading data from one bank while programming or erasing in the other bank. Access times of 70ns, 80ns and 90ns are available for the device. The device ′s fast access times allow high speed microprocessors to operate without wait states. The device performs a program operation in units of 8 bits (Byte) or 16 bits (Word) and erases in units of a block. Single or multiple blocks can be erased. The block erase operation is completed within typically 0.7 sec. The device requires 15mA as program/erase current in the standard and industrial temperature ranges.The K8D1716U NOR Flash Memory is created by using Sam-sung's advanced CMOS process technology. This device is available in 48 pin TSOP1 and 48 ball FBGA package. The device is compatible with EPROM applications to require high-density and cost-effective nonvolatile read/write storage solu-tions.FEATURES• Single Voltage, 2.7V to 3.6V for Read and Write operations • Organization1,048,576 x 16 bit (Word mode)• Fast Read Access Time : 70ns• Read While Program/Erase Operation • Dual Bank architecturesBank 1 / Bank 2 : 8Mb / 8Mb• Secode(Security Code) Block : Extra 64K Byte block • Power Consumption (typical value @5MHz) - Read Current : 14mA- Program/Erase Current : 15mA- Read While Program or Read While Erase Current : 25mA - Standby Mode/Auto Sleep Mode : 5µA • WP/ACC input pin- Allows special protection of two outermost boot blocks at V IL , regardless of block protect status- Removes special protection of two outermost boot block at V IH, the two blocks return to normal block protect status - Program time at V HH : 9µs/word • Erase Suspend/Resume • Unlock Bypass Program • Hardware RESET Pin• Command Register Operation• Block Group Protection / Unprotection• Supports Common Flash Memory Interface • Industrial Temperature : -40°C to 85°C• Endurance : 100,000 Program/Erase Cycles Minimum • Data Retention : 10 years• Package : 48 Pin TSOP1 : 12 x 20 mm / 0.5 mm Pin pitch 48 Ball FBGA : 6 x 8.5 mm / 0.8 mm Ball pitchGENERAL DESCRIPTIONSAMSUNG ELECTRONICS CO., LTD. reserves the right to change products and specifications without notice.PIN DESCRIPTIONPin Name Pin FunctionA0 - A19Address Inputs DQ0 - DQ14Data Inputs / Outputs DQ15/A-1DQ15 Data Input / Output A-1 LSB Address BYTE Word / Byte Selection CE Chip Enable OE Output Enable RESET Hardware Reset Pin RY/BY Ready/Busy Output WE Write EnableWP/ACCHardware Write Protection/Program Acceleration Vcc Power Supply V SS Ground N.CNo ConnectionPIN CONFIGURATION48-pin TSOP1Standard Type 12mm x 20mm123456789101112131415161718192021222324484746454443424140393837363534333231302928272625A15A14A13A12A11A10A9A8A19N.C WE RESETN.C WP/ACC RY/BY A18A17A7A6A5A4A3A2A1A16BYTE VssDQ15/A-1DQ7DQ14DQ6DQ13DQ5DQ12DQ4Vcc DQ11DQ3DQ10DQ2DQ9DQ1DQ8DQ0OE Vss CE A0Note :Please refer to the package dimension.FLASH MEMORY K8D1716UTC / K8D1716UBCFUNCTIONAL BLOCK DIAGRAMVccVssCEOEWEBYTERESETRY/BYA0~A19 DQ0~DQ14I/OInterface&BankControlXDecY Dec Latch &ControlLatch &ControlDecXY DecEraseControlProgramControlHighVoltageGen.Bank2Cell ArrayBank1AddressBank2AddressBank1 Data-In/OutBank2 Data-In/OutBank1Cell ArrayWP/ACC DQ15/A-1A3A7A9A13A4A17RESETRY/BYA8A12A2A6A18N.C A10A14DQ15/A5N.C A19A11A0DQ0DQ2DQ5DQ7A16CE DQ8DQ10DQ12DQ14BYTEDQ9DQ11V CC DQ13V SS DQ1DQ3DQ4DQ6V SSA-123456CDEFGHWEWP/A1A15OEACC48 Ball FBGA TOP VIEW (BALL DOWN)1ABFLASH MEMORYK8D1716UTC / K8D1716UBCORDERING INFORMATIONK 8 D 17 1 6 U T C - Y I 0 7SamsungNOR Flash Memory Device TypeDual Bank Boot BlockOperating Temperature RangeC = Commercial Temp. (0 °C to 70 °C) I = Industrial Temp. (-40 °C to 85 °C)Block Architecture T = Top Boot Block B = Bottom Boot BlockVersion ionAccess Time 07 = 70 ns 08 = 80 ns 09 = 90 nsOperating Voltage Range 2.7V to 3.6VOrganization x16Table 1. PRODUCT LINE-UPPart No.- 7-8-9Vcc2.7V~3.6V Max. Address Access Time (ns)70ns 80ns 90ns Max. CE Access Time (ns)70ns 80ns 90ns Max. OE Access Time (ns)25ns 25ns35ns Table 2. K8D1716U DEVICE BANK DIVISIONSDevice Part Number Bank 1Bank 2Mbit Block Sizes Mbit Block Sizes K8D1716U8 MbitEight 8 Kbyte/4 Kword,fifteen 64 Kbyte/32 Kword8 MbitSixteen64 Kbyte/32 KwordBank Division17 = 8Mbits + 8Mbits PackageP = 48TSOP1(Lead-Free) Y = 48 TSOP1 D : FBGA(Lead Free) F : FBGAFLASH MEMORY K8D1716UTC / K8D1716UBCTable 3. Top Boot Block Address(K8D1716UT)K8D1716UT Block A19A18A17A16A15A14A13A12 Block Size(KW/KB)Address RangeWord Mode Byte ModeBank1BA38111111114/8FF000H-FFFFFH1FE000H-1FFFFFH BA37111111104/8FE000H-FEFFFH1FC000H-1FDFFFH BA36111111014/8FD000H-FDFFFH1FA000H-1FBFFFH BA35111111004/8FC000H-FCFFFH1F8000H-1F9FFFH BA34111110114/8FB000H-FBFFFH1F6000H-1F7FFFH BA33111110104/8FA000H-FAFFFH1F4000H-1F5FFFH BA32111110014/8F9000H-F9FFFH1F2000H-1F3FFFH BA31111110004/8F8000H-F8FFFH1F0000H-1F1FFFH BA3011110X X X32/64F0000H-F7FFFH1E0000H-1EFFFFH BA2911101X X X32/64E8000H-EFFFFH1D0000H-1DFFFFH BA2811100X X X32/64E0000H-E7FFFH1C0000H-1CFFFFH BA2711011X X X32/64D8000H-DFFFFH1B0000H-1BFFFFH BA2611010X X X32/64D0000H-D7FFFH1A0000H-1AFFFFH BA2511001X X X32/64C8000H-CFFFFH190000H-19FFFFH BA2411000X X X32/64C0000H-C7FFFH180000H-18FFFFH BA2310111X X X32/64B8000H-BFFFFH170000H-17FFFFH BA2210110X X X32/64B0000H-B7FFFH160000H-16FFFFH BA2110101X X X32/64A8000H-AFFFFH150000H-15FFFFH BA2010100X X X32/64A0000H-A7FFFH140000H-14FFFFH BA1910011X X X32/6498000H-9FFFFH130000H-13FFFFH BA1810010X X X32/6490000H-97FFFH120000H-12FFFFH BA1710001X X X32/6488000H-8FFFFH110000H-11FFFFH BA1610000X X X32/6480000H-87FFFH100000H-10FFFFHBank2BA1501111X X X32/6478000H-7FFFFH0F0000H-0FFFFFH BA1401110X X X32/6470000H-77FFFH0E0000H-0EFFFFH BA1301101X X X32/6468000H-6FFFFH0D0000H-0DFFFFH BA1201100X X X32/6460000H-67FFFH0C0000H-0CFFFFH BA1101011X X X32/6458000H-5FFFFH0B0000H-0BFFFFH BA1001010X X X32/6450000H-57FFFH0A0000H-0AFFFFH BA901001X X X32/6448000H-4FFFFH090000H-09FFFFH BA801000X X X32/6440000H-47FFFH080000H-08FFFFH BA700111X X X32/6438000H-3FFFFH070000H-07FFFFH BA600110X X X32/6430000H-37FFFH060000H-06FFFFH BA500101X X X32/6428000H-2FFFFH050000H-05FFFFH BA400100X X X32/6420000H-27FFFH040000H-04FFFFH BA300011X X X32/6418000H-1FFFFH030000H-03FFFFH BA200010X X X32/6410000H-17FFFH020000H-02FFFFH BA100001X X X32/6408000H-0FFFFH010000H-01FFFFH BA000000X X X32/6400000H-07FFFH000000H-00FFFFHDeviceBlock AddressA19-A12BlockSize(X8)Address Range(X16)Address RangeK8D1716UT11111xxx64/321F0000H-1FFFFFH F8000H-FFFFFHTable 4. Secode Block Addresses for Top Boot DevicesFLASH MEMORY K8D1716UTC / K8D1716UBCTable 5. Bottom Boot Block Address(K8D1716UB)K8D1716UT Block A19A18A17A16A15A14A13A12 Block Size(KW/KB)Address RangeWord Mode Byte ModeBank2BA3811111X X X32/64F8000H-FFFFFH1F0000H-1FFFFFH BA3711110X X X32/64F0000H-F7FFFH1E0000H-1EFFFFH BA3611101X X X32/64E8000H-EFFFFH1D0000H-1DFFFFH BA3511100X X X32/64E0000H-E7FFFH1C0000H-1CFFFFH BA3411011X X X32/64D8000H-DFFFFH1B0000H-1BFFFFH BA3311010X X X32/64D0000H-D7FFFH1A0000H-1AFFFFH BA3211001X X X32/64C8000H-CFFFFH190000H-19FFFFH BA3111000X X X32/64C0000H-C7FFFH180000H-18FFFFH BA3010111X X X32/64B8000H-BFFFFH170000H-17FFFFH BA2910110X X X32/64B0000H-B7FFFH160000H-16FFFFH BA2810101X X X32/64A8000H-AFFFFH150000H-15FFFFH BA2710100X X X32/64A0000H-A7FFFH140000H-14FFFFH BA2610011X X X32/6498000H-9FFFFH130000H-13FFFFH BA2510010X X X32/6490000H-97FFFH120000H-12FFFFH BA2410001X X X32/6488000H-8FFFFH110000H-11FFFFH BA2310000X X X32/6480000H-87FFFH100000H-10FFFFHBank1BA2201111X X X32/6478000H-7FFFFH0F0000H-0FFFFFH BA2101110X X X32/6470000H-77FFFH0E0000H-0EFFFFH BA2001101X X X32/6468000H-6FFFFH0D0000H-0DFFFFH BA1901100X X X32/6460000H-67FFFH0C0000H-0CFFFFH BA1801011X X X32/6458000H-5FFFFH0B0000H-0BFFFFH BA1701010X X X32/6450000H-57FFFH0A0000H-0AFFFFH BA1601001X X X32/6448000H-4FFFFH090000H-09FFFFH BA1501000X X X32/6440000H-47FFFH080000H-08FFFFH BA1400111X X X32/6438000H-3FFFFH070000H-07FFFFH BA1300110X X X32/6430000H-37FFFH060000H-06FFFFH BA1200101X X X32/6428000H-2FFFFH050000H-05FFFFH BA1100100X X X32/6420000H-27FFFH040000H-04FFFFH BA1000011X X X32/6418000H-1FFFFH030000H-03FFFFH BA900010X X X32/6410000H-17FFFH020000H-02FFFFH BA800001X X X32/6408000H-0FFFFH010000H-01FFFFH BA7000001114/807000H-07FFFH00E000H-00FFFFH BA6000001104/806000H-06FFFH00C000H-00DFFFH BA5000001014/805000H-05FFFH00A000H-00BFFFH BA4000001004/804000H-04FFFH008000H-009FFFH BA3000000114/803000H-03FFFH006000H-007FFFH BA2000000104/802000H-02FFFH004000H-005FFFH BA1000000014/801000H-01FFFH002000H-003FFFH BA0000000004/800000H-00FFFH000000H-001FFFHDeviceBlock AddressA19-A12BlockSize(X8)Address Range(X16)Address Range K8D1716UB00000xxx64/32000000H-00FFFFH00000H-07FFFHTable 6. Secode Block Addresses for Bottom Boot DevicesFLASH MEMORYK8D1716UTC / K8D1716UBCPRODUCT INTRODUCTIONTable 7. Operations TableOperation CEOE WE BYTE WP/ACC A9A6A1A0DQ15/A-1DQ8/DQ14DQ0/DQ7RESET Read word L L H H L/H A9A6A1A0DQ15D OUT D OUT H byteL L H L A9A6A1A0A-1High-Z D OUT H Stand-by Vcc ±0.3V X X X (2)X X X X High-Z High-Z High-Z (2)Output Disable L H H X L/H X X X X High-Z High-Z High-Z H Reset X X X X L/H X X X X High-Z High-Z High-Z L Writeword L H L H (4)A9A6A1A0D IN D IN D IN H byteL H L L A9A6A1A0A-1High-Z D IN H Enable Block Group Protect (3)L H L X L/H X L H L X X D IN V ID Enable Block Group Unprotect (3)L H L X (4)X H H L X X D IN V ID Temporary Block GroupX X X X (4)X X X X X X X V ID Auto SelectManufacturer ID (5)L L H X L/H V ID L L L X X Code (SeeTable 9)H Auto SelectDevice Code (5)LLHXL/HV IDLLHXXCode (SeeTable 9)HNotes :1. L = V IL (Low), H = V IH (High), V ID = 8.5V~12.5V, D IN = Data in, D OUT = Data out, X = Don't care. 2. WP/ACC and RESET pin are asserted at Vcc ±0.3 V or Vss ±0.3 V in the Stand-by mode.3. Addresses must be composed of the Block address (A12 - A19).The Block Protect and Unprotect operations may be implemented via programming equipment too. Refer to the "Block Group Protection and Unprotection".4. If WP/ACC =V IL, the two outermost boot blocks is protected. If WP/ACC =V IH, the two outermost boot block protection depends on whether those blocks were last protected or unprotected using the method described in "Block Group Protection and Unprotection". If WP/ACC =V HH , all blocks will be temporarily unprotected.5. Manufacturer and device codes may also be accessed via a command register write sequence. Refer to Table 9.The K8D1716U is a 16Mbit (16,777,216 bits) NOR-type Flash memory. The device features single voltage power supply operating within the range of 2.7V to 3.6V. The device is programmed by using the Channel Hot Electron (CHE) injection mechanism which is used to program EPROMs. The device is erased electrically by using Fowler-Nordheim tunneling mechanism. To provide highly flex-ible erase and program capability, the device adapts a block memory architecture that divides its memory array into 39 blocks (64-Kbyte x 31 , 8-Kbyte x 8). Programming is done in units of 8 bits (Byte) or 16 bits (Word). All bits of data in one or multiple blocks can be erased simultaneously when the device executes the erase operation. To prevent the device from accidental erasing or over-writ-ing the programmed data, 39 memory blocks can be hardware protected by the block group. Byte/Word modes are available for read operation. These modes can be selected via BYTE pin. The device provides read access times of 70ns, 80ns and 90ns supporting high speed microprocessors to operate without any wait states.The command set of K8D1716U is fully compatible with standard Flash devices. The device is controlled by chip enable (CE), output enable (OE) and write enable (WE). Device operations are executed by selective command codes. The command codes to be com-bined wih addresses and data are sequentially written to the command registers using microprocessor write timing. The command codes serve as inputs to an internal state machine which controls the program/erase circuitry. Register contents also internally latch addresses and data necessary to execute the program and erase operations. The K8D1716U is implemented with Internal Program/Erase Algorithms to execute the program/erase operations. The Internal Program/Erase Algorithms are invoked by program/erase command sequences. The Internal Program Algorithm automatically programs and verifies data at specified addresses. The Internal Erase Algorithm automatically pre-programs the memory cell which is not programmed and then executes the erase operation. The K8D1716U has means to indicate the status of completion of program/erase operations. The status can be indicated via the RY/BY pin, Data polling of DQ7, or the Toggle bit (DQ6). Once the operations have been completed, the device automatically resets itself to the read mode. The device requires only 14 mA as active read current and 15 mA for program/erase operations.FLASH MEMORY K8D1716UTC / K8D1716UBCCOMMAND DEFINITIONSThe K8D1716U operates by selecting and executing its operational modes. Each operational mode has its own command set. In order to select a certain mode, a proper command with specific address and data sequences must be written into the command reg-ister. Writing incorrect information which include address and data or writing an improper command will reset the device to the read mode. The defined valid register command sequences are stated in Table 8. Note that Erase Suspend (B0H) and Erase Resume (30H) commands are valid only while the Block Erase Operation is in progress.Table 8. Command SequencesCommand Sequence Cycle1st Cycle2nd Cycle3rd Cycle4th Cycle5th Cycle6th Cycle Word Byte Word Byte Word Byte Word Byte Word Byte Word ByteRead Addr1RA Data RDReset Addr1XXXH Data F0HAutoselect Manufacturer ID (2,3) Addr4555H AAAH2AAH555HDA/555HDA/AAAHDA/X00HDA/X00H Data AAH 55H90H ECHAutoselect Device Code (2,3) Addr4555H AAAH2AAH555HDA/555HDA/AAAHDA/X01HDA/X02HData AAH 55H90H(SeeTable9)Autoselect Block Group Protect Verify (2,3) Addr4555H AAAH2AAH555HDA/555HDA/AAAHBA /X02HBA/X04H Data AAH 55H90H(See Table 9)Auto Select Secode Block Factory Protect Verify (2,3) Addr4555H AAAH2AAH555HDA/555HDA/AAAHDA /X03HDA/X06H Data AAH 55H90H(See Table 9)Enter Secode Block Region Addr3555H AAAH2AAH555H 555H AAAH Data AAH 55H88HExit Secode Block Region Addr4555H AAAH2AAH555H 555H AAAH XXXH Data AAH 55H90H00HProgram Addr4555H AAAH2AAH555H 555H AAAH PA Data AAH55H A0H PDUnlock Bypass Addr3555H AAAH2AAH555H 555H AAAH Data AAH55H20HUnlock Bypass Program Addr2XXXH PA Data A0H PDUnlock Bypass Reset Addr2XXXH XXXH Data90H00HChip Erase Addr6555H AAAH2AAH555H 555H AAAH 555H AAAH 2AAH555H555H AAAH Data AAH55H80H AAH55H10HBlock Erase Addr6555H AAAH2AAH555H 555H AAAH 555H AAAH 2AAH555H BA Data AAH55H80H AAH55H30HBlock Erase Suspend (4, 5)Addr1XXXH Data B0HBlock Erase Resume Addr1XXXH Data30HCFI Query (6)Addr155H AAH Data98HFLASH MEMORY K8D1716UTC / K8D1716UBCNotes : 1. RA : Read Address, PA : Program Address, RD : Read Data, PD : Program DataDA : Dual Bank Address, BA : Block Address (A12 - A19), X = Don’t care .2. To terminate the Autoselect Mode, it is necessary to write Reset command to the register.3. The 4th cycle data of Autoselect mode is output data.The 3rd and 4th cycle bank addresses of Autoselect mode must be same.4. The Read / Program operations at non-erasing blocks and the autoselect mode are allowed in the Erase Suspend mode.5. The Erase Suspend command is applicable only to the Block Erase operation.6. Command is valid when the device is in read mode or Autoselect mode.7. DQ8 - DQ15 are don’t care in command sequence, but RD and PD is excluded.8. A11 - A19 are also don’t care, except for the case of special notice.Description CE OE WE A19toA12A11toA10A9A8toA7A6A5toA2A1A0DQ8 to DQ15DQ7toDQ0BYTE=V IHBYTE=V ILManufacturer ID L L H DA X V ID X L X L L X X ECH Device Code K8D1716UT(Top Boot Block)L L H DA X V ID X L X L H22H X75HDevice Code K8D1716UB(Bottom Boot Block)L L H DA X V ID X L X L H22H X77HBlock Protection Verification L L H BA X V ID X L X H L X X01H (Protected),00H (Unprotected)Secode Block (2) Indicator Bit (DQ7)L L H DA X V ID X L X H H X X80H (Factory locked),00H (Not factory locked)Table 9. K8D1716U Autoselect Codes, (High Voltage Method)Notes : 1. L=Logic Low=V IL, H=Logic High=V IH, DA=Dual Bank Address, BA=Block Address, X=Don’t care.2. Secode Block : Security Code Block.FLASH MEMORYK8D1716UTC / K8D1716UBCDEVICE OPERATION Byte/Word ModeIf the BYTE pin is set at logical "1" , the device is in word mode, DQ0-DQ15 are active. Otherwise the BYTE pin is set at logical "0" ,the device is in byte mode, DQ0-DQ7 are active. DQ8-DQ14 are in the High-Z state and DQ15 pin is used as an input for the LSB (A-1) address pin.Read ModeThe K8D1716U is controlled by Chip Enable (CE), Output Enable (OE) and Write Enable (WE). When CE and OE are low and WE is high, the data stored at the specified address location,will be the output of the device. The outputs are in high impedance state whenever CE or OE is high.Standby ModeThe K8D1716U features Stand-by Mode to reduce power consumption. This mode puts the device on hold when the device is dese-lected by making CE high (CE = V IH ). Refer to the DC characteristics for more details on stand-by modes.Output DisableThe device outputs are disabled when OE is High (OE = V IH ). The output pins are in high impedance state.Automatic Sleep ModeK8D1716U features Automatic Sleep Mode to minimize the device power consumption. Since the device typically draws 5µA of the current in Automatic Sleep Mode, this feature plays an extremely important role in battery-powered applications. When addresses remain steady for t AA +50ns, the device automatically activates the Automatic Sleep Mode. In the sleep mode, output data is latched and always available to the system. When addresses are changed, the device provides new data without wait time.Data Outputst AA + 50nsDataAuto Sleep ModeAddressData Data Data DataFigure 1. Auto Sleep Mode OperationAutoselect ModeThe K8D1716U offers the Autoselect Mode to identify manufacturer and device type by reading a binary code. The Autoselect Mode allows programming equipment to automatically match the device to be programmed with its corresponding programming algorithm.In addition, this mode allows the verification of the status of write protected blocks. This mode is used by two method. The one is high voltage method to be required V ID (8.5V~12.5V) on address pin A9. When A9 is held at V ID and the bank address or block address is asserted, the device outputs the valid data via DQ pins(see Table 9 and Figure 2). The rest of addresses except A0, A1 and A6 are Don ′t Care. The other is autoselect command method that the autoselect code is accessible by the commamd sequence without V ID.The manufacturer and device code may also be read via the command register. The Command Sequence is shown in Table 8 and Figure 3. The autoselect operation of block protect verification is initiated by first writing two unlock cycle. The third cycle must con-tain the bank address and autoselect command (90H). If Block address while (A6, A1, A0) = (0,1,0) is finally asserted on the address pin, it will produce a logical "1" at the device output DQ0 to indicate a write protected block or a logical "0" at the device output DQ0to indicate a write unprotected block. To terminate the autoselect operation, write Reset command (F0H) into the command register.FLASH MEMORYK8D1716UTC / K8D1716UBCFigure 3. Autoselect Operation ( by command sequence method )WE555H/AAAH 2AAH/555H 555H/AAAH AAH 55H 90H 00H/01H/ECHManufacturerCode Device Code A19∼A0(x16)/*DQ15∼DQ0F0HReturn to Read ModeWrite (Program/Erase) ModeThe K8D1716U executes its program/erase operations by writing commands into the command register. In order to write the com-mands to the register, CE and WE must be low and OE must be high. Addresses are latched on the falling edge of CE or WE (which-ever occurs last) and the data are latched on the rising edge of CE or WE (whichever occurs first). The device uses standard microprocessor write timing.ProgramThe K8D1716U can be programmed in units of a word or a byte. Programming is writing 0's into the memory array by executing the Internal Program Routine. In order to perform the Internal Program Routine, a four-cycle command sequence is necessary. The first two cycles are unlock cycles. The third cycle is assigned for the program setup command. In the last cycle, the address of the mem-ory location and the data to be programmed at that location are written. The device automatically generates adequate program pulses and verifies the programmed cell margin by the Internal Program Routine. During the execution of the Routine, the system is not required to provide further controls or timings.During the Internal Program Routine, commands written to the device will be ignored. Note that a hardware reset during a program operation will cause data corruption at the corresponding location.Figure 4. Program Command SequenceWE555H/AAAH2AAH/555H555H/AAAHAAH55HA0HProgram Program Program StartDQ15-DQ0AddressDataRY/BYA9V ID00H01HECH2275H or 2277H Manufacturer CodeDevice Code A6,A1,A0*DQ15-DQ0Figure 2. Autoselect Operation ( by high voltage method )Return to Read ModeV = V IH or V IL2275H or 2277H Note : The addresses other than A0 , A1 and A6 are Don ′t care. Please refer to Table 9 for device code.Note : The 3rd Cycle and 4th Cycle address must include the same bank address. Please refer to Table 9 for device code.(K8D1716U )(K8D1716U)A19∼A-1(x8)A19∼A0(x16)/A19∼A-1(x8)00H 02HFLASH MEMORYK8D1716UTC / K8D1716UBCUnlock BypassThe K8D1716U provides the unlock bypass mode to save its program time for program operation. The mode is invoked by the unlock bypass command sequence. Then, the unlock bypass program command sequence is required to program the device.Unlike the standard program command sequence that contains four bus cycles, the unlock bypass program command sequence comprises only two bus cycles.The unlock bypass mode is engaged by issuing the unlock bypass command sequence which is comprised of three bus cycles. Writ-ing first two unlock cycles is followed by a third cycle containing the unlock bypass command (20H). Once the device is in the unlock bypass mode, the unlock bypass program command sequence is necessary to program in this mode. The unlock bypass program command sequence is comprised of only two bus cycles; writing the unlock bypass program command (A0H) is followed by the pro-gram address and data. This command sequence is the only valid one for programming the device in the unlock bypass mode.The unlock bypass reset command sequence is the only valid command sequence to exit the unlock bypass mode. The unlock bypass reset command sequence consists of two bus cycles. The first cycle must contain the data (90H). The second cycle contains only the data (00H). Then, the device returns to the read mode.Chip EraseTo erase a chip is to write 1′s into the entire memory array by executing the Internal Erase Routine. The Chip Erase requires six bus cycles to write the command sequence. The erase set-up command is written after first two "unlock" cycles. Then, there are two more write cycles prior to writing the chip erase command. The Internal Erase Routine automatically pre-programs and verifies the entire memory for an all zero data pattern prior to erasing. The automatic erase begins on the rising edge of the last WE or CE pulse in the command sequence and terminates when DQ7 is "1". After that the device returns to the read mode.Figure 5. Chip Erase Command SequenceWE555H/AAAH2AAH/555H555H/AAAHAAH55H80H555H Chip Erase StartDQ15-DQ0AAAH2AAH/555HAAH55H10HRY/BY555H/AAAHA19∼A0(x16)/A19∼A-1(x8)Block EraseTo erase a block is to write 1′s into the desired memory block by executing the Internal Erase Routine. The Block Erase requires six bus cycles to write the command sequence shown in Table 8. After the first two "unlock" cycles, the erase setup command (80H) is written at the third cycle. Then there are two more "unlock" cycles followed by the Block Erase command. The Internal Erase Routine automatically pre-programs and verifies the entire memory prior to erasing it. The block address is latched on the falling edge of WE or CE, while the Block Erase command is latched on the rising edge of WE or CE.Multiple blocks can be erased sequentially by writing the six bus-cycle operation in Figure 6. Upon completion of the last cycle for the Block Erase, additional block address and the Block Erase command (30H) can be written to perform the Multi-Block Erase. An 50µs (typical) "time window" is required between the Block Erase command writes. The Block Erase command must be written within the 50µs "time window", otherwise the Block Erase command will be ignored. The 50µs "time window" is reset when the falling edge of the WE occurs within the 50µs of "time window" to latch the Block Erase command. During the 50µs of "time window", any command other than the Block Erase or the Erase Suspend command written to the device will reset the device to read mode. After the 50µs of "time window", the Block Erase command will initiate the Internal Erase Routine to erase the selected blocks. Any Block Erase address and command following the exceeded "time window" may or may not be accepted. No other commands will be recognized except the Erase Suspend command during Block Erase operation.。

ic卡1604的原理及应用如ft1780芯片内部结构和特点

逻辑加密存储卡芯片AT88SC1604卡的应用摘要:本文介绍了目前应用较为广泛的AT88SC1604逻辑加密卡的特点和工作原理,同时给出了通过单片机控制操作IC卡的的应用实例及程序。

前言IC卡按结构划分,可分为存储器卡和微处理器卡(CPU card)两大类。

逻辑加密卡与普通存储卡相比,内部结构较复杂,其存储区可以分成卡片设置区和应用区。

卡片设置区内存放与卡片厂商及发卡者相关代码和卡片密码;应用区又可以根据需要分为不同的分区。

逻辑加密卡的安全性相对较高,体现在:卡片设立主密码、每个应用分区具有各自独立的操作密码。

逻辑加密卡主要控制作用是:对数据存储区开放/关闭的控制;对数据存储区读/写的控制;对数据存储区擦除操作的控制以及对密码校验和错误次数计数及锁闭功能控制。

AT88SC1604卡的工作原理AT88SC1604是由美国ATMEL公司设计的逻辑加密存储卡芯片。

它具有15704位的存储容量,是目前逻辑加密存储卡中容量较大的一种产品芯片。

芯片特点(1) AT88SC1604芯片属于单存储器多逻辑分区结构。

主存储器除划分了特定的标志数据区和控制数据区之外,还将应用数据区分成四个完全隔离的子区,并在每个子区中配备了各自的读、写控制标志和写入/擦除密码以及密码输入错误计数器等逻辑控制。

(2) 芯片为串行传输方式,并满足ISO7816-3同步传输协议。

(3)芯片采用低功耗的CMOS工艺制造,每字位的读取时间为 s,写周期为5ms。

(4) 芯片内部的存储单元具有至少10000次的擦除/改写循环次数。

数据保存期为10年。

芯片存储分区结构及定义AT88SC1604芯片分为制造商代码区、发行商代码区、用户安全密码区、用户密码比较计数区、个人代码区以及四个应用区。

每个应用区都由密码区,密码比较计数区,擦除密码区和擦除密码比较计数区、应用数据区和存储器测试区组成。

(1) 制造商代码区(FZ)该区里记录的卡芯片生产商的特定信息(例如:生产批号、日期、以及特别制定的特征代码),由制造商在芯片出厂前写入。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FLASH MEMORY K8D1716UTC / K8D1716UBCDocument Title16M Bit (2M x8/1M x16) Dual Bank NOR Flash MemoryRevision HistoryRevision No.0.00.10.21.0RemarkAdvancePreliminaryPreliminary HistoryInitial DraftSupport 48TSOP1 Lead Free PackageSupport 48FBGA Leaded/Lead Free PackageSpecification finalizedDraft DateJuly 25, 2004Sep 16, 2004Nov 29, 2004Dec 16, 2004FLASH MEMORYK8D1716UTC / K8D1716UBC16M Bit (2M x8/1M x16) Dual Bank NOR Flash MemoryThe K8D1716U featuring single 3.0V power supply, is a 16Mbit NOR-type Flash Memory organized as 2Mx8 or 1M x16. The memory architecture of the device is designed to divide its memory arrays into 39 blocks to be protected by the block group. This block architecture provides highly flexible erase and program capability. The K8D1716U NOR Flash consists of two banks. This device is capable of reading data from one bank while programming or erasing in the other bank. Access times of 70ns, 80ns and 90ns are available for the device. The device ′s fast access times allow high speed microprocessors to operate without wait states. The device performs a program operation in units of 8 bits (Byte) or 16 bits (Word) and erases in units of a block. Single or multiple blocks can be erased. The block erase operation is completed within typically 0.7 sec. The device requires 15mA as program/erase current in the standard and industrial temperature ranges.The K8D1716U NOR Flash Memory is created by using Sam-sung's advanced CMOS process technology. This device is available in 48 pin TSOP1 and 48 ball FBGA package. The device is compatible with EPROM applications to require high-density and cost-effective nonvolatile read/write storage solu-tions.FEATURES• Single Voltage, 2.7V to 3.6V for Read and Write operations • Organization1,048,576 x 16 bit (Word mode)• Fast Read Access Time : 70ns• Read While Program/Erase Operation • Dual Bank architecturesBank 1 / Bank 2 : 8Mb / 8Mb• Secode(Security Code) Block : Extra 64K Byte block • Power Consumption (typical value @5MHz) - Read Current : 14mA- Program/Erase Current : 15mA- Read While Program or Read While Erase Current : 25mA - Standby Mode/Auto Sleep Mode : 5µA • WP/ACC input pin- Allows special protection of two outermost boot blocks at V IL , regardless of block protect status- Removes special protection of two outermost boot block at V IH, the two blocks return to normal block protect status - Program time at V HH : 9µs/word • Erase Suspend/Resume • Unlock Bypass Program • Hardware RESET Pin• Command Register Operation• Block Group Protection / Unprotection• Supports Common Flash Memory Interface • Industrial Temperature : -40°C to 85°C• Endurance : 100,000 Program/Erase Cycles Minimum • Data Retention : 10 years• Package : 48 Pin TSOP1 : 12 x 20 mm / 0.5 mm Pin pitch 48 Ball FBGA : 6 x 8.5 mm / 0.8 mm Ball pitchGENERAL DESCRIPTIONSAMSUNG ELECTRONICS CO., LTD. reserves the right to change products and specifications without notice.PIN DESCRIPTIONPin Name Pin FunctionA0 - A19Address Inputs DQ0 - DQ14Data Inputs / Outputs DQ15/A-1DQ15 Data Input / Output A-1 LSB Address BYTE Word / Byte Selection CE Chip Enable OE Output Enable RESET Hardware Reset Pin RY/BY Ready/Busy Output WE Write EnableWP/ACCHardware Write Protection/Program Acceleration Vcc Power Supply V SS Ground N.CNo ConnectionPIN CONFIGURATION48-pin TSOP1Standard Type 12mm x 20mm123456789101112131415161718192021222324484746454443424140393837363534333231302928272625A15A14A13A12A11A10A9A8A19N.C WE RESETN.C WP/ACC RY/BY A18A17A7A6A5A4A3A2A1A16BYTE VssDQ15/A-1DQ7DQ14DQ6DQ13DQ5DQ12DQ4Vcc DQ11DQ3DQ10DQ2DQ9DQ1DQ8DQ0OE Vss CE A0Note :Please refer to the package dimension.FLASH MEMORY K8D1716UTC / K8D1716UBCFUNCTIONAL BLOCK DIAGRAMVccVssCEOEWEBYTERESETRY/BYA0~A19 DQ0~DQ14I/OInterface&BankControlXDecY Dec Latch &ControlLatch &ControlDecXY DecEraseControlProgramControlHighVoltageGen.Bank2Cell ArrayBank1AddressBank2AddressBank1 Data-In/OutBank2 Data-In/OutBank1Cell ArrayWP/ACC DQ15/A-1A3A7A9A13A4A17RESETRY/BYA8A12A2A6A18N.C A10A14DQ15/A5N.C A19A11A0DQ0DQ2DQ5DQ7A16CE DQ8DQ10DQ12DQ14BYTEDQ9DQ11V CC DQ13V SS DQ1DQ3DQ4DQ6V SSA-123456CDEFGHWEWP/A1A15OEACC48 Ball FBGA TOP VIEW (BALL DOWN)1ABFLASH MEMORYK8D1716UTC / K8D1716UBCORDERING INFORMATIONK 8 D 17 1 6 U T C - Y I 0 7SamsungNOR Flash Memory Device TypeDual Bank Boot BlockOperating Temperature RangeC = Commercial Temp. (0 °C to 70 °C) I = Industrial Temp. (-40 °C to 85 °C)Block Architecture T = Top Boot Block B = Bottom Boot BlockVersion ionAccess Time 07 = 70 ns 08 = 80 ns 09 = 90 nsOperating Voltage Range 2.7V to 3.6VOrganization x16Table 1. PRODUCT LINE-UPPart No.- 7-8-9Vcc2.7V~3.6V Max. Address Access Time (ns)70ns 80ns 90ns Max. CE Access Time (ns)70ns 80ns 90ns Max. OE Access Time (ns)25ns 25ns35ns Table 2. K8D1716U DEVICE BANK DIVISIONSDevice Part Number Bank 1Bank 2Mbit Block Sizes Mbit Block Sizes K8D1716U8 MbitEight 8 Kbyte/4 Kword,fifteen 64 Kbyte/32 Kword8 MbitSixteen64 Kbyte/32 KwordBank Division17 = 8Mbits + 8Mbits PackageP = 48TSOP1(Lead-Free) Y = 48 TSOP1 D : FBGA(Lead Free) F : FBGAFLASH MEMORY K8D1716UTC / K8D1716UBCTable 3. Top Boot Block Address(K8D1716UT)K8D1716UT Block A19A18A17A16A15A14A13A12 Block Size(KW/KB)Address RangeWord Mode Byte ModeBank1BA38111111114/8FF000H-FFFFFH1FE000H-1FFFFFH BA37111111104/8FE000H-FEFFFH1FC000H-1FDFFFH BA36111111014/8FD000H-FDFFFH1FA000H-1FBFFFH BA35111111004/8FC000H-FCFFFH1F8000H-1F9FFFH BA34111110114/8FB000H-FBFFFH1F6000H-1F7FFFH BA33111110104/8FA000H-FAFFFH1F4000H-1F5FFFH BA32111110014/8F9000H-F9FFFH1F2000H-1F3FFFH BA31111110004/8F8000H-F8FFFH1F0000H-1F1FFFH BA3011110X X X32/64F0000H-F7FFFH1E0000H-1EFFFFH BA2911101X X X32/64E8000H-EFFFFH1D0000H-1DFFFFH BA2811100X X X32/64E0000H-E7FFFH1C0000H-1CFFFFH BA2711011X X X32/64D8000H-DFFFFH1B0000H-1BFFFFH BA2611010X X X32/64D0000H-D7FFFH1A0000H-1AFFFFH BA2511001X X X32/64C8000H-CFFFFH190000H-19FFFFH BA2411000X X X32/64C0000H-C7FFFH180000H-18FFFFH BA2310111X X X32/64B8000H-BFFFFH170000H-17FFFFH BA2210110X X X32/64B0000H-B7FFFH160000H-16FFFFH BA2110101X X X32/64A8000H-AFFFFH150000H-15FFFFH BA2010100X X X32/64A0000H-A7FFFH140000H-14FFFFH BA1910011X X X32/6498000H-9FFFFH130000H-13FFFFH BA1810010X X X32/6490000H-97FFFH120000H-12FFFFH BA1710001X X X32/6488000H-8FFFFH110000H-11FFFFH BA1610000X X X32/6480000H-87FFFH100000H-10FFFFHBank2BA1501111X X X32/6478000H-7FFFFH0F0000H-0FFFFFH BA1401110X X X32/6470000H-77FFFH0E0000H-0EFFFFH BA1301101X X X32/6468000H-6FFFFH0D0000H-0DFFFFH BA1201100X X X32/6460000H-67FFFH0C0000H-0CFFFFH BA1101011X X X32/6458000H-5FFFFH0B0000H-0BFFFFH BA1001010X X X32/6450000H-57FFFH0A0000H-0AFFFFH BA901001X X X32/6448000H-4FFFFH090000H-09FFFFH BA801000X X X32/6440000H-47FFFH080000H-08FFFFH BA700111X X X32/6438000H-3FFFFH070000H-07FFFFH BA600110X X X32/6430000H-37FFFH060000H-06FFFFH BA500101X X X32/6428000H-2FFFFH050000H-05FFFFH BA400100X X X32/6420000H-27FFFH040000H-04FFFFH BA300011X X X32/6418000H-1FFFFH030000H-03FFFFH BA200010X X X32/6410000H-17FFFH020000H-02FFFFH BA100001X X X32/6408000H-0FFFFH010000H-01FFFFH BA000000X X X32/6400000H-07FFFH000000H-00FFFFHDeviceBlock AddressA19-A12BlockSize(X8)Address Range(X16)Address RangeK8D1716UT11111xxx64/321F0000H-1FFFFFH F8000H-FFFFFHTable 4. Secode Block Addresses for Top Boot DevicesFLASH MEMORY K8D1716UTC / K8D1716UBCTable 5. Bottom Boot Block Address(K8D1716UB)K8D1716UT Block A19A18A17A16A15A14A13A12 Block Size(KW/KB)Address RangeWord Mode Byte ModeBank2BA3811111X X X32/64F8000H-FFFFFH1F0000H-1FFFFFH BA3711110X X X32/64F0000H-F7FFFH1E0000H-1EFFFFH BA3611101X X X32/64E8000H-EFFFFH1D0000H-1DFFFFH BA3511100X X X32/64E0000H-E7FFFH1C0000H-1CFFFFH BA3411011X X X32/64D8000H-DFFFFH1B0000H-1BFFFFH BA3311010X X X32/64D0000H-D7FFFH1A0000H-1AFFFFH BA3211001X X X32/64C8000H-CFFFFH190000H-19FFFFH BA3111000X X X32/64C0000H-C7FFFH180000H-18FFFFH BA3010111X X X32/64B8000H-BFFFFH170000H-17FFFFH BA2910110X X X32/64B0000H-B7FFFH160000H-16FFFFH BA2810101X X X32/64A8000H-AFFFFH150000H-15FFFFH BA2710100X X X32/64A0000H-A7FFFH140000H-14FFFFH BA2610011X X X32/6498000H-9FFFFH130000H-13FFFFH BA2510010X X X32/6490000H-97FFFH120000H-12FFFFH BA2410001X X X32/6488000H-8FFFFH110000H-11FFFFH BA2310000X X X32/6480000H-87FFFH100000H-10FFFFHBank1BA2201111X X X32/6478000H-7FFFFH0F0000H-0FFFFFH BA2101110X X X32/6470000H-77FFFH0E0000H-0EFFFFH BA2001101X X X32/6468000H-6FFFFH0D0000H-0DFFFFH BA1901100X X X32/6460000H-67FFFH0C0000H-0CFFFFH BA1801011X X X32/6458000H-5FFFFH0B0000H-0BFFFFH BA1701010X X X32/6450000H-57FFFH0A0000H-0AFFFFH BA1601001X X X32/6448000H-4FFFFH090000H-09FFFFH BA1501000X X X32/6440000H-47FFFH080000H-08FFFFH BA1400111X X X32/6438000H-3FFFFH070000H-07FFFFH BA1300110X X X32/6430000H-37FFFH060000H-06FFFFH BA1200101X X X32/6428000H-2FFFFH050000H-05FFFFH BA1100100X X X32/6420000H-27FFFH040000H-04FFFFH BA1000011X X X32/6418000H-1FFFFH030000H-03FFFFH BA900010X X X32/6410000H-17FFFH020000H-02FFFFH BA800001X X X32/6408000H-0FFFFH010000H-01FFFFH BA7000001114/807000H-07FFFH00E000H-00FFFFH BA6000001104/806000H-06FFFH00C000H-00DFFFH BA5000001014/805000H-05FFFH00A000H-00BFFFH BA4000001004/804000H-04FFFH008000H-009FFFH BA3000000114/803000H-03FFFH006000H-007FFFH BA2000000104/802000H-02FFFH004000H-005FFFH BA1000000014/801000H-01FFFH002000H-003FFFH BA0000000004/800000H-00FFFH000000H-001FFFHDeviceBlock AddressA19-A12BlockSize(X8)Address Range(X16)Address Range K8D1716UB00000xxx64/32000000H-00FFFFH00000H-07FFFHTable 6. Secode Block Addresses for Bottom Boot DevicesFLASH MEMORYK8D1716UTC / K8D1716UBCPRODUCT INTRODUCTIONTable 7. Operations TableOperation CEOE WE BYTE WP/ACC A9A6A1A0DQ15/A-1DQ8/DQ14DQ0/DQ7RESET Read word L L H H L/H A9A6A1A0DQ15D OUT D OUT H byteL L H L A9A6A1A0A-1High-Z D OUT H Stand-by Vcc ±0.3V X X X (2)X X X X High-Z High-Z High-Z (2)Output Disable L H H X L/H X X X X High-Z High-Z High-Z H Reset X X X X L/H X X X X High-Z High-Z High-Z L Writeword L H L H (4)A9A6A1A0D IN D IN D IN H byteL H L L A9A6A1A0A-1High-Z D IN H Enable Block Group Protect (3)L H L X L/H X L H L X X D IN V ID Enable Block Group Unprotect (3)L H L X (4)X H H L X X D IN V ID Temporary Block GroupX X X X (4)X X X X X X X V ID Auto SelectManufacturer ID (5)L L H X L/H V ID L L L X X Code (SeeTable 9)H Auto SelectDevice Code (5)LLHXL/HV IDLLHXXCode (SeeTable 9)HNotes :1. L = V IL (Low), H = V IH (High), V ID = 8.5V~12.5V, D IN = Data in, D OUT = Data out, X = Don't care. 2. WP/ACC and RESET pin are asserted at Vcc ±0.3 V or Vss ±0.3 V in the Stand-by mode.3. Addresses must be composed of the Block address (A12 - A19).The Block Protect and Unprotect operations may be implemented via programming equipment too. Refer to the "Block Group Protection and Unprotection".4. If WP/ACC =V IL, the two outermost boot blocks is protected. If WP/ACC =V IH, the two outermost boot block protection depends on whether those blocks were last protected or unprotected using the method described in "Block Group Protection and Unprotection". If WP/ACC =V HH , all blocks will be temporarily unprotected.5. Manufacturer and device codes may also be accessed via a command register write sequence. Refer to Table 9.The K8D1716U is a 16Mbit (16,777,216 bits) NOR-type Flash memory. The device features single voltage power supply operating within the range of 2.7V to 3.6V. The device is programmed by using the Channel Hot Electron (CHE) injection mechanism which is used to program EPROMs. The device is erased electrically by using Fowler-Nordheim tunneling mechanism. To provide highly flex-ible erase and program capability, the device adapts a block memory architecture that divides its memory array into 39 blocks (64-Kbyte x 31 , 8-Kbyte x 8). Programming is done in units of 8 bits (Byte) or 16 bits (Word). All bits of data in one or multiple blocks can be erased simultaneously when the device executes the erase operation. To prevent the device from accidental erasing or over-writ-ing the programmed data, 39 memory blocks can be hardware protected by the block group. Byte/Word modes are available for read operation. These modes can be selected via BYTE pin. The device provides read access times of 70ns, 80ns and 90ns supporting high speed microprocessors to operate without any wait states.The command set of K8D1716U is fully compatible with standard Flash devices. The device is controlled by chip enable (CE), output enable (OE) and write enable (WE). Device operations are executed by selective command codes. The command codes to be com-bined wih addresses and data are sequentially written to the command registers using microprocessor write timing. The command codes serve as inputs to an internal state machine which controls the program/erase circuitry. Register contents also internally latch addresses and data necessary to execute the program and erase operations. The K8D1716U is implemented with Internal Program/Erase Algorithms to execute the program/erase operations. The Internal Program/Erase Algorithms are invoked by program/erase command sequences. The Internal Program Algorithm automatically programs and verifies data at specified addresses. The Internal Erase Algorithm automatically pre-programs the memory cell which is not programmed and then executes the erase operation. The K8D1716U has means to indicate the status of completion of program/erase operations. The status can be indicated via the RY/BY pin, Data polling of DQ7, or the Toggle bit (DQ6). Once the operations have been completed, the device automatically resets itself to the read mode. The device requires only 14 mA as active read current and 15 mA for program/erase operations.FLASH MEMORY K8D1716UTC / K8D1716UBCCOMMAND DEFINITIONSThe K8D1716U operates by selecting and executing its operational modes. Each operational mode has its own command set. In order to select a certain mode, a proper command with specific address and data sequences must be written into the command reg-ister. Writing incorrect information which include address and data or writing an improper command will reset the device to the read mode. The defined valid register command sequences are stated in Table 8. Note that Erase Suspend (B0H) and Erase Resume (30H) commands are valid only while the Block Erase Operation is in progress.Table 8. Command SequencesCommand Sequence Cycle1st Cycle2nd Cycle3rd Cycle4th Cycle5th Cycle6th Cycle Word Byte Word Byte Word Byte Word Byte Word Byte Word ByteRead Addr1RA Data RDReset Addr1XXXH Data F0HAutoselect Manufacturer ID (2,3) Addr4555H AAAH2AAH555HDA/555HDA/AAAHDA/X00HDA/X00H Data AAH 55H90H ECHAutoselect Device Code (2,3) Addr4555H AAAH2AAH555HDA/555HDA/AAAHDA/X01HDA/X02HData AAH 55H90H(SeeTable9)Autoselect Block Group Protect Verify (2,3) Addr4555H AAAH2AAH555HDA/555HDA/AAAHBA /X02HBA/X04H Data AAH 55H90H(See Table 9)Auto Select Secode Block Factory Protect Verify (2,3) Addr4555H AAAH2AAH555HDA/555HDA/AAAHDA /X03HDA/X06H Data AAH 55H90H(See Table 9)Enter Secode Block Region Addr3555H AAAH2AAH555H 555H AAAH Data AAH 55H88HExit Secode Block Region Addr4555H AAAH2AAH555H 555H AAAH XXXH Data AAH 55H90H00HProgram Addr4555H AAAH2AAH555H 555H AAAH PA Data AAH55H A0H PDUnlock Bypass Addr3555H AAAH2AAH555H 555H AAAH Data AAH55H20HUnlock Bypass Program Addr2XXXH PA Data A0H PDUnlock Bypass Reset Addr2XXXH XXXH Data90H00HChip Erase Addr6555H AAAH2AAH555H 555H AAAH 555H AAAH 2AAH555H555H AAAH Data AAH55H80H AAH55H10HBlock Erase Addr6555H AAAH2AAH555H 555H AAAH 555H AAAH 2AAH555H BA Data AAH55H80H AAH55H30HBlock Erase Suspend (4, 5)Addr1XXXH Data B0HBlock Erase Resume Addr1XXXH Data30HCFI Query (6)Addr155H AAH Data98HFLASH MEMORY K8D1716UTC / K8D1716UBCNotes : 1. RA : Read Address, PA : Program Address, RD : Read Data, PD : Program DataDA : Dual Bank Address, BA : Block Address (A12 - A19), X = Don’t care .2. To terminate the Autoselect Mode, it is necessary to write Reset command to the register.3. The 4th cycle data of Autoselect mode is output data.The 3rd and 4th cycle bank addresses of Autoselect mode must be same.4. The Read / Program operations at non-erasing blocks and the autoselect mode are allowed in the Erase Suspend mode.5. The Erase Suspend command is applicable only to the Block Erase operation.6. Command is valid when the device is in read mode or Autoselect mode.7. DQ8 - DQ15 are don’t care in command sequence, but RD and PD is excluded.8. A11 - A19 are also don’t care, except for the case of special notice.Description CE OE WE A19toA12A11toA10A9A8toA7A6A5toA2A1A0DQ8 to DQ15DQ7toDQ0BYTE=V IHBYTE=V ILManufacturer ID L L H DA X V ID X L X L L X X ECH Device Code K8D1716UT(Top Boot Block)L L H DA X V ID X L X L H22H X75HDevice Code K8D1716UB(Bottom Boot Block)L L H DA X V ID X L X L H22H X77HBlock Protection Verification L L H BA X V ID X L X H L X X01H (Protected),00H (Unprotected)Secode Block (2) Indicator Bit (DQ7)L L H DA X V ID X L X H H X X80H (Factory locked),00H (Not factory locked)Table 9. K8D1716U Autoselect Codes, (High Voltage Method)Notes : 1. L=Logic Low=V IL, H=Logic High=V IH, DA=Dual Bank Address, BA=Block Address, X=Don’t care.2. Secode Block : Security Code Block.FLASH MEMORYK8D1716UTC / K8D1716UBCDEVICE OPERATION Byte/Word ModeIf the BYTE pin is set at logical "1" , the device is in word mode, DQ0-DQ15 are active. Otherwise the BYTE pin is set at logical "0" ,the device is in byte mode, DQ0-DQ7 are active. DQ8-DQ14 are in the High-Z state and DQ15 pin is used as an input for the LSB (A-1) address pin.Read ModeThe K8D1716U is controlled by Chip Enable (CE), Output Enable (OE) and Write Enable (WE). When CE and OE are low and WE is high, the data stored at the specified address location,will be the output of the device. The outputs are in high impedance state whenever CE or OE is high.Standby ModeThe K8D1716U features Stand-by Mode to reduce power consumption. This mode puts the device on hold when the device is dese-lected by making CE high (CE = V IH ). Refer to the DC characteristics for more details on stand-by modes.Output DisableThe device outputs are disabled when OE is High (OE = V IH ). The output pins are in high impedance state.Automatic Sleep ModeK8D1716U features Automatic Sleep Mode to minimize the device power consumption. Since the device typically draws 5µA of the current in Automatic Sleep Mode, this feature plays an extremely important role in battery-powered applications. When addresses remain steady for t AA +50ns, the device automatically activates the Automatic Sleep Mode. In the sleep mode, output data is latched and always available to the system. When addresses are changed, the device provides new data without wait time.Data Outputst AA + 50nsDataAuto Sleep ModeAddressData Data Data DataFigure 1. Auto Sleep Mode OperationAutoselect ModeThe K8D1716U offers the Autoselect Mode to identify manufacturer and device type by reading a binary code. The Autoselect Mode allows programming equipment to automatically match the device to be programmed with its corresponding programming algorithm.In addition, this mode allows the verification of the status of write protected blocks. This mode is used by two method. The one is high voltage method to be required V ID (8.5V~12.5V) on address pin A9. When A9 is held at V ID and the bank address or block address is asserted, the device outputs the valid data via DQ pins(see Table 9 and Figure 2). The rest of addresses except A0, A1 and A6 are Don ′t Care. The other is autoselect command method that the autoselect code is accessible by the commamd sequence without V ID.The manufacturer and device code may also be read via the command register. The Command Sequence is shown in Table 8 and Figure 3. The autoselect operation of block protect verification is initiated by first writing two unlock cycle. The third cycle must con-tain the bank address and autoselect command (90H). If Block address while (A6, A1, A0) = (0,1,0) is finally asserted on the address pin, it will produce a logical "1" at the device output DQ0 to indicate a write protected block or a logical "0" at the device output DQ0to indicate a write unprotected block. To terminate the autoselect operation, write Reset command (F0H) into the command register.FLASH MEMORYK8D1716UTC / K8D1716UBCFigure 3. Autoselect Operation ( by command sequence method )WE555H/AAAH 2AAH/555H 555H/AAAH AAH 55H 90H 00H/01H/ECHManufacturerCode Device Code A19∼A0(x16)/*DQ15∼DQ0F0HReturn to Read ModeWrite (Program/Erase) ModeThe K8D1716U executes its program/erase operations by writing commands into the command register. In order to write the com-mands to the register, CE and WE must be low and OE must be high. Addresses are latched on the falling edge of CE or WE (which-ever occurs last) and the data are latched on the rising edge of CE or WE (whichever occurs first). The device uses standard microprocessor write timing.ProgramThe K8D1716U can be programmed in units of a word or a byte. Programming is writing 0's into the memory array by executing the Internal Program Routine. In order to perform the Internal Program Routine, a four-cycle command sequence is necessary. The first two cycles are unlock cycles. The third cycle is assigned for the program setup command. In the last cycle, the address of the mem-ory location and the data to be programmed at that location are written. The device automatically generates adequate program pulses and verifies the programmed cell margin by the Internal Program Routine. During the execution of the Routine, the system is not required to provide further controls or timings.During the Internal Program Routine, commands written to the device will be ignored. Note that a hardware reset during a program operation will cause data corruption at the corresponding location.Figure 4. Program Command SequenceWE555H/AAAH2AAH/555H555H/AAAHAAH55HA0HProgram Program Program StartDQ15-DQ0AddressDataRY/BYA9V ID00H01HECH2275H or 2277H Manufacturer CodeDevice Code A6,A1,A0*DQ15-DQ0Figure 2. Autoselect Operation ( by high voltage method )Return to Read ModeV = V IH or V IL2275H or 2277H Note : The addresses other than A0 , A1 and A6 are Don ′t care. Please refer to Table 9 for device code.Note : The 3rd Cycle and 4th Cycle address must include the same bank address. Please refer to Table 9 for device code.(K8D1716U )(K8D1716U)A19∼A-1(x8)A19∼A0(x16)/A19∼A-1(x8)00H 02HFLASH MEMORYK8D1716UTC / K8D1716UBCUnlock BypassThe K8D1716U provides the unlock bypass mode to save its program time for program operation. The mode is invoked by the unlock bypass command sequence. Then, the unlock bypass program command sequence is required to program the device.Unlike the standard program command sequence that contains four bus cycles, the unlock bypass program command sequence comprises only two bus cycles.The unlock bypass mode is engaged by issuing the unlock bypass command sequence which is comprised of three bus cycles. Writ-ing first two unlock cycles is followed by a third cycle containing the unlock bypass command (20H). Once the device is in the unlock bypass mode, the unlock bypass program command sequence is necessary to program in this mode. The unlock bypass program command sequence is comprised of only two bus cycles; writing the unlock bypass program command (A0H) is followed by the pro-gram address and data. This command sequence is the only valid one for programming the device in the unlock bypass mode.The unlock bypass reset command sequence is the only valid command sequence to exit the unlock bypass mode. The unlock bypass reset command sequence consists of two bus cycles. The first cycle must contain the data (90H). The second cycle contains only the data (00H). Then, the device returns to the read mode.Chip EraseTo erase a chip is to write 1′s into the entire memory array by executing the Internal Erase Routine. The Chip Erase requires six bus cycles to write the command sequence. The erase set-up command is written after first two "unlock" cycles. Then, there are two more write cycles prior to writing the chip erase command. The Internal Erase Routine automatically pre-programs and verifies the entire memory for an all zero data pattern prior to erasing. The automatic erase begins on the rising edge of the last WE or CE pulse in the command sequence and terminates when DQ7 is "1". After that the device returns to the read mode.Figure 5. Chip Erase Command SequenceWE555H/AAAH2AAH/555H555H/AAAHAAH55H80H555H Chip Erase StartDQ15-DQ0AAAH2AAH/555HAAH55H10HRY/BY555H/AAAHA19∼A0(x16)/A19∼A-1(x8)Block EraseTo erase a block is to write 1′s into the desired memory block by executing the Internal Erase Routine. The Block Erase requires six bus cycles to write the command sequence shown in Table 8. After the first two "unlock" cycles, the erase setup command (80H) is written at the third cycle. Then there are two more "unlock" cycles followed by the Block Erase command. The Internal Erase Routine automatically pre-programs and verifies the entire memory prior to erasing it. The block address is latched on the falling edge of WE or CE, while the Block Erase command is latched on the rising edge of WE or CE.Multiple blocks can be erased sequentially by writing the six bus-cycle operation in Figure 6. Upon completion of the last cycle for the Block Erase, additional block address and the Block Erase command (30H) can be written to perform the Multi-Block Erase. An 50µs (typical) "time window" is required between the Block Erase command writes. The Block Erase command must be written within the 50µs "time window", otherwise the Block Erase command will be ignored. The 50µs "time window" is reset when the falling edge of the WE occurs within the 50µs of "time window" to latch the Block Erase command. During the 50µs of "time window", any command other than the Block Erase or the Erase Suspend command written to the device will reset the device to read mode. After the 50µs of "time window", the Block Erase command will initiate the Internal Erase Routine to erase the selected blocks. Any Block Erase address and command following the exceeded "time window" may or may not be accepted. No other commands will be recognized except the Erase Suspend command during Block Erase operation.。