VHDL做PWM发生器的大作业

VHDL语言设计信号发生器实验报告

实验四用VHDL设计多功能信号发生器一、设计任务基于《VHDL语言》,通过给定的仪器(EDA6000试验箱)设计一个多功能信号发生器,要求:(1)能产生周期性正弦波、方波、三角波、锯齿波以及用户自己编辑的特定波形(选作);(2)输出信号的频率范围为100Hz~200KHz,且输出频率可以调节;(3)具有显示输出波形、频率的功能。

(选作)二、系统顶层框图弦波的数字幅度信息,每个查找表的地址对应正(余)弦波幅度信号,同时输出到数模转换器(DAC)输入端,DAC输出的模拟信号经过低通滤波器(LPF),可以得到一个频谱纯净的正(余)弦波。

二、设计步骤用VHDL语言结合原理图设计实现一个函数信号发生器,输出正弦波、方波和三角波三种波形。

将频率控制、分频、三角波、正弦波、方波发生邓各个模块分别用VHDL语言编程为一个子程序,并把每一个模块转换成图形文件,然后在原理图编辑框调用这些图形模块,连接电路如上图系统顶层框图所示。

通过按键1到按键8控制频率调节f〔7...0〕,用按键6、按键7、按键8控制dlt 、sin 、sqr 波形选通,最后把八位输出接DAC0832通过D/A 转换,从示波器上就能看到波形输出。

按下不同的按键输出不同的波形及频率。

三、系统设计(1)数控分频器模块在时钟的作用下,通过预置分频数DIN ,来改变输出频率。

假如分频系数为N ,波形存储模块存储一个周期的波形,实验里按照一个周期波形采样64个点存储在波形存储模块里。

则输出频率N f f clkout .64=(2).数据存储模块 (存储波形数据)数据存储模块主要存的是正弦波、三角波、锯齿波等一个周期的采样点。

三角波模块可设计一个可逆计数器实现,设计时设置一变量作为工作状态标志,在此变量为0时,当检测到时钟的上升沿进行加同一个数操作;为1时,进行减同一个数操作。

DA 转换采用的DA0832,输入有8个数据端,范围是0到255;而且设置64个时钟周期为一个三角波周期,所有每次加、减为8.锯齿波的存储数据与三角波类似。

VHDL多路波形发生器实验报告

VHDL多路波形发生器实验报告一、基本要求:1、对输入时钟信号进行分频,实现三路互差120°的信号。

2、实现输出信号的占空比控制clk: 输入时钟信号reset: 同步复位信号(低电平有效)div: 输入分频控制信号(注意:6n分频)ctrl: 占空比控制信号ctrl=1时, 占空比为1:1ctrl=2时, 占空比为1:2ctrl=3时, 占空比为2:1A,B,C: 三路输出信号二、设计思路:1.实验为6n分频,用变量s来控制,0~6n-1这六个数,当时钟信号每来一个上升沿时加1,当为6n-1时清零;2.定义N为常量,通过改变N的值改变分频;3.ctrl值不同时,占空比不同,用case语句控制,ctrl分别为01,10,11和其他;4.具体波形的实现用if语句,当占空比为1时,A输出信号在s=0和s=3*n时翻转,B输出信号在s=2*n和s=5*n时翻转,C输出信号在s=4*n和s=n的时候翻转。

当占空比为1:2时,A输出信号在s=0和s=2*n时翻转,B输出信号在s=2*n和s=4*n时翻转,C输出信号在s=4*n和s=0的时候翻转。

当占空比为2:1时,A输出信号在s=0和s=4*n时翻转,B输出信号在s=2*n和s=0时翻转,C输出信号在s=4*n和s=2*n的时候翻转;5.在占空比为1和1:2时,C输出信号应比B慢120度,但是实际输出超前B,所以要对C输出进行反相;同理,在占空比为2:1时,要对B、C分别进行反向。

6.用if语句判断是否复位,若非,则执行case语句。

三、流程图:四、源程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity top isport(clk,reset:in std_logic;ctrl:in std_logic_vector(1 downto 0);A,B,C:out std_logic);end top ;architecture rel of top issignal temp1,temp2,temp3,temp4,temp5 : std_logic; constant N: integer:=1;signal s:integer range 0 to 6*N-1 ;beginprocess(clk,reset,ctrl)beginif (reset='0') thentemp1<='0';temp2<='0';temp3<='0';temp4<='0';temp5<='0';s<=0;elsecase ctrl iswhen "01"=>if (clk 'event and clk='1') thenif s=6*N-1 thens<=0;elses <= s+1;end if;if s=0 thentemp1<= not temp1;end if;if s=3*N thentemp1<= not temp1;end if;if s=2*N thentemp2<= not temp2;end if;if s=5*N thentemp2<= not temp2;end if;if s=4*N thentemp4<= not temp4;end if;if s=N thentemp4<= not temp4;end if;end if;temp3<= not temp4;when "10"=>if (clk 'event and clk='1') thenif s=6*N-1 thens<=0;elses <= s+1;end if;if s=0 thentemp1<= not temp1;end if;if s=2*N thentemp1<= not temp1;end if;if s=2*N thentemp2<= not temp2;end if;if s=4*N thentemp2<= not temp2;end if;if s=4*N thentemp4<= not temp4;end if;if s=0 thentemp4<= not temp4;end if;end if;temp3<= not temp4;when "11"=>if (clk 'event and clk='1') thenif s=6*N-1 thens<=0;elses <= s+1;end if;if s=0 thentemp1<= not temp1;end if;if s=4*N thentemp1<= not temp1;end if;if s=2*N thentemp5<= not temp5;end if;if s=0 thentemp5<= not temp5;end if;if s=4*N thentemp4<= not temp4;end if;if s=2*N thentemp4<= not temp4;end if;end if;temp2<= not temp5;temp3<= not temp4;when others=>temp1<='0';temp2<='0';temp3<='0';end case;end if;end process;A<=temp1;B<=temp2;C<=temp3;end rel;五、仿真波形:整体波形:当ctrl=1 当ctrl=2 当ctrl=3复位当ctrl=其他:六、实验过程遇到的问题:在程序设计时,开始不知该怎样使A,B,C互差120度,开始是想通过定义一个变量,每来一个上升沿加1,从0开始,A路信号除3n 取余为0则翻转,B路信号除3n取余为1则翻转,C路信号除3n取余为2则翻转,我觉得这样的想法应该没有错,可是实际却调不出来,可能是某处逻辑有问题,后来就模仿老师给的6分频程序,设计了现在的程序。

VHDL课程设计_函数信号发生器

学生:学号:专业:年级班级:课程名称: 可编程数字系统设计实验项目: VHDL设计一信号发生器试验时间: 2014年5月24日指导老师:一、实验目的:熟悉EDA工具,掌握用VHDL语言进行数字系统设计的基本方法和流程,提高工程实践能力二、设计任务设计信号发生器,用VHDL语言描述,用QuartusII工具编译和综合,并在实验板上调试并实现所要求功能和技术指标,撰写实验报告,最后提交验收并答辩。

题目一:设计正弦波发生器题目二:设计锯齿波发生器题目三:设计三角波发生器三、功能要求与技术指标基本功能:(1 )模拟输出:由于FPGA上无D/A转换模块,因此设计中必须包含PWM发生模块,PWM输出后经过RC低通波电路转换为电压幅值正比于占空比的模拟电压。

滤波电路需自行设计。

(2)可以通过按键设定波形的频率,频率可以显示在数码管上。

(3)按钮开关输入须消抖处理。

在完成以上功能的前提下,可增加其它一些实用的功能。

要求:1、每个同学必须完成基本功能,在完成基本功能的前提下可自由发挥。

2、实验报告主要容包含:设计原理、系统分析、程序设计、仿真/实验结果(例如波形图和实验板运行时的照片)、结论或分析、使用说明等,在最后附上主要源程序。

3、程序代码结构清晰,可读性强,关键语句应注释。

四、设计原理:原理图:原理图(PS:RESTA按键已被删除)频器将FPGA上的晶振进行分频所得的时钟信号作为计数时钟。

最后进行利用比较的方式得到占空比可调的脉冲波。

同时,分频器的分频系数可由键盘和数码管配合的显示数值进行运算反馈回PWM模块,达到频率可调的目的。

此外,另设一输出接至LED2,无法测量波形的情况下,利用呼吸灯的效果可检测PWM模块的完成与频率可调的成功性。

2、键盘设移位复位键,数码管计数键与频率传送键。

同时设立消抖计数值,当按键按下以后进行计数,在按键退出后,停止计数,取最后一次计数作为按键信号完成按键消抖。

按下移位复位键,数码管位选下一位,同时示数复位清零,并且循环移位,当按完4次按键后,数码管全部清零。

基于VHDL语言的波形发生器的设计

基于VHDL语言的波形发生器的设计基于VHDL语言的波形发生器的设计利用FPGA芯片信号发生器的设计。

当按下开关1时产生三角波,当按下开关2时产生正弦波,当按下开关3时产生方波。

本次设计采用xilinx公司的ISE设计工具,在zedboard开发板中的xc7z020芯片上用VHDL来实现,并且利用ISE自带的chipscop完成对FPGA内部的信号的读取。

这样的设计具有体积小,修改升级容易等特点。

本设计采用自顶向下、纯文本实现数字时钟的设计、下载和调试。

1 设计原理本设计由信号产生,信号选择,信号控制输出三大模块组合而成。

其中信号产生模块有:三角波模块、方波模块、正弦波模块。

本设计采用K0~K2这三个按键为信号选择开关,选择信号产生模块输出的信号。

(顶层设计的例化语句见附录一)其RTL 图1-1:RTL图1-12主要功能模块u1:square方波产生模块;u2:sin正弦波产生模块;u3:delta三角波产生模块;u4:sig_control数据选择器模块;u5,u6:为使用chipscope所需生成的IP核。

2.1 u1方波产生模块(程序见附录二)产生方波,初始化为幅值225的高电平,每有一次时钟上升沿触发产生一次计数,当计数值达到128时跳到为0的低电平。

利用循环语句不断的产生高低电平的方波输出。

原理如图2-1:方波模块RTL 图2-12.2 u1正弦波产生模块(程序见附录三)功能是产生正弦波,产用信号抽样的原理,在一个正弦信号中等间隔的抽样64点,此64点的幅值作为一个正弦波数据表,每有一次时钟上升沿触发便赋予输出端q一个点的数据,依次赋值64个点的数据便完成一个周期的正弦波的输出。

并利用循环语句不断的产生正弦波的输出。

原理如图2-2:正弦波模块RTL 图2-22.3 u1三角波产生模块(程序见附录四)功能是产生三角波,初始化为幅值为0,每有一次时钟上升沿触发便进行幅值加1,当幅值达到最大255时,每有一次时钟上升沿触发便进行幅值减1,当幅值减为0时完成一个周期的输出。

SVPWM信号发生器的VHDL实现

SVPWM信号发生器的VHDL实现

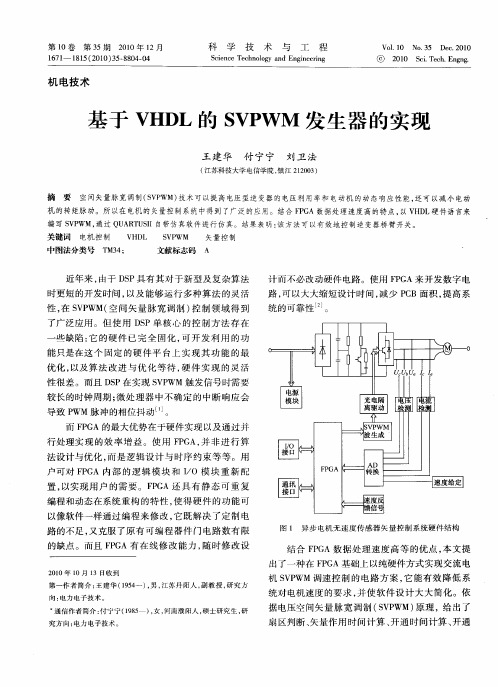

近年来,DSP 在SVPWM(空间矢量脉宽调制)控制领域得到了广泛应用。

但是使用DSP 单核心的控制方法仍然存在一些缺陷:基于软件的:DSP 在实现SVPWM 触发信号时需要较长的时钟周期;微处理器中不确定的中断响应会导致PWM 脉冲的相位抖动。

针对以上问题,本文提出了一种利用FPGA 实现的SVPWM 信号发生器,系统结构如SVPWM 简介

SVPWM 的主要思想在于利用逆变器空间电压矢量的切换合成参考电压

矢量。

具体方法如下:在桥式电路中,同一桥臂上两个开关的工作状态在任意

时刻都是互补的,所以可以用二值逻辑函数表示6 个开关的工作状态:

由式1 可见,3 组开关的工作状态共有23=8 种,不同的开关工作状态对应着不同的三相输出电压。

这8 种工作状态分别对应着8 条基本空间电压矢量,任意区域内的空间电压参考矢量都可以由2 条非零矢量以及2 条零矢量合成。

在进行电压矢量合成时,规定每一次开关动作只能有一相桥臂的工作状态发生

转换,目的是为了降低电路中的谐波含量,确定基本电压矢量的切换顺序。

SVPWM 信号发生器的设计

基本原理

在状态机的一个工作周期内,输入时间信号的突变会使状态机的工作状

态发生不规则跳变,对输出信号造成巨大影响,无法得到所需要的SVPWM 触发信号。

因此,利用有限状态机的方法设计FPGA,只须控制三相桥臂开关状

态的保持时间,就可以实现SVPWM 触发信号。

设计方法

本设计采用自顶向下、层次化、模块化的设计思想。

实验三:PWM信号发生器

实验三:PWM信号发生器1.实验目的(1)学习Quartus II 8.0 软件的基本使用方法。

(2)学习GW48-CK EDA实验开发系统的基本使用方法。

(3)学习VHDL程序中数据对象,数据类型,顺序语句和并行语句的综合使用。

2.实验内容设计并调试好一个脉宽数控调制信号发生器,此信号发生器是由两个完全相同的可自加载加法计数器LCNT8组成的,它的信号的高低电平脉宽可分别由两组8位预置数进行控制。

3.实验条件(1)开发软件:Quartus II 8.0。

(2)实验设备:GW48-CK EDA实验开发系统。

(3)拟用芯片:EPM7128S-PL84。

4.实验要求(1)画出系统原理框图,说明系统中各主要组成部分的功能。

(2)编写各个VHDL源程序。

(3)根据系统功能,选好测试用例,画出测试输入信号波形或编好测试文件。

(4)根据选用的EDA实验开发装置编好用于硬件验证的管脚锁定表格或文件。

(5)记录系统仿真、逻辑综合及硬件验证结果。

(6)记录实验过程中出现的问题及解决办法。

5.实验过程(1)PWM即脉冲宽度调制,就是利用微处理器的数字输出来对模拟电路进行控制的一种非常有效的技术。

PWM从处理器到被控制系统信号都是数字式的,无需进行数/模转换。

让信号保持为数字形式可将噪声影响降到最小,因此广泛应用在测量、通信和功率控制与变换的许多领域中。

下图是一种PWM信号发生器的逻辑图,此信号发生器是由两个完全相同的可自加载加法计数器LCNT8组成的,它的输出信号的高、低电平脉宽可分别由两组8位预置数进行控制。

如果将初始值可预置的加法计数器的溢出信号作为本计数器的初始预置值加载信号LD,则可构成计数器初始值自加载方式的加法计数器,从而构成数控分频器。

图中D 触发器的一个重要功能就是均匀输出信号的占空比,提高驱动能力,这对驱动,诸如扬声器或电动机十分重要。

(2)VHDL源程序①8位可自加载加法计数器的源程序LCNT8.VHD--LCNT8.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY LCNT8 ISPORT(CLK,LD:IN STD_LOGIC;D:IN INTEGER RANGE 0 TO 255;CAO:OUT STD_LOGIC);END ENTITY LCNT8;ARCHITECTURE ART OF LCNT8 ISSIGNAL COUNT:INTEGER RANGE 0 TO 255;BEGINPROCESS(CLK)ISBEGINIF CLK'EVENT AND CLK='1'THENIF LD='1'THEN COUNT<=D;ELSE COUNT<=COUNT+1;END IF;END IF;END PROCESS;PROCESS(COUNT)ISBEGINIF COUNT=255 THEN CAO<='1';ELSE CAO<='0';END IF;END PROCESS;END ARCHITECTURE ART;②PWM信号发生器的源程序PWM.VHD--PWM.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY PWM ISPORT(CLK:IN STD_LOGIC;A,B:IN STD_LOGIC_VECTOR(7 DOWNTO 0);PWM:OUT STD_LOGIC);END ENTITY PWM;ARCHITECTURE ART OF PWM ISCOMPONENT LCNT8 ISPORT(CLK,LD:IN STD_LOGIC;D:IN STD_LOGIC_VECTOR(7 DOWNTO 0);CAO:OUT STD_LOGIC);END COMPONENT LCNT8;SIGNAL CAO1,CAO2:STD_LOGIC;SIGNAL LD1,LD2:STD_LOGIC;SIGNAL SPWM:STD_LOGIC;BEGINU1:LCNT8 PORT MAP(CLK=>CLK,LD=>LD1,D=>A,CAO=>CAO1);U2:LCNT8 PORT MAP(CLK=>CLK,LD=>LD2,D=>B,CAO=>CAO2);PROCESS(CAO1,CAO2)ISBEGINIF CAO1='1'THEN SPWM<='0';ELSIF CAO2'EVENT AND CAO2='1'THEN SPWM<='1';END IF;END PROCESS;LD1<=NOT SPWM;LD2<=SPWM;PWM<=SPWM;END ARCHITECTURE ART;(3)仿真结果验证PWM.VHD的时序仿真结果(4)逻辑综合结果6.实验总结经过本次实验,我学会了Quartus II 8.0 开发系统的基本操作,并对它有了一定的了解和认识。

基于vhdlpwm信号发生器的设计说明书

Yi bin UniversityEDA技术及应用课程设计报告题目基于VHDL的PWM信号发生器系别物理与电子工程学院专业电子信息科学与技术学生XX学号班级2013 年 12月 21日摘要本次课程设计是基于VHDL的PWM信号发生器,PWM信号发生器应用所学的数字电路和模拟电路的知识进行设计。

在设计过程中,所有电路仿真均基于Quartus II 9.1仿真软件。

本课程设计介绍了PWM 信号发生器的设计方案及其基本原理,并着重介绍了PWM信号发生器各单元电路的设计思路,原理及仿真,整体电路的的工作原理,控制器件的工作情况。

设计共有三大组成部分:一是原理电路的设计,本部分详细讲解了电路的理论实现,是关键部分;二是性能测试,这部分用于测试设计是否符合任务要求。

三是是对本次课程设计的总结。

关键词: PWM信号发生器仿真设计目录第1章绪论1.1 EDA 和QuartusⅡ的简介及起源 (1)1.2 EDA的优势及发展趋势 (1)第2章系统设计思路 (3)第3章可自加载加法计数器的设计 (4)第4章信号发生器设计过程 (6)第5章软件仿真5.1 QuartusⅡ软件简介 (8)5.2 用QuartusⅡ的仿真步骤和图像 (9)5.3 逻辑综合结果 (12)第6章设计总结 (13)第7章参考文献 (15)附录设计程序 (16)第1章绪论1.1 EDA和QuartusⅡ的简介及起源EDA是英文“electronic design automation”(电子自动化设计)的缩写,EDA技术是20世纪90年代迅速发展起来的,是现代电子设计的最新技术潮流,是综合现代电子技术和计算机技术的最新研究成果,是电子线路设计与分析的一门技术。

EDA包括电子线路的设计、计算机模拟仿真和电路分析及印制电路板的自动化设计三个方面的内容。

随着可编程逻辑器件迅速发展,出现了功能强大的全新的EDA工具。

具有较强描述能力的硬件描述语言(VHDL、Verilog、HDL)及高性能综合工具的使用,使过去单功能电子产品开发转向系统级电子产品开发。

实验2—占空比可调的PWM信号发生器

实验2—占空比可调的PWM信号发生器第一篇:实验2—占空比可调的PWM信号发生器实验2占空比可调的PWM信号发生器一、实验任务基本部分:(1)用51单片机设计一个周期固定且占空比可调的PWM信号发生器。

(2)参数要求:a、信号周期为20ms,占空比范围1%-100%可调;b、用两个按键分别调整增量或减量;增量级别分为±1%和±5%两档可调,且要求可用按键选择;c、要求用两位LED数码管实时显示当前的占空比;d、51单片机晶振频率为12MHz。

扩展部分:(1)在基本部分设计的电路中,为输出的PWM信号增加光耦隔离输出电路;(2)为占空比调整过程增加超界声光报警电路;(3)可否改为脉宽固定而周期可改变的PWM信号发生器(简略说明,不要求设计编程)。

二、实验要求1、在PROTEUS中画出硬件设计图(AT89C51、12MHz晶振震荡电路、复位电路、按键调整电路、LED数码管显示电路、扩展部分电路)。

2、按任务要求用汇编或C编写程序并编译通过。

3、在PROTEUS下仿真通过。

三、报告要求1、任务分析、实现方案和程序流程图;2、硬件电路图;3、全部程序清单;4、打印出实验报告。

第二篇:信号发生器设计(推荐)模拟课程设计题信号发生器设计设计一个能够输出正弦波、三角波和矩形波的信号源电路,电路形式自行选择。

输出信号的频率可通过开关进行设定,具体要求如下:(1)输出信号的频率范围为100~800Hz,步进为100Hz。

(60分)(2)要求输出信号无明显失真,特别是正弦波信号。

(30分)评分标准:(1)范围满足设计要求得满分,否则酌情扣分。

(2)输出信号无明显失真可满分,有明显失真酌情扣分。

发挥部分(附加10分):进一步扩大输出信号范围和减小步进频率。

第三篇:VHDL实验四函数信号发生器设计.VHDL实验四:函数信号发生器设计设计要求:设计一个函数信号发生器,能产生方波,三角波,正弦波,阶梯波。

基于VHDL的SVPWM发生器的实现

模 块 、 WM 波输 出模块 、 P 同步 脉 冲模 块 , 下面将 分 别

进 行详 细的说 明 。 前 面介 绍 了 S P V WM 的 基 本 原 理 , 用 V L 采 HD

计 而不必 改动硬 件 电路 。使 用 F G P A来 开发 数字 电 路 , 以大大缩 短设计 时 间 , 少 P B面积 , 可 减 C 提高 系

统 的可靠 性 。

了广 泛应 用 。但 使 用 D P单 核 心 的控 制 方 法 存 在 S

一

些 缺陷 : 的硬 件 已完 全 固化 , 开 发 利 用 的 功 它 可

种 基于 F G 的无 速 度 传 感 器 矢 量 控 制 系 统 的 PA

目的 。

3 SP V WM 模块设计及其仿真结果

SP V WM模 块是 整个 设 计 的难 点 与 重 点 , 这 在

里 主要分 为作 用时 间 及输 出状 态 模块 、 间过 调 制 时

1 无速度传感器矢量控制 系统硬件结构

机的转矩脉 动。所 以在 电机 的矢量控制系统中得到 了广泛的应用。结合 F G P A数据处理速度高的特 点, V D 以 H L硬件语言来

编写 S P V WM, 过 Q A T SI自带 仿 真 软 件进 行 仿 真 。结 果 表 明 : 方 法 可 以有 效 地 控 制 逆 变 器桥 臂 开 关 。 通 U R UI 该

⑥

2 1 S i eh E gg 0 0 c T c. nn. .

机 电技 术

基 于 V L的 S P HD V WM 发 生 器 的实 现

一个用Verilog实现PWM硬件的开发实例

一个用Verilog实现PWM硬件的开发实例一个用Verilog实现PWM硬件的开发实例2008-01-17 12:48:34 来源:嵌入式技术网关键字: Verilog PWM硬件本文举例说明了一个使用FPGA的新设计流程,我们从中可以知道如何用软件实现PWM,然后如何将该设计转换成一个可以在FPGA 中运行的逻辑块,并能利用存储器映射I/O接口通过软件完成对该逻辑块的控制。

软硬件划分现在的情况与以前有所不同,软件工程师能够方便地参与到硬件设计中。

不管是硬件模块还是软件模块现在都可以用编程语言进行设计。

众所周知,C语言是嵌入式软件设计的通用语言。

在硬件设计方面,Verilog则是流行的选择(用VHDL的人也很多)。

Verilog的语法和结构与C编程语言非常相似,从本文的例子中也可以看到这一点。

同时,硬件的升级和修改也变得越来越方便。

以前可以通过下载新的可执行映像文件升级软件,但对硬件却行不通。

现在情况不同了。

就像软件开发人员能够快速编辑、重新编译、然后将新代码下载到存储器那样,使用可编程逻辑器件的硬件设计者也能做类似的事情。

可编程逻辑改变了嵌入式系统的设计方法,设计者可以像修改软件那样方便地修改硬件。

换句话说,在设计和调试阶段,设计者能够灵活选择软件方式或硬件方式来作为完成任务的最佳方式。

设计者无需太多的硬件知识就可以利用FPGA供应商提供的工具轻松地开发出可编程逻辑嵌入式系统。

例如,Altera公司的SOPC Builder能帮助系统设计师从已有的库中选择和配置外围电路,并增加用来创建和连接外围电路的用户逻辑。

加上一些可编程逻辑和硬件知识,软件工程师就能够充分利用硬件的优势改进他们的系统。

PWM软件PWM控制器会产生一连串脉冲。

通常需要规定脉冲的周期和宽度。

占空比被定义为脉冲宽度与周期的比值。

PWM有着广泛的应用,大多数情况下用于控制模拟电路。

因为数字信号连续变化的速率相对较快(当然取决于信号周期),因此最终会形成一个用来控制模拟设备的平均电压值。

基于VHDL的可控脉冲发声器 设计

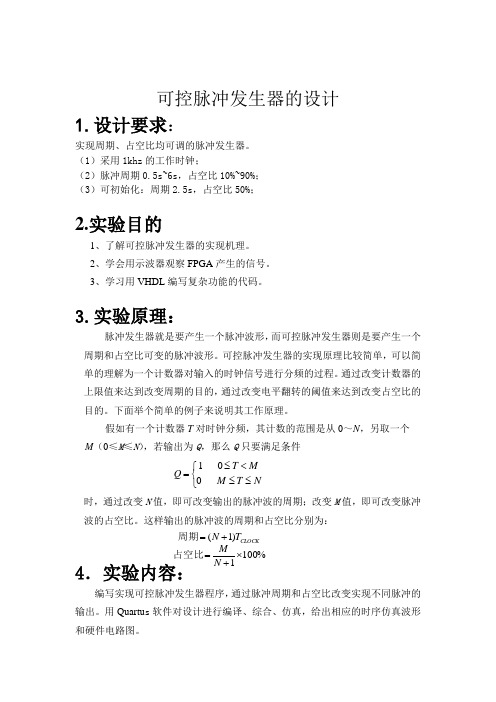

可控脉冲发生器的设计1.设计要求:实现周期、占空比均可调的脉冲发生器。

(1)采用1khz 的工作时钟;(2)脉冲周期0.5s~6s ,占空比10%~90%;(3)可初始化:周期2.5s ,占空比50%;2.实验目的1、了解可控脉冲发生器的实现机理。

2、学会用示波器观察FPGA 产生的信号。

3、学习用VHDL 编写复杂功能的代码。

3.实验原理:脉冲发生器就是要产生一个脉冲波形,而可控脉冲发生器则是要产生一个周期和占空比可变的脉冲波形。

可控脉冲发生器的实现原理比较简单,可以简单的理解为一个计数器对输入的时钟信号进行分频的过程。

通过改变计数器的上限值来达到改变周期的目的,通过改变电平翻转的阈值来达到改变占空比的目的。

下面举个简单的例子来说明其工作原理。

假如有一个计数器T 对时钟分频,其计数的范围是从0~N ,另取一个 M (0≤M ≤N ),若输出为Q ,那么Q 只要满足条件时,通过改变N 值,即可改变输出的脉冲波的周期;改变M 值,即可改变脉冲波的占空比。

这样输出的脉冲波的周期和占空比分别为:4.实验内容:编写实现可控脉冲发生器程序,通过脉冲周期和占空比改变实现不同脉冲的输出。

用Quartu s 软件对设计进行编译、综合、仿真,给出相应的时序仿真波形和硬件电路图。

⎩⎨⎧≤≤<≤=N T M M T Q 001%1001)1(⨯+=+=N M T N CLOCK 占空比周期5.程序设计及仿真:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity exp10 isport( Clk : in std_logic; --时钟输入Rst : in std_logic; --复位输入NU,ND : in std_logic; --输入:控制频率的改变MU,MD : in std_logic; --输入:控制占空比的改变Fout : out std_logic --波形输出);end exp10;architecture behave of exp10 issignal N_Buffer,M_Buffer : std_logic_vector(10 downto 0);signal N_Count :std_logic_vector(10 downto 0);signal clkin : std_logic;signal Clk_Count : std_logic_vector(12 downto 0); --产生一个低速时钟,用于按键判断beginprocess(Clk) --计数器累加beginif(Clk'event and Clk='1') thenif(N_Count=N_Buffer) thenN_Count<="00000000000";elseN_Count<=N_Count+1;end if;end if;end process;process(Clk) --波形判断beginif(Clk'event and Clk='1') thenif(N_Count<M_Buffer) thenFout<='1';elsif(N_Count>M_Buffer and N_Count<N_Buffer) then Fout<='0';end if;end if;end process;process(Clk)beginif(Clk'event and Clk='1') thenClk_Count<=Clk_Count+1;end if;clkin<=Clk_Count(12);end process;process(clkin) --频率及占空比的改变1beginif(clkin'event and clkin='0') thenif(Rst='0') thenM_Buffer<="010********";N_Buffer<="10000000000";elsif(NU='0') thenN_Buffer<=N_Buffer+1;elsif(ND='0') thenN_Buffer<=N_Buffer-1;elsif(MU='0') thenM_Buffer<=M_Buffer+1;elsif(MD='0') thenM_Buffer<=M_Buffer-1;end if;end if;end process;end behave;(2)仿真图:6.引脚绑定:7.心得体会:在课程设计的这段时间里,我认为收获还是很多的,不但进一步掌握了数字电子技术的基础知识及一门专业仿真软件的基本操作,还提高了自己的设计能力及动手能力,同时对于抢答器来了个系统的总结。

VHDL做PWM发生器的大作业

VHDL 大作业――PWM发生器姓名:贾胜文学号:036086279一.功能描述如下图所示:D0-D7为8位数据输入,A为内部脉宽寄存器/计数分频器选择信号,LOAD为所存信号输入,当有上升沿在LOAD上时,D0-D7上的数据被锁存进内部脉宽寄存器(A为高电平)或计数分频器(A为低电平)。

COUNTCLK为内部8位分频计数器时钟,当有上升沿出现在COUNTCLK上时,内部分频计数器值减1,当计数值0时再减1,分频计数器就重新从分频寄存器中装入计数初值,准备进行下一论计数,同时让内部的PWM周期计数器加1。

RS为内部PWM周期计数器、分频计数器清零信号,高电平有效。

PWMOUT为PWM信号输出端。

内部PWM周期计数器计数的同时与脉宽寄存器值比较,前者比后者小时,PWMOUT 输出高电平否则输出低电平。

这样通过改变分频寄存器中的值就可以改变PWM信号的周期,改变脉宽寄存器中的值就可以改变PWM信号的脉宽。

二.源程序:LIBRARY ieee;USE ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity pwm isport(a:in std_logic; --脉宽寄存器/分频寄存器选择.1-脉宽寄存器,0-分频寄存器countclk: in std_logic;--分频计数器计数信号rs: in std_logic;--分频计数器、PWM周期计数器清零信号load: in std_logic;--数据装载信号dat: in std_logic_vector(7 downto 0);--8位数据输入pwmout: out std_logic);--PWM信号输出end pwm;architecture work of pwm issignal mycounter,cmpdat,fenpindat,fenpincount:integer range 0 to 255;signal theout:std_logic;begindataload_block:process(load)beginif(load'event and load='1') thenif a='1' thencmpdat<=conv_integer(dat);elsefenpindat<=conv_integer(dat);end if;end if;end process;counter_block:process(countclk,rs)beginif (countclk'event and countclk='1') then if rs='0' thenif fenpincount=0 thenfenpincount<=fenpindat;mycounter<=mycounter+1;if cmpdat<mycounter thentheout<='0';elsetheout<='1';end if;elsefenpincount<=fenpincount-1;end if;elsemycounter<=0;fenpincount<=fenpindat;end if;end if;end process;pwmout<=theout;end work;三.仿真时序图四.附件:源程序:pwm.vhd仿真时序:pwm.scf。

PWM信号发生器的设计程序(veriloghdl)

PWM信号发生器的设计程序module pwmgen(clk,rst,ce,addr,write,wrdata,read,bytesel,rddata,pwm); input clk,rst,ce;input [1:0]addr;input write,read;input[31:0]wrdata;output[31:0]rddata;input[31:0]bytesel;output pwm;reg[31:0]clk_div_reg,duty_cycle_reg;reg control_reg;reg clk_div_reg_sel,duty_cycle_reg_sel,control_reg_sel;reg[31:0]pwm_cnt,rddata;reg pwm;wire pwm_ena;always@(addr)beginclk_div_reg_sel<=0;duty_cycle_reg_sel<=0;control_reg_sel<=0; case(addr)2'b00:clk_div_reg_sel<=1;2'b01:duty_cycle_reg_sel<=1;2'b10:control_reg_sel<=1;default:beginclk_div_reg_sel<=0;duty_cycle_reg_sel<=0;control_reg_sel<=0;endendcaseendalways@(posedge clk or negedge rst)beginif(rst==1'b0)clk_div_reg=0;elsebeginif(write & ce & clk_div_reg_sel)beginif(bytesel[0])clk_div_reg[7:0]=wrdata[7:0];if(bytesel[1])clk_div_reg[15:8]=wrdata[15:8];if(bytesel[2])clk_div_reg[23:16]=wrdata[23:16];if(bytesel[3])clk_div_reg[31:24]=wrdata[31:24];endendendalways@(posedge clk or negedge rst)beginif(rst==1'b0)duty_cycle_reg=0;elsebeginif(write&ce&duty_cycle_reg_sel)beginif(bytesel[0])duty_cycle_reg[7:0]=wrdata[7:0];if(bytesel[1])duty_cycle_reg[15:8]=wrdata[15:8];if(bytesel[2])duty_cycle_reg[23:16]=wrdata[23:16];if(bytesel[3])duty_cycle_reg[31:24]=wrdata[31:24];endendendalways@(posedge clk or negedge rst)beginif(rst==1'b0)control_reg=0;elsebeginif(write & ce & control_reg_sel)beginif(bytesel[0])control_reg=wrdata[0];endendendalways@(addr or read or clk_div_reg or duty_cycle_reg or control_reg or ce) beginif(read & ce)case(addr)2'b00:rddata<=clk_div_reg;2'b01:rddata<=duty_cycle_reg;2'b10:rddata<=control_reg; default:rddata=32'h8888;endcaseendassign pwm_en=control_reg; always@(posedge clk or negedge rst) beginif(rst==1'b0)pwm_cnt=0;elsebeginif(pwm_en)beginif(pwm_cnt>=clk_div_reg)pwm_cnt<=0;elsepwm_cnt<=pwm_cnt+1;endelsepwm_cnt<=0;endendalways@(posedge clk or negedge rst) beginif(rst==1'b0);elsebeginif(pwm_en)beginif(pwm_cnt<=duty_cycle_reg)pwm<=1'b1;elsepwm<=1'b0;endelsepwm<=1'b0;endendendmodule。

VHDL用pwm生成函数信号

library IEEE;use IEEE.STD_LOGIC_1164.all;use ieee.std_logic_arith.all;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity zuoye isPORT( clk : IN STD_LOGIC;--时钟信号led : out std_logic;--亮灯信号num2 : IN STD_LOGIC; --频率选定num1 : IN STD_LOGIC; --波形选择smg : out std_logic_vector(6 downto 0); --数码管的段数据smgkz : out std_logic_vector(3 downto 0); --数码管的选通信号pwm_out:out std_logic);END zuoye;architecture boxing of zuoye issignal k:integer range 0 to 3;signal m:integer range 1 to 3:=1;signal clk1k,clk1:std_logic;signal count:integer range 1 to 25000:=1;signal key3filt : std_logic; --按键change消抖后得到的信号signal key3cnt : integer range 0 to 50000000; --用于对yiwei按键输入有效时间进行计数signal key4filt : std_logic; --按键yiwei消抖后得到的信号signal key4cnt : integer range 0 to 50000000; --用于对CHANGE按键输入有效时间进行计数signal pin:integer range 1 to 3:=1;signal counta,countb,countc,countd,counte,countf,countg,counth,counti:integer range 0 to 50000000;signal counta1,countb1,countc1,countd1,counte1,countf1,countg1,counth1,counti1:integer range 0 to 50000000;signal out1,out2,out3,out4,out5,out6,out7,out8,out9:std_logic;signal aa,ab,ac:integer:=0;signal c1,c2,c3:integer range 0 to 50000000;--按键消抖Beginprocess (num1)---num1constant N :integer := 5000000;beginif clk'event and clk = '1' thenif num1 = '0' then --当key1 输入低电平,即按键按下if key3cnt /= N then --一直计数到Nkey3cnt <= key3cnt + 1;end if;if key3cnt = N-1 then --最后一个计数时输出key1filt脉冲key3filt <= '1';elsekey3filt <= '0';end if;elsekey3cnt <= 0;end if;end if;end process;process (num2)---num2——消抖constant N :integer := 5000000;beginif clk'event and clk = '1' thenif num2 = '0' thenif key4cnt /= N thenkey4cnt <= key4cnt + 1;end if;if key4cnt = N-1 thenkey4filt <= '1';elsekey4filt <= '0';end if;elsekey4cnt <= 0;end if;end if;end process;process(clk)beginif (clk'event and clk='1') thenif count=25000 thenclk1k<=not clk1k;count<=1;else count<=count+1;end if;end if;end process;process(clk1k)——数码管动态显示beginif (clk1k'event and clk1k='1') thenif (k=3) thenk<=0;else k<=k+1;end if;end if;case k iswhen 0=>smgkz<="0111";when 1=>smgkz<="1011";when 2=>smgkz<="1101";when 3=>smgkz<="1110";end case;end process;process(clk,key3filt)——波形选择beginif (clk'event and clk='1') thenif (key3filt='1') thenif m=3 thenm<=1;else m<=m+1;end if;end if;end if;end process;process(clk,key4filt) ——选择波形频率beginif (clk'event and clk='1') thenif (key4filt='1') thenif pin=3 thenpin<=1;else pin<=pin+1;end if;end if;end if;end process;process(clk) ——第一个三角波函数beginif rising_edge(clk) thenif aa=0 thenif counta <1000-counta1 thenout1<='0';elseend if;if counta=1000 thencounta<=0;if counta1=1000 thenaa<=1;elsecounta1<=counta1+1;end if;elsecounta<=counta+1;end if;elsif aa=1 thenif counta <1000-counta1 thenout1<='0';elseout1<='1';end if;if counta=1000 thencounta<=0;if counta1=0 thenaa<=0;elsecounta1<=counta1-1;end if;elsecounta<=counta+1;end if;end if;end if;end process;process(clk) ——第二个三角波函数beginif rising_edge(clk) thenif ab=0 thenif countb <2000-countb1 thenout2<='0';elseout2<='1';end if;if countb=2000 thencountb<=0;if countb1=2000 thenelsecountb1<=countb1+1;end if;elsecountb<=countb+1;end if;elsif ab=1 thenif countb <2000-countb1 thenout2<='0';elseout2<='1';end if;if countb=2000 thencountb<=0;if countb1=0 thenab<=0;elsecountb1<=countb1-1;end if;elsecountb<=countb+1;end if;end if;end if;end process;process(clk) ——第三个三角波函数beginif rising_edge(clk) thenif ac=0 thenif countg <500-countg1 thenout7<='0';elseout7<='1';end if;if countg=500 thencountg<=0;if countg1=500 thenac<=1;elsecountg1<=countg1+1;end if;elsecountg<=countg+1;end if;elsif ac=1 thenif countg <500-countg1 thenout7<='0';elseout7<='1';end if;if countg=500 thencountg<=0;if countg1=0 thenac<=0;elsecountg1<=countg1-1;end if;elsecountg<=countg+1;end if;end if;end if;end process;process(clk) ——第一个正弦函数variable a:integer range 0 to 50000000; variable b:integer range 0 to 50000000:=8; beginif rising_edge(clk) thenif countc=2100 thencountc<=0;if c1=0 thenif a=31 thenc1<=1;elsea:=a+1;end if;end if;if c1=1 thenif a=1 thenc1<=0;elsea:=a-1;end if;end if;if countc1=2100 thencountc1<=0;elsecase a iswhen 1=>countc1<=1*b;when 2=>countc1<=4*b;when 4=>countc1<=13*b; when 3=>countc1<=8*b;when 5=>countc1<=19*b;when 6=>countc1<=26*b;when 7=>countc1<=34*b;when 8=>countc1<=43*b;when 9=>countc1<=53*b;when 10=>countc1<=64*b;when 11=>countc1<=75*b;when 12=>countc1<=87*b;when 13=>countc1<=99*b;when 14=>countc1<=112*b;when 15=>countc1<=124*b;when 16=>countc1<=137*b;when 17=>countc1<=150*b;when 18=>countc1<=162*b;when 19=>countc1<=174*b;when 20=>countc1<=186*b;when 21=>countc1<=197*b;when 22=>countc1<=207*b;when 23=>countc1<=217*b;when 24=>countc1<=225*b;when 25=>countc1<=233*b;when 26=>countc1<=239*b;when 27=>countc1<=245*b;when 28=>countc1<=249*b;when 29=>countc1<=252*b;when 30=>countc1<=254*b;when others=>countc1<=255*b;end case;end if;elsecountc<=countc+1;end if;if countc <countc1 thenout3<='1';else out3<='0';end if;end if;end process;process(clk) ——第二个正弦函数variable a:integer range 0 to 50000000;variable b:integer range 0 to 50000000:=8;beginif rising_edge(clk) thenif countd=3000 thencountd<=0;if c2=0 thenif a=31 thenc2<=1;elsea:=a+1;end if;end if;if c2=1 thenif a=1 thenc2<=0;elsea:=a-1;end if;end if;if countd1=3000 thencountd1<=0;elsecase a iswhen 1=>countd1<=1*b;when 2=>countd1<=4*b;when 4=>countd1<=13*b; when 3=>countd1<=8*b;when 5=>countd1<=19*b;when 6=>countd1<=26*b;when 7=>countd1<=34*b;when 8=>countd1<=43*b;when 9=>countd1<=53*b;when 10=>countd1<=64*b;when 11=>countd1<=75*b;when 12=>countd1<=87*b;when 13=>countd1<=99*b;when 14=>countd1<=112*b;when 15=>countd1<=124*b;when 16=>countd1<=137*b;when 17=>countd1<=150*b;when 18=>countd1<=162*b;when 19=>countd1<=174*b;when 20=>countd1<=186*b;when 21=>countd1<=197*b;when 22=>countd1<=207*b;when 23=>countd1<=217*b;when 24=>countd1<=225*b;when 25=>countd1<=233*b;when 26=>countd1<=239*b;when 27=>countd1<=245*b;when 28=>countd1<=249*b;when 29=>countd1<=252*b;when 30=>countd1<=254*b;when others=>countd1<=255*b;end case;end if;elsecountd<=countd+1;end if;if countd <countd1 thenout4<='1';else out4<='0';end if;end if;end process;process(clk)——第三个正弦函数variable a:integer range 0 to 50000000;variable b:integer range 0 to 50000000:=8;beginif rising_edge(clk) thenif counth=5000 thencounth<=0;if c3=0 thenif a=31 thenc3<=1;elsea:=a+1;end if;end if;if c3=1 thenif a=1 thenc3<=0;elsea:=a-1;end if;end if;if counth1=5000 thencounth1<=0;elsecase a iswhen 1=>counth1<=1*b;when 2=>counth1<=4*b;when 4=>counth1<=13*b; when 3=>counth1<=8*b;when 5=>counth1<=19*b;when 6=>counth1<=26*b;when 7=>counth1<=34*b;when 8=>counth1<=43*b;when 9=>counth1<=53*b;when 10=>counth1<=64*b;when 11=>counth1<=75*b;when 12=>counth1<=87*b;when 13=>counth1<=99*b;when 14=>counth1<=112*b;when 15=>counth1<=124*b;when 16=>counth1<=137*b;when 17=>counth1<=150*b;when 18=>counth1<=162*b;when 19=>counth1<=174*b;when 20=>counth1<=186*b;when 21=>counth1<=197*b;when 22=>counth1<=207*b;when 23=>counth1<=217*b;when 24=>counth1<=225*b;when 25=>counth1<=233*b;when 26=>counth1<=239*b;when 27=>counth1<=245*b;when 28=>counth1<=249*b;when 29=>counth1<=252*b;when 30=>counth1<=254*b;when others=>counth1<=255*b;end case;end if;elsecounth<=counth+1;end if;if counth <counth1 thenout8<='1';else out8<='0';end if;end if;end process;process(clk) ——第一个锯齿波函数beginif rising_edge(clk) thenif counte <1500-counte1 thenout5<='0';elseout5<='1';end if;if counte=1500 thencounte<=0;if counte1=1500 thencounte1<=0;elsecounte1<=counte1+1;end if;elsecounte<=counte+1;end if;end if;end process;process(clk)——第二个锯齿波函数beginif rising_edge(clk) thenif countf <2000-countf1 thenout6<='0';elseout6<='1';end if;if countf=2000 thencountf<=0;if countf1=2000 thencountf1<=0;elsecountf1<=countf1+1;end if;elsecountf<=countf+1;end if;end if;end process;process(clk)——第三个锯齿波函数beginif rising_edge(clk) thenif counti <1000-counti1 thenout9<='0';elseout9<='1';end if;if counti=1000 thencounti<=0;if counti1=1000 thencounti1<=0;elsecounti1<=counti1+1;end if;elsecounti<=counti+1;end if;end if;end process;process(clk)beginif rising_edge(clk) thencase m iswhen 1=>if pin=2 thenpwm_out<=out1; ——输出第二个三角波频率case k iswhen 0 =>smg<="0010010";when 1 =>smg<="0100100";when 2 =>smg<="1000000";when 3 =>smg<="1111001";end case;elsif pin=3 thenpwm_out<=out2; ——输出第三个三角波频率case k iswhen 0 =>smg<="0000010";when 1 =>smg<="1000000";when 2 =>smg<="1000000";when 3 =>smg<="1111001";end case;else pwm_out<=out7; ——输出第一个三角波频率case k iswhen 0 =>smg<="1000000";when 1 =>smg<="1000000";when 2 =>smg<="1111001";when 3 =>smg<="1111001";end case;end if;when 3=>if pin=2 thenpwm_out<=out5; ——输出第二个正弦波频率case k iswhen 0 =>smg<="0100100";when 1 =>smg<="0100100";when 2 =>smg<="1000000";when 3 =>smg<="0110000";end case;elsif pin=3 thenpwm_out<=out6; ——输出第三个正弦波频率case k iswhen 0 =>smg<="0100100";when 1 =>smg<="1111001";when 2 =>smg<="1000000";when 3 =>smg<="0110000";end case;else pwm_out<=out9; ——输出第一个正弦波频率case k iswhen 0 =>smg<="1000000";when 1 =>smg<="0010010";when 2 =>smg<="1000000";when 3 =>smg<="0110000";end case;end if;when 2=> if pin=1 thenpwm_out<=out3; ——输出第二个锯齿波频率case k iswhen 0 =>smg<="0110000";when 1 =>smg<="0000000";when 2 =>smg<="0110000";when 3 =>smg<="0100100";end case;elsif pin=2 thenpwm_out<=out4; ——输出第三个锯齿波频率case k iswhen 0 =>smg<="0000000";when 1 =>smg<="0000010";when 2 =>smg<="0100100";when 3 =>smg<="0100100";end case;else pwm_out<=out8; ——输出第一个锯齿波频率case k iswhen 0 =>smg<="1111001";when 1 =>smg<="0000010";when 2 =>smg<="1111001";when 3 =>smg<="0100100";end case;end if;end case;end if;end process;end architecture bingxing;——结束。

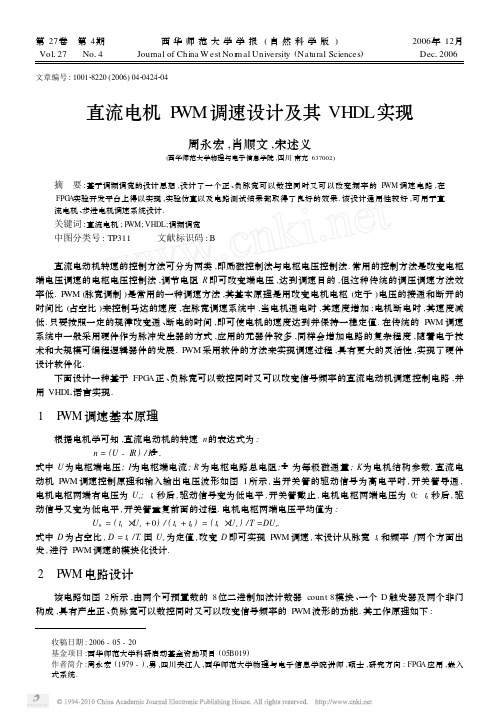

直流电机PWM调速设计及其VHDL实现

第27卷Vol 127 第4期No 14西华师范大学学报(自然科学版)Journal of China W est Nor mal University (Natural Sciences )2006年12月Dec 12006文章编号:100128220(2006)0420424204 收稿日期:2006-05-20基金项目:西华师范大学科研启动基金资助项目(05B019)作者简介:周永宏(1979-),男,四川夹江人,西华师范大学物理与电子信息学院讲师,硕士,研究方向:FPG A 应用,嵌入式系统.直流电机P WM 调速设计及其VHDL 实现周永宏,肖顺文,宋述义(西华师范大学物理与电子信息学院,四川南充637002)摘 要:基于调频调宽的设计思想,设计了一个正、负脉宽可以数控同时又可以改变频率的P WM 调速电路,在FPG A 实验开发平台上得以实现,实验仿真以及电路测试结果都取得了良好的效果.该设计通用性较好,可用于直流电机、步进电机调速系统设计.关键词:直流电机;P WM;VHDL;调频调宽中图分类号:TP311 文献标识码:B直流电动机转速的控制方法可分为两类,即励磁控制法与电枢电压控制法.常用的控制方法是改变电枢端电压调速的电枢电压控制法,调节电阻R 即可改变端电压,达到调速目的,但这种传统的调压调速方法效率低.P WM (脉宽调制)是常用的一种调速方法,其基本原理是用改变电机电枢(定子)电压的接通和断开的时间比(占空比)来控制马达的速度,在脉宽调速系统中,当电机通电时,其速度增加;电机断电时,其速度减低.只要按照一定的规律改变通、断电的时间,即可使电机的速度达到并保持一稳定值.在传统的P WM 调速系统中一般采用硬件作为脉冲发生器的方式,应用的元器件较多,同样会增加电路的复杂程度,随着电子技术和大规模可编程逻辑器件的发展.P WM 采用软件的方法来实现调速过程,具有更大的灵活性,实现了硬件设计软件化.下面设计一种基于FPG A 正、负脉宽可以数控同时又可以改变信号频率的直流电动机调速控制电路,并用VHDL 语言实现.1 P WM 调速基本原理根据电机学可知,直流电动机的转速n 的表达式为: n =(U -I R )/KΦ.式中U 为电枢端电压;I 为电枢端电流;R 为电枢电路总电阻;Φ为每极磁通量;K 为电机结构参数.直流电动机P WM 调速控制原理和输入输出电压波形如图1所示,当开关管的驱动信号为高电平时,开关管导通,电机电枢两端有电压为U s ;t 1秒后,驱动信号变为低电平,开关管截止,电机电枢两端电压为0;t 2秒后,驱动信号又变为低电平,开关管重复前面的过程.电机电枢两端电压平均值为: U 0=(t 1×U s +0)/(t 1+t 2)=(t 1×U s )/T =DU s .式中D 为占空比,D =t 1/T .因U s 为定值,改变D 即可实现P WM 调速,本设计从脉宽t 1和频率f 两个方面出发,进行P WM 调速的模块化设计.2 P WM 电路设计该电路如图2所示,由两个可预置数的8位二进制加法计数器count 8模块、一个D 触发器及两个非门构成,具有产生正、负脉宽可以数控同时又可以改变信号频率的P WM 波形的功能.其工作原理如下: 第27卷第4期 周永宏,等:直流电机P WM调速设计及其VHDL实现425 电路刚开始工作时Q=0,下方count8处于计数状态并对CLK进行计数,且cin=0;上方count8处于置数状态,即通过dataa端直接给计数器置数.当下方count8计数到255时,计数器送出进位信号cin=1,即cin端送出高电平,D触发器接收信号即Q=1.Q=1使得上方Count8处于计数状态并对CLK进行计数,且cin=0;下方count8处于置数状态,即通过datab端直接给计数器置数;当上方count8由预置数计数到255时,计数器送出进位信号cin=1,经非门后使得D触发器清零即Q=0.Q=0使得下方count8由预置数计数到255,下方count8处于置数状态.如此反复进行.dataa端信号为控制高电平脉宽的预置数,datab端信号为控制低电平脉宽的预置数.该电路输出信号y占空比为:q y=(256-dataa端预置数)/[(256-dataa端预置数)+(256-datab端预置数)]=(256-dataa端预置数)/(512-dataa端预置数-datab端预置数)].该电路输出信号y周期为:T y=[(256-dataa端预置数)+(256-datab端预置数)]×Tclk=(512-dataa端预置数-datab端预置数)×Tclk.该电路输出信号y频率为:f y=1/[(512-dataa端预置数-datab端预置数)×Tclk].3 控制系统count8模块软件设计count8模块为可预置数的8位二进制加法计数器,该模块有3个输入信号和1个输出信号,其中LD端为其预置数控制端,cin端为加法计数器进位端.count8模块计数范围为0-255,其源程序如下: library ieee; use ieee.std_l ogic1164.a11; use ieee.std_l ogic_arith.all; use ieee.std_l ogic_unsigned.all; entity count8is —8位可预置加法计数器 port(clk,ld:in std_l ogic; data:in integer range0t o255; cin:out std_l ogic); end count8; architecture rtl of count8is signal count;integer range0t o255; begin 西华师范大学学报(自然科学版)2006年426 p r ocess(clk) begin if(clkπevent and clk=πlπ)then if ld=πlπthen count<=data; —置数else count<=count+t; —加计数 end if; end if; end p r ocess; p r ocess(count) begin if count=255then cin<=πl’; —计数进位 else cin<=’0’; end if; end p r ocess; end rt1;4 P WM波形产生电路仿真结果图3为dataa端预置数=datab端预置数=50的仿真结果:占空比为:q=(256-dataa端预置数)/(512-dataa端预置数-datab端预置数)=(256-50)/(512-y50-50)=50%.频率为:f=1/[(512-dataa端预置数-datab端预置数)×Tclk]=1/412×Tclk.y图4为dataa端预置数=200、datab端预置数=50的仿真结果:占空比为:q=(256-dataa端预置数)/(512-dataa端预置数-datab端预置数)=(256-200)/(512-y200-50)=21%.频率为:f=1/[(512-dataa端预置数-datab端预置数)×TCLK]=1/262×Tclk.y5 结束语近年来,随着HDL语言的出现及FPG A主频的不断提高,以前由硬件完成的功能,现在很大程度上已被软件取代,硬件设计软件化已经成为一种趋势.用软件实现直流电动机的P WM调速,大大的简化了电路,从实际运用的效果来看,它较好地实现了对直流电机的速度控制,并具有精度高、快速响应性好、稳定性高等优点,具有很好的应用前景.参考文献:[1] 潘 松,黄继业.E DA技术实用教程[M].北京:科学出版社,2002.[2] 黄智伟.全国大学生电子设计竞赛训练教程[M].北京:电子工业出版社,2005. 第27卷第4期 周永宏,等:直流电机P WM调速设计及其VHDL实现427[3] 张晓青.直流电动机数字P WM调速系统设计[J].北京机械工业学院学报,2000.(4).[4] 马书雷,张立勋.用AVR单片机实现直流电机P WM调速[J].应用科技,2000.(10).[5] 何最红,李 扬.基于微控制的P WM调速系统[J].邵阳学院学报(自然科学版),2004.(4).[6] 李维军,韩小刚.基于单片机用软件实现直流电机P WM调速系统[J].机电一体化,2004.(5).Desi gn of P WM Speed Adjusti n g Syste m ofDC M otor with VH DL LanguageZHOU Yong2hong,X I A O Shun2wen,S ONG Shu2yi(College of Physics&Electr onic I nf or mati on,China W est Nor mal University,Nanchong,637002,China)Abstract:Based on the design thought of adjusting the frequency and the width,we have designed the P WM s peed adjusting circuit which can change the width of the negative and the positive pulse at the sa me ti m e can change the frequency of the pulse by digital f or m contr ol,and which has been realized in the FPG A experi m ent p latf or m.The experi m ental si m ulati on aswell as the electric circuit test result have all obtained the good effect.This design versa2 tility is good,may be used in the direct current mot or,step2by2step s the electric mot ors peed adjusting syste m de2 sign.Key words:direct current mot or;P WM;VHDL;adjusting the frequency and the width(上接第380页)Appli cati on of W ei bull D istri buti on i n Esti m ati n gReli a ble L i feti m e of He2Ne LaserX I A NG J ing,CHEN Chuan2yang,ZHANG De2ran(College of M ath and I nfor mati on,China W est Nor mal Univ.,Nanchong637002,China)Abstract:This paper fetches the lighting electrical current as accelerating stress under the objective backgr ound of W eibull distributi on,and carries on the data analysis of a batch of He2Ne laser under accelerated life test with f our accelerating stresses.Finally,it esti m ates the reliable lifeti m e and every dependable index of the laser under nor mal electrical current.Key words:W eibull distributi on;He2Ne laser;accelerated life test;accelerating stress。

一种基于VHDL与CPLD器件的PWM发生器

比较器的输出脉冲确定了 T触发器的翻转时间 ,从而

确定了 PWM 脉冲的占空比 。由于 T触发器输出初始

值为 0,两路 PWM 脉冲占空比为 :

ρ 1

=

coun tq 212 ,

ρ 2

212 =

- coun tq 212

(1)

EN2为使能信号 ,与单片机 I/O 口相连 , EN2 为

高电平时 , COUNTQ 为固定值 , PWM 脉冲占空比不

摘 要 :介绍了一种自行研制的基于硬件描述语言 (VHDL )和复杂可编程逻辑器件 ( CPLD )的 PWM 发

生器的设计 ,在产生正反两路 PWM 波形信号的同时 ,实现了两路信号互锁 、延时时间可调 。该发生器

采用数字化设计 ,结构简单 、控制精确 、可在线编程 。

关键词 :硬件描述语言 ;复杂可编程逻辑器件 ;脉宽调制发生器

度 。本研究采用

8

位计数器

,延时时间为

20

1 ×106

×

256 = 12. 8 us,其相应的最大死区宽度值为 12. 8 us。

“使能控制 1”信号用于控制电机停启 。

图 1 PWM 发生器原理图

2 电路设计和程序实现

本研究中的电路设计采用的软件工具是 A ltera公 司的 MAX + PLUSII。并采用 VHDL 硬件描述语言对 计数器单元 、基准数据锁存控制器以及死区逻辑控制 模块进行了描述 。

脉宽调制PWM的VHDL实现

COMPONENT lpm_compare

GENERIC (

lpm_representation

: STRING;

lpm_type

: STRING;

lpm_width

: NATURAL

4/6

); PORT (

dataa : IN STD_LOGIC_VECTOR (7 DOWNTO 0); datab : IN STD_LOGIC_VECTOR (7 DOWNTO 0); AgB : OUT STD_LOGIC ); END COMPONENT;

pwm_output : out std_logic ); end PWM;

architecture behav of PWM is

signal Triangle_data : std_logic_vector( 7 downto 0 ); 5/6

signal pwm_data : std_logic;

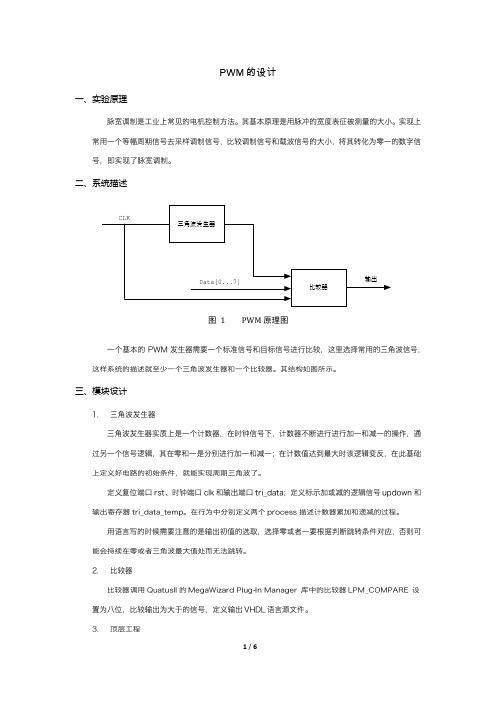

一、实验原理

PWM 的设计

二、系统描述

CLK

三角波发生器

Data[0...7]

输出 比较器

图 1 PWM 原理图

三、模块设计

1/6

四、实验结果

五、问题与展望

图 2 PWM 仿真波形图

2/6

附源代码

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_arith.all; USE ieee.std_logic_unsigned.all;

component Triangle is port( rst : in std_logic; clk : in std_logic; tri_data : out std_logic_vector ( 7 downto 0 ) );

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

VHDL 大作业――PWM发生器

姓名:贾胜文

学号:036086279

一.功能描述

如下图所示:

D0-D7为8位数据输入,A为内部脉宽寄存器/计数分频器选择信号,LOAD为所存信号输入,当有上升沿在LOAD上时,D0-D7上的数据被锁存进内部脉宽寄存器(A为高电平)或计数分频器(A为低电平)。

COUNTCLK为内部8位分频计数器时钟,当有上升沿出现在COUNTCLK上时,内部分频计数器值减1,当计数值0时再减1,分频计数器就重新从分频寄存器中装入计数初值,准备进行下一论计数,同时让内部的PWM周期计数器加1。

RS为内部PWM周期计数器、分频计数器清零信号,高电平有效。

PWMOUT为PWM信号输出端。

内部PWM周期计数器计数的同时与脉宽寄存器值比较,前者比后者小时,PWMOUT 输出高电平否则输出低电平。

这样通过改变分频寄存器中的值就可以改变PWM信号的周期,改变脉宽寄存器中的值就可以改变PWM信号的脉宽。

二.源程序:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity pwm is

port(

a:in std_logic; --脉宽寄存器/分频寄存器选择.1-脉宽寄存器,0-分频寄存器

countclk: in std_logic;--分频计数器计数信号

rs: in std_logic;--分频计数器、PWM周期计数器清零信号

load: in std_logic;--数据装载信号

dat: in std_logic_vector(7 downto 0);--8位数据输入

pwmout: out std_logic);--PWM信号输出

end pwm;

architecture work of pwm is

signal mycounter,cmpdat,fenpindat,fenpincount:integer range 0 to 255;

signal theout:std_logic;

begin

dataload_block:process(load)

begin

if(load'event and load='1') then

if a='1' then

cmpdat<=conv_integer(dat);

else

fenpindat<=conv_integer(dat);

end if;

end if;

end process;

counter_block:process(countclk,rs)

begin

if (countclk'event and countclk='1') then if rs='0' then

if fenpincount=0 then

fenpincount<=fenpindat;

mycounter<=mycounter+1;

if cmpdat<mycounter then

theout<='0';

else

theout<='1';

end if;

else

fenpincount<=fenpincount-1;

end if;

else

mycounter<=0;

fenpincount<=fenpindat;

end if;

end if;

end process;

pwmout<=theout;

end work;

三.仿真时序图

四.附件:

源程序:pwm.vhd

仿真时序:pwm.scf。