迟滞性比较器的设计方法

cmos电压迟滞比较器电路

cmos电压迟滞比较器电路标题:CMOS电压迟滞比较器电路的原理与应用导语:本文将深入探讨CMOS电压迟滞比较器电路的原理与应用。

通过分析其工作原理、特点和优势,我们可以更好地理解它在现代电路设计中的重要性和应用价值。

摘要:CMOS电压迟滞比较器电路是一种关键的电子元件,其通过比较输入电压与参考电压,产生高或低电平输出。

本文将从基本原理的介绍开始,详细讨论CMOS电压迟滞比较器电路的结构、工作方式和性能特点,并介绍其在数模转换、振荡器等领域的应用。

目录:1. 引言2. CMOS电压迟滞比较器电路的基本原理3. CMOS电压迟滞比较器电路的结构和工作方式4. CMOS电压迟滞比较器电路的性能特点4.1 高输入阻抗和低功率消耗4.2 快速响应和高精度4.3 低噪声和抗干扰能力强5. CMOS电压迟滞比较器电路的应用5.1 数模转换5.2 振荡器5.3 其他应用领域6. 我对CMOS电压迟滞比较器电路的个人观点和理解7. 总结1. 引言CMOS电压迟滞比较器电路是一种用于比较输入电压和参考电压的重要元件。

它在现代集成电路设计中发挥着关键作用,广泛应用于数模转换、振荡器以及其他各种电路设计中。

在本文中,我们将对CMOS 电压迟滞比较器电路进行深入研究,以更好地了解其原理、结构、性能特点和应用。

2. CMOS电压迟滞比较器电路的基本原理CMOS电压迟滞比较器电路通过将输入电压与参考电压进行比较,输出高或低电平。

其基本原理基于MOS管的开关特性。

当输入电压大于参考电压时,输出结果为高电平;当输入电压小于参考电压时,输出结果为低电平。

这种电路可以通过调整参考电压的阈值、电流源和电压迟滞等参数,实现不同的比较功能。

3. CMOS电压迟滞比较器电路的结构和工作方式CMOS电压迟滞比较器电路一般由输入级、差分放大器和输出级等部分组成。

输入级主要负责将输入电压进行增益放大,差分放大器用于进行输入电压和参考电压的比较,并输出差分信号,输出级将差分信号转化为高或低电平输出。

滞回比较器设计

滞回比较器设计

滞回比较器是一种基本的电子电路,在模拟电路中起着重要的作用。

它可以用于信号的比较和判别,常用于阈值判定和数字信号处理等应用场景。

以下是一个简单的滞回比较器的设计过程,供参考:

1. 电源选择:根据设计需求和系统要求,选择合适的电源电压。

常见的电源电压包括单电源(如+5V)和双电源(如±12V)。

2. 运放选择:根据设计要求选择适合的运放芯片。

常用的运放芯片有LM358、LM741等。

这里我们选择LM358作为滞回比较器的运放芯片。

3. 连接电源:将正电源和负电源引线分别连接到运放芯片的正电源和负电源引脚上。

4. 连接滞回电阻:根据设计要求选择合适的滞回电阻值,一般在几千欧姆至几十万欧姆之间。

将两个滞回电阻分别连接到运放芯片的输入端和反馈端。

5. 连接信号输入:将待比较的信号输入引线连接到运放芯片的输入端。

6. 反馈电容连接:为了增加滞回效果,可以选择适当的反馈电容连接到滞回电阻之间。

7. 设定比较阈值:通过调整滞回电阻和反馈电阻的比例,可以设定滞回比较器的比较阈值。

当输入信号超过阈值时,输出会发生跳变。

8. 连接输出:将输出引脚连接到需要的电路或设备上,用于实现对信号的比较和判别。

通过以上步骤,就可以完成一个简单的滞回比较器的设计。

根据具体的应用需求和系统要求,还可以进一步优化和改进滞回比较器的性能和功能。

同向迟滞比较器电路

同向迟滞比较器电路同向迟滞比较器电路(hysteresis comparator)是一种常见的电路设计,用于比较输入信号与参考电压并输出相应的逻辑电平。

它在电子设备和系统中广泛应用于电压比较、开关控制和信号处理等领域。

同向迟滞比较器电路能够解决传统比较器电路中的抖动和干扰问题,并提供更稳定可靠的输出。

它通过使用正反馈回路,增加了一个称为迟滞带(hysteresis band)的区域,在输入信号变化时产生一个阈值,这使得比较器只在输入信号超过或低于特定阈值时才能切换输出状态。

在同向迟滞比较器电路中,输入信号与参考电压被连接到一个差分放大器。

差分放大器通过放大输入信号,并将其转换成一个电流或电压信号,再经过一个反馈网络,形成一个正反馈回路。

这个正反馈回路通过改变阈值电压,实现输入信号的比较和输出电平的切换。

正反馈回路通常由一个滞回电阻和一个滞回电容组成,它们决定了比较器电路的迟滞特性。

滞回电阻控制着迟滞带的大小,滞回电容则决定着迟滞带的斜率。

通常情况下,选择合适的滞回电阻和滞回电容可以根据系统需求来调整迟滞带的宽度和响应速度。

同向迟滞比较器电路的优点在于能够抑制输入信号中的噪声和抖动,从而提高系统的稳定性和抗干扰能力。

它适用于需要在信号变化较小的情况下进行精确比较的应用,例如温度传感器、光电传感器和压力传感器等。

在设计同向迟滞比较器电路时,一些注意事项需要被考虑。

首先,选取合适的滞回电阻和滞回电容值,以确保迟滞带的宽度满足系统要求。

其次,特别关注电源电压和输入偏置电流对比较器性能的影响,避免过大的电源电压或输入偏置电流导致误差或不稳定的输出。

此外,考虑到比较器的功耗和速度要求,选择合适的操作放大器和电源电压,使得电路能够在所需的响应速度和功耗范围内工作。

总之,同向迟滞比较器电路是一种功能强大且实用的电路设计,通过增加正反馈回路和迟滞带,解决了传统比较器电路的抖动和干扰问题。

合理选取滞回电阻和滞回电容值,注意电源电压和输入偏置电流对比较器性能的影响,能够确保电路工作稳定可靠。

迟滞比较器原理及计算

迟滞比较器原理及计算迟滞比较器(Hysteresis Comparators)是一种电路器件,用于将一个电压信号进行比较,并在输入信号穿过设定阈值时提供一个输出。

其原理基于正反馈,可以提供一种滞后效应,使得输出在阈值之间有一个死区。

迟滞比较器的原理如下:当输入电压超过上限阈值时,输出切换到高电平,然后输入电压必须降低到下限阈值以下,输出才能切换回低电平。

这种死区效应有助于排除输入信号的噪声,并提高比较器的稳定性。

常见的迟滞比较器电路包括基于运算放大器(OP-AMP)和正反馈电阻网络构成的非反转比较器。

迟滞比较器的工作原理导出了其计算方式。

在理想情况下,假设电压源的输入为V_in,上限阈值为V_upper,下限阈值为V_lower,输出电压为V_out。

则当输入电压超过上限阈值时,输出电压切换为高电平,当输入电压低于下限阈值时,输出电压切换为低电平。

常见的计算方式是基于迟滞比较器的振幅范围(或称为迟滞窗口)来确定。

振幅范围是指上限阈值与下限阈值之间的差值,即V_upper - V_lower。

选择合适的振幅范围可以在输入信号的变化过程中提供适当的抗干扰能力。

为了更好地理解迟滞比较器的计算,可以考虑一个经典的非反转迟滞比较器电路,其中上限阈值为V_upper,下限阈值为V_lower,输入电压为V_in,输出电压由一个比较器和正反馈网络决定。

根据电路设计和正反馈网络的选择,我们可以计算出适当的上限阈值和下限阈值,以及输出状态的切换时刻。

总之,迟滞比较器通过正反馈的设计提供一个滞后效应,使得输出在输入信号穿过设定阈值时有一个死区。

其计算方式可以基于阈值的选择和正反馈网络的特性来确定。

迟滞比较器被广泛应用于各种电子设备和电路,如电压比较、斜率计算器、峰值检测等领域。

迟滞比较器

迟滞比较器单门限电压比较器虽然有电路简单、灵敏度高等特点,但其抗干扰能力差。

例如,在单门限电压v中含XX_01中,当比较器的图I有噪声或干扰电压时,其输入和所示,输出电压波形如图XX_01VvV附近出现干扰,由于在==REFthI VvV,导致将时而为,时而为OLOOH比较器输出不稳定。

如果用这个v去控制电机,将出现输出电压O频繁的起停现象,这种情况是不允许的。

提高抗干扰能力的一种方案是采用迟滞比较器。

.电路组成1迟滞比较器是一个具有迟滞回环所示为特性的比较器。

图XX_02aXX_01图反相输入迟滞比较器原理电路,它是在反相输入单门限电压比较器的基础上引入了正反馈网络,如其传输特性如图XX_02b所示。

Vv位置互换,就可组成将与REFI同相输入迟滞比较器。

(a)2.门限电压的估算由于比较器中的运放处于开环状态或正反馈状态,因此一般情况vv不下,输出电压与输入电压IO成线性关系,只有在输出电压发生跳变瞬间,集成运放两个输入(b) 端之间的电压才可近似认为等于图XX_02零,即(1)或设运放是理想的并利用叠加原理,则有(2)word编辑版.vVVVV和下门限电压的不同值(根据输出电压),可求出上门限电压或TOLOT+–OH分别为(3)(4)门限宽度或回差电压为(5),则由式(3)~(5)XX_02a所示,且可求得设电路参数如图,和。

3.传输特性开始讨论。

设从,和vvv增加当由零向正方向增加到接近前,不变。

当一直保持IOIvVvVV下跳到下跳到,到略大于。

再增加,,则同时使由POLOHOIv保持不变。

Ovv不变,将始终保持只有当,则若减小,只要oIV。

其传输特性如图XX_02b跳到所示。

时,才由OH v的变化而改变的。

由以上分析可以看出,迟滞比较器的门限电压是随输出电压o它的灵敏度低一些,但抗干扰能力却大大提高了(此文档部分内容来源于网络,如有侵权请告知删除,文档可自行编辑修改内容,供参考,感谢您的配合和支持)word编辑版.word编辑版.。

滞回比较器电路设计

课程设计说明书课程名称:电子技术课程设计设计题目:滞回比较器电路设计专业:电气工程及其自动化班级:电气1502班*名:***学号: ************ 指导教师:设计时间: 2017年6月19日—2017 年6月30日目录1 . 概述 (1)2 . Multisim单元电路设计、仿真及原理介绍 (1)2.1.电源设计 (1)2.2.滞回比较器 (2)2.3.窗口比较器电压部分 (4)3.2.1窗口比较器 (4)3.2.1窗口比较器的限幅 (5)3.2.1总电路图 (5)3. 仿真测试 (6)4. 设计心得体会 (7)5. 参考文献 (9)6. 附录 (10)1 概述压比较器可以看作是放大倍数接近"无穷大"的运算放大器。

电压比较器的功能:比较两个电压的大小(用输出电压的高或低电平,表示两个输入电压的大小关系): 当"+"输入端电压高于"-"输入端时,电压比较器输出为高电平; 当"+"输入端电压低于"-"输入端时,电压比较器输出为低电平。

电压比较器的作用:它可用作模拟电路和数字电路的接口,还可以用作波形产生和变换电路等。

利用简单电压比较器可将正弦波变为同频率的方波或矩形波。

简单的电压比较器结构简单,灵敏度高,但是抗干扰能力差,因此人们就要对它进行改进。

改进后的电压比较器有:滞回比较器和窗口比较器。

运放,是通过反馈回路和输入回路的确定"运算参数",比如放大倍数,反馈量可以是输出的电流或电压的部分或全部。

而比较器则不需要反馈,直接比较两个输入端的量,如果同相输入大于反相,则输出高电平,否则输出低电平。

电压比较器输入是线性量,而输出是开关(高低电平)量。

一般应用中,有时也可以用线性运算放大器,在不加负反馈的情况下,构成电压比较器来使用。

可用作电压比较器的芯片:所有的运算放大器。

常见的有LM324 LM358 uA741 TL081\2\3\4 OP07 OP27,这些都可以做成电压比较器(不加负反馈)。

具有带隙结构的迟滞比较器电路设计

具有带隙结构的迟滞比较器电路设计摘要:基于LED驱动的微功耗DC—DC转换器,针时低压高稳定性的要求设计了一款具有带隙结构的迟滞比较器电路,它的最低输入电压为1.2 V,其核心电路有带隙基准比较器、射极跟随器和迟滞比较嚣。

整个电路采用Bipolar工艺设计,利用HSpice软件对所设计的电路进行了仿真与验证。

结果表明,迟滞比较器的迟滞电压为8 mV,翻转门限电压随输入电压和温度的变化均很小。

关键词:DC—DC转换器;带隙基准;迟滞比较器;Bipolar在大多数的便携式产品中,它的显示器几乎都采用LCD,LCD本身不能独立发光,必须要有背光源才能发光,因此LED驱动变得越来越重要。

在便携式产品中,它的电源几乎都采用电池供电,电池有镍镉、镍氢、锂离子和碱性电池,镍镉、镍氢、碱性电池的工作电压是1.2V,锂离子工作电压是3.6 V或3.7 V。

要驱动串联的几颗LED。

上述的几种电源均不能满足要求,所以必须采用升压型的DC—DC驱动LED。

本电路没有设计单一的基准源模块。

这是因为它的最低输入电压为1.2 V。

如果采用基准源模块的设计方法,要获得一个与温度和电源电压无关的基准源,整个电路的输入电压基本上要超过2 V,不满足设计要求。

因此,采用一个自身具有恒定翻转门限的迟滞比较器,实现了基准源和使能比较器的功能。

1 电路设计1.1 电路功能迟滞比较器的功能是将反馈电压VFB与内部的门限电压相比较,控制其他模块是否正常工作。

当反馈电压VFB比内部上门限电压高时,迟滞比较器的输出将使其他模块不工作;当反馈电压VFB比内部下门限电压高时,迟滞比较器的输出使其他模块正常工作。

1.2 具有带隙结构迟滞比较器的电路原理带隙基准迟滞比较器由3部分构成(见图1),带隙基准比较器、射随器和迟滞比较器。

工作原理为:输入端与内部的基准门限电压进行比较,当输入端电压超过内部基准门限时,Q12集电极中没有电流流过,即输出电流IOUT为0;当输入端电压低于较低门限时,Q12集电极中有电流流过,即有IOUT流过,从而实现了输出电流IOUT的迟滞控制。

迟滞比较器的工作原理

迟滞比较器的工作原理

迟滞比较器是一种电子装置,用于检测输入信号是否在某个预设范围内,并根据预设的上下阈值产生输出信号。

它通过引入一个迟滞(hysteresis)反馈回路来实现。

迟滞比较器的基本原理如下:首先,将输入信号与上阈值(高电压)和下阈值(低电压)进行比较。

如果输入信号超过上阈值,输出信号将转换为高电平;如果输入信号低于下阈值,输出信号将转换为低电平。

然而,在输入信号在阈值范围内变化时,输出信号不会立即翻转。

当输入信号超过上阈值时,输出信号保持为高电平,直到输入信号下降到下阈值以下才会翻转为低电平。

同样地,当输入信号低于下阈值时,输出信号保持为低电平,直到输入信号上升到上阈值以上才会翻转为高电平。

这种迟滞作用使得输出信号在阈值范围内具有较好的稳定性,可以有效抑制输入信号的噪声和干扰。

迟滞比较器通常由一个比较器和一个反馈网络组成。

比较器是一个电路块,用于实现输入信号与阈值的比较;反馈网络则是为了产生迟滞效应。

反馈网络一般由正反馈网络和负反馈网络构成,通过调整反馈增益可以改变迟滞的大小。

迟滞比较器的应用领域广泛,包括电源管理、模拟信号处理、传感器接口等。

它可以用于电压检测、电流限制、信号判断等功能,提供稳定可靠的输出。

迟滞比较器运算

迟滞比较器运算

滞回比较器又称迟滞比较器,是一个具有迟滞回环传输特性的比较器。

它的运算过程相对复杂,下面以一个实例进行说明:

假设要设计一个电池欠压保护电路,该电路使用双阈值迟滞比较器,以18.5V作为低阈值电压,高阈值电压在18.5V到24V之间,即选择21V作为高阈值电压。

首先,确定比较器的负输入端。

通过两个分压电阻进行分压,这两个分压电阻的取值既不能过大也不能过小。

电池的阈值设置为18.5V到21V,而电池标称电压值为24V,最大值为29V,综合考虑后选择在21V时保证流过分压电阻的电流为1mA左右。

因此,选择R1=20K,R6=1K。

其次,计算阈值电压变化时U1的值。

当BATT=18.5V时,U1=18.5乘以R6/R1+R6=0.88V;当BATT=21.0V时,U1=21.0乘以

R6/R1+R6=1V。

然后,计算比较器输出高电平和低电平时的等效电路。

当U1=0.88V 时,比较器输出低电平,忽略R3、R4支路,此时电源电压为5V,保持电路1mA电流,可确定R5+R2等于5K上下,选择R5=1K,

R2=4K。

最后,确定R3的阻值。

通过以上步骤,就可以完成双阈值迟滞比较器的运算。

需要注意的是,上述示例仅为基本原理,实际运算过程中还需要考虑许多因素,如输入信号的频率、噪声、比较器的响应时间等。

迟滞比较器电路

迟滞比较器电路

迟滞比较器电路是一种常见的电路,可用于比较两个信号的大小。

它通常用于控制系统,如电路自动稳定,控制器,数模转换器,等等。

它的作用是把两个输入信号作比较,然后根据比较结果产生一个输出信号。

迟滞比较器电路的基本原理是:在一个迟滞比较器电路中,有一对信号输入端口,输入端口中有一个参考端口和一个差分端口。

当差分端口的输入信号大于参考端口的输入信号时,输出端口会产生高电平的输出信号,也就是逻辑“1”的输出信号;当差分端口的输入信

号小于参考端口的输入信号时,输出端口会产生低电平的输出信号,也就是逻辑“0”的输出信号。

迟滞比较器电路的结构可以简单地分为三个主要部分:一个可调阈值放大器,一个滞回环,以及一个求和环路。

在可调阈值放大器中,可调舵节可以改变迟滞比较器电路的阈值大小。

滞回环路用于抑制非线性,以防止在进行比较时出现抖动,从而保证输出信号的精确性。

最后,求和环路用于将输入信号运算与可调舵节的阈值运算进行比较,从而产生高电平或低电平的输出信号。

迟滞比较器电路的使用非常广泛,它可以提供许多系统的精确控制。

例如:用于调节功率脉冲宽度来实现转换效率的最大化;用于实现低压-低功率电源的完备无比的输出;用于控制传感器的容量测量;用于提高数模转换器的测量精度;等等。

总之,迟滞比较器电路是一种非常重要的电路,可用于提供多种

电路控制和测量功能。

它具有低成本、稳定性强、可靠性高等优势,可以有效地控制和管理各种控制系统和电路的运行。

cmos电压迟滞比较器电路

cmos电压迟滞比较器电路摘要:一、引言二、CMOS 电压迟滞比较器电路的工作原理1.基本结构2.工作原理三、CMOS 电压迟滞比较器电路的特性1.输入电压范围2.输出电压3.灵敏度四、CMOS 电压迟滞比较器电路的应用1.电源监控电路2.窗口比较器五、CMOS 电压迟滞比较器电路的设计1.设计步骤2.设计实例六、总结正文:一、引言CMOS 电压迟滞比较器电路是一种广泛应用于电子设备中的电路,具有较高的性能和较低的功耗。

本篇文章将详细介绍CMOS 电压迟滞比较器电路的工作原理、特性、应用以及设计方法。

二、CMOS 电压迟滞比较器电路的工作原理1.基本结构CMOS 电压迟滞比较器电路主要由NMOS 和PMOS 晶体管组成。

其中,NMOS 晶体管作为负载,PMOS 晶体管作为传输门。

此外,还有一个参考电压源用于提供基准电压。

2.工作原理当输入电压高于基准电压时,PMOS 晶体管导通,使得NMOS 晶体管的导通电阻减小,从而使得输出电压上升;反之,当输入电压低于基准电压时,PMOS 晶体管截止,使得NMOS 晶体管的导通电阻增大,从而使得输出电压下降。

三、CMOS 电压迟滞比较器电路的特性1.输入电压范围CMOS 电压迟滞比较器电路的输入电压范围较宽,可以满足不同应用场景的需求。

2.输出电压CMOS 电压迟滞比较器电路的输出电压具有较高的分辨率,可以实现较高的比较精度。

3.灵敏度CMOS 电压迟滞比较器电路的灵敏度较高,可以实现对输入电压的快速响应。

四、CMOS 电压迟滞比较器电路的应用1.电源监控电路CMOS 电压迟滞比较器电路可以用于监控电源电压,当电源电压发生波动时,通过控制相应的电路开关实现对电源电压的稳定。

2.窗口比较器CMOS 电压迟滞比较器电路可以应用于窗口比较器,实现对输入信号的波形检波和幅度比较。

五、CMOS 电压迟滞比较器电路的设计1.设计步骤CMOS 电压迟滞比较器电路的设计主要包括确定电路结构、选择合适的元件参数以及进行仿真验证等步骤。

LM339设计的迟滞比较器电路

LM339 设计的迟滞比较器电路LM339 设计的迟滞比较器电路

迟滞比较器又可理解为加正反馈的单限比较器。

前面介绍的单限比较器,如果输入信号Uin 在门限值附近有微小的干扰,则输出电压就会产生相应的抖动(起伏)。

在电路中引入正反馈可以克服这一缺点。

图a 给出了一个迟滞比较器,人们所熟悉的“史密特”电路即是有迟滞的比较器。

图b 为迟滞比较器的传输特性。

当输出状态一旦转换后,只要在跳变电压值附近的干扰不超过ΔU之值,输出电压的值就将是稳定的。

但随之而来的是分辨率降低。

因为对迟滞比较器来说,它不能分辨差别小于ΔU的两个输入电压值。

迟滞比较器加有正反馈可以加快比较器的响应速度,这是它的一个优点。

除此之外,由于迟滞比较器加的正反馈很强,远比电路中的寄生耦合强得多,故迟滞比较器还可免除由于电路寄生耦合而产生的自激振荡。

如果需要将一个跳变点固定在某一个参考电压值上,可在正反馈电路中接入一个非线性元件,如晶体二极管,利用二极管的单向导电性,便可实现上述要求。

如图为其原理图。

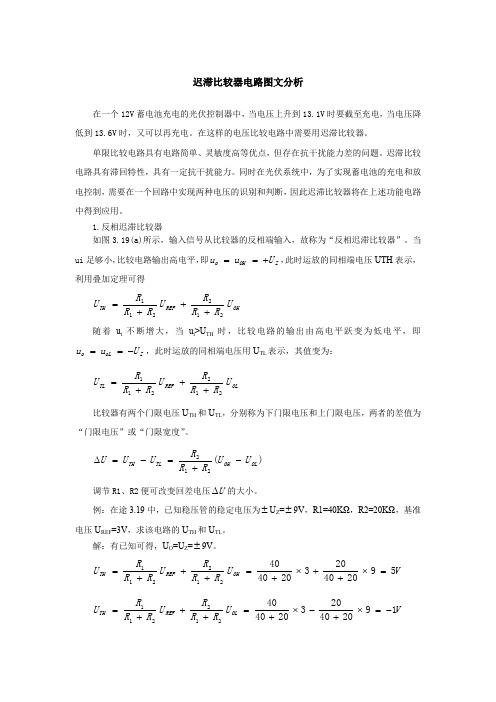

迟滞比较器电路图文分析

迟滞比较器电路图文分析在一个12V 蓄电池充电的光伏控制器中,当电压上升到13.1V 时要截至充电,当电压降低到13.6V 时,又可以再充电。

在这样的电压比较电路中需要用迟滞比较器。

单限比较电路具有电路简单、灵敏度高等优点,但存在抗干扰能力差的问题。

迟滞比较电路具有滞回特性,具有一定抗干扰能力。

同时在光伏系统中,为了实现蓄电池的充电和放电控制,需要在一个回路中实现两种电压的识别和判断,因此迟滞比较器将在上述功能电路中得到应用。

1.反相迟滞比较器如图3.19(a)所示,输入信号从比较器的反相端输入,故称为“反相迟滞比较器”。

当ui 足够小,比较电路输出高电平,即Z OH o U u u +==,此时运放的同相端电压UTH 表示,利用叠加定理可得OH REF TH U R R R U R R R U 212211+++=随着u i 不断增大,当u i >U TH 时,比较电路的输出由高电平跃变为低电平,即Z oL o U u u -==,此时运放的同相端电压用U TL 表示,其值变为:OL REF TL U R R R U R R R U 212211+++=比较器有两个门限电压U TH 和U TL ,分别称为下门限电压和上门限电压,两者的差值为“门限电压”或“门限宽度”。

)(212OL OH TL TH U U R R R U U U -+=-=∆调节R1、R2便可改变回差电压U ∆的大小。

例:在途3.19中,已知稳压管的稳定电压为±U Z =±9V ,R1=40K Ω,R2=20K Ω,基准电压U REF =3V ,求该电路的U TH 和U TL 。

解:有已知可得,U O =U Z =±9V 。

V U R R R U R R R U OH REF TH 592040203204040212211=⨯++⨯+=+++= V U R R R U R R R U OL REF TH 192040203204040212211-=⨯+-⨯+=+++=所以,输入电压u i 在增大过程中,当输入u i <+5V 时,输出电压为+9V ;当输入u i >+5V 时,输出电压为-9V ;输入电压u i 在减小过程中,当输入u i >-1V 时,输出电压为-9V ;当输入u i <-1V 时,输出电压为+9V 。

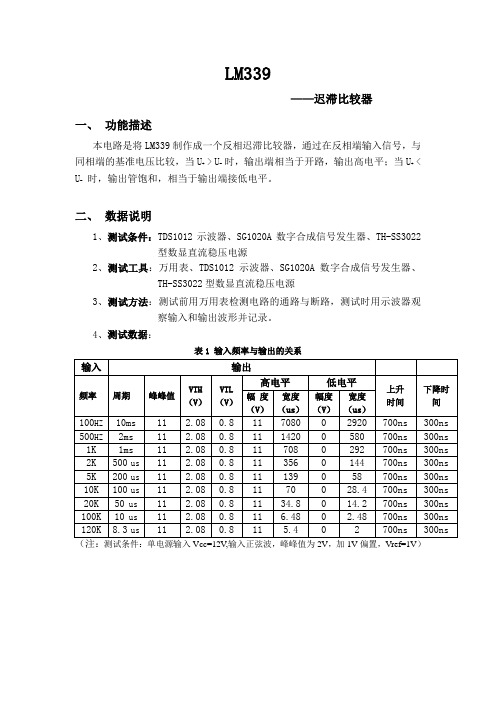

LM339--迟滞比较器

LM339——迟滞比较器一、功能描述本电路是将LM339制作成一个反相迟滞比较器,通过在反相端输入信号,与同相端的基准电压比较,当U+> U-时,输出端相当于开路,输出高电平;当U+<U-时,输出管饱和,相当于输出端接低电平。

二、数据说明1、测试条件:TDS1012示波器、SG1020A数字合成信号发生器、TH-SS3022型数显直流稳压电源2、测试工具:万用表、TDS1012示波器、SG1020A数字合成信号发生器、TH-SS3022型数显直流稳压电源3、测试方法:测试前用万用表检测电路的通路与断路,测试时用示波器观察输入和输出波形并记录。

4、测试数据:表1 输入频率与输出的关系测试条件:单电源输入Vcc=12V,输入正弦波,峰峰值为2V,加1V偏置,Vref=1V)图1 输入频率与输出的关系表2 输入电压与输出的关系测试条件:单电源输入Vcc=12V,输入正弦波,频率为5K,Vref=1V)5、结果分析:迟滞比较器中加入正反馈可以克服输出端的抖动,所以在输入电压幅值增加时,输出端的幅值没有发生任何改变。

输出电压的幅值不会随频率的改变而改变,但是保持高低电平的时间高度随着频率的增大而减小,并且波形随频率的增大开始产生失真,在我们的测量中,最大可以达到210KHZ。

同时从上面的数据可以看出,上升时间总是大于下降时间。

三、芯片介绍1、芯片特点:内部装有四个独立的电压比较器,工作电源电压范围宽,单电源、双电源均可工作(单电源: 2~36V ,双电源:±1~±18V );消耗电流小,I CC =1.3mA;输入失调电压小,V IO =±2mV ; 共模输入电压范围宽, Vic=0~Vcc-1.5V;输出与TTL ,DTL ,MOS ,CMOS 等兼容; 输出可以用开路集电极连接“或”门.2、芯片用途:满足比较器的基本用途,可以用作单限比较器,迟滞比较器,窗口比较器等,用来比较电压,用得最多的是在电磁炉中,做过压过热保护。

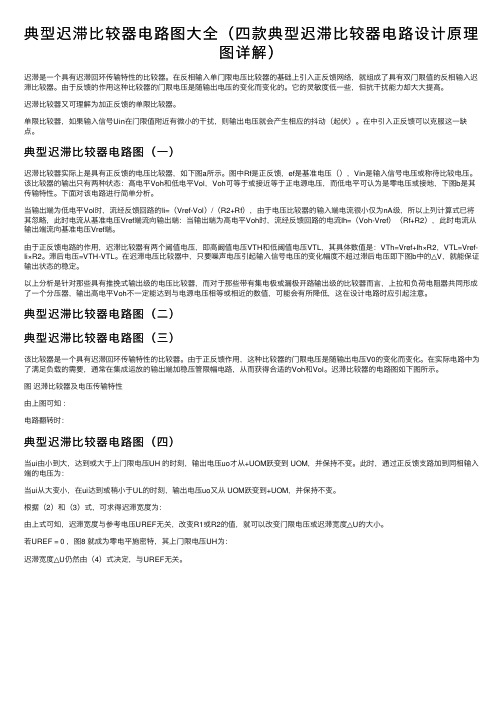

典型迟滞比较器电路图大全(四款典型迟滞比较器电路设计原理图详解)

典型迟滞⽐较器电路图⼤全(四款典型迟滞⽐较器电路设计原理图详解)迟滞是⼀个具有迟滞回环传输特性的⽐较器。

在反相输⼊单门限电压⽐较器的基础上引⼊正反馈⽹络,就组成了具有双门限值的反相输⼊迟滞⽐较器。

由于反馈的作⽤这种⽐较器的门限电压是随输出电压的变化⽽变化的。

它的灵敏度低⼀些,但抗⼲扰能⼒却⼤⼤提⾼。

迟滞⽐较器⼜可理解为加正反馈的单限⽐较器。

单限⽐较器,如果输⼊信号Uin在门限值附近有微⼩的⼲扰,则输出电压就会产⽣相应的抖动(起伏)。

在中引⼊正反馈可以克服这⼀缺点。

典型迟滞⽐较器电路图(⼀)迟滞⽐较器实际上是具有正反馈的电压⽐较器,如下图a所⽰。

图中Rf是正反馈,ef是基准电压(),Vin是输⼊信号电压或称待⽐较电压。

该⽐较器的输出只有两种状态:⾼电平Voh和低电平Vol,Voh可等于或接近等于正电源电压,⽽低电平可认为是零电压或接地,下图b是其传输特性。

下⾯对该电路进⾏简单分析。

当输出端为低电平Vol时,流经反馈回路的Ii=(Vref-Vol)/(R2+Rf),由于电压⽐较器的输⼊端电流很⼩仅为nA级,所以上列计算式已将其忽略,此时电流从基准电压Vref端流向输出端:当输出端为⾼电平Voh时,流经反馈回路的电流Ih=(Voh-Vref)(Rf+R2),此时电流从输出端流向基准电压Vref端。

由于正反馈电路的作⽤,迟滞⽐较器有两个阈值电压,即⾼阚值电压VTH和低阈值电压VTL,其具体数值是:VTh=Vref+Ih×R2,VTL=Vref-Ii×R2。

滞后电压=VTH-VTL。

在迟滞电压⽐较器中,只要噪声电压引起输⼊信号电压的变化幅度不超过滞后电压即下图b中的△V,就能保证输出状态的稳定。

以上分析是针对那些具有推挽式输出级的电压⽐较器,⽽对于那些带有集电极或漏极开路输出级的⽐较器⽽⾔,上拉和负荷电阻器共同形成了⼀个分压器,输出⾼电平Voh不⼀定能达到与电源电压相等或相近的数值,可能会有所降低,这在设计电路时应引起注意。

cmos电压迟滞比较器电路

cmos电压迟滞比较器电路【一、CMOS电压迟滞比较器电路简介】CMOS电压迟滞比较器电路是一种采用互补金属氧化物半导体(CMOS)技术实现的比较器电路。

它在电子设备中有着广泛的应用,如在模拟信号处理、数字信号处理、电源管理等领域。

CMOS电压迟滞比较器电路具有低功耗、高噪声抑制比、宽电源电压范围等优点。

【二、CMOS电压迟滞比较器电路工作原理】CMOS电压迟滞比较器电路的工作原理是通过比较两个输入电压的大小,输出一个代表比较结果的信号。

它主要由输入端、输出端和迟滞环节组成。

当输入端电压变化时,迟滞环节会延迟输出端的响应,使得输出信号具有迟滞特性。

这种特性可以有效地抑制噪声,提高电路的稳定性。

【三、CMOS电压迟滞比较器电路应用】CMOS电压迟滞比较器电路的应用十分广泛,主要包括以下几个方面:1.模拟信号处理:在模拟信号处理系统中,CMOS电压迟滞比较器电路可以用于电压比较、波形整形等功能。

2.数字信号处理:在数字信号处理领域,CMOS电压迟滞比较器电路常用于触发器、寄存器等电路的设计。

3.电源管理:CMOS电压迟滞比较器电路在电源管理领域具有很高的实用价值,可以用于电压监控、电池充电控制等功能。

【四、CMOS电压迟滞比较器电路设计要点】设计CMOS电压迟滞比较器电路时,应注意以下几个要点:1.电源电压选择:应根据实际应用场景选择合适的电源电压,以满足电路的性能要求和降低功耗。

2.输入端电阻匹配:为减小输入端电流对比较器性能的影响,应合理选择输入端电阻。

3.输出端驱动能力:根据负载电流大小,选择具有合适驱动能力的比较器电路。

4.迟滞特性调整:通过合理设计迟滞环节,调整比较器的迟滞特性,以满足实际应用需求。

【五、总结】CMOS电压迟滞比较器电路作为一种重要的比较器电路,在电子设备中具有广泛的应用。

了解其工作原理、应用场景以及设计要点,有助于更好地发挥其在实际工程中的优势。

反相迟滞比较器课件

当输入信号发生变化时,反相迟滞比较器的输出状态将发生翻转,并且存在一 个阈值范围,当输入信号回到该范围时,输出状态将保持不变,从而实现抗干 扰功能。

电路组成与结构

电路组成

反相迟滞比较器主要由运算放大器、 电阻和电容等元件组成。

结构

反相迟滞比较器的电路结构通常包括 正反馈和负反馈两个回路,其中正反 馈回路用于实现输出状态的翻转,负 反馈回路用于调整阈值范围。

测试信号生成

生成各种类型的测试信号 ,如正弦波、方波、三角 波等,以全面评估比较器 的性能。

噪声与干扰

在测试信号中加入噪声和 干扰,模拟实际应用中的 复杂环境条件。

性能指标的测试与评估

01

02

03

04

迟滞特性

测量比较器的迟滞特性,即输 入信号在阈值电压上下变化时

,输出信号的翻转范围。

精度与线性度

评估比较器的精度和线性度, 确保其在实际应用中的准确性

当输入信号达到阈值时,正反 馈和负反馈回路的平衡被打破 ,输出信号发生跳变,由于集 成电路工艺的特点,这种跳变 幅度较大且速度快,从而实现 迟滞比较功能。

05

反相迟滞比较器的调试与 测试

调试方法与步骤

输入信号调整

确保输入信号的幅度和频率满 足比较器的要求,调整信号源 或衰减器以获得适当的输入信

号。

在控制系统中的应用

反馈控制

反相迟滞比较器可以用于构成反 馈控制系统,通过比较实际输出 与预设值的差异,调整系统的输 入或参数,实现系统的自动控制

。

调节器

利用反相迟滞比较器可以设计出 各种调节器,如比例调节器、积 分调节器和微分调节器等,用于

控制系统的参数调节和优化。

动态跟踪

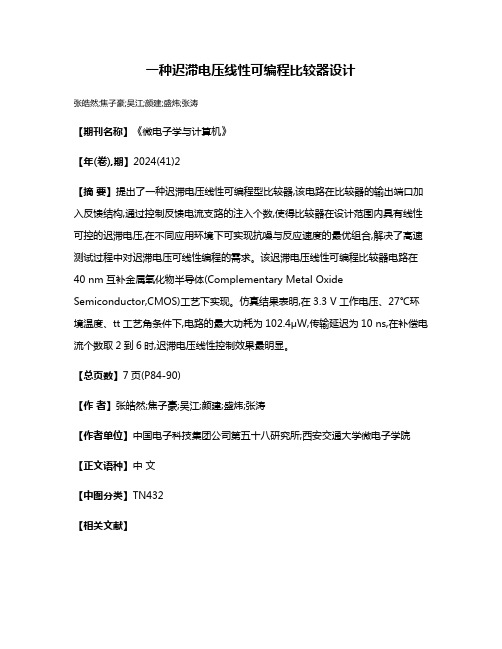

一种迟滞电压线性可编程比较器设计

一种迟滞电压线性可编程比较器设计

张皓然;焦子豪;吴江;颜建;盛炜;张涛

【期刊名称】《微电子学与计算机》

【年(卷),期】2024(41)2

【摘要】提出了一种迟滞电压线性可编程型比较器,该电路在比较器的输出端口加入反馈结构,通过控制反馈电流支路的注入个数,使得比较器在设计范围内具有线性可控的迟滞电压,在不同应用环境下可实现抗噪与反应速度的最优组合,解决了高速测试过程中对迟滞电压可线性编程的需求。

该迟滞电压线性可编程比较器电路在40 nm互补金属氧化物半导体(Complementary Metal Oxide Semiconductor,CMOS)工艺下实现。

仿真结果表明,在3.3 V工作电压、27℃环境温度、tt工艺角条件下,电路的最大功耗为102.4μW,传输延迟为10 ns,在补偿电流个数取2到6时,迟滞电压线性控制效果最明显。

【总页数】7页(P84-90)

【作者】张皓然;焦子豪;吴江;颜建;盛炜;张涛

【作者单位】中国电子科技集团公司第五十八研究所;西安交通大学微电子学院【正文语种】中文

【中图分类】TN432

【相关文献】

1.基于迟滞电压比较器的冰箱自动除霜电路研究

2.一种高速低功耗迟滞CMOS比较器的分析与设计

3.一种自适应迟滞性比较器的设计

4.一种新颖的低阈值迟滞比较器的设计及应用

5.一种应用于CAN收发器的宽输入范围的迟滞比较器设计

因版权原因,仅展示原文概要,查看原文内容请购买。

一种自适应迟滞性比较器的设计

一种自适应迟滞性比较器的设计

刘晓巍;张红南

【期刊名称】《现代电子技术》

【年(卷),期】2006(29)4

【摘要】设计了一种由滤波器和迟滞比较器构成的传输频率信号电路.设计使用滤波器将输入信号改变适当的相位作为迟滞比较器标准端的信号,而原信号输入比较器的另一端.那么由于迟滞比较器标准端的电压同时随输入信号改变.电路对不同的信号有一定的适应能力.即对不同的输入信号,不需要另外确定标准端的电压.简化了电路,提高了可靠性.同时滤波器的加入使电路同时获得频率选择的能力.仿真证明了电路的可行性.

【总页数】3页(P6-8)

【作者】刘晓巍;张红南

【作者单位】湖南大学,湖南,长沙,410082;湖南大学,湖南,长沙,410082

【正文语种】中文

【中图分类】TN702

【相关文献】

1.一种高速低功耗迟滞CMOS比较器的分析与设计 [J], 李辛毅;姚素英;赵毅强

2.一种基于迟滞比较器的锯齿波产生电路 [J], 魏荷坪;孙江;陈向东

3.一种新颖的低阈值迟滞比较器的设计及应用 [J], 郭晓锋;成俊;江喜平;王正文;王春娟

4.一种带有迟滞比较器的新型RC振荡器 [J], 王洪祥;赵野;黑勇

5.一种应用于CAN收发器的宽输入范围的迟滞比较器设计 [J], 冯世勤;冯全源因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一种自适应迟滞性比较器的设计

关键词:迟滞电路,比较器

摘要:设计了一种由滤波器和迟滞比较器构成的传输频率信号电路。

设计使用滤波器将输入信号改变适当的相位作为迟滞比较器标准端的信号,而原信号输入比较器的另一端。

那么由于迟滞比较器的电压同时随输入信号改变。

迟滞电路(hysteresis circuit)又称施密特触发电路(schmitt trigger circuit)。

因他能滤除干扰噪声而获得很广泛的运用。

在一些应用场合中,特别在某些模/数转换电路中[1],迟滞比较器作为抗干扰的比较器应用较多。

为了获得更好的转换效果,需要较好地选择迟滞比较器正端输入的基准电压。

而信号的未知为确定基准电压带来麻烦。

本文设计的一种加入滤波器的迟滞比较器解决了这个问题。

1 迟滞比较器的设计

迟滞性是比较器的一种特性,他使比较器的输入阈值随输入(出)电平而改变。

比较器实现的方法很多。

他们都有不同形式的正反馈。

最常见的即是由放大器接成正反馈组成。

这类迟滞比较器由于方便的设计和放大器的标准生产成为主流。

设计选用了最常见的由放大器正反馈的设计,如图1所示。

由米尔曼公式可得输入电压升高和降低时的基准电压如下式:

而电路能滤掉的噪声即迟滞性为:

由上式可知,迟滞性由电源电压和R4,R5阻值决定。

本设计中V r的大小是变成的,因此正负基准电压也随V r变化,为了达到自适应的目的希望基准电压对输入有好的跟随性同时减小输出端的影响。

因此将R4取值得比R5要小一个数量级。

2 滤波器的设计

设计滤波器往往要考虑下列因素:

(1)工作频率范围。

(2)参数变化的灵敏度及稳定度。

(3)实际元件的重量和大小。

(4)运算放大器的电压源。

2.1 滤波器的选择[2]

本设计是工作在低频的比较器。

此时当信号频率是低频时可以考虑的方式有低通、带通或全通,同时还可选择一阶或多阶。

在考虑此设计后,一阶滤波器在此设计中是较好的,且低通

滤波器是相对比较简单的,所以设计选择低通滤波器。

简单低通滤波器通常可由电容与电阻组成。

本设计采用了电容与电阻并联接地的方式,最后的滤波器连同迟滞比较器设计如图2所示。

2.2 元件值的确定[3]

一阶的滤波器有公用的传输函数:

其中Z是T(S)的零点,P是极点,在S平面上,Z可能落在正实轴或负实轴上,而P永远落在负实轴上。

其中K为正数时由函数T(S)的相位公式得:

由图2得其传输函数标准形式为:

则:

对于S,当S=jω=0时:

当S=jω趋向无穷大∞时:

由上式可知,电阻值可按设计的要求大概约束,如果需要其是低通滤波器则有关系式:

当上式成立时,滤波器为低通。

当R为正实数时与上式等价。

同时需要S=0时|T(S)|接近1为约束条件。

由以上条件可知R1的电阻最大,R3的电阻与其有可比性。

在此取R1=10R3,R2的电阻比其低几个数量级。

下面进行相位约束条件的探讨:

将S=jω代入式(2)中有:

计算相位的公式如下:

由式(6)结合式(1)可得:

要此电路在1 rad/s为处有45°的相位落差即要求:

则有:

而结合式(3),(4),(5),因为R1=10R3,R2的电阻比其低几个数量级,则有:

两式联立求解并取C=1,可得:

根本式(7):当一个方程有两个未知数,可取得的某一个为定值。

如果计算后是合理值,便能解决问题。

选择P=0.005,由式(7)得Z=1,则:

从以上的结果可以找出元件值[3]。

由于C new= ,R new=k m R old,根据实际电路中元件值的需要,如果按k f=1来设计很难与实际电容大小匹配。

在此令k f=1 000,k m=420。

得电路元件的实际值为:R1=840kΩ,R3=84kΩ,R2=420Ω,C=2.34μF。

再将C的值标准化为2.2μF。

对R4选择值为R3的1/10,即8.4kΩ,R5则确定为R4的20倍为170kΩ。

3 仿真和讨论

仿真在HSpice[5]下进行,设定其电源电压为2.3V,输入信号选择正弦信号。

用HSpice的表示方法[6]为sin(1.2V 0.45V 1Hz)即直流偏置为1.2V,幅值为0.45V,频率为1Hz。

其仿真波形如图3所示。

图3(a)即是输入电压随时间变化的波形,图3(b)中虚线为比较器正端的电压,其相位与输入电压相同,在波谷由于输出端反馈而畸变;实线表征比较器负端电压,相位超前,完成预先设计。

则图3(c)中可见符合输入信号的方波输出。

多种信号的输入测试表明,电路的适应性较好,能在多个不同偏置条件的输入下工作。

经过电路仿真有以下结论:

(1)此电路有较好的适应性,能在不同的偏置条件的输入下工作。

(2)由于低通滤波器的原因,电路具有频率选择的功能。

(3)迟滞比较器提高了抗干扰能力,可将此电路形式推广。

如果滤波器是高通的,则可用在较高频率中。

对滤波器的形式也可多加选取。

只要使两端的信号产生相位差,电路的比较功能就能实现。