第7章 触发器

脉冲信号的产生及波形变换

一、 由门电路构成的多谐振荡器 二、由555定时器构成的多谐振荡器 三、 多谐振荡器的应用

3

第7章 脉冲信号的产生及波形变换

一、 由门电路构成的多谐振荡器

能产生矩形脉冲的自激振荡电路叫做多谐振荡器。

1、RC环形多谐振荡器

G1 ui1 &

G2 ui2 & uo2

R

C

G3 ui3 & RS

uo (ui1)

动翻转的工作过程

0 ui2

t1 t2 t3

t

(uo1)

G1

G2

ui1 & ui2 & uo2

G3 ui3 &

0 uo uo2

t

R

RS

0

t

ui3

C (a) 电路图

UT

t

0

(b) 波形图

在t2时刻,uo2变为低电平,电容C开始通过电阻R放电。随着放 电的进行,ui3逐渐下降。在t3时刻,ui3下降到UT,使uo(ui1)又 由0变为1,第二个暂稳态结束,电路返回到第一个暂稳态,又 开始重复前面的过程。

24

第7章 脉冲信号的产V生DD及波形变换

ui

ui

号

发

生

器

FF1 Q1 FF2

Q2 FF14 Q14 FF15 Q15 分

C1

C1

C1

C1

频

电

f0

f1

f2

f14

f

路

32768Hz 16384Hz 8192Hz 2Hz

1Hz 17

第7章 脉冲信号的产生及波形变换

模拟声响电路

VCC

R1

84

7

第7章 SQL Server 2008高级应用

常用算术函数 幂函数 EXP LOG LOG10 SQRT 取近似值函数 CEILING FLOOR ROUND 符号函数 返回表达式的指数值 返回表达式的自然对数值 返回表达式的以10 为底的对数值 返回表达式的平方根 返回大于等于表达式的最小整数 返回小于等于表达式的最大整数 取整数,小数的第一位四舍五入

DECLARE @MyCounter INT; SET @MyCounter = 1;

字符串串联运算符

加号 (+) 是字符串串联运算符,可以用它将字符串串 联起来。其他所有字符串操作都使用字符串函数进 行处理。

例如'good' + ' ' + 'morning'的结果是'good morning'。

ABS SIGN

其他函数

返回表达式的绝对值 测试参数的正负号,返回0、1或-1 返回值为π,即3.1415926535897936 返回0到1之间的随机浮点数

PI RAND

字符串函数

字符转换函数

ASCII(character_expression) 返回字符表达式最左端字符的ASCII 码值 CHAR (integer_expression) CHAR函数用于将ASCII 码转换为字符 LOWER (character _expression) LOWER函数用于把字符串全部转换为小写

CHECKPOINT

用于将当前工作的数据库中被更改过的数据页或日 志页从数据缓冲器中强制写入硬盘。

DBCC

用于验证数据库完整性、查找错误、分析系统使用 情况等。

DECLARE

DECLARE的语法格式如下: DECLARE {{ @local_variable data_type } | { @cursor_variable_name CURSOR } | { table_type_definition } } [, ...n] DECLARE命令用于声明一个或多个局部变量、游标 变量或表变量。 例:

电子技术基础第7章时序逻辑电路课件

7.2 防止空翻的触发器

7.2.1 主从型JK触发器

3.主从触发器的一次翻转问题 由于主从JK触发器存在“一次变化”问题,在CP脉冲为高电平期间,如果JK端出现 一定宽度的正向干扰。因此,在使用主从JK触发器时,一般要求在CP=1期间,JK的状态 保持不变;若需要改变J、K的状态,应在CP=0期间进行。

2.集成D触发器

D触发器74HC74

7.3 集成触发器

7.3.2 触发器的时间参数

1.最高时钟频率fmax 2.传输延迟时间 3.建立时间tset 4.保持时间th

7.4 二进制计数器 7.4.1 异步二进制计数器

1.异步二进制加法计数器

异步二进制加法计数器原理图

7.4 二进制计数器 7.4.1 异步二进制计数器

7.2 防止空翻的触发器 7.2.2 边沿触发器

2.负边沿JK触发器 (1)电路组成及逻辑符号

负边沿JK触发器

7.2 防止空翻的触发器

7.2.2 边沿触发器 2.负边沿JK触发器 (2)逻辑功能 触发器输出状态的变化发生在CP的下降沿,而次态输出仅取决于CP下降沿到达时到

J、K的状态,时钟的其他时间J、K值都可以变化,因而它的抗干扰能力强。

7.2 防止空翻的触发器 7.2.2 边沿触发器

3.T触发器 把JK触发器的两个输入端J、K接在一起成为一个输入端,并称之为T输入端,就构成 了T触发器

T触发器

7.3 集成触发器 7.3.1 集成触发器的品种和类型

1.集成JK触发器

JK触发器HC76

7.3 集成触发器 7.3.1 集成触发器的品种和类型

4.扭环计数器

扭环计数器

7.5 十进制计数器 7.5.1 同步十进制加法计数器

第七章 时序逻辑电路题库

1.JK触发器可完成:保持、置0、置1、翻转四种功能。

(对)2、JK触发器只有置0、置1两种功能。

(错)3、JK触发器只有保持、翻转两种功能。

(错)4、JK触发器可完成:保持、置0、置1、计数四种功能。

(错)5、RS触发器没有不确定的输出状态。

(错)6、RS触发器有不确定的输出状态。

(对)7、仅具有保持和翻转功能的触发器是RS触发器。

(错)8、仅具有保持和翻转功能的触发器是T触发器。

(对)9、仅具有保持和翻转功能的触发器是T’触发器。

(错)10、仅具有翻转功能的触发器是T’触发器。

(对)11、同步时序逻辑电路中各触发器的时钟脉冲CP是同一个信号。

(对)12、同步时序逻辑电路中各触发器的时钟脉冲CP不是同一个信号。

(错)13、异步时序逻辑电路中各触发器的时钟脉冲CP不是同一个信号。

(对)14、异步时序逻辑电路中各触发器的时钟脉冲CP是同一个信号。

(错)15、触发器在某一时刻的输出状态,不仅取决于当时输入信号的状态,还与电路的原始状态有关。

(对)16、触发器进行复位后,其两个输出端均为0.(错)17、触发器进行复位后,其两个输出端均为1.(错)18、触发器与组合电路两者都没有记忆能力。

(错)19、基本RS触发器要受时钟脉冲的控制。

(错)20、Qn+1表示触发器原来所处的状态,即现态。

(错)21、Qn表示触发器原来所处的状态,即现态。

(对)22、当CP处于下降沿时,触发器的状态一定发生翻转。

(错)23、当CP处于上升沿时,触发器的状态一定发生翻转。

(错)24、所谓单稳态触发器,只有一个稳定状态,而不具有其他的状态。

(错)25、JK触发器能够克服RS触发器存在的缺点。

(对)26、寄存器具有记忆功能,可用于暂存数据。

(对)27、74LS194可执行左移、右移、保持等几种功能。

(对)28、在异步计数器中,当时钟脉冲到达时,各触发器的翻转是同时发生的。

(错)29、可逆计数器既能作加法计数,又能作减法计数。

(对)30、 计数器计数前不需要先清零。

数字逻辑-第7章-736

电平异步时序逻辑电路

由图7 -14所示的结构模型及相应方程组可知,它具有如下特点: ➢ 电路输出和状态的改变是由输入电位的变化直接引起的,由于电平异步时 序逻辑电路可以及时地对输入信号的变化作出响应,所以工作速度较高。

➢ 电路的二次状态和激励状态仅相差一个时间延迟。即二次状态y是激励 状态Y经过Δt延迟后的“重现”,因此,y被命名为二次状态。当输入信号不 变时,激励状态与二次状态相同,即y= Y,此时电路处于稳定状态。

电平异步时序逻辑电路的分析

二、电平异步逻辑电路的分析

电平异步时序逻辑电路的分析过程的一般步骤如下: ① 根据逻辑电路图写出输出函数和激励函数表达式; ② 作出流程表; ③ 作出总态图或时间图; ④ 说明电路逻辑功能。

➢ 功能分析: 由状态图和时间图可知,该电路是一个模4加1计数器, 当

收到第 四个输入脉冲时,电路产生一个进位输出脉冲。

脉冲异步时序逻辑电路的分析

例7-2 分析图7-5所示脉冲异步时序逻辑电路

解:该电路的存储电路部分由两个 与非门构成的基本R- S触发器组成。 电路有3个输入端x1、x2和x3 ,一个 输出端Z,输出Z是状态变量的函数, 属于Moore型脉冲异步时序电路。

脉冲异步时序逻辑电路的分析

3)作出状态表和状态图

根据表7 -1所示次态真值表和输出函数 表达式可作出该电路的状态表 如右表7 -2所示

状态图 如下图7-3所示

脉冲异步时序逻辑电路的分析

3)画出时间图并说明电路逻辑功能

➢ 为了进一步描述该电路在输入脉冲作用下的状态和 输出变化 过程,可根据状态表或状态图画出该电路的时间图如图7 -4所 示。

电平异步时序逻辑电路

2.输入信号的约束

考虑到电平异步时序电路输入信号的变化将直接引起输入和状态的变化, 为了保证电路可靠地工作,对输入信号有如下两条约束:

触发器获奖课件

END IF; END trigger_emp;

❖ SQL> UPDATE employees SET salary=1000;

12

7.2.2 语句级触发器

❖ 使用触发器谓词

假如触发器响应多种DML事件,而且需要根据事 件旳不同进行不同旳操作,则能够在触发器体中 使用谓词判断是哪个触发事件触动了触发器。

❖ 【例7-6】创建一种带限制条件旳UPDATE 触发器,修改雇员旳工资时,只输出80号部 门雇员修改前工资旳值与改后旳工资旳值。

❖ 见书94页【例7-6】

22

7.2.3 行级触发器

❖ 【 例 7-7】 创 建 一 种 行 级 触 发 器 , 当 向 departments表中插入数据时,将插入后旳 值 写 入 到 deptlog 日 志 表 中 , 当 删 除 departments数据时,将被删除前旳值写入 到日志表中,当对departments表中某一列 进行更新时,将更新前和更新后旳值写入到 日志表中。

17

7.2.3 行级触发器

❖ 【例7-4】创建一种行级旳DELETE触发器。 CREATE OR REPLACE TRIGGER tg_delete AFTER DELETE ON departments FOR EACH ROW BEGIN DBMS_OUTPUT.PUT_LINE (‘您执行了删除操作…’); END tg_delete;

❖ SQL> INSERT INTO departments VALUES(220,‘edu’,103,2500);

11

7.2.2 语句级触发器

❖ 【例7-2】创建一种 BEFORE型语句级触发器。禁止周六、周 日对employees表进行DML操作,假如在周六、周日对 employees表进行了任何操作,则中断操作,并提醒顾客不允 许在此时间对employees表进行操作。

第07章存储过程和触发器

山东工商学院

陈章良

7.1.2 用户存储过程的创建与执行

(2)存储过程的执行 语 法 格 式

[ EXEC [ UTE ] ] { [ @return_status = ] { procedure_name [ ;number ] | @procedure_name_var } [ [ @parameter = ] { value | @variable [ OUTPUT ] | [ DEFAULT ] } [ ,...n ] [ WITH RECOMPILE ] }

山东工商学院

陈章良

7.1.4 用户存储过程的删除

语法格式

DROP PROCEDURE { procedure } [ ,...n ]

【例7.10】删除 PXSCJ数据库中的student_info1 存储过程。 USE PXSCJ GO DROP PROCEDURE student_info1

山东工商学院

CREATE PROCEDURE student_info AS SELECT a.xh,xm,kcm,cj,xf FROM XSB a JOIN CJB b ON a.xh=b.xh JOIN KCB t ON b.kch= t.kch GO

山东工商学院

陈章良

7.1.2 用户存储过程的创建与执行

3) 使用带OUTPUT参数的存储过程

山东工商学院

陈章良

7.1.2 用户存储过程的创建与执行

(3)举例 1) 设计简单的存储过程

【例7.1】从XSCJ USE PXSCJ 数据库的三个表中查 /*检查是否已存在同名的存储过程,若有,删除*/ 询,返回学生学号、 IF EXISTS (SELECT name FROM sysobjects WHERE name = 'student_info' AND type='P') 姓名、课程名、成绩、 DROP PROCEDURE student_info 学分。该存储过程不 GO 使用任何参数。 /*创建存储过程*/

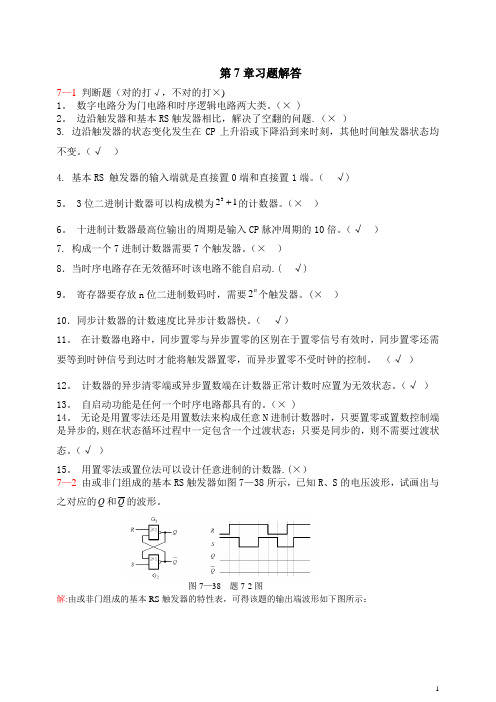

第7章习题详细解答

第7章习题解答7—1判断题(对的打√,不对的打×)1。

数字电路分为门电路和时序逻辑电路两大类。

(× )2。

边沿触发器和基本RS触发器相比,解决了空翻的问题.(×)3. 边沿触发器的状态变化发生在CP上升沿或下降沿到来时刻,其他时间触发器状态均不变。

(√)4. 基本RS 触发器的输入端就是直接置0端和直接置1端。

(√)23 的计数器。

(×)5。

3位二进制计数器可以构成模为16。

十进制计数器最高位输出的周期是输入CP脉冲周期的10倍。

(√)7. 构成一个7进制计数器需要7个触发器。

(×)8.当时序电路存在无效循环时该电路不能自启动.( √)9。

寄存器要存放n位二进制数码时,需要n2个触发器。

(×)10.同步计数器的计数速度比异步计数器快。

(√)11。

在计数器电路中,同步置零与异步置零的区别在于置零信号有效时,同步置零还需要等到时钟信号到达时才能将触发器置零,而异步置零不受时钟的控制。

(√)12。

计数器的异步清零端或异步置数端在计数器正常计数时应置为无效状态。

(√)13。

自启动功能是任何一个时序电路都具有的。

(× )14。

无论是用置零法还是用置数法来构成任意N进制计数器时,只要置零或置数控制端是异步的,则在状态循环过程中一定包含一个过渡状态;只要是同步的,则不需要过渡状态。

(√)15。

用置零法或置位法可以设计任意进制的计数器.(×)7—2 由或非门组成的基本RS触发器如图7—38所示,已知R、S的电压波形,试画出与之对应的Q和Q的波形。

图7—38 题7-2图解:由或非门组成的基本RS触发器的特性表,可得该题的输出端波形如下图所示:或非门RS 触发器特性表 题7—2 波形图7—3由与非门组成的基本RS 触发器如图7-39所示,已知R 、S 的电压波形,试画出与之对应的Q 和Q 的波形。

图7-39 题7-3图解:由与非门组成的基本RS 触发器的特性表,可得该题的输出端波形如下图所示:与非门RS 触发器特性表 题7—3波形图7-4已知如图7-40所示的各触发器的初始状态均为0,试对应画出在时钟信号CP 的连续作用下各触发器输出端Q 的波形。

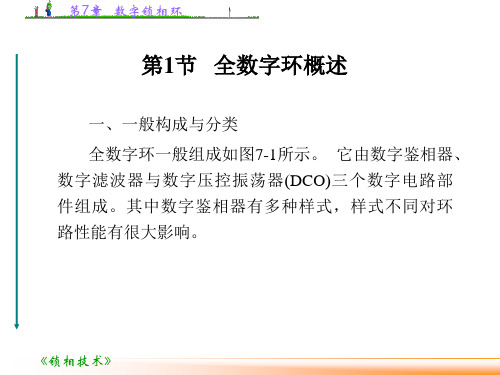

第7章数字锁相环

第7章 数字锁相环

《锁相技术》

图7-11 数字环路滤波器一般形式

第7章 数字锁相环

3. 数字压控振荡器(DCO)数字压控振荡器的基本组 成如图7-13所示。它由频率稳定的信号钟、计数器与 比较器组成,其输出是一取样脉冲序列,脉冲周期受数字 环路滤波器送来的校正电压控制。前一个取样时刻的 校正电压将改变下一个取样时刻的脉冲时间的位置。 DCO在环路中又被称为本地受控时钟或本地参考时钟 信号。

第7章 数字锁相环

《锁相技术》

图7-2 触发器型鉴相器

第7章 数字锁相环

(2) 奈奎斯特速率抽样鉴相器。该型鉴相器组成如 图7-3所示。模数变换器(A/D)的抽样率按带通信号的取 样定理选择,以使取样后信号含有充分的输入信号相 位信息。

《锁相技术》

第7章 数字锁相环

《锁相技术》

图7-3 奈奎斯特速率抽样鉴相器

图7-15 超前—滞后数字锁相环基本组成 《锁相技术》

第7章 数字锁相环

一、电路组成与说明 电路实例是数字通信中常用的一种简单的超前—滞 后位同步环路,未用序列滤波器,电路组成如图7-16所示。

《锁相技术》

第7章 数字锁相环

《锁相技术》

图7-16 位同步数字环组成电路

第7章 数字锁相环

二、环路位同步原理 图7-18为图7-16方案内各点的波形图,这里为分析 简便,以均匀变换的数字脉冲序列作为输入信号,它与随 机的数字脉冲序列作用下环路取得位同步的原理是一 样的。

《锁相技术》

第7章 数字锁相环

《锁相技术》

图7-7 简单二元鉴相器

第7章 数字锁相环

图 7-8 上 的 中 相 积 分 — 抽 样 — 清 除 电 路 是 用 来 判 断 DCO输出与码元转换边沿之间相位关系的。例如,中相 积分区间跨在从正到负的两个码元之间,而积分结果为 正,说明DCO时钟超前;积分结果为负,说明DCO时钟滞 后;积分结果为零,相位准确对准。

数字电子技术第7章习题答案

数字电子技术第7章习题答案

1. 什么是逻辑门?

答:逻辑门是数字电路中的基本组件,用于对输入进行逻辑运算并产生输出。

2. 列举几种常见的逻辑门。

答:与门、或门、非门、异或门、与非门、或非门等。

3. 什么是真值表?

答:真值表是一种用来展示逻辑函数输入与输出关系的表格,其中列出了所有可能的输入和对应的输出。

4. 什么是逻辑电路?

答:逻辑电路是指由逻辑门组成的电路,用于对输入进行逻辑运算并产生输出。

5. 什么是卡诺图?

答:卡诺图是一种用于最小化逻辑函数的图形化工具,通过将函数的真值表转化为图形,可快速找到最小化的逻辑表达式。

6. 什么是多路复用器?

答:多路复用器是一种数字电路,可以选择不同的输入并将其发送到一个输出线上。

7. 什么是解码器?

答:解码器是一种数字电路,用于将二进制数字输入转换为对应的输出,通常用于驱动其他数字电路中的寄存器、计数器等。

8. 什么是编码器?

答:编码器是一种数字电路,用于将多个输入端连接到一个二进制数字输出端,也可以实现将多个开关等输入转换为一个数字信号输出。

9. 什么是计数器?

答:计数器是一种数字电路,可用于记录电路所经过的时间或事件数量,通常用于计时器、频率计等应用。

10. 什么是触发器?

答:触发器是一种数字电路,可用于存储和控制数字信号,通常用于存储器、寄存器等应用。

第7章 S7-200系列PLC基本指令

第7章 S7-200系列PLC基本指令 S7-200系列PLC基本指令

3. 边沿触发指令(脉冲生成) 边沿触发指令(脉冲生成) (1) EU(Edge Up):上升沿微分输出指令。 (2) ED(Edge Down):下降沿微分输出指令。

第7章 S7-200系列PLC基本指令 S7-200系列PLC基本指令

例7-10 断电延时型定时器应用示例

第7章 S7-200系列PLC基本指令 S7-200系列PLC基本指令

7.1.4 定时器指令

应当注意:对于S7-200系列PLC的定时器,时基分别为1ms、 应当注意 10ms、100ms定时器的刷新方式是不同的。1ms时基定时器,每隔 1ms定时器刷新一次当前值,与扫描周期和程序处理无关,扫描周期较 长时,定时器在一个周期内可能多次被刷新,其当前值在一个周期内不 一定保持一致;10ms定时器,在每个扫描周期开始时刷新,在每个扫 描周期内,当前值不变;100ms定时器在该定时器指令执行时被刷新。

第7章 S7-200系列PLC基本指令 S7-200系列PLC基本ቤተ መጻሕፍቲ ባይዱ令

7.1.1 基本位操作指令

基本逻辑指令的语句表由指令助记符和操作数两部分组成,操作数 由可以进行位操作的寄存器元件及地址组成。常用位操作指令助计符的 定义如下所述: (1)LD(Load):装载指令,对应梯形图从左侧母线开始,连接常开 触点。 (2)LDN(Load Not):装载指令,对应梯形图从左侧母线开始,连 接常闭触点。 (3)A(And):与操作指令,用于常开触点的串联。 (4)AN(And Not):与操作指令,用于常闭触点的串联。 (5)O(Or):或操作指令,用于常开触点的并联。 (6)ON(Or Not):或操作指令,用于常闭触点的并联。 (7)=(Out):置位指令,线圈输出。

数字电路 第七章 时序逻辑电路

/0 001

/0

010 /0

101

100 /1 /0

011

结论:该电路是一个同步五进制( ⑥ 结论:该电路是一个同步五进制(模5)的加 法计数器,能够自动启动, 为进位端. 法计数器,能够自动启动,C为进位端.

§7.3 计数器

7.3.1 计数器的功能和分类

1. 计数器的作用

记忆输入脉冲的个数;用于定时,分频, 记忆输入脉冲的个数;用于定时,分频,产 生节拍脉冲及进行数字运算等等. 生节拍脉冲及进行数字运算等等.

1 0 1 0 1 0 1 0

3. 还可以用波形图显示状态转换表. 还可以用波形图显示状态转换表.

CP Q0 Q1 Q2

思考题: 思考题:试设计一个四位二进制同步加法计数 器电路,并检验其正确性. 器电路,并检验其正确性.

7.3.4 任意进制计数器的分析

例:

Q2 J2 Q2 K2 Q1 J1 Q1 K1 Q0 J0 Q0 K0

第七章 时序逻辑电路

§7.1 概述 §7.2 时序逻辑电路的分析方法 §7.3 计数器 §7.4 寄存器和移位寄存器 §7.5 计数器的应用举例

§7.1Байду номын сангаас概述

在数字电路中, 在数字电路中,凡是任一时刻的稳定 输出不仅决定于该时刻的输入,而且还和 输出不仅决定于该时刻的输入,而且还和 电路原来的状态有关者 电路原来的状态有关者,都叫做时序逻辑 电路,简称时序电路 时序电路. 电路,简称时序电路. 时序电路的特点:具有记忆功能. 时序电路的特点:具有记忆功能.

下面将重点 讨论蓝颜色 电路—移位 电路 移位 寄存器的工 寄存器的工 作原理. 作原理. D0 = 0 D1 = Q0 D2 = Q1 D3 = Q2

数字逻辑第7章 触发器

《数字逻辑》 假设门传输延时时间为t pd

四、最高时钟频率

2S

VCC 4S 4R 4Q 3SA 3SB 3R 3Q

VDD 4S 4R 1Q 2R 2S 3Q 2Q

16 15 14 13 12 11 10 9 74LS279

12345678

16 15 14 13 12 11 10 9 CC4044

12345678

1R 1SA 1SB 1Q 2R 2S 2Q GND (a) 74LS279 的引脚图

···

《数字逻辑》

一、电路结构和工作原理 1、用两个电平触发D触发器组成的边沿触发器

利用CMOS传输门的边沿触发器

《数字逻辑》

(4)列出真值表

CLK D Q Q *

XXXQ 0 X0 1 X1

(1)clk

0时,T

TG1通,TG2断 G3断,TG4通

Q Q保持,

D, Q随着D而变化 反馈通路接通,自锁

Q’

SR

Q*

《数字逻辑》

10

0

01

1

1 1 保持

0 0 不定

置1 保持 置1 置0 置1 不允许 置1

二、动作特点 在任何时刻,输入都能直接改变输出的状态。

《数字逻辑》

例:

SD和RD同时为0 Q,Q同为1

三、由或非门构成的锁存器

《数字逻辑》

《数字逻辑》

1.工作原理

SD RD Q Q *

两个或非门接成反馈,引出输入端用来置0,1 0 0 0 0

R

Q’m

Q’

CLK

Q 0时,只允许J 1的信号进入主触发器

Q 1时,只允许K 1的信号进入主触发器

《数字逻辑》

第七章触发器及时序电路

第七章触发器及时序电路第一节RS触发器一、填空题1触发器具有_______ 个稳定状态,在输入信号消失后,它能保持 __________ 不变。

2、“与非”门构成的基本RS触发器,输入端是 ____________ 和_____________ ;输出端是 _____________ 和_____________________ ,将 _____________ 称为触发器的0状态,称为触发器的1状态。

3、“与非”门构成的基本RS触发器R D =1,S D =0时,其输出状态为 ____ 。

4、触发器电路中,R D端、S D端可以根据需要预先将触发器____________ 或_______ ,而不受的同步控制。

5、同步RS 触发器状态的_________ 与___________ 同步。

二、判断题(正确的在括号中打“,错误的打“X” ))1、触发器只需具备两个稳态功能,不必具有记忆功能。

2、基本RS触发器要受时钟的控制。

3、Q n+1表示触发器原来所处的状态,即现态。

4、当CP处于下降沿时,触发器的状态一定发生翻转。

二、绘图题1、设“与非”门组成的基本RS触发器的输入信号波形如图所示,试在输入波形下方画出Q和Q端的信号波形。

R ----- ----------------------QQ2、已知同步RS触发器的S、R、CP脉冲波形如图所示。

试在它们下方画出Q端的信号波形(设触发器的初始状态为0)R -------------- ---------Q第二节JK触发器一、填空题1、在时钟脉冲的控制下,JK触发器根据输入信号J、K的不同情况,具有______、、和功能。

2、在时钟脉冲下,JK触发器输入端J = 0、K = 0时,触发器状态为_________ ; J= 0、K = 1时,触发器状态为 ________ ; J= 1、K = 0时,触发器状态为_______ ;J= 1、K = 1时,触发器状态随CP脉冲的到来而。

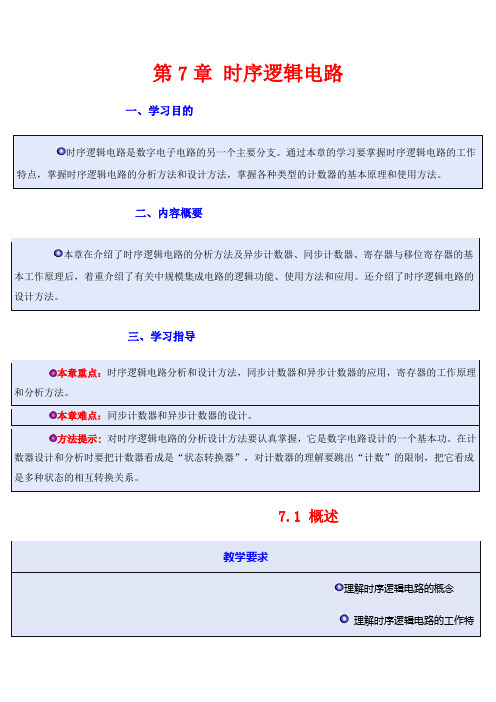

第7章 时序逻辑电路

第7章时序逻辑电路一、学习目的时序逻辑电路是数字电子电路的另一个主要分支。

通过本章的学习要掌握时序逻辑电路的工作特点,掌握时序逻辑电路的分析方法和设计方法,掌握各种类型的计数器的基本原理和使用方法。

二、内容概要本章在介绍了时序逻辑电路的分析方法及异步计数器、同步计数器、寄存器与移位寄存器的基本工作原理后,着重介绍了有关中规模集成电路的逻辑功能、使用方法和应用。

还介绍了时序逻辑电路的设计方法。

三、学习指导本章重点:时序逻辑电路分析和设计方法,同步计数器和异步计数器的应用,寄存器的工作原理和分析方法。

本章难点:同步计数器和异步计数器的设计。

方法提示: 对时序逻辑电路的分析设计方法要认真掌握,它是数字电路设计的一个基本功。

在计数器设计和分析时要把计数器看成是“状态转换器”,对计数器的理解要跳出“计数”的限制,把它看成是多种状态的相互转换关系。

7.1 概述教学要求理解时序逻辑电路的概念理解时序逻辑电路的工作特点7.2 时序逻辑电路的分析方法教学要求理解同步时序逻辑电路的分析方法了解异步时序逻辑电路的分析方法掌握状态方程、驱动方程、输出方程的概念和用法掌握状态转换图、状态转换真值表和时序图的用法时序逻辑电路的分析:根据给定的电路,写出它的方程、列出状态转换真值表、画出状态转换图和时序图,而后得出它的功能。

一、同步时序逻辑电路的分析方法同步时序逻辑电路的主要特点:在同步时序逻辑电路中,由于所有触发器都由同一个时钟脉冲信号CP来触发,它只控制触发器的翻转时刻,而对触发器翻转到何种状态并无影响,所以,在分析同步时序逻辑电路时,可以不考虑时钟条件。

1、基本分析步骤写方程式:输出方程:时序逻辑电路的输出逻辑表达式,它通常为现态和输入信号的函数。

驱动方程:各触发器输入端的逻辑表达式。

状态方程:将驱动方程代入相应触发器的特性方程中,便得到该触发器的状态方程。

列状态转换真值表:将电路现态的各种取值代入状态方程和输出方程中进行计算,求出相应的次态和输出,从而列出状态转换真值表。

FPGA设计及应用 褚振勇:第7章 MAX+PLUSⅡ开发软件中的宏模块及其应用

第7章 MAX+PLUSⅡ开发软件中的宏模块及其应用

宏模块名称

lpm——— counter

gray4

表7.6 计数器宏模块目录

功能 描述 参数化计数器(限于FLEX系列器件) 格雷码计数器 通用4位加/减计数器 , 带有异步设置、读取、清零和级联 功能的 左/右 移位寄 存器 16位二进制加/减计数器 , 带有异步设置的左/右移位寄存器 16位二进制加/减计数器 , 带有异步清零和设置的左/右移位寄 存器 4位二进制加/减计数器 , 同步/异步读取 , 异步清零 8位二进制加/减计数器 , 同步/异步读取 , 异步清零 双十进制计数器

第7章 MAX+PLUSⅡ开发软件中的宏模块及其应用

图7.3 利用T触发器设计的二分频电路

第7章 MAX+PLUSⅡ开发软件中的宏模块及其应用

在普通JK型、 D型和T型触发器的基础上, MAX+PLUSⅡ软件还提供了具有扩展 功能的 触发器 宏 模块 , 如具有预置、 清零端和三态输出端的触发器, 如果在电路设计中灵活加以运用 , 可以大大提高电路 设计的效率和性能。

带三态输出的8位两级流水线寄存器

74670

带三态输出的4位寄存器文件

74821

带三态输出的10位总线接口触发器

74821b

带三态输出的10位D触发器

74822

带三态反相输出的10位总线接口触发器

74822b

带三态反相输出的10位反相输出D触发器

第7章 MAX+PLUSⅡ开发软件中的宏模块及其应用

74823

带清零端的XY. JK触发器

第7章 MAX+PLUSⅡ开发软件中的宏模块及其应用

宏模块名称 74109 74112 74113 74114 74171 74172 74173 74174

数字逻辑第七章作业答案

H’·L’·R’

1

IDLE

R R·H’ 1 H’

R1

H

R2

L2

H’(L’+R’) 1

L3 1 H+LR L L·H’·R’ IDLE 1 R3 1 H’(L’+R’) R R·H’·L’ H+LR

H’(L’+R’) 1 L1 H+LR 1 H+L·R H H+LR R1 1H’(L’+R’) LR3

R

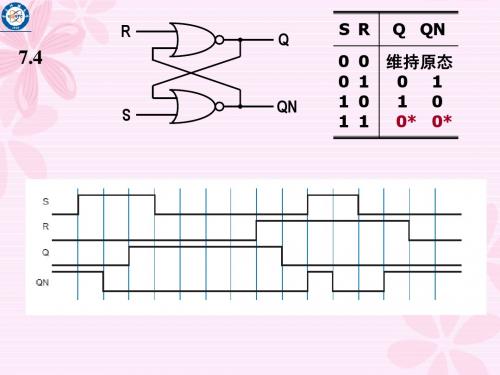

7.4

S

Q

S R 0 0 1 1 0 1 0 1

Q QN 维持原态 0 1 1 0 0* 0*

QN

R

Q

7.5

S QN

7.6 利用带有使能端的T触发器和组合逻辑构造D触发 器

D触发器:Q* = D (转移方程) T触发器的特征方程:Q*= EN·Q’ + EN’·Q=ENQ 所以,激励方程:EN = DQ

W’Y’

X’YZ

X’Z’

对A状态,不满足完备性,少了(X+YZ)’ 对B状态,不满足互斥性,多了W’Y’ 对C状态,满足二义性 对D状态,不满足互斥性,多了XY,并且不满足完备性, 少了(X+Y’)’

L2

7.24修改状态图

L3

H’ 1

H’ 1

H

L1

1 L L·H’·R’ H 1 H+L·R H H

H’·L’·R’

R2

Transition list

Q2Q1Q0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 S 转移表达式 S* Q2*Q1*Q0* 0 0 1 1 0 0 0 0 0 0 1 0 0 1 1 0 1 0 H’·L’·R’ IDLE L1 IDLE L·H’·R’ R·H’·L’ R1 H+L·R LR3 H’·(L’+R’) L2 L1 H+LR LR3

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第7章触发器触发器是一种特殊的存储过程,其特殊性在于它不需要由用户来直接调用,而是在对表中的数据进行UPDATE、INSERT或DELETE操作时自动触发执行的。

触发器通常用于保证业务规则和数据完整性,其主要优点是用户可以用编程的方法来实现复杂的处理逻辑和商业规则,增强了数据完整性约束的功能。

触发器通常用在下列场合:z完成比CHECK约束更复杂的数据约束。

与 CHECK 约束不同,触发器可以引用其它表中的列。

例如,触发器可以使用另一个表中的列来比较插入或更新的数据,也可以执行其它的操作,比如修改数据或显示用户定义的错误信息。

z为保证数据库性能而维护的非规范化数据。

比如,为提高数据的统计效率,在销售情况表中增加了统计销售总值的列(使销售情况表成为非规范化表),以后,每当在此表中插入数据时,都使用触发器统计销售总值列的新数值,并将统计后的新值保存在此表中。

以后每当有对销售总值的查询时,就直接从表中取数据即可,而不再需要使用查询语句再进行统计,从而提高数据的统计效率。

z可实现复杂的商业规则。

触发器可使业务的处理任务自动进行。

例如:在库存系统中,更新触发器可以检测什么时侯库存下降到了需要再进货的量,并自动生成给供货商的定单。

又例如:在记录工厂加工过程的数据库中,当某个加工过程超过所定义的安全限制时,可以使用触发器给操作员发出电子邮件或寻呼。

z触发器也可以评估数据修改前后的表状态,并根据其差异采取对策。

z一个表中的多个同类触发器(INSERT、UPDATE 或 DELETE)允许采取多个不同的对策以响应同一个修改语句。

7.1创建触发器建立触发器时,要指定触发器的名称、触发器所作用的表、引发触发器的操作以及在触发器中要完成的功能。

建立触发器有两种方法,一种是使用企业管理器,另一种是使用SQL语句。

我们这里只介绍使用SQL语句建立触发器的方法,使用企业管理器建立触发器的思想与用SQL语句是一样的。

1.创建触发器的语句建立触发器的SQL语句为:CREATE TRIGGER ,其语法格式为:CREATE TRIGGER 触发器名称ON {表名 | 视图名}[ WITH ENCRYPTION ]{ FOR | AFTER | INSTEAD OF } { [ INSERT ] [ , ] [ DELETE ] [ , ] [UPDATE ] }AS[ { IF UPDATE ( column )[ { AND | OR } UPDATE ( column ) ...]SQL 语句其中:z触发器名称在数据库中必须是惟一的。

z ON子句用于指定在其上执行触发器的表。

z AFTER:指定触发器只有在触发SQL语句中指定的操作都已成功执行,并且所有的约束检查也成功完成后,才执行此触发器。

z FOR:作用同AFTER。

z INSTEAD OF:指定执行触发器而不是执行引发触发器执行的SQL语句,从而替代触发语句的操作。

注意:只有SQL Server 2000版本才开始支持INSTEAD OF触发器。

z INSERT、DELETE和UPDATE是引发触发器执行的操作,若同时指定多个操作,则各操作之间用逗号分隔。

创建触发器时,需要注意如下几点:(1) 在一个表上可以建立多个名称不同、类型各异的触发器,每个触发器可由所有三个操作来引发。

对于AFTER型的触发器,可以在一种操作上建立多个触发器;对于INSTEAD OF型的触发器,在一种操作上只能建立一个触发器。

(2) 大部分Transact-SQL语句都可用在触发器中,但也有一些限制。

例如,所有的建立和更改数据库以及数据库对象的语句、所有的DROP语句都不允许在触发器中使用。

(3) 在触发器定义中,可以使用IF UPDATE子句来测试在INSERT和UPDATE语句中是否对指定字段有影响。

如果将一个值赋给指定字段或更改了指定字段,则这个子句就为真。

(4) 通常不要在触发器中返回任何结果,因此不要在触发器定义中使用SELECT语句或变量赋值语句。

(5) 在触发器中可以使用两个特殊的临时表:INSERTED表和DELETED表。

前者保存了INSERT操作中新插入的数据和UPDATE操作中的更新后的数据,后者保存了DELETE 操作删除的数据和UPDATE操作中的更新前的数据。

在触发器中对这两个表的使用方法同一般基本表一样,可以通过这两个临时表所记录的数据来判断对数据的修改是否正确。

2.INSERTED表和DELETED表触发器语句中使用了两个特殊的临时工作表:INSERTED 表和DELETED表。

这两个表是在用户执行数据的更改操作时,SQL Server自动创建和管理的。

这两个表驻留在内存中,其结构同触发器所作用的基本表的结构,并且只可以被触发器使用,当触发器结束时,系统自动释放这两个表的空间。

在触发器中可以象普通表一样对这两个表进行查询,并作为测试某些数据修改的效果及设置触发器操作的条件。

但在触发器中不能直接对这两个逻辑表中的数据进行更改。

DELETED表用于存储 DELETE 和 UPDATE 语句所影响的行的复本。

在执行 DELETE 或 UPDATE 语句时,行从触发器表中删除,并传输到 DELETED表中。

DELETED表和触发器表通常没有相同的行。

INSERTED表用于存储 INSERT 和 UPDATE 语句所影响的行的副本。

在一个插入或更新操作中,新建行被同时添加到 INSERTED表和触发器表中。

INSERTED表中的行是触发器表中新行的副本。

更新操作类似于在删除之后执行插入:首先在触发器表中删除更新前的行,并将这些行复制到DELETED表中,然后将更新后的新行复制到触发器表和 INSERTED表中。

在设置触发器条件时,应当为引发触发器的操作恰当使用 INSERTED和 DELETED表。

虽然在测试INSERT操作时引用DELETED表或在测试DELETE操作时引用 INSERTED表不会引起任何错误,但是在这种情形下这些触发器测试表中不会包含任何数据记录。

在触发器中对这两种逻辑表的使用方法同一般基本表一样,可以通过这两个临时表所记录的数据来判断对数据的修改是否正确。

7.2 后触发的触发器使用FOR 或AFTER选项定义的触发器为后触发的触发器,即只有在引发触发器执行的语句中指定的操作都已成功执行,并且所有的约束检查也成功完成后,才执行此触发器。

注:不能在视图上定义AFTER触发器。

例1.创建带有提示信息的触发器。

每当用户在pubs数据库的jobs表中插入数据时,向客户产生一条提示信息。

CREATE TRIGGER tri_insert_jobsON SC FOR insertASPRINT '在jobs表中插入了数据'执行如下语句测试触发器的作用:INSERT INTO jobs V ALUES(100, 'writer', 80, 100)系统会显示:在jobs表中插入了数据7.2.1维护数据完整性约束的触发器1.维护不同列数据之间的取值完整性例2.创建实现数据完整性约束的触发器。

限制销售表(sales)中的订购日期(ord_date)必须晚于图书的出版日期(titles表中的pubdate)。

这种涉及两个表的不同列之间的取值完整性约束,可以用触发器来实现。

实现此约束的触发器代码为:CREATE TRIGGER tri_sales_orddateON salesFOR insert, updateASIF EXISTS(SELECT * FROM inserted a JOIN titles bON a.title_id = b.title_idWHERE ord_date < pubdate )BEGINPRINT '订购日期应晚于出版日期'ROLLBACKEND执行如下语句测试触发器的作用:INSERT INTO sales V ALUES('7896','P723','1983-03-11', 20, 'Net 30','BU1111')注:触发器与引发触发器执行的操作共同构成了一个事务,事务的开始是引发触发器执行的操作,事务的结束是触发器的结束。

由于AFTER型的触发器在执行时,引发触发器执行的操作已经执行完了,因此,在触发器中应使用rollback撤消不正确的操作,这里的rollback实际是回滚到引发触发器执行的操作之前的状态。

2.维护数据完整性——级联更新所谓级联更新是指当父表(主码所在的表)的主码值更新时,如果在子表(外码所在的表)中有对此主码值的引用,则将此外码值一起更新。

许多大型数据库管理系统都支持对数据的级联更新的功能,但在定义外码时,如果没有特殊指定,则对主码的更新是受限制的。

即如果在外码表中有对此主码值的引用,则限制更新此主码的值。

如果所使用的数据库管理系统不支持级联更新功能,则可以使用触发器实现级联更新操作。

例3.对pubs数据库,更改stores表中的商店编号(stor_id)列的值时,同时更改sales表中相应的stor_id列的值。

CREATE TRIGGER storid_updateON stores FOR updateASIF UPDATE(stor_id)BEGINIF EXISTS(SELECT * FROM deleted INNER JOIN salesON Deleted.stor_id = sales.stor_id)BEGINDECLARE @new_id intDECLARE @old_id intSelect @new_id = stor_id from insertedSelect @old_id = stor_id from deletedUPDATE sales SET stor_id = @new_idWHERE stor_id = @old_idENDEND注意:当两个表之间有外码约束时,默认情况下,不能通过触发器实现主码和其相关的表的外码的级联更新。

若要验证此触发器的执行,请按下述步骤执行:(1) 删除sales表与stores表的外码引用约束(因为系统是先检查约束,后执行触发器);(2) 查看sales表和stores表中的数据,特别是商店号为“6380”的记录;(3) 执行如下更新语句:UPDATE stores SET stor_id = '1111' where stor_id = '6380'(4)再次查看sales表和stores表中的数据,特别观察商店号为“1111”的记录,可发现sales表中的商店id号为“6380”的记录现已变为“1111”7.2.2 维护数据一致性的触发器触发器的一个重要作用是维护非规范化数据的一致性,有时,为了提高数据的查询效率,我们会特意在表中保存一些统计数据,使规范化的表变成非规范化的。