EI1202NPCSL中文资料

EI1204NPCSS中文资料

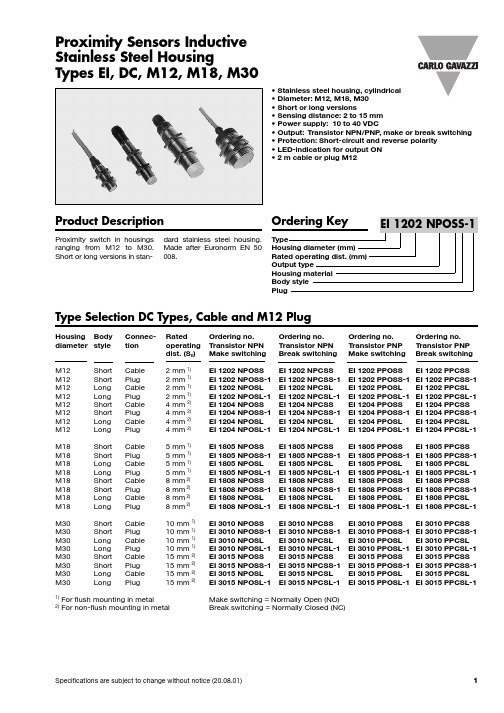

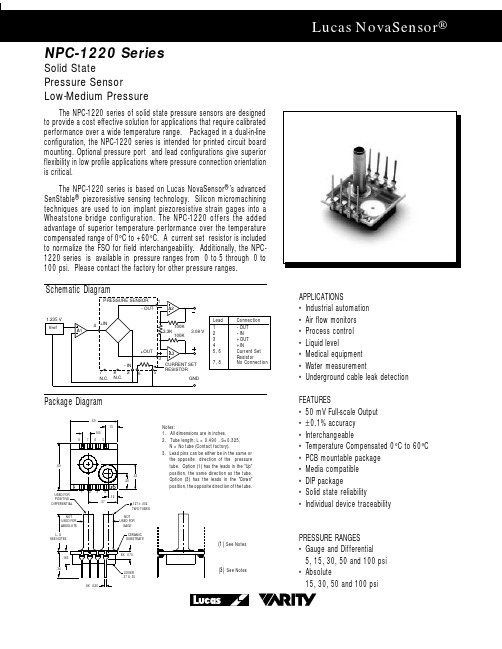

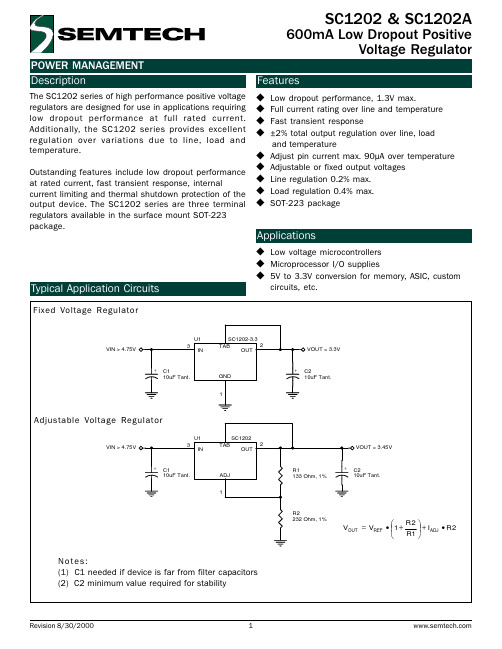

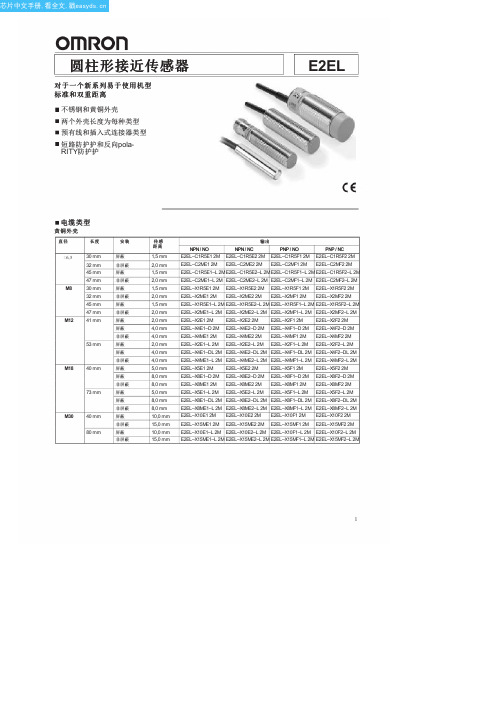

Specifications are subject to change without notice (20.08.01)1Proximity Sensors Inductive Stainless Steel HousingTypes EI, DC, M12, M18, M30•Stainless steel housing, cylindrical •Diameter: M12, M18, M30•Short or long versions•Sensing distance: 2 to 15 mm •Power supply:10 to 40 VDC•Output:Transistor NPN/PNP , make or break switching •Protection: Short-circuit and reverse polarity •LED-indication for output ON •2 m cable or plug M12Product Descriptiondard stainless steel hou sing.Made after Eu ronorm EN 50008.Proximity switch in hou sings ranging from M12 to M30.Short or long versions in stan-Type Selection DC Types, Cable and M12 PlugHousing Body Connec-Rated Ordering no.Ordering no.Ordering no.Ordering no.diameter style tion operating Transistor NPN Transistor NPN Transistor PNP Transistor PNP dist. (S n )Make switching Break switching Make switching Break switching M12Short Cable 2 mm 1)EI 1202 NPOSS EI 1202 NPCSS EI 1202 PPOSS EI 1202 PPCSS M12Short Plug 2 mm 1)EI 1202 NPOSS-1EI 1202 NPCSS-1EI 1202 PPOSS-1EI 1202 PPCSS-1M12Long Cable 2 mm 1)EI 1202 NPOSL EI 1202 NPCSL EI 1202 PPOSL EI 1202 PPCSL M12Long Plug 2 mm 1)EI 1202 NPOSL-1EI 1202 NPCSL-1EI 1202 PPOSL-1EI 1202 PPCSL-1M12Short Cable 4 mm 2)EI 1204 NPOSS EI 1204 NPCSS EI 1204 PPOSS EI 1204 PPCSS M12Short Plug 4 mm 2)EI 1204 NPOSS-1EI 1204 NPCSS-1EI 1204 PPOSS-1EI 1204 PPCSS-1M12Long Cable 4 mm 2)EI 1204 NPOSL EI 1204 NPCSL EI 1204 PPOSL EI 1204 PPCSL M12Long Plug 4 mm 2)EI 1204 NPOSL-1EI 1204 NPCSL-1EI 1204 PPOSL-1EI 1204 PPCSL-1M18Short Cable 5 mm 1)EI 1805 NPOSS EI 1805 NPCSS EI 1805 PPOSS EI 1805 PPCSS M18Short Plug 5 mm 1)EI 1805 NPOSS-1EI 1805 NPCSS-1EI 1805 PPOSS-1EI 1805 PPCSS-1M18Long Cable 5 mm 1)EI 1805 NPOSL EI 1805 NPCSL EI 1805 PPOSL EI 1805 PPCSL M18Long Plug 5 mm 1)EI 1805 NPOSL-1EI 1805 NPCSL-1EI 1805 PPOSL-1EI 1805 PPCSL-1M18Short Cable 8 mm 2)EI 1808 NPOSS EI 1808 NPCSS EI 1808 PPOSS EI 1808 PPCSS M18Short Plug 8 mm 2)EI 1808 NPOSS-1EI 1808 NPCSS-1EI 1808 PPOSS-1EI 1808 PPCSS-1M18Long Cable 8 mm 2)EI 1808 NPOSL EI 1808 NPCSL EI 1808 PPOSL EI 1808 PPCSL M18Long Plug 8 mm 2)EI 1808 NPOSL-1EI 1808 NPCSL-1EI 1808 PPOSL-1EI 1808 PPCSL-1M30Short Cable 10 mm 1)EI 3010 NPOSS EI 3010 NPCSS EI 3010 PPOSS EI 3010 PPCSS M30Short Plug 10 mm 1)EI 3010 NPOSS-1EI 3010 NPCSS-1EI 3010 PPOSS-1EI 3010 PPCSS-1M30Long Cable 10 mm 1)EI 3010 NPOSL EI 3010 NPCSL EI 3010 PPOSL EI 3010 PPCSL M30Long Plug 10 mm 1)EI 3010 NPOSL-1EI 3010 NPCSL-1EI 3010 PPOSL-1EI 3010 PPCSL-1M30Short Cable 15 mm 2)EI 3015 NPOSS EI 3015 NPCSS EI 3015 PPOSS EI 3015 PPCSS M30Short Plug 15 mm 2)EI 3015 NPOSS-1EI 3015 NPCSS-1EI 3015 PPOSS-1EI 3015 PPCSS-1M30Long Cable 15 mm 2)EI 3015 NPOSL EI 3015 NPCSL EI 3015 PPOSL EI 3015 PPCSL M30LongPlug15 mm 2)EI 3015 NPOSL-1EI 3015 NPCSL-1EI 3015 PPOSL-1EI 3015 PPCSL-11)For flush mounting in metal Make switching = Normally Open (NO)2)For non-flush mounting in metal Break switching = Normally Closed (NC)EI, DC, M12, M18, M30SpecificationsDimensionsType A B C D E F G H I SW K LØ mm mm mm mm mm mm mm mm mmØ mmØ mm EI 1202 XPXSS M12 x 1 x 3010.73011 5.0417EI 1202 XPXSL M12 x 1 x 5010.75011 5.0417EI 1202 XPXSS-1M12 x 1 x 3010.73012.611.9417EI 1202 XPXSL-1M12 x 1 x 5010.75012.611.9417EI 1204 XPXSS M12 x 1 x 3010.73411 5.0417EI 1204 XPXSL M12 x 1 x 5010.75411 5.0417EI 1204 XPXSS-1M12 x 1 x 3010.73412.611.9417EI 1204 XPXSL-1M12 x 1 x 5010.75412.611.9417EI 1805 XPXSS M18 x 1 x 3016.73011.615.4424EI 1805 XPXSL M18 x 1 x 5016.75011.615.4424EI 1805 XPXSS-1M18 x 1 x 3016.73013.111.9424EI 1805 XPXSL-1M18 x 1 x 5016.75013.111.9424EI 1808 XPXSS M18 x 1 x 3016.73811.615.4424EI 1808 XPXSL M18 x 1 x 5016.75811.615.4424EI 1808 XPXSS-1M18 x 1 x 3016.73813.111.9424EI 1808 XPXSL-1M18 x 1 x 5016.75813.111.9424EI 3010 XPXSS M30 x 1.5 x 30283013.615.4536EI 3010 XPXSL M30 x 1.5 x 50285013.615.4536EI 3010 XPXSS-1M30 x 1.5 x 30283013.611.9536EI 3010 XPXSL-1M30 x 1.5 x 50285013.611.9536EI 3015 XPXSS M30 x 1.5 x 30284213.615.4536EI 3015 XPXSL M30 x 1.5 x 50286213.615.4536EI 3015 XPXSS-1M30 x 1.5 x 30284213.611.9536EI 3015 XPXSL-1M30 x 1.5 x 50286213.611.95362Specifications are subject to change without notice (20.08.01)Specifications are subject to change without notice (20.08.01)3Power SuppliesPower supplies VDC:> SS 130/140.Power supplies with amplifier relays:> SV 190.Dimensions (cont.)Wiring DiagramsInstallation HintsRelief of cable strainProtection of the sensing faceSwitch mounted on mobile carrierTo avoid interference from inductive voltage/current peaks, separate the prox. switch pow-er cables from any other power cables, e.g.motor, contactor or solenoid cablesIncorrectCorrectThe cable should not be pulledA proximity switch should not serve as mechanical stopAny repetitive flexing of the cable should be avoidedEI, DC, M12, M18, M30。

X1202资料

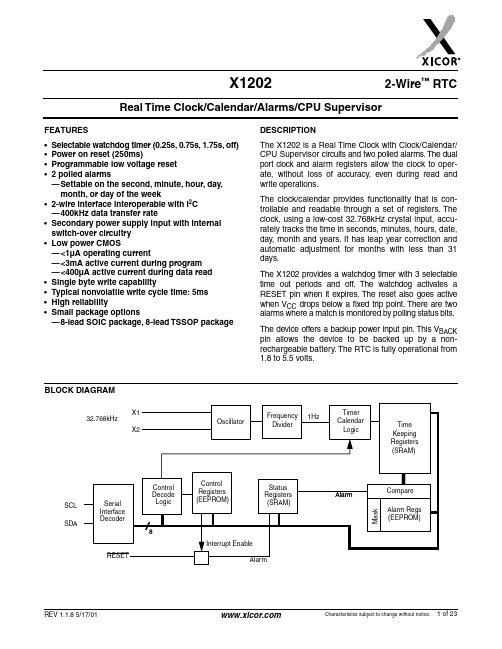

X12022-Wire™ RTC Real Time Clock/Calendar/Alarms/CPU SupervisorFEATURES•Selectable watchdog timer (0.25s, 0.75s, 1.75s, off)•Power on reset (250ms)•Programmable low voltage reset• 2 polled alarms—Settable on the second, minute, hour, day, month, or day of the week•2-wire interface interoperable with I2C—400kHz data transfer rate•Secondary power supply input with internal switch-over circuitry•Low power CMOS—<1µA operating current—<3mA active current during program—<400µA active current during data read •Single byte write capability•Typical nonvolatile write cycle time: 5ms•High reliability•Small package options—8-lead SOIC package, 8-lead TSSOP package DESCRIPTIONThe X1202 is a Real Time Clock with Clock/Calendar/ CPU Supervisor circuits and two polled alarms. The dual port clock and alarm registers allow the clock to oper-ate, without loss of accuracy, even during read and write operations.The clock/calendar provides functionality that is con-trollable and readable through a set of registers. The clock, using a low-cost 32.768kHz crystal input, accu-rately tracks the time in seconds, minutes, hours, date, day, month and years. It has leap year correction and automatic adjustment for months with less than 31 days.The X1202 provides a watchdog timer with 3 selectable time out periods and off. The watchdog activates a RESET pin when it expires. The reset also goes active when V CC drops below a fixed trip point. There are two alarms where a match is monitored by polling status bits. The device offers a backup power input pin. This V BACK pin allows the device to be backed up by a non-rechargeable battery. The RTC is fully operational from 1.8 to 5.5 volts.BLOCK DIAGRAMSCLSDA元器件交易网X1202PIN CONFIGURATIONPIN DESCRIPTIONSSerial Clock (SCL)The SCL input is used to clock all data into and out of the device. The input buffer on this pin is always active (not gated).Serial Data (SDA)SDA is a bidirectional pin used to transfer data into and out of the device. It has an open drain output and may be wire ORed with other open drain or open collector outputs. The input buffer is always active (not gated). An open drain output requires the use of a pull-up resistor. The output circuitry controls the fall time of the output signal with the use of a slope controlled pull-down. The circuit is designed for 400kHz 2-wire inter-face speeds.V BACKThis input provides a backup supply voltage to the device. V BACK supplies power to the device in the event the V CC supply fails.RESET Output—RESETThis is a reset signal output. This signal notifies a host processor that the watchdog time period has expired or that the supply voltage V CC has dropped below a fixed V TRIP threshold. It is an open drain active LOW output. X1, X2The X1 and X2 pins are the input and output,respectively, of an inverting amplifier that can be configured for use as an on-chip oscillator. A32.768kHz quartz crystal is used. Recommended crystalinput. The power control circuit will switch to V BACK when V CC < VBACK – 0.2V . It will switch back to V CC when V CC exceeds V BACK . Figure 2. Power ControlREAL TIME CLOCK OPERATIONThe Real Time Clock (RTC) uses an external,32.768kHz quartz crystal to maintain an accurate inter-nal representation of the year, month, day, date, hour,minute, and seconds. The RTC has leap-year correc-tion and century byte. The clock also corrects for months having fewer than 31 days and has a bit that controls 24-hour or AM/PM format. When the X1202powers up after the loss of both V CC and V BACK , the clock will not increment until at least one byte is written to the clock register.Reading the Real Time ClockThe RTC is read by initiating a Read command and specifying the address corresponding to the register of the real time clock. The RTC Registers can then be read in a Sequential Read Mode. Since the clock runs continuously and a read takes a finite amount of time,there is the possibility that the clock could change dur-ing the course of a read operation. In this device, the元器件交易网X1202time is latched by the read command (falling edge of the clock on the ACK bit prior to RTC data output) into a separate latch to avoid time changes during the read operation. The clock continues to run. Alarms occurring during a read are unaffected by the read operation. Writing to the Real Time ClockThe time and date may be set by writing to the RTC registers. T o avoid changing the current time by an uncompleted write operation, the current time value is loaded into a separate buffer at the falling edge of the clock on the ACK bit before the RTC data input bytes, the clock continues to run. The new serial input data replaces the values in the buffer. This new RTC value is loaded back into the RTC register by a stop bit at the end of a valid write sequence. An invalid write opera-tion aborts the time update procedure and the contents of the buffer are discarded. After a valid write operation the RTC will reflect the newly loaded data beginning with the first “one second” clock cycle after the stop bit. The RTC continues to update the time while an RTC register write is in progress and the RTC continues to run during any nonvolatile write sequences. A single byte may be written to the RTC without affecting the other bytes.CLOCK/CONTROL REGISTERS (CCR)The Control/Clock Registers are located in an area separate from the EEPROM array and are only acces-sible following a slave byte of “1101111x” and reads or writes to addresses [0000h:003Fh].CCR AccessThe contents of the CCR can be modified by perform-ing a byte or a page write operation directly to any address in the CCR. Prior to writing to the CCR (except the status register), however, the WE L and RWEL bits must be set using a two step process (See section “Writing to the Clock/Control Registers.”)The CCR is divided into 5 sections. These are:1. Alarm 0 (8 bytes)2. Alarm 1 (8 bytes)3. Control (1 byte)4. Real Time Clock (8 bytes)5. Status (1 byte)Sections 1) through 3) are nonvolatile and Sections 4) and 5) are volatile. E ach register is read and written through buffers. The nonvolatile portion (or the counter portion of the RTC) is updated only if RWEL is set and only after a valid write operation and stop bit. A sequential read or page write operation provides access to the contents of only one section of the CCR per operation. Access to another section requires a new operation. Continued reads or writes, once reach-ing the end of a section, will wrap around to the start of the section. A read or page write can begin at any address in the CCR.Section 5) is a volatile register. It is not necessary to set the RWE L bit prior to writing the status register. Section 5) supports a single byte read or write only. Continued reads or writes from this section terminates the operation.The state of the CCR can be read by performing a ran-dom read at any address in the CCR at any time. This returns the contents of that register location. Additional registers are read by performing a sequential read. The read instruction latches all clock registers into a buffer, so an update of the clock does not change the time being read. At the end of a read, the master supplies a stop condition to end the operation and free the bus. After a read of the CCR, the address remains at the previous address +1 so the user can execute a current address read of the CCR and continue reading the next Register.ALARM REGISTERSThere are two alarm registers whose contents mimic the contents of the RTC register, but add enable bits and exclude the 24-hour time selection bit. The enable bits specify which registers to use in the comparison between the Alarm and real time registers. For example:–The user can set the X1202 to alarm every Wednes-day at 8:00AM by setting the EDWn, the EHRn and EMNn enable bits to ‘1’ and setting the DWAn, HRAn and MNAn Alarm registers to 8:00AM Wednesday.–A daily alarm for 9:30PM results when the EHRn and EMNn enable bits are set to ‘1’ and the HRAn and MNAn registers set 9:30PM.–Setting the EMOn bit in combination with other enable bits and a specific alarm time, the user can establish an alarm that triggers at the same time once a year.When there is a match, an alarm flag is set. The occur-rence of an alarm can only be determined by polling the AL0 and AL1 bits.The alarm enable bits are located in the MSB of the particular register. When all enable bits are set to ‘0’, there are no alarms.元器件交易网X1202Table 1. Clock/Control Memory MapAddr.TypeRegNameBitRangeFactorySetting 76543210(optional)003F Status SR BAT AL1AL000RWEL WEL RTCF01h0037RTC(SRAM)Y2K00Y2K21Y2K20Y2K1300Y2K1019/2020h0036DW00000DY2DY1DY00-600h 0035YR Y23Y22Y21Y20Y13Y12Y11Y100-9900h 0034MO000G20G13G12G11G101-1200h 0033DT00D21D20D13D12D11D101-3100h 0032HR MIL0H21H20H13H12H11H100-2300h 0031MN0M22M21M20M13M12M11M100-5900h 0030SC0S22S21S20S13S12S11S100-5900h 0010Control(EEPROM)BL000WD1WD000000h000F Alarm1(EEPROM)Y2K000A1Y2K21A1Y2K20A1Y2K1300A1Y2K1019/2020h000E DWA0EDW10000DY2DY1DY00-600h 000D YRA0Unused - Default = RTC Year value000C MOA0EMO100A1G20A1G13A1G12A1G11A1G101-1200h 000B DTA0EDT10A1D21A1D20A1D13A1D12A1D11A1D101-3100h 000A HRA0EHR10A1H21A1H20A1H13A1H12A1H11A1H100-2300h 0009MNA0EMN1A1M22A1M21A1M20A1M13A1M12A1M11A1M100-5900h 0008SCA0ESC1A1S22A1S21A1S20A1S13A1S12A1S11A1S100-5900h0007Alarm0(EEPROM)Y2K100A0Y2K21A0Y2K20A0Y2K1300A0Y2K1019/2020h0006DWA1EDW00000DY2DY1DY00-600h 0005YRA1Unused - Default = RTC Year value0004MOA1EMO000A0G20A0G13A0G12A0G11A0G101-1200h 0003DTA1EDT00A0D21A0D20A0D13A0D12A0D11A0D101-3100h 0002HRA1EHR00A0H21A0H20A0H13A0H12A0H11A0H100-2300h 0001MNA1EMN0A0M22A0M21A0M20A0M13A0M12A0M11A0M100-5900h 0000SCA1ESC0A0S22A0S21A0S20A0S13A0S12A0S11A0S100-5900hREAL TIME CLOCK REGISTERSYear 2000 (Y2K)The X1202 has a century byte that “rolls over” from 19 to 20 when the years byte changes from 99 to 00. The Y2K byte can contain only the values of 19 or 20.Day of the Week Register (DW)This register provides a Day of the Week status and uses three bits DY2 to DY0 to represent the seven days of the week. The counter advances in the cycle 0-1-2-3-4-5-6-0-1-2-... The assignment of a numerical value to a specific day of the week is arbitrary and may be decided by the system software designer. The Clock Default values define 0 = Sunday.元器件交易网X1202Clock/Calendar Register (YR, MO, DT, HR, MN, SC) These registers depict BCD representations of the time. As such, SC (Seconds) and MN (Minutes) range from 0 to 59, HR (Hour) is 1 to 12 with an AM or PM indicator (H21 bit) or 0 to 23 (with MIL = 1), DT (Date) is 1 to 31, MO (Month) is 1 to 12, YR (Y ear) is 0 to 99.24 Hour TimeIf the MIL bit of the HR register is 1, the RTC uses a 24-hour format. If the MIL bit is 0, the RTC uses a 12-hour format and bit H21 functions as an AM/PM indica-tor with a ‘1’ representing PM. The clock defaults to Standard Time with H21 = 0.Leap YearsLeap years add the day February 29 and are defined as those years that are divisible by 4. Y ears divisible by 100 are not leap years, unless they are also divisible by 400. This means that the year 2000 is a leap year, the year 2100 is not. The X1202 does not correct for the leap year in the year 2100.STATUS REGISTER (SR)The Status Register is located in the RTC area at address 003Fh. This is a volatile register only and is used to control the WE L and RWE L write enable latches, read two power status and two alarm bits. This register is separate from both the array and the Clock/ Control Registers (CCR).Table 2. Status Register (SR)BAT: Battery Supply—VolatileThis bit set to “1” indicates that the device is operating from V BACK, not V CC. It is a read only bit and is set/ reset by hardware.AL1, AL0: Alarm bits—VolatileThese bits announce if either alarm 1 or alarm 2 match the real time clock. If there is a match, the respective bit is set to ‘1’. The falling edge of the last data bit in a SR Read operation resets the flags. Note: Only the AL bits that are set when an SR read starts will be reset. An alarm bit that is set by an alarm occurring during an SR read operation will remain set after the read operation is complete.RWEL: Register Write Enable Latch—VolatileThis bit is a volatile latch that powers up in the LOW (disabled) state. The RWEL bit must be set to “1” prior to any writes to the Clock/Control Registers. Writes to RWEL bit do not cause a nonvolatile write cycle, so the device is ready for the next operation immediately after the stop condition. A write to the CCR requires both the RWE L and WE L bits to be set in a specific sequence. RWEL bit is reset after each high voltage or reset by sending 00h to status register.WEL: Write Enable Latch—VolatileThe WEL bit controls the access to the CCR and mem-ory array during a write operation. This bit is a volatile latch that powers up in the LOW (disabled) state. While the WE L bit is LOW, writes to the CCR or any array address will be ignored (no acknowledge will be issued after the Data Byte). The WEL bit is set by writing a “1”to the WEL bit and zeroes to the other bits of the Status Register. Once set, WEL remains set until either reset to “0” (by writing a “0” to the WEL bit and zeroes to the other bits of the Status Register) or until the part pow-ers up again. Writes to WEL bit do not cause a nonvol-atile write cycle, so the device is ready for the next operation immediately after the stop condition.RTCF: Real Time Clock Fail Bit—VolatileThis bit is set to a ‘1’ after a total power failure. This is a read only bit that is set by hardware when the device powers up after having lost all power to the device. The bit is set regardless of whether V CC or V BACK is applied first. The loss of one or the other supplies does not result in setting the RTCF bit. The first valid write to the RTC (writing one byte is sufficient) resets the RTCF bit to ‘0’.Unused BitsThese devices do not use bits 3 or 4, but must have a zero in these bit positions. The Data Byte output during a SR read will contain zeros in these bit locations.CONTROL REGISTERWatchdog Timer Control BitsThe bits WD1 and WD0 control the period of the Watchdog Timer. See T able 3 for options.Addr76543210003Fh BAT AL1AL000RWEL WEL RTCFDefault00000001元器件交易网X1202Table 3. Watchdog Timer Time Out OptionsWRITING TO THE CLOCK/CONTROL REGISTERS Changing any of the nonvolatile bits of the clock/control register requires the following steps:–Write a 02H to the status register to set the Write Enable Latch (WEL). This is a volatile operation, so there is no delay after the write. (Operation pre-ceeded by a start and ended with a stop).–Write a 06H to the status register to set both the Register Write Enable Latch (RWEL) and the WEL bit. This is also a volatile cycle. The zeros in the data byte are required. (Operation preceeded by a start and ended with a stop).–Write one to 8 bytes to the clock/control registers with the desired clock, alarm, or control data. This sequence starts with a start bit, requires a slave byte of “11011110” and an address within the CCR and is terminated by a stop bit. A write to the CCR changes EEPROM values so these initiate a nonvolatile write cycle and will take up to 10ms to complete. Writes to undefined areas have no effect. The RWEL bit is reset by the completion of a nonvolatile write cycle, so the sequence must be repeated to again initiate another change to the CCR contents. If the sequence is not completed for any reason (by sending an incorrect number of bits or sending a start instead of a stop, for example) the RWEL bit is not reset and the device remains in an active mode.–The RWEL and WEL bits can be reset by writing a 0 to the status register.–A read operation occurring between any of the previous operations will not interrupt the register write operation. POWER ON RESETApplication of power to the X1202 activates a power on reset circuit that pulls the RESET pin active. This signal provides several benefits.–It prevents the system microprocessor from starting to operate with insufficient voltage.–It prevents the processor from operating prior to sta-bilization of the oscillator.–It allows time for an FPGA to download its configura-tion prior to initialization of the circuit.When V CC exceeds the device V TRIP threshold value for 250ms the circuit releases RE SE T, allowing the system to begin operation.WATCHDOG TIMER OPERATIONThe watchdog timer is selectable. By writing a value to WD1 and WD0, the watchdog timer can be set to 3 dif-ferent time out periods or off. When the watchdog timer is set to off, the watchdog circuit is configured for low power operation.Watchdog Timer RestartThe Watchdog Timer is restarted by a falling edge of SDA when the SCL line is high. This is also referred to as start condition. The restart signal restarts the watch-dog timer counter, resetting the period of the counter back to the maximum. If another start fails to be detected prior to the watchdog timer expiration, then the RE SE T pin becomes active. In the event that the restart signal occurs during a reset time out period, the restart will have no effect.LOW VOLTAGE RESET OPERATIONWhen a power failure occurs, and the voltage to the part drops below a fixed V TRIP voltage, a reset pulse is issued to the host microcontroller. The circuitry monitors the V CC line with a voltage comparator which senses a preset threshold voltage. Power up and power down waveforms are shown in Figure 4. The low voltage reset circuit is to be designed so the RE SE T signal is valid down to 1.0V.When the low voltage reset signal is active, the operation of any in-progress nonvolatile write cycle is unaffected, allowing a nonvolatile write to continue as long as possi-ble (down to the power on reset voltage). The low voltage reset signal, when active, terminates in-progress commu-nications to the device and prevents new commands, to reduce the likelihood of data corruption.WD1WD0Watchdog Time Out Period00 1.75 seconds01750 milliseconds10250 milliseconds11disabled元器件交易网X1202Figure 3. Watchdog Restart/Time OutFigure 4. Power On Reset and Low Voltage ResetV CC THRESHOLD RESET PROCEDUREThe X1202 is shipped with a standard V CC threshold (V TRIP) voltage. This value will not change over normal operating and storage conditions. However, in applica-tions where the standard V TRIP is not exactly right, or if higher precision is needed in the V TRIP value, the X1202 threshold may be adjusted. The procedure is described below, and uses the application of a nonvolatile write control signal.Setting the V TRIP VoltageThis procedure is used to set the V TRIP to a higher voltage value. It is necessary to reset the trip point before setting the new value.T o set the new V TRIP voltage, apply the desired V TRIP threshold voltage to the V CC pin and tie the RE SE T pad pin to the programming voltage V P. Then write data 00h to address 01h. The stop bit following a valid write operation initiates the V TRIP programming sequence. Bring RESET to V CC to complete the operation. Note: This operation also writes 00h to address 01h of the EEPROM array.元器件交易网Figure 5. Set V TRIP Level Sequence (V CC = desired V TRIP value)Resetting the V TRIP VoltageThis procedure is used to set the V TRIP to a “native”voltage level. For example, if the current V TRIP is 4.4V and the new V TRIP must be 4.0V , then the V TRIP must be reset. When V TRIP is reset, the new V TRIP is less than 1.7V . This procedure must be used to set the volt-age to a lower value.T o reset the new V TRIP voltage, apply more than 3V to the V CC pin and tie the RESET pin to the programming voltage V P . Then write 00h to address 03h. The stop bit of a valid write operation initiates the V TRIP programming sequence. Bring RESET to complete the operation. Note: This operation also writes 00h to address 03h of the EEPROM array.Figure 6. Reset V TRIP Level Sequence (V CC > 3V)Figure 7. Sample V TRIP Reset Circuit01234567SCLSDAAEh0123456703hRESET V P = 15V00h012345670123456700hV CCV CCSERIAL COMMUNICATIONInterface ConventionsThe device supports a bidirectional bus oriented proto-col. The protocol defines any device that sends data onto the bus as a transmitter, and the receiving device as the receiver. The device controlling the transfer is called the master and the device being controlled is called the slave. The master always initiates data transfers, and provides the clock for both transmit and receive operations. Therefore, the devices in this family operate as slaves in all applications.Clock and DataData states on the SDA line can change only during SCL LOW. SDA state changes during SCL HIGH are reserved for indicating start and stop conditions. See Figure 8.Figure 8. Valid Data Changes on the SDA BusStart ConditionAll commands are preceded by the start condition, which is a HIGH to LOW transition of SDA when SCL is HIGH. The device continuously monitors the SDA and SCL lines for the start condition and will not respond to any command until this condition has been met. See Figure 9.Stop ConditionAll communications must be terminated by a stop con-dition, which is a LOW to HIGH transition of SDA when SCL is HIGH. The stop condition is also used to place the device into the Standby power mode after a read sequence. A stop condition can only be issued after the transmitting device has released the bus. See Figure 8. AcknowledgeAcknowledge is a software convention used to indicate successful data transfer. The transmitting device, either master or slave, will release the bus after transmitting eight bits. During the ninth clock cycle, the receiver will pull the SDA line LOW to acknowledge that it received the eight bits of data. Refer to Figure 10.Figure 9. Valid Start and Stop ConditionsFigure 10. Acknowledge Response From ReceiverThe device will respond with an acknowledge after rec-ognition of a start condition and if the correct device identifier and select bits are contained in the slave address byte. If a write operation is selected, the device will respond with an acknowledge after the receipt of each subsequent eight bit word. The device will acknowledge all incoming data and address bytes, except for:–The slave address byte when the device identifier and/or select bits are incorrect–All data bytes of a write when the WEL in the write protect register is LOW–The 2nd data byte of a status register write operation (only 1 data byte is allowed)In the read mode, the device will transmit eight bits of data, release the SDA line, then monitor the line for an acknowledge. If an acknowledge is detected and no stop condition is generated by the master, the device will continue to transmit data. The device will terminate further data transmissions if an acknowledge is not detected. The master must then issue a stop condition to return the device to standby mode and place the device into a known state.WRITE OPERATIONSByte WriteFor a byte write operation, the device requires the slave address byte and the CCR address bytes. This gives the master access to any one of the words in the CCR. (Note: Prior to writing to the CCR, the master must write a 02h, then 06h to the status register in two preceeding operations to enable the write operation. See “Writing to the Clock/Control Registers” on page 6.) Upon receipt of each address byte, the X1202 responds with an acknowledge. After receiving both address bytes the X1202 awaits the eight bits of data. After receiving the 8 data bits, the X1202 again responds with an acknowledge. The master then termi-nates the transfer by generating a stop condition. The X1202 then begins an internal write cycle of the data to the nonvolatile memory. During the internal write cycle, the device inputs are disabled, so the device will not respond to any requests from the master. The SDA out-put is at high impedance. See Figure 11.Page WriteThe X1202 has a page write operation. It is initiated in the same manner as the byte write operation; but instead of terminating the write cycle after the first data byte is transferred, the master can transmit up to 7 more bytes to the clock/control registers.Note: Prior to writing to the CCR, the master must write a 02h, then 06h to the status register in two pre-ceeding operations to enable the write operation. See “Writing to the Clock/Control Registers” on page 6.)Figure 11. Byte Write SequenceFigure 12. Page Write SequenceS t a r tS t o pSlave AddressCCR Address 1 DataA C KA C KSDA Bus Signals from the SlaveSignals from the Master 0CCR Address 0111101100000000A C KA C KCCR Address 0S t a r tS t o pSlave AddressCCR Address 1Data (n)A C KA C KA C KSDA BusSignals from the SlaveSignals from the MasterData (1)A C K(1 ≤ n 64)111101100000000After the receipt of each byte, the X1202 responds with an acknowledge, and the address is internally incrimi-nated by one. When the counter reaches the end of the page, it “rolls over” and goes back to the first address on the same page. If the master supplies more than 8bytes of data, then the previously loaded data is over written by the new data, one byte at a time. The master terminates the data byte loading by issuing a stop con-dition, which causes the device to begin the non vola-tile write cycle. As with the byte write operation, all inputs are disabled until completion of the internal write cycle. Refer to Figure 12 for the address, acknowledge,and data transfer sequence.Stops and Write ModesStop conditions that terminate write operations must be sent by the master after sending at least 1 full data byte and its associated ACK signal. If a stop is issued in the middle of a data byte, or before 1 full data byte +ACK is sent, then the device will reset itself without performing the write. The contents of the array will not be affected.Acknowledge PollingThe disabling of the inputs during non volatile write cycles can be used to take advantage of the typical 5ms write cycle time. Once the stop condition is issued to indicate the end of the master’s byte load operation,the device initiates the internal non volatile write cycle.Acknowledge polling can be initiated immediately. T o do this, the master issues a start condition followed by the slave address byte for a write or read operation. If the device is still busy with the non volatile write cycle then no ACK will be returned. If the device has com-pleted the write operation, an ACK will be returned and the host can then proceed with the read or write opera-tion. Refer to the flow chart in Figure 13.Figure 13. Acknowledge Polling SequenceREAD OPERATIONSThere are three basic read operations: Current Address Read, Random Read, and Sequential Read.Current Address ReadInternally the device contains an address counter that maintains the address of the last word read incrimi-nated by one. Therefore, if the last read was to address n, the next read operation would access data from address n + 1.Upon receipt of the slave address byte with the R/W bit set to one, the device issues an acknowledge and then transmits the eight bits of the data byte. The master terminates the read operation when it does not respond with an acknowledge during the ninth clock and then issues a stop condition. Refer to Figure 14 for the address, acknowledge, and data transfer sequence.It should be noted that the ninth clock cycle of the read operation is not a “don’t care.” T o terminate a read operation, the master must either issue a stop condi-tion during the ninth cycle or hold SDA HIGH during the ninth clock cycle and then issue a stop condition.Figure 14. Current Address Read SequenceS t a r tS t o pSlave AddressDataA C KSDA Bus Signals from the SlaveSignals from the Master 11111011。

ACE12022BN14资料

ACE1202 Product Family Arithmetic Controller Engine (ACEx™) for Low Power ApplicationsACE1202 Product Family Arithmetic Controller Engine (ACEx™) for Low Power ApplicationsACE1202 Product Family Arithmetic Controller Engine (ACEx™) for Low Power ApplicationsF r e q u e n c y (M H z )Temperature [°C]Temperature [°C]ACE1202 Product Family Arithmetic Controller Engine (ACEx™) for Low Power Applications I c c I D L E(µA)IDLE current vs. Temperature Temperature [°C]ACE1202 Product Family Arithmetic Controller Engine (ACEx™) for Low Power ApplicationsACE1202 Product Family Arithmetic Controller Engine (ACEx™) for Low Power ApplicationsACE1202 Product Family Arithmetic Controller Engine (ACEx™) for Low Power ApplicationsACE1202 Product Family Arithmetic Controller Engine (ACEx™) for Low Power ApplicationsACE1202 Product Family Arithmetic Controller Engine (ACEx™) for Low Power ApplicationsACE1202 Product Family Arithmetic Controller Engine (ACEx™) for Low Power ApplicationsACE1202 Product Family Arithmetic Controller Engine (ACEx™) for Low Power ApplicationsACE1202 Product Family Arithmetic Controller Engine (ACEx™) for Low Power ApplicationsACE1202 Product Family Arithmetic Controller Engine (ACEx™) for Low Power ApplicationsACE1202 Product Family Arithmetic Controller Engine (ACEx™) for Low Power ApplicationsACE1202 Product Family Arithmetic Controller Engine (ACEx™) for Low Power Applicationsinto the decision register is 1, the pattern in the HPATTERN register is shifted out of the output port. Similarly, if the active bit is 0 the pattern in the LPATTERN register is shifted out.The HBC control (HBCNTRL) register is used to configure and control the data transmission. HBCNTRL is divided in 5 different controlling signal FRAME[2:0], IOSEL, TXBUSY, START/STOP, and OCFLAG (see Figure 23.)FRAME[2:0] selects the number of bits of DAT0 to encode and transmit. The HBC allows from 2 (0x1) to 8 (0x7) DAT0 bits to be encoded and transmitted. Upon a reset, FRAME is initialized to zero disabling the DAT0’s decision register transmitting no data. The IOSEL signal selects the transmission to output (TX) through either port G2 or G5. If IOSEL is 1, G5 is selected as the output port otherwise G2 is selected.The TXBUSY signal is read only and is used to inform software that a transmission is in progress. TXBUSY goes high when the encoded data begins to shift out of the output port and will remains high during each consecutive DAT0 frame bit transmission (see Figure 25). The HBC will clear the TXBUSY signal when the last DAT0 encoded bit of the frame is transmitted and the STOP signal is 0.The START / STOP signal controls the encoding and transmission process for each data frame. When software sets the START / STOP bit the D AT0 frame transmission process begins. The START signal will remain high until the beginning of the last encoded DAT0 frame bit transmission. The HBC then clears the START / STOP bit allowing software to either continue with a new DAT0 frame transmission or stop the transmission all together (see Figure 25). If TXBUSY is 0 when the START signal is enabled, a synchronization period occurs before any data is transmitted lasting the amount of time to transmit a 0 encoded bit (see Figure 24).The OCFLAG signal is read only and goes high when the last encoded bit of the D AT0 frame is transmitting. The OCFLAG signal is used to inform software that the D AT0 frame transmission operation is completing (see Figure 25). If multiple DAT0 frames are to be transmitted consecutively, software should poll the OCFLAG signal for a 1. Once OCFLAG is 1, DAT0 must be reload and the START / STOP bit must be restored to 1 in order to begin the new frame transmission without interruptions (the synchroni-zation period). Since OCFLAG remains high during the entire last encoded DAT0 frame bit transmission, software should wait for the HBC to clear the OCFLAG signal before polling for the new OCFLAG high pulse. If new data is not reloaded into D AT0 and the START signal (STOP is active) is not set before the OCFLAG is 0, the transmission process will end (TXBUSY is cleared) and a new process will begin starting with the synchronization period. Figure 24 and 25 shows how the HBC performs its data encoding. In the example, two frames are encoded and transmitted consecu-tively with the following bit encoding format specification:1.Transmission frequency = 62.5KHz2.Data to be encoded = 0x52, 0x92 (all 8-bits)3.Each bit should be encoded as a 3-bit binary value, ‘1’ =110b and ‘0’ = 100b4.Transmission output port : G2To perform the data transmission, software must first initialize the PSCALE, BPSEL, HPATTERN, LPATTERN, and DAT0 registers with the appropriate values.LD PSCALE, #03H; (1MHz ÷ 4) ÷ 4 = 62.5KHz LD BPSEL, #012H; BPH = 2, BPL = 2 (3 bits each) LD HPATTERN, #0C0H; HPATTERN = 0xC0LD LPATTERN, #090H; LPATTERN = 0x90LD DAT0, #052H; DAT0 = 0x52Once the basic registers are initialized, the HBC can be started. (At the same time, software must set the number of data bits per data frame and select the desired output port.)LD HBCNTRL, #27H;START / STOP = 1,FRAME = 7, IOSEL = 0ACE1202 Product Family Arithmetic Controller Engine (ACEx™) for Low Power Applications8.0Hardware Bit-Coder (ACE1202-2 only)The ACE1202-2 contains a dedicated hardware bit-encoding peripheral block, Hardware Bit-Coder (HBC), for IR/RF data transmission (see Figure 21.) The HBC is completely software programmable and can be configured to emulate various bit-encoding formats. The software developer has the freedom to encode each bit of data into a desired pattern and output the encoded data at the desired frequency through either the G2 or G5output (TX) ports.The HBC contains six 8-bit memory-mapped configuration regis-ters PSCALE, HPATTERN, LPATTERN, BPSEL, HBCNTRL, and D AT0. The registers are used to select the transmission fre-quency, store the data bit-encoding patterns, configure the data bit-pattern/frame lengths, and control the data transmission flow.To select the IR/RF transmission frequency, an 8-bit divide constant must be written into the IR/RF Pre-scalar (PSCALE)register. The IR/RF transmission frequency generator divides the1MHz instruction clock down by 4 and the PSCALE register is used to select the desired IR/RF frequency shift. Together, the transmission frequency range can be configured between 976Hz(PSCALE = 0xFF) and 125kHz (PSCALE = 0x01). Upon a reset,the PSCALE register is initialized to zero disabling the IR/RF transmission frequency generator. However, once the PSCALE register is programmed, the desired IR/RF frequency is main-tained as long as the device is powered.Once the transmission frequency is selected, the data bit-encod-ing patterns must be stored in the appropriate registers. The HBC contains two 8-bit bit-encoding pattern registers, High-pattern(HPATTERN) and Low-pattern (LPATTERN). The encoding pat-tern stored in the HPATTERN register is transmitted when the data bit value to be encoded is a 1. Similarly, the pattern stored in the LPATTERN register is transmitted when the data bit value to be encoded is a 0. The HBC transmits each encoded pattern MSB first.The number of bits transmitted from the HPATTERN and LPATTERN registers is software programmable through the Bit Period Configuration (BPSEL) register (see Figure 22). D uring the transmission of HPATTERN, the number of bits transmitted is configured by BPH[2:0] (BPSEL[2:0]) while BPL[2:0] (BPSEL[5:3])configures the number of transmitted bits for the LPATTERN. The HBC allows from 2 (0x1) to 8 (0x7) encoding pattern bits to be transmitted from each register. Upon a reset, BPSEL is initially 0disabling the HBC from transmitting pattern bits from either register.The Data (DAT0) register is used to store up to 8 bits of data to be encoded and transmitted by the HBC. This data is shifted, bit by bit, MSB to LSB into a 1-bit decision register. If the active bit shiftedACE1202 Product Family Arithmetic Controller Engine (ACEx™) for Low Power ApplicationsACE1202 Product Family Arithmetic Controller Engine (ACEx™) for Low Power ApplicationsACE1202 Product Family Arithmetic Controller Engine (ACEx™) for Low Power ApplicationsACE1202 Product Family Arithmetic Controller Engine (ACEx™) for Low Power ApplicationsACE1202 Product Family Arithmetic Controller Engine (ACEx™) for Low Power ApplicationsACE1202 Product Family Arithmetic Controller Engine (ACEx™) for Low Power ApplicationsACE1202 Product Family Arithmetic Controller Engine (ACEx™) for Low Power ApplicationsACE1202 Product Family Arithmetic Controller Engine (ACEx™) for Low Power ApplicationsACE1202 Product Family Arithmetic Controller Engine (ACEx™) for Low Power Applications14-Pin DIP (N14)Order Number ACE1202(12022, 1202L)N14/ACE1202(12022)EN14/ACE1202VN14 ACE1202(12022)BN14/ACE1202(12022)BEN14/ACE1202(12022)BVN14Package Number N14AACE1202 Product Family Arithmetic Controller Engine (ACEx™) for Low Power Applications。

1202P中文资料

Document Number: 63055For any questions, contact: foil@1202Vishay Foil ResistorsBulk Metal ® Foil TechnologyPrecision Trimming Potentiometers, 1 1/4 Inch Rectilinear, RJ12 Style, Designed to Meet or Exceed The Requirements of MIL-PRF-22097, Char. FNote1.See Figures 1 and2.FEATURES•Temperature coefficient of resistance (TCR): ± 10 ppm/°C maximum 3) (- 55 °C to + 150 °C ref. at + 25 °C); through the wiper 4); ± 25 ppm/°C•Load life stability: 0.1 % typical ΔR, 0.5 %maximum ΔR under full rated power at + 85 °C for 2000 h•Settability: 0.05 % typical; 0.1 % maximum•Setting stability: 0.1 % typical; 0.5 % maximum, ΔSS •Power rating: 0.5 W at + 85 °C •Resistance range: 2 Ω to 20 k Ω•“O“-ring prevents ingress of fluids during any board cleaning operation•Electrostatic discharge: above 25 000 V •Terminal finishes available: gold platedNotes†Under full rated power of 0.5 W at + 85 °C.•Refer to page 4 for footnotes.* Pb containing terminations are not RoHS compliant, exemptions may applyTABLE 1 - MODEL SELECTION †MODELTERMINATIONSTYLE AVERAGEWEIGHT(g)POWERRATING at + 85 °C AMBIENTNO. OFTURNS1202P-In line PC pins 2.50.5 W25 ± 2Y -staggered PC pins 1)2.5L-flexible wire leads3.3LB-flexible wire leadswith bushings5.1TABLE 2 - VALUES VS. TOLERANCESSTANDARD RESISTANCE VALUES (in Ω)STANDARD TOLERANCES2, 5, 10± 10 %2), ± 20 %20, 50, 100, 200, 250, 500, 1K, 2K, 5K, 10K, 20K5 %, 10 %TABLE 3 - 1202 (RJ12) SERIES ELECTRICAL SPECIFICATIONSTemperature Coefficient of Resistance (TCR)end-to-end 3)± 10 ppm/°C maximum (- 55 °C to + 25 °C)± 10 ppm/°C maximum (+ 25 °C to + 150 °C)2 Ω, 5 Ω, 10 Ω, 20 Ωthrough the wiper 4)± 20 ppm/°C ± 25 ppm/°CStabilityload life at 2000 h †load life at 10000 h †0.1 % typical ΔR; 0.5 % maximum ΔR 0.1 % typical ΔR; 1.0 % maximum ΔR Power Rating 5)0.5 W at + 85 °CSettability 0.05 % typical; 0.1 % maximum Setting Stability0.1 % typical; 0.5 % maximum ΔSS Contact Resistance variation - CRV (noise) 3 Ω typical; 10 Ω maximum Hop-off0.25 % typical; 1.0 % maximum High-Frequency Operation Rise time Inductance Capacitanceto 100 MHz 10 ns at 1 k Ω0.08 µH typical 0.5 pF typical Operating Temperature Range- 55 °C to + 150 °CTABLE 4 - MECHANICAL SPECIFICATIONSAdjustment Turns 25 ± 2Case Material Glass fortified diallyl-phthalate (DAP); black Mechanical StopsWiper idles - no discontinuityShaft Torque 8 oz. in. maximum; 3 oz. in. typical Internal Terminations All welded - no fluxBacklash0.05 % typical1202Vishay Foil Resistors Bulk Metal® Foil Technology Precision TrimmingPotentiometers, 1 1/4 Inch Rectilinear, RJ12 Style, Designed toMeet or Exceed The Requirements of MIL-PRF-22097, Char. F Array For any questions, contact: foil@ Document Number: 63055Document Number: 63055For any questions, contact: foil@1202Bulk Metal ® Foil Technology Precision Trimming Potentiometers, 1 1/4 Inch Rectilinear, RJ12 Style, Designed to Meet or Exceed The Requirements of MIL-PRF-22097, Char. FVishay Foil Resistors1202Vishay Foil ResistorsBulk Metal ® Foil Technology Precision TrimmingPotentiometers, 1 1/4 Inch Rectilinear, RJ12 Style, Designed to Meet or Exceed The Requirements of MIL-PRF-22097, Char. F For any questions, contact: foil@Document Number: 63055Notes1.Preferred Termination style for current 1-1/4 inch rectilinear trimmers (staggered PC pins present a sturdier mounting arrangement for shock, vibration, and impact situations).2.10 W at ± 5 % available on special order.3.Maximum TCR applies to the 3 σ (sigma) limit or 99.73 % of a production lot. (Measured end-to-end with wiper off the element.)4.Measurements of TCR through the wiper are influenced more by setting stability and the percentage of the total resistance in use (at the wiper) than by fundamental resistance change due to temperature alone. The parameter shown in Table 3 is a 2 σdistribution typifying the behavior of the device when used with 40% or more of the total resistance in use.5.Derated linearly from full power at + 85 °C to zero (0) W at +150 °C. See Figure 3 in this data sheet.6.All ΔR’s are measured to the tolerance specified + 0.01 Ω.7.Whichever is greater.8.Load-Life test performed at nominal rated power, 0.5 W, at +85 °C.Special Available Options:Special markingSpecial lengths for lead wires (L, LB Style)Hooked leadsAlternate bushing and PC combinationsPower conditioning and screening operations VISHAY TRIMMERS ARE INSPECTED 100 % for:•Short-time overload (6.25 x rated power for 5 s on; and for 30 s off - 3 cycles)•Immersion•Resistance tolerance check •End resistance •Visual-mechanical•Dynamic tests for continuity, CRV By Sample for:•TCR •DWVTABLE 5 - COMPARISONMIL-PRF-22097/2 CHARACTERISTIC F 7)1202 MAXIMUM (Worst Case)TEST GROUP IVisual and mechanical Total resistanceActual effective electrical travel End resistanceContact resistance variation - CRV (noise) Dielectric withstanding voltage - DWV (atmospheric and barometric pressure) Insulation resistance Shaft torque Thermal shock No failures ± 10 %17 to 27 turns ± 2 % or 20 Ω7)± 3.0 % or 3 Ω7)Per MIL-STD-202, methods 301 and 105≥ 1000 M Ω8 oz. in. maximum± 1.0 %No failures ± 10 %25 ± 2 turns2 Ω3 Ω typical, 10 Ω maximumPer MIL-STD-202, methods 301 and 105≥ 1000 M Ω8 oz. in. maximum± 1.0 %TEST GROUP IIResistance temperature characteristic - TCR Moisture resistanceContact resistance variation - CRV (noise)± 0.01 % (± 100 ppm/°C)± 1.0 %3.0 % or 3 Ω7)± 0.001 % (± 10 ppm/°C)± 0.5 %3 Ω typical, 10 Ω maximum TEST GROUP IIIShock (specified pulse)Vibration (high-frequency)Contact resistance variation - CRV (noise)Salt spray± 1.0 %± 1.0 %± 3.0 % or 3 Ω7)No corrosion ± 0.5 %± 0.5 %3 Ω typical, 10 Ω maximumNo corrosion TEST GROUP IV Solder heatLife (1000 h at + 85 °C)8)Contact resistance variation - CRV (noise)± 1.0 %± 2.0 %± 3.0 % or 3 Ω7)± 0.05 %± 0.5 %3 Ω typical, 10 Ω maximum TEST GROUP VLow-temperature operation High-temperature exposureContact resistance variation - CRV (noise)± 1.0 %± 2.0 %± 3.0 % or 3 Ω7)± 0.5 %± 0.5 %3 Ω typical, 10 Ω maximum TEST GROUP VI Rotational lifeContact resistance variation - CRV (noise)Terminal strength ± 2.0 %± 3.0 % or 3 Ω7)2 lbs± 2.0 %3 Ω typical, 10 Ω maximum2 lbs TEST GROUP VIISolderability (excluding termination L)Immersion (excluding termination L)MIL-STD-202 method 208No continuous stream of bubblesMIL-STD-202 method 208No continuous stream of bubbles TEST GROUP VIII Fungus MIL-STD-810 method 508No mechanical damageMIL-STD-810 method 508No mechanical damageDocument Number: 63055For any questions, contact: foil@1202Bulk Metal ® Foil Technology Precision Trimming Potentiometers, 1 1/4 Inch Rectilinear, RJ12 Style, Designed to Meet or Exceed The Requirements of MIL-PRF-22097, Char. FVishay Foil Resistors Note* For non-standard requests, please contact Application Engineering.TABLE 6 - GLOBAL PART NUMBER INFORMATIONNEW GLOBAL PART NUMBER:Y5050500R000K0L (preferred part number format)DENOTES PRECISIONVALUE AER*YR = ΩK = k Ω0 = standard 1 - 999 = customPRODUCT CODE TOLERANCE PACKAGING 5050 = 1202L 0050 = 1202LB 0051 = 1202P 6050 = 1202PB 5051 = 1202Y 7050 = 1202YBJ = ± 5 %K = ± 10 %M = ± 20 %L = bulk packFOR EXAMPLE: ABOVE GLOBAL ORDER Y5050 500R000 K 0 L:TYPE: 1202L VALUE: 500.0 ΩABSOLUTE TOLERANCE: ± 10.0 %AER: standardPACKAGING: bulk packHISTORICAL PART NUMBER:1202L 500R00 K B (will continue to be used)1202L 500R00K B MODEL RESISTANCE VALUETOLERANCE PACKAGING 1202L 1202LB 1202P 1202PB 1202Y 1202YB500.0 ΩJ = ± 5 %K = ± 10 %M = ± 20 %B = bulk pack05050R 00Y 5K 00LDisclaimer Legal Disclaimer NoticeVishayAll product specifications and data are subject to change without notice.Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, “Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay’s terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.Product names and markings noted herein may be trademarks of their respective owners.元器件交易网Document Number: 。

ISL12022MAIBZ;中文规格书,Datasheet资料

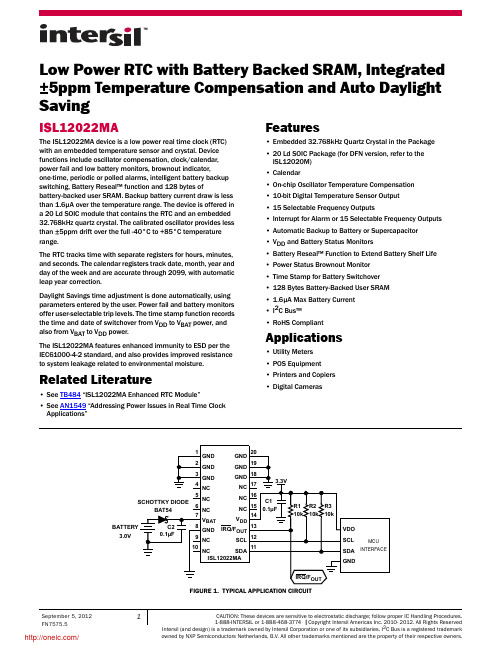

Low Power RTC with Battery Backed SRAM, Integrated ±5ppm Temperature Compensation and Auto Daylight SavingISL12022MAThe ISL12022MA device is a low power real time clock (RTC) with an embedded temperature sensor and crystal. Device functions include oscillator compensation, clock/calendar, power fail and low battery monitors, brownout indicator,one-time, periodic or polled alarms, intelligent battery backup switching, Battery Reseal™ function and 128 bytes ofbattery-backed user SRAM. Backup battery current draw is less than 1.6µA over the temperature range. The device is offered in a 20Ld SOIC module that contains the RTC and an embedded 32.768kHz quartz crystal. The calibrated oscillator provides less than ±5ppm drift over the full -40°C to +85°C temperature range.The RTC tracks time with separate registers for hours, minutes, and seconds. The calendar registers track date, month, year and day of the week and are accurate through 2099, with automatic leap year correction.Daylight Savings time adjustment is done automatically, using parameters entered by the user. Power fail and battery monitors offer user-selectable trip levels. The time stamp function records the time and date of switchover from V DD to V BAT power, and also from V BAT to V DD power.The ISL12022MA features enhanced immunity to ESD per the IEC61000-4-2 standard, and also provides improved resistance to system leakage related to environmental moisture.Related Literature•See TB484 “ISL12022MA Enhanced RTC Module”•See AN1549 “Addressing Power Issues in Real Time Clock Applications”Features•Embedded 32.768kHz Quartz Crystal in the Package •20 Ld SOIC Package (for DFN version, refer to the ISL12020M)•Calendar•On-chip Oscillator Temperature Compensation •10-bit Digital Temperature Sensor Output •15 Selectable Frequency Outputs•Interrupt for Alarm or 15 Selectable Frequency Outputs •Automatic Backup to Battery or Supercapacitor •V DD and Battery Status Monitors•Battery Reseal™ Function to Extend Battery Shelf Life •Power Status Brownout Monitor •Time Stamp for Battery Switchover •128 Bytes Battery-Backed User SRAM •1.6µA Max Battery Current •I 2C Bus™•RoHS CompliantApplications•Utility Meters •POS Equipment •Printers and Copiers •Digital CamerasFIGURE 1.TYPICAL APPLICATION CIRCUITGND GND GND NC GND GND GND NC NC NC NC NC V BAT V DD GNDIRQ/F OUTNCNCSCL SDA ISL12022MA1234567891020191817161514131211SCHOTTKY DIODEBAT54BATTERY 3.0V3.3V C20.1µFC10.1µFR110k R210k R310kVDO SCLSDA GNDMCUINTERFACE IRQ/F OUTBlock DiagramPin ConfigurationISL12022MA (20 LD SOIC)TOP VIEWI 2CINTERFACECONTROL LOGIC ALARMFREQUENCYOUTRTC DIVIDERSDA BUFFER CRYSTAL OSCILLATORPORSWITCH SCL BUFFERSDA SCLV DDV BAT INTERNAL SUPPLYV TRIPSECONDSMINUTES HOURS DAY OF WEEKDATE MONTHYEARUSER SRAMCONTROL REGISTERS GNDREGISTERSTEMPERATURESENSORFREQUENCY CONTROLIRQ/F OUT+-GND NC NC GND NC NC1 234567891020 19 18 17 16 15 14 13 12 11GND NC NC V DD GND GND NC V BAT GND GND NC IRQ/F OUT SCL SDAPin DescriptionsPIN NUMBER SYMBOL DESCRIPTION4, 5, 6, 9, 10, 15, 16, 17NC No Connection . Do not connect to a signal or supply voltage.7V BATBackup Supply . This input provides a backup supply voltage to the device. VBAT supplies power to the device in the event that the VDD supply fails. This pin can be connected to a battery, a supercapacitor or tied to ground if not used. See the Battery Monitor parameter in the “” table on page 6. This pin should be tied to ground if not used.11SDASerial Data . SDA is a bi-directional pin used to transfer data into and out of the device. It has an open drain output and may be OR’ed with other open drain or open collector outputs. The input buffer is always active (not gated) in normal mode.An open drain output requires the use of a pull-up resistor. The output circuitry controls the fall time of the output signal with the use of a slope controlled pull-down. The circuit is designed for 400kHz I 2C interface speeds. It is disabled when the backup power supply on the VBAT pin is activated.12SCLSerial Clock . The SCL input is used to clock all serial data into and out of the device. The input buffer on this pin is always active (not gated). It is disabled when the backup power supply on the VBAT pin is activated to minimize power consumption.13IRQ/F OUT Interrupt Output/Frequency Output (Default 32.768kHz frequency output).This dual function pin can be used as an interrupt or frequency output pin. The IRQ/F OUT mode is selected via the frequency out control bits of the control/statusregister. Interrupt Mode. The pin provides an interrupt signal output. This signal notifies a host processor that an alarmhas occurred and requests action. It is an open drain active low output. Frequency Output Mode. The pin outputs a clocksignal, which is related to the crystal frequency. The frequency output is user selectable and enabled via the I2C bus. Itis an open drain output. The output is open drain and requires a pull-up resistor.14V DD Power Supply. Chip power supply and ground pins. The device will operate with a power supply from V DD = 2.7V to5.5VDC. A 0.1µF capacitor is recommended on the VDD pin to ground.1, 2, 3, 8, 18, 19, 20GND Ground Pin.Pin Descriptions (Continued)PIN NUMBER SYMBOL DESCRIPTION Ordering InformationPART NUMBER (Notes 2, 3)PARTMARKINGV DD RANGE(V)TEMP RANGE(°C)PACKAGE(RoHS Compliant)PKG.DWG. #ISL12022MAIBZ ISL12022MAIBZ 2.7 to 5.5-40 to +8520 Ld SOIC M20.3ISL12022MAIBZ-T (Note 1)ISL12022MAIBZ 2.7 to 5.5-40 to +8520 Ld SOIC (Tape and Reel)M20.31.Please refer to TB347 for details on reel specifications.2.These Intersil plastic packaged products employ special material sets, molding compounds and 100% matte tin plate plus anneal (e3) terminationfinish. These products do contain Pb but they are RoHS compliant by exemption 7 (Pb in high melting temperature type solders, electronic ceramic parts (e.g. piezoelectronic devices)) and exemption 5 (Pb in glass of electronic components). These Intersil RoHS compliant products are compatible with both SnPb and Pb free soldering operations. These Intersil RoHS compliant products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.3.For Moisture Sensitivity Level (MSL), please see device information page for ISL12022MA. For more information on MSL please see Tech BriefTB363.Table of ContentsBlock Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 Pin Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2Pin Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 Ordering Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3 Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6Thermal Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6DC Operating Characteristics RTC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6Power-Down Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7I2C Interface Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7SDA vs SCL Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Symbol Table. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9 Typical Performance Curves . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Power Control Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Normal Mode (V DD) to BatteryBackup Mode (V BAT). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Battery Backup Mode (V BAT) toNormal Mode (V DD). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Power Failure Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Brownout Detection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 Battery Level Monitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12Real Time Clock Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Single Event and Interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Frequency Output Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 General Purpose User SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 I2C Serial Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Oscillator Compensation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13Register Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Real Time Clock Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Addresses [00h to 06h] . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15Control and Status Registers (CSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Addresses [07h to 0Fh]. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 Power Supply Control Register (PWR_VDD). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Battery Voltage Trip Voltage Register(PWR_VBAT). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Initial AT and DT Setting Register (ITRO) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 ALPHA Register (ALPHA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19 BETA Register (BETA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20 Final Analog Trimming Register (FATR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Final Digital Trimming Register (FDTR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 ALARM Registers (10h to 15h) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Time Stamp VDD to Battery Registers (TSV2B). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 Time Stamp Battery to VDD Registers (TSB2V). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 DST Control Registers (DSTCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23 TEMP Registers (TEMP). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23 NPPM Registers (NPPM). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 XT0 Registers (XT0). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24ALPHA Hot Register (ALPHAH). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 User Registers (Accessed by Using Slave Address 1010111x). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Addresses [00h to 7Fh]. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 I2C Serial Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Protocol Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Device Addressing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 Write Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 Read Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 Application Section. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 Power Supply Considerations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 Battery Backup Details. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 Layout Considerations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 Measuring Oscillator Accuracy. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 Temperature Compensation Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 Daylight Savings Time (DST) Example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 Device Handling Precautions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 Revision History. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Products . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Package Outline Drawing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31Absolute Maximum Ratings Thermal InformationVoltage on V DD, V BAT and IRQ/F OUT pins(Respect to Ground). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . -0.3V to 6.0V Voltage on SCL and SDA pins(Respect to Ground). . . . . . . . . . . . . . . . . . . . . . . . . . .-0.3V to V DD+0.3V ESD RatingHuman Body Model (Per JESD22-A114F) . . . . . . . . . . . . . . . . . . . . . . >3kV Machine Model (Per JESD22-A115B) . . . . . . . . . . . . . . . . . . . . . . . .>300V Charge Device Model (Per JESD22-C101D) . . . . . . . . . . . . . . . . . . . .2.2kV Latch Up (Tested per JESD-78B; Class 2, Level A) . . . . . . . . . . . . . . 100mA Shock Resistance. . . . . . . . . . . . . . . . . . . . . . . . . . .5000g, 0.3ms, 1/2 sine Vibration (Ultrasound cleaning not advised). . . . . . . . . . .20g/10-2000Hz,Thermal Resistance (Typical)θJA (°C/W)θJC (°C/W) 20 Lead SOIC (Notes 4, 5). . . . . . . . . . . . . . 7035 Storage Temperature. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .-40°C to +85°C Pb-Free Reflow Profile (Note 6). . . . . . . . . . . . . . . . . . . . . . . . see link below /pbfree/Pb-FreeReflow.aspCAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.NOTES:4.θJA is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.5.For θJC, the “case temp” location is on top of the package and measured in the center of the package between pins 6 and 15.6.The ISL12022MA Oscillator Initial Accuracy can change after solder reflow attachment. The amount of change will depend on the reflow temperatureand length of exposure. A general rule is to use only one reflow cycle and keep the temperature and time as short as possible. Changes on the order of ±1ppm to ±3ppm can be expected with typical reflow profiles.DC Operating Characteristics RTC Test Conditions: VDD = +2.7 to +5.5V, TA = -40°C to +85°C, unless otherwise stated. Boldface limits apply over the operating temperature range, -40°C to +85°C.SYMBOL PARAMETER CONDITIONSMIN(Note 7)TYP(Note 8)MAX(Note 7)UNITS NOTESV DD Main Power Supply(Note 15) 2.7 5.5VV BAT Battery Supply Voltage(Note 15) 1.8 5.5V9I DD1Supply Current. (I2C Not Active,Temperature Conversion Not Active, F OUTNot Active)V DD = 5V 4.115µA10, 11 V DD = 3V 3.514µA10, 11I DD2Supply Current. (I2C Active, TemperatureConversion Not Active, F out Not Active)V DD = 5V200500µA10, 11I DD3Supply Current. (I2C Not Active,Temperature Conversion Active, F OUT NotActive)V DD = 5V120400µA10, 11I BAT Battery Supply Current V DD = 0V, V BAT = 3V, T A=+25°C 1.0 1.6µA10V DD = 0V, V BAT = 3V 1.0 5.0µA10 I BATLKG Battery Input Leakage V DD = 5.5V, V BAT = 1.8V100nAI LI Input Leakage Current on SCL V IL = 0V, V IH = V DD-1.0±0.1 1.0µAI LO I/O Leakage Current on SDA V IL = 0V, V IH = V DD-1.0±0.1 1.0µAV BATM Battery Level Monitor Threshold-100+100mVV PBM Brownout Level Monitor Threshold-100+100mVV TRIP V BAT Mode Threshold(Note 15) 2.0 2.2 2.4VV TRIPHYS V TRIP Hysteresis30mV13 V BATHYS V BAT Hysteresis50mV13OSCILLATOR ACCURACYΔFout I Oscillator Initial AccuracyV DD = 3.3V -2+8ppm 6, 17ΔFout R Oscillator Accuracy after Reflow Cycle V DD = 3.3V ±5ppm 6, 17ΔFout T Oscillator Stability vs Temperature V DD = 3.3V ±2ppm 6, 18ΔFout V Oscillator Stability vs Voltage 2.7V ≤ V DD ≤ 5.5V -3+3ppm 19TempTemperature Sensor AccuracyV DD = V BAT = 3.3V±2°C13IRQ/F OUT (OPEN DRAIN OUTPUT)V OLOutput Low VoltageV DD = 5V, I OL = 3mA 0.4V V DD = 2.7V, I OL = 1mA0.4VDC Operating Characteristics RTCTest Conditions: VDD = +2.7 to +5.5V, TA = -40°C to +85°C, unless otherwise stated. Boldfacelimits apply over the operating temperature range, -40°C to +85°C. (Continued)SYMBOLPARAMETERCONDITIONSMIN (Note 7)TYP (Note 8)MAX (Note 7)UNITSNOTESPower-Down TimingTest Conditions: VDD = +2.7 to +5.5V, Temperature = -40°C to +85°C, unless otherwise stated. Boldface limits applyover the operating temperature range, -40°C to +85°C.SYMBOL PARAMETERCONDITIONSMIN (Note 7)TYP (Note 8)MAX (Note 7)UNITS NOTES V DDSR-V DD Negative Slew Rate10V/ms 12V DDSR+V DD Positive Slew Rate, minimum0.05V/ms16I 2C Interface SpecificationsTest Conditions: V DD = +2.7 to +5.5V, Temperature = -40°C to +85°C, unless otherwise specified. Boldfacelimits apply over the operating temperature range, -40°C to +85°C.SYMBOL PARAMETERTEST CONDITIONSMIN (Note 7)TYP (Note 8)MAX (Note 7)UNITS NOTESV IL SDA and SCL Input Buffer LOW Voltage-0.30.3 x V DD V V IH SDA and SCL Input Buffer HIGH Voltage0.7 x V DDV DD + 0.3V Hysteresis SDA and SCL Input Buffer Hysteresis0.05 x V DD V 13, 14V OL SDA Output Buffer LOW Voltage, Sinking 3mA V DD = 5V, I OL = 3mA 00.020.4V C PINSDA and SCL Pin Capacitance T A = +25°C, f = 1MHz, V DD = 5V, V IN =0V, V OUT = 0V10pF13, 14f SCL SCL Frequency400kHz t INPulse Width Suppression Time at SDA and SCL InputsAny pulse narrower than the max spec is suppressed.50nst AASCL Falling Edge to SDA Output Data ValidSCL falling edge crossing 30% of V DD , until SDA exits the 30% to 70% of V DD window.900nst BUFTime the Bus Must be Free Before the Start of a New Transmission SDA crossing 70% of V DD during a STOP condition, to SDA crossing 70% of V DD during the following START condition.1300nst LOW Clock LOW Time Measured at the 30% of V DD crossing.1300ns t HIGHClock HIGH TimeMeasured at the 70% of V DD crossing.600nst SU:STA START Condition Setup TimeSCL rising edge to SDA falling edge. Both crossing 70% of V DD .600ns t HD:STASTART Condition Hold TimeFrom SDA falling edge crossing 30% of V DD to SCL falling edge crossing 70% of V DD .600nst SU:DATInput Data Setup TimeFrom SDA exiting the 30% to 70% of V DD window, to SCL rising edge crossing 30% of V DD.100nst HD:DATInput Data Hold Time From SCL falling edge crossing 30% of V DD to SDA entering the 30% to 70% of V DD window.20900nst SU:STOSTOP Condition Setup TimeFrom SCL rising edge crossing 70% of V DD , to SDA rising edge crossing 30% of V DD .600nst HD:STO STOP Condition Hold Time From SDA rising edge to SCL falling edge.Both crossing 70% of V DD .600ns t DHOutput Data Hold TimeFrom SCL falling edge crossing 30% of V DD , until SDA enters the 30% to 70% of V DD window.nst R SDA and SCL Rise Time From 30% to 70% of V DD.20 +0.1 x Cb 300ns 13, 14t F SDA and SCL Fall TimeFrom 70% to 30% of V DD.20 +0.1 x Cb300ns 13, 14Cb Capacitive Loading of SDA or SCLTotal on-chip and off-chip 10400pF 13, 14R PUSDA and SCL Bus Pull-up Resistor Off-chipMaximum is determined by t R and t F .For Cb = 400pF, max is about 2k Ω~2.5k Ω.For Cb = 40pF, max is about 15k Ω~20k Ω1k Ω13, 14NOTES:7.Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.8.Specified at +25°C.9.Temperature Conversion is inactive below V BAT = 2.7V. Device operation is not guaranteed at V BAT <1.8V.10.IRQ/F OUT inactive.11.V DD > V BAT +V BATHYS12.In order to ensure proper timekeeping, the V DD SR- specification must be followed.13.Limits should be considered typical and are not production tested.14.These are I 2C specific parameters and are not tested, however, they are used to set conditions for testing devices to validate specification.15.Minimum V DD and/or V BAT of 1V to sustain the SRAM. The value is based on characterization and it is not tested.16.To avoid EEPROM recall issues, it is advised to use this minimum power up slew rate. Not tested, shown as typical only.17.Defined as the deviation from a target oscillator frequency of 32,768.0Hz at room temperature.18.Defined as the deviation from the room temperature measured 1Hz frequency, V DD = 3.3V, at T A = -40°C to +85°C.19.Defined as the deviation at room temperature from the measured 1Hz frequency (or equivalent) at V DD = 3.3, over the range of V DD = 2.7V toV DD =5.5V.I 2C Interface SpecificationsTest Conditions: V DD = +2.7 to +5.5V, Temperature = -40°C to +85°C, unless otherwise specified. Boldfacelimits apply over the operating temperature range, -40°C to +85°C. (Continued)SYMBOL PARAMETERTEST CONDITIONSMIN (Note 7)TYP (Note 8)MAX (Note 7)UNITS NOTES。

IEEE1202